(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6000708号

(P6000708)

(45) 発行日 平成28年10月5日(2016.10.5)

(24) 登録日 平成28年9月9日(2016.9.9)

(51) Int.Cl.

F 1

G06F 12/00 (2006.01)

G06F 12/06 (2006.01)G06F 12/00 550E

G06F 12/06 540E

G06F 12/00 597U

G06F 12/06 515H

請求項の数 9 (全 14 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2012-161964 (P2012-161964) |

| (22) 出願日  | 平成24年7月20日 (2012.7.20)       |

| (65) 公開番号 | 特開2014-21859 (P2014-21859A)  |

| (43) 公開日  | 平成26年2月3日 (2014.2.3)         |

| 審査請求日     | 平成27年7月13日 (2015.7.13)       |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】メモリ制御装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のバンクを有する不揮発メモリを制御するメモリ制御装置であって、

複数のバンクの間でバンクインターリープのアクセスを行う第1の領域と、バンクインターリープのアクセスを行わない第2の領域のいずれかの領域に、前記不揮発メモリにおける複数のバンクを設定し、前記不揮発メモリへのアクセス制御を行うメモリアクセス手段と、

前記第1の領域のバンクと前記第2の領域のバンクとを独立に省電力状態に制御する電力制御手段とを備えることを特徴とするメモリ制御装置。

## 【請求項 2】

前記電力制御手段は、前記第1の領域の複数のバンクを一括して前記省電力状態に制御することを特徴とする請求項1に記載のメモリ制御装置。

## 【請求項 3】

前記電力制御手段は、前記第2の領域の少なくとも一つのバンクを独立に前記省電力状態に制御することを特徴とする請求項1または2に記載のメモリ制御装置。

## 【請求項 4】

前記電力制御手段は、前記第2の領域の複数のバンクを一括して前記省電力状態に制御することを特徴とする請求項1または2に記載のメモリ制御装置。

## 【請求項 5】

CPUを備え、

前記第2の領域のバンクには前記CPUにより実行されるプログラムが記憶され、前記第1の領域のバンクには前記プログラムを前記CPUが実行するときに使用されるデータが記憶されることを特徴とする請求項1から4のいずれか1項に記載のメモリ制御装置。

**【請求項6】**

前記電力制御手段は、前記第1の領域のバンクに対するアクセス要求が所定時間発行されない場合に、前記第1の領域のバンクを省電力状態にすることを特徴とする請求項1から5のいずれか1項に記載のメモリ制御装置。

**【請求項7】**

前記電力制御手段は、前記第1の領域のバンクが省電力状態である場合に、前記第1の領域のバンクに対するアクセス要求が発行されたことに応じて、前記第1のバンクを通常動作状態にすることを特徴とする請求項1から6のいずれか1項に記載のメモリ制御装置

10

**【請求項8】**

前記メモリアクセス手段は、前記第1の領域のバンクに対しては、前記第1の領域に設定された複数のバンクに跨るように連続した論理アドレスを割り当て、前記第2の領域のバンクに対しては、一つのバンクの先頭から終端まで連続した論理アドレスを割り当てるることを特徴とする請求項1から7のいずれか1項に記載のメモリ制御装置。

**【請求項9】**

複数のバンクを有する不揮発メモリを制御するメモリ制御装置のメモリ制御方法であつて、

20

複数のバンクの間でバンクインターリープのアクセスを行う第1の領域と、バンクインターリープのアクセスを行わない第2の領域のいずれかの領域に、前記不揮発メモリにおける複数のバンクを設定し、前記不揮発メモリへのアクセス制御を行うメモリアクセス工程と、

前記第1の領域のバンクと前記第2の領域のバンクとを独立に省電力状態に制御する電力制御工程とを有することを特徴とするメモリ制御方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

不揮発性メモリによる記憶領域へのアクセスを制御するメモリ制御装置および方法に関する。

30

**【背景技術】**

**【0002】**

近年、磁性体を用いた磁気抵抗メモリ(Magnetoresistive Random Access Memory、以下MRAMと称する)が注目されている。MRAMは磁気によって情報を記憶するメモリであり、不揮発性であるとともに、スタティックRAM(以下SRAMと称する)並みの高速なアクセス性能を実現している。これらの特徴により、将来ダイナミックRAM(以下DRAMと称する)の代わりに利用することも可能であると同時に、SRAMやDRAMでは実現できない、電源オフでも記憶を維持し続けるメモリシステムを構成出来る。また記憶は磁性効果によって維持される仕組みである為、記憶部にフリップフロップ回路を用いるSRAMのように回路が複雑化することも無く、大容量化も容易である。

40

**【0003】**

不揮発性メモリを用いて装置のメインメモリを構成する例として、特許文献1の無線装置に関する提案がある。特許文献1によれば、電源OFFでも記憶状態を維持するMRAMを装置のメインメモリとして使用することで、揮発性メモリの量を削減し電力消費を低減できるといった効果が得られることが記載されている。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献1】特開2005-26912号公報**

50

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

特許文献1の構成によれば、MRAMにより構成された2つのメインメモリを切り替えて用いるため、使用中でない方のメインメモリの電源をオフすることで省電力を図ることができる。しかしながら、特許文献1には、使用中のメインメモリにおいて、記憶領域のうちの一部の領域（例えば、メモリバンク）への電源供給をオフにして省電力を図るという着想はない。一般に、メモリシステムにおいて、メモリ領域内におけるデータやプログラムの配置は複雑である。例えばメモリ領域が複数のメモリバンク（以下、バンクともいう）によって構成されている場合にはプログラムやデータが複数のバンクに跨って配置されることも有り得る。また一つのバンクにプログラムやデータが混在している可能性もある。特に、データの読み出しや書き込みを高速化するべくインターリープ方式のメモリアクセスを採用した場合には、その複雑さが増す。したがって、これらのようなケースに於いて、どのバンクが電源オン・オフ制御可能であるかを正確に判断することは極めて困難である。そのため、バンク単位での電源のオン、オフによる省電力化の実現は困難であった。

10

**【0006】**

本発明は上記の課題に鑑みてなされたものであり、インターリープ領域と非インターリープ領域が混在するメモリ空間において、バンクを単位とした電源のオン、オフにより消費電力の低減を実現することを目的とする。

**【課題を解決するための手段】**

20

**【0007】**

上記の目的を達成するための本発明の一態様によるメモリシステムは以下の構成を備える。すなわち、

複数のバンクを有する不揮発メモリを制御するメモリ制御装置であって、

複数のバンクの間でバンクインターリープのアクセスを行う第1の領域と、バンクインターリープのアクセスを行わない第2の領域のいずれかの領域に、前記不揮発メモリにおける複数のバンクを設定し、前記不揮発メモリへのアクセス制御を行うメモリアクセス手段と、

前記第1の領域のバンクと前記第2の領域のバンクとを独立に省電力状態に制御する電力制御手段とを備える。

30

**【発明の効果】****【0008】**

本発明によれば、インターリープ領域と非インターリープ領域が混在するメモリ空間において、バンクを単位とした電源のオン、オフにより消費電力の低減を実現することができる。

**【図面の簡単な説明】****【0009】**

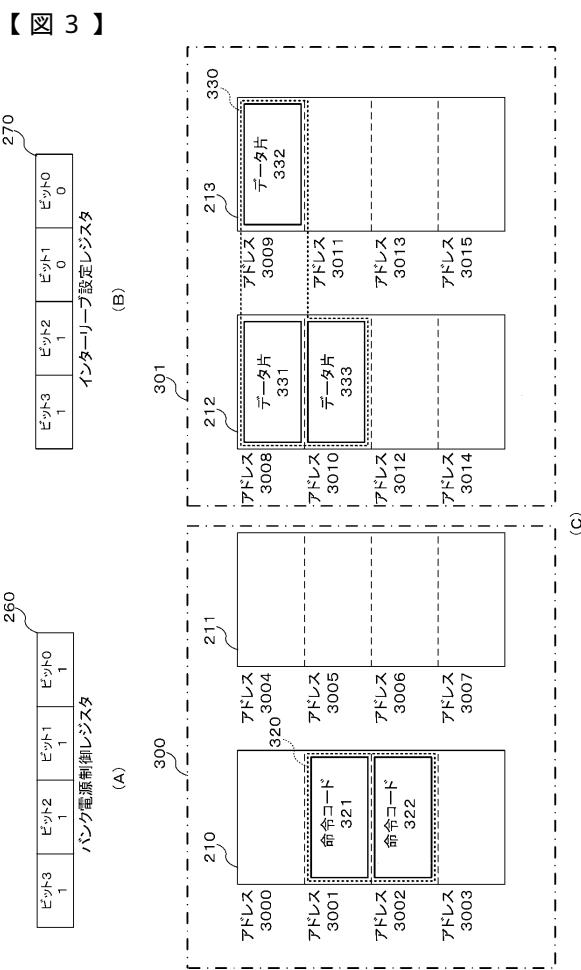

【図1】一般的なインターリープ構成を説明する図。

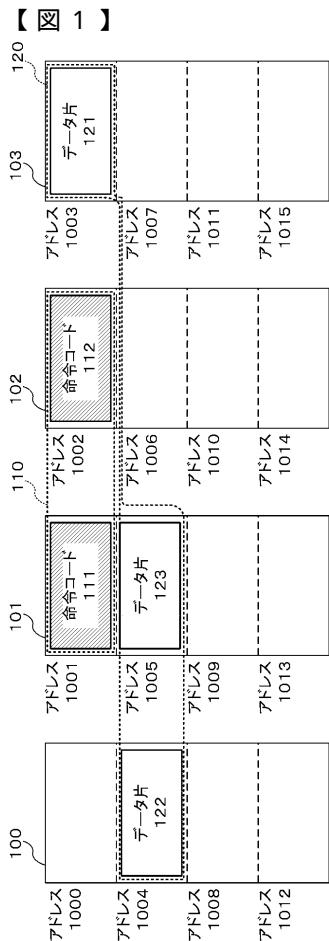

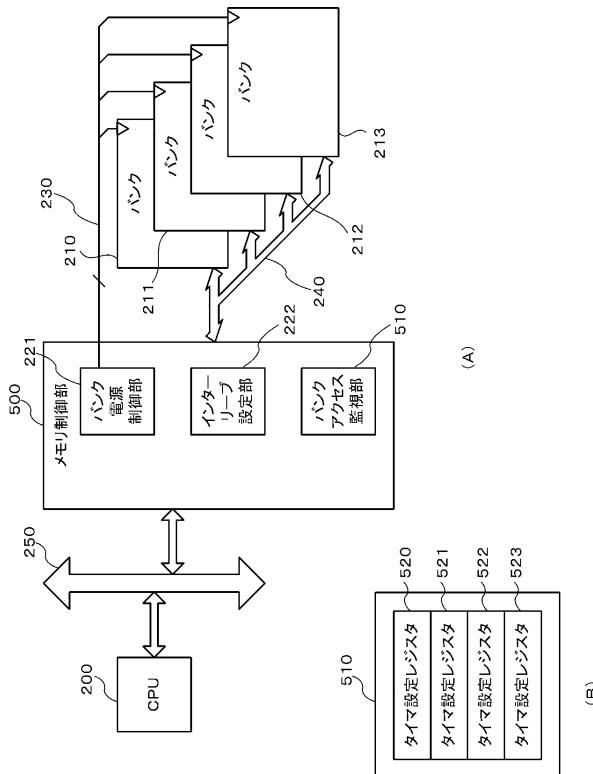

【図2】(A)は第一実施形態によるメモリシステム構成例を示す図、(B)はバンク電源制御レジスタを説明する図、(C)はインターリープ設定レジスタを説明する図。

40

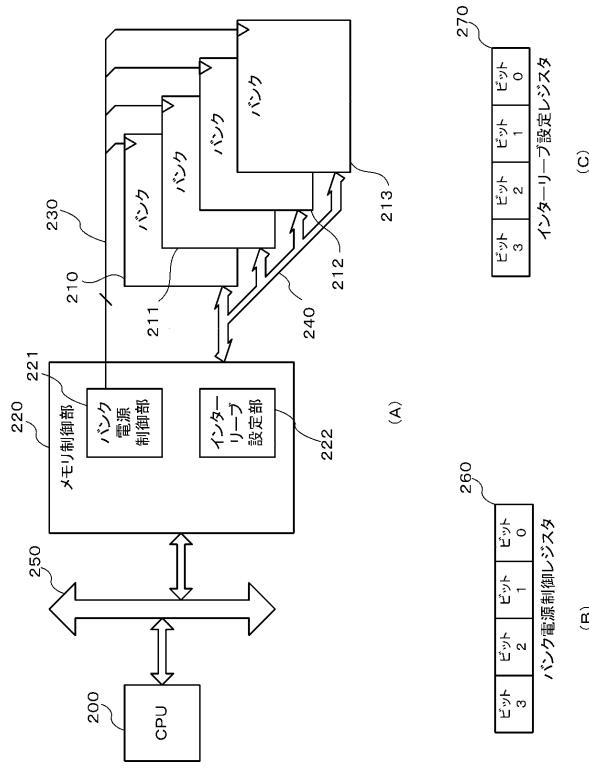

【図3】(A)は第一実施形態におけるバンク電源制御レジスタの設定状態を示す図、(B)はインターリープ設定レジスタの設定状態を示す図、(C)はインターリープ構成を説明する図。

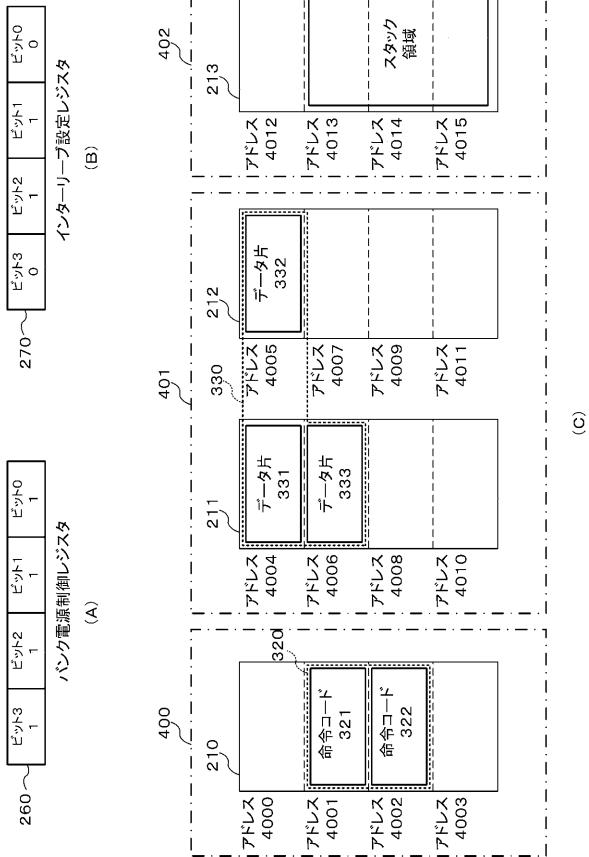

【図4】(A)は第二実施形態におけるバンク電源制御レジスタの設定状態を示す図、(B)はインターリープ設定レジスタの設定状態を示す図、(C)はインターリープ構成を説明する図。

【図5】(A)は第三実施形態によるメモリシステム構成例を示す図、(B)はタイマ設定レジスタを示す図。

【図6】(A)はバンク210の物理及び論理アドレスを示す図、(B)はバンク213の物理及び論理アドレスを示す図、(C)はバンク211、212の物理及び論理アドレ

50

スを示す図、(D)はバンク211、212の物理及び論理アドレスを示す図。

【図7】図6に示したバンク210、211、212、213の物理及び論理アドレスを示す図。

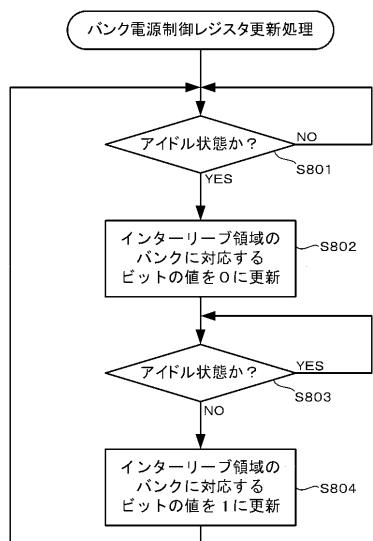

【図8】バンク電源制御レジスタの更新処理の例を示すフローチャート。

【発明を実施するための形態】

【0010】

以下、本発明の実施形態のいくつかについて図面を参照しながら説明する。

【0011】

[第一実施形態]

実施形態の構成及び効果に言及するに先立って、まず本提案が課題としている構成について説明する。 10

【0012】

メモリインターリープ(以下インターリープと称する)は、CPUがメモリに対してアクセス要求を行ってから実際にデータを読み出したり、データの書き込みを完了したりするまでのレイテンシを削減し、メモリアクセスを高速化する上で重要な仕組みである。インターリープでは、複数のメモリバンクに跨って連続したアドレスを交互に振っておき、あるバンクのデータにアクセスする遅延時間の最中に次のバンクのアドレスへのアクセス要求が発行される。そのため、時間を有効利用することができ、メモリアクセス効率が向上する。

【0013】

インターリープを構成した場合、たとえば、図1に示すようなメモリ空間の利用が考えられる。図1では、バンク100～103の4つのバンクを利用したインターリープの例を示している。メモリ上に配置されるプログラム110が複数のバンク(バンク101、102)に跨り、且つこのプログラムによって使用されるデータ120が複数のバンク(バンク100、101、103)に跨るように配置されている。ここで例えばデータ120が、CPUやその他周辺デバイスとの間で高速アクセスを要する場合、インターリープの特性により高速アクセスが実現可能になる。 20

【0014】

ここで不揮発性メモリ(例えば、MRAM)によるメモリシステムでインターリープを構成する場合について考える。不揮発性メモリは電源オフでも記憶を維持し続ける。その為、例えば装置の特定の状態に於いてデータやプログラムの部分若しくは全体が未使用状態である場合には、未使用状態のデータ若しくはプログラムが格納されているバンクの電源を一時的に切り、必要に応じて電源供給をオンにするといった使い方が可能になる。このような電源制御は省電力に貢献することが明らかである。 30

【0015】

次にこのメモリシステムに於いて、必要に応じてバンクへの電源供給のオン・オフを切り替える場合の、より効率的なプログラム及びデータの配置方法について考える。図1は不揮発性メモリで構成されるバンク100、101、102、103から成るメモリ領域において、全てのバンクがインターリープ構成になっている状態を示している。命令コード111、112から成るプログラム110、及びデータ片121、122、123から成るデータ120が図1のように配置されている場合を考える。この場合、不図示のCPUやその他周辺デバイスからのデータ120に対するアクセスが一時的に無い状態の時には、データ120の格納バンクに関しては電源オフにして電力を削減することができる。 40

【0016】

このとき、バンク100及び103に配置されているのは夫々データ片122、121のみでありプログラム110の命令コードのいずれも含まれていない。その為、一時的にデータ120へのアクセスが無い場合にこれらバンク100、103の電源をオフにしてもプログラム110の実行に支障は無い。しかしながらバンク101にはデータ片123だけでなくプログラム110の命令コード111も配置されている。よって、このプログラム110の稼動中にバンク101の電源オフを実施すると、プログラム110の実行に 50

支障をきたしてしまう為、データ 120へのアクセスが無い場合でもバンク 101 の電源をオフにすることは出来ない。

#### 【0017】

次に、本実施形態のメモリ制御装置としてのメモリアクセス装置について、図 2 を用いて説明する。図 2 (A) は本実施形態によるメモリアクセス装置を含むメモリシステム周辺の構成例を示すブロック図である。CPU 200 はメモリに対して読み出しや書き込みアクセスを行う中央処理回路であり、バンク 210、211、212、213 は不揮発性メモリから成るメモリバンクである。メモリ制御部 220 は、バンク 210、211、212、213 によって構成されるメモリ領域へのメモリアクセス制御を行なう回路である。バンク電源制御部 221 はバンク 210、211、212、213 の電源オン・オフ状態を設定するレジスタを備えた制御回路である。インターリープ設定部 222 は各バンクをインターリープ領域として扱うか、若しくは非インターリープ領域として扱うかを設定する回路である。10

#### 【0018】

バンク電源制御線 230 はバンク電源制御部 221 からバンク 210、211、212、213 の夫々に接続され、バンク電源制御部 221 に設定された各バンクの電源オン・オフ状態を元に、各バンクの電源を制御するための信号線である。メモリバス 240 はメモリ制御部 220 とバンク 210、211、212、213 を接続し、メモリアクセスのためのアドレス線とデータ線及び制御線からなるバスである。システムバス 250 は CPU 200 とメモリ制御部 220 若しくは不図示の周辺デバイスとを接続するバスである。20

#### 【0019】

図 2 (B) は、バンク電源制御部 221 が有するバンク電源制御レジスタ 260 を示す。バンク電源制御レジスタ 260 は、複数のバンクの各々について電源供給をオンするかオフするかを示す情報を保持する。この実施形態では、バンク電源制御レジスタ 260 は 4 ビットから成り、ビット 0、1、2、3 の夫々がバンク 210、211、212、213 に対応する。バンク電源制御部 221 は、バンク電源制御レジスタ 260 のビットの値が 0 の時はそのビットに対応するバンク電源の供給をオフに、1 の時にはそのビットに対応するバンク電源の供給をオンにする。

#### 【0020】

図 2 (C) にインターリープ設定部 222 が有するインターリープ設定レジスタ 270 を示す。インターリープ設定レジスタは、複数のバンクの各々についてインターリープ領域と非インターリープ領域のいずれに設定されているかを示す設定情報を保持する。この実施形態では、インターリープ設定レジスタ 270 は 4 ビットから成り、ビット 0、1、2、3 の夫々がバンク 210、211、212、213 に対応する。インターリープ設定部 222 は、インターリープ設定レジスタ 270 のビットの値が 0 の時はそのビットに対応するバンクは非インターリープ領域として、1 の時にはそのビットに対応するバンクはインターリープ領域としてアクセスするようアドレスを設定する。なお、インターリープ領域、非インターリープ領域におけるアドレスの設定は、図 3 (C) において詳述する。30

#### 【0021】

次に、図 2 で説明したメモリシステムで実際にインターリープ設定を行い、且つ各バンクの電源制御を行う例を図 3 (A)、(B) 及び (C) を用いて説明する。図 3 (A) は、図 2 (B) で説明したバンク電源制御レジスタ 260 のビット 0 ~ 3 を全て 1 に設定した状態を示している。この場合、バンク電源制御部 221 は、バンク 210 ~ 213 の全てのバンクへの電源供給をオン状態とし、全てのバンクに電源が供給されるようにする。また、図 3 (B) は、図 2 (C) で説明したインターリープ設定レジスタ 270 のビット 0 及び 1 に 0 を、ビット 2 及び 3 に 1 を設定した状態を示している。この場合、バンク 210、211 が非インターリープに、バンク 212、213 がインターリープに設定される。40

#### 【0022】

更に、図 3 (C) は、図 1 の説明で示した 4 つの不揮発性メモリで構成されるバンク 2 50

10、211、212、213から成る非インターリープ領域及びインターリープ領域の構成を示している。本実施形態では、インターリープ設定レジスタ270により、バンク毎にインターリープ、非インターリープを設定できる。そのため、複数のバンク210～213により構成される記憶領域のうちの一部をインターリープ領域に、他の領域を非インターリープ領域に設定することができる。図3(A)のバンク電源制御レジスタ260の設定に基づき、図3(C)のバンク210、211、212、213の夫々の電源がオン状態になっている。また図3(B)のインターリープ設定レジスタ270の設定に基づき、バンク210、バンク211は非インターリープ領域300を、またバンク211、バンク212はインターリープ領域301を構成する。

## 【0023】

10

図3(C)において、アドレス3000～3007は非インターリープ領域300内に割り当てられる論理アドレスであり、このアドレスはバンクを跨ぐこと無くバンク210の先頭から終端、続いてバンク211の先頭から終端の順に割り当てられる。またアドレス3008～3015はインターリープ領域内に割り当てられた論理アドレスであり、この論理アドレスは各バンクに交互に跨るように割り振られる。

## 【0024】

なお、図3の例では、バンク212とバンク213の2つがインターリープに設定されている様子を示したが、3つ以上のバンクがインターリープに設定されてもよい。例えば、インターリープ設定レジスタ270のビット1～3に1が設定されると、バンク211～213の3つのバンクがインターリープで動作するようになる。また、図3に示した複数のインターリープ領域を設定できるようにしてもよい。すなわち、図3(C)において、非インターリープ領域300をインターリープとして設定できるようにしてもよい。その場合、インターリープ設定レジスタ270は、インターリープ領域を識別できるように、各バンクについて2ビット以上の深さを有するように構成される必要がある。例えば、各バンクに対応して2ビットを設ければ、「0：非インターリープ領域」、「1：インターリープ領域A」、「2：インターリープ領域B」、「3：インターリープ領域C」というように、独立したインターリープ領域を3つまで設定することが可能となる。

20

## 【0025】

図3(C)において、プログラム320は命令コード321及び命令コード322から成るプログラムコードであり、CPU200によって実行される。本実施形態ではプログラム320は非インターリープ領域300のバンク210に配置されている。データ330はCPU200による読み出しや書き込みが可能なデータである。本実施形態では、バンク212及び213に跨るように格納されたデータの各部分を夫々データ片331、データ片332、データ片333とする。

30

## 【0026】

今、CPU200はプログラム320を実行しており、かつプログラム320はデータ330に関して読み出し若しくは書き込みアクセスを伴う処理を有しているものとする。データ330はインターリープ領域301に格納されている為、CPU200からの読み出し及び書き込みに関してレイテンシの少ない高速なアクセスが可能である。

## 【0027】

40

ここでCPU200が実行しているプログラム320は、図8のフローチャートで示されるバンク電源制御レジスタ260の更新処理を含む。すなわち、ステップS801において、CPU200は、実行中のプログラムからデータ330へのアクセスが発生しない状態になるのを待つ。例えば、実行中のプログラム320のメイン処理がアイドル状態（例えば、装置が省電力のための待機状態）になり、データ330に対するアクセスが無い状態になったとする。この場合、もはやインターリープ領域301に対する一切のアクセスが発生しない為、インターリープ領域301に含まれるバンク212及び213の電源をオフすることが可能である。したがって、データ330へのアクセスが発生しない状態になったと判定されると、処理はステップS802に進み、CPU200は、バンク電源制御レジスタ260のビット2及び3（インターリープ領域のバンクに対応したビット）

50

を 0 に書き換える。バンク電源制御レジスタ 260 がこのように更新されると、バンク電源制御部 221 は、バンク 212 及び 213 の電源をオフ状態とする。

#### 【 0028 】

その後、ステップ S803において CPU200 はデータ 330へのアクセスが発生する状態に復帰するのを待つ。例えば、実行中のプログラム 320 のメイン処理がアイドル状態から通常状態に復帰すると処理はステップ S804へ進む。ステップ S804において、CPU200 は、ステップ S802 で 0 に書き換えたビット（本例では、インターリープ領域のバンクに対応したビット 2 及び 3）を 1 に書き換える。バンク電源制御レジスタ 260 がこのように更新されると、バンク電源制御部 221 は、バンク 212 及び 213 の電源をオン状態とする。各バンクは全て不揮発性メモリである為、電源オフの状態でもインターリープ領域 301 に配置されているデータ 330 は消える事は無い。従ってバンク電源制御レジスタ 260 のビット 2 及び 3 を 1 に書き戻すことでバンク 212 及び 213 の電源をオンにすれば、再びデータ 330 を読み出すことが出来る。10

#### 【 0029 】

なお、上記第 1 実施形態ではプログラムを非インターリープ領域に、データをインターリープ領域に配置したが、実際の利用にあたっては必ずしもこの配置に限定されるものでは無い。また本実施形態では実運用中にデータへのアクセスが不要になったケースに言及し、データが格納されているインターリープ領域の電源をオン・オフする例を示した。しかしながら、必ずしもインターリープ領域だけが電源オン・オフの対象に限定されるものではなく、実際の適用形態に応じて非インターリープ領域が電源オン・オフされてもよいことは明らかである。すなわち、複数のバンクのうちの一部をインターリープ領域、他のバンクを非インターリープ領域として使用する構成において、インターリープ領域を構成するバンクと非インターリープ領域を構成するバンクとで個別に電源供給が制御されるようにはよい。また、非インターリープ領域への電源供給の制御は、非インターリープ領域を構成する全てのバンクを一括して電源供給のオン、オフを行なってもよいし、非インターリープ領域を構成する個々のバンクに対して個別に電源供給のオン、オフを行なってもよい。さらに、CPU200 が非インターリープ領域 300 及びインターリープ領域 301 へアクセスした場合について説明しているが、必ずしも CPU からのアクセスに限定するものではない。例えば DMA コントローラ等の不図示の周辺デバイスからのアクセスであってもよい。20

#### 【 0030 】

バンク電源制御レジスタ 260 に関しては、各ビットの論理として 0 で電源オフ、1 で電源オンとしたが、必ずしもこの論理に限定するものではなく、例えば 0 で電源オン、1 で電源オフとしてもよい。同様に、インターリープ設定レジスタ 270 に関しては、各ビットの論理として 0 で非インターリープ設定、1 でインターリープ設定としたが、必ずしもこの論理に限定するものではなく、例えば 0 でインターリープ設定、1 で非インターリープ設定としてもよい。また、本実施形態では、バンク電源制御部 221 はメモリ制御部 220 に内蔵しているが、本発明はこのような形態に限られるものではなく、例えば他の周辺回路内にバンク電源制御部 221 が存在してもよい。30

#### 【 0031 】

以上のように、第一実施形態によれば、インターリープ領域と非インターリープ領域とが混在する構成において、バンクを単位とした電源供給が適切に制御され、省電力効果を向上させることができる。40

#### 【 0032 】

##### [ 第二実施形態 ]

第一実施形態では、4 つのバンクから成るメモリ領域を 1 つの非インターリープ領域と 1 つのインターリープ領域の 2 つの領域に分割するケースについて述べた。第二実施形態ではメモリ領域内に 2 つの非インターリープ領域と 1 つのインターリープ領域が混在するケースについて説明する。以下、図 2 で説明したメモリシステムにおいて、2 つの非インターリープ領域を設定し、各バンクの電源制御を行う例を図 4 (A)、(B) 及び (C) 50

を用いて説明する。

**【0033】**

図4(A)は、図2(B)で説明したバンク電源制御レジスタ260のビット0～3を全て1に設定した状態を示している。図4(B)は、図2(C)で説明したインターリープ設定レジスタ270のビット0及び3に0を、ビット1及び2に1を設定した状態を示している。図4(C)は、図1及び第一実施形態で説明したものと同じ不揮発性メモリで構成されるバンク210、211、212、213から成る非インターリープ領域及びインターリープ領域の構成を示している。

**【0034】**

図4(C)に示されるように、図4(B)のインターリープ設定レジスタ270の設定に基づき、バンク210は非インターリープ領域400を、バンク211及び212はインターリープ領域401を、またバンク213は非インターリープ領域を構成する。また図4(A)のバンク電源制御レジスタ260の設定に基づき、バンク210、211、212、213の夫々の電源がオン状態になっている。

10

**【0035】**

図4(C)において、アドレス4000～4003は非インターリープ領域400に、アドレス4004～4011はインターリープ領域401に、アドレス4012～4015は非インターリープ領域402に、割り当てられる論理アドレスである。ここでアドレス4004～4011はインターリープ領域401内のバンク211及び212に交互に跨るように割り当てられる。

20

**【0036】**

プログラム320及びデータ330は第一実施形態で説明したものと同様である。第二実施形態では、データ330はインターリープ領域401に配置される。すなわちバンク211及び212に跨るように格納される。スタック領域413は、プログラム320によって管理され使用されるスタックメモリである。このスタック領域413は、プログラム320が実行される際の一時的な情報の退避及び参照に常時用いられる。

**【0037】**

今、CPU200はプログラム320を実行しており、かつプログラム320はデータ330に対し読み出し若しくは書き込みアクセスを伴う処理を有しているものとする。データ330はインターリープ領域401に格納されている為、CPU200からの読み出し及び書き込みに関してレイテンシの少ない高速なアクセスが可能である。プログラム320は、更に、図8のフローチャートにより上述した処理(バンク電源制御レジスタ260の更新処理)を実行する。その結果、以下のような動作が実現される。

30

**【0038】**

CPU200が実行しているプログラム320がアイドル状態になり、データ330に対するアクセスが無い状態になったとする。この場合、もはやインターリープ領域401に対する一切のアクセスが発生しない為、インターリープ領域401に含まれるバンク211及び212の電源をオフすることが可能である。ここでCPU200がバンク電源制御レジスタ260のビット1及び2を0に書き換えると、バンク211及び212の電源がオフ状態になる。スタック領域413は、プログラム320がアイドル動作中も常時使用されているため、バンク210同様、バンク213についても電源はオン状態を維持しておく。

40

**【0039】**

以上のように、第二実施形態によれば、待機動作の実行中にアクセスが必要なプログラムやデータを非インターリープ領域に保持し、待機動作の実行中にアクセスが不要なプログラムやデータをインターリープ領域に保持するようにした。そのため、待機動作中においてインターリープ領域への電源供給を停止することができ、省電力効果を向上させることができる。なお、待機動作中にアクセス可能な領域を非インターリープ領域、待機動作中にアクセス不能な領域をインターリープ領域としたが、これに限られるものではない。待機動作中に電源供給をオフする領域を非インターリープ領域としてもよい。更に、図3

50

(C)の300で示した領域をインターリープ領域301とは独立したインターリープ領域に設定し、それぞれのインターリープ領域について個別に電源供給を制御するようにしてもよい。その場合、待機動作中にもアクセスの必要なプログラムやデータを高速アクセスが可能なインターリープ領域(図3(C)の300の領域)に配置し、待機動作中も電源が供給されるように構成できる。

#### 【0040】

各バンクは全て不揮発性メモリである為、電源オフの状態でもインターリープ領域401に配置されているデータ330は消える事は無い。従ってバンク電源制御レジスタ260のビット1及び2を1に書き戻すことでバンク211及び212の電源をオンにすれば、再びデータ330を読み出すことが出来る。

10

#### 【0041】

このように、一時的に動作不要なバンクについて電源オフ状態にすることで、消費電力を削減することが可能である。また不揮発性メモリである為、バンクの電源を再度オン状態にするだけで、一切の書き戻し作業を必要とせずに、バンク内の記憶を参照することができる。その為、例えば上記例のようにアイドル動作時にこの仕組みを使用するプログラムなどでは、待機動作から通常動作への状態遷移が速くなる。

#### 【0042】

##### [第三実施形態]

第一実施形態及び第二実施形態では、各バンクへのメモリアクセス要・不要の状態に応じて、CPU200からバンク電源制御レジスタ260を書き換えることで、各バンクの電源制御を行なう方法について説明した。先の方法ではCPU200によって実行中のプログラムが、データの使用状態を把握していた。そして一時的にデータアクセスが不要になった場合には、プログラムによるソフトウェア処理(レジスタ書き換え)を行って、データを配置しているバンクを電源オフした。またデータアクセスが必要になった場合は、再度プログラムがソフトウェア処理を行って当該バンクの電源をオンするという仕組みであった。第三実施形態では各バンクの電源オン・オフ制御を、CPU200が実行するプログラムのソフトウェア処理によらずハードウェア処理で実現する方法について説明する。

20

#### 【0043】

図5(A)は第三実施形態におけるメモリシステムの構成例を示すブロック図である。メモリ制御部500では、図2(A)に於けるメモリ制御部220に対し、新たにバンクアクセス監視部510が追加されている。バンクアクセス監視部510は、各バンクへのアクセスが最後に発生してから現在までどのくらいの時間が経過したか、すなわちバンクへの未アクセス時間の経過を、タイマカウンタを用いて監視する回路である。メモリ制御部500及びバンクアクセス監視部510以外の部位に関しては、第一実施形態及び第二実施形態で説明したものと同様である。

30

#### 【0044】

図5(B)はバンクアクセス監視部510に内蔵されたタイマ設定レジスタ520、521、522、523を示している。タイマ設定レジスタ520、521、522、523は各々バンク210、211、212、213に対応している。メモリ制御部500は、夫々のバンクへの未アクセス時間をバンクアクセス監視部510で計測しつつ、これらのレジスタのタイマ設定値と比較する。どこからもバンクへのアクセスが無く、バンク未アクセス時間がそのバンクに対応するレジスタ設定値を超えた場合は、メモリ制御部500は、バンク電源制御レジスタ260の当該バンクに対応するビットを0に設定し、当該バンクへの電源供給をオフにする。但し、第一、第二実施形態から明らかにるように、インターリープ領域に関しては個別にバンクの電源供給をオン、オフすることはできない。したがって、インターリープ領域を構成する全てのバンクへの未アクセス時間がタイマ設定レジスタにより設定された所定時間を超えた場合に、バンク電源制御レジスタ260におけるそれらバンクのビットを0に設定する。例えば、図4(C)のような設定の場合、バンク211とバンク212における未アクセス時間がそれぞれタイマ設定レジスタ521

40

50

、522に設定されている時間を超えた場合に、バンク電源制御レジスタ260のビット1とビット2が0に設定される。

#### 【0045】

その後、電源オフ状態のバンクに対してCPU200から読み出し若しくは書き込みアクセスがあった場合、そのバンクアクセスがバンクアクセス監視部510により検出される。バンクアクセス監視部510により電源オフ状態のバンクへのアクセスが検出されると、メモリ制御部500はバンク電源制御レジスタ260の当該バンクに対応するビットを1に設定することで、当該バンクの電源を再びオンにする。また、バンク電源制御レジスタ260の電源オフ状態であったバンクに対応するビットを1に設定するとともに、当該バンクに関わるタイマ計測処理を一旦リセットして再度計測を開始する。

10

#### 【0046】

以上のように、第三実施形態によれば、メモリ制御部500内にバンクへのアクセス状態を監視する仕組みを持たせ、アクセス状態に応じて自動的にバンクへの電源供給をオン・オフするようにした。そのため、CPU200によるアクセス状態監視やプログラム制御による電源オン・オフ処理が不要になり、システムを効率化することができる。

#### 【0047】

なお第三実施形態では電源供給のオン及びオフ処理の両方をバンクアクセス監視部510とバンク電源制御部221によるハードウェア制御で行っているが、必ずしもこの構成に限定するものではない。例えばバンク電源オンはCPU200によるソフトウェア処理で行い、バンク電源オフは上述したようなハードウェア制御で行ってもよい。あるいはバンク電源オンはハードウェア制御で行い、バンク電源オフはCPU200によるソフトウェア処理（例えば図8の処理）で行うようにしてもよい。

20

#### 【0048】

##### 〔第四実施形態〕

第四実施形態では、第一実施形態、第二実施形態及び第三実施形態で示した構成におけるメモリ領域内の任意の論理アドレスが、いずれのバンクの何処の物理アドレスに対応付けられるかを求める方法の一例について述べる。

#### 【0049】

第二実施形態で説明した図4(C)を例にして説明する。まず図4(C)のバンク210、211、212及び213について夫々のバンク内の物理アドレス、すなわちROWアドレス及びCOLUMNアドレスを想定する。ここでは説明を簡便にするために各バンクともROWアドレス数が2、COLUMNアドレス数が2とする。従って各バンクはROWアドレス数×COLUMNアドレス数=4アドレス構成となる。

30

#### 【0050】

次に、非インターリープ領域400のバンク210に割り当てられた論理アドレス4000、4001、4002及び4003と、バンク内の物理アドレスの対応付けについて考える。バンク210内の物理アドレスをバンク番号、ROWアドレス、COLUMNアドレスで表し、論理アドレスとの対応関係を整理すると、図6(A)のような対応関係になる。同様に非インターリープ領域402内のバンク213についても、バンク番号、ROW及びCOLUMNアドレスと論理アドレスに関して、図6(B)のような対応関係が得られる。

40

#### 【0051】

さらにインターリープ領域401内のバンク211及び212について考える。先の図4(C)に示したように、バンク211及び212はインターリープ領域を構成している為、論理アドレスは各バンクを跨るように交互にアドレスされる。即ちバンク211にはアドレス4004、4006、4008、4010が、またバンク212にはアドレス4005、4007、4009、4011が割り当てられる。この状態において、各バンク内のROW及びCOLUMNアドレスと論理アドレスの対応関係は図6(C)のようになる。これを論理アドレス順に再整理したものが図6(D)である。

#### 【0052】

50

図7は、上記の図6(A)、(B)、及び(D)を論理アドレス順にひとつにまとめたテーブルであり、論理アドレスを物理アドレスにマッピングするルックアップテーブル(以下LUTと証する)である。例えばこのLUTをメモリ制御部220に内蔵すれば、CPU200若しくは不図示の周辺デバイスから発生する任意の論理アドレスを、このLUTを参照して物理アドレス(バンク番号、ROW及びCOLUMN)に変換することが出来る。

#### 【0053】

なお、実際の構成においては、上述のようにあらかじめ論理アドレスと物理アドレスの対応関係を求めておき、LUTとしてメモリ制御部220の中に内蔵してもよい。あるいは論理アドレスと物理アドレスの対応関係に算術的な規則性が存在するならば、論理アドレスから物理アドレスへ変換する演算処理によってLUTを生成してもよい。若しくはLUTそのものを持たず、メモリアクセス発生の都度、論理アドレスから物理アドレスへ変換する演算処理を動的に行って、論理アドレスと物理アドレスの対応関係を求めてよい。本提案は、これら論理アドレスと物理アドレスの対応関係の導出の仕方について限定するものではない。10

#### 【0054】

以上のように、上記実施形態によれば、高速アクセスが必要なデータやプログラムを配置するバンクと、低速アクセスでも構わないデータやプログラムを配置するバンクを完全に分離出来る。そして、分離したインターリーブ領域若しくは非インターリーブ領域の何れかが一時的にアクセス不要な場合には各領域を個別に電源オフすることが可能になり、消費電力を削減できる。20

#### 【0055】

なお、上記実施形態では、MRAMを用いた構成を示したが、本発明の適用はMRAMを用いたメモリシステム限られるものではなく、不揮発性メモリを用いたメモリシステム全般において本発明は好適に適用できる。

#### 【0056】

また、上述したメモリシステムは、デジタルカメラ、ビデオカメラ、携帯電話やタブレットなどの各種情報処理装置、電子機器に用いることができ、上述したメモリシステムが適用された情報処理装置、電子機器も本発明の範疇である。

#### 【0057】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。30

【図 2】

【図 4】

(C)

(B)

(C)

インターフィード設定レジスタ

バンク電源制御レジスタ

【図5】

【図6】

| バンク | 物理アドレス |        | 論理アドレス   |

|-----|--------|--------|----------|

|     | ROW    | COLUMN |          |

| 210 | 0      | 0      | アドレス4001 |

| 210 | 0      | 1      | アドレス4002 |

| 210 | 1      | 0      | アドレス4003 |

| 210 | 1      | 1      | アドレス4004 |

| 211 | 0      | 0      | アドレス4004 |

| 212 | 0      | 0      | アドレス4005 |

| 211 | 0      | 1      | アドレス4006 |

| 212 | 0      | 1      | アドレス4007 |

| 211 | 1      | 0      | アドレス4008 |

| 212 | 1      | 0      | アドレス4009 |

| 211 | 1      | 1      | アドレス4010 |

| 212 | 1      | 1      | アドレス4011 |

| 213 | 0      | 0      | アドレス4012 |

| 213 | 0      | 1      | アドレス4013 |

| 213 | 1      | 0      | アドレス4014 |

| 213 | 1      | 1      | アドレス4015 |

(A)

| バンク | 物理アドレス |        | 論理アドレス   |

|-----|--------|--------|----------|

|     | ROW    | COLUMN |          |

| 213 | 0      | 0      | アドレス4012 |

| 213 | 0      | 1      | アドレス4013 |

| 213 | 1      | 0      | アドレス4014 |

| 213 | 1      | 1      | アドレス4015 |

(B)

|     | バンク211 |        | バンク212 |        |      |

|-----|--------|--------|--------|--------|------|

|     | COLUMN | COLUMN | COLUMN | COLUMN |      |

| ROW | 0      | 4004   | 4006   | 4005   | 4007 |

|     | 1      | 4008   | 4010   | 4009   | 4011 |

(C)

| バンク | 物理アドレス |        | 論理アドレス   |

|-----|--------|--------|----------|

|     | ROW    | COLUMN |          |

| 211 | 0      | 0      | アドレス4004 |

| 212 | 0      | 0      | アドレス4005 |

| 211 | 0      | 1      | アドレス4006 |

| 212 | 0      | 1      | アドレス4007 |

| 211 | 1      | 0      | アドレス4008 |

| 212 | 1      | 0      | アドレス4009 |

| 211 | 1      | 1      | アドレス4010 |

| 212 | 1      | 1      | アドレス4011 |

| 211 | 1      | 1      | アドレス4012 |

| 212 | 1      | 1      | アドレス4013 |

| 211 | 1      | 1      | アドレス4014 |

| 212 | 1      | 1      | アドレス4015 |

(D)

【図7】

| バンク | 物理アドレス |        | 論理アドレス   |

|-----|--------|--------|----------|

|     | ROW    | COLUMN |          |

| 210 | 0      | 0      | アドレス4001 |

| 210 | 0      | 1      | アドレス4002 |

| 210 | 1      | 0      | アドレス4003 |

| 210 | 1      | 1      | アドレス4004 |

| 211 | 0      | 0      | アドレス4004 |

| 212 | 0      | 0      | アドレス4005 |

| 211 | 0      | 1      | アドレス4006 |

| 212 | 0      | 1      | アドレス4007 |

| 211 | 1      | 0      | アドレス4008 |

| 212 | 1      | 0      | アドレス4009 |

| 211 | 1      | 1      | アドレス4010 |

| 212 | 1      | 1      | アドレス4011 |

| 213 | 0      | 0      | アドレス4012 |

| 213 | 0      | 1      | アドレス4013 |

| 213 | 1      | 0      | アドレス4014 |

| 213 | 1      | 1      | アドレス4015 |

【図8】

---

フロントページの続き

(72)発明者 西森 公治

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 蓬覚寺 秀行

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 後藤 彰

(56)参考文献 特開2011-018222(JP, A)

特開平09-212416(JP, A)

国際公開第2011/046788(WO, A1)

特開昭52-068331(JP, A)

特開2000-267986(JP, A)

特開2008-152687(JP, A)

米国特許第5960462(US, A)

米国特許出願公開第2005/0210206(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00

G 06 F 12 / 06