(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5279939号

(P5279939)

(45) 発行日 平成25年9月4日(2013.9.4)

(24) 登録日 平成25年5月31日(2013.5.31)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 21/336 (2006.01)H01L 29/78 618 F

H01L 29/78 618 B

H01L 29/78 618 E

H01L 29/78 618 Z

請求項の数 4 (全 50 頁)

(21) 出願番号 特願2012-209947 (P2012-209947)

(22) 出願日 平成24年9月24日 (2012.9.24)

(65) 公開番号 特開2013-84940 (P2013-84940A)

(43) 公開日 平成25年5月9日 (2013.5.9)

審査請求日 平成25年1月24日 (2013.1.24)

(31) 優先権主張番号 特願2011-215682 (P2011-215682)

(32) 優先日 平成23年9月29日 (2011.9.29)

(33) 優先権主張国 日本国 (JP)

早期審査対象出願

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 本田 達也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 津吹 将志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 野中 裕介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 島津 貴志

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート電極と、

前記ゲート電極上を覆い、シリコンを含むゲート絶縁膜と、

前記ゲート絶縁膜上の、少なくとも前記ゲート電極と重畳するように設けられた酸化物半導体膜と、を有し、

前記酸化物半導体膜は、前記酸化物半導体膜の被形成面に垂直な方向と沿うようにC軸配向した結晶部を含み、

前記酸化物半導体膜に含まれるシリコンの濃度は、前記酸化物半導体膜のいずれの部分においても、1.0原子%以下である半導体装置。

10

## 【請求項 2】

ゲート電極と、

前記ゲート電極上を覆い、シリコンを含むゲート絶縁膜と、

前記ゲート絶縁膜上の、少なくとも前記ゲート電極と重畳するように設けられた酸化物半導体膜と、を有し、

前記酸化物半導体膜は、前記酸化物半導体膜の被形成面に垂直な方向と沿うようにC軸配向した結晶部を含み、

前記酸化物半導体膜は、前記ゲート絶縁膜側の界面から前記酸化物半導体膜の内部に向けて、シリコンが1.0原子%以下の濃度で分布する第1の領域を有する半導体装置。

## 【請求項 3】

20

請求項 2 において、

前記酸化物半導体膜は、前記第 1 の領域とは異なる第 2 の領域を有し、

前記第 2 の領域に含まれるシリコンの濃度は、前記第 1 の領域に含まれるシリコンの濃度より小さい半導体装置。

**【請求項 4】**

ゲート電極と、

前記ゲート電極上を覆い、シリコンを含むゲート絶縁膜と、

前記ゲート絶縁膜上の、少なくとも前記ゲート電極と重畳するように設けられた酸化物半導体膜と、を有し、

前記酸化物半導体膜は、前記酸化物半導体膜の被形成面に垂直な方向と沿うように C 軸配向した結晶部を含み、 10

前記第 1 の領域は、前記第 2 の領域よりも、前記ゲート絶縁膜側に位置し、

前記第 1 の領域に含まれるシリコンの濃度は、1.0 原子%以下であり、

前記第 2 の領域に含まれるシリコンの濃度は、前記第 1 の領域に含まれるシリコンの濃度より小さい半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

半導体装置及び半導体装置の作製方法に関する。 20

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

**【背景技術】**

**【0003】**

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路（I C）や画像表示装置（表示装置）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

**【0004】**

例えば、トランジスタの活性層として、インジウム（In）、ガリウム（Ga）、及び亜鉛（Zn）を含む非晶質酸化物を用いたトランジスタが開示されている（特許文献 1 参照）。 30

**【0005】**

酸化物半導体を用いたトランジスタは、アモルファスシリコンを用いたトランジスタよりも高いオン特性（オン電流など）を有する。酸化物半導体を用いたトランジスタを、高機能デバイスに応用するために、さらなる特性の向上が求められており、酸化物半導体の結晶化の技術が進められている（特許文献 2）。特許文献 2 では、酸化物半導体を熱処理することによって、結晶化する技術が開示されている。

**【先行技術文献】**

**【特許文献】**

**【0006】**

【特許文献 1】特開 2006 - 165528 号公報

【特許文献 2】特開 2008 - 311342 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0007】**

トランジスタに用いられる酸化物半導体膜は、スパッタリング法を用いて成膜されることが多い。しかしながら、酸化物半導体膜のスパッタリングの際に、イオン化された希ガス元素やターゲット表面からはじき飛ばされた粒子が、ゲート絶縁膜などの酸化物半導体膜

の被形成面となる膜の粒子をはじき飛ばしてしまうことがある。このようにして被形成面となる膜からはじき飛ばされた粒子は、酸化物半導体膜に不純物元素として取り込まれてしまい、特に酸化物半導体膜の被形成面近傍には不純物元素が高い濃度で取り込まれるおそれがある。また、不純物元素が、酸化物半導体膜の被形成面近傍に残存すると、トランジスタの特性に影響を与える要因になる。

【0008】

また、酸化物半導体膜の被形成面近傍に不純物元素が取り込まれていると、不純物元素によって酸化物半導体膜の結晶化が阻害されてしまう。そのため、酸化物半導体膜の被形成面近傍において非晶質領域が残存してしまう。

【0009】

そこで、酸化物半導体膜を厚くして表層の結晶領域を使用することも考えられる。しかし、寄生容量を低減し、低消費電力でトランジスタを動作させるためには、酸化物半導体膜を薄くすることが望ましく、その場合、チャネル形成領域は酸化物半導体膜の被形成面近傍に形成されるため、酸化物半導体膜の被形成面近傍まで結晶化されることが望ましい。

【0010】

このような問題に鑑み、酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減することを目的の一とする。また、酸化物半導体膜の結晶性を向上させることを目的の一とする。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供することを目的の一とする。

【課題を解決するための手段】

【0011】

開示する発明の一態様は、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンが1.0原子%以下の濃度で分布する第1の領域を有し、少なくとも第1の領域内に、結晶部を含む半導体装置である。

【0012】

また、開示する発明の一態様は、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜に接して設けられたチャネル保護膜と、チャネル保護膜上に設けられ、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンが1.0原子%以下の濃度で分布する第1の領域を有し、少なくとも第1の領域内に、結晶部を含む半導体装置である。

【0013】

上記各構成において、第1の領域は、ゲート絶縁膜との界面からの厚さが5nm以下の範囲に存在し、第1の領域以外に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さいことが好ましい。

【0014】

上記各構成において、酸化物半導体膜の第1の領域以外の領域に、結晶部を含むことが好みしい。

【0015】

また、開示する発明の一態様は、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、酸化物半導体膜、ソース電極およびドレイン電極を覆い、シリコンを含む酸化物を含む保護絶縁膜と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンが1.0原子%以下の濃度で分布する第1の領域を有し、酸化物半導体膜は、保護絶縁膜との界面から酸化物半導体膜に向けてシリコンが1.0原子%

10

20

30

40

50

以下の濃度で分布する第2の領域を有し、少なくとも第1の領域内および第2の領域内に、結晶部を含む半導体装置である。

**【0016】**

上記構成において、第1の領域は、ゲート絶縁膜との界面からの厚さが5nm以下の範囲に存在し、第2の領域は、保護絶縁膜との界面からの厚さが5nm以下の範囲に存在し、第1の領域及び第2の領域以外に含まれるシリコンの濃度は、第1の領域及び第2の領域に含まれるシリコンの濃度より小さいことが好ましい。

**【0017】**

また、上記構成において、酸化物半導体膜の第1の領域および第2の領域以外の領域に、結晶部を含むことが好ましい。

10

**【0018】**

また、上記各構成において、結晶部は、c軸が、酸化物半導体膜とゲート絶縁膜との界面に対して垂直な方向に揃うことが好ましい。

**【0019】**

また、上記各構成において、第1の領域に含まれるシリコンの濃度が0.1原子%以下であることが好ましい。

**【0020】**

また、上記各構成において、ゲート絶縁膜は炭素を含み、第1の領域において、炭素濃度が $1.0 \times 10^{20}$ atoms/cm<sup>3</sup>以下となることが好ましい。

20

**【発明の効果】**

**【0021】**

開示する発明の一態様によれば、酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減することができる。また、酸化物半導体膜の結晶性を向上させることができる。そして、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供することができる。

**【図面の簡単な説明】**

**【0022】**

**【図1】**半導体装置の一態様を示す平面図及び断面図。

**【図2】**半導体装置の一態様を示す平面図及び断面図。

30

**【図3】**半導体装置の一態様を示す平面図及び断面図。

**【図4】**半導体装置の作製工程の一例を示す断面図。

**【図5】**半導体装置の作製工程の一例を示す断面図。

**【図6】**計算に用いたモデル図。

**【図7】**計算結果を示す図。

**【図8】**計算結果を示す図。

**【図9】**半導体装置の一形態を説明する図。

**【図10】**半導体装置の一形態を説明する図。

**【図11】**半導体装置の一形態を説明する図。

**【図12】**半導体装置の一形態を説明する図。

**【図13】**電子機器を示す図。

40

**【図14】**本発明の一実施例に係る測定結果を示すグラフ。

**【図15】**本発明の一実施例に係るサンプルの構造を示す図。

**【図16】**本発明の一実施例に係る測定結果を示すグラフ。

**【図17】**本発明の一実施例に係るサンプルの構造を示す図。

**【図18】**本発明の一実施例に係る測定結果を示すグラフ。

**【図19】**本発明の一実施例に係るサンプルの構造を示す図。

**【図20】**本発明の一実施例に係る測定結果を示すグラフ。

**【図21】**計算に用いたモデル図。

**【図22】**計算に用いたモデル図。

**【図23】**計算結果を示す図。

50

【図24】計算に用いたモデル図。

【図25】計算結果を示す図。

【発明を実施するための形態】

【0023】

以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0024】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0025】

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0026】

なお、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

10

20

【0027】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

30

【0028】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0029】

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

【0030】

(実施の形態1)

本実施の形態では、半導体装置及び半導体装置の作製方法の一形態を、図1乃至図5を用いて説明する。

40

【0031】

半導体装置の構成例

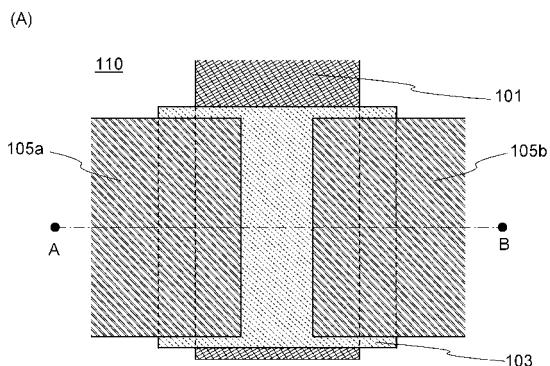

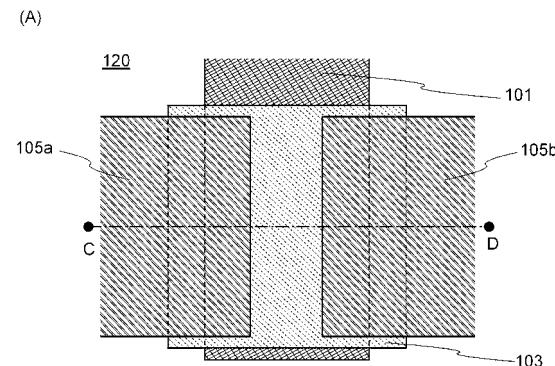

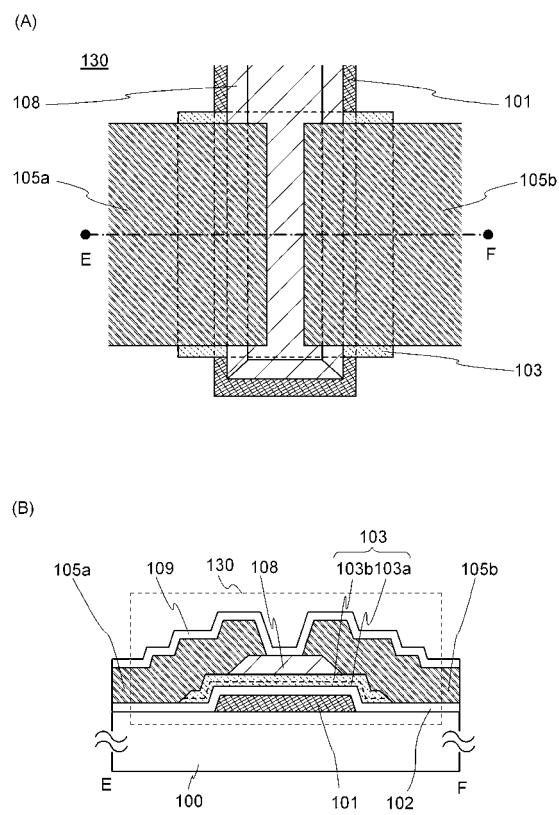

図1(A)および図1(B)に、半導体装置の例として、ボトムゲート構造の一つであるチャネルエッチ型のトランジスタの平面図および断面図を示す。図1(A)は平面図であり、図1(B)は、図1(A)におけるA-B断面に係る断面図である。なお、図1(A)では、煩雑になることを避けるため、トランジスタ110の構成要素の一部(例えば、保護絶縁膜109など)を省略している。

【0032】

図1(A)および図1(B)に示すトランジスタ110は、絶縁表面を有する基板100

50

上に、ゲート電極 101、ゲート電極 101を覆うゲート絶縁膜 102、ゲート絶縁膜 102と接し、少なくともゲート電極 101と重疊する領域に設けられた酸化物半導体膜 103、酸化物半導体膜 103と電気的に接続するソース電極 105a およびドレイン電極 105b、酸化物半導体膜 103、ソース電極 105a およびドレイン電極 105b を覆う保護絶縁膜 109 を含む。

#### 【0033】

酸化物半導体膜 103 の膜厚は、5 nmより大きく 200 nm以下とし、好ましくは 10 nm以上 30 nm以下とする。また、酸化物半導体膜 103 は、単結晶、または微結晶などの結晶性を有する構造とすることが好ましい。

#### 【0034】

本実施の形態において、酸化物半導体膜 103 は、 C AAC - OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜であることが好ましい。

10

#### 【0035】

C AAC - OS 膜は、完全な単結晶ではなく、完全な非晶質でもない。C AAC - OS 膜は、非晶質相に結晶部を有する結晶 - 非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が 100 nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡 (TEM: Transmission Electron Microscope) による観察像では、C AAC - OS 膜に含まれる非晶質領域と結晶部との境界は明確ではない。また、TEMによってC AAC - OS 膜には粒界 (グレインバウンダリーともいう) は確認できない。そのため、C AAC - OS 膜は、粒界に起因する電子移動の低下が抑制される。

20

#### 【0036】

C AAC - OS 膜に含まれる結晶部は、c 軸がC AAC - OS 膜の被形成面または表面に垂直な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸及び b 軸の向きが異なっていてもよい。本明細書等において、単に垂直と記載する場合、85°以上 95°以下の範囲も含まれることとする。

30

#### 【0037】

なお、C AAC - OS 膜において、結晶部の分布が一様でなくてもよい。例えば、C AAC - OS 膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、表面の近傍では結晶部の占める割合が高くなることがある。

#### 【0038】

C AAC - OS 膜に含まれる結晶部の c 軸は、C AAC - OS 膜の被形成面または表面に垂直な方向に揃うため、C AAC - OS 膜の形状 (被形成面の断面形状または表面の断面形状) によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸の方向は、C AAC - OS 膜が形成されたときの被形成面または表面に垂直な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

40

#### 【0039】

C AAC - OS 膜を用いたトランジスタは、可視光や紫外光の照射によるトランジスタの電気特性の変動を低減することが可能である。また、しきい値の変動及びバラツキを抑制できる。よって、当該トランジスタは信頼性が高い。

#### 【0040】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができる。さらに、結晶性を有する酸化物半導体膜表面の平坦性を高めることによって、該酸化物半導体を用いたトランジスタは、アモルファス状態の酸化物半導体を用いたトランジスタ以上の電界効果移動度を得ることができる。酸化物半導体膜表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ (Ra

50

) が 0.15 nm 以下、好ましくは 0.1 nm 以下の表面上に形成するとよい。

#### 【0041】

なお、Ra とは、JIS B 0601:2001 (ISO 4287:1997) で定義されている算術平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

#### 【0042】

##### 【数1】

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

10

#### 【0043】

ここで、指定面とは、粗さ計測の対象となる面であり、座標 ((x<sub>1</sub>, y<sub>1</sub>, f(x<sub>1</sub>, y<sub>1</sub>))、(x<sub>1</sub>, y<sub>2</sub>, f(x<sub>1</sub>, y<sub>2</sub>))、(x<sub>2</sub>, y<sub>1</sub>, f(x<sub>2</sub>, y<sub>1</sub>))、(x<sub>2</sub>, y<sub>2</sub>, f(x<sub>2</sub>, y<sub>2</sub>)) の 4 点で表される四角形の領域とし、指定面を xy 平面上に投影した長方形の面積を S<sub>0</sub>、基準面の高さ (指定面の平均の高さ) を Z<sub>0</sub> とする。Ra は原子間力顕微鏡 (AFM: Atomic Force Microscope) にて測定可能である。

#### 【0044】

20

また、図 1 (B) に示すように、酸化物半導体膜 103 は端部に 20° 乃至 50° のテー

パーを有していることが好ましい。酸化物半導体膜 103 の端部が垂直であると酸化物半

導体膜 103 から酸素が抜けやすく酸素欠損を生じやすいが、酸化物半導体膜 103 の端

部にテーパーを有することで酸素欠損の発生を抑制し、トランジスタ 110 のリーク電流

の発生を低減することができる。

#### 【0045】

酸化物半導体膜 103 に用いる酸化物半導体としては、少なくともインジウム (In) ある

いは亜鉛 (Zn) を含むことが好ましい。特に、In と Zn を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビラ

イザーとして、それらに加えてガリウム (Ga)、スズ (Sn)、ハフニウム (Hf)、

ジルコニウム (Zr)、チタン (Ti)、スカンジウム (Sc)、イットリウム (Y)、

ランタノイド (例えば、セリウム (Ce)、ネオジム (Nd)、ガドリニウム (Gd))

から選ばれた一種又は複数種が含まれていることが好ましい。

30

#### 【0046】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化

物である In-Zn 系酸化物、Sn-Zn 系酸化物、Al-Zn 系酸化物、Zn-Mg 系

酸化物、Sn-Mg 系酸化物、In-Mg 系酸化物、In-Ga 系酸化物、三元系金属の

酸化物である In-Ga-Zn 系酸化物 (IGZO とも表記する)、In-Al-Zn 系

酸化物、In-Sn-Zn 系酸化物、Sn-Ga-Zn 系酸化物、Al-Ga-Zn 系酸

化物、Sn-Al-Zn 系酸化物、In-Hf-Zn 系酸化物、In-Zr-Zn 系酸化

物、In-Ti-Zn 系酸化物、In-Sc-Zn 系酸化物、In-Y-Zn 系酸化物、

In-La-Zn 系酸化物、In-Ce-Zn 系酸化物、In-Pr-Zn 系酸化物、In-

Nd-Zn 系酸化物、In-Sm-Zn 系酸化物、In-Eu-Zn 系酸化物、In-

Gd-Zn 系酸化物、In-Tb-Zn 系酸化物、In-Dy-Zn 系酸化物、In-

Ho-Zn 系酸化物、In-Er-Zn 系酸化物、In-Tm-Zn 系酸化物、In-Y

b-Zn 系酸化物、In-Lu-Zn 系酸化物、四元系金属の酸化物である In-Sn-

Ga-Zn 系酸化物、In-Hf-Ga-Zn 系酸化物、In-Al-Ga-Zn 系酸化

物、In-Sn-Al-Zn 系酸化物、In-Sn-Hf-Zn 系酸化物、In-Hf-

Al-Zn 系酸化物を用いることができる。

40

#### 【0047】

50

ここで、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

#### 【0048】

また、酸化物半導体として、 $InMO_3(ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素、若しくは上記のスタビライザーとしての元素を示す。また、酸化物半導体として、 $In_2SnO_5(ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数) で表記される材料を用いてもよい。

#### 【0049】

例えば、 $In:Ga:Zn = 1:1:1$ 、 $In:Ga:Zn = 3:1:2$ 、あるいは $In:Ga:Zn = 2:1:3$ の原子数比のIn:Ga:Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0050】

ゲート絶縁膜102は、十分な耐圧および絶縁性を有する酸化物絶縁膜を用いることが好み。ゲート絶縁膜102を単層構造とする場合には、例えば、酸化シリコンのようなシリコンを含む酸化物を含む絶縁膜を用いればよい。

#### 【0051】

また、ゲート絶縁膜102を積層構造としても良い。ゲート絶縁膜102を積層構造とする場合、酸化ガリウム、酸化アルミニウム、窒化シリコン、酸化窒化シリコン、酸化窒化アルミニウム、酸化イットリウム、酸化ランタンまたは窒化酸化シリコンなどの上に酸化シリコンを積層すればよい。また、酸化ハフニウム、ハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムシリケート( $HfSiO_xN_y$  ( $x > 0$ 、 $y > 0$ ))、ハフニウムアルミネート( $HfAl_xO_y$  ( $x > 0$ 、 $y > 0$ ))などのhigh-k材料の上に酸化シリコンを積層すればよい。また、high-k材料を用いることでゲートリーク電流を低減することができる。

#### 【0052】

ゲート絶縁膜102として酸化物絶縁膜を用いることにより、当該酸化物絶縁膜を加熱することにより酸素の一部を脱離させることができるので、酸化物半導体膜103に酸素を供給し、酸化物半導体膜103中の酸素欠損を補填することができる。特に、ゲート絶縁膜102中(バルク中)に少なくとも化学量論比を超える量の酸素が存在することが好み、例えば、ゲート絶縁膜102として、 $SiO_{2+}$  (ただし、 $> 0$ ) で表される酸化シリコン膜を用いることが好み。このような酸化シリコン膜をゲート絶縁膜102として用いることで、酸化物半導体膜103に酸素を供給することができ、当該酸化物半導体膜103を用いたトランジスタ110のトランジスタ特性を良好にすることができる。

#### 【0053】

しかしながら、ゲート絶縁膜102として酸化シリコン膜を用いる場合、ゲート絶縁膜102中のシリコンが不純物として酸化物半導体膜103に取り込まれるおそれがある。酸化物半導体膜103にシリコンなどが不純物として取り込まれることにより、トランジスタの特性に影響を与える要因になる。また、酸化物半導体膜103の被形成面近傍に不純物元素が取り込まれると、不純物元素によって酸化物半導体膜の結晶化が阻害されてしまう。そのため、酸化物半導体膜の被形成面近傍において非晶質領域が残存してしまう。また、酸化物半導体膜103をCAC-O<sub>S</sub>膜とする場合には、被形成面近傍において、結晶部を形成することが困難となる。

#### 【0054】

特に、酸化物半導体膜103とゲート絶縁膜102が接する、酸化物半導体膜103の被形成面近傍においてはシリコンなどの不純物が取り込まれやすい。酸化物半導体膜103の被形成面近傍にトランジスタ110のチャネル形成領域が形成されるため、被形成面近傍にシリコンなどの不純物が取り込まれると、トランジスタ110の特性を変動させてし

10

20

30

40

50

まうおそれがある。

#### 【0055】

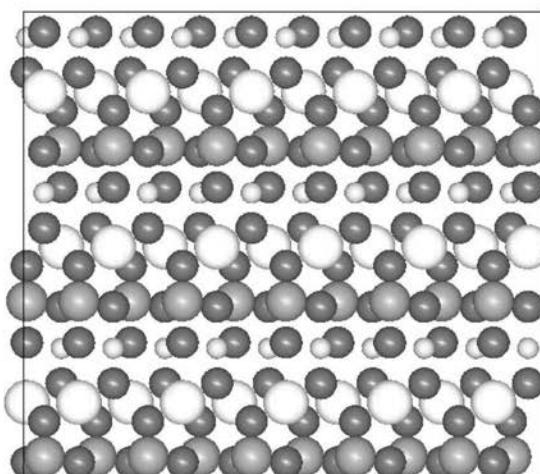

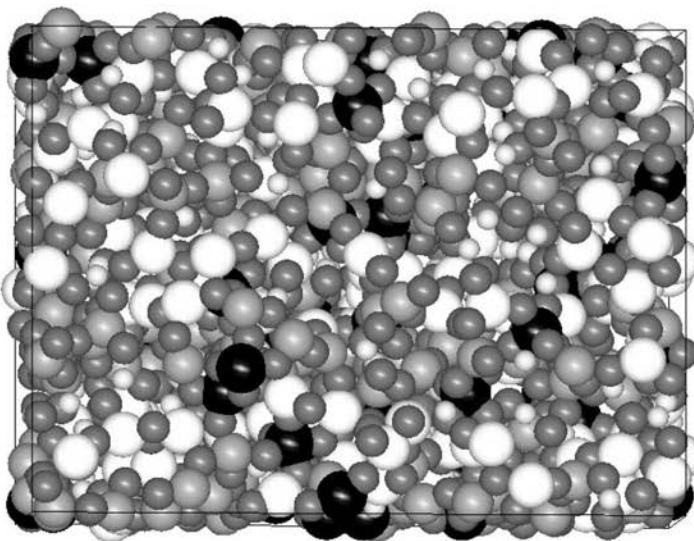

ここで、酸化物半導体膜103に、不純物としてシリコンを含む酸化物であるSiO<sub>2</sub>が添加されると、どのような構造変化が起こるかについて、古典分子動力学計算により調査した結果について、図21乃至図25を用いて説明する。なお、上記計算を行うため、古典分子動力学計算ソフトウェアとして、富士通株式会社製SCIGRESS MEを用いた。古典分子動力学法では、原子間相互作用を特徴づける経験的ポテンシャルを定義することで、各原子に働く力を評価する。ニュートンの運動方程式を数値的に解くことにより、各原子の運動（時間発展）を決定論的に追跡できる。

#### 【0056】

以下に、計算モデルと計算条件を述べる。なお、本計算においては、Born-Mayer-Hugginsポテンシャルを用いた。

#### 【0057】

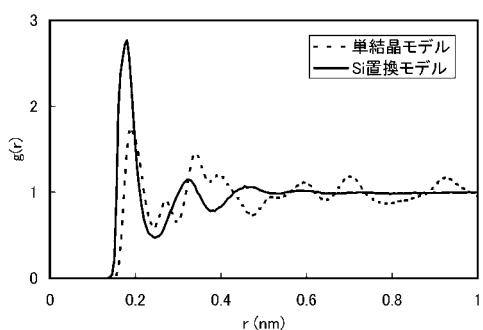

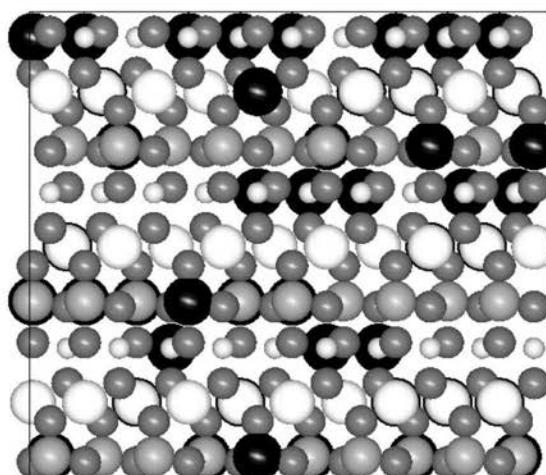

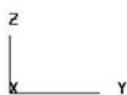

計算モデルとして、1680原子のInGaZnO<sub>4</sub>の単結晶構造（図21（A）参照）と、1680原子のInGaZnO<sub>4</sub>のIn、Ga、Znのそれぞれ20原子ずつをシリコン（Si）原子で置換した構造（図21（B）参照）を作製した。図21（B）に示すシリコン（Si）置換モデルにおいて、シリコン（Si）は、3.57atom%（2.34重量%）である。また、図21（A）に示す単結晶モデルの密度は、6.36g/cm<sup>3</sup>であり、図21（B）に示すシリコン（Si）置換モデルの密度は、6.08g/cm<sup>3</sup>である。

#### 【0058】

図21（A）及び図21（B）に示す計算モデルに対して、InGaZnO<sub>4</sub>の単結晶の融点（古典分子動力学計算による見積もりでは、約2000）より低い1727において、圧力一定（1atm）で、150psc間（時間刻み幅0.2fsec×75万ステップ）の古典分子動力学計算により、構造緩和を行った。また、これら2つの構造に対して、動径分布関数g(r)を求めた。なお、動径分布関数g(r)とは、ある原子から距離r離れた位置において、他の原子が存在する確率密度を表す関数である。原子同士の相関がなくなっていくと、g(r)は1に近づく。

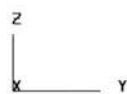

#### 【0059】

上記、2つの計算モデルを、150psc間の古典分子動力学計算を行うことにより得られた最終構造をそれぞれ図22（A）及び図22（B）に示す。また、それぞれの構造における動径分布関数g(r)を、図23に示す。

#### 【0060】

図22（A）に示す単結晶モデルは安定で、最終構造においても結晶構造を保っているが、図22（B）に示すシリコン（Si）置換モデルは不安定で、時間経過とともに結晶構造が崩れていき、アモルファス構造へと変化することが確認できる。また、図23において、各構造モデルの動径分布関数g(r)を比較すると、単結晶モデルでは、長距離でもピークがあり、長距離秩序があることがわかる。一方、シリコン（Si）置換モデルでは、0.6nm近傍でピークが消え、長距離秩序がないことがわかる。

#### 【0061】

これらの計算結果により、InGaZnO<sub>4</sub>にシリコン（Si）が含まれることにより、InGaZnO<sub>4</sub>のアモルファス化が起こりやすくなることが示唆された。また、InGaZnO<sub>4</sub>にシリコン（Si）が含まれた状態で高温加熱を行っても、InGaZnO<sub>4</sub>は結晶化しないことが確認された。

#### 【0062】

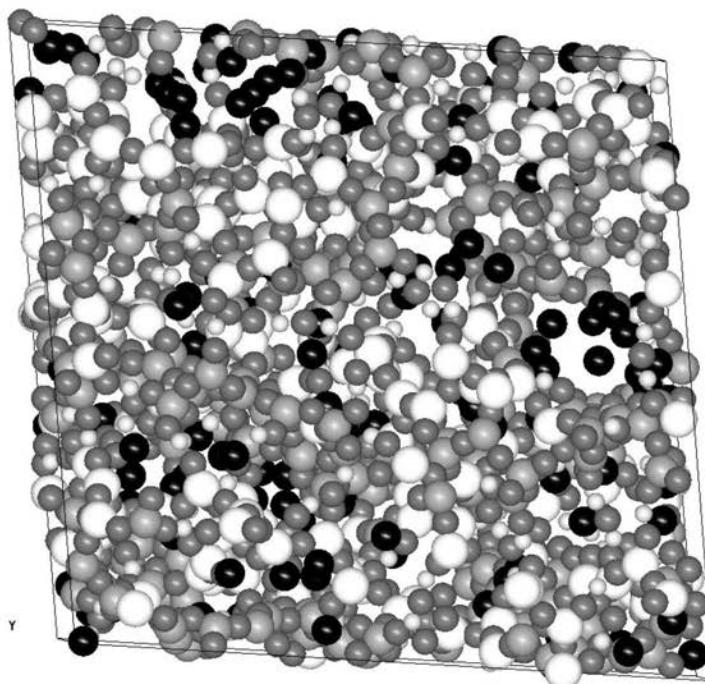

次に、酸化物半導体膜103に炭素原子（C）が添加されると、どのような構造変化が起こるかについて、古典分子動力学計算により調査した結果について、図21（A）、図24、及び図25を用いて説明する。なお、上記計算を行うため、古典分子動力学計算ソフトウェアとして、富士通株式会社製SCIGRESS MEを用いた。

#### 【0063】

10

20

30

40

50

以下に、計算モデルと計算結果を述べる。なお、本計算においては、Born-Mayer-Hugginsポテンシャルを用いた。また、炭素原子(C)との原子間相互作用にはLennard-Jonesポテンシャルを用いた。

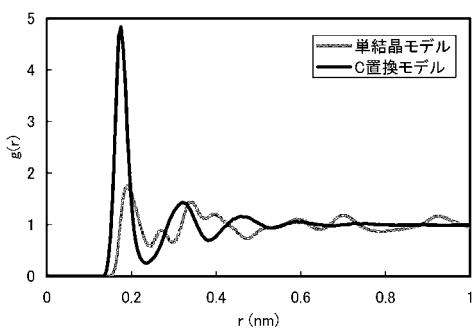

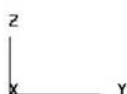

#### 【0064】

計算モデルとして、1680原子の $\text{InGaZnO}_4$ の単結晶構造(図21(A)参照)と、1680原子の $\text{InGaZnO}_4$ のIn、Ga、Znのそれぞれ20原子ずつを炭素原子(C)で置換し、酸素(O)の80原子を炭素原子(C)で置換した構造(図24(A)参照)を作製した。図24(A)に示す炭素(C)置換モデルにおいて、炭素原子(C)は、8.33 atom%である。また、図21(A)に示す単結晶モデルの密度は、6.36 g/cm<sup>3</sup>であり、図24(A)に示す炭素(C)置換モデルの密度は、5.89 g/cm<sup>3</sup>である。

#### 【0065】

図21(A)及び図24(A)に示す計算モデルに対して、 $\text{InGaZnO}_4$ の単結晶の融点(古典分子動力学計算による見積もりでは約2000)より低い1727において、圧力一定(1 atm)で、140 ps e c間(時間刻み幅0.2 fs e c × 75万ステップ)の古典分子動力学計算により、構造緩和を行った。また、これら2つの構造に対して、動径分布関数g(r)を求めた。なお、動径分布関数g(r)とは、ある原子から距離r離れた位置において、他の原子が存在する確率密度を表す関数である。原子同士の相関がなくなっていくと、g(r)は1に近づく。

#### 【0066】

上記の2つの計算モデルを、150 ps e c間の古典分子動力学計算を行うことにより得られた最終構造をそれぞれ、図22(A)及び図24(B)に示す。また、それぞれの構造における動径分布関数g(r)を図25に示す。

#### 【0067】

図22(A)に示す単結晶モデルは安定で、最終構造においても結晶構造を保っているが、図24(B)に示す炭素(C)置換モデルは不安定で、時間経過とともに結晶構造が崩れていき、アモルファス構造へと変化することが確認できる。また、図25において、各構造モデルの動径分布関数g(r)を比較すると、単結晶モデルでは、長距離でもピークがあり、長距離秩序があることがわかる。一方、炭素(C)置換モデルでは、0.6 nm近傍でピークが消え、長距離秩序がないことがわかる。

#### 【0068】

これらの計算結果により、 $\text{InGaZnO}_4$ に炭素(C)が含まれることによって、 $\text{InGaZnO}_4$ のアモルファス化が起こりやすくなることが示唆された。また、 $\text{InGaZnO}_4$ に炭素(C)が含まれた状態で高温加熱を行っても、 $\text{InGaZnO}_4$ は結晶化しないことが確認された。

#### 【0069】

以上、説明したように、酸化物半導体膜に不純物が取り込まれることは、酸化物半導体膜の結晶性が低下する要因となる。そこで、本実施の形態に示す半導体装置においては、酸化物半導体膜の被形成面近傍にシリコンなどの不純物が取り込まれることを抑制する。その結果、酸化物半導体膜103において、ゲート絶縁膜102との界面から酸化物半導体膜103に向けてシリコンが1.0原子%以下の濃度で分布する領域が形成される。該領域を、領域103aと示す。また、領域103aに含まれるシリコンの濃度は、0.1原子%以下であるとより好ましい。また、領域103aは、ゲート絶縁膜102との界面からの厚さが5 nm以下の範囲に存在する。

#### 【0070】

なお、酸化物半導体膜103の領域103a以外の領域を領域103bと示す。また、領域103bに含まれるシリコンの濃度は、領域103aに含まれるシリコンの濃度より小さくなる。

#### 【0071】

また、ゲート絶縁膜102に炭素などの不純物が含まれる場合、これも上記のシリコンと

10

20

30

40

50

同様に酸化物半導体膜 103 に不純物として取り込まれるおそれがある。そこで、領域 103a に含まれる炭素濃度は  $1.0 \times 10^{20}$  atoms/cm<sup>3</sup> 以下、より好ましくは  $1.0 \times 10^{19}$  atoms/cm<sup>3</sup> 以下とする。

#### 【0072】

このように、酸化物半導体膜 103 の領域 103a に取り込まれるシリコンなどの不純物の濃度を低減することにより、トランジスタ 110 の特性の変動を抑制することができる。また、酸化物半導体膜 103 の被形成面近傍まで結晶化させることができる。また、酸化物半導体膜 103 を CAC-OS 膜とする場合には、被形成面近傍まで結晶部を形成することができる。このような酸化物半導体膜を用いてトランジスタを作製することにより、安定した電気特性を有する半導体装置とすることができます。

10

#### 【0073】

なお、その他の構成要素の詳細については、後述するトランジスタ 110 の作製方法において、図 4(A) 乃至 図 4(E) を用いて説明する。

#### 【0074】

なお、トランジスタ 110 上には、さらに平坦化絶縁膜が設けられていても良い。また、ソース電極 105a やドレイン電極 105b と配線とを電気的に接続するために、ゲート絶縁膜 102、保護絶縁膜 109、などには開口が形成されていても良い。また、酸化物半導体膜 103 の上方のゲート電極 101 と重畠する領域に、さらに、第 2 のゲート電極を有していても良い。

20

#### 【0075】

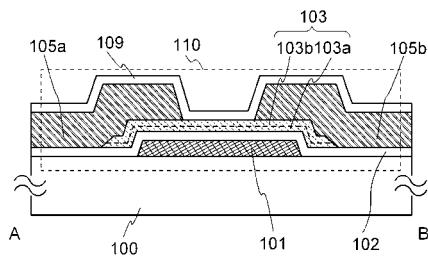

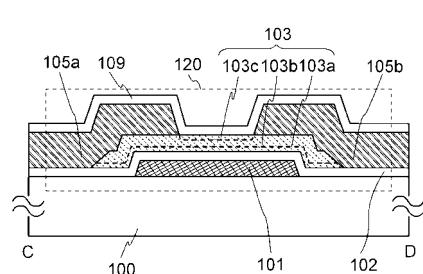

また、図 2(A) および図 2(B) に図 1(A) および図 1(B) に示すトランジスタ 110 とは異なる構成のトランジスタ 120 を示す。図 2(A) は平面図であり、図 2(B) は、図 2(A) における C-D 断面に係る断面図である。なお、図 2(A) では、煩雑になることを避けるため、トランジスタ 120 の構成要素の一部（例えば、保護絶縁膜 109 など）を省略している。

#### 【0076】

図 2(A) および図 2(B) に示すトランジスタ 120 は、絶縁表面を有する基板 100 上に、ゲート電極 101、ゲート電極 101 を覆うゲート絶縁膜 102、ゲート絶縁膜 102 と接し、少なくともゲート電極 101 と重畠する領域に設けられた酸化物半導体膜 103、酸化物半導体膜 103 と電気的に接続するソース電極 105a およびドレイン電極 105b、酸化物半導体膜 103、ソース電極 105a およびドレイン電極 105b を覆う保護絶縁膜 109 を含む。ここで、トランジスタ 120 のトランジスタ 110 との相違点は、保護絶縁膜 109 として上記ゲート絶縁膜 102 と同様にシリコンを含む酸化物を含む絶縁膜を用いている点と、酸化物半導体膜 103 と保護絶縁膜 109 が接する界面近傍に領域 103c を有する点である。

30

#### 【0077】

トランジスタ 120 の酸化物半導体膜 103 は、領域 103a 乃至 領域 103c を有する。領域 103a は、酸化物半導体膜 103 において、ゲート絶縁膜 102 との界面から酸化物半導体膜 103 に向けてシリコンが 1.0 原子% 以下の濃度で分布する領域である。領域 103a は、ゲート絶縁膜 102 との界面からの厚さが 5 nm 以下の範囲に存在することが好ましい。また、領域 103c は、酸化物半導体膜 103 において、保護絶縁膜 109 との界面から酸化物半導体膜 103 に向けてシリコンが 1.0 原子% 以下の濃度で分布する領域である。領域 103c は、保護絶縁膜 109 との界面からの厚さが 5 nm 以下の範囲に存在することが好ましい。また、酸化物半導体膜 103 の領域 103a および領域 103c 以外の領域を領域 103b とする。

40

#### 【0078】

なお、領域 103b に含まれるシリコンの濃度は、領域 103a に含まれるシリコンの濃度より小さくなる。また、領域 103a に含まれるシリコンの濃度は、0.1 原子% 以下であるとより好ましい。

#### 【0079】

50

ここで、領域 103a に含まれるシリコンの濃度を 1.0 原子%以下、好ましくは 0.1 原子%以下とし、領域 103c に含まれるシリコンの濃度も 1.0 原子%以下、好ましくは 0.1 原子%以下とする。また、このとき、領域 103b に含まれるシリコンの濃度は、領域 103a 及び領域 103c に含まれるシリコンの濃度より小さくなる。

#### 【0080】

このように、酸化物半導体膜 103 のバックチャネルに当たる領域 103c においても、シリコンなどの不純物の濃度を低減させることにより、トランジスタ 120 の電気特性の変動を抑制することができる。

#### 【0081】

その他の構成要素については、図 1(A) および図 1(B) に示す半導体装置と同様である。詳細は、図 1(A) および図 1(B) に関する記載を参照することができる。 10

#### 【0082】

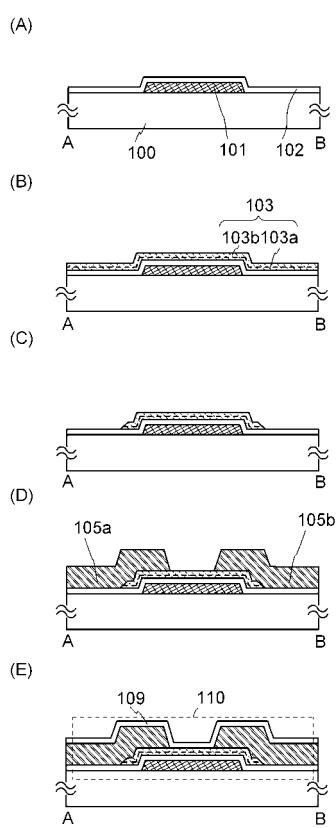

また、図 1 および図 2 に示すトランジスタは所謂チャネルエッチ型のトランジスタであるが、本実施の形態に示す半導体装置はこれに限られるものではない。図 3(A) および図 3(B) に、図 1 および図 2 に示すトランジスタとは異なるチャネルトップ型のトランジスタ 130 の構成例を示す。図 3(A) は平面図であり、図 3(B) は、図 3(A) における E-F 断面に係る断面図である。なお、図 3(A) では、煩雑になることを避けるため、トランジスタ 130 の構成要素の一部（例えば、保護絶縁膜 109 など）を省略している。また、図 3(A) では、理解が容易になるようにチャネル保護膜 108 の形状を立体的に示している。 20

#### 【0083】

図 3(A) および図 3(B) に示すトランジスタ 130 は、絶縁表面を有する基板 100 上に、ゲート電極 101、ゲート電極 101 を覆うゲート絶縁膜 102、ゲート絶縁膜 102 と接し、少なくともゲート電極 101 と重畠する領域に設けられた酸化物半導体膜 103、酸化物半導体膜 103 上に接して設けられたチャネル保護膜 108、チャネル保護膜 108 上に設けられて酸化物半導体膜 103 と電気的に接続するソース電極 105a およびドレイン電極 105b、そして、酸化物半導体膜 103、ソース電極 105a およびドレイン電極 105b を覆う保護絶縁膜 109 を含む。また、酸化物半導体膜 103 は、トランジスタ 110 と同様に領域 103a および領域 103b を有する。つまり、トランジスタ 130 のトランジスタ 110 との相違点はチャネル保護膜 108 を有する点である。 30

#### 【0084】

チャネル保護膜 108 としては、酸素を含む無機絶縁膜を用いることが好ましく、例えば、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ガリウム膜、酸化ハフニウム膜などの絶縁膜を用いることができる。また、チャネル保護膜 108 の膜厚としては 5 nm 以上 300 nm 以下とすることが好ましい。

#### 【0085】

このように、酸化物半導体膜 103 上に接してチャネル保護膜 108 を設けることにより、ソース電極 105a およびドレイン電極 105b のエッティングによる酸化物半導体膜 103 のバックチャネル側へのダメージ（例えば、エッティング時のプラズマまたはエッティング剤によるダメージ）を防ぐことができる。これにより、トランジスタ 130 の電気特性を安定したものにすることができる。 40

#### 【0086】

また、図 3(B) に示すように、チャネル保護膜 108 は端部に 10° 以上 60° 以下のテーパーを有していることが好ましい。チャネル保護膜 108 をこのような形状とすることにより、チャネル保護膜 108 の下端部近傍における電界集中を緩和することができる。

#### 【0087】

その他の構成要素については、図 1(A) および図 1(B) に示す半導体装置と同様である。詳細は、図 1(A) および図 1(B) に関する記載を参照することができる。 50

**【0088】**

トランジスタの作製工程の例

以下、図4または図5を用いて、図1乃至図3に示すトランジスタの作製工程の例について説明する。

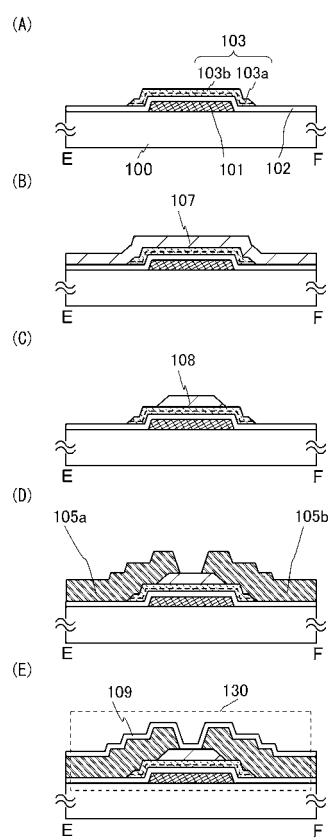

**【0089】**

トランジスタ110の作製工程

図4(A)乃至図4(E)を用いて、図1に示すトランジスタ110の作製工程の一例について説明する。

**【0090】**

まず、絶縁表面を有する基板100を準備する。絶縁表面を有する基板100に使用することができる基板に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などの基板を用いることができる。また、絶縁表面を有していれば、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能である。10

**【0091】**

また、基板100として、可撓性基板を用いてもよい。可撓性基板を用いる場合、可撓性基板上に酸化物半導体膜103を含むトランジスタを直接作製してもよいし、他の作製基板に酸化物半導体膜103を含むトランジスタを作製し、その後可撓性基板に剥離、転置してもよい。なお、作製基板から可撓性基板に剥離、転置するために、作製基板と酸化物半導体膜103を含むトランジスタとの間に剥離層を設けるとよい。20

**【0092】**

下地膜となる絶縁膜を基板100とゲート電極101との間に設けてもよい。下地膜は、基板100からの水素、水分などの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

**【0093】**

次いで、基板100上に、ゲート電極(これと同じ層で形成される配線を含む)を形成するための導電膜を形成する。ゲート電極に用いる導電膜としては、例えば、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いることができる。また、ゲート電極に用いる導電膜としては、導電性の金属酸化物を用いて形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、インジウムスズ酸化物( $In_2O_3 - SnO_2$ 、ITOと略記する場合がある)、インジウム亜鉛酸化物( $In_2O_3 - ZnO$ )、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。ゲート電極は、上記の材料を用いて単層又は積層して形成することができる。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンドル法などの各種成膜方法を用いることができる。30

**【0094】**

次いで、フォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行って、ゲート電極101を形成した後、レジストマスクを除去する。また、ゲート電極101を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。なお、ゲート電極101のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

**【0095】**

次いで、ゲート電極101を覆ってゲート絶縁膜102を形成する(図4(A)参照)。ここで、ゲート絶縁膜102の膜厚は、例えば1nm以上500nm以下とすることがで4050

きる。また、ゲート絶縁膜 102 の作製方法に特に限定はないが、例えば、スパッタリング法、MBE 法、CVD 法、パルスレーザ堆積法、ALD 法等を適宜用いてゲート絶縁膜 102 を作製することができる。

#### 【0096】

ゲート絶縁膜 102 は、十分な耐圧および絶縁性を有する酸化物絶縁膜を用いることが好ましい。ゲート絶縁膜 102 を単層構造とする場合には、例えば、酸化シリコンのようなシリコンを含む酸化物を含む絶縁膜を用いればよい。

#### 【0097】

また、ゲート絶縁膜 102 を積層構造としても良い。ゲート絶縁膜 102 を積層構造とする場合、酸化ガリウム、酸化アルミニウム、窒化シリコン、酸化窒化シリコン、酸化窒化アルミニウム、酸化イットリウム、酸化ランタンまたは窒化酸化シリコンなどの上に酸化シリコンを積層すればよい。また、酸化ハフニウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート ( $HfSiO_xN_y$  ( $x > 0$ ,  $y > 0$ ))、ハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ )) などの high-k 材料の上に酸化シリコンを積層すればよい。また、high-k 材料を用いることでゲートリーコン電流を低減することができる。10

#### 【0098】

ゲート絶縁膜 102 として酸化物絶縁膜を用いることにより、後述する熱処理によって当該酸化物絶縁膜の酸素の一部を脱離させることができるので、酸化物半導体膜 103 に酸素を供給し、酸化物半導体膜 103 中の酸素欠損を補填することができる。特に、ゲート絶縁膜 102 中（バルク中）に少なくとも化学量論比を超える量の酸素が存在することが好ましく、例えば、ゲート絶縁膜 102 として、 $SiO_{2+}$ （ただし、 $> 0$ ）で表される酸化シリコン膜を用いることが好ましい。このような酸化シリコン膜をゲート絶縁膜 102 として用いることで、酸化物半導体膜 103 に酸素を供給することができ、当該酸化物半導体膜 103 を用いたトランジスタ 110 のトランジスタ特性を良好にすることができる。20

#### 【0099】

また、酸化物半導体膜 103 を成膜する前に、ゲート絶縁膜 102 に平坦化処理を行ってもよい。平坦化処理としては、特に限定されないが、ドライエッチング処理、プラズマ処理、研磨処理（例えば、化学的機械研磨法）などを用いることができる。30

#### 【0100】

プラズマ処理としては、例えば、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行うことができる。逆スパッタリングとは、アルゴン雰囲気下で基板側に RF 電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。逆スパッタリングを行うと、酸化物半導体膜 103 の成膜表面に付着している粉状物質（パーティクル、ごみともいう）を除去することができる。

#### 【0101】

平坦化処理として、ドライエッチング処理、プラズマ処理、研磨処理を複数回行ってもよく、それらを組み合わせて行ってもよい。また、組み合わせて行う場合、工程順も特に限定されず、酸化物半導体膜 103 の被形成面の凹凸状態に合わせて適宜設定すればよい。40

#### 【0102】

また、酸化物半導体膜 103 の成膜工程において、酸化物半導体膜 103 に水素、又は水がなるべく含まれないようにするために、酸化物半導体膜 103 の成膜工程の前処理として、スパッタリング装置の予備加熱室でゲート絶縁膜 102 が成膜された基板 100 を予備加熱し、基板 100 及びゲート絶縁膜 102 に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。

#### 【0103】

次いで、ゲート絶縁膜 102 上に、膜厚 5 nm より大きく 200 nm 以下、好ましくは 150

0 nm 以上 30 nm 以下の酸化物半導体膜 103 を成膜する(図4(B)参照)。酸化物半導体膜 103 は、単結晶または微結晶などの結晶性を有する構造とすることが好ましい。また、酸化物半導体膜 103 は、CAAC-O<sub>S</sub> 膜とすることが好ましい。なお、ゲート絶縁膜 102 および酸化物半導体膜 103 は、大気に触れさせることなく連続して成膜するのが好ましい。

#### 【0104】

本実施の形態では、酸化物半導体膜 103 として In-Ga-Zn 系酸化物ターゲットを用いてスパッタリング法により成膜する。また、酸化物半導体膜 103 は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下においてスパッタ法により形成することができる。

10

#### 【0105】

酸化物半導体膜 103 として In-Ga-Zn-O 膜をスパッタリング法で作製するためのターゲットとしては、例えば、原子数比が In : Ga : Zn = 1 : 1 : 1 の酸化物ターゲットや、原子数比が In : Ga : Zn = 3 : 1 : 2 の酸化物ターゲットや、原子数比が In : Ga : Zn = 2 : 1 : 3 の酸化物ターゲットを用いることができる。ただし、酸化物半導体膜 103 をスパッタリング法で作製するためのターゲットは、これらのターゲットの材料及び組成に限定されるものではない。

#### 【0106】

また、酸化物ターゲットの相対密度は 90% 以上 100% 以下、好ましくは 95% 以上 99.9% 以下である。相対密度の高い酸化物ターゲットを用いることにより、成膜した酸化物半導体膜 103 は緻密な膜とができる。

20

#### 【0107】

酸化物半導体膜 103 を成膜する際に用いるスパッタガスとしては、水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

#### 【0108】

酸化物半導体膜 103 として、CAAC-O<sub>S</sub> 膜を適用する場合、該 CAAC-O<sub>S</sub> 膜を形成するための熱処理方法としては、三つ挙げられる。一つめは、成膜温度を 200 以上 450 以下として酸化物半導体膜の成膜を行うことで、酸化物半導体膜の被形成面または表面に対して c 軸が垂直な方向に揃った結晶部を形成する方法である。二つめは、酸化物半導体膜を薄い膜厚で成膜した後、200 以上 700 以下の熱処理を行うことで、酸化物半導体膜の被形成面または表面に対して c 軸が垂直な方向に揃った結晶部を形成する方法である。三つめは、一層目の酸化物半導体膜を薄く成膜した後、200 以上 700 以下の熱処理を行い、さらに二層目の酸化物半導体膜の成膜を行うことで、酸化物半導体膜の被形成面または表面に対して c 軸が垂直な方向に揃った結晶部を形成する方法である。

30

#### 【0109】

また、基板 100 を加熱しながら成膜することにより、成膜した酸化物半導体膜 103 に含まれる水素や水などの不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減されるため好ましい。

#### 【0110】

40

なお、酸化物半導体膜 103 として、CAAC-O<sub>S</sub> 膜以外の結晶性を有する酸化物半導体膜(単結晶または微結晶)を成膜する場合には、成膜温度は特に限定されない。

#### 【0111】

酸化物半導体膜 103 として、CAAC-O<sub>S</sub> 膜を用いる場合、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域が a - b 面から劈開し、a - b 面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、CAAC-O<sub>S</sub> 膜を成膜することができる。

50

## 【0112】

また、CACOS膜を成膜するために、以下の条件を適用することが好ましい。

## 【0113】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。

## 【0114】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起り、スパッタリング粒子の平らな面が基板に付着する。

10

## 【0115】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

## 【0116】

スパッタリング用ターゲットの一例として、多結晶のIn-Ga-Zn系酸化物ターゲットについて以下に示す。

20

## 【0117】

多結晶のIn-Ga-Zn系酸化物ターゲットは、 $In_{n-x}$ 粉末、 $GaO_y$ 粉末および $ZnO_z$ 粉末を所定のmol数で混合し、加圧処理後、1000以上1500以下の温度で加熱処理をすることで得られる。なお、X、YおよびZは任意の正数である。ここで、 $In_{n-x}$ 粉末、 $GaO_y$ 粉末および $ZnO_z$ 粉末のmol数比は、例えば、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3または3:1:2とする。なお、粉末の種類、およびその混合するmol数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。

## 【0118】

そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板100上に酸化物半導体膜103を成膜する。成膜室内的残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段は、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水( $H_2O$ )など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜103に含まれる水素、水分などの不純物の濃度を低減できる。

30

## 【0119】

なお、スパッタリング法を用いて酸化物半導体膜103を成膜する場合、酸化物半導体膜103を構成する粒子などがゲート絶縁膜102に対して衝突すると、ゲート絶縁膜102を構成する元素が酸化物半導体膜103中に混入してしまう(ミキシング、ミキシング効果とも言われる。)。当該混入現象は、ゲート絶縁膜102との界面近傍の酸化物半導体膜103中、具体的には、上述の領域103aにおいて、特に顕著に生じる。本実施の形態等に記載するトランジスタでは、ゲート絶縁膜102近傍の酸化物半導体膜103中にチャネル領域が形成されるため、ゲート絶縁膜102を構成する元素が当該領域に不純物として混入することにより、トランジスタのオン特性(例えば、オン電流など)を低下させる要因となり得る。

40

## 【0120】

ここで、ゲート絶縁膜102上に酸化物半導体膜103を成膜する際に、ゲート絶縁膜102と酸化物半導体膜103との界面近傍においてミキシングが起こる可能性について、

50

古典分子動力学計算により調査した結果について説明する。なお、上記計算を行うため古典分子動力学計算ソフトウェアとして、富士通株式会社製 S C I G R E S S M E を用いた。

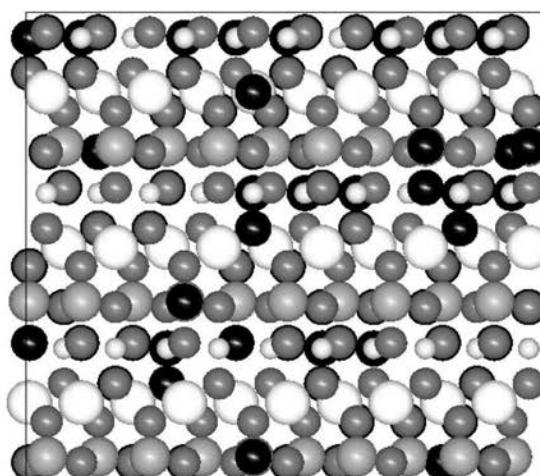

#### 【 0 1 2 1 】

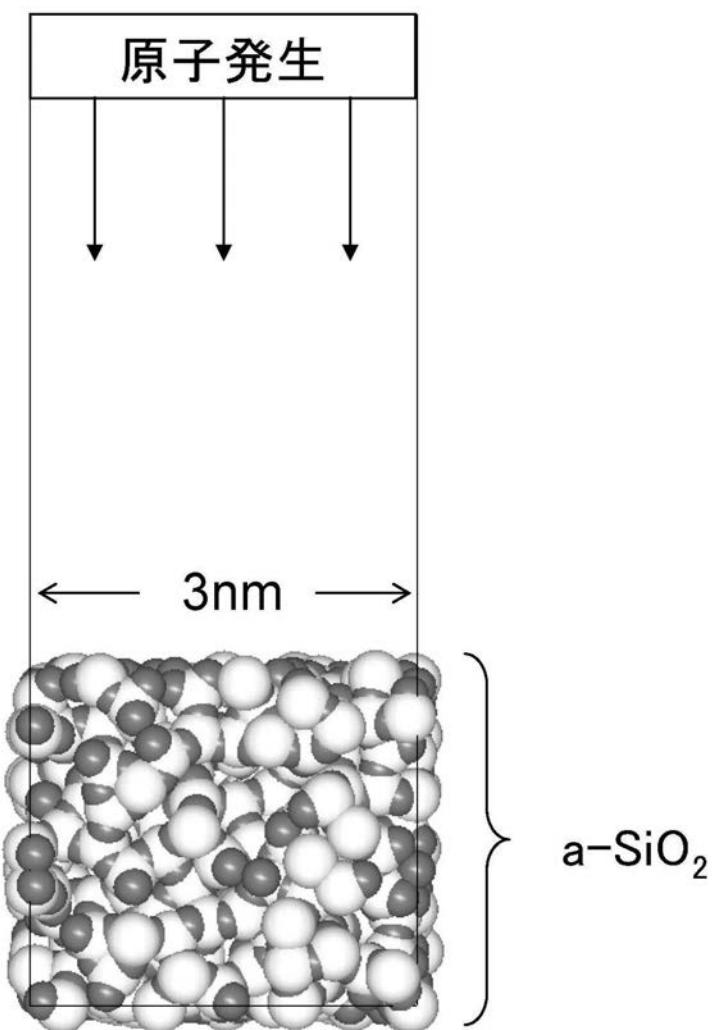

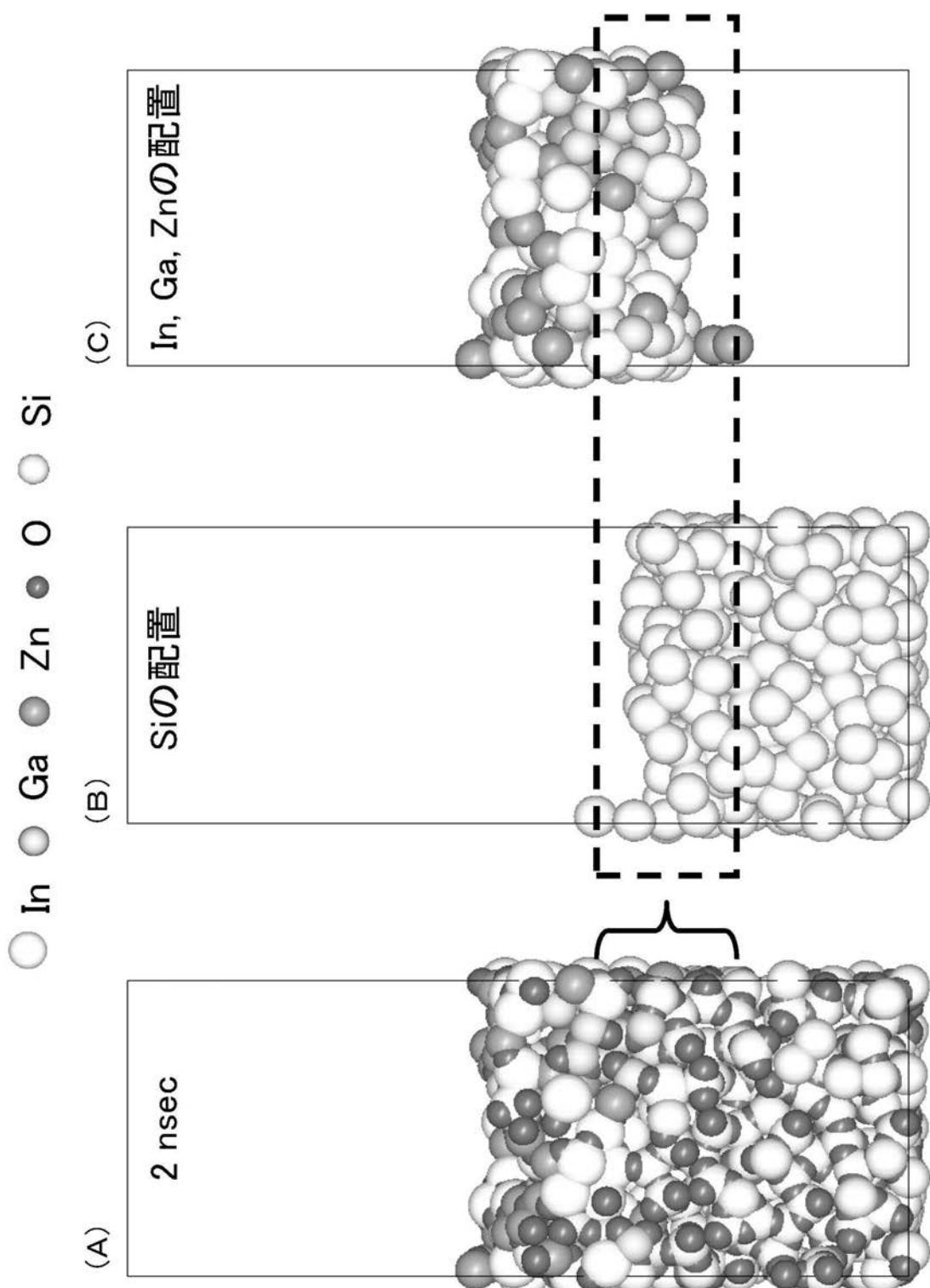

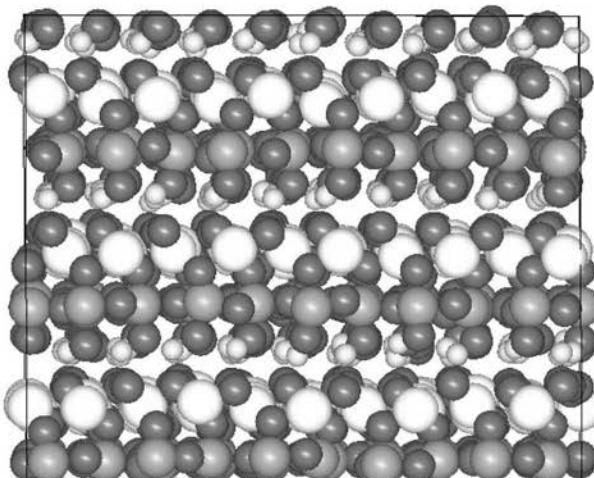

ゲート絶縁膜としてアモルファス酸化シリコン膜（以下、 $a\text{-SiO}_2$ と記す。）を用いて、図6に示すモデルを作製した。計算に係る単位胞（計算単位胞）のサイズは、 $x$ 軸方向に3 nm、 $y$ 軸方向に3 nm、 $z$ 軸方向に7.5 nmとした。ここで、 $x$ 軸及び $y$ 軸は、 $a\text{-SiO}_2$ 膜に平行な方向であり、 $z$ 軸は、 $a\text{-SiO}_2$ 膜の膜厚方向である。なお、計算に当たって、 $x$ 軸方向及び $y$ 軸方向に周期境界条件を適用することで、 $x$ 軸方向及び $y$ 軸方向に十分広い膜を想定することとした。

10

#### 【 0 1 2 2 】

次に、 $a\text{-SiO}_2$ 膜上に、1 eVのエネルギーをもつインジウム原子、ガリウム原子、亜鉛原子、酸素原子を、1:1:1:4の割合（合計840原子）で、上方（図6中、原子発生）から下方に向かって入射させ、温度を300、時間を2 nsec（時間刻み幅を0.2 fs、ステップ数を1000万回）として古典分子動力学計算を行った。

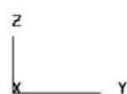

#### 【 0 1 2 3 】

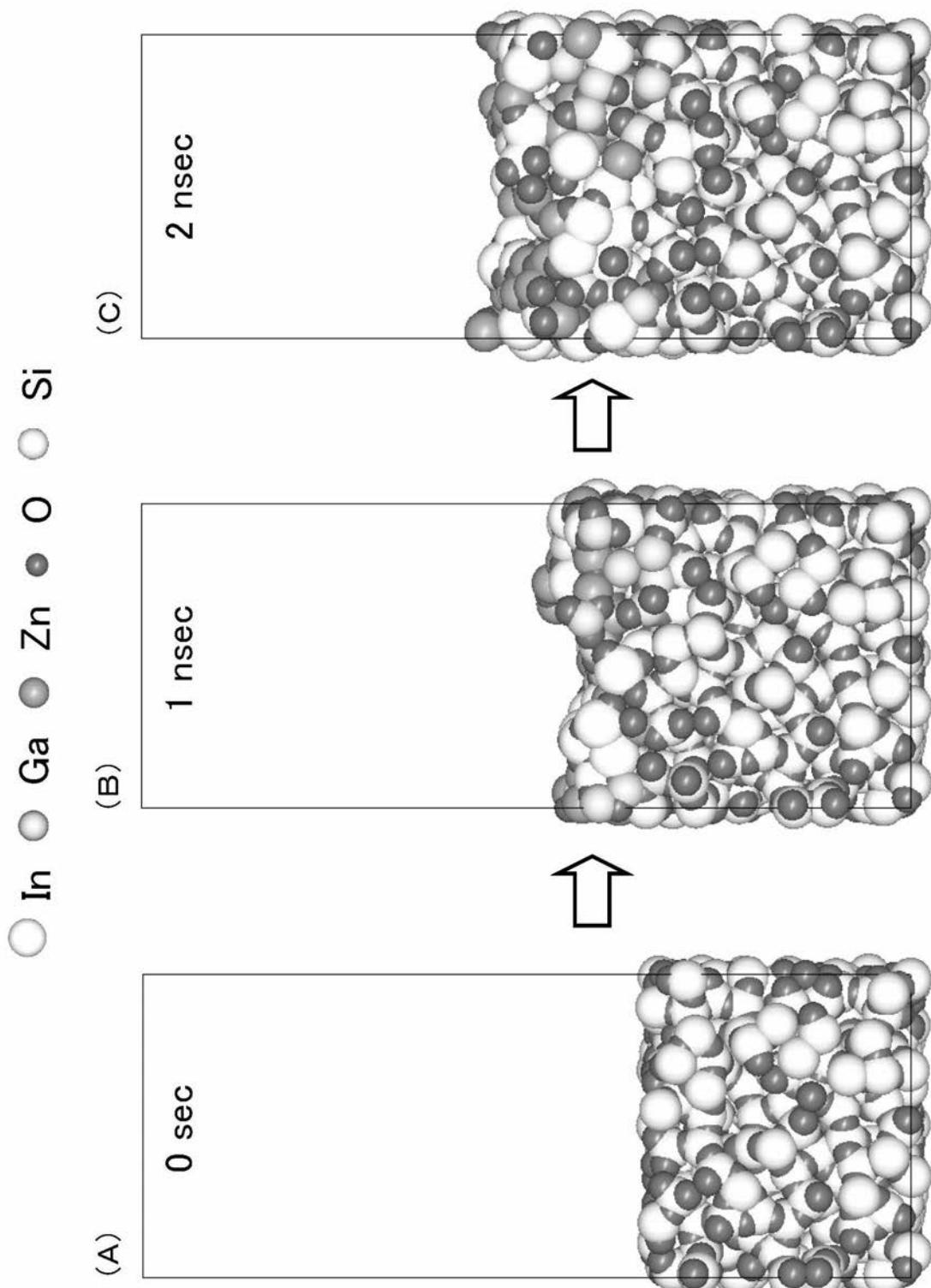

図7及び図8に、上記計算の結果を示す。図7(A)に、0 secにおける酸素原子及びシリコン原子の配置を示し、図7(B)に、1 nsec後の酸素原子、シリコン原子、ガリウム原子、及び亜鉛原子の配置を示し、図7(C)に、2 nsec後の酸素原子、シリコン原子、ガリウム原子、及び亜鉛原子の配置を示す。また、図8(A)は、2 nsec後の酸素原子、シリコン原子、ガリウム原子、及び亜鉛原子の配置を示し、図8(B)に、2 nsec後のシリコン原子のみの配置を示し、図8(C)に、2 nsec後のインジウム原子、ガリウム原子、及び亜鉛原子の配置を示す。

20

#### 【 0 1 2 4 】

図8(B)に示すシリコン原子のみの配置と、図8(C)に示すインジウム原子、ガリウム原子、及び亜鉛原子の配置とを比較することによって、シリコン原子の層に、インジウム原子、ガリウム原子、及び亜鉛原子が浸入していることが確認された。

#### 【 0 1 2 5 】

上記計算の結果から、1 eVのエネルギーをもつインジウム原子、ガリウム原子、亜鉛原子、および酸素原子を、 $a\text{-SiO}_2$ 膜に入射させることより、 $a\text{-SiO}_2$ 膜とIGZO膜との間に、シリコン原子、インジウム原子、ガリウム原子、亜鉛原子、および酸素原子とが混合した層が形成されることが示された。

30

#### 【 0 1 2 6 】

以上の結果から、酸化物半導体膜103とゲート絶縁膜102とが混合した層を形成させないためには、酸化物半導体膜103を構成する粒子がゲート絶縁膜102に衝突する勢いを弱くすることが有効であり、例えば、酸化物半導体膜103の成膜電力を低くする、成膜圧力を高くする方法がある。または、ターゲットと被成膜基板間の距離（以下、T-S間距離とも記載する。）を広げてもよい。

#### 【 0 1 2 7 】

なお、上述のようにスパッタリングによるミキシングは、ゲート絶縁膜102との界面近傍の酸化物半導体膜103中において発生しうる。よって、酸化物半導体膜103を構成する粒子がゲート絶縁膜102に衝突する勢いを弱くしてスパッタリングを行って、ミキシング効果を低減して当該界面近傍の酸化物半導体膜を成膜してしまえば、その後は衝突する勢いを強くしてもよい。例えば、酸化物半導体膜103の成膜電力を低くして当該界面近傍の酸化物半導体膜を成膜し、それから成膜電力を高くして酸化物半導体膜を成膜してもよい。また、酸化物半導体膜103の成膜圧力を高くして当該界面近傍の酸化物半導体膜を成膜してから成膜圧力を低くして酸化物半導体膜を成膜してもよい。また、酸化物半導体膜103のT-S間距離を広くして当該界面近傍の酸化物半導体膜を成膜し、それからT-S間距離を狭くして酸化物半導体膜を成膜してもよい。

40

#### 【 0 1 2 8 】

50

成膜電力の具体的な数値としては、5 kW以下、好ましくは1 kW以下、より好ましくは500W以下、更に好ましくは200W以下とすることが望ましい。なお、成膜電力を下げるほど酸化物半導体膜103の成膜レートが低下してしまう。また、成膜電力が非常に低いと、スパッタリング装置内でプラズマが発生しにくくなり、正常に成膜処理が行えなくなる可能性が高まる。このため、成膜電力は、使用するスパッタ装置で印加することのできる最大電力の5%以上とすることが望ましい。成膜電力をどの程度まで下げるかについては、スパッタリング装置の性能や酸化物半導体膜103の膜厚などを鑑み、成膜を正常に行うことができ、かつ、成膜時間がトランジスタ110の作製工程（タクトタイム）に対して重大な影響を及ぼさない範囲で、実施者が適宜最適な電力値を選択すればよい。

## 【0129】

10

また、成膜圧力の具体的な数値としては、0.4Pa以上、好ましくは1.0Pa以上、より好ましくは2.0Pa以上、更に好ましくは5.0Pa以上とすることが望ましい。なお、成膜圧力を高くするほど、成膜される膜の膜質が悪化する（例えば、膜質が疎になる。）傾向がある。このため、成膜圧力は100Pa以下とすることが望ましい。成膜圧力をどの程度まで高めるかについては、酸化物半導体膜103に必要とされる特性（例えば、電界効果移動度など）を鑑み、実施者が適宜最適な圧力値を選択すればよい。

## 【0130】

また、T-S間距離の具体的な数値としては、30mm以上、好ましくは50mm以上、より好ましくは100mm以上、更に好ましくは300mm以上とすることが望ましい。なお、T-S間距離を広くするほど酸化物半導体膜103の成膜レートが低下してしまう。このため、T-S間距離は500mm以下とすることが望ましい。T-S間距離をどの程度まで広げるかについては、成膜時間がトランジスタ110の作製工程（タクトタイム）に対して重大な影響を及ぼさない範囲で、実施者が適宜最適なT-S間距離を選択すればよい。

20

## 【0131】

なお、酸化物半導体膜103を構成する粒子がゲート絶縁膜102に衝突する勢いを弱くするためには、成膜電力、成膜圧力またはT-S間距離のいずれか一つの条件を上述の範囲として酸化物半導体膜103を成膜してもよいし、複数の条件を上述の範囲として酸化物半導体膜103を成膜してもよい。

## 【0132】

30

なお、スパッタリング装置として、ターゲットと被成膜基板が略平行に設置されたマグネットロン方式スパッタ装置（単に、マグネットロൺスパッタ装置とも言われる。）を用いた場合、ゲート絶縁膜102には、酸化物半導体膜103を構成する粒子以外にもプラズマや二次電子なども衝突するため、ゲート絶縁膜102を構成する元素が酸化物半導体膜103中に非常に混入しやすい状態にあると言える。このため、酸化物半導体膜103を成膜するスパッタリング装置としては、対向ターゲット式スパッタ装置（ミラートロൺスパッタ装置とも言われる。）を用いてもよい。当該装置は、2枚のターゲットが対向する状態に設置され、被成膜基板は2枚のターゲットに挟まれた空間以外の場所に、ターゲットに対して概垂直な状態に設置されている。そして、対向する2枚のターゲット間に高密度のプラズマを生成し、当該プラズマによりターゲット（酸化物半導体膜103の成膜に用いるターゲット。）表面がスパッタリングされることで、被成膜基板に酸化物半導体膜103が成膜される。このため、被成膜基板はプラズマや二次電子に直接晒されることがない（または非常に少ない）。

40

## 【0133】

また、酸化物半導体膜103のスパッタリング成膜を希ガス雰囲気で行う場合、アルゴンの代わりにヘリウムを用いてもよい。アルゴンより原子量の小さいヘリウムを用いることにより、酸化物半導体膜103を構成する粒子がゲート絶縁膜102に衝突する勢いを弱くすることができる。さらに、酸化物半導体膜103のゲート絶縁膜102との界面近傍の成膜をヘリウム雰囲気で行った後、成膜室内をアルゴン雰囲気に切り替えることにより、酸化物半導体膜103の成膜スピードを向上させることができる。

50

**【 0 1 3 4 】**

また、酸化物半導体膜 103 を、 A L D ( A t o m i c L a y e r D e p o s i t i o n ) 法、蒸着法、塗布法などのゲート絶縁膜 102 への衝撃が弱い方法で成膜してもよい。

**【 0 1 3 5 】**

以上のように、酸化物半導体膜 103 を構成する粒子がゲート絶縁膜 102 に衝突する勢いを弱くして酸化物半導体膜 103 を成膜することで、上述のように酸化物半導体膜 103 において、ゲート絶縁膜 102 との界面から酸化物半導体膜 103 に向けてシリコンが 1.0 原子 % 以下の濃度で分布する領域 103a と、領域 103a より含有されるシリコン濃度が小さい領域 103b が形成される。ここで、領域 103b とは、酸化物半導体膜 103 の領域 103a 以外の領域のことである。また、領域 103a に含まれるシリコンの濃度は、 0.1 原子 % 以下であるとより好ましい。10

**【 0 1 3 6 】**

また、このようにして酸化物半導体膜 103 を成膜することでゲート絶縁膜 102 中に含まれる炭素などの不純物が酸化物半導体膜 103 に混入することも低減されるので、上述のように領域 103a に含まれる炭素濃度は  $1.0 \times 10^{20}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1.0 \times 10^{19}$  atoms / cm<sup>3</sup> 以下となる。

**【 0 1 3 7 】**

また、酸化物半導体膜 103 として C A A C - O S 膜を加熱しながら成膜する（一つめの方法）場合、領域 103a に取り込まれるシリコンなどの不純物の量を低減することにより、C A A C - O S 膜の被形成面近傍においても、酸化物半導体膜の被形成面または表面に対して c 軸が垂直な方向に揃った結晶部を形成することができる。20

**【 0 1 3 8 】**

また、酸化物半導体膜 103 を構成する粒子がゲート絶縁膜 102 に衝突する勢いを弱くして酸化物半導体膜 103 を成膜することにより、ゲート絶縁膜 102 中に酸化物半導体膜 103 を構成する元素が混入することも抑制できる。これにより、ゲート絶縁膜 102 中に酸化物半導体膜 103 を構成する金属元素などの導電性の高い元素が混入することを抑制できるので、ゲート絶縁膜 102 の抵抗率の低減を防ぐことができる。

**【 0 1 3 9 】**

また、酸化物半導体膜 103 の成膜後、酸化物半導体膜 103 に対して、熱処理を行ってよい。当該熱処理の温度は、 200 以上 700 以下、または基板の歪み点未満とする。当該熱処理を行うことで、過剰な水素（水や水酸基を含む）を除去することが可能である。30

**【 0 1 4 0 】**

また、二つめの方法または三つめの方法を用いて、C A A C - O S 膜を形成する場合には、当該熱処理を行うことにより、酸化物半導体膜の被形成面または表面に対して c 軸が垂直な方向に揃った結晶部を形成することができる。また、酸化物半導体膜 103 の領域 103a において、シリコンなどの不純物の濃度が低減されているため、酸化物半導体膜 103 の被形成面近傍まで該結晶部を形成させることができる。

**【 0 1 4 1 】**

当該熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、 450 、 1 時間の条件で行うことができる。この間、酸化物半導体膜 103 は大気に触れさせず、水や水素の混入が生じないようにする。40

**【 0 1 4 2 】**

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、 G R T A ( G a s R a p i d Thermal Anneal ) 装置、 L R T A ( Lamp Rapid Thermal Anneal ) 装置等の R T A ( R a p i d Thermal Anneal ) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ラン50

プなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。

#### 【 0 1 4 3 】

例えば、当該熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間加熱した後、当該不活性ガス雰囲気から被処理物を取り出す G R T A 処理を行ってもよい。G R T A 処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えても良い。

10

#### 【 0 1 4 4 】

なお、不活性ガス雰囲気としては、窒素、または希ガス（ヘリウム、ネオン、アルゴン等）を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6 N ( 9 9 . 9 9 9 9 % ) 以上、好ましくは 7 N ( 9 9 . 9 9 9 9 9 % ) 以上（すなわち、不純物濃度が 1 p p m 以下、好ましくは 0 . 1 p p m 以下）とする。

#### 【 0 1 4 5 】

また、当該熱処理で酸化物半導体膜 1 0 3 を加熱した後、同じ炉に高純度の酸素ガス、一酸化二窒素ガス、高純度の一酸化二窒素ガス、又は超乾燥エア（C R D S（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が 2 0 p p m（露点換算で - 5 5 ）以下、好ましくは 1 p p m 以下、より好ましくは 1 0 p p b 以下の空気）を導入してもよい。酸素ガスまたは一酸化二窒素ガスに、水、水素などが含まれないことが好ましい。または、熱処理装置に導入する酸素ガスまたは一酸化二窒素ガスの純度を、6 N 以上好ましくは 7 N 以上（即ち、酸素ガスまたは一酸化二窒素ガス中の不純物濃度を 1 p p m 以下、好ましくは 0 . 1 p p m 以下）とすることが好ましい。酸素ガス又は一酸化二窒素ガスの作用により、上記熱処理によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体膜を高純度化及び i 型（真性）化することができる。

20

#### 【 0 1 4 6 】

また、三つめの方法を用いて、C A A C - O S 膜を形成する場合には、さらに酸化物半導体膜を成膜すればよい。これにより、酸化物半導体膜の被形成面または表面に対して c 軸が垂直な方向に揃った結晶部を種として、その上に成膜された酸化物半導体膜も、該結晶部を有する酸化物半導体膜とすることができます。

30

#### 【 0 1 4 7 】

なお、C A A C - O S 膜以外の結晶性を有する酸化物半導体膜（単結晶または微結晶）を形成する場合、当該熱処理を行うことにより、酸化物半導体膜を結晶化させることができる。また、酸化物半導体膜 1 0 3 の領域 1 0 3 a において、シリコンなどの不純物の濃度が低減されているため、酸化物半導体膜の被形成面まで結晶化させることができる。

#### 【 0 1 4 8 】

なお、ここでは、酸化物半導体膜を島状に加工する前に、熱処理を行う構成について説明したが、開示する発明の一態様はこれに限定して解釈されない。酸化物半導体膜を島状に加工した後に、当該熱処理を行ってもよい。

40

#### 【 0 1 4 9 】

次いで、酸化物半導体膜 1 0 3 をフォトリソグラフィ工程により島状の酸化物半導体膜 1 0 3 に加工するのが好ましい（図 4 ( C ) 参照）。また、島状の酸化物半導体膜 1 0 3 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。なお、酸化物半導体膜 1 0 3 のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

#### 【 0 1 5 0 】

50

ここで、図4(C)に示すように、酸化物半導体膜103は端部に20°乃至50°のテー<sup>10</sup>パーを有していることが好ましい。酸化物半導体膜103の端部が垂直であると酸化物半導体膜103から酸素が抜けやすく酸素欠損を生じやすいが、酸化物半導体膜103の端部にテー<sup>10</sup>パーを有することで酸素欠損の発生を抑制し、トランジスタ110のリーク電流の発生を低減することができる。

#### 【0151】

次いで、酸化物半導体膜103上に、ソース電極及びドレイン電極(これと同じ層で形成される配線を含む)に用いる導電膜を成膜する。ソース電極及びドレイン電極に用いる導電膜としては、例えば、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タングステン膜)等を用いることができる。また、アルミニウム、銅などの金属膜の下側又は上側の一方または双方にチタン、モリブデン、タングステンなどの高融点金属膜またはそれらの金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タングステン膜)を積層させた構成としても良い。また、ソース電極及びドレイン電極に用いる導電膜は、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、インジウムスズ酸化物( $In_2O_3 - SnO_2$ 、ITOと略記する)、インジウム亜鉛酸化物( $In_2O_3 - ZnO$ )を用いることができる。ソース電極及びドレイン電極に用いる導電膜は、上記の材料を用いて単層で又は積層して成膜することができる。<sup>20</sup>形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンドル法などの各種成膜方法を用いることができる

#### 【0152】

フォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極105a、ドレイン電極105bを形成した後、レジストマスクを除去する(図4(D)参照)。当該フォトリソグラフィ工程におけるレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いることが好ましい。ここで、酸化物半導体膜103上で隣り合うソース電極105aの下端部とドレイン電極105bの下端部との間隔幅によって、後に形成されるトランジスタのチャネル長Lが決定される。よって、チャネル長L=25nm未満の露光を行う場合には、例えば、数nm~数10nmと極めて波長が短い超紫外線(Extreme Ultraviolet)を用いてフォトリソグラフィ工程でのレジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを微細化することが可能であり、回路の動作速度を高速化できる。<sup>30</sup>

#### 【0153】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。<sup>40</sup>

#### 【0154】

なお、導電膜のエッチングの際に、酸化物半導体膜103がエッチングされ、分断することのないようエッチング条件を最適化することが望まれる。しかしながら、導電膜のみをエッチングし、酸化物半導体膜103を全くエッチングしないという条件を得ることは難しく、導電膜のエッチングの際に酸化物半導体膜103は一部のみがエッチングされ、例えば、酸化物半導体膜103の膜厚の5%乃至50%がエッチングされ、溝部(凹部)を有する酸化物半導体膜103となることもある。

#### 【0155】

10

20

30

40

50

次いで、ソース電極 105a、及びドレイン電極 105b を覆い、且つ酸化物半導体膜 103 の一部と接する保護絶縁膜 109 を形成する（図 4（E）参照）。保護絶縁膜 109 としては、無機絶縁膜を用いることが好ましく、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ガリウム膜、酸化ハフニウム膜などの酸化物絶縁膜を単層、或いは積層して用いればよい。また、上述の酸化物絶縁膜上に、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、窒化酸化アルミニウム膜などの窒化物絶縁膜の単層、或いは積層をさらに形成してもよい。例えば、スパッタリング法を用いて、ソース電極 105a 及びドレイン電極 105b 側から順に酸化シリコン膜及び酸化アルミニウム膜の積層を形成する。

## 【0156】

10

なお、当該工程において、保護絶縁膜 109 を、スパッタリング法を用いて成膜する場合、酸化物半導体膜 103 を成膜する場合と同様に、保護絶縁膜 109 を構成する粒子が酸化物半導体膜 103 に衝突する勢いを弱くすることが有効である。これにより、酸化物半導体膜 103 と保護絶縁膜 109 が接する界面近傍に領域 103c が形成される。これにより、図 2（A）および図 2（B）に示すトランジスタ 120 が形成される。ここで、領域 103c は、酸化物半導体膜 103 において、保護絶縁膜 109 との界面から酸化物半導体膜 103 に向けてシリコンが 1.0 原子%以下の濃度で分布する領域である。領域 103c は、保護絶縁膜 109 との界面からの厚さが 5 nm 以下の範囲に存在することが好ましい。

## 【0157】

20

ここで、保護絶縁膜 109 としては、ゲート絶縁膜 102 と同様の絶縁膜を用いることができる。また、シリコンなどの不純物を酸化物半導体膜 103 に混入させないためには、酸化物半導体膜 103 と保護絶縁膜 109 の界面近傍においてミキシングを抑制させねばよいため、スパッタリングの時に保護絶縁膜 109 を構成するシリコンが酸化物半導体膜 103 に衝突する勢いを弱くすればよい。例えば、保護絶縁膜 109 の成膜電力を低くする、保護絶縁膜 109 の成膜圧力を高くする、または T-S 間距離を長くする等の方法がある。

## 【0158】

このように、酸化物半導体膜 103 のバックチャネルに当たる領域 103c においても、シリコンなどの不純物の濃度を低減させることができる。

30

## 【0159】

以下、トランジスタ 110 の作製方法と同様の工程でトランジスタ 120 を作製することができる。

## 【0160】

保護絶縁膜 109 の成膜後、酸化物半導体膜 103 に対して熱処理を行うのが好ましい。当該熱処理の温度は、300 以上 700 以下、または基板の歪み点未満とする。

## 【0161】

当該熱処理は、窒素、酸素、超乾燥空気（水の含有量が 20 ppm 以下、好ましくは 1 ppm 以下、好ましくは 10 ppm 以下の空気）、または希ガス（アルゴン、ヘリウムなど）の雰囲気下で行えばよいが、上記窒素、酸素、超乾燥空気、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、熱処理装置に導入する窒素、酸素、または希ガスの純度を、6N（99.9999%）以上好ましくは 7N（99.9999%）以上（即ち不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下）とすることが好ましい。

40

## 【0162】

酸化物半導体膜成膜後の熱処理によって、酸化物半導体を構成する主成分材料の一つである酸素が同時に減少してしまう可能性がある。しかし、当該熱処理において、シリコンを含む酸化物を含む絶縁膜を用いて形成されるゲート絶縁膜 102 より、酸素を酸化物半導体膜 103 へ供給することができるので、酸化物半導体膜 103 の酸素欠損を補完することができる。

50

**【 0 1 6 3 】**

上述のような熱処理を行うことで、酸化物半導体膜 103 を、その主成分以外の不純物が極力含まれないように高純度化することができる。高純度化された酸化物半導体膜 103 中にはドナーに由来するキャリアが極めて少なく(ゼロに近い)、キャリア濃度は  $1 \times 10^{-4} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{-2} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{-1} / \text{cm}^3$  未満である。このようにして、i型(真性)化された酸化物半導体膜 103 を形成することができる。

**【 0 1 6 4 】**

以上の工程でトランジスタ 110 が形成される(図 4(E) 参照)。トランジスタ 110 は、酸化物半導体膜 103 の領域 103a に取り込まれるシリコンなどの不純物の濃度が低減されている。これにより、トランジスタ 110 を、安定した電気特性を有するものとすることができる。

**【 0 1 6 5 】**

また、トランジスタ 110 上に平坦化絶縁膜を設けても良い。平坦化絶縁膜としては、アクリル樹脂、ポリイミド樹脂、ベンゾシクロブテン系樹脂、ポリアミド樹脂、エポキシ樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(LOW-k 材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させてもよい。

**【 0 1 6 6 】****トランジスタ 130 の作製工程**

次に、図 5(A) 乃至図 5(E) を用いて、図 3 に示すトランジスタ 130 の作製工程の一例について説明する。

**【 0 1 6 7 】**

まず、図 4(C) に示す工程までトランジスタ 110 と同様の方法で、基板 100 上にゲート電極 101、ゲート絶縁膜 102 および、領域 103a および領域 103b を有する酸化物半導体膜 103 を形成する(図 5(A) 参照)。基板 100、ゲート電極 101、ゲート絶縁膜 102 および酸化物半導体膜 103 の詳細については、図 4(A) 乃至図 4(C) に関する記載を参照することができる。

**【 0 1 6 8 】**

次に、チャネル保護膜に用いる絶縁膜 107 を膜厚 5 nm 以上 300 nm 以下として成膜する(図 5(B) 参照)。絶縁膜 107 としては、酸素を含む無機絶縁膜を用いることが好ましく、例えば、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ガリウム膜、酸化ハフニウム膜などの絶縁膜を用いることができる。また、絶縁膜 107 の作製方法に特に限定はないが、例えば、スパッタリング法、MBE 法、CVD 法、パルスレーザ堆積法、ALD 法等を適宜用いて成膜することができる。

**【 0 1 6 9 】**

次に、フォトリソグラフィ工程により絶縁膜 107 上にレジストマスクを形成し、エッチングを行ってチャネル保護膜 108 を形成した後、レジストマスクを除去する(図 5(C) 参照)。また、チャネル保護膜 108 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。ここでチャネル保護膜 108 のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

**【 0 1 7 0 】**

ここで、図 5(C) に示すように、チャネル保護膜 108 は端部に 10° 以上 60° 以下のテーパーを有していることが好ましい。チャネル保護膜 108 をこのような形状とすることにより、チャネル保護膜 108 の下端部近傍における電界集中を緩和することができる。

**【 0 1 7 1 】**

10

20

30

40

50

このように、酸化物半導体膜 103 上に接してチャネル保護膜 108 を設けることにより、ソース電極 105a およびドレイン電極 105b のエッティングによる酸化物半導体膜 103 のバックチャネル側へのダメージ（例えば、エッティング時のプラズマまたはエッティング剤によるダメージ）を防ぐことができる。これにより、安定した電気特性を有する、酸化物半導体を用いた半導体装置を提供することができる。

#### 【0172】

次に、チャネル保護膜 108 および酸化物半導体膜 103 上に、ソース電極及びドレイン電極（これと同じ層で形成される配線を含む）に用いる導電膜を成膜し、フォトリソグラフィ工程により当該導電膜を選択的にエッティングしてソース電極 105a およびドレイン電極 105b を形成する（図 5（D）参照）。当該工程は図 4（D）に示す工程と同様の方法を用いて行うことができるので、ソース電極 105a およびドレイン電極 105b の詳細については、図 4（D）に関する記載を参照することができる。10

#### 【0173】

次いで、ソース電極 105a、及びドレイン電極 105b およびチャネル保護膜 108 を覆って保護絶縁膜 109 を形成する（図 5（E）参照）。当該工程は図 4（E）に示す工程と同様の方法を用いて行うことができるので、保護絶縁膜 109 の詳細については、図 4（E）に関する記載を参照することができる。

#### 【0174】

以上のようにして、酸化物半導体膜を成膜することにより、酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減することができる。また、酸化物半導体膜 103 の被形成面近傍まで結晶化させることができるために、酸化物半導体膜 103 の結晶性を向上させることができる。また、酸化物半導体膜 103 を C A A C - O S 膜とする場合には、被形成面近傍まで結晶部を形成することができる。なお、結晶部は、酸化物半導体膜 103 とゲート絶縁膜 102 との界面、または酸化物半導体膜 103 と保護絶縁膜 109 との界面に対して c 軸が垂直な方向に揃っている。このような酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供することができる。20

#### 【0175】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

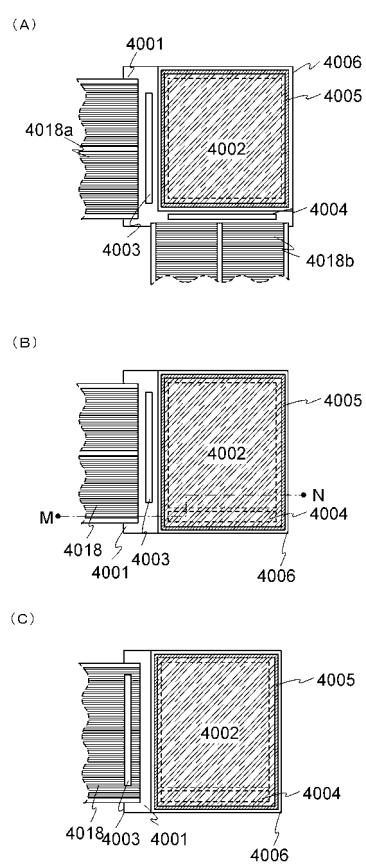

#### 【0176】

##### （実施の形態 2）

実施の形態 1 で例示したトランジスタを用いて表示機能を有する半導体装置（表示装置ともいう）を作製することができる。また、トランジスタを含む駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

#### 【0177】

図 9（A）において、第 1 の基板 4001 上に設けられた画素部 4002 を囲むようにして、シール材 4005 が設けられ、第 2 の基板 4006 によって封止されている。図 9（A）においては、第 1 の基板 4001 上のシール材 4005 によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された走査線駆動回路 4004、信号線駆動回路 4003 が実装されている。また、別途形成された信号線駆動回路 4003 と、走査線駆動回路 4004 または画素部 4002 に与えられる各種信号及び電位は、F P C (Flexible printed circuit) 4018a、4018b から供給されている。40

#### 【0178】

図 9（B）及び図 9（C）において、第 1 の基板 4001 上に設けられた画素部 4002 と、走査線駆動回路 4004 とを囲むようにして、シール材 4005 が設けられている。また画素部 4002 と、走査線駆動回路 4004 の上に第 2 の基板 4006 が設けられている。よって画素部 4002 と、走査線駆動回路 4004 とは、第 1 の基板 4001 とシール材 4005 と第 2 の基板 4006 とによって、表示素子と共に封止されている。図 9（B）及び図 9（C）においては、第 1 の基板 4001 上のシール材 4005 によって囲50

まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路 4003 が実装されている。図 9 (B) 及び図 9 (C)においては、別途形成された信号線駆動回路 4003 と、走査線駆動回路 4004 または画素部 4002 に与えられる各種信号及び電位は、FPC4018 から供給されている。

#### 【0179】

また、図 9 (B) 及び図 9 (C)においては、信号線駆動回路 4003 を別途形成し、第 1 の基板 4001 に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

10

#### 【0180】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG (Chip On Glass) 方法、ワイヤボンディング方法、或いは TAB (Tape Automated Bonding) 方法などを用いることができる。図 9 (A) は、COG 方法により信号線駆動回路 4003、走査線駆動回路 4004 を実装する例であり、図 9 (B) は、COG 方法により信号線駆動回路 4003 を実装する例であり、図 9 (C) は、TAB 方法により信号線駆動回路 4003 を実装する例である。

#### 【0181】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。

20

#### 【0182】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源（照明装置含む）を指す。

#### 【0183】

また、コネクター、例えば FPC もしくは TAB テープもしくは TCP が取り付けられたモジュール、TAB テープや TCP の先にプリント配線板が設けられたモジュール、または表示素子に COG 方式により IC（集積回路）が直接実装されたモジュールも全て表示装置に含むものとする。

#### 【0184】

また、第 1 の基板上に設けられた画素部及び走査線駆動回路は、トランジスタを複数有しており、実施の形態 1 に例示したトランジスタを適用することができる。

30

#### 【0185】

表示装置に設けられる表示素子としては液晶素子（液晶表示素子ともいう）、発光素子（発光表示素子ともいう）、を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機 EL（Electro Luminescence）、有機 EL 等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

#### 【0186】

半導体装置の一形態について、図 10 乃至図 12 を用いて説明する。図 10 乃至図 12 は、図 9 (B) の M - N における断面図に相当する。

40

#### 【0187】

図 10 乃至図 12 で示すように、半導体装置は接続端子電極 4015 及び端子電極 4016 を有しており、接続端子電極 4015 及び端子電極 4016 は FPC4018 が有する端子と異方性導電膜 4019 を介して、電気的に接続されている。

#### 【0188】

接続端子電極 4015 は、第 1 の電極層 4030 と同じ導電膜から形成され、端子電極 4016 は、トランジスタ 4010、トランジスタ 4011 のソース電極及びドレイン電極と同じ導電膜で形成されている。

#### 【0189】

また、第 1 の基板 4001 上に設けられた画素部 4002 と、走査線駆動回路 4004 は

50

、トランジスタを複数有しており、図10乃至図12では、画素部4002に含まれるトランジスタ4010と、走査線駆動回路4004に含まれるトランジスタ4011とを例示している。

#### 【0190】

本実施の形態では、トランジスタ4010、トランジスタ4011として、実施の形態1で示したトランジスタを適用することができる。トランジスタ4010、トランジスタ4011は、電気的特性変動が抑制されており、電気的に安定である。よって、図10乃至図12で示す本実施の形態の半導体装置として信頼性の高い半導体装置を提供することができる。

#### 【0191】

走査線駆動回路4004に含まれるトランジスタ4011は、絶縁膜4034上に第2のゲート電極を設ける構造である。第2のゲート電極に印加される電圧を制御することにより、トランジスタ4011のしきい値電圧を制御することができる。

#### 【0192】

画素部4002に設けられたトランジスタ4010は表示素子と電気的に接続し、表示パネルを構成する。表示素子は表示を行うことができれば特に限定されず、様々な表示素子を用いることができる。

#### 【0193】

図10に表示素子として液晶素子を用いた液晶表示装置の例を示す。図10において、表示素子である液晶素子4013は、第1の電極層4030、第2の電極層4031、及び液晶層4008を含む。なお、液晶層4008を挟持するように配向膜として機能する絶縁膜4032、絶縁膜4033が設けられている。第2の電極層4031は第2の基板4006側に設けられ、第1の電極層4030と第2の電極層4031とは液晶層4008を介して積層する構成となっている。

#### 【0194】

また、4035は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、液晶層4008の膜厚(セルギャップ)を制御するために設けられている。なお、球状のスペーサを用いていても良い。

#### 【0195】

表示素子として、液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スマクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

#### 【0196】

また、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために数重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1 msec以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。また、配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。よって、液晶表示装置の生産性を向上させることができる。

#### 【0197】

また、液晶材料の固有抵抗率は、 $1 \times 10^9 \text{ } \cdot \text{cm}$ 以上であり、好ましくは $1 \times 10^{11} \text{ } \cdot \text{cm}$ 以上であり、さらに好ましくは $1 \times 10^{12} \text{ } \cdot \text{cm}$ 以上である。なお、本明細書における固有抵抗率の値は、20で測定した値とする。

#### 【0198】

液晶表示装置に設けられる保持容量の大きさは、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間の間電荷を保持できるように設定される。高純度の酸化

10

20

30

40

50

物半導体膜を有するトランジスタを用いることにより、各画素における液晶容量に対して1/3以下、好ましくは1/5以下の容量の大きさを有する保持容量を設ければ充分である。

#### 【0199】

本実施の形態で用いる高純度化された酸化物半導体膜を用いたトランジスタは、オフ状態における電流値（オフ電流値）を低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

#### 【0200】

また、本実施の形態で用いる高純度化された酸化物半導体膜を用いたトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に上記トランジスタを用いることで、高画質な画像を提供することができる。また、上記トランジスタは、同一基板上に駆動回路部または画素部に作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

#### 【0201】

液晶表示装置には、TN (Twisted Nematic) モード、IPS (In-Plane-Switching) モード、FFS (Fringe Field Switching) モード、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optical Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) モードなどを用いることができる。

#### 【0202】

また、ノーマリーブラック型の液晶表示装置、例えば垂直配向 (VA) モードを採用した透過型の液晶表示装置としてもよい。ここで、垂直配向モードとは、液晶表示パネルの液晶分子の配列を制御する方式の一種であり、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。垂直配向モードとしては、いくつか挙げられるが、例えば、MVA (Multi-Domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ASV モード (Advanced Super-View)などを用いることができる。また、画素 (ピクセル) をいくつかの領域 (サブピクセル) に分け、それぞれ別の方向に分子を倒すよう工夫されているマルチドメイン化あるいはマルチドメイン設計といわれる方法を用いることができる。

#### 【0203】

また、表示装置において、ブラックマトリクス (遮光層)、偏光部材、位相差部材、反射防止部材などの光学部材 (光学基板) などは適宜設ける。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

#### 【0204】

また、バックライトとして複数の発光ダイオード (LED) を用いて、時間分割表示方式 (フィールドシーケンシャル駆動方式) を行うことも可能である。フィールドシーケンシャル駆動方式を適用することで、カラーフィルタを用いることなく、カラー表示を行うことができる。

#### 【0205】

また、画素部における表示方式は、プログレッシブ方式やインターレース方式等を用いることができる。また、カラー表示する際に画素で制御する色要素としては、RGB (Rは赤、Gは緑、Bは青を表す) の三色に限定されない。例えば、RGBW (Wは白を表す)、又はRGBに、イエロー、シアン、マゼンタ等を一色以上追加したものがある。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。ただし、本発明の一態

10

20

30

40

50

様はカラー表示の表示装置に限定されるものではなく、モノクロ表示の表示装置に適用することができる。

#### 【0206】

また、表示装置に含まれる表示素子として、エレクトロルミネッセンスを利用する発光素子を適用することができる。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

#### 【0207】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア（電子および正孔）が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

#### 【0208】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー・アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

#### 【0209】

発光素子は発光を取り出すために少なくとも一対の電極の一方が透明であればよい。そして、基板上にトランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、どの射出構造の発光素子も適用することができる。

#### 【0210】

図11に表示素子として発光素子を用いた発光装置の例を示す。表示素子である発光素子4513は、画素部4002に設けられたトランジスタ4010と電気的に接続している。なお発光素子4513の構成は、第1の電極層4030、電界発光層4511、第2の電極層4031の積層構造であるが、示した構成に限定されない。発光素子4513から取り出す光の方向などに合わせて、発光素子4513の構成は適宜変えることができる。

#### 【0211】

隔壁4510は、有機絶縁材料、又は無機絶縁材料を用いて形成する。特に感光性の樹脂材料を用い、第1の電極層4030上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

#### 【0212】

電界発光層4511は、単数の層で構成されていても、複数の層が積層されるように構成されてもどちらでも良い。

#### 【0213】

発光素子4513に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4031及び隔壁4510上に保護膜を形成してもよい。保護膜としては、窒化シリコン膜、窒化酸化シリコン膜、DLC膜等を形成することができる。また、第1の基板4001、第2の基板4006、及びシール材4005によって封止された空間には充填材4514が設けられ密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム（貼り合わせフィルム、紫外線硬化樹脂フィルム等）やカバー材でパッケージング（封入）することが好ましい。

#### 【0214】

充填材4514としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂また

10

20

30

40

50

は熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル樹脂、ポリイミド樹脂、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。例えば充填材として窒素を用いればよい。

**【0215】**

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてもよい。また、偏光板又は円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

**【0216】**

また、表示装置として、電子インクを駆動させる電子ペーパーを提供することも可能である。電子ペーパーは、電気泳動表示装置(電気泳動ディスプレイ)とも呼ばれており、紙と同じ読みやすさ、他の表示装置に比べ低消費電力、薄くて軽い形状とすることが可能という利点を有している。

**【0217】**

電気泳動表示装置は、様々な形態が考えられ得るが、プラスの電荷を有する第1の粒子とマイナスの電荷を有する第2の粒子とを含むマイクロカプセルが溶媒または溶質に複数分散されたものであり、マイクロカプセルに電界を印加することによって、マイクロカプセル中の粒子を互いに反対方向に移動させて一方側に集合した粒子の色のみを表示するものである。なお、第1の粒子または第2の粒子は染料を含み、電界がない場合において移動しないものである。また、第1の粒子の色と第2の粒子の色は異なるもの(無色を含む)とする。

**【0218】**

このように、電気泳動表示装置は、誘電定数の高い物質が高い電界領域に移動する、いわゆる誘電泳動的効果を利用したディスプレイである。

**【0219】**

上記マイクロカプセルを溶媒中に分散させたものが電子インクと呼ばれるものであり、この電子インクはガラス、プラスチック、布、紙などの表面に印刷することができる。また、カラーフィルタや色素を有する粒子を用いることによってカラー表示も可能である。

**【0220】**

なお、マイクロカプセル中の第1の粒子および第2の粒子は、導電体材料、絶縁体材料、半導体材料、磁性材料、液晶材料、強誘電性材料、エレクトロルミネセント材料、エレクトロクロミック材料、磁気泳動材料から選ばれた一種の材料、またはこれらの複合材料を用いればよい。

**【0221】**

また、電子ペーパーとして、ツイストボール表示方式を用いる表示装置も適用することができる。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を表示素子に用いる電極層である第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を生じさせての球形粒子の向きを制御することにより、表示を行う方法である。

**【0222】**

図12に、半導体装置の一形態としてアクティブマトリクス型の電子ペーパーを示す。図12の電子ペーパーは、ツイストボール表示方式を用いた表示装置の例である。

**【0223】**

トランジスタ4010と接続する第1の電極層4030と、第2の基板4006に設けられた第2の電極層4031との間には黒色領域4615a及び白色領域4615bを有し、周りに液体で満たされているキャビティ4612を含む球形粒子4613が設けられており、球形粒子4613の周囲は樹脂等の充填材4614で充填されている。第2の電極層4031が共通電極(対向電極)に相当する。第2の電極層4031は、共通電位線と電気的に接続される。

10

20

30

40

50

**【0224】**

なお、図10乃至図12において、第1の基板4001、第2の基板4006としては、ガラス基板の他、可撓性を有する基板も用いることができ、例えば透光性を有するプラスチック基板などを用いることができる。プラスチックとしては、FRP (Fiber glass-Reinforced Plastics) 板、PVF (ポリビニルフルオライド) フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。

**【0225】**

絶縁層4021は、無機絶縁材料又は有機絶縁材料を用いて形成することができる。なお、アクリル樹脂、ポリイミド樹脂、ベンゾシクロブテン樹脂、ポリアミド樹脂、エポキシ樹脂等の、耐熱性を有する有機絶縁材料を用いると、平坦化絶縁膜として好適である。また、上記有機絶縁材料の他に、低誘電率材料 (low-k材料)、シリコン系樹脂、PSG (リングガラス)、BPSG (リンボロンガラス) 等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層を形成してもよい。

10

**【0226】**

絶縁層4021の形成法は、特に限定されず、その材料に応じて、スパッタリング法、スピンドルコート法、ディッピング法、スプレー塗布、液滴吐出法 (インクジェット法等)、印刷法 (スクリーン印刷、オフセット印刷等)、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。

20

**【0227】**

表示装置は光源又は表示素子からの光を透過させて表示を行う。よって、光が透過する画素部に設けられる基板、絶縁膜、導電膜などの薄膜はすべて可視光の波長領域の光に対して透光性とする。

**【0228】**

表示素子に電圧を印加する第1の電極層4030及び第2の電極層4031 (画素電極層、共通電極層、対向電極層などともいう) においては、取り出す光の方向、電極層が設けられる場所、及び電極層のパターン構造によって透光性、反射性を選択すればよい。

**【0229】**

第1の電極層4030、第2の電極層4031は、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物 (以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

30

**【0230】**

また、第1の電極層4030、第2の電極層4031はタンクステン (W)、モリブデン (Mo)、ジルコニア (Zr)、ハフニウム (Hf)、バナジウム (V)、ニオブ (Nb)、タンタル (Ta)、クロム (Cr)、コバルト (Co)、ニッケル (Ni)、チタン (Ti)、白金 (Pt)、アルミニウム (Al)、銅 (Cu)、銀 (Ag) 等の金属、又はその合金、若しくはその窒化物から一つ、又は複数種を用いて形成することができる。

40

**【0231】**

また、第1の電極層4030、第2の電極層4031として、導電性高分子 (導電性ポリマーともいう) を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆる 電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはアニリン、ピロールおよびチオフェンの2種以上からなる共重合体またはその誘導体などがあげられる。

**【0232】**

また、トランジスタは静電気などにより破壊されやすいため、駆動回路保護用の保護回路

50

を設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

**【0233】**

以上のように実施の形態1で例示したトランジスタを適用することで、信頼性の高い半導体装置を提供することができる。なお、実施の形態1で例示したトランジスタは上述の表示機能を有する半導体装置のみでなく、電源回路に搭載されるパワーデバイス、LSI等の半導体集積回路、対象物の情報を読み取るイメージセンサ機能を有する半導体装置など様々な機能を有する半導体装置に適用することが可能である。

**【0234】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

10

**【0235】**

(実施の形態3)

本明細書等に開示する半導体装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態で説明した液晶表示装置を具備する電子機器の例について説明する。

**【0236】**

20

図13(A)は、ノート型のパーソナルコンピュータであり、本体3001、筐体3002、表示部3003、キーボード3004などによって構成されている。実施の形態1または2で示した半導体装置を適用することにより、信頼性の高いノート型のパーソナルコンピュータとすることができます。

**【0237】**

図13(B)は、携帯情報端末(PDA)であり、本体3021には表示部3023と、外部インターフェイス3025と、操作ボタン3024等が設けられている。また操作用の付属品としてスタイルス3022がある。実施の形態1または2で示した半導体装置を適用することにより、信頼性の高い携帯情報端末(PDA)とすることができます。

**【0238】**

30

図13(C)は、電子書籍の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

**【0239】**

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705および表示部2707は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部(図13(C)では表示部2705)に文章を表示し、左側の表示部(図13(C)では表示部2707)に画像を表示することができる。実施の形態1または2で示した半導体装置を適用することにより、信頼性の高い電子書籍2700とすることができます。

40

**【0240】**

また、図13(C)では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカー2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体插入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

50

**【0241】**

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

**【0242】**

図13(D)は、スマートフォンであり、筐体2800と、ボタン2801と、マイクロフォン2802と、タッチパネルを備えた表示部2803と、スピーカー2804と、カメラ用レンズ2805と、を具備し、携帯型電話機としての機能を有する。実施の形態1または2で示した半導体装置を適用することにより、信頼性の高いスマートフォンとすることができる。10

**【0243】**

表示部2803は、使用形態に応じて表示の方向が適宜変化する。また、表示部2803と同一面上にカメラ用レンズ2805を備えているため、テレビ電話が可能である。スピーカー2804及びマイクロフォン2802は音声通話に限らず、テレビ電話、録音、再生などが可能である。

**【0244】**

また、外部接続端子2806はA Cアダプタ及びU S Bケーブルなどの各種ケーブルと接続可能であり、充電及びパーソナルコンピュータなどとのデータ通信が可能である。また、外部メモリスロット(図示せず)に記録媒体を挿入し、より大量のデータ保存及び移動に対応できる。20

**【0245】**

また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってもよい。

**【0246】**

図13(E)は、デジタルビデオカメラであり、本体3051、表示部(A)3057、接眼部3053、操作スイッチ3054、表示部(B)3055、バッテリー3056などによって構成されている。実施の形態1または2で示した半導体装置を適用することにより、信頼性の高いデジタルビデオカメラとすることができる。

**【0247】**

図13(F)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することが可能である。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。実施の形態1または2で示した半導体装置を適用することにより、信頼性の高いテレビジョン装置9600とすることができる。30

**【0248】**

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機により行うことができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

**【0249】**

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。40

**【0250】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【実施例1】****【0251】**

本実施例では、酸化物ターゲット中に含まれるシリコンの濃度について、S I M S測定を行った結果について説明する。50

**【0252】**

まず、本実施例で用いた酸化物ターゲットについて説明する。

**【0253】**

サンプルAとして、In-Ga-Zn系酸化物ターゲット（原子数比がIn:Ga:Zn = 2:1:3）を用い、サンプルBとしてIn-Ga-Zn系酸化物ターゲット（原子数比がIn:Ga:Zn = 3:1:2）、サンプルCとして、In-Sn-Zn系酸化物（原子数比がIn:Sn:Zn = 2:1:3）を用いた。また、標準サンプルDとして、シリコンが添加されたIn-Ga-Zn系酸化物ターゲット（原子数比がIn:Ga:Zn = 1:1:1）を用いた。

**【0254】**

サンプルA、サンプルB、サンプルC、及び標準サンプルDに対して、SIMS測定を行うことにより、各サンプルに含まれるシリコンの濃度を調べた。

**【0255】**

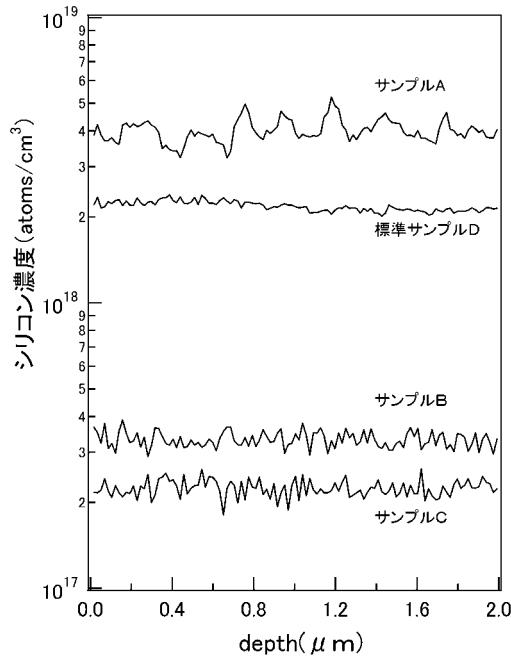

図14に、サンプルA乃至サンプルC、及び標準サンプルDのSIMS測定の結果を示す。

**【0256】**

図14に示すように、サンプルAのシリコンの濃度は、 $4 \times 10^{18}$  atoms/cm<sup>3</sup>、サンプルBのシリコンの濃度は、 $3 \times 10^{17}$  atoms/cm<sup>3</sup>、サンプルCのシリコンの濃度は、 $2 \times 10^{17}$  atoms/cm<sup>3</sup>、標準サンプルDのシリコンの濃度は、 $2 \times 10^{18}$  atoms/cm<sup>3</sup>であることがわかった。なお、サンプルA乃至サンプルCのSIMS測定結果は、標準サンプルDにより定量した結果である。

**【0257】**

上述のデータは、サンプルA乃至サンプルC、及び標準サンプルDのターゲットを用いて酸化物半導体膜を成膜した際に、ターゲット中に含まれるシリコン以外のシリコン（例えば、ミキシングにより混入した絶縁膜中のシリコン）が酸化物半導体膜中に含まれるか否かを判断する材料として用いることができる。

**【0258】**

例えば、ターゲットとしてサンプルA（In:Ga:Zn = 2:1:3（原子数比）である酸化物ターゲット）を用いて成膜した酸化物半導体膜において、膜中のシリコン濃度が $4 \times 10^{18}$  atoms/cm<sup>3</sup>より高い場合、ターゲット以外の部分からシリコンが混入されていると判断できる。

**【実施例2】****【0259】**

上述の実施の形態において、酸化物半導体膜中への絶縁膜構成元素の混入は、酸化物半導体膜を成膜する際に生じるミキシングが原因であると記載したが、酸化物半導体膜を成膜後に基板を加熱処理することで、絶縁膜構成元素が酸化物半導体中に拡散している可能性も考えられる。そこで、本実施例では、酸化物半導体膜中への絶縁膜構成元素の混入が熱拡散に起因するかを調査した実験についての説明を行う。

**【0260】**

実験内容は、まず、基板上に絶縁膜および酸化物半導体膜を形成した構造の基板を3つ準備した後、熱処理を行わないサンプル（以下、サンプルEと呼称する。）、450の熱処理を行ったサンプル（以下、サンプルFと呼称する。）、650の熱処理を行ったサンプル（以下、サンプルGと呼称する。）を作製した。そして、各サンプルについて、飛行時間型二次イオン質量分析法（TOF-SIMS：Time-of-Flight Secondary Ion Mass Spectrometer）を用いて、酸化物半導体膜中のゲート絶縁膜との界面近傍におけるシリコン濃度を測定した。

**【0261】**

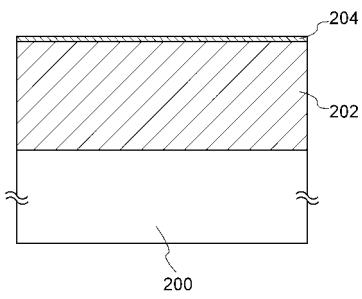

まず、TOF-SIMS測定に用いたサンプルの構造を図15に示す。

**【0262】**

図15に示すサンプルは、シリコン基板200上に酸化シリコン膜202を成膜し、化学

10

20

30

40

50

機械研磨( C M P : Chemical Mechanical Polishing )装置を用いて表面の平坦性を高め、IGZO膜204を成膜し、最後に熱処理を行ったものである。

#### 【0263】

酸化シリコン膜202は、スパッタリング装置を用いて成膜した。酸化シリコン膜202の成膜条件は、基板温度：100、ガス流量： $\text{Ar}/\text{O}_2 = 25 \text{ sccm} / 25 \text{ sccm}$ 、成膜電力：1.5 kW (RF電源)、成膜圧力：0.4 Pa、膜厚：300 nmとした。なお、スパッタリングターゲットとしては、酸化シリコンターゲットを用いた。なお、酸化シリコン膜202を形成する前に、希フ酸にてシリコン基板200表面に形成された酸化膜を除去した。

10

#### 【0264】

IGZO膜204は、スパッタリング装置を用いて成膜した。IGZO膜204の成膜条件は、基板温度：200、ガス流量： $\text{Ar}/\text{O}_2 = 30 \text{ sccm} / 15 \text{ sccm}$ 、成膜電力：0.5 kW (DC電源)、成膜圧力：0.4 Pa、膜厚：15 nmとした。なお、スパッタリングターゲットとしては、In : Ga : Zn = 3 : 1 : 2 [原子数比] の酸化物ターゲットを用いた。

#### 【0265】

熱処理は、抵抗発熱体などを用いた電気炉に基板を導入して加熱処理を行った。処理条件は、サンプルFについては、加熱温度：450、加熱時間：1時間とし、サンプルGについては、加熱温度：650、加熱時間：1時間とした。なお、加熱雰囲気は、両サンプルとも窒素および酸素の混合雰囲気とした。また、サンプルEは、加熱処理を行っていない。

20

#### 【0266】

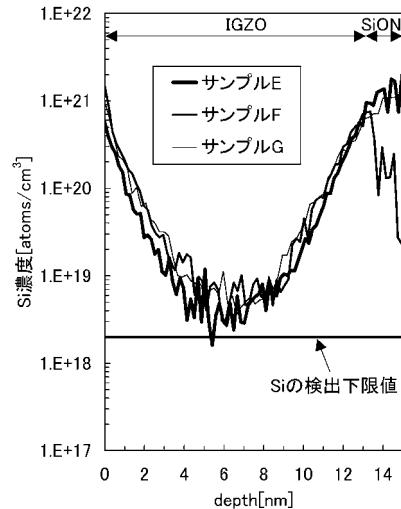

次に、サンプルE乃至サンプルGに対して、基板表面側(IGZO膜204側)からToF-SIMS測定を行い、酸化シリコン膜との界面近傍におけるIGZO膜中のシリコン濃度を測定した。結果を図16に示す。

#### 【0267】

図16より、全てのサンプルにおいて、酸化シリコン膜界面近傍の酸化物半導体膜中のシリコン濃度は、実施例1にて記載したIn-Ga-Zn系酸化物ターゲット(原子数比がIn : Ga : Zn = 3 : 1 : 2)中に含まれるシリコン濃度である $3 \times 10^{17} \text{ atom s/cm}^3$ よりも高くなっていることが確認できる。したがって、酸化シリコン膜界面近傍の酸化物半導体膜中に測定されたシリコンは、In-Ga-Zn系酸化物ターゲット起因のシリコンではないと言える。

30

#### 【0268】

また、図16より、加熱処理を行っていないサンプル(サンプルE)および、加熱処理を行ったサンプル(サンプルFおよびサンプルG)において、酸化シリコン膜界面近傍における、IGZO膜中のシリコン濃度の傾き(シリコン濃度勾配とも言える。)に、特異な差は確認されない。したがって、酸化物半導体膜中への絶縁膜構成元素の混入は、熱拡散に起因するものではなくミキシングに起因するものであると言える。

40

#### 【実施例3】

#### 【0269】

本実施例では、ミキシングによって生じる酸化物半導体膜中への絶縁膜構成元素の混入を、酸化物半導体膜の成膜電力を弱くすることで抑制できるかを調査した実験についての説明を行う。

#### 【0270】

実験内容は、まず、基板上に絶縁膜を成膜し、絶縁膜上に酸化物半導体膜を4種類の電力条件(1 kW、5 kW、9 kWおよび1 kW + 5 kW)で成膜した後に、各基板に対して熱処理を行い4種類のサンプルを作製した。そして、各サンプルについて、酸化物半導体膜中のゲート絶縁膜との界面近傍におけるシリコン濃度を、ToF-SIMS法を用いて測定した。

50

**【0271】**

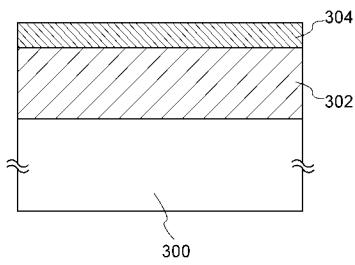

まず、T o F - S I M S 測定に用いたサンプルの構造を図17に示す。

**【0272】**

図17に示すサンプルは、ガラス基板300上に酸化窒化シリコン膜302を成膜した後に、IGZO膜304を成膜し、最後に熱処理を行ったものである。

**【0273】**

酸化窒化シリコン膜302は、高密度プラズマCVD装置を用いて成膜した。酸化窒化シリコン膜302の成膜条件は、基板温度：325、ガス流量： $\text{SiH}_4 / \text{N}_2\text{O} / \text{Ar} = 250 \text{ sccm} / 250 \text{ sccm} / 250 \text{ sccm}$ 、成膜電力： $5 \text{ kW} \times 4$ 台(マイクロ波電源)、成膜圧力：30Pa、膜厚：100nmとした。なお、酸化窒化シリコン膜302を形成する前に、ガラス基板300表面を洗浄してパーティクル等を除去した。

10

**【0274】**

IGZO膜304は、スパッタリング装置を用いて成膜した。IGZO膜304の成膜条件は、基板温度：170、ガス流量： $\text{Ar} / \text{O}_2 = 100 \text{ sccm} / 100 \text{ sccm}$ 、成膜圧力：0.6Pa、膜厚：35nmとし、1kW、5kW、9kWおよび1kW+5kWの4条件の電力で成膜を行った(共に、AC電源使用)。なお、スパッタリングターゲットとしては、 $\text{In : Ga : Zn} = 1 : 1 : 1$ [原子数比]の酸化物ターゲットを用いた。

**【0275】**

なお、上述成膜電力の「1kW+5kW」とは、最初の5nmの成膜を1kWの電力で、その後の30nmの成膜を5kWの電力で成膜したことを表す。また、以下では、酸化物半導体膜を9kWで成膜したサンプルをサンプルH、5kWで成膜したサンプルをサンプルI、1kWで成膜したサンプルをサンプルJ、1kW+5kWで成膜したサンプルをサンプルKと呼称する。

20

**【0276】**

熱処理は、抵抗発熱体などを用いた電気炉に基板を導入して加熱処理を行った。処理条件は、まず、加熱温度：450、加熱雰囲気： $\text{N}_2$ の条件で1時間の加熱を行った後、加熱温度：650、加熱雰囲気： $\text{N}_2 + \text{O}_2$ の条件で、1時間の加熱を行った。

**【0277】**

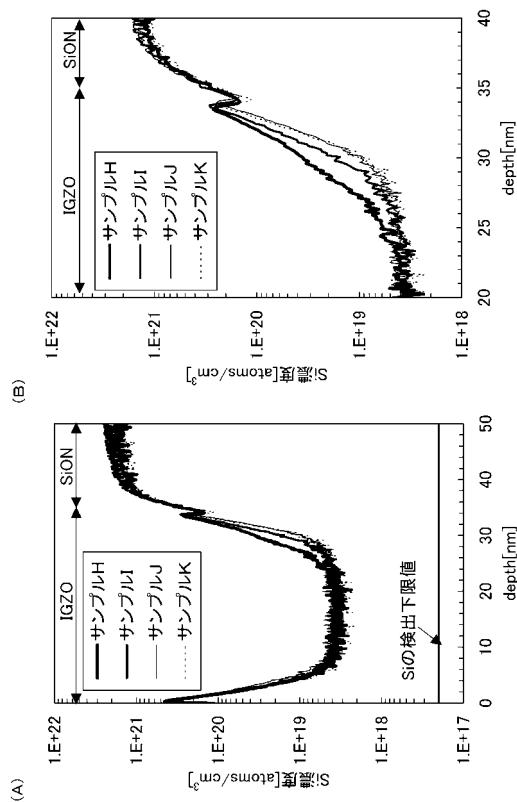

次に、サンプルH乃至サンプルKに対して、基板表面側(IGZO膜304側)からT o F - S I M S 測定を行い、酸化窒化シリコン膜との界面近傍におけるIGZO膜中のシリコン濃度を測定した。結果を図18に示す。なお、図18(B)は図18(A)の一部分を拡大した図である。

30

**【0278】**

図18より、全てのサンプルにおいて、酸化窒化シリコン膜界面近傍のIGZO膜中のシリコン濃度は、実施例1にて記載した $\text{In} - \text{Ga} - \text{Zn}$ 系酸化物ターゲット(原子数比が $\text{In : Ga : Zn} = 1 : 1 : 1$ )中に含まれるシリコン濃度である $2 \times 10^{18} \text{ atom s/cm}^3$ よりも高くなっていることが確認できる。したがって、酸化窒化シリコン膜界面近傍の酸化物半導体膜中にて測定されたシリコンは、 $\text{In} - \text{Ga} - \text{Zn}$ 系酸化物ターゲット起因のシリコンではないと言える。

40

**【0279】**

また、図18より、酸化窒化シリコン膜界面近傍におけるIGZO膜中のシリコン濃度は、成膜電力を弱くするに従い低下する傾向が確認された。したがって、酸化物半導体膜の成膜電力を弱くすることにより、ミキシングによって生じる酸化物半導体膜中への絶縁膜構成元素の混入を抑制できることが確認された。

**【0280】**

加えて、サンプルJとサンプルKのシリコン濃度が略一致していることより、成膜初期段階は弱い電力で酸化物半導体膜を成膜し、その後、成膜電力を高めて酸化物半導体膜を成膜しても、ミキシングによって生じる酸化物半導体膜中への絶縁膜構成元素の混入を抑制

50

できることが確認された。

**【実施例 4】**

**【0281】**

本実施例では、酸化物半導体膜中に絶縁膜構成元素が混入することにより生じる、酸化物半導体膜中における結晶状態について調査した結果についての説明を行う。

**【0282】**

まず、基板上に組成の異なるターゲットを用いて酸化物半導体膜を成膜した2枚の基板を準備し、各々の基板を三分割した。その後、三分割した基板に対して異なる条件で熱処理を行うことで、合計6枚の異なる条件のサンプルを作製した。そして各サンプルについて、酸化物半導体膜の結晶状態を、X線回折法(XRD:X-ray Diffraction)を用いて測定した。

10

**【0283】**

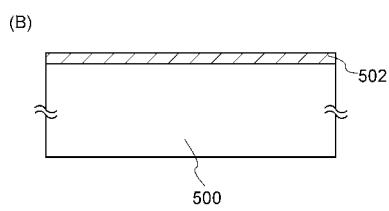

まず、XRD測定に用いたサンプルの構造を図19(A)に示す。

**【0284】**

図19(A)に示すサンプルは、ガラス基板400上にSiO<sub>2</sub>が添加されたIGZO(In:Ga:Zn=1:1:1[原子数比])ターゲットを用いてIGZO膜402を成膜した後に、熱処理を行ったものである。

**【0285】**

IGZO膜402は、スパッタリング装置を用いて成膜した。IGZO膜402の成膜条件は、基板温度：200、成膜電力：100W、成膜圧力：0.4Pa、ガス流量： $O_2 = 10 \text{ sccm}$ 、膜厚：100nmとした。なお、スパッタリングターゲットとしては、In:Ga:Zn=1:1:1[原子数比]に2wt%のSiO<sub>2</sub>を添加したターゲット、およびIn:Ga:Zn=1:1:1[原子数比]に5wt%のSiO<sub>2</sub>を添加したターゲットを用いた。なお、IGZO膜402を形成する前に、ガラス基板400表面を洗浄してパーティクル等を除去した。

20

**【0286】**

熱処理は、抵抗発熱体などを用いた電気炉に基板を導入して熱処理を行った。IGZO膜成膜後に三分割した基板の一枚は、650のN<sub>2</sub>雰囲気で1時間の熱処理を行った後、650のO<sub>2</sub>雰囲気で1時間の熱処理を行った。また、三分割した基板の一枚は、450のN<sub>2</sub>雰囲気で1時間の加熱を行った後、450のO<sub>2</sub>雰囲気で1時間の加熱を行った。また、三分割した基板の一枚は、熱処理を行っていない。

30

**【0287】**

上述の、使用ターゲットおよび加熱条件振りを行うことで、表1に示すサンプルL乃至サンプルQの6種類のサンプルを準備した。

**【0288】**

**【表1】**

| サンプル名 | 使用ターゲット                                | 加熱条件                                                              |

|-------|----------------------------------------|-------------------------------------------------------------------|

| L     | In:Ga:Zn=1:1:1+SiO <sub>2</sub> (2wt%) | 《650°C, N <sub>2</sub> 雰囲気, 1時間》+《650°C, O <sub>2</sub> 雰囲気, 1時間》 |

| M     | In:Ga:Zn=1:1:1+SiO <sub>2</sub> (2wt%) | 《450°C, N <sub>2</sub> 雰囲気, 1時間》+《450°C, O <sub>2</sub> 雰囲気, 1時間》 |

| N     | In:Ga:Zn=1:1:1+SiO <sub>2</sub> (2wt%) | 加熱処理なし                                                            |

| O     | In:Ga:Zn=1:1:1+SiO <sub>2</sub> (5wt%) | 《650°C, N <sub>2</sub> 雰囲気, 1時間》+《650°C, O <sub>2</sub> 雰囲気, 1時間》 |

| P     | In:Ga:Zn=1:1:1+SiO <sub>2</sub> (5wt%) | 《450°C, N <sub>2</sub> 雰囲気, 1時間》+《450°C, O <sub>2</sub> 雰囲気, 1時間》 |

| Q     | In:Ga:Zn=1:1:1+SiO <sub>2</sub> (5wt%) | 加熱処理なし                                                            |

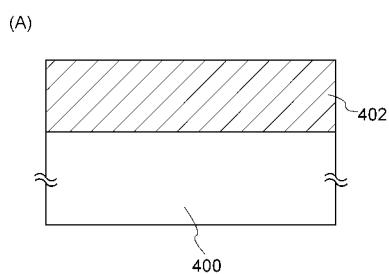

**【0289】**

次に、サンプルL乃至サンプルQのIGZO膜に対してXRD測定を行い、各々の膜の結晶状態を測定した。結果を図20(A)および図20(B)に示す。図20(A)は、サンプルL乃至サンプルNのXRD測定結果であり、図20(B)は、サンプルO乃至サン

40

プルQのXRD測定結果である。

【0290】

図20(A)より、上述の実施の形態に記載された温度範囲内の650の熱処理を行ったサンプルLにおいて、 $\theta = 31^\circ$ 近傍に結晶に起因するピークが見られた。これに対し図20(B)では、全てのサンプルで結晶に起因するピークが見られなかった。したがって、IGZO膜は、不純物として過剰なシリコンが含まれることにより、熱処理による結晶化が阻害されることが確認された。

【0291】

次に、2wt%のシリコンが添加されたターゲットを用いて成膜したIGZO膜に、どの程度のシリコンが含有されているかを調査するため、X線光電子分光法(XPS:X-ray photoelectron spectroscopy)を用いて、IGZO膜中に含まれる元素の組成を測定した。

【0292】

XPS測定に用いたサンプルは、図19(B)に示すように、シリコン基板500上にIGZO膜502を成膜した構造である。

【0293】

IGZO膜502は、スパッタリング装置を用いて成膜した。IGZO膜502の成膜条件は、基板温度：200、成膜電力：100W、成膜圧力：0.4Pa、ガス流量： $O_2 = 10\text{ sccm}$ 、膜厚：15nmとした。なお、スパッタリングターゲットとしては、In:Ga:Zn = 1:1:1[原子数比]に2wt%のSiO<sub>2</sub>を添加したターゲットを用いた。なお、IGZO膜502を形成する前に、希フ酸にてシリコン基板500表面に形成された酸化膜を除去した。

【0294】

XPS測定の結果、2wt%のシリコンが添加されたターゲットを用いて成膜したIGZO膜は、膜中に1.1atm%のシリコンが含有されていることが確認された。

【0295】

上述のように、ミキシングなどによって酸化物半導体膜のゲート絶縁膜との界面近傍にシリコンなどの不純物が混入すると、酸化物半導体膜のチャネル形成領域の結晶化が阻害されるおそれがあることがわかった。よって、酸化物半導体膜のゲート絶縁膜との界面近傍において、上記のようにシリコンの濃度を低減させることが重要であることが実施例によつて示された。

【符号の説明】

【0296】

100 基板

101 ゲート電極

102 ゲート絶縁膜

103 酸化物半導体膜

103a 領域

103b 領域

103c 領域

105a ソース電極

105b ドレイン電極

107 絶縁膜

108 チャネル保護膜

109 保護絶縁膜

110 トランジスタ

120 トランジスタ

130 トランジスタ

200 シリコン基板

202 酸化シリコン膜

10

20

30

40

50

|         |            |    |

|---------|------------|----|

| 2 0 4   | I G Z O 膜  |    |

| 3 0 0   | ガラス基板      |    |

| 3 0 2   | 酸化窒化シリコン膜  |    |

| 3 0 4   | I G Z O 膜  |    |

| 4 0 0   | ガラス基板      |    |

| 4 0 2   | I G Z O 膜  |    |

| 5 0 0   | シリコン基板     |    |

| 5 0 2   | I G Z O 膜  |    |

| 2 7 0 0 | 電子書籍       |    |

| 2 7 0 1 | 筐体         | 10 |

| 2 7 0 3 | 筐体         |    |

| 2 7 0 5 | 表示部        |    |

| 2 7 0 7 | 表示部        |    |

| 2 7 1 1 | 軸部         |    |

| 2 7 2 1 | 電源         |    |

| 2 7 2 3 | 操作キー       |    |

| 2 7 2 5 | スピーカー      |    |

| 2 8 0 0 | 筐体         |    |

| 2 8 0 1 | ボタン        |    |

| 2 8 0 2 | マイクロフォン    | 20 |

| 2 8 0 3 | 表示部        |    |

| 2 8 0 4 | スピーカー      |    |

| 2 8 0 5 | カメラ用レンズ    |    |

| 2 8 0 6 | 外部接続端子     |    |

| 3 0 0 1 | 本体         |    |

| 3 0 0 2 | 筐体         |    |

| 3 0 0 3 | 表示部        |    |

| 3 0 0 4 | キーボード      |    |

| 3 0 2 1 | 本体         |    |

| 3 0 2 2 | スタイルス      | 30 |

| 3 0 2 3 | 表示部        |    |

| 3 0 2 4 | 操作ボタン      |    |

| 3 0 2 5 | 外部インターフェイス |    |

| 3 0 5 1 | 本体         |    |

| 3 0 5 3 | 接眼部        |    |

| 3 0 5 4 | 操作スイッチ     |    |

| 3 0 5 6 | バッテリー      |    |

| 4 0 0 1 | 基板         |    |

| 4 0 0 2 | 画素部        |    |

| 4 0 0 3 | 信号線駆動回路    | 40 |

| 4 0 0 4 | 走査線駆動回路    |    |

| 4 0 0 5 | シール材       |    |

| 4 0 0 6 | 基板         |    |

| 4 0 0 8 | 液晶層        |    |

| 4 0 1 0 | トランジスタ     |    |

| 4 0 1 1 | トランジスタ     |    |

| 4 0 1 3 | 液晶素子       |    |

| 4 0 1 5 | 接続端子電極     |    |

| 4 0 1 6 | 端子電極       |    |

| 4 0 1 9 | 異方性導電膜     | 50 |

|           |          |    |

|-----------|----------|----|

| 4 0 2 1   | 絶縁層      |    |

| 4 0 3 0   | 電極層      |    |

| 4 0 3 1   | 電極層      |    |

| 4 0 3 2   | 絶縁膜      |    |

| 4 0 3 3   | 絶縁膜      |    |

| 4 0 3 4   | 絶縁膜      |    |

| 4 5 1 0   | 隔壁       |    |

| 4 5 1 1   | 電界発光層    |    |

| 4 5 1 3   | 発光素子     |    |

| 4 5 1 4   | 充填材      | 10 |

| 4 6 1 2   | キャビティ    |    |

| 4 6 1 3   | 球形粒子     |    |

| 4 6 1 4   | 充填材      |    |

| 4 6 1 5 a | 黒色領域     |    |

| 4 6 1 5 b | 白色領域     |    |

| 9 6 0 0   | テレビジョン装置 |    |

| 9 6 0 1   | 筐体       |    |

| 9 6 0 3   | 表示部      |    |

| 9 6 0 5   | スタンド     |    |

【図1】

(B)

【図2】

(B)

【図3】

【図4】

【図5】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図23】

【図25】

【図6】

【図7】

【図 8】

【図21】

(A)

In : Ga : Zn : O :

(B)

In : Ga : Zn : O : Si :

【図22】

(A)

|      |  |      |  |      |  |     |  |

|------|--|------|--|------|--|-----|--|

| In : |  | Ga : |  | Zn : |  | O : |  |

|------|--|------|--|------|--|-----|--|

(B)

|      |  |      |  |      |  |     |  |      |  |

|------|--|------|--|------|--|-----|--|------|--|

| In : |  | Ga : |  | Zn : |  | O : |  | Si : |  |

|------|--|------|--|------|--|-----|--|------|--|

【図24】

(A)

|    |  |    |  |    |  |     |  |     |  |

|----|--|----|--|----|--|-----|--|-----|--|

| In |  | Ga |  | Zn |  | O : |  | C : |  |

|----|--|----|--|----|--|-----|--|-----|--|

(B)

|    |  |    |  |    |  |     |  |     |  |

|----|--|----|--|----|--|-----|--|-----|--|

| In |  | Ga |  | Zn |  | O : |  | C : |  |

|----|--|----|--|----|--|-----|--|-----|--|

---

フロントページの続き

(72)発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 鈴木 聰一郎

(56)参考文献 特開2010-186994(JP,A)

特開2011-142315(JP,A)

特開2011-096884(JP,A)

特開2009-081413(JP,A)

特開2010-097212(JP,A)

特開2008-311342(JP,A)

特開2011-205017(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786

JSTPlus (JDreamIII)

WPI