## RÉPUBLIQUE FRANÇAISE

## INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

(1) N° de publication : (A n'utiliser que pour les commandes de reproduction). 2 480 501

**PARIS**

A1

## DEMANDE DE BREVET D'INVENTION

<sub>10</sub> N° 80 08270

- Dispositif semi-conducteur à grille profonde accessible par la surface et procédé de fabrication.

Classification internationale (Int. Cl. 3). H 01 L 29/40, 21/30 // 29/74, 31/06.

- - Déposant : Société dite : THOMSON-CSF, société anonyme, résidant en France.

- (72) Invention de : Jacques Arnould et Eugène Tonnel.

- (73) Titulaire : Idem (71)

- Mandataire : Thomson-CSF, Michel de Beaumont, SCPI, 173, bd Haussmann, 75360 Paris Cedex 08.

La présente invention concerne des structures semiconductrices à grille profonde localisée accessible par la surface et leur procédé de fabrication.

Dans divers types de composants semiconducteurs, 5 discrets ou intégrés, tels que des transistors bipolaires de grande puissance, des thyristors ouvrables par la gâchette, des transistors à effet de champ vertical de puissance à jonction et autres, on trouve une couche profonde localisée en forme de grille disposée à l'intérieur 10 de la plaquette semiconductrice dans un plan parallèle à celui des faces principales de gette plante.

De telles couches profondes sont couramment désignées dans la technique par l'appellation grilles enterrées en raison du procédé de fabrication classique

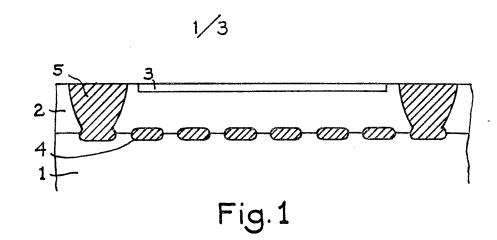

15 de l'art antérieur par lequel elles étaient obtenues. En effet, ce procédé consistait à partir d'un substrat semiconducteur, à y implanter des atomes dopants selon le type de conductivité correspondant à celui de la grille que l'on voulait obtenir, puis à former au-dessus de ce substrat une ou plusieurs couches épitaxiées dans lesquelles sont éventuellement formées une ou plusieurs diffusions. Une telle structure est représentée schématiquement dans la figure l ci-jointe. On peut y voir le substrat l surmonté d'une couche épitaxiée 2 dans laquelle ést formée

- 25 une zone diffusée 3. La couche ou grille enterrée 4 est présente à la limite entre le substrat 1 et la couche épitaxiée 2. Ensuite, un contact est assuré entre la surface supérieure de la plaquette semiconductrice et la grille enterrée 4 au moyen d'une diffusion profonde 5.

- 30 Dans de nombreuses applications pratiques, la grille 4 doit avoir un pas extrêmement fin et bien déterminé. En outre, cette grille sert couramment à l'ouverture du dispositif semiconducteur. Il est alors nécessaire que la résistivité transversale de la couche de grille soit la

- 35 plus faible possible. Son niveau de dopage doit donc

être très important. Le haut niveau de dopage rend difficile de maîtriser avec une grande précision l'étendue de la diffusion à partir de la couche initialement implantée pour que les mailles de la grille ne se ferment pas et 5 aient une épaisseur prédéterminée. Le contrôle de cette diffusion est très délicat à réaliser notamment du fait des autres étapes de diffusion thermique qui doivent être prévues pour la formation des autres couches élaborées sur le substrat. Des diffusions parasites du do-10 pant implanté peuvent également se produire lors de la formation de la couche épitaxiée.

Ces inconvénients sont d'autant plus notables que, dans de nombreux dispositifs, on a cherché à réaliser de façon pratique des dimensions de mailles de 15 grilles de l'ordre de quelques microns. D'autre part, du fait même de l'utilisation d'une couche épitaxiée déposée sur un substrat, il ne peut se développer entre les mailles de la grille, au niveau de l'interface entre la couche épitaxiée et le substrat, une charge d'espace né-20 cessaire aubon fonctionnement du dispositif.

Ainsi, un objet de la présente invention est de prévoir une nouvelle structure de dispositifs semiconducteurs à grille profonde qui pallie les inconvénients structurels ou de fabrication des dispositifs à grille enterrée 25 de l'art antérieur.

Un autre objet de la présente invention est de prévoir un nouveau procédé de fabrication de dispositif semiconducteur à grille profonde.

Pour atteindre ces objets ainsi que d'autres, 30 la présente invention prévoit une structure de dispositif semiconducteur à grille profonde ne comprenant pas de couche enterrée sous une couche épitaxiée selon la technique qui a été adoptée au cours de ces dernières années.

structure de dispositif semiconducteur, comprenant un corps semiconducteur comportant diverses couches de types de conductivité et/ou de niveaux de dopage distincts dont une première face comprend des rainures, 5 dans lequel les parois latérales des rainures sont revêtues d'un agent isolant sur au moins une partie de leur hauteur à partir de leur affleurement avec la première face, dans lequel le fond et la partie non isolée des parois latérales des rainures sont au 10 contact d'une couche profonde et sont éventuellement entourés d'une zone de type de conductivité et deniveau de dopage particuliers choisis et dans lequel les rainures sont remplies d'un matériau conducteur. La zone d'affleurement du matériau conducteur à la surface de la 15 rainure peut être recouverte d'une couche isolante à l'exception d'emplacements où l'on souhaite prendre un contact avec le matériau conducteur. On peut ainsi obtenir une structure dans laquelle une première électrode principale correspondant aux parties non rainurées de 20 la première face et l'électrode de grille sont au même niveau plan, ce qui permet une grande simplicité de réalisation de contact et de métallisation.

Dans un mode de réalisation particulier, le substrat semiconducteur à partir duquel est formé le 25 dispositif selon la présente invention est en silicium, l'agent isolant de la partie supérieure latérale des rainures est de la silice et le matériau conducteur permettant d'assurer le contact avec la zone profonde est du silicium polycristallin fortement dopé; ce 30 silicium polycristallin peut servir de source de diffusion pour doper le corps semiconducteur au voisinage du fond et de la partie latérale non isolée des rainures.

La présente invention est mise en œuvre simplement sur un substrat de silicium.

Dans ce cas, un procédé particulier de fabrication d'un dispositif selon la présente invention à partir 5 d'un corps de silicium comportant diverses couches de type de conductivité et/ou de niveau de dopage distincts comprend les étapes suivantes : revêtir la face supérieure d'une couche de nitrure de silicium ; ouvrir des fenêtres dans le nitrure de silicium et procéder à une 10 attaque anisotrope pour former des rainures en U selon ce quadrillage ; oxyder les parois des rainures ; enlever la couche d'oxyde au fond des rainures ; procéder éventuellement à une attaque anisotrope complémentaire pour approfondir les rainures ; remplir les rainures de 15 silicium polycristallin fortement dopé ; procéder à une étape thermique pour faire diffuser le dopant dans le substrat sous l'emplacement du sillon non protégé par la silice et oxyder, pour la transformer en silice, la surface supérieure de silicium polycristallin dans les 20 rainures ; enlever sélectivement la couche de nitrure de silicium ; ouvrir des fenêtres en des emplacements choisis sur la couche de silice pour faire apparaître des zones de contact sur le silicium polycristallin remplissant les rainures ; procéder au dépôt d'une 25 métallisation ; graver la métallisation pour séparer une électrode principale en contact avec la première face et une électrode en contact avec le silicium polycristallin, c'est-à-dire la grille.

L'étape d'enlèvement de la couche de silice au 30 fond des rainures en U peut être réalisée en attaquant par bombardement ionique, d'argon ou de bore par exemple, le fond des rainures et en attaquant sélectivement cette couche de silice ayant subi l'implantation par un produit d'attaque approprié, par exemple un mélange 35 d'acide fluorhydrique et de fluorure d'ammonium.

Ces objets, caractéristiques et avantages ainsi que d'autres de la présente invention seront exposés plus en détail dans la description suivante de modes de réalisation particuliers faite en relation avec les figures 5 jointes parmi lesquelles :

la figure l qui a été décrite précédemment était destinée à rappeler l'état de la technique ;

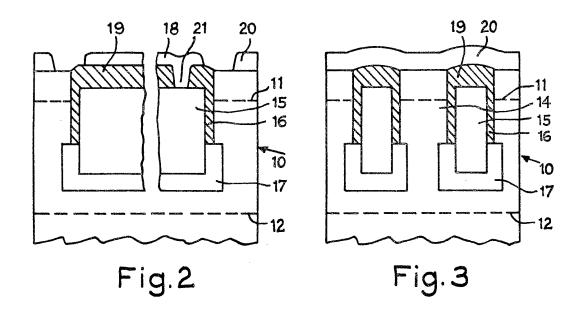

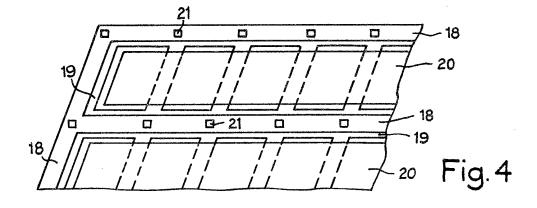

les figures 2 et 3 représentent des vues en coupe de modes de réalisation d'un dispositif à grille 10 profonde selon la présente invention prises selon des plans différents ; et la figure 4 en représente une vue de dessus ;

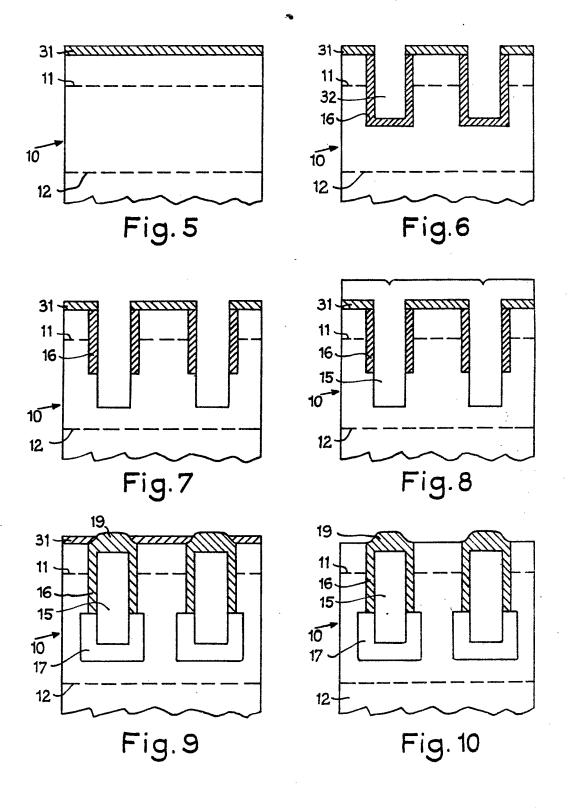

les figures 5 à 10 illustrent des étapes de fabrication d'un dispositif selon l'invention ; et

15 les figures 11 et 12 illustrent des applications de la présente invention.

Les figures 2 et 3 représentent des vues en coupe partielle longitudinale et transversale de modes de réalisation d'un dispositif selon la présente invention.

Ce dispositif comprend un corps semiconducteur comprenant par exemple des jonctions 11 et 12 entre des couches semiconductrices de type et/ou de niveau de dopage distincts. Des zones en saillie 14 sont délimitées par des rainures 15. La partie supérieure de la paroi latérale de ces rainures est revêtue d'une couche d'un matériau isolant 16; le fond des rainures ainsi que les parties des parois latérales non isolées par la couche 16 sont éventuellement entourés d'une zone 17 à niveau de dopage et de type de conductivité choisis. L'intérieur des sillons ou rainures est rempli d'un produit électriquement conducteur 15 assurant un contact ohmique avec les zones 17 ou un contact direct, ohmique ou non, avec le fond du sillon si les zones 17 n'existent pas 35 pour servir de couche de conduction électrique entre une

électrode 18 sur la face supérieure du corps semiconducteur et les couches ou zones en contact avec le fond du sillon. Une deuxième électrode 20 assure le contact électrique avec la partie non sillonnée de la face supérieure.

Dans un mode de réalisation particulier de la présente invention, la partie supérieure du produit conducteur 15 remplissant les rainures est isolée par une couche d'isolement 19 et seulement quelques fenêtres 21 sont prévues dans cette couche d'isolement 19 pour assurer le contact entre la métallisation 18 et le produit conducteur remplissant chaque rainure. Ceci permet de réaliser la couche métallique 20 de contact avec la face supérieure de façon continue en évitant de prévoir des ouvertures de cette couche de métallisation en regard de 15 chaque des rainures.

On peut ainsi obtenir une structure à grille profonde présentant par rapport aux structures à grille enterrée de l'art antérieur de nombreux avantages structurels résultant notamment du fait que : la zone diffusée 20 17 est nettement délimitée par la partie du sillon isolée latéralement 16; les contacts d'électrode principale sur la face supérieure et d'électrode de grille sont ramenés sur un même plan et leur réalisation peut être simplifiée; enfin et surtout comme cela sera exposé ci-après, en relation avec un exemple particulier, la structure selon la présente invention peut être fabriquée de façon simple tout en obtenant une miniaturisation extrême des diverses dimensions.

Dans le cas particulier où le substrat semicon30 ducteur 10 est un substrat de silicium, on choisira celuici selon une orientation (1,1,0). Les sillons 15 sont

formés dans le substrat par gravure anisotrope. Les gravures forment préférentiellement, comme le représente la

vue de dessus de la figure 4, des parallélogrammes d'angles

35 70° et 110°. Le matériau d'isolement 16 des rainures est

de préférence de la silice, le matériau conducteur 15 de remplissage de ces rainures est de préférence du silicium polycristallin dopé et la zone de grille 17 est de préférence une zone diffusée obtenue par diffusion dans le substrat d'atomes dopants initialement contenus dans le silicium polycristallin. Les métallisations 18 et 20 sont de préférence des métallisations d'aluminium. A titre d'exemple, on pourra réaliser un dispositif pratique à grille parallélépipèdique présentant les caractéristiques dimen-

- profondeur totale des sillons : 5 à 50 microns.

- distance entre sillons : 10 à 15

- largeur des sillons : 3 à 5

- largeur ou profondeur de la

15

couche 17 : 2 à 3

- longueur des sillons : 0,5 à 1 mm

Dans le cas où le dispositif aurait la configuration digitée représentée en vue de dessus en figure 6, le doigt de métallisation destiné à venir prendre un con-20 tact avec des ouvertures 21 en plusieurs points de la grille peut avoir une largeur de l'ordre de 30 à 50 microns.

Un procédé de fabrication d'une structure telle que representée en figures 2 à 4 réalisée sur substrat de silicium (1,1,0) va maintenant être décrit plus en détail 25 en relation avec les figures 5 à 10.

La figure 5 représente un corps de silicium 10 comportant des jonctions 11 et 12, sur la première face ou face supérieure duquel on a formé une couche de protection 31 en nitrure de silicium (Si<sub>3</sub>N<sub>4</sub>). Des ouvertures 30 sont formées en des emplacements choisis de la couche de nitrure de silicium, par exemple selon le quadrillage en parallélogrammes représenté en vue de dessus en figure 4. Ces ouvertures dans la couche de nitrure de silicium servent de masque d'attaque pour effectuer une gravure anissotrope de la plaquette et fournir les sillons en U 32

représentés dans la figure 6. Les crêtes des ouvertures sont alignées sur les directions (2,1,1) et les faces latérales sont constituées par des plans (1,1,1). Une étape d'échauffement thermique en atmosphère oxydante perfet d'oxyder les parois des rainures de façon à former une couche d'isolement 16 en silice (SiO<sub>2</sub>).

On procède ensuite à une implantation d'ions, d'argon ou de bore par exemple, selon une incidence normale à la surface de la plaquette de façon à réaliser 10 cette implantation dans la couche de silice se trouvant au fond des rainures 32. Il est alors possible d'attaquer sélectivement par un produit d'attaque de dosage approprié le fond des sillons qui a reçu l'implantation sans attaquer les parois de ces sillons ni la couche de ni15 trure à la surface de la plaquette.

Comme le représente schématiquement la figure 7, après cet enlèvement de la couche d'oxyde au fond des sillons, on procède éventuellement à une attaque anisotrope complémentaire pour approfondir ces sillons ou 20 rainures qui gardent toujours néanmoins leur forme en U. On obtient ainsi des sillons dont la partie supérieure est isolée par la couche de silice 16 et dont la partie la plus profonde pénètre sans couche intermédiaire dans le silicium du substrat. Si l'on n'a pas procédé à une 25 attaque complémentaire, seul le fond des sillons laisse apparaître le silicium du substrat. Le sillon est ensuite rempli de silicium polycristallin 8 dopé, par exemple de type P<sup>+</sup> (au bore) des techniques existant actuellement pour effectuer de tels dépôts à des températures relati-30 vement basses (inférieures à 600°C).

Comme le représente la figure 9. le silicium polycristallin en excès sur la face supérieure du dispositif est enlevé par un produit d'attaque approprié, par exemple par une attaque sous plasma, et l'on procède 35 à une étape d'échauffement pour fournir une couche de

silice 19 à la partie supérieure des rainures et également pour assurer la diffusion des atomes dopants contenus dans le silicium polycristallin 15 (par exemple du bore) vers le substrat pour former les zones 17. On no-5 tera néanmoins que pour certains dispositifs il n'est pas nécessaire de former les zones 17.

Lors de l'étape illustrée en figure 10 on enlève la couche de nitrure de silicium 31. Après quoi l'on procède à des ouvertures de contact dans la couche de 10 silice 19 puis à une métallisation, par exemple d'aluminium, des faces supérieures et inférieures du dispositif. La couche d'aluminium sur la face supérieure est gravée pour séparer l'électrode principale de l'électrode de grille en contact avec le silicium polycristal-15 lin 15 en les emplacements définis par les fenêtres ouvertes dans la couche d'oxyde 19. On obtient ainsi un dispositif selon l'invention tel que représenté dans les figures 2 à 4.

Selon l'un des avantages de la présente inven20 tion, l'étape de formation de la couche de grille proprement dite 17 est l'une des dernières étapes du procédé de fabrication et n'est suivie d'aucune autre étape

de diffusion, c'est-à-dire d'échauffement important.

Ainsi, la profondeur ou épaisseur de la zone 17 à partir

25 du sillon peut être contrôlée avec une grande précision.

On évite les phénomènes d'exo-diffusion qui rendent si

difficile technologiquement la réalisation de structures

à grille enterrée à pas très fin du type de celle illustrée en figure 1.

Bien entendu, le procédé de fabrication selon la présente invention est susceptible de nombreuses variantes, par exemple en ce qui concerne l'attaque du fond de la couche d'oxyde dans les sillons illustrée en figure 6 et le procédé de formation de la couche 17.

35 Celle-ci pourrait être formée à partir d'un dopant implanté ou diffusé à partir de la structure se trouvant

dans l'état de la figure 7, le silicium polycristallin 15 de remplissage des sillons étant disposé ultérieurement. Ceci permet un contrôle indépendant de la diffusion de la proction P et de la conductivité transversale 5 de la grille par le remplissage du silicium polycristallin de type P + 15. Selon une variante de la présente invention, le matériau conducteur remplissant les sillons, au lieu d'être du silicium polycristallin, peutêtre un composé de silicium et d'un métal réfractaire 10 tel que du platine, du tungstène ou du molybdène, ce qui permet de disposer d'un matériau conducteur de plus faible résistivité que le silicium polycristallin. Dans le cas où l'on utilise un tel composé de silicium et de métal réfractaire, on réalisera, dans le cas où il con-15 vient de prévoir des couches 17, une implantation préalable de ces couches. On notera qu'un avantage d'un composé silicium + métal réfractaire est qu'il peut s'oxyder en surface comme le silicium polycristallin. Il tend alors d'ailleurs, lors d'une étape d'oxydation, à se 20 produire une séparation entre le silicium et le métal réfractaire, le silicium transformé en silice apparaissant à la périphérie dans les zones oxydées, ce qui améliore encore la résistivité. On notera également que la présente invention, même dans le cas d'un substrat de 25 silicium, ne se limite pas à la formation de sillons par attaque anisotrope. Des techniques sont maintenant connues pour former des sillons profonds et de très faibles largeurs par gravure ionique. En fonction de considérations techniques et économiques on pourra préférer ce mode de 30 réalisation des sillons ou tout autre mode connu.

EXEMPLES D'APPLICATIONS DE LA PRESENTE INVENTION

- fabrication de transistors de grande puissance

à grille de base enterrée.

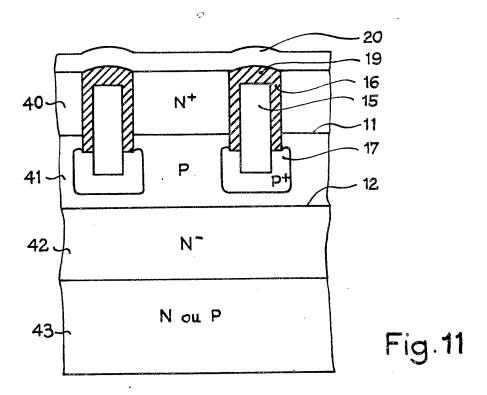

Comme le montre la figure 11, ces transistors 35 comprennent un émetteur 40 de type  $\operatorname{N}^+$  sur une base 41 de

type P et sur un collecteur constitué d'une couche 42 de type N- puis d'une couche superficielle 43 de type N<sup>+</sup>. On cherche alors à réaliser une grille de base à haut niveau de dopage P<sup>+</sup> à l'intérieur de la base de type P 5 ou à prendre un contact direct avec divers emplacements de la couche de base. Les sillons selon la présente invention sont alors formés pour que leur fond débouche dans la couche de base 41 de type P. On peut réaliser simplement des contacts de base multiples en ne prévo10 yant pas de zones diffusées de type P<sup>+</sup> 17 ou bien former effectivement une grille profonde à haut niveau de dopage en formant des zones diffusées 17.

- fabrication de thyristors ouvrables par la gâchette.

- 15 Ces thyristors ont une structure analogue à celle des transistors représentés en figure 11 sauf que la couche 43 est alors une couche de type P et non plus une couche de type N.

- fabrication de transistors à effet de champ 20 de type vertical à jonction.

Ces structures comprennent un substrat de type N à l'intérieur duquel on forme une grille de type  $P^+$ .

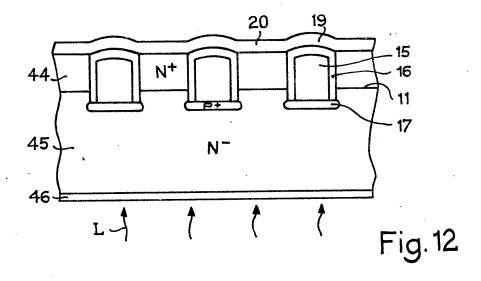

- fabrication de cellules solaires multijonctions horizontales (figure 12).

- 25 Cette cellule ou ensemble de diodes comprend une couche 44 de type N<sup>+</sup> sur un substrat 45 de type N-. La face inférieure du substrat est revêtue d'une couche anti-reflets 46 qui reçoit un faisceau lumineux incident concentré L. Dans cette application, les sillons sont

- 30 formés en une seule fois et traversent la couche de type  $N^+$  44 pour pénétrer dans la couche de type  $N^-$  45. Le fond des sillons repose sur une couche de type  $P^+$ 17 formée par exemple, comme cela a été exposé précédemment à partir de silicium polycristallin 15 dopé de type  $P^+$  et

- 35 remplissant les sillons. On peut également prévoir, comme cela a été indiqué à titre de variante de l'invention que

les zones 17 de type P soient formées par implantation au fond des sillons avant le remplissage de ceux-ci par un matériau conducteur 15. Par rapport à une structure MJH (multijonctions horizontales) classique, la structure 5 selon la présente invention présente d'une part l'avantage d'une plus grande compacité, étant donné que, dans une structure classique, les zones N<sup>+</sup> et P<sup>+</sup> adjacentes doivent être séparées par une zone à faible niveau de dopage qui correspond à de la place perdue. D'autre 10 part, la formation de la façon exposée précédemment de la couche isolante 19 à la limite entre le matériau conducteur 15 remplissant les sillons et la métallisation 20 recouvrant la diode permet de prendre une métallisation de grande dimension en contact avec toutes les zones N+ 15 et pouvant être montée sur un radiateur, les contacts avec les sillons pouvant être pris sur un bord ou à la périphérie de la cellule solaire.

- Bien entendu la présente demande est susceptible d'autres applications, et notamment le mot grille 20 tel qu'il est employé dans la présente description et dans les revendications ci-après doit se comprendre de façon générale comme désignant éventuellement une zone limitée profonde dans un corps semiconducteur ayant une forme autre qu'un quadrillage, par exemple un anneau ou même 25 un ensemble de zones disjointes.

En effet, en ce qui concerne cette dernière application et les précédentes, on notera qu'un avantage de la présente invention réside dans le fait que le procédé exposé permet d'atteindre une couche profonde en formant un sillon occupant une surface minimale sur la plaquette semiconductrice alors que la prise de contact avec une couche profonde réalisée par une diffusion descendante telle que désignée par la référence 5 en figure 1 occupe une surface nettement plus importante sur la plaquette semiconductrice. D'autre part, quand on procède par dif-

fusion descendante, il faut veiller à la disposition des couches pour que cette diffusion descendante ne provoque pas de courts-circuits ou de jonctions parasites entre couches distinctes. Au contraire, en utilisant le procédé selon la présente invention, du fait que les sillons sont isolés sur au moins une partie de leur surface latérale, on évite tout risque de court-circuit avec les couches rencontrées entre la couche profonde et la surface de la plaquette semiconductrice; il en résulte une simplification d'ensemble de la conception de certains dispositifs semiconducteurs.

En revenant sur les figures, il convient de souligner que, conformément à l'usage dans le domaine de la représentation des semiconducteurs, les diverses dimen-15 sions des couches et structures ne sont pas représentées à l'échelle, ni d'une figure à l'autre ni à l'intérieur d'une même figure. D'autre part, en ce qui concerne les figures 2 à 4, ces figures ne correspondent pas à des vues selon des plans différents d'un même mode de réali-20 sation. Si l'on part de la figure 4, qui représente une structure à quadrillage de rainures, la figure 3 pourrait correspondre à une vue en coupe perpendiculairement à la grande longueur des sillons sous l'électrode 20, et la figure 4 montre, à titre d'exemple, comment pourraient 25 être disposées les fenêtres 21 permettant un accès à la grille avec des électrodes principales (20) et de grille (18) digitées. Par contre la figure 2 représente une vue en coupe longitudinale d'un sillon unique n'appartenant pas à un quadrillage et la métallisation de grille 18 et 30 la fenêtre 21 de cette figure 2 ne correspondent pas au mode de réalisation de la figure 4.

La présente invention n'est pas limitée aux modes de réalisation qui ont été explicitement décrits cidessus; elle en inclut les diverses variantes et généra-lisations comprises dans le domaine des revendications ci-après.

## REVENDICATIONS

- 1. Dispositif semiconducteur comprenant un corps semiconducteur comportant diverses couches de type de conductivité et/ou de niveaux de dopage distincts dont une première face comprend des rainures, caractérisé en 5 ce que les parois latérales des rainures sont revêtues d'un agent isolant sur au moins une partie de leur hauteur à partir de leur affleurement avec la première face, et en ce que ces rainures sont remplies d'un matériau conducteur.

- 2. Dispositif selon la revendication 1, caractérisé en ce que le fond et la partie non isolée des parois latérales des rainures sont entourés d'une zone de type de conductivité et de niveau de dopage choisis.

- 3. Dispositif à effet de champ selon l'une des 15 revendications 1 ou 2, caractérisé en ce que l'affleurement du matériau conducteur à la surface de la rainure est recouvert d'une couche isolante à l'exception d'emplacements où l'on souhaite prendre un contact avec ce matériau conducteur.

- 4. Dispositif selon l'une quelconque des revendications l à 3, caractérisé en ce que le substrat semiconducteur est un substrat de silicium, l'agent isolant de la silice, et le matériau conducteur du silicium polycristallin fortement dopé.

- 5. Dispositif selon les revendications 3 et 4, caractérisé en ce qu'il comprend à sa surface supérieure des métallisations principales et des grilles interdigitées, la métallisation principale recouvrant notamment des portions de la couche isolante énoncée en re30 vendication 3 et la métallisation de grille venant en contact avec les emplacements où cette couche isolante est enlevée.

- 6. Procédé de fabrication d'un dispositif selon

la revendication 4, fabriqué à partir d'un substrat de silicium d'orientation (1,1,0), caractérisé en ce qu'il comprend l'étape consistant à former des sillons par gravure anisotrope en U.

- 7. Procédé de fabrication selon la revendication 6, pour former des sillons dont la partie la moins profonde est latéralement isolée et la partie la plus profonde entre directement dans le substrat, caractérisé en ce qu'il comprend les étapes suivantes :

- prévoir deux produits de protection sensibles à des produits d'attaque distincts ;

recouvrir le substrat d'une couche du premier

produit de protection ;

former une rainure d'une première profondeur ; 15 revêtir les parois de la rainure d'une couche du produit de protection de deuxième type ; et

approfondir la rainure.

30

8. Procédé selon la revendication 7, dans lequel le substrat est un substrat de silicium recouvert d'une 20 couche de nitrure de silicium, caractérisé en ce qu'il comprend les étapes suivantes :

ouvrir la couche de nitrure de silicium aux endroits où on souhaite effectuer les sillons ;

former ces sillons selon une première profon25 deur par attaque chimique d'une durée déterminée ;

procéder à une étape d'oxydation pour oxyder

les parois et le fond du sillon ;

bombarder ioniquement le fond des sillons pour le rendre sélectivement sensible à une attaque chimique; enlever par attaque chimique la silice bombardée déposée au fond des sillons;

approfondir les sillons d'une valeur supérieure ou égale à 0 par une deuxième attaque chimique.

9. Procédé de fabrication selon l'une des reven-35 dications 7 ou 8, caractérisé en ce qu'il comprend en outre l'étape consistant à remplir les sillons de silicium polycristallin fortement dopé.

- 10. Procédé selon la revendication 9, caractérisé en ce qu'il comprend l'étape consistant à procéder 5 à une étape d'échauffement pour faire diffuser des atomes dopants contenu dans le silicium polycristallin dans le substrat au voisinage du fond des sillons et de la partie des parois latérales la plus proche du fond.

- 11. Procédé selon l'une des revendications 9 ou 10 10, caractérisé en ce que la surface supérieure du silicium polycristallin contenu dans les rainures est recouverte d'une couche isolante de silice.

- 12. Procédé selon la revendication 11 dans lequel des électrodes métalliques sont formées sur la pre15 mière face du dispositif, caractérisé en ce qu'il comprend les étapes suivantes :

ouvrir en certains emplacements de la couche de silice selon la revendication 11 des fenêtres permettant un accès vers la zone de silicium polycris-20 tallin;

déposer uniformément une couche de métallisation telle que de l'aluminium sur la première face du dispositif;

graver cette couche selon une structure

25 digitée pour séparer une électrode de grille passant

sur lesdites fenêtres et une électrode principale recouvrant la plus grande partie de la première face audessus desdites couches de silice et de la zone surdopée de cette face supérieure.