(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7586972号

(P7586972)

(45)発行日 令和6年11月19日(2024.11.19)

(24)登録日 令和6年11月11日(2024.11.11)

(51)国際特許分類

H 01 L 23/12 (2006.01)

H 01 L 23/14 (2006.01)

F I

H 01 L 23/12

H 01 L 23/14F

M

請求項の数 21 (全12頁)

|                   |                                                              |          |                                                                                                                   |

|-------------------|--------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2023-113367(P2023-113367)                                  | (73)特許権者 | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>- 5474 ダラス メイル ステイション<br>3999 ピーオーボックス 655474 |

| (22)出願日           | 令和5年7月10日(2023.7.10)                                         | (74)代理人  | 230129078<br>弁護士 佐藤 仁                                                                                             |

| (62)分割の表示         | 特願2021-500044(P2021-500044<br>の分割<br>原出願日 令和1年7月2日(2019.7.2) | (72)発明者  | ナジラ ダドバンド<br>アメリカ合衆国 75081 テキサス州<br>リチャードソン, イー バッキンガム<br>ロード 826-430                                             |

| (65)公開番号          | 特開2023-126980(P2023-126980<br>A)                             | (72)発明者  | クリストファー ダニエル マナック<br>アメリカ合衆国 75022 テキサス州<br>フラー マウンド, サン メドウ ドラ<br>最終頁に続く                                         |

| (43)公開日           | 令和5年9月12日(2023.9.12)                                         |          |                                                                                                                   |

| 審査請求日             | 令和5年7月31日(2023.7.31)                                         |          |                                                                                                                   |

| (31)優先権主張番号       | 16/026,371                                                   |          |                                                                                                                   |

| (32)優先日           | 平成30年7月3日(2018.7.3)                                          |          |                                                                                                                   |

| (33)優先権主張国・地域又は機関 | 米国(US)                                                       |          |                                                                                                                   |

(54)【発明の名称】 電気めつきされたダイ取り付けを備える半導体デバイス

## (57)【特許請求の範囲】

## 【請求項1】

パッケージ化半導体装置をつくる方法であって、

中央開口部と前記中央開口部の周りの複数の隆起トレースとを有する金属基板を提供することであって、前記隆起トレースが誘電体ベース層と前記誘電体ベース層上の金属層とを含む、前記金属基板を提供することと、

裏側金属(BSM)層を有する半導体ダイを頂部側を上にして前記中央開口部の頂部部分上に搭載することと、

前記中央開口部の底部を充填するダイ取り付けを提供するために前記BSM層と前記中央開口部の境界を区切る前記金属基板の壁との間に直接的に単一金属層を形成することと、

前記複数の隆起トレースの金属層に接するリードを形成することであって、前記リードが少なくとも1つの屈曲部と前記金属基板を超えて延在する末端部とを含む、前記リードを形成することと、

前記複数の隆起トレースと前記半導体ダイ上のボンドパッドとの間にボンドワイヤを取り付けることと、

を含む、方法。

## 【請求項2】

請求項1に記載の方法であって、

前記誘電体ベース層がポリイミドを含む、方法。

## 【請求項3】

請求項 1 に記載の方法であって、

前記金属基板と前記単一金属層とがすべて銅を含む、方法。

【請求項 4】

請求項 1 に記載の方法であって、

前記単一金属層が 20  $\mu\text{m}$  から 100  $\mu\text{m}$  の厚さである、方法。

【請求項 5】

請求項 1 に記載の方法であって、

前記金属基板が 0.1  $\text{mm}$  から 0.3  $\text{mm}$  の厚さである、方法。

【請求項 6】

請求項 1 に記載の方法であって、

前記単一金属層が電気めっきされた金属層である、方法。

10

【請求項 7】

パッケージ化半導体装置をつくる方法であって、

中央開口部と前記中央開口部の周りの複数の隆起トレースとを有する銅含有基板を提供することであって、前記隆起トレースが誘電体ベース層と前記誘電体ベース層上の金属層とを含む、前記銅含有基板を提供することと、

頂部側を上にして裏側金属（BSM）層を有する半導体ダイを前記中央開口部の頂部部分に搭載することと、

前記中央開口部の底部を充填するダイ取り付けを提供するために前記 BSM 層と前記中央開口部の境界を区切る前記銅含有基板の壁との間に直接的に単一銅層を形成することと、

前記複数の隆起トレースの金属層に接するリードを形成することであって、前記リードが少なくとも 1 つの屈曲部と前記銅含有基板を超えて延在する末端部とを含む、前記リードを形成することと、

前記複数の隆起トレースと前記半導体ダイ上のボンドパッドとの間にボンドワイヤを取り付けることと、

前記半導体ダイをモールド化合物で覆うことと、

を含む、方法。

【請求項 8】

請求項 7 に記載の方法であって、

前記単一銅層が 20  $\mu\text{m}$  から 100  $\mu\text{m}$  の厚さである、方法。

20

【請求項 9】

半導体ダイ取り付けの方法であって、

凹部を有する誘電体カバーと中央スルーホール開口部と前記中央スルーホール開口部の周りの複数の隆起トレースとを含む金属基板とを提供することであって、前記中央スルーホール開口部が前記誘電体カバーの凹部と調和する位置の外側リングを有し、前記隆起トレースが前記金属基板上の誘電体ベース層と前記誘電体ベース層上の金属層とを含む、前記誘電体カバーと金属基板とを提供することと、

前記外側リング上に載るように頂部側を上にして半導体ダイを前記中央スルーホール開口部に挿入することであって、前記半導体ダイが裏側金属（BSM）層を有する、前記半導体ダイを挿入することと、

スタックを形成するために前記誘電体カバーを前記半導体ダイの上に置くことと、

前記誘電体カバーと前記金属基板との間の周辺に沿って密封することと、

溶液容器内の金属電気めっき溶液に前記スタックを浸漬することであって、前記金属基板が電源の負側端子に接続され、前記金属基板から間隔を開けられた電気的導電性構造が前記電源の正側端子に接続される、前記スタックを浸漬することと、

ダイ取り付けを提供するために前記 BSM 層と前記中央スルーホール開口部の境界を区切る前記金属基板の壁との間の容積を充填するように電気めっきされる単一金属層を堆積するように電気めっきすることと、

を含む、方法。

【請求項 10】

40

50

請求項 9 に記載の方法であって、

前記金属電気めっき溶液が銅電気めっき溶液を含む、方法。

【請求項 11】

請求項 9 に記載の方法であって、

前記誘電体ベース層がポリイミドを含む、方法。

【請求項 12】

請求項 9 に記載の方法であって、

前記金属基板と前記単一金属層の全てが銅を含む、方法。

【請求項 13】

請求項 9 に記載の方法であって、

前記金属基板が複数の金属基板を含む基板シートの一部であり、

前記方法が、

前記複数の隆起トレースと前記半導体ダイ上のボンドパッドとの間にボンドワイヤを置くことと、

前記置くことの後に、第 1 のパッケージ化半導体装置前駆体を含む複数のパッケージ化半導体装置前駆体を形成するために前記基板シートを個片化することと、

前記複数の隆起トレースの金属層に接するリードを付加することであって、前記リードが少なくとも 1 つの屈曲部と前記金属基板を超えて延在する末端部とを含む、前記リードを付加することと、

第 1 のパッケージ化半導体装置を形成するために封止を付加するモールド化合物を形成するようにモールドすることと、

を更に含む、方法。

【請求項 14】

請求項 9 に記載の方法であって、

前記電気めっきされた単一金属層が 20  $\mu\text{m}$  から 100  $\mu\text{m}$  の厚さである、方法。

【請求項 15】

請求項 9 に記載の方法であって、

前記誘電体カバーがプラスチックを含む、方法。

【請求項 16】

請求項 9 に記載の方法であって、

前記電気めっきすることが、15 から 30 の温度で実行される、方法。

【請求項 17】

請求項 9 に記載の方法であって、

前記密封することが、前記誘電体カバーと前記金属基板との間の周辺に沿ってテープを置くことを含む、方法。

【請求項 18】

請求項 9 に記載の方法であって、

前記電気めっきすることが直流電気めっきすることを含む、方法。

【請求項 19】

請求項 9 に記載の方法であって、

前記電気めっきすることがパルス状に電気めっきすることを含む、方法。

【請求項 20】

半導体ダイ取り付けの方法であって、

凹部の第 1 の繰り返しパターンを有する誘電体カバーと前記第 1 の繰り返しパターンに調和する位置を有する第 2 の繰り返しパターンを有する金属基板とを提供することであって、前記第 2 の繰り返しパターンが前記凹部に調和する位置の外側リングを有する中央スルーホール開口部と前記中央スルーホール開口部の周りの複数の隆起トレースとを含み、前記隆起トレースが前記金属基板上の誘電体ベース層と前記誘電体ベース層上の金属層とを含む、前記誘電体カバーと金属基板とを提供することと、

前記外側リング上に載るように頂部側を上にして裏側金属 (BSM) 層を有する半導体

10

20

30

40

50

ダイを前記複数の中央スルーホール開口部のそれぞれの開口部に挿入することと、複数のスタッカートを形成するために前記半導体ダイの上に前記誘電体カバーを置くことと、ダイ取り付けを提供するために前記B S M層と前記中央スルーホール開口部の境界を区切る前記金属基板の壁との間の容積を充填するように電気めっきされる単一金属層を堆積するように電気めっきすることと、

を含む、方法。

【請求項 2 1】

半導体ダイ取り付けの方法であって、

外側リングを有する複数のスルーホール開口部と前記スルーホール開口部の周りの複数の隆起トレースとを有する金属基板を提供することであって、前記隆起トレースが前記金属基板上の誘電体ベース層と前記誘電体ベース層上の金属層とを含む、前記金属基板を提供することと、

前記外側リング上に載るように頂部側を上にして裏側金属（B S M）層を有する半導体ダイを前記複数のスルーホール開口部のそれぞれの開口部に挿入することと、

ダイ取り付けを提供するために前記B S M層と前記スルーホール開口部の境界を区切る前記金属基板の壁との間の容積を充填するように電気メッキされる単一金属層を堆積するように電気めっきすることと、

を含む、方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本記載は、半導体デバイスアッセンブリに関し、より具体的には、基板へのダイ取り付けに関する。

【背景技術】

【0 0 0 2】

パッケージ化された半導体デバイスは、ダイ取り付け接着材を用いてリードフレームなどのワークピースのダイパッド上に取り付けられる、シリコンダイなどの集積回路（I C）ダイを含み得る。他のワークピースとしては、インターポーラ、印刷回路基板（P C B）、及び他のI Cダイが挙げられる。頂部（アクティブ）側を上に逆側を下にアセンブルされたI Cダイの場合、ダイ取り付け接着材は、機械的取り付けを提供し、ダイパッドに電気的及び/又は熱的経路も提供し得る。ダイ取り付け接着材は、ポリイミド又はエポキシベースの接着材などのポリマーを含み得る。ポリマー材料の電気伝導率及び熱伝導率の両方を上げるための充填材として、銀が粒子薄片形態で付加され得る。

【発明の概要】

【0 0 0 3】

本概要は、記載される概念から一部選択したものを、提供される図面を含み詳細な説明において以下にさらに記載される簡略化された形態で紹介するために提供される。本概要是、特許請求される主題の範囲を限定しない。

【0 0 0 4】

記載される態様は、金属粒子充填ポリマーを含む幾つかのダイ取り付け解決策が、有意な熱及び電気抵抗性を有することを認識する。より小さな特徴を有し、より高い動作電流で動く、よりコンパクトでより高度に集積された電子機器システムを求める傾向と共に、熱管理がますます重要視されるようになってきているので、裏側電気コントラクトが用いられるときにも低い電気抵抗を提供する、より高い熱伝導率のダイ取り付け配置が必要とされる。共晶金錫（A u S n）などのはんだダイ取り付けは、金属充填ポリマーと比較して比較的良好な熱及び電気抵抗で裏側電気的コントラクトを提供することができるが、はんだダイ取り付けは、比較的高価であり、はんだ付け可能なダイ表面に限定され、また、はんだダイ取り付けプロセスは、半導体ダイの金属相互接続に温度誘起応力を生じさせ得る温度での不活性リフローに関与することが認識されている。

【0 0 0 5】

10

20

30

40

50

記載されるパッケージ化された半導体デバイスは、外側リングを含む中央アーチャを有する金属基板を含み、中央アーチャの周りの複数の隆起したトレースが誘電体ベース層上の金属層を含む。裏側金属（BSM）層を有する半導体ダイが、頂部側を上にして中央アーチャの頂部上に取り付けられる。単一の金属層が、BSM層と、中央アーチャを区切る基板壁との間に直接にあり、アーチャの底部部分を充填するダイ取り付けを提供する。金属層に接する少なくとも1つの屈曲部を備えるリードが、複数のトレース上にあり、金属基板を越えて延在する末端部（distal end）を含む。トレースと半導体ダイ上のボンドパッドとの間にボンドワイヤがある。モールド化合物が封止を提供する。

【0006】

10

ここで、必ずしも一定の縮尺で描かれていない添付の図面を参照する。

【図面の簡単な説明】

【0007】

【図1A】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

【図1B】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

20

【図1C】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

【図1D】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

【図1E】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

30

【図1F】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

【図1G】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

40

【図1H】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

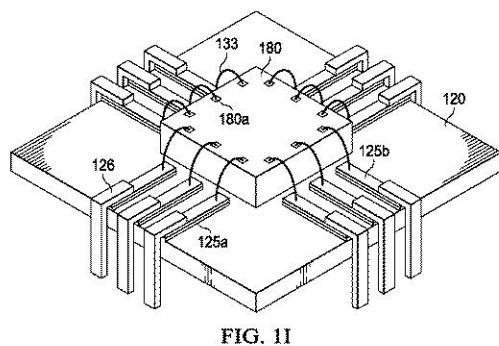

【図1I】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられたBSM層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

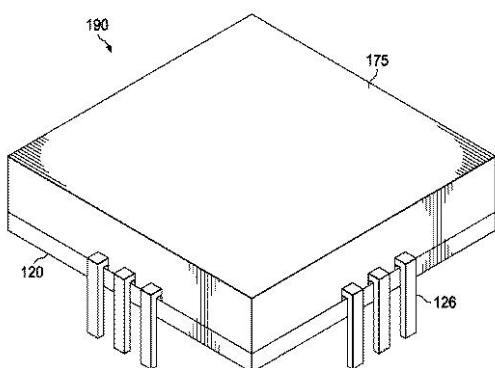

【図1J】例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板

50

上に直接取り付けられた BSM 層を備える半導体ダイを有する、開示されたパッケージ化された半導体デバイスを形成するためのアッセンブリプロセスのための、利用される構成要素及びアッセンブリプロセス進行プロセスを示す。

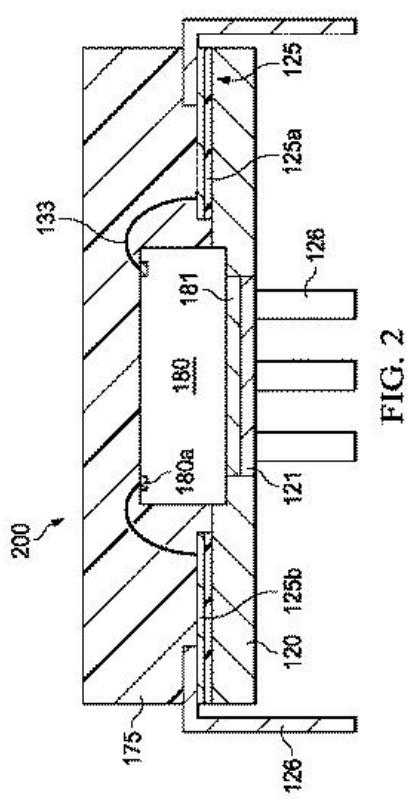

【0008】

【図2】例示の態様に従った、90度の屈曲部を備えるリードを有する、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられた BSM 層を備える半導体ダイを有する、例示のパッケージ化された半導体デバイスの断面図である。

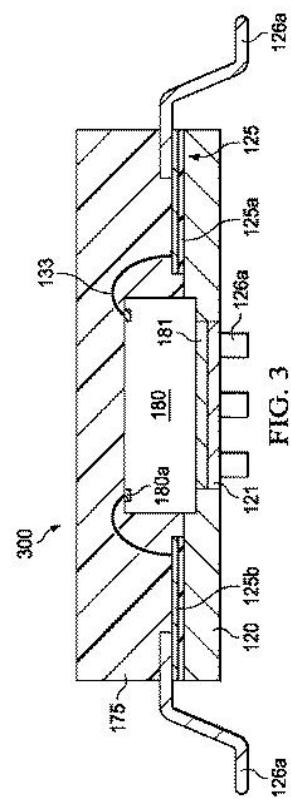

【0009】

【図3】例示の態様に従った、90度の屈曲部ではないリード屈曲部の例としてガルウィングリードを有する、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けた BSM 層を備える半導体ダイを有する、例示のパッケージ半導体デバイスの断面図である。

10

【発明を実施するための形態】

【0010】

例示の実施例が図面に関連して記載され、図面において、同様の参照数字は類似又は同等の要素を示すために用いられる。幾つかの行為又は事象は別の順序で及び／又は他の行為又は事象と同時に起こり得るので、行為又は事象の例示される順序は限定するものと見なされるべきではない。また、幾つかの例示される動作又は事象は、本記載による手法を実装するために必要とされないこともある。

20

【0011】

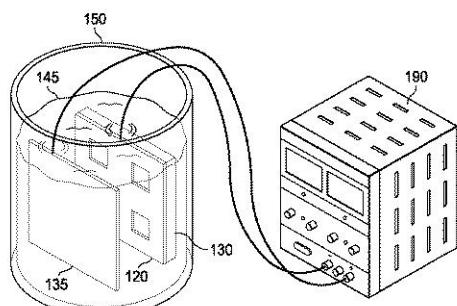

図1A～図1Iは、例示の態様に従った、電気めっきされた金属ダイ取り付け層によって金属基板上に直接取り付けられた裏側金属めっき半導体ダイを有する記載されるパッケージ化された半導体デバイスを形成するための、利用される構成要素及びアッセンブリプロセス進行を示す。図1Aは、中にダイを有する金属基板120上の誘電体カバー130を含む記載されるスタックを、電気めっき槽を提供するめっき容器150内に浸漬することを示す。これらの構成要素は、一つ又はそれ以上の溶解した金属塩、並びに、電気の流れを可能にする他のイオンを含む、電解質と呼ばれる溶液に浸漬される。

【0012】

カバー130は、金属基板120の頂部を覆う誘電体（例えば、プラスチック）材料を含む。金属基板120は、複数のダイ位置を有する基板シート／パネルの形態であり、金属基板120におけるアーチャ内で矩形のダイ位置に頂部側を上に置かれるダイ（図示せず）を備える例によって4つが示される。基板シート／パネルは、約50～1,000個のダイ位置を有し得る。めっき容器150内にはめっき溶液145がある。また、半導体ダイの頂部側へのめっき金属を回避するために、誘電体カバー130と金属基板120との間に電気めっき溶液耐性テープなどの封止がある。電気めっきのために、金属基板120は、電力供給190の負の端子（カソード）に接続され、金属基板120から離間して配置される図1Aにおいてアノード135として示される金属ブロックなど、金属基板120から離間された導電性構造が、電力供給190の正の端子（アノード）に接続される。電気めっきは、温度誘起応力の、半導体ダイ相互接続への導入などを回避するために、15～30の温度で行われ得る。カソードにおいて、電解質溶液中の溶解した金属イオン（例えば、Cu+2）は、溶液とカソードとの間の界面において還元されて、そのため、それらは、めっきされてカソード上のゼロ原子価状態金属（例えば、Cu金属）になる。電気めっきは直流（DC）を用いて行うことができるが、パルス電気めっきとして行われてもよい。

30

【0013】

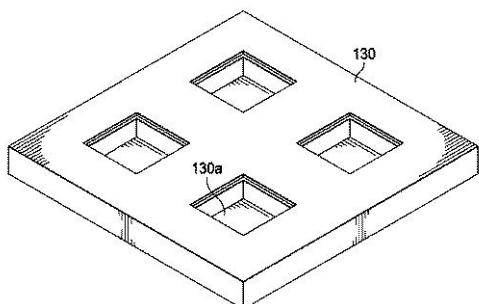

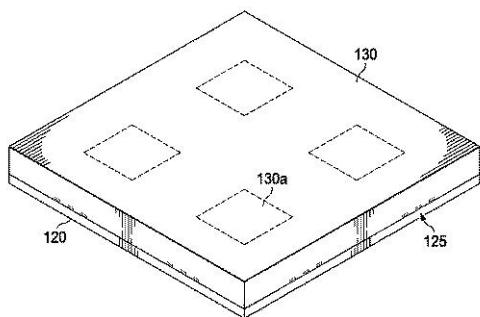

図1Bは、例示の誘電体カバー130を示す。誘電体カバー130はプラスチックを含み得る。誘電体カバー130は、第1の繰り返しパターンの窪み130aを有し、第1の繰り返しパターンの窪み130aは、覆われる半導体ダイに適合するような寸法及び形状とされる矩形であり、半導体ダイを受けることを可能にするための半導体ダイと比べて面積が僅かに大きいように示されている。

40

50

## 【0014】

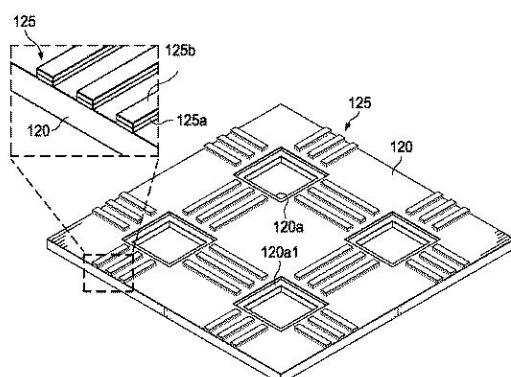

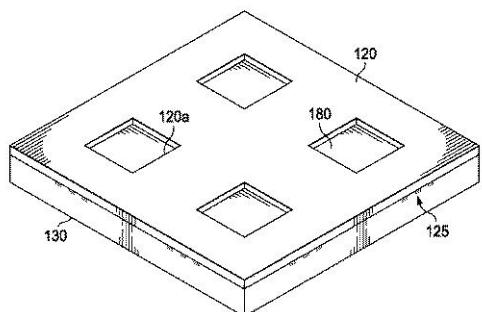

図1Cは、例示の金属基板120を示し、金属基板120上の隆起トレース125のそれぞれの構成要素を示すために一部を拡大した挿入図を備えている。金属基板120は、銅合金などの銅を含み得る。他の例示の金属には、Ni、Co、Sn、又はそれらの合金が含まれる。金属基板120は、窪み130aに位置整合する中央スルーホールアーチャ120aを含む、図1Bに示された誘電体カバー130上の第1の繰り返しパターンに位置整合する第2の繰り返しパターンを含む。スルーホールアーチャ120aは、ダイが上に搭載される外側リング120aと、スルーホールアーチャ120aの周りの複数の隆起トレース125とを有し、隆起トレース125は、金属基板120上の誘電体ベース層125a(例えば、ポリイミド)上の金属層125bを含む。金属層125bは、誘電体ベース層125a上に印刷され得る。

10

## 【0015】

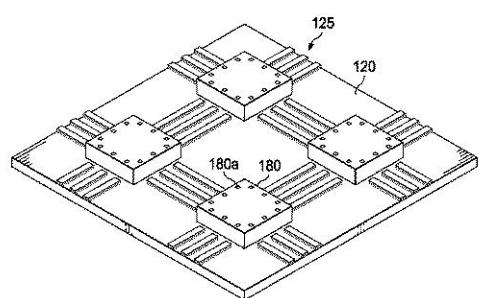

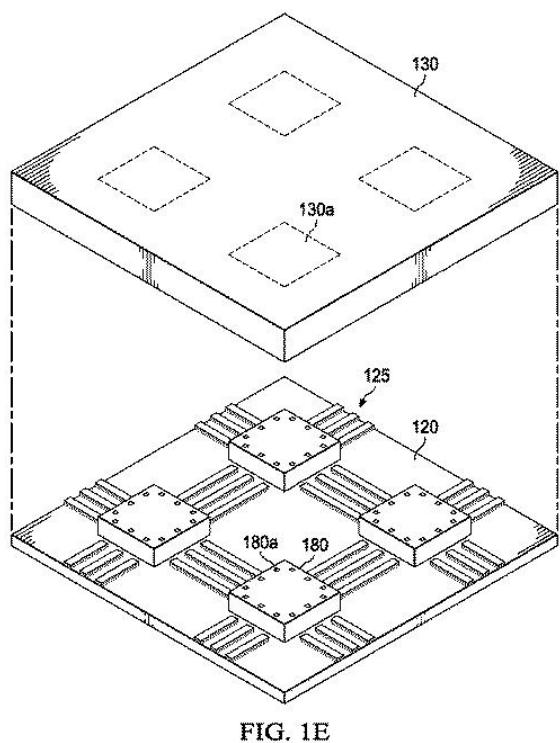

図1Dは、例示の金属基板120のスルーホールアーチャ120a内の外側リング120a(図示せず)上に、頂部(アクティブ)側を上にし、裏側を下にして置かれている半導体ダイ180を示す。半導体ダイ180のアクティブ頂部側にボンドパッド180aが示されている。図1Eは、半導体ダイ180の上の金属基板120上に配置する直前の誘電体カバー130を示す。図1Fは、誘電体カバー130を見下ろす、半導体ダイ180の上に金属基板120上に配置された後の誘電体カバー130を示す。図1Gは、半導体ダイ180によって占有されていないアーチャ120aの部分をあらわにする、金属基板120の底部を見下ろすために反転された図1Fの図である。

20

## 【0016】

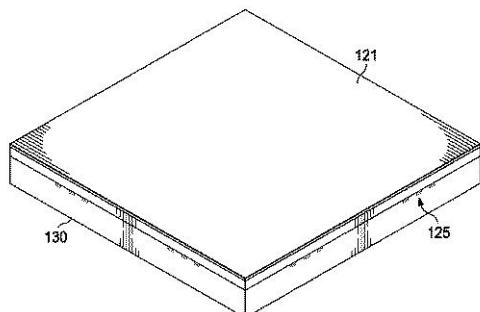

図1Hは、半導体ダイ180上のBSM層と、ダイ取り付けを提供するためにアーチャの境界を区切る金属基板120の壁との間の容積を充填するための、銅などの電気めっきされた単一金属層を堆積するための電気めっきに続く、半導体ダイ180の上の金属基板120上の誘電体カバー130を含むスタックの裏側を示す。電気めっきプロセスのための時間は、所望の厚みを堆積速度で割ることによって計算できる。金属ダイ取り付け層121の厚みは、例えば20~100μmの厚みなど、10~250μmなどの厚みであるアーチャを充填するように設計される。図1Hは、金属基板120の底部側全体にシートとして堆積される、電気めっきされた金属ダイ取り付け層121で充填されている半導体ダイ180(ダイの下)によって占有されていないアーチャ部を示す。金属ダイ取り付け層121は平坦であるように示されているが、それぞれのスルーホールアーチャ120aを覆うときにはわずかな窪みがあつてもよい。

30

## 【0017】

電気めっきされた金属層である金属ダイ取り付け層121は、スパッタされた金属層など、他の方法によって堆積された同じ金属材料の他の層と比較して特徴的である。電着層は、スパッタされた層とは異なり、見通しのきかない領域を充填することが知られている。また、電着層は、電着層のバルク部のものとは異なる密度及び微細構造を有する初期的に堆積されたネルンスト拡散層を含む、固有の微細構造を有することが知られている。

## 【0018】

図1Iは、スタックをめっき溶液から取り除き、誘電体カバー130を取り除き、金属基板120を個片化して、第1のパッケージ化された半導体デバイス前駆物質を含む複数のパッケージ化された半導体デバイス前駆物質を形成し、次いでリード126を追加した後の、単一のパッケージ化された半導体デバイス前駆物質を示す。リード126は、銅、銅合金、又は市販されているか又は自社で生成し得る錫被覆されたリードなどの金属ストリップ(例えば、リードフレームと同じ金属)を含む。例えば、金属シートを金属ストリップに切断することができる。

40

## 【0019】

リード126は、複数の隆起したトレース125上の金属層125bと接し、少なくとも1つの屈曲部を有し、金属基板120を越えて延在する末端部を含む。リード126は、金属層125bにはんだ付けされてもよいが、溶接又は導電性接着性材料を介して取り

50

付けることもできる。図示のボンドワイヤ 133 は、個片化前に付加され、複数の隆起トレース 125 と半導体ダイ 180 上のボンドパッド 180a との間にある。図 1J は、パッケージ化された半導体デバイスを完成させるための封止のためのモールド化合物 175 を形成するためのモールディング後の、単一のパッケージ化された半導体デバイス 190 を示す。任意で Sn (錫) 層をリード 126 に付加することもできる。

#### 【0020】

図 2 は、例示のパッケージ化された半導体デバイス 200 の断面図であり、パッケージ化された半導体デバイス 200 は、例示の態様に従って、90 度の屈曲部を備えるリード 126 を有して、電気めっきされた金属ダイ取り付け層 121 によって金属基板 120 上に直接取り付けられた BSM 層 181 を備える半導体ダイ 180 を有する。上述のように、金属基板 120 は、銅合金、Ni、Co、Sn、又はそれらの合金など、銅を含み得る。金属基板 120 は、約 0.1 mm (3.94 ミル (mils)) ~ 0.3 mm (11.81 ミル) の厚みとし得る。また、上述のように、金属ダイ取り付け層 121 は、20 ~ 100  $\mu$ m の厚みなど、10 ~ 250  $\mu$ m の厚みとし得る。図 3 は、例示のパッケージ化された半導体デバイス 300 の断面図であり、パッケージ化された半導体デバイス 300 は、例示の態様に従って、電気めっきされた金属ダイ取り付け層 121 によって金属基板上に直接取り付けられた BSM 層 181 を備える半導体ダイ 180 を有し、90 度の屈曲部でないリード屈曲部の一例としてガルウィングリード 126a を有する。

10

#### 【0021】

記載された態様の利点には、室温でダイ取り付けを行う能力、半導体ダイから金属基板への高い熱放散、並びに、銅を含む場合など、電気めっきされた金属ダイ取り付け層の高い延性に起因する強い機械的ダイ支持が含まれる。また、銀で充填されるエポキシ樹脂と比べて、低コストのダイ取り付け解決策が提供される。

20

#### 【0022】

記載された実施例は、種々の異なったパッケージ化された半導体集積回路 (IC) デバイス及び関連製品を形成するために、種々のアッセンブリフローに統合され得る。アッセンブリには、单一半導体ダイ、又は、複数の積層半導体ダイを含む PnP 構成などの多重半導体ダイが含まれ得る。様々なパッケージ基板が用いられ得る。半導体ダイは、障壁層、誘電体層、デバイス構造、能動要素、並びに、ソース領域、ドレイン領域、ピットライン、ベース、エミッタ、コレクタ、導電性ライン、導電性ビアなどを含む受動要素を含む、その中の種々の要素及び/又はその上の層を含み得る。また、半導体ダイは、バイポーラ、絶縁ゲートバイポーラトランジスタ (IGBT)、CMOS、BiCMOS、及び MEMS を含む、種々のプロセスから形成され得る。

30

#### 【0023】

本記載に関係する当業者であれば、特許請求の範囲内で多くの他の実施例及び実施例の変形が可能であり、本記載の範囲から逸脱することなく、記載された実施例にさらなる追加、削除、置換、及び変形を行うことができる事が理解されるであろう。

40

50

## 【図面】

## 【図 1 A】

FIG. 1A

## 【図 1 B】

FIG. 1B

10

## 【図 1 C】

FIG. 1C

## 【図 1 D】

FIG. 1D

20

30

40

50

【図 1 E】

FIG. 1E

【図 1 F】

FIG. 1F

10

20

【図 1 G】

FIG. 1G

【図 1 H】

FIG. 1H

30

40

50

【図 1 I】

FIG. 1I

【図 1 J】

FIG. 1J

10

【図 2】

FIG. 2

20

【図 3】

FIG. 3

30

40

50

---

フロントページの続き

イブ 5309

審査官 秋山 直人

(56)参考文献      特開平05-166971 (JP, A)

米国特許出願公開第2015/0243591 (US, A1)

特開2012-094643 (JP, A)

国際公開第2015/174198 (WO, A1)

特開2002-249891 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 23/12

H01L 23/14