(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년02월15일

(11) 등록번호 10-1111529

(24) 등록일자 2012년01월26일

(51) Int. Cl.

G09G 3/36 (2006.01) G09G 3/20 (2006.01)

(21) 출원번호 10-2010-0008474

(22) 출원일자 2010년01월29일

심사청구일자 2010년01월29일

(65) 공개번호 10-2011-0088797

(43) 공개일자 2011년08월04일

(56) 선행기술조사문헌

KR100855989 B1\*

KR1020070001475 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

주식회사 실리콘웍스

대전광역시 유성구 테크노2로 222 (탑립동)

(72) 발명자

임현용

대전광역시 유성구 판평동 한화꿈에그린아파트 2

차 1003동 902호

최정환

대전광역시 동구 삼성2동 319-11번지

(뒷면에 계속)

(74) 대리인

이철희

전체 청구항 수 : 총 7 항

심사관 : 이성현

(54) 액정표시장치의 소스 드라이버 회로

**(57) 요 약**

본 발명은 액정표시장치에서 파워 온 시 유효데이터가 입력되기 전에 잡음성 데이터가 디스플레이되는 것을 방지하는 기술에 관한 것이다.

이러한 본 발명은, VCC 전원전압과 VDD 전원전압을 분압하여 출력함에 있어서, VDD 전원전압의 중간레벨을 VCC 전원전압의 레벨보다 낮게 분압하여 출력하는 전원전압 입력부; 상기 전원전압 입력부로부터 분압되어 입력되는 전압을 비교하여 상기 VDD 전원전압의 중간레벨보다 VCC 전원전압의 레벨이 높게 나타나는 구간에서 출력전압을 '하이'로 출력하는 전원전압 비교부; 상기 전원전압 비교부의 출력전압을 리세트신호로 출력함에 있어서, 외부 환경에 민감하게 반응하는 것을 방지하기 위한 슈미트트리거; 상기 슈미트트리거로부터 입력되는 리세트신호와 첫 번째의 게이트 스타트펄스의 사이 구간에서 특정 레벨의 전압을 출력하는 특정전압 공급부를 포함하여 구성함을 특징으로 한다.

**대 표 도**

(72) 발명자

김언영

대전광역시 대덕구 읍내동 현대아파트 106동 303호

나준호

대전광역시 서구 둔산2동 수정아파트 8동 608호

김대성

대전광역시 대덕구 오정동 635-1 신동아아파트 6동

1503호

한대근

대전광역시 서구 둔산동 970 향촌아파트 109동

1301호

---

## 특허청구의 범위

### 청구항 1

제1전원전압과 제2전원전압을 분압하여 출력함에 있어서, 제2전원전압의 중간레벨을 제1전원전압의 레벨보다 낮게 분압하여 출력하는 전원전압 입력부와;

상기 전원전압 입력부로부터 분압되어 입력되는 전압을 비교하여 상기 제2전원전압의 중간레벨보다 제1전원전압의 레벨이 높게 나타나는 구간에서 출력전압을 '하이'로 출력하는 전원전압 비교부와;

상기 전원전압 비교부의 출력전압을 리세트신호로 출력함에 있어서, 외부 환경에 민감하게 반응하는 것을 방지하기 위한 슈미트트리거와;

상기 슈미트트리거로부터 입력되는 리세트신호와 첫 번째의 게이트 스타트펄스의 사이 구간에서 특정 레벨의 전압을 출력하는 특정전압 공급부 및,

파워가 온된 직후 상기 특정전압 공급부로부터 공급되는 특정 레벨의 전압을 액정표시패널의 데이터라인에 출력한 후 유효 데이터를 출력하는 출력버퍼부로 구성한 것을 특징으로 하는 액정표시장치의 소스 드라이버 회로.

### 청구항 2

제1항에 있어서, 제1전원전압은 VCC이고, 제2전원전압은 VDD인 것을 특징으로 하는 액정표시장치의 소스 드라이버 회로.

### 청구항 3

제1항에 있어서, 전원전압 입력부는

상위 파워다운신호에 의해 턴온되어 제2전원전압을 통과시키는 상위 피모스 트랜지스터와;

상기 상위 피모스 트랜지스터를 통해 입력되는 제2전원전압을 저항의 비율로 분압하여 상위 분압전압을 출력하는 상위 분압전압출력부와;

하위 파워다운신호에 의해 턴온되어 제1전원전압을 통과시키는 하위 피모스 트랜지스터와;

상기 하위 피모스 트랜지스터를 통해 입력되는 제1전원전압을 저항의 비율로 분압하여 하위 분압전압을 출력하는 하위 분압전압출력부로 구성된 것을 특징으로 하는 액정표시장치의 소스 드라이버 회로.

### 청구항 4

제3항에 있어서, 상위 분압전압출력부는 분압된 제2전원전압의 중간레벨이 상기 분압된 제1전원전압의 레벨보다 낮게 되도록 저항값의 비율이 설정된 것을 특징으로 하는 액정표시장치의 소스 드라이버 회로.

### 청구항 5

제1항에 있어서, 전원전압 비교부는

상위 파워다운신호에 의해 스텐바이 모드에서 인에이블 모드로 전환하는 인에이블부와;

상기 인에이블부를 통해 제1전원전압을 공급받고, 하위 입력전압과 상위 입력전압을 비교하여 그에 따른 출력전압을 출력하는 비교부와;

상기 비교부로부터 출력전압이 발생되도록 하기 위한 부하부로 구성된 것을 특징으로 하는 액정표시장치의 소스 드라이버 회로.

## 청구항 6

제1항에 있어서, 출력버퍼부는 상기 특정전압과 유효 데이터를 공통 입력단자를 통해 입력받거나, 스위치를 통해 선택적으로 입력받도록 구성된 것을 특징으로 하는 액정표시장치의 소스 드라이버 회로.

## 청구항 7

제1항에 있어서, 파워다운신호에 의해 턴온되어 상기 전원전압 비교부의 출력전압을 접지단자로 뮤팅시키는 모스트랜지스터를 더 포함하여 구성된 것을 특징으로 하는 액정표시장치의 소스 드라이버 회로.

## 청구항 8

삭제

### 명세서

#### 기술분야

[0001]

본 발명은 액정표시장치의 소스 드라이버 구동기술에 관한 것으로, 특히 파워 온 시 소스 드라이버로부터 액정표시패널에 잡음성 데이터가 공급되어 불량 화면이 디스플레이되는 것을 방지할 수 있도록 한 액정표시장치의 소스 드라이버 회로에 관한 것이다.

#### 배경기술

[0002]

일반적으로, 액정표시장치는 복수개의 게이트 라인과 데이터 라인이 서로 수직한 방향으로 배열되어 매트릭스 형태의 픽셀영역을 갖는 액정표시패널과, 액정표시패널에 구동 신호와 데이터 신호를 공급하는 구동회로부와, 액정표시패널에 광원을 제공하는 백라이트를 구비한다.

[0003]

그리고, 상기 구동회로부는 액정표시패널의 각 데이터 라인에 데이터 신호를 공급하는 소스 드라이버와, 액정표시패널의 각 게이트 라인에 게이트 구동 펄스를 인가하는 게이트 드라이버와, 액정표시패널의 구동 시스템으로부터 입력되는 디스플레이 데이터와 수직 및 수평동기신호 그리고 클럭신호 등 제어신호를 입력받아 소스 드라이버와 게이트 드라이버가 화면을 재생하기에 적합한 타이밍으로 출력하는 타이밍 콘트롤러 등을 구비한다.

[0004]

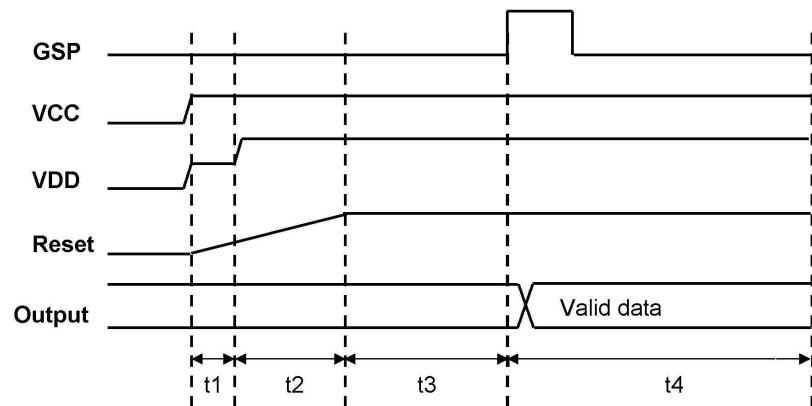

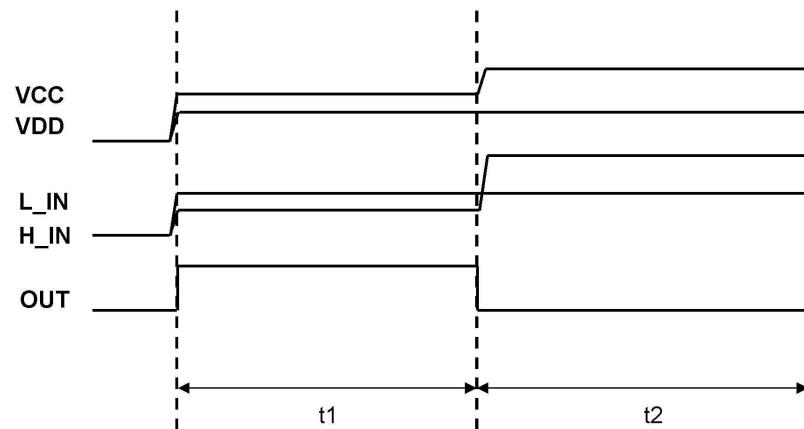

도 1은 종래 액정표시패널의 파워 온 시퀀스를 나타낸 것이다.

[0005]

제1전원전압(VCC)이 목표 레벨로 상승될 때 또 다른 제2전원전압(VDD)은 중간 레벨로 상승된다. 이때, 리세트신호(Reset)가 목표 레벨을 향해 상승되기 시작하고, 상기 전원원압(VDD)은 t1 시간 동안 중간 레벨로 유지된 후 최종 목표 레벨로 상승된다. 이후, t2 시간이 경과되면 상기 리세트신호(Reset)가 목표 레벨에 도달된다. 이후, t3 시간이 경과되고 t4 시간이 시작될 때 첫 번째의 게이트 스타트 펄스(GSP)가 공급되고, 이어서 타이밍 콘트롤러 및 소스 드라이버를 통해 유효 데이터(Valid data)가 공급되기 시작한다. 여기서, 상기 제1전원전압(VCC)은 소스 드라이버의 로직회로를 구동하는 전원전압이고, 제2전원전압(VDD)은 소스 드라이버를 구동하는 전원전압이다.

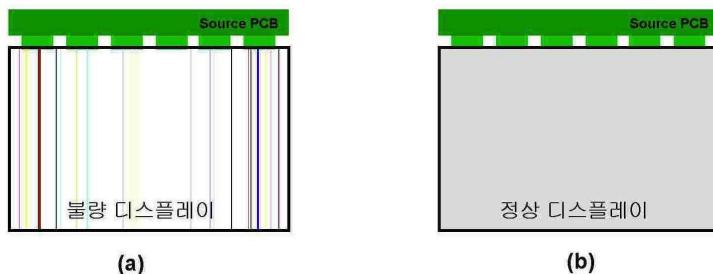

[0006]

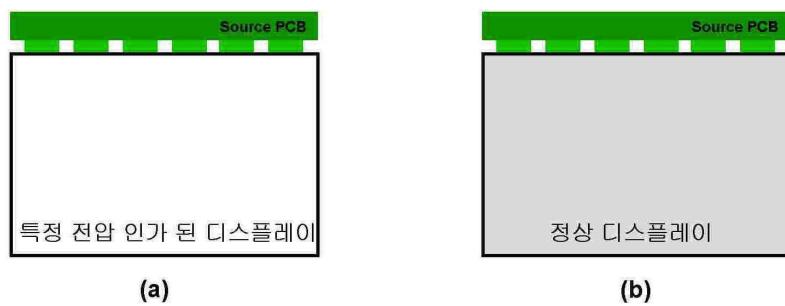

상기 설명에서와 같이 소스 드라이버로부터 액정표시패널에 유효 데이터가 공급되기 전에 두 개의 전원전압이 시차를 두고 인가되는데, 이와 같은 경우 소스 드라이버 내의 출력버퍼의 입력단이 플로팅되어 t2~t3 구간에 불분명한 잡음성의 데이터가 액정표시패널에 공급된다. 이에 따라, 상기 t2~t3 구간에서 도 2의 (a)에서와 같이 노이즈 형태의 화면이 디스플레이되고, 이후 t4 구간에서부터 도 2의 (b)에서와 같이 정상적인 디스플레이 동작이 이루어진다.

[0007]

이와 같이, 종래의 소스 드라이버를 사용하는 경우, 액정표시패널에 유효 데이터를 출력하기 전에 액정표시패널에 불분명한 잡음성 데이터를 출력하였다. 이로 인하여, 액정표시패널에 잡음성 화상이 디스플레이되어 사용자에게 불쾌감을 줄 뿐만 아니라 제품의 신뢰성을 저하시키게 되는 문제점이 있었다.

## 발명의 내용

### 해결하려는 과제

- [0008] 따라서, 본 발명의 목적은 파워 온 후 소스 드라이버로부터 액정표시패널에 유효 데이터가 공급되기 전에 소스 드라이버 내의 출력버퍼를 통해 특정 레벨의 전압을 공급하여 잡음성 불량화면이 디스플레이되는 것을 방지하는데 있다.

- [0009] 본 발명의 목적들은 앞에서 언급한 목적으로 제한되지 않는다. 본 발명의 다른 목적 및 장점들은 아래 설명에 의해 더욱 분명하게 이해될 것이다.

### 과제의 해결 수단

- [0010] 상기와 같은 목적을 달성하기 위한 본 발명은,

- [0011] 제1전원전압과 제2전원전압을 분압하여 출력함에 있어서, 제2전원전압의 중간레벨을 제1전원전압의 레벨보다 낮게 분압하여 출력하는 전원전압 입력부와;

- [0012] 상기 전원전압 입력부로부터 분압되어 입력되는 전압을 비교하여 상기 제2전원전압의 중간레벨보다 제1전원전압의 레벨이 높게 나타나는 구간에서 출력전압을 '하이'로 출력하는 전원전압 비교부와;

- [0013] 상기 전원전압 비교부의 출력전압을 리세트신호로 출력함에 있어서, 외부 환경에 민감하게 반응하는 것을 방지하기 위한 슈미트트리거와;

- [0014] 상기 슈미트트리거로부터 입력되는 리세트신호와 첫 번째의 게이트 스타트펄스의 사이 구간에서 특정 레벨의 전압을 출력하는 특정전압 공급부 및,

- [0015] 파워가 온된 직후 상기 특정전압 공급부로부터 공급되는 특정 레벨의 전압을 액정표시패널의 데이터라인에 출력한 후 유효 데이터를 출력하는 출력버퍼부로 구성함을 특징으로 한다.

- [0016] 상기와 같은 목적을 달성하기 위한 또 다른 본 발명은,

- [0017] 파워가 온된 후 유효데이터가 입력될 때까지 출력버퍼들의 출력단자와 해당 데이터라인들을 개방시키는 다수의 출력스위치와;

- [0018] 상기 파워가 온된 직후부터 유효데이터가 입력될 때까지 상기 데이터라인들을 서로 연결시켜 차지쉐어링이 이루어지도록 하는 다수의 차지쉐어링 스위치와;

- [0019] 상기 출력스위치 및 차지쉐어링 스위치의 스위칭 동작을 제어하는 제어부를 포함하여 구성함을 특징으로 한다.

### 발명의 효과

- [0020] 본 발명은 액정표시장치에서 파워가 온된 직후부터 데이터라인을 통해 액정표시패널에 유효 데이터가 입력될 때까지 데이터라인에 강제로 특정 레벨의 전압을 공급함으로써, 잡음성 불량화면이 디스플레이되는 것을 확실하게 방지할 수 있는 효과가 있다.

- [0021] 또한, 액정표시장치에서 파워가 온된 직후부터 데이터라인을 통해 액정표시패널에 유효 데이터가 입력될 때까지 데이터라인에 연결된 출력버퍼의 출력단자들을 개방시키고, 각 데이터라인을 서로 연결시켜 차지 쉐어링이 이루어지도록 함으로써, 잡음성 불량화면이 디스플레이되는 것을 확실하게 방지할 수 있는 효과가 있다.

- [0022] 이에 의해, 제품에 대해 신뢰감이 저하되는 것을 방지할 수 있는 효과가 있다.

### 도면의 간단한 설명

- [0023] 도 1은 종래 액정표시패널의 파워 온 시퀀스를 나타낸 파형도.

- 도 2의 (a),(b)는 종래 액정표시장치에서 초기 구동시 불량화면이 디스플레이된 후 정상화면이 디스플레이되는 것을 나타낸 예시도.

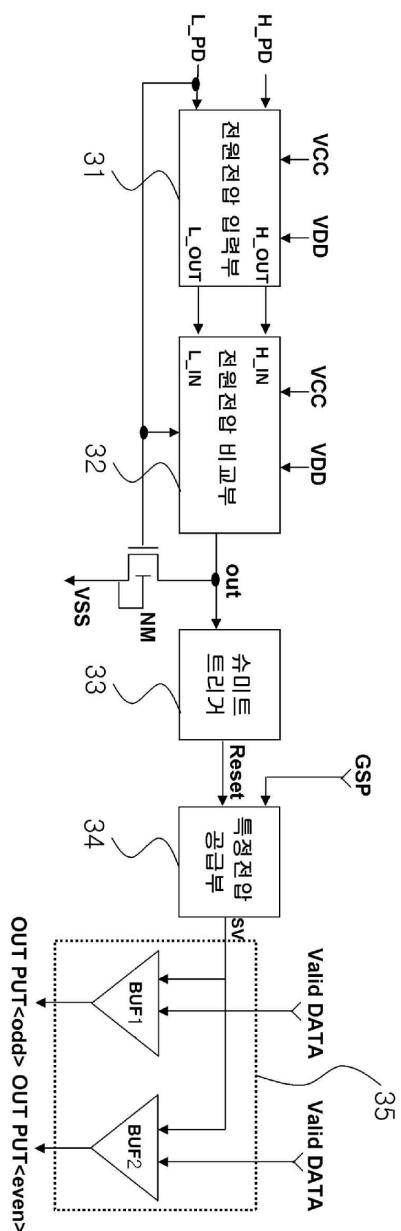

- 도 3은 본 발명에 의한 액정표시장치의 소스 드라이버 회로의 실시예를 나타낸 블록도.

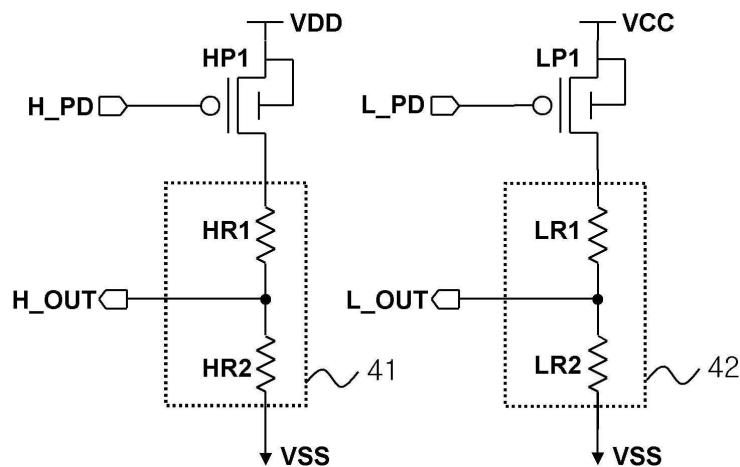

- 도 4는 도 3에서 전원전압 입력부의 상세 회로도.

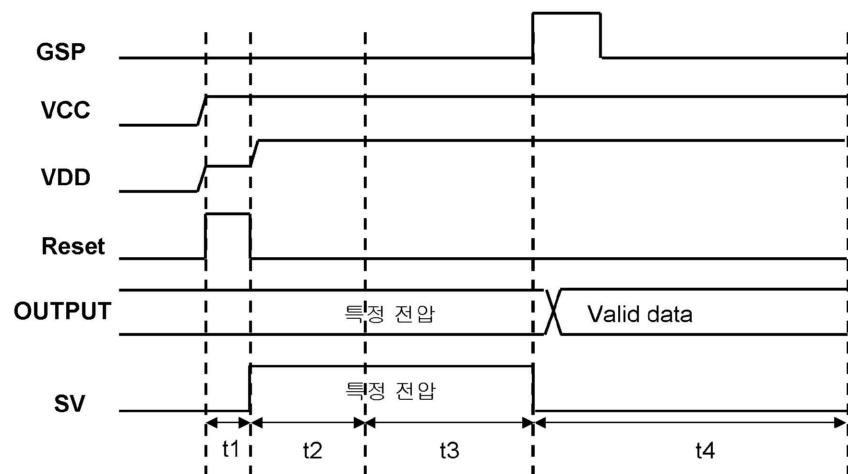

도 5는 도 3 각부의 출력 파형도.

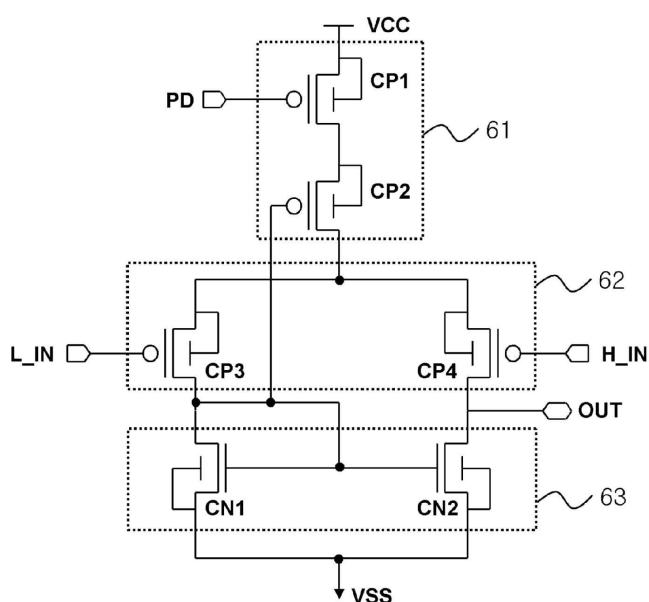

도 6은 도 3에서 전원전압 비교부의 상세 회로도.

도 7은 전원전압 비교부의 입력전압 및 출력전압의 파형도.

도 8의 (a),(b)는 본 발명의 액정표시장치에서 초기 구동시 유효데이터가 입력되기 전후에 모두 정상화면이 디스플레이되는 것을 나타낸 예시도.

도 9는 본 발명에 의한 액정표시장치의 소스 드라이버 회로의 다른 실시예를 나타낸 블록도.

### 발명을 실시하기 위한 구체적인 내용

- [0024] 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 상세히 설명하면 다음과 같다.

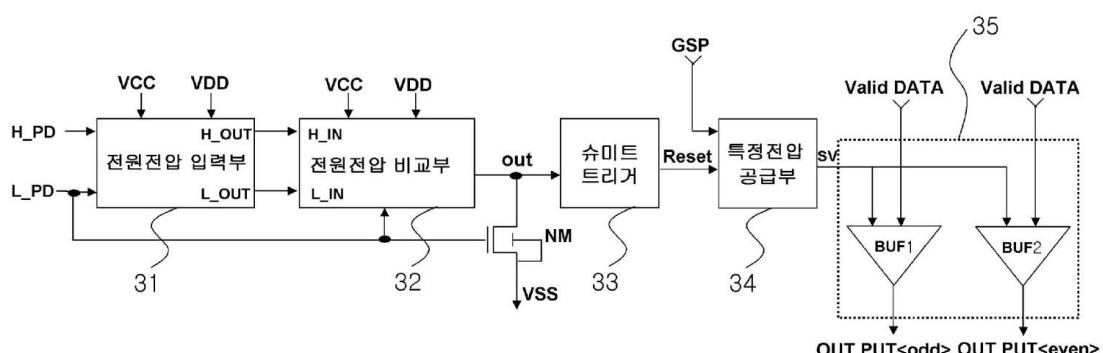

- [0025] 도 3은 본 발명에 의한 액정표시장치의 소스 드라이버 회로의 블록도로서 이에 도시한 바와 같이, 전원전압 입력부(31), 전원전압 비교부(32), 슈미트트리거(33), 특정전압 공급부(34) 및 출력버퍼부(35)로 구성된다.

- [0026] 전원전압 입력부(31)는 서로 다른 레벨의 제1,2 전원전압(VCC),(VDD)을 소정 비율로 분압하여 출력하는 역할을 수행한다.

- [0027] 도 4는 상기 전원전압 입력부(31)의 구현예를 보인 회로도로서, 스위칭용 페모스 트랜지스터(HP1), 상위 분압전압출력부(41), 스위칭용 페모스 트랜지스터(LP1), 하위 분압전압출력부(42)로 구성된다.

- [0028] 도 5에서와 같이 제2전원전압(VDD)이 중간 레벨로 유지되는 t1 구간에서 상위 파워다운신호(H\_PD)에 의해 페모스 트랜지스터(HP1)가 터온된다. 따라서, 상기 제2전원전압(VDD)이 상기 페모스 트랜지스터(HP1)를 통해 상위 분압전압출력부(41)에 전달된다. 이때, 상기 상위 분압전압출력부(41)는 직렬접속된 두 저항(HR1),(HR2)으로 상기 페모스 트랜지스터(HP1)를 통해 공급되는 제2전원전압(VDD)을 분압하여 상위 분압전압(H\_OUT)을 전원전압 비교부(32)의 상위 입력전압(H\_IN)으로 공급한다.

- [0029] 또한, 상기 t1 구간에서 하위 파워다운신호(L\_PD)에 의해 페모스 트랜지스터(LP1)가 터온된다. 따라서, 상기 제1전원전압(VCC)이 상기 페모스 트랜지스터(LP1)를 통해 하위 분압전압출력부(42)에 전달된다. 이때, 상기 하위 분압전압출력부(42)는 직렬접속된 두 저항(LR1),(LR2)으로 상기 페모스 트랜지스터(LP1)를 통해 공급되는 제1전원전압(VCC)을 분압하여 하위 분압전압(L\_OUT)을 전원전압 비교부(32)의 하위 입력전압(L\_IN)으로 공급한다.

- [0030] 도 7에서와 같이 원래 제1전원전압(VCC)은 제2전원전압(VDD)의 중간 레벨보다 낮다. 하지만, 상기 상위 분압전압출력부(41)의 저항(HR1),(HR2)의 비율과 하위 분압전압출력부(42)의 저항(LR1),(LR2)의 비율을 적절히 설정하여, t1 구간에서 전원전압 비교부(32)에 공급되는 하위 입력전압(L\_IN)이 상위 입력전압(H\_IN)보다 높도록 하였다.

- [0031] 전원전압 비교부(32)는 상기 전원전압 입력부(31)로부터 입력되는 상기 하위 입력전압(L\_IN)과 상위 입력전압(H\_IN)를 비교하여 그 하위 입력전압(L\_IN)이 상위 입력전압(H\_IN)보다 높게 나타나는 t1 구간에서 출력신호(OUT)를 '하이'로 출력한다.(도 7 참조)

- [0032] 도 6은 상기 전원전압 비교부(32)의 구현예를 보인 회로도로서, 이에 도시한 바와 같이 인에이블부(61), 비교부(62), 로드부(63)로 구성된다.

- [0033] 인에이블부(61)는 직렬 접속된 페모스 트랜지스터(CP1),(CP2)를 구비한다. 상기 t1 구간에서 상기 파워다운신호(PD)가 '로우'로 공급되어 상기 페모스 트랜지스터(CP1)가 터온된다. 이에 따라, 제1전원전압(VCC)이 상기 페모스 트랜지스터(CP1),(CP2)를 통해 비교부(62)에 전달된다.

- [0034] 비교부(62)는 페모스 트랜지스터(CP3),(CP4)를 구비하는데, 이들은 소스 공통접속점을 통해 상기 제1전원전압(VCC)을 공급받고, 게이트로 상기 하위 입력전압(L\_IN), 상위 입력전압(H\_IN)을 각기 공급받는다.

- [0035] 따라서, 상기 설명에서와 같이 t1 구간에서 상기 하위 입력전압(L\_IN)이 상위 입력전압(H\_IN)보다 높으므로, 상기 페모스 트랜지스터(CP3)가 터오프되는 반면 페모스 트랜지스터(CP4)가 터온된다.

- [0036] 부하부(63)는 엔모스 트랜지스터(CN1),(N2)를 구비하는데, 상기 페모스 트랜지스터(CP3)의 터오프에 의해 노드(N1)가 '로우' 상태이므로 그 엔모스 트랜지스터(CN1),(N2)가 터오프 상태로 유지된다.

- [0037] 이에 따라, 상기 비교부(62)의 페모스 트랜지스터(CP4)를 통해 도 7에서와 같이 출력전압(OUT)이 '하이'로 출력

된다.

[0038] 결국, 전원전압 비교부(32)는 도 5 및 도 7에서와 같이 제1전원전압(VCC)이 목표레벨로 상승된 후부터 제2전원전압(VDD)이 최종 목표 레벨로 상승되기 시작하는 구간 즉, 상기 제2전원전압(VDD)이 중간 레벨로 유지되는 t1 구간에서 리세트신호(Reset)를 '하이'로 출력한다.

[0039] 슈미트트리거(33)는 상기 전원전압 비교부(32)를 통해 발생되는 출력전압(OUT)을 리세트신호(Reset)로 사용함에 있어서, 외부 환경(노이즈)에 의해 너무 민감하게 반응하지 않고 안정된 형태를 유지할 수 있도록 하기 위해 사용되었다.

[0040] 특정전압 공급부(34)는 도 5에서와 같이 리세트신호(Reset)와 특정전압(SV)을 논리조합하여 t2, t3 구간에서 특정 전압(SV)을 출력한다. 상기 특정전압 공급부(34)에서 출력되는 특정전압(SV)은 출력버퍼부(35)의 출력버퍼(BUF1), (BUF2)를 통해 액정표시패널의 데이터라인에 공급된다. 도 3에서는 출력버퍼부(35)에 한 쌍의 출력버퍼(BUF1), (BUF2)가 구비된 것으로 표현하였으나, 이와 같은 출력버퍼들이 필요한 개수만큼 구비된다.

[0041] 이에 따라, 도 8의 (a)에서와 같이 액정표시패널 상에 불분명한 잡음성 화상이 디스플레이되지 않는다.

[0042] 이후, t4 구간부터 상기 특정전압(SV)이 더 이상 상기 출력버퍼부(35)의 출력버퍼(BUF1), (BUF2)에 공급되지 않고, 이때부터 유효 데이터(Valid data)가 상기 출력버퍼(BUF1), (BUF2)를 통해 액정표시패널의 데이터라인에 공급된다.

[0043] 이에 따라, 도 8의 (b)에서와 같이 유효 데이터에 의해 정상적으로 디스플레이되는 화면이 나타난다.

[0044] 상기 출력버퍼부(35)의 출력버퍼(BUF1), (BUF2)는 상기 특정전압(SV)과 유효 데이터(Valid data)를 하나의 입력 단자를 통해 시간 차이를 두고 입력받을 수 있고, 별도의 스위치를 구비하여 선택적으로 입력받을 수 있다.

[0045] 상기 도 3에서 엔모스 트랜지스터(NM)는 상기 t2, t3 구간이 경과된 후 하위 파워다운신호(L\_PD)에 의해 턴온되어 상기 전원전압 비교부(32)에서 출력되는 전압(OUT)을 접지단자(VSS)로 뮤팅시켜 그 출력전압(OUT)이 무효화되도록 하기 위해 사용된 것이다.

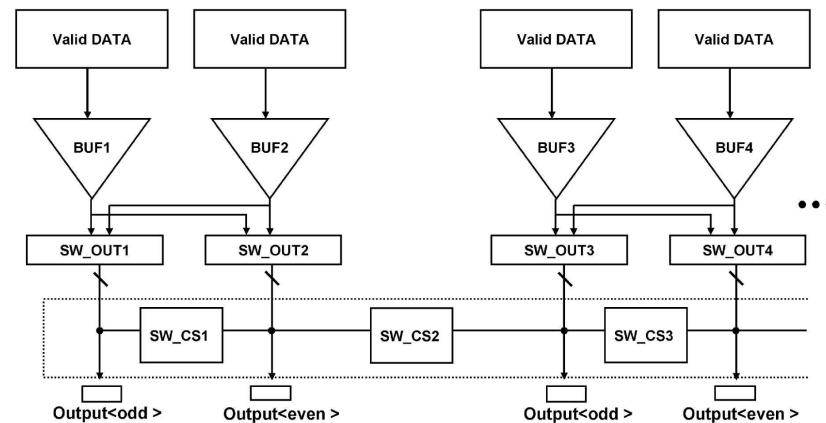

[0046] 한편, 도 9는 본 발명의 액정표시장치의 소스 드라이버 회로에 대한 다른 실시예를 나타낸 것으로, 출력버퍼(BUF1, BUF2), (BUF3, BUF4), 출력스위치(SW\_OUT1, SW\_OUT2), (SW\_OUT3, SW\_OUT4), 차지쉐어링 스위치(SW\_CS1, SW\_CS2), (SW\_CS3, SW\_CS4)로 구성된다.

[0047] 평상시, 출력스위치(SW\_OUT1)는 상기 타이밍 콘트롤러와 같은 제어부의 제어를 받아 출력버퍼(BUF1)의 출력단자나 출력버퍼(BUF2)의 출력단자를 데이터라인에 연결된 홀수출력단자 OUTPUT<odd>에 연결한다. 또한, 출력스위치(SW\_OUT2)는 상기 제어부의 제어를 받아 출력버퍼(BUF1)의 출력단자나 출력버퍼(BUF2)의 출력단자를 데이터라인에 연결된 짝수출력단자 OUTPUT<even>에 연결한다.

[0048] 이와 마찬가지로, 출력스위치(SW\_OUT3, SW\_OUT4)도 출력버퍼(BUF3, BUF4)의 출력단자를 또 다른 데이터라인에 각기 연결된 홀수 출력단자 OUTPUT<odd> 및 짝수 출력단자 OUTPUT<even>에 연결한다.

[0049] 그런데, 상기 출력스위치(SW\_OUT1, SW\_OUT2), (SW\_OUT3, SW\_OUT4)는 상기 불분명한 데이터가 입력될 우려가 있는 t2~t3 구간에서 상기 제어부에 의해 턴오프되도록 하였다. 따라서, 상기 t2~t3 구간에서 액정표시패널에 불분명한 잡음성 데이터가 액정표시패널에 유입되어 디스플레이되는 것이 방지된다.

[0050] 하지만, 상기와 같이 단순히 t2~t3 구간에서 상기 출력스위치(SW\_OUT1, SW\_OUT2), (SW\_OUT3, SW\_OUT4)를 오프시키는 경우, 데이터라인에 불균등하게 잔존하는 데이터 전압에 의해 약간의 잡음성 화상이 디스플레이될 수 있다.

[0051] 이를 방지하기 위해 본 실시예에서는 상기 제어부의 제어하에 차지쉐어링 스위치(SW\_CS1, SW\_CS2), (SW\_CS3, SW\_CS4)를 모두 턴온시키도록 하였다. 이에 따라, 상기 다수의 홀수 출력단자 OUTPUT<odd>와 짝수 출력단자 OUTPUT<even>에 연결된 각각의 데이터라인들이 모두 연결되어 차지쉐어링되므로 상기 t2~t3 구간에서 잡음성 화상이 디스플레이되는 것을 보다 확실하게 방지할 수 있을 뿐만 아니라, 화면을 깨끗한 단색으로 디스플레이할 수 있게 된다.

[0052] 상기에서는 상기 t2~t3 구간에서 각각의 데이터라인들을 모두 연결시켜 차지쉐어링되게 하여 상기 잡음성 화상이 디스플레이되는 것을 방지하는 기술이, 출력스위치(SW\_OUT1), (SW\_OUT2)가 출력버퍼(BUF1, BUF2)의 출력을 선

택적으로 입력받고, 출력스위치(SW\_OUT3),(SW\_OUT4)가 출력버퍼(BUF1,BUF2),(BUF3,BUF4)의 출력을 선택적으로 입력받는 크로스 구조에 적용된 것을 예로 하였으나, 본 발명이 이에 한정되는 것이 아니라 출력버퍼(BUF1-BUF4)의 출력과 출력스위치(SW\_OUT1-SW\_OUT4)가 1대1 대응관계로 연결된 구조에 적용하는 경우에도 동일한 효과를 얻을 수 있다.

[0053] 이상에서 본 발명의 바람직한 실시예에 대하여 상세히 설명하였지만, 본 발명의 권리범위가 이에 한정되는 것이 아니라 다음의 청구범위에서 정의하는 본 발명의 기본 개념을 바탕으로 보다 다양한 실시예로 구현될 수 있으며, 이러한 실시예들 또한 본 발명의 권리범위에 속하는 것이다.

### 부호의 설명

31 : 전원전압 입력부

32 : 전원전압 비교부

33 : 슈미트트리거

34 : 특정전압 공급부

35 : 출력버퍼부

### 도면

#### 도면1

#### 도면2

도면3

## 도면4

## 도면5

## 도면6

도면7

도면8

도면9