#### **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>3</sup>:

G06F 13/00

(11) International Publication Number: WO 82/03711

(43) International Publication Date: 28 October 1982 (28.10.82)

(21) International Application Number: PCT/US82/00455

(22) International Filing Date: 13 April 1982 (13.04.82)

(31) Priority Application Number: 255,061

(32) Priority Date: 16 April 1981 (16.04.81)

(33) Priority Country: US

(71) Applicant: NCR CORPORATION [US/US]; World Headquarters, Dayton, OH 45479 (US).

(72) Inventors: KOCOL, James, Edward; 1429 East Esperanza Way, Escondido, CA 92027 (US). GUNDERSON, Robert, Ogden; 1360-30 Black Forest Drive, West Carrollton, OH 45449 (US). SCHUCK, David, Burton; 1640 Queenston Drive, Escondido, CA 92027 (US). MARRO, Daniel, Joseph; 17637 Pomerado Road, San Diego, CA 92128 (US).

(74) Agents: JEWETT, Stephen, F. et al.; Patent Division, NCR Corporation, World Headquarters, Dayton, OH 45479 (US).

(81) Designated States: AU, BE (European patent), CH (European patent), DE (European patent), FR (European patent), GB (European patent), JP.

**Published**

With international search report.

(54) Title: DATA PROCESSING SYSTEM INCLUDING SUBSYSTEMS HAVING LOCAL MEMORIES

#### (57) Abstract

A data processing system (10) employs broadcast packet switching and having a plurality of subsystems (24) and a system bus (16, 18, 18A, 20, 20A) for linking with the subsystems (24). The subsystems (24) are grouped within stations (12) that are each enclosed by a computer cabinet. The system bus includes a star coupler (16), first and second external transmission lines (18, 20) connecting each station (12) to the star coupler (16), and first and second internal transmission lines (18A, 20A) within each station (12) that are coupled to the first and second external transmission lines (18, 20). The subsystems (24) within each station (12) are each coupled to the first and second internal transmission lines (18A, 20A) by a system bus interface (28). Each subsystem has a local memory (351) that includes a mailbox (350) for storing header information of messages that are to be copied by that subsystem. DMA circuitry (140) in each system bus interface (28) manages the operation of the mailbox (350) in its subsystem. A plurality of messages can be received by a subsystem and stored in the associated mailbox (350), without processor interruption.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT   | Austria                               | LI | Liechtenstein            |

|------|---------------------------------------|----|--------------------------|

| . AU | Australia                             | LK | Sri Lanka                |

| BE   | Belgium                               | LU | Luxembourg               |

| BR   | Brazil                                | MC | Monaco                   |

| CF   | Central African Republic              | MG | Madagascar               |

| CG   | Congo                                 | MR | Mauritania               |

| CH   | Switzerland                           | MW | Malawi                   |

| CM   | Cameroon                              | NL | Netherlands              |

| DE   | Germany, Federal Republic of          | NO | Norway                   |

| DK   | Denmark                               | RO | Romania                  |

| FI   | Finland                               | SE | Sweden                   |

| FR   | France                                | SN | Senegal                  |

| GA   | Gabon                                 | SU | Soviet Union             |

| GB   | United Kingdom                        | TD | Chad                     |

| HU   | Hungary                               | TG | Togo                     |

| JP   | Japan                                 | US | United States of America |

| KP   | Democratic People's Republic of Korea |    |                          |

10

15

20

25

3.0

35

# DATA PROCESSING SYSTEM INCLUDING SUBSYSTEMS HAVING LOCAL MEMORIES

#### Technical Field

This invention relates to data processing systems of the kind including a plurality of subsystems, a bus for carrying messages to be received by said subsystems, and a processor associated with at least one of said subsystems.

The invention also relates to methods of transferring blocks of data between two subsystems.

The invention has a particular application to data processing networks employing broadcast packet switching.

#### Background Art

In traditional data processing systems, several subsystems are linked to each other along a system bus and share the bus for the transfer of data. The control of the bus is typically given to one subsystem. Accordingly, when a message is to be sent from one subsystem to another subsystem, either the message has to be sent through the controlling subsystem or the controlling subsystem has to at least occasionally operatively connect each subsystem to the bus in order to pass its message.

As advancements in semiconductor technology have permitted increased amounts of circuitry to be fabricated on a single integrated circuit chip, there has been increasing interest in developing data processing systems that do not rely on a single subsystem to control the transmission of messages among plural subsystems in the data processing systems. It is widely believed that future data processing systems will be comprised of subsystem modules. Each module provides either processing or memory capability. No single module or subsystem in the system will have control over the system bus but, rather, each module shares with the

10

15

35

other modules the control of the communication lines that link the modules. When the user of the system desires to increase the capability of his system, he simply adds modules. Ideally, little or no software or hardware modifications would be needed in an existing system in order to add modules.

Recently proposed data processing systems that eliminate central control of the system bus use a feature referred to in the art as "broadcast packet switching". Broadcast packet switching means that when each subsystem desires to transmit a message, it transmits the message on the bus so that all subsystems "hear" or receive the message. The message, or "packet", includes a destination address so that only the addressed subsystem will act on the message.

One example of a system or network employing broadcast packet switching is the ETHERNET System, described in U.S. Patent No. 4,063,220, issued to Robert M. Metcalfe et al., and in Metcalfe & Boggs, Ethernet: 20 Distributed Packet Switching for Local Computer Networks, 7 Comm. of The ACM 395 (1976). In the ETHERNET System, a plurality of subsystems or stations are connected by taps along a coaxial cable bus, so that the message generated by any station is broadcasted in both direc-25 tions along the coaxial cable to all of the stations. In order to prevent message interference resulting from simultaneous transmission from two stations, the stations are operated so that they will not transmit if they detect a message already being transmitted on the bus. 30 Also, each station compares the message that it is transmitting with the message being carried on the bus, in order to detect interference resulting from two stations beginning their transmission simultaneously.

Another example of a system employing broadcast packet switching is the FIBERNET System, described in Rawson and Metcalfe, Fibernet: Multimode Optical Fibers

For Local Computer Networks, 26 IEEE Trans. on Comm. 93

(1978). In the FIBERNET System, a plurality of stations

or subsystems are each connected to an optical star coupler by a pair of optical transmission lines. One of each pair of transmission lines carries optical signals from the star coupler to a station, and the other of each pair of transmission lines carry signals from the station to the star coupler. When a signal is generated by any station, the signal is passed through the star coupler to all of the stations, including the station from which it came.

5

10

15

25

30

35

The use of a star coupler, such as contemplated in the FIBERNET System, does provide some advantages over the use of a single coaxial cable bus, such as that proposed for use in the ETHERNET System. For example, in the FIBERNET System, all messages pass through the star coupler before being received by any of the subsystems. Consequently, if two subsystems should transmit simultaneously, the two messages are combined at the star coupler and all subsystems receive the same combined and garbled message. In contrast, two inter-20 fering messages in the single bus ETHERNET System can combine differently at all points along the bus, and perhaps "look" like a valid message to one subsystem and an invalid message to another subsystem.

Furthermore, all messages in a system employing a centrally located star coupler, such as the FIBERNET System, are of the same strength or intensity, since all subsystems are located at approximately equal distances from the star coupler. In the FIBERNET System, in contrast to the ETHERNET System, there is little likelihood of the circumstance occurring where two messages interfere and are each invalid, but the messages are not sensed as invalid because of one message being much stronger than the other.

# Disclosure of the Invention

According to one aspect of the present invention, there is provided a data processing system having

10

15

20

25

30

35

a plurality of subsystems, a bus for carrying messages to be received by said subsystems, and a processor associated with at least one of said subsystems, characterized by: a mailbox memory associated with said one of said subsystems and having memory locations for storing message information from messages received by that one of said subsystems; and means for sequentially accessing the memory locations in said mailbox memory for storing message information from each received message as an entry in said mailbox memory, including means for pointing to the next entry following the entry of the last received message, so that message information of each received message may be stored in said mailbox memory without interrupting said processor.

According to another aspect of the present invention, there is provided a method for transferring a block of data between two subsystems linked by a system bus in a data processing system employing broadcast switching, each subsystem having a processor and a local memory, characterized by the steps of: providing a header-only message from one of the subsystems to the other of the subsystems, the header-only message requesting data from the other of the subsystems and having header information that includes a local memory address within the local memory of the one of the subsystems at which the requested data is to be stored; providing a header and data message from the other of the subsystems to the one of the subsystems, the header and data message having header information that includes the local memory address within the local memory of the one of the subsystems at which the requested data is to be stored, and a data portion that includes the requested data; storing the header information of the header and data message from the other of the subsystems in a mailbox portion of the local memory of the one of the subsystems, said mailbox portion being apart from the local memory address at which the requested data is to be stored; and

10

15

20

25

30

35

storing the requested data in the header and data message in the local memory of the one of the subsystems at the local memory address included in the header information stored in the mailbox portion.

It will be appreciated that a plurality of messages can be received by a subsystem and stored in the associated mailbox without processor interruption.

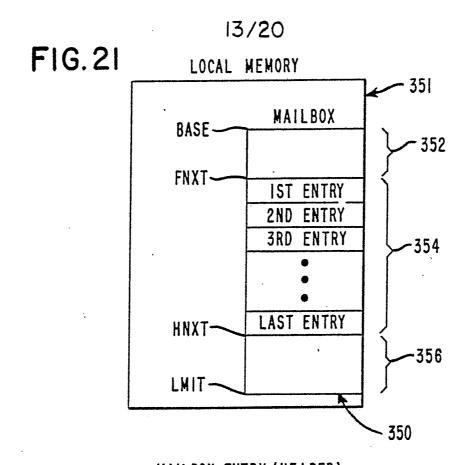

The mailbox memory may be a portion or section of a larger local memory of the subsystem, and the mailbox addressing circuitry may be part of DMA (direct memory access) circuitry that also sequentially accesses memory locations in the local memory in order to store blocks of data that may accompany the control information in a received message.

By storing the header information in the mailbox memory, and separately storing the blocks of data elsewhere in the local memory, the blocks of data may be stored at memory locations where they may be directly accessed by the processor during the execution of a task.

In a disclosed preferred embodiment, the data processing system includes a plurality of subsystems and a system bus linking the subsystems, with broadcast packet switching used for delivering messages over the system bus between the subsystems. The system bus includes an optical star coupler and pairs of optical transmission lines, each pair of transmission lines having plural ones of the subsystems coupled thereto and carrying signals to and from the star coupler. Each message carried over the system bus is either a headeronly message or a header and data message, with the header-only message having only header or control information, and with the header and data message having both header information and blocks of data. When data is requested by one of the subsystems from another of the subsystems, the requesting subsystem sends a header-only message that includes the address at which the requested

10

15

20

25

30

35

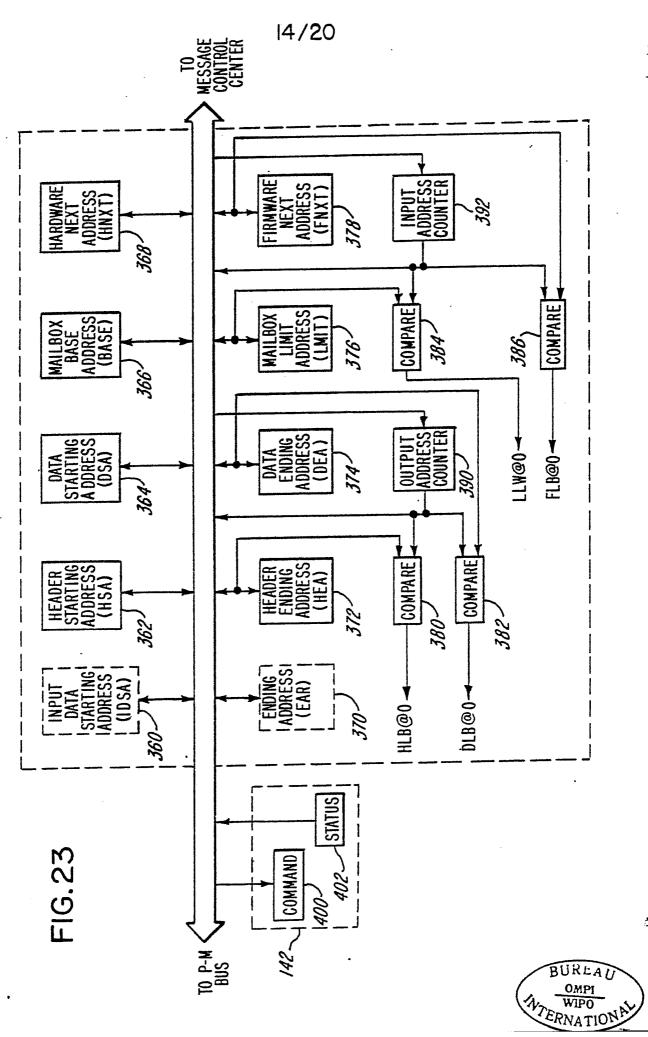

data is to be stored in the local memory of the requesting subsystem. This address, referred to as a data starting (DSA) address, is included in a header and data message that is returned with the requested data. The DSA address is included in the header information of the returning header and data message, and, after the header information has been stored as an entry in the mailbox, the DSA address is used by the DMA to begin storing the requested blocks of data at the memory location in the local memory specified by the DSA address.

A system bus interface couples each subsystem to the system bus and includes the DMA circuitry for storing both the blocks of data and the header information directly into the local memory. The DMA circuitry includes mailbox addressing circuitry that stores the parameters or limits of the mailbox, including an address defining the beginning memory location of the mailbox, an address defining the ending memory location of the mailbox, as well as the address of the first entry available in the mailbox to be accessed by the processor and the address following the last entry in the mailbox at which the next entry received is stored.

#### Brief Description of the Drawings

An embodiment of the present invention will now be described by way of example with reference to the accompanying drawings, in which:

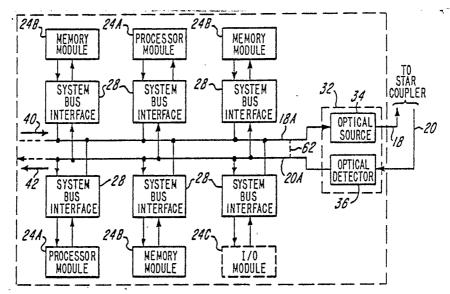

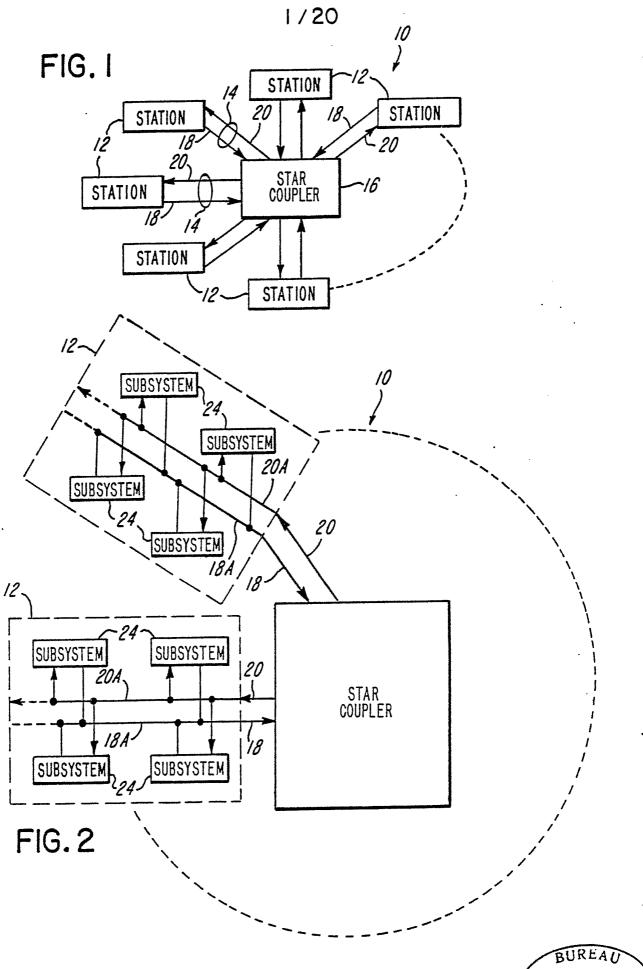

Fig. 1 is a simplified block diagram of a data processing system, including a star coupler and a plurality of stations, each station linked by a pair of transmission lines to the star coupler.

Fig. 2 is a simplified block diagram of the data processing system of Fig. 1, illustrating a plurality of subsystems at each station.

Fig. 3 is a simplified block diagram showing in greater detail a plurality of subsystems at one

10

15

20

25

station in the data processing system of Figs. 1 and 2, the subsystems including processor modules, memory modules and an I/O module each coupled to the pair of transmission lines from the star coupler.

Fig. 4 is a circuit diagram showing the bus driver circuit and bus receiver circuit connecting each system bus interface to the system bus.

Fig. 5 is a block diagram of a passive optical star coupler that could be employed in the data processing system of Figs. 1 and 2.

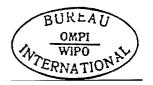

Fig. 6 is a simplified block diagram of an active optical star coupler that could be employed in the data processing system of Figs. 1 and 2.

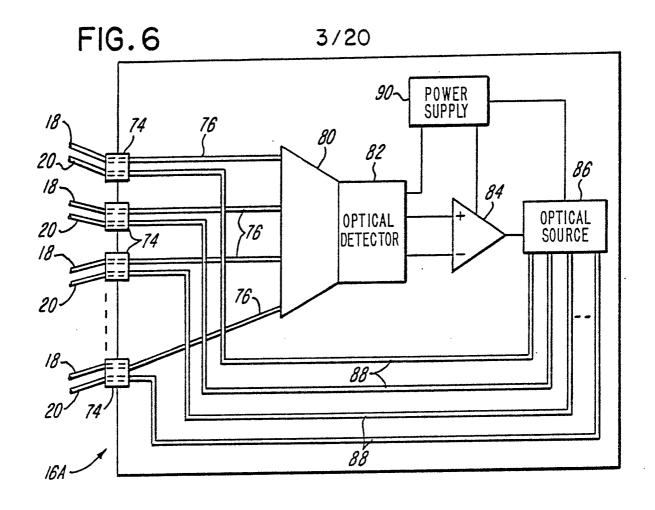

Fig. 7 is a simplified block diagram of an electrical star coupler that could be employed in the data processing system of Figs. 1 and 2.

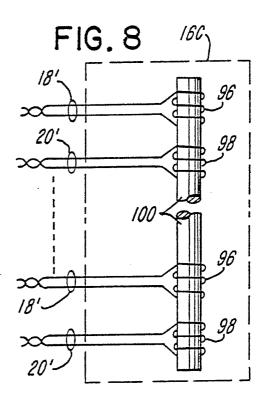

Fig. 8 is a simplified block diagram of a magnetic star coupler that could be employed in the data processing system of Figs. 1 and 2.

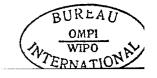

Fig. 9 is a simplified block diagram illustrating one of the processor modules shown in Fig. 3.

Fig. 10 is a simplified block diagram illustrating one of the memory modules shown in Fig. 3.

Fig. 11 is a simplified block diagram illustrating the I/O module shown in Fig. 3.

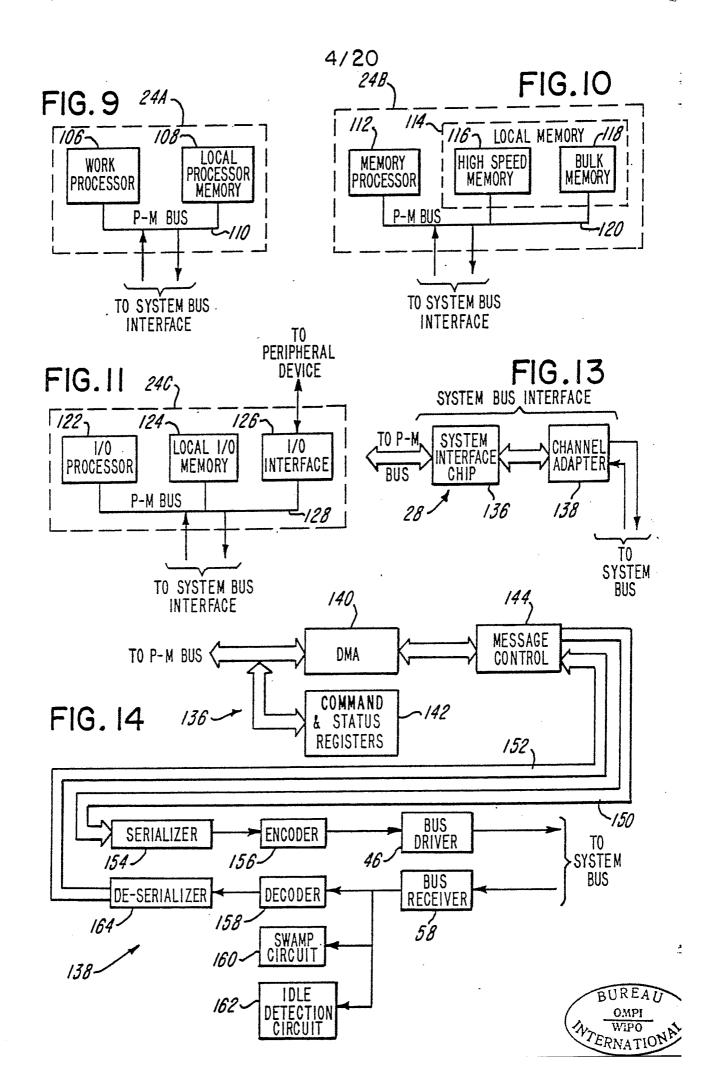

Figs. 12A and 12B illustrate the format of messages transmitted by subsystems in the data processing system of Figs. 1 and 2.

Fig. 13 is a simplified block diagram of the system bus interface shown connecting each subsystem or module to the system bus in Fig. 3.

Fig. 14 is a block diagram illustrating in greater detail the circuitry within the system bus interface shown in Fig. 13.

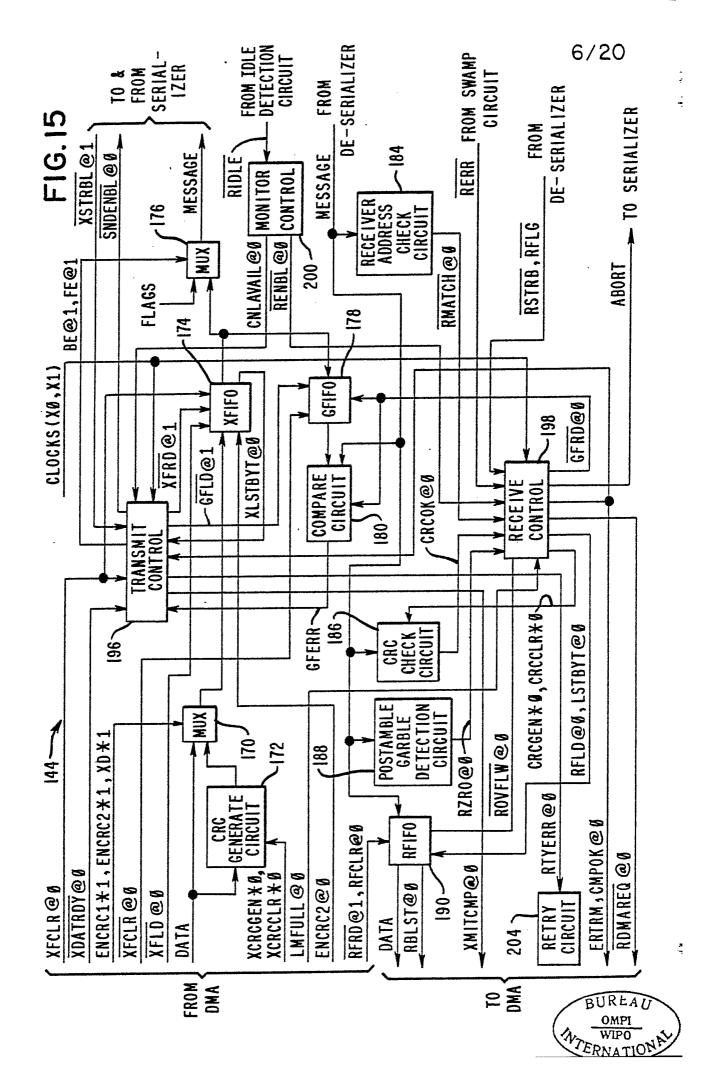

Fig. 15 is a detailed block diagram of the message control circuit shown in the system bus interface of Fig. 14.

WO 82/03711 PCT/US82/00455

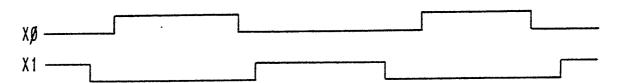

Fig. 16 shows waveforms illustrating the nature of the clock signals X0 and X1.

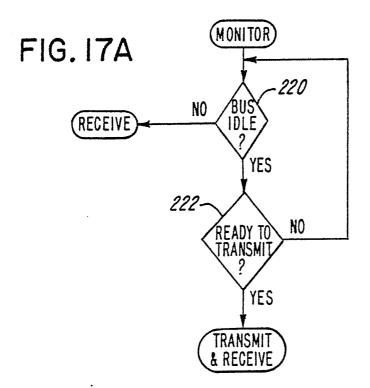

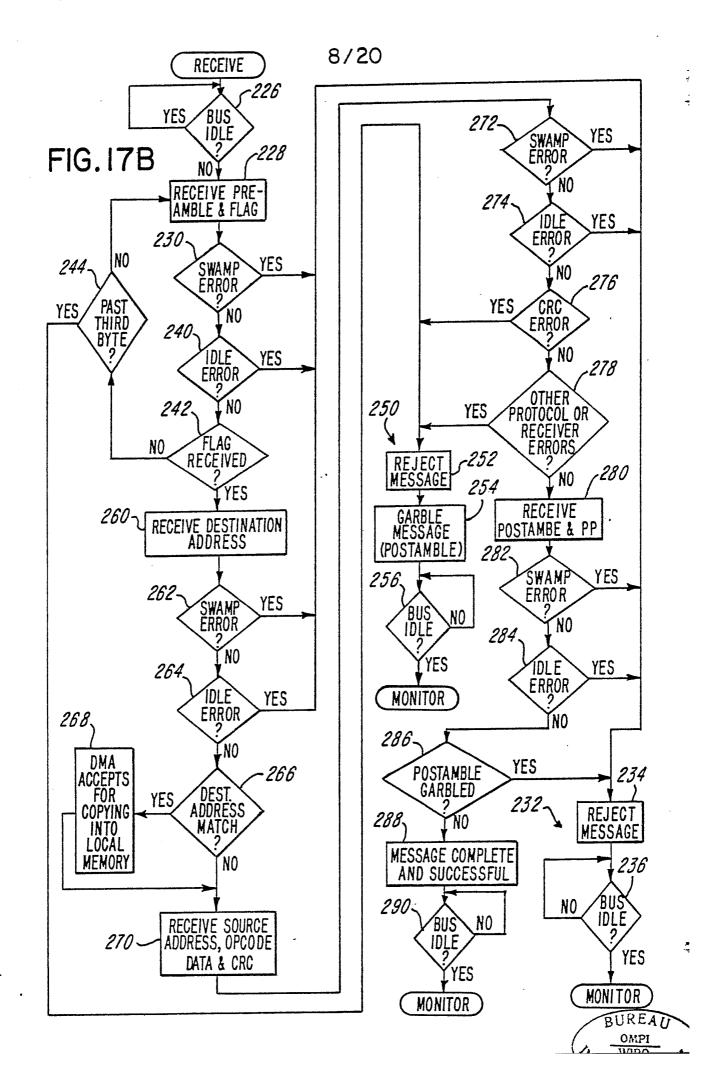

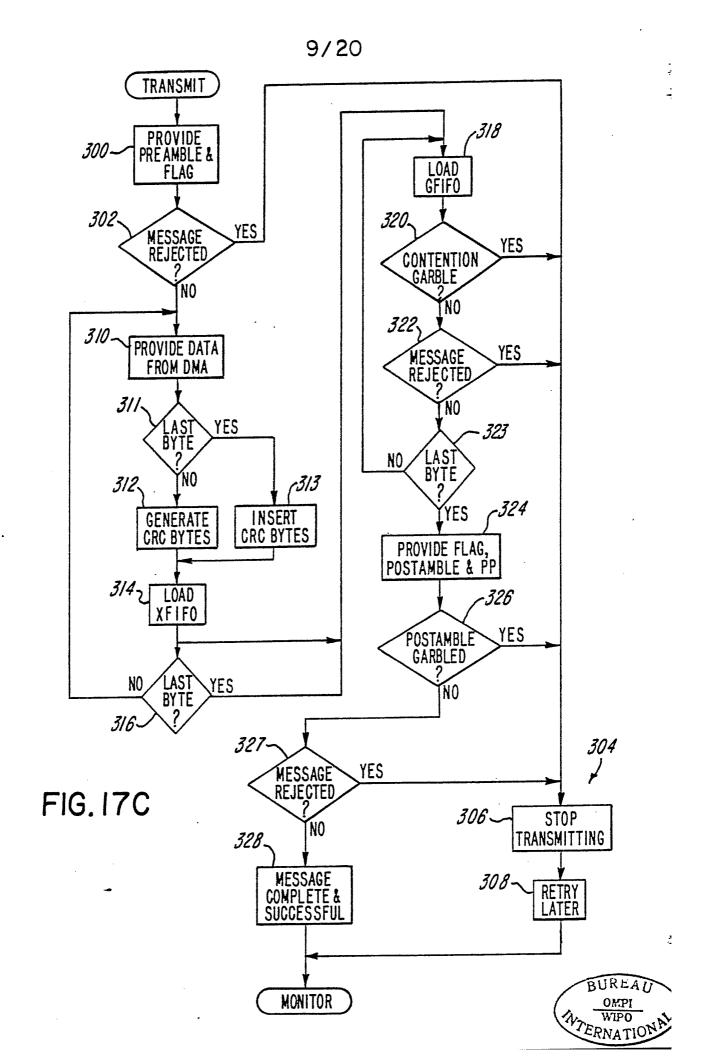

Figs. 17A, 17B and 17C are flow diagrams illustrating the general operation of the system bus interface of Fig. 14.

5

10

15

20

25

35

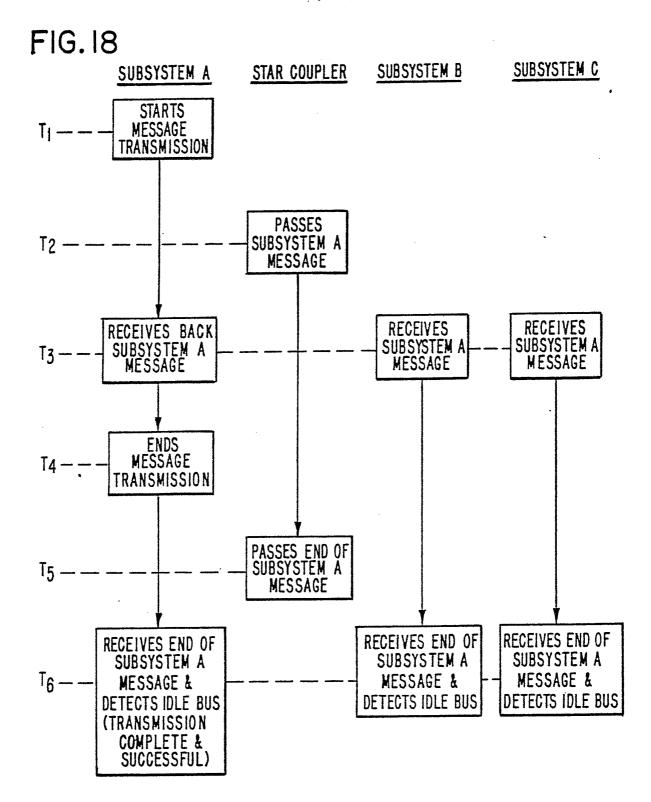

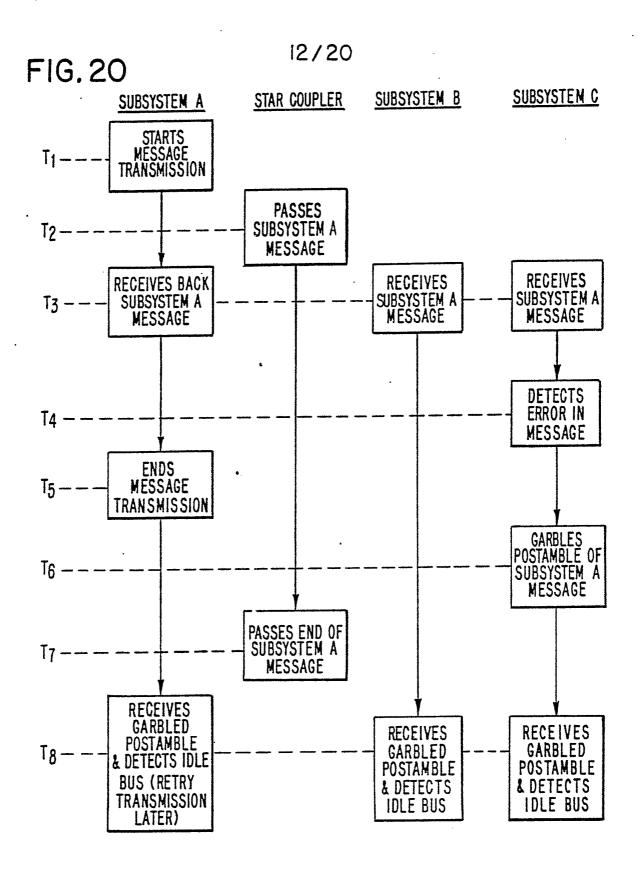

Figs. 18, 19 and 20 illustrate three exemplary cases in which messages are transmitted in the data processing system of Figs. 1 and 2.

Fig. 21 illustrates the content of the local memory in each of the subsystems.

Figs. 22A and 22B illustrate the format of mailbox entries in the local memory shown in Fig. 21.

Fig. 23 is a block diagram illustrating in greater detail the DMA and the control and status registers shown in Fig. 14.

Fig. 24 illustrates the content of the command register shown in Fig. 23.

Fig. 25 illustrates the content of the status register shown in Fig. 23.

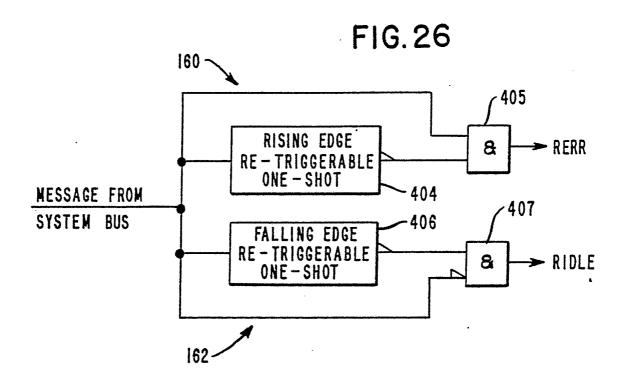

Fig. 26 is a detailed block diagram of the swamp circuit and the idle detection circuit shown in the system bus interface of Fig. 14.

Fig. 27 is a simplified block diagram illustrating an alternate embodiment of a data processing system.

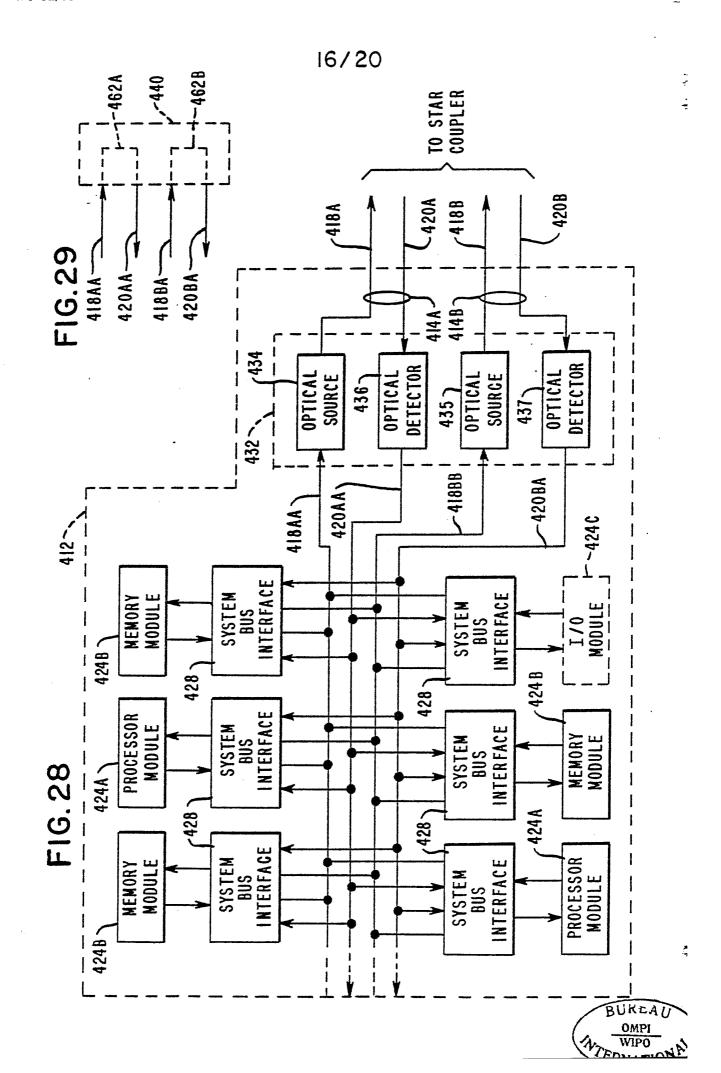

Fig. 28 is a simplified block diagram showing in greater detail a plurality of subsystems within one of the stations in the data processing system of Fig. 27.

Fig. 29 illustrates a wiring pattern for providing electrical turn around paths in the station of Fig. 28.

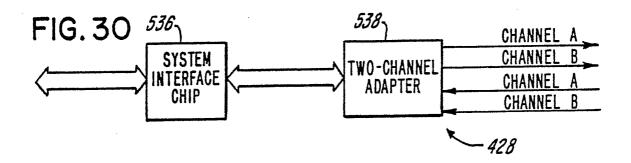

Fig. 30 is a simplified block diagram of the system bus interface shown connecting each subsystem or module to the dual-channel system bus in Fig. 28.

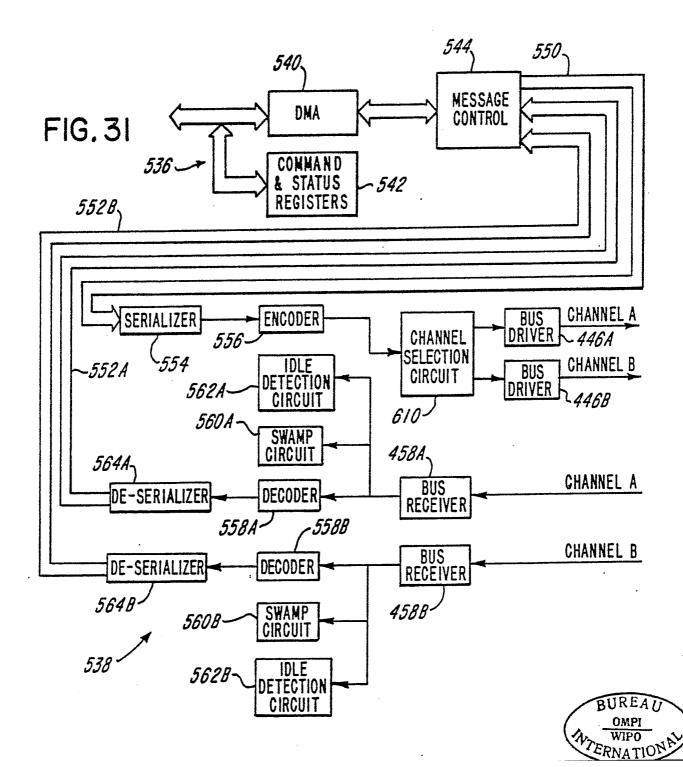

Fig. 31 is a block diagram illustrating in greater detail the circuitry within the system bus interface shown in Fig. 30.

10

15

20

25

30

35

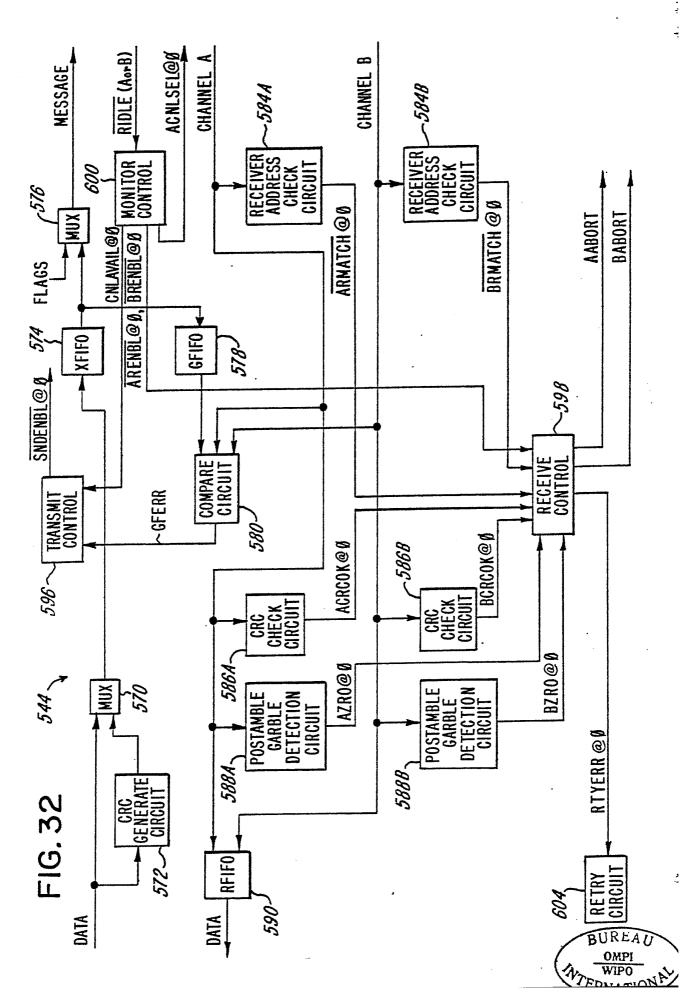

Fig. 32 is a detailed block diagram of the message control circuit shown in the system bus interface of Fig. 31.

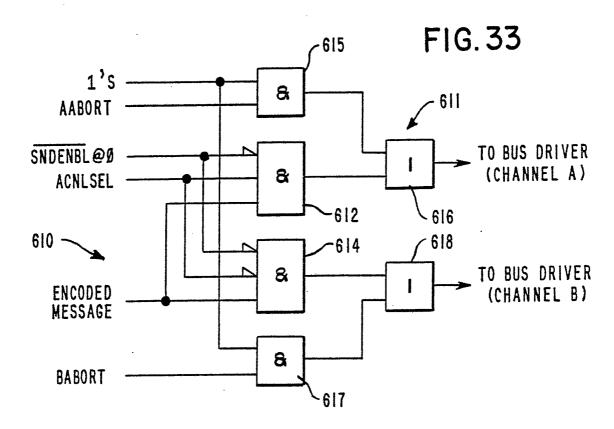

Fig. 33 is a block diagram illustrating the circuitry within the channel selection circuit shown in the system bus interface in Fig. 31.

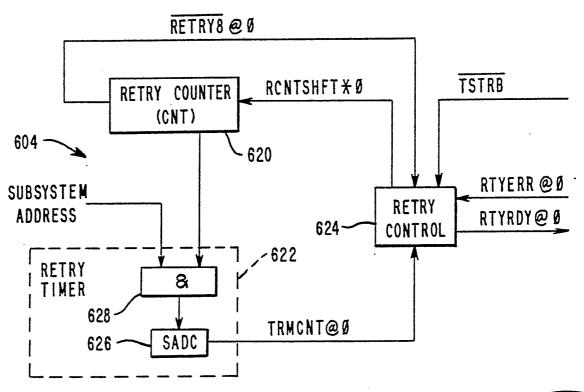

Fig. 34 is a simplified block diagram of a retry circuit for use in the message control circuit of the system bus interface in Fig. 31.

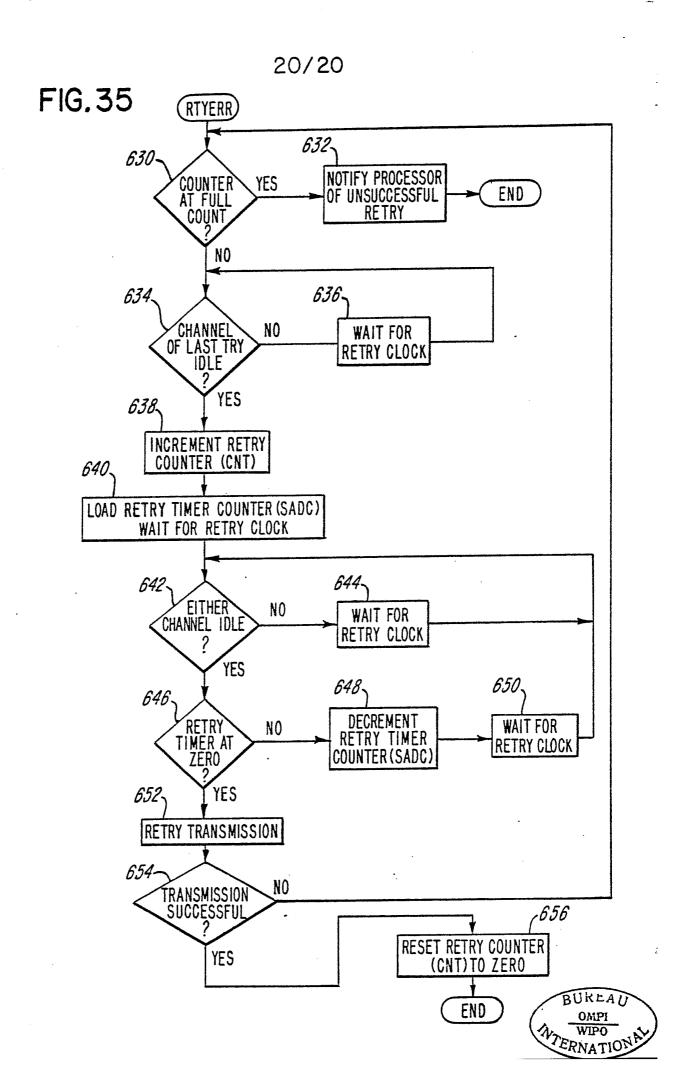

Fig. 35 is a flow diagram illustrating the operation of the retry circuit shown in Fig. 33.

# Best Mode for Carrying Out the Invention

# A. DATA PROCESSING SYSTEM 10 (GENERAL)

Referring now to Fig. 1, there is shown in general and simplified form a data processing system 10. The data processing system 10 is comprised of a plurality of stations 12, each of which is linked by an associated cable 14 to a central star coupler 16. Each cable 14 comprises a first transmission line 18 and a second transmission line 20. As is conventional in systems employing star couplers, the star coupler 16 receives a signal generated or transmitted at any one of the stations from the first transmission line 18 associated with that one of the stations. The star coupler then directs that signal to all of the second transmission lines 20 for transmission to all of the stations, including the station that generated the signal.

As will be more fully described later, it is contemplated that in the actual practice of the present invention each of the stations 12 includes data processing equipment located within a single cabinet. Therefore, if the data processing system 10 were viewed in its actual physical form, one would see a plurality of cabinets, each for housing data processing equipment, and a centrally located cabinet for housing the star

10

15

20

25

35

coupler 16, with the star coupler 16 connected to each of the cabinets by the cables 14.

It should be noted that, for reasons which will become apparent later, the data processing system 10 in its preferred form is a local network, i.e., the stations 12 are not separated by long distances. Accordingly, each of the cables 14 is no longer than, say, 300 feet (approximately 91 meters), with all of the stations probably located within a single building and considered, for all practical purposes, a single "computer system".

It should be further noted that the star coupler 16, in its preferred form, is an optical star coupler. Accordingly, optical signals are generated at each of the stations 12 and are carried along the first transmission lines 18 to the star coupler 16. coupler 16, in turn, directs those optical signals back to all of the stations 12 along the second transmission lines 20. The first and second transmission lines 18 and 20 could each comprise a single optical fiber, suitably wrapped and packaged together to form the cable 14.

Referring now to Fig. 2, there is shown in greater detail the data processing system 10 in accordance with one aspect of the present invention. As seen in Fig. 2, each of the stations 12 include a plurality of subsystems 24, with the subsystems 24 at each station enclosed by broken lines in the drawings to indicate their physical enclosure within a cabinet. Each first transmission line 18 has an associated internal trans-30 . mission line 18A within the cabinet or station 12, and each second transmission line 20 has an associated internal transmission line 20A within the cabinet or station 12. Each of the subsystems 24 is connected to the internal transmission lines 18A and 20A so that each subsystem transmits messages along the internal transmission line 18A and receives messages along the internal transmission line 20A.

10

15

20

25

In a preferred form of the present invention, the transmission lines 18A and 20A are each formed by a coaxial electrical line or cable and carry electrical signals, which are converted into or from optical signals at the transmission lines 18 and 20 by an optical interface (not shown in Fig. 2). In addition, each of the subsystems 24, as will be more fully described later, is coupled or tapped into the internal electrical transmission lines 18A and 20A without disrupting the connection of any other subsystem to the transmission lines 18A and 20A. The data processing system 10 can thus be seen as providing the advantages of a readily expandable electrical system, since subsystems within each station 12 may be added along the internal transmission lines 18A and 20A.

Since the message or information packet sent by any one of the subsystems 24 is broadcasted to all of the subsystems 24, there is no selection or control of paths to route a message packet from one subsystem 24 to another subsystem 24. Accordingly, for purposes of transmitting or receiving message packets, the subsystems 24 operate as if all the pairs of first and second internal transmission lines 18A and 20A, all the first and second transmission lines 18 and 20, and the star coupler 16 were, collectively, a single bus. This ostensible single bus, for purposes of describing the present invention, is hereinafter referred to as the "System Bus".

In Fig. 3, there is shown in greater detail

the subsystems within the cabinet of one of the stations

12. As can be seen, the subsystems are shown as processor modules 24A, memory modules 24B, and an I/O module

24C. Each of the processor modules 24A, memory modules

24B and I/O module 24C is connected to the internal

transmission lines 18A and 20A through a system bus

interface 28. Each system bus interface 28, as will be

described in greater detail later in conjunction with

WO 82/03711 PCT/US82/00455

5

10

15

20

25

30

35

Figs. 13 through 17C, includes circuitry for encoding messages transmitted on the System Bus, for adding preambles, postambles, flags and CRC bits to messages transmitted on the System Bus, for decoding messages received from the System Bus, for checking received messages for errors, for monitoring the System Bus for an idle condition before its associated subsystem 24 can transmit, for comparing any message transmitted by its associated subsystem with the messages received to determine if a message from another module is interfering with its transmitted message, and for performing DMA (direct memory access) functions so that data can be read from or written into the local memory of the associated subsystem without repeated processor commands.

The system bus interface 28 associated with each processor module 24A, memory module 24B and I/O module 24C is connected to each of the internal transmission lines 18A and 20A by circuitry and T-couplers that will be described in detail later in connection with Fig. 4. The internal transmission lines 18A and 20A are in turn coupled or connected to the external optical transmission lines 18 and 20 by an optical interface circuit 32 which, as seen in Fig. 3, includes an optical source 34 and an optical detector 36.

Still referring to Fig. 3, the internal transmission line 18A is connected to each of the processor, memory and I/O modules for carrying messages in one direction, which is illustrated by an arrow 40 that is pointing toward the right as viewed in Fig. 3. The internal transmission line 20A, on the other hand, is connected to each of the processor, memory and I/O modules for carrying signals in an opposite direction, which is illustrated by an arrow 42 that is pointing toward the left as viewed in Fig. 3. The messages carried on internal transmission line 18A are in the form of electrical signals and are converted by the optical source 34 to optical signals and are passed to the

optical transmission line 18, which in turn carries the optical signals to the optical star coupler 16. The optical star coupler 16, in turn, directs the optical signals received from any one of the optical transmission lines 18 to every optical transmission line 20, including the one returning to the cabinet or station 12 that generated the message. As seen in Fig. 3, the optical signals on the transmission line 20 are received at the optical detector 36 at each cabinet or station 12 and are converted into electrical signals that are passed to the internal transmission line 20A. All of the processor, memory and I/O modules receive the message or signals that are passed along the internal transmission line 20A, including any one of the modules that may at that very moment be transmitting the same message.

5

10

15

20

25

30

35

In an alternate form of the present invention the internal transmission lines 18A and 20A could be connected directly to, or even formed integrally with, the external lines 18 and 20, respectively. That is, for example, the internal transmission line 18A could be an optical line and an integral end section of the external optical transmission line 18, and the internal transmission line 20A could be an optical line and an integral end section of the external optical transmission line 20. In such a case, there would be no optical interface 32 and each system bus interface 28 would be connected to the internal transmission lines 18A and 20A by a suitable optical T-coupler.

However, the use of the electrical lines 18A and 20A in the system 10 as shown in Figs. 1 through 3 is preferred because they may be implemented with low-cost electrical coaxial cables and T-connectors. The electrical conductors are adequately shielded within the cabinet or station 12 from radio frequency interference (RFI) and electromagnetic interference (EMI). Away from each of the stations 12, the optical transmission lines 18 and 20 are preferred since they will not be subjected to RFI and EMI by virtue of their being optical fibers.

BUKEAT

10

15

20

25

35

#### B. BUS DRIVER CIRCUIT 46 & BUS RECEIVER 58

In Fig. 4 there is illustrated the circuitry within each system bus interface 28 that physically and electrically connects the system bus interface to the internal transmission lines 18A and 20A. As shown, the message transmitted by any one of the modules or subsystems 24 is passed within the system bus interface 28 to a bus driver circuit 46. The bus driver circuit 46 includes a Schottky TTL driver 48 that has its output connected to the transmission line 18A by way of a transistor 50. The emitter of the transistor 50 is physically connected to the line 18A by a suitable conventional coaxial T-coupler 52. The collector of transistor 50 is connected to a voltage source +V, and a resistor 54 is connected between the voltage source +V and the base of transistor 50. Although signals placed on the transmission line 18A will tend to propagate in both directions, only those signals traveling in the direction of arrow 40 (Figs. 3 and 4) will be converted into optical signals at the optical interface 32 (Fig. 3) and be passed to the star coupler 16.

Referring still to Fig. 4, signals traveling in the direction of arrow 42 from the optical detector 36 (Fig. 3) along the transmission line 20A are passed, by way of a coaxial T-coupler 56, to a bus receiver circuit that includes a TTL line receiver 58. The message received by the receiver 58, after passing through the system bus interface 28, is provided to its associated module 24A, 24B or 24C.

#### 30 C. STAR COUPLERS 16, 16A, 16B & 16C

It should be apparent from the description thus far that the data processing system 10 is readily expandable even though the stations 12 are linked by the star coupler 16. The internal transmission lines 18A and 20A within the cabinets at each station 12 may be nondestructively tapped into by the T-couplers 52 and

15

20

25

30

35

56. Accordingly, the number of processor modules 24A, memory modules 24B, or I/O modules 24C that may be added is theoretically unlimited (providing there is unlimited bus capacity), as long as sufficient volume is provided within each cabinet for positioning the modules.

Since it is contemplated that the data processing system 10 can be expanded as processing or memory requirements increase, it could well be that the system 10 comprises, for a user initially needing only small computer capability, a single one of the cabinets or stations 12. In such a case, as processing and memory needs increase, the user would first add additional subsystems 24 at a single station. Then, as needs further increase, the user would employ the star coupler 16 in order to link plural stations or cabinets. the case where only one station or cabinet is needed initially, the return path of the System Bus to that station formed by external transmission line 18, star coupler 16, and external transmission line 20 could be replaced by a single connecting transmission line 62, seen as a broken line in Fig. 3. The connecting transmission line 62 would comprise a coaxial electrical line and would provide an electrical path between the internal transmission line 18A and the internal transmission When the connecting line 62 is in place, and if any one of the modules 24A, 24B or 24C within the station 12 of Fig. 3 transmits a message, the message is carried down line 18A, across connecting line 62, and then back along line 20A to each of the modules. optical interface 32 is, of course, not needed when the connecting line 62 is used.

Referring now to Fig. 5 there is shown in greater detail the star coupler 16 in one preferred form. The star coupler 16 is a passive star coupler, meaning that it does not amplify or regenerate any of the optical signals it receives. As seen in Fig. 5, the star coupler 16 includes a mixing element or rod 64

10

15

20

25

30

35

comprising a cylindrical glass core, with the fibers that each make up one of the external transmission lines 18 (Figs. 1, 2 and 3) having ends terminating at one end face 66 of the mixing rod. The optical fibers that each make up one of the external transmission lines 20 (Figs. 1, 2 and 3) have ends terminating at an opposite end face 68 of the mixing rod 64. As conventional, the star coupler 16 is constructed so that the fibers of the transmission lines 18 and 20 are optically matched with the mixing rod 64 at the end faces 66 and 68.

When an optical signal is passed from any one of the transmission lines 18 to the mixing rod 64 at the end face 66, it is distributed uniformly across the opposite end face 68 of the mixing rod, and is then passed to each one of the transmission lines 20.

A commercially available passive star coupler that performs the functions of the star coupler 16 as shown in Fig. 5 could, for example, be the sixteen-port star coupler, product No. SPX3720, sold by Spectronics Incorporated, Richardson, Texas.

In circumstances where the data processing system 10 might use optical transmission lines of sufficient length to warrant the use of an active star coupler, an alternate star coupler 16A shown in Fig. 6 would be more suitable. The active star coupler 16A amplifies the optical signals received from any one of the stations 12 by way of one of the transmission lines 18, and then passes the amplified optical signals back to all of the stations 12 by way of the transmission lines 20. As seen in Fig. 6, each pair of the transmission lines 18 and 20 that is associated with each station 12 is connected to the star coupler 16A by an optical coupler 74. The signals received from any one of the transmission lines 18 is passed through the coupler 74 to an optical fiber 76. The signals on each fiber 76 are in turn passed to a tapered waveguide 80, which directs the optical signals to an optical detector

10

15

20

25

30

35

82. The optical detector 82 converts the optical signals to electrical signals, which are then amplified by an electrical amplifier 84. The amplified electrical signals are presented to an optical source 86, which includes suitable source driver circuitry and an optical interface, in order to provide amplified optical signals to a plurality of optical fibers 88. Each of the fibers 88 is coupled to one of the transmission lines 20 at the couplers 74, in order to return the amplified optical signals to each of the stations 12. A power supply 90 provides sufficient operating voltages to the optical detector 82, amplifier 84, and optical source 86. For a more detailed description of an active optical star coupler, such as the star coupler 16A in Fig. 6, reference can be had to U. S. Patent No. 4,234,968, issued to Amar J. Singh.

While in the preferred embodiment the star coupler 16 in the data processing 10 is an optical star coupler, and the transmission lines 18 and 20 connecting each of the stations 12 to the star coupler are optical fibers or lines, it should be appreciated that other forms of star couplers may be used within the scope of the present invention. In Fig. 7, there is shown an electrical star coupler 16B that includes circuitry for receiving and passing electrical signals at the star coupler and that could alternatively be used in the data processing system 10.

As illustrated in Fig. 7, pairs of external transmission lines 18' and 20' link the stations 12 and the star coupler 16B, with each of the lines 18' and 20' comprising a twisted pair of electrical conductors rather than an optical fiber as used in the previously described preferred embodiments. The conductors of each transmission line 18' carry electrical signals from one of the stations 12 and are connected to the input terminals of a single output line receiver 90. The conductors of each transmission line 20' carry electrical

10

15

20

25

30

35

19.F

signals from the star coupler 16B back to one of the stations 12 and are connected to the output terminals of a single input line driver 92. The output of each receiver 90 and the input of each driver 92 are connected to a common electrical line 94. Accordingly, when a signal is received by one of the receivers 90 from any one of the transmission lines 18', the signal is provided, by way of the common line 94, to each of the drivers 92. The drivers 92 supply the signal from the common line 94 to each of the transmission lines 20', which then return the signal to all of the stations 12. The receivers 90 may each be implemented by a Line Receiver Circuit No. 10115 and the drivers 92 may each be implemented by an OR-NOR Circuit No. 10101, both available from Signetics, Inc., Sunnyvale, California. The star coupler 16B may also include a conventional power supply (not shown), for supplying suitable operating voltages to each of the receivers 90 and drivers 92.

In Fig. 8, there is shown a magnetic star coupler 16C that could also be alternatively used in the data processing system 10. The external transmission lines 18' and 20' can again each comprise a pair of twisted electrical conductors, with each of the transmission lines 18' and 20' formed into coils 96 and 98, respectively, along a core or rod 100. The coils 96 are wound oppositely relative to the coils 98. The rod 100 is made of a suitable ferromagnetic material, such as ferrite, so that when an electrical signal is received from any one of the transmission lines 18', a change in magnetic flux is induced in the rod 100 and a corresponding signal is provided to each of the transmission lines 20'. The star coupler 16C could be located within a suitably shielded cabinet but, unlike the electrical star coupler 16B in Fig. 7, it is passive and requires no power supply.

10

15

20

25

30

35

# D. MODULES 24A, 24B & 24C

Referring again briefly to Fig. 3, it has earlier been noted that the ability to add the memory modules 24A and the processor modules 24B along the internal transmission lines 18A and 20A within each station 12 permits the system 10 to have either its memory capacity or processing capacity increased at will. It is envisioned that the processor modules 24A, memory modules 24B and I/O modules 24C are self-contained, with much of the circuitry of each fabricated on one or a few VLSI (very large-scale integration) chips. of the modules has its own processor and a local memory storing data to be processed by its processor. contrast to traditional systems, however, the data processing system 10 of Fig. 1 has no single processor that both performs normal processing tasks and also controls the operation of the memories or peripheral devices. Rather, each memory module 24B has sufficient processing capability to manage the memory operations in its own module, and manage those memory operations independently of any one of the processing modules 24A. In addition, each of the processor modules 24A contains a sufficient amount of memory that is not shared with any other module, so that the processor module will not need to frequently access any of the memory modules.

Of course, the data processing system 10 requires suitable data entry and data output points, which are provided by each of the I/O modules 24C. Each I/O module 24C, as will be described in greater detail below, is connected to a peripheral device and includes the necessary processing and memory capability to manage the transfer of data between the peripheral device and one of the processor modules 24A or memory modules 24B.

Figs. 9, 10 and 11 show in greater detail the structure of each processor module 24A, memory module 24B, and I/O module 24C, respectively.

10

15

20

25

30

35

#### 1. PROCESSOR MODULE 24A

Referring first to Fig. 9, it can be seen that the processor module 24A includes a work processor 106 and a local processor memory 108. The work processor 106 and the local memory 108 are connected by an internal processor-memory (P-M) bus 110 so that, as conventional, the work processor may read software instructions from addressable memory locations in the local memory 108 and read data from or write data into the addressable memory locations in the local memory 108. The term "work processor" is used to refer to the processor 106 because the processor 106 performs the actual execution of software programs and steps to complete jobs or tasks provided to the data processing system 10. While the work processor 106 does perform some memory management operations relating to its associated local memory 108, it does not control the memory operations performed within any of the memory modules 24B, other than merely to request or provide data to the memory modules 24B.

The local memory 108 may be a suitable high access-speed memory, such as commonly found in processor cache memories, so that software and data in the local memory may be quickly provided when needed for use by the work processor 106. However, the local memory 108 is also sufficiently large, in fact, larger than traditional cache memories, so that data normally needed by the work processor to complete any given job or task resides largely in the local memory 108. Only when the processor module 24A needs a large block of data, must the work processor 106 send a request to one of the memory modules 24B or to one of the I/O modules 24C for As a result, the System Bus which interconnects all of the processor modules 24A and memory modules 24B is not crowded with excessive numbers of data requests. Rather, each work processor will frequently be able to find the data it needs in order to complete a task within its own local memory 108. When the work processor

10

15

20

25

30

35

106 does need a block of data that is only stored in one of the memory modules 24B or must come from a peripheral device through one of the I/O modules 24C, it broadcasts the request. The request is placed on the System Bus in the form of a message that includes the address or identification of the module that has the needed data (as well as the module that is requesting the data), so that the addressed module can receive and act on the request.

### 2. MEMORY MODULE 24B

In Fig. 10 the memory module 24B is shown as including a memory processor 112 and a local memory 114, with the local memory 114 including a high speed memory 116 and a large-capacity bulk memory 118. The memory processor 112 is connected to the high speed memory 116 and to the bulk memory 118 by an internal processormemory (P-M) bus 120 so that, in response to requests from any one of the processor modules 24A, the memory processor 112 can access data stored in either the high speed memory 116 or the bulk memory 118. The high-speed memory and bulk memory are arranged in a conventional, hierarchial configuration, with the high speed memory 116 being a fast access RAM and the bulk memory 118 being, for example, a magnetic disk having a sloweraccess speed but a considerably larger storage capacity than the high-speed memory 116. The memory processor 112, as will be described below, performs a number of memory management operations, one of which includes the transfer of data between the high speed memory 116 and the bulk memory 118.

The memory processor 112 is microprogrammed to perform many memory operations that in more traditional data processing systems would be performed by a central work processor. By performing these operations in the memory processor 112, the need for requests or commands between the processor modules 24A and the memory modules

WO 82/03711 PCT/US82/00455

-22-

24B is vastly reduced, thereby making the processor modules 24A and memory modules 24B less dependent on communications with each other and, in turn, making the data processing system 10 readily expandable with minimal effect on the software in accordance with which the work processors 106 are operating.

The types of memory operations performed by the memory processor 112 can include the following:

(1) receiving and operating on read requests,write requests, and other memory access operations;

- (2) exercising ownership control, so that if data is accessed by one processor module 24A, that data can be made inaccessable to any other processor module 24A;

- (3) performing global claim management functions, to avoid two processor modules 24A being placed in deadlock because each desires data that only the other has access to;

- (4) performing queue management functions, by maintaining lists or queues of messages that are stored in the memory module and that are being sent to and from programs executing in the various processor modules 24A, so that as each program is free to take a message, it takes or acts on the message at the top of the queue containing messages directed to it;

- (5) performing time-of-day services to permit start and end times to be given to each job acted on by one of the processor modules 24A;

- (6) duplicating certain files of data using independent memory modules so that if damage is done to a file or block of data or to a memory module, and the data is critical, the duplicate files may then be accessed by the processor modules;

- (7) transferring data between the high-speed memory 116 and the low access-speed bulk memory 118 within the memory modules; and

35

30 -

5

10

15

20

25

10

15

20

25

30

35

(8) managing and allocating space within the bulk memory such that the processor modules need know nothing about the physical placement of related data.

#### 3. I/O MODULE 24C

In Fig. 11, the I/O module 24C is shown in greater detail. The illustrated I/O module 24C includes an I/O processor 122, a local I/O memory 124, and I/O interface circuitry 126. The I/O processor 122 is connected to the local I/O memory 124 and the I/O interface circuitry 126 by an internal processor-memory (P-M) bus 128. The I/O interface circuitry 126 is connected to a peripheral device, such as a keyboard, CRT display, printer, magnetic tape unit, or the like.

Data may either be transferred into or out of the system 10 at the I/O module 24C. If either a processor module 24A or a memory module 24B needs data from a peripheral device, a message, having the destination address of the I/O module 24C connected to the peripheral device, is transmitted over the System Bus and is stored in the local I/O memory 124. The I/O processor 122 will use the message stored in the local I/O memory 124 to generate specific commands for obtaining data, such commands passing through the I/O interface circuitry 126 to the peripheral device. Data is returned by the peripheral device and is stored in the local I/O memory until the I/O processor 122 formulates a message that will include the data. The message is transmitted or broadcasted on the System Bus and has the destination address of the module that requested the data.

Of course, in other circumstances the peripheral device itself may initiate the transfer of data. In such circumstances, the peripheral device loads the local I/O memory 124 with the data and, in response, the I/O processor 122 will send a message, including the data, to a selected memory or processor module.

10

20

30

35

While not shown in the drawings, any one of the modules 24A, 24B or 24C could be connected to more than one System Bus by, for example, connecting a completely independent second System Bus to the P-M bus of the module by way of a separate second system bus interface (not shown). Furthermore, any one of the modules could be connected, by way of an additional system bus interface (not shown), to an additional single bus that could be used solely for transferring messages between that module and one other module. While not part of the present invention, such a connection might be useful when two subsystems or modules have a disproportionate need for communicating with each other and would otherwise require the use of the System Bus.

#### 15 E. MESSAGE FORMATS

In Figs. 12A and 12B there is shown the format of messages that are transmitted from any one of the modules or subsystems 24 along the System Bus to another one of the subsystems 24. Each message is shown in the drawings as having a number of fields, with the number of bytes in each field shown in parentheses above the field. As can be seen in Figs. 12A and 12B, the message can be one of two types:

- (1) a header-only message; or

- 25 (2) a header and data message.

For reasons which will become apparent later, each message is always preceded and followed by an idle condition of the System Bus.

A header-only message is a message sent from one subsystem to another when the message only contains control information, such as a data or service request, information relating to status, or a limited amount of data information. On the other hand, a header and data message is a message sent from one subsystem to another which includes header control information and accompanying blocks of data to be stored in the local memory of

10

25

30

35

the destination subsystem. Messages that are generally of the type referred to herein as "header-only" or "header and data" type are well known to those skilled in the art, and the general manner in which such messages cause the individual subsystems 24 to ultimately operate forms no part of the present invention and will not be described in detail herein.

Referring now in particular to Fig. 12A, it can be seen that the header-only message has ten fields in the following order:

- (1) preamble

- (2) first single flag

- (3) destination address

- (4) source address

- 15 (5) op code

- (6) optional header data

- (7) cyclical redundancy code (CRC)

- (8) second single flag

- (9) postamble

- 20 (10.) post-postamble (PP).

The preamble in the header-only message indicates to all receiving subsystems that a message is beginning. The preamble only occurs after the transmitting subsystem detects an idle condition on the System Bus. The preamble consists, for example, of two flag characters. In the preferred form of the present invention, it is contemplated that each flag character consists of one byte (eight bits) as follows:

#### 01111110

After the generation of the preamble, a single flag character is generated and then two one-byte destination addresses that indicate to each of the subsystems the address or addresses of the intended destination of the message. As will be more fully described later, the system bus interface 28 associated with each subsystem 24 includes circuitry for recognizing the unique address

25

30

35

of its associated subsystem or the group address of a group of subsystems that includes its associated subsystem.

In a preferred form of the present invention, it is contemplated that, in addition to a unique one-byte address associated with each of the subsystems 24, there are several one-byte group addresses that include the following:

- memory module group address;

- 10 (2) application or work processor module group address;

- (3) I/O processor module group address; and

- (4) data base processor module group address. Other available group addresses can be assigned as needed.

When the destination address field has an address representing the memory module group address, all memory modules within the data processing system 10 are destination subsystems, and all will receive and act on the transmitted message if the message is successfully transmitted. Similarly, if the destination field contains the work processor module group address, all processor modules within the system 10 that perform user or application tasks will receive and act on the message. If the destination field contains the I/O processor module group address, all processors within the system that perform input/output functions will receive and act on the message. Finally, if the destination field contains the data base processor module group address, all processor modules within the data processing system 10 that perform data base functions will copy and act on the transmitted message. A data base processor module is similar to the memory module, but may include the necessary programming to perform some processing functions on its stored data, such as merge, sort, or the like.

Since the destination address field is two bytes wide, it can include two unique subsystem addres-

10

15

20

25

30

35

ses, two group addresses, or one subsystem address and one group address. In addition, there is no reason why the address cannot be the address associated with the very subsystem that is transmitting the message.

Also seen in Fig. 12A is the source address field of the header-only message, which follows the destination address field and which comprises one byte (8 bits) of information. The source address informs the destination subsystem of the source of the message, that is, the subsystem generating the message over the System Bus. An op code field, comprising one byte, follows the source address and indicates to the destination subsystem the type of message that is being transmitted. is contemplated that the op code indicates, at its highest order bit, whether the message is a header-only message, as seen in Fig. 12A, or a header and data message, as seen in Fig. 12B. In addition, the remaining bits of the op code indicate to the destination subsystem the type of command which the message represents. commands, and the specific operation of any destination subsystem in response to the commands, form no part of the present invention and are not described in any greater detail herein. Depending, of course, upon the type of tasks that the subsystems will be performing, suitable commands to be represented by the bits in the op code field can be found in the command sets of many conventional data processing systems.

Following the op code field is an optional data field of variable length (from zero to 32K bytes) that contains, e.g., operands or other header data necessary for execution of the command represented by the op code in the header. In accordance with one aspect of the present invention to be described more fully later, the data field includes a data starting (DSA) address in the local memory of the sending or source subsystem if the header-only message is a request for data. Following the optional header data field is a

10

25

30

35

two byte (sixteen bit) cyclical redundancy code (CRC) field. The CRC check bits in the CRC field permit each subsystem in the data processing system 10 to check the validity of all the bits preceding the CRC check bits.

Following the CRC field is another flag character which prepares the system bus interface 28 associated with each of the subsystems for receipt of a postamble field in the message. The postamble field consists of 15 bytes, and includes eight flag characters, followed by a series of six bytes of binary zeroes, and then ending with a flag character. The postamble field would thus appear as follows:

#### FFFFFFFF000000F

where each "F" represents a flag character and each "0" represents a byte of zeroes. The postamble is followed by a post-postamble (PP), which consists of two flags. The post-postamble simply continues the self-clocking features of the message long enough to fully clock or strobe the postamble into the system bus interface.

The significance of the postamble in the practice of one aspect of the present invention will be described later in connection with the description of Fig. 15. However, briefly, the postamble is a critical portion of each message transmitted over the System Bus because it permits any subsystem that detects an error to cause the message to be aborted. The subsystem receiving the erroneous message aborts the message by superimposing binary l's (or some other non-zero signal) on the postamble, so that every subsystem in the data processing system senses a "garbled" postamble and will reject the message.

In Fig. 12B, there is illustrated the format of a header and data message. Each header and data message is used to transfer blocks of data from one subsystem to another subsystem. Other than not having a post-postamble, the header portion of the message in

10

15

20

30

35

Fig. 12B has the same format as the header-only message in Fig. 12A. The high order bit of the op code field in the header portion indicates to the destination subsystem that the message includes the data portion, which immediately follows the postamble of the header portion. If the header and data message is returning data requested by another subsystem, the header data field of the header portion includes, in its first three bytes, the starting address in the local memory at which the data is to be stored.

The data portion of the header and data message includes a beginning single flag character, a data field which contains blocks of data information of variable length (zero to 64K bytes), followed by sixteen CRC bits, followed in turn by a single flag character, then followed by a postamble field of the same format as the postamble in the header portion, and ending with a post-postamble field (two flag characters). If any subsystem in the data processing system 10 detects an error in the data portion of the message, it garbles the postamble field associated with the data portion of the data and header message. After the post-postamble, the System Bus again goes into an idle condition before any subsequent message is transmitted on the System Bus.

#### 25 F. SYSTEM BUS INTERFACE 28

Turning now to Fig. 13, there is shown in simplified form the major circuit blocks within each system bus interface 28. The system bus interface 28 includes a system interface circuit or chip 136 that, in the preferred embodiment, is fabricated entirely on a single integrated circuit chip. The system interface chip 136 receives and provides data or message information to the P-M bus of its associated subsystem 24. The system interface chip 136 is connected to a channel adapter 138 that, in turn, is connected to the System Bus. The channel adapter 138 both provides messages

WO 82/03711 PCT/US82/00455

5

10

1.5

20

25

30

from its associated subsystem 24 to the System Bus, and receives all messages that are on the System Bus.

The system interface chip 136 and the channel adapter 138 are shown simplified, but in somewhat greater detail, in Fig. 14. As seen in Fig. 14, the system interface chip 136 includes a DMA (direct memory access) circuit 140, command and status registers 142, and a message control circuit 144. The DMA 140 and command and status registers 142 will be described in greater detail later in conjunction with the Figs. 21 through However, briefly, in addition to novel features forming certain aspects of the present invention that will be described later, the DMA performs conventional functions, such as buffering messages that are being generated by its associated subsystem or that have been received from the System Bus. The DMA 140 permits blocks of data to be transferred between the local memory of its associated subsystem and the System Bus, by accessing sequential memory locations in the local memory. Since access to the local memory is accomplished by the DMA, independently of the processor in the associated subsystem, the processor is free to perform other operations. The command and status registers 142 simply receive control and status bits from the processor of the associated subsystem or the control circuitry of the system bus interface, and in response provide such bits to the DMA 140 and message control circuit 144 in order to cause the system bus interface to accomplish designated operations.

The message control circuit 144 performs a number of functions that are critical to the operation of the system bus interface and the transmission and receipt of messages on the System Bus. These functions include:

35 (1) monitoring the System Bus and permitting its associated subsystem to transmit a message only when the System Bus is idle;

10

15

20

25

30

35

- (2) receiving data or message information to be transmitted from the associated subsystem and inserting flags, preambles, postambles, and CRC bits;

- (3) comparing each byte of information being transmitted by its associated subsystem with each corresponding byte of information received from the System Bus, in order to detect any interference or collision of messages (contention garble);

- (4) checking the destination address of any received message in order to determine whether its associated subsystem should copy or act on that message;

- (5) performing a CRC check on information received on the System Bus, and causing the message to be aborted if an error is detected, regardless of whether the associated subsystem is an addressed destination;

- (6) checking the postamble of each message received from the System Bus, and indicating that the message should be disregarded if garble is detected in the postamble;

- (7) indicating that the message should be disregarded if other errors (such as swamp or idle errors) are detected;

- (8) indicating to its associated subsystem if its message has been successfully transmitted; and

- (9) generating the necessary control signals to cause the DMA to access successive memory locations in the local memory of its associated subsystem.

The channel adapter 138 is shown in Fig. 14 as connected to the message control circuit 144 by a pair of buses 150 and 152. Messages to be provided to the System Bus are passed, one byte at a time, along the bus 150 to the channel adapter 138. Messages that are received from the System Bus after passing through the

10

15

channel adapter 138 are passed, one byte at a time, along the bus 152 to the message control circuit 144.

The channel adapter 138 includes a serializer 154 that serializes the message from the bus 150, i.e., converts each byte in the message into a serial stream of bits. In addition, the serializer 154, as conventional, inserts "0's" at appropriate locations in the message so that, as in standard protocols, no more than five consecutive "1's" will appear in the message, other than at control or flag characters.

The serial stream of bits at the output of the serializer 154 is provided to an encoder circuit 156, which encodes the serial stream into a signal suitable for transmission. Such a signal may be in the form of a double frequency code, such as the well-known diphase or Manchester code. The encoded data at the output of encoder circuit 156 is then provided to the bus driver 46, which was described in detail earlier in conjunction with Fig. 4.

Simple circuitry, which by itself forms no 20 part of the present invention, can be associated with either the serializer 154 or the encoder 156 in order to garble a message postamble. Such circuitry gates a source of "l's" or low frequency pulses to the signal line carrying the message, prior to the message being 25 provided by the bus driver 46 to the System Bus. For present purposes, it can be assumed that this garbling circuitry consists simply of a gate or multiplexing circuit that selectively gates 1's at the output of the serializer 154. A specific circuit for garbling.the 30 postamble will be illustrated and described later in conjunction with a dual-channel System Bus seen in Figs. 27 through 35.

When a message or signal is received from the

System Bus by the system bus interface 28, it first

passes through the bus receiver 58, which was also

described earlier in conjunction with Fig. 4. The

35

output of the bus receiver 58 is provided to a decoder circuit 158, a swamp circuit 160, and an idle detection circuit 162.

Exemplary forms of the swamp circuit 160 and the idle detection circuit 162 will be described in 5 detail later in conjunction with Fig. 26. Briefly, the swamp circuit 160 monitors the pulse width of the encoded messages received from the System Bus, and provides a signal (not shown in Fig. 14) indicating to the message control circuit 144 when a signal having 10 excessive pulse widths, such as one resulting from two interfering messages, is received. The idle detection circuit 162 monitors the System Bus for an idle condition, and provides a signal (not shown in Fig. 14) indicating to the message control circuit 144 when the 15 System Bus is idle so that, among other things, a message from the message control circuit 144 is passed to the channel adapter 138 only when no other message is already on the System Bus. If an idle condition occurs at an inappropriate point in time, such as during a message, 20 the message control circuit will determine that an idle error condition exists. The System Bus is detected as idle if the interval between pulses on the System Bus exceeds the normal interval between each pulse in an 25 encoded message.

The decoder circuit 158 receives the encoded message from the output of the bus receiver 58, and decodes the signal in order to provide a serial stream of bits to a de-serializer 164. The de-serializer 164 takes the serial bits of the message and, in a conventional fashion, converts the message into parallel bytes and deletes any "0's" that were inserted when the message was serialized. The output of the de-serializer is provided to the message control circuit 144 by way of the bus 152.

Fig. 15 illustrates, in simplified form, the major circuit components within the message control

10

15

20

25

30

35

circuit 144. As noted earlier, each message control circuit 144 performs a number of functions in controlling the transmission and receipt of messages at its associated subsystem 24. At the heart of one aspect of the present invention are the following functions:

- (1) the detection of contention garble, i.e., the collision or interference between a message being transmitted by the associated subsystem and a message simultaneously transmitted by another subsystem;

- (2) the detection of message errors, such as CRC errors, in any message on the System Bus, by the message control circuit 144 associated with every subsystem 24 in the data processing system 10, and causing the postamble of the message to be garbled if such an error is detected; and

- (3) the detection of a garbled postamble by the message control circuit 144 associated with every subsystem 24, and causing each subsystem to ignore or reject a message if a garbled postamble is detected.

Before proceeding with the description of the message control circuit 144 in Fig. 15, it should be noted that only major circuit components of the message control circuit 144 are shown in somewhat simplified form as functional blocks in Fig. 15 in order to teach the important aspects of the present invention.

Referring now to Fig. 15, it can be seen that the illustrated message control circuit 144 receives data (representing destination address, source address, op code or data information) for a header-only message or a header and data message one byte at a time by way of the DMA 140 (Fig. 14) and passes the data through a multiplexer (MUX) 170. The MUX 170 also receives CRC check bits generated at a CRC generate circuit 172. The CRC generate circuit 172 can generate CRC bits in accordance with any one of numerous algorithms well known to

10

15

20

25

30

35

those skilled in the art, such algorithms and the specific circuitry in CRC generate circuit 172 forming no part of the present invention. For example, one such well-known algorithm, and circuitry for implementing that algorithm, are described in detail in Pandeya and Cassa, Parallel CRC Lets Many Lines Use One Circuit, 14 Computer Design 87 (September, 1975).

Data, and any CRC bits inserted at appropriate locations in the data by the MUX 170, are provided to a first-in-first-out memory (XFIFO) 174 which is capable of storing ten nine-bit words. The bytes of data provided by an associated subsystem 24 by way of the DMA 140 to the XFIFO 174 are only eight bits wide, with the reason for the ninth bit (referred to as ENCRC200 in the drawings) of each word stored in XFIFO 174 being described later with reference to the operation of the system bus interface 28 and the circuitry shown in Fig. 15.

Eight bits of each nine-bit word stored in the XFIFO 174 can be passed to a MUX 176 and to a first-in-first-out memory (GFIFO) 178. The GFIFO 178 stores ten bytes of data, each for comparison at a compare circuit 180 with each corresponding byte of data in each transmitted message that is returned by the System Bus. The MUX 176 has an input connected in a conventional fashion to selectively provide flag characters and is conventionally constructed so that it can also be controlled to selectively provide at its output zeroes for a postamble. The MUX 176 is controlled to insert flags and postamble bits at appropriate points during the transmission of each message.

The output of the MUX 176 is provided by way of the output bus 150 to the serializer 154 (Fig. 14), which in turn takes each byte of the message and serializes the byte for transmission on the System Bus.

After a message is received from the System Bus and passed, through bus receiver 58, decoder 158 and

de-serializer 164, to the input bus 152 (Fig. 14), the message is provided, as seen in Fig. 15, to a receiver address check circuit 184, a CRC check circuit 186, and a postamble garble detection circuit 188. In addition, each byte of the received message (less flags, preambles and postambles) is stored in a ten byte first-in-first-out memory (RFIFO) 190.

5

10

15

20

25

30

35

As will be described in detail below in connection with the operation of the system bus interface 28, receiver address check circuit 184 checks the destination address field of each message received from the System Bus, and if the destination address or addresses in the address field match the unique subsystem address or the group address of the subsystem associated with the message control circuit, an appropriate signal (RMATCH@0) is generated. The address check circuit 184 includes two registers (SADD and MASK, not shown) that are loaded during initialization of the subsystem. register SADD is loaded with the unique subsystem address and the register MASK with a group address assignment. When the destination addresses of a message are received, the contents of the two registers are compared with the addresses in the destination address field.

The CRC check circuit 186 generates CRC bits from the data received in each message and performs an error code check on the message by comparing the CRC bits with the CRC check bits in the CRC field of the message. The postamble garble detection circuit 188 checks the postamble of each message received from the System Bus and indicates when the postamble has been garbled, i.e., "1's" have been superimposed on the "0's" in the postamble.

Still referring to Fig. 15, a transmit control circuit 196, a receive control circuit 198, and a monitor control circuit 200 generally control the circuit components shown in the message control circuit 144. In the implementation of the message control circuit, much

15

20

of the control represented by control circuits 196, 198 and 200 is accomplished by programmable logic arrays (PLA's). In addition, the representation of only three control blocks 196, 198 and 200 only serves to generally illustrate the control functions needed to accomplish the operation to be described below. It should be obvious that in actual practice the control functions will be accomplished by many PLA's and by logic circuits associated with each of the major circuit components shown in Fig. 15.

Also shown in Fig. 15 is a retry circuit 204 which will cause any message that has not been successfully transmitted (for example, because of contention garble) to be retried later. A specific circuit and operational algorithm for implementing the retry circuit 204 in a system employing a dual-channel System Bus will be described later in conjunction with Figs. 34 and 35.

In addition to the major circuit components, there are also shown in Fig. 15 numerous control signals for controlling the circuit components. These signals are identified by mnemonics which represent descriptive signal names. The mnemonics, descriptive signal names, and a general signal description for each of the control signals in Fig. 15 are shown below in Signal List #1.

25 SIGNAL LIST #1

|    | MNEMONIC   | SIGNAL NAME       | SIGNAL DESCRIPTION     |

|----|------------|-------------------|------------------------|

|    | ABORT      | Abort Message     | Causes serializer 154  |

|    |            |                   | to superimpose "l's"   |

|    |            |                   | on the postamble       |

| 30 | BE@1       | Byte Enable       | Controls passage of    |

|    |            |                   | data thru MUX 176      |

|    | CMPOK@0    | Complete and OK   | Indicates that re-     |

|    |            |                   | ceived message was     |

|    |            |                   | complete and valid     |

| 35 | CNLAVAIL@0 | Channel Available | Indicates that channel |

|    |            |                   | (System Bus) is idle   |

|    | MNEMONIC | SIGNAL NAME  | SIGNAL DESCRIPTION     |

|----|----------|--------------|------------------------|

|    |          |              | and available for      |

|    |          |              | transmission           |

|    | CRCCLR*0 | CRC Clear    | Clears the CRC check   |

| 5  |          |              | circuit 186            |

|    | CRCGEN*0 | CRC Generate | Causes CRC check cir-  |

|    |          |              | cuit 186 to compute    |

|    |          |              | CRC bits and compare   |

|    |          |              | with CRC check bits    |

| 10 | CRCOK@0  | CRC OK       | Indicates whether a    |

|    |          |              | CRC error has occurred |

| ·  | ENCRC1*1 | Enable CRC1  | Controls MUX 170 to    |

|    |          |              | pass first CRC byte    |

|    |          |              | from CRC generate      |

| 15 |          |              | circuit 172            |

|    | ENCRC2*1 | Enable CRC2  | Controls MUX 170 to    |

|    |          |              | pass second CRC byte   |

|    |          |              | from CRC generate      |

|    |          |              | circuit 172            |

| 20 | ENCRC2@0 | Enable CRC2  | Status signal to be    |

|    |          |              | stored with data in    |

|    |          |              | XFIFO as ninth bit to  |

|    |          |              | indicate last byte     |

|    |          |              | before flag character  |

| 25 | ERTRM    | Error Term   | Indicates an error in  |

|    |          |              | the received message   |

|    | FE@1     | Flag Enable  | Causes flags or post-  |

|    |          |              | amble to be provided   |

|    |          |              | at output of MUX 176   |

| 30 | GFERR    | GF Error     | Indicates when a mis-  |

|    |          |              | match occurs at com-   |

|    |          |              | pare circuit 180       |

|    | GFLD@1   | GFIFO Load   | Causes byte to be      |

|    |          |              | loaded into GFIFO 178  |

| 35 | GFRD@0   | GFIFO Read   | Causes byte to be read |

|    |          |              | from GFIFO 178 for     |

|    |          |              | comparison in compare  |

|    |          |              | circuit 180            |

|    | MNEMONIC<br>LMFULL@0 | SIGNAL NAME Local Memory Full | in the associated                                                                                      |

|----|----------------------|-------------------------------|--------------------------------------------------------------------------------------------------------|

| 5  |                      |                               | local memory, des-<br>cribed as the "mail-<br>box", is full and<br>cannot accept message               |

| 10 | LSTBYT@0             | Last Byte                     | information Status signal stored with data in RFIFO as ninth bit to indicate last byte of data for DMA |

| 15 | RDMAREQ@0            | Receive DMA Re-               | Indicates to DMA that associated subsystem is the addressed destination                                |

| 20 | RENBL@0              | Receive Enable                | Indicates when channel (System Bus) is not idle, to enable message control circuit 144 to              |

| 25 | RERR                 | Receive Error                 | receive message Indicates when swamp circuit 160 has detected a swamp error                            |

| 23 | RFCLR@0<br>RFLD@0    | RFIFO Clear<br>RFIFO Load     | Clears the RFIFO 190 Causes byte to be loaded into RFIFO 190                                           |

| 30 | RFLG                 | Receive Flag                  | Indicates when re-<br>ceived byte in de-<br>serializer 164 is flag<br>character                        |