(12)

## Patentschrift

(21) Deutsches Aktenzeichen: 11 2013 007 724.8

(86) PCT-Aktenzeichen: PCT/US2013/077785

(87) PCT-Veröffentlichungs-Nr.: WO 2015/099730

(86) PCT-Anmeldetag: 26.12.2013

(87) PCT-Veröffentlichungstag: 02.07.2015

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: 15.09.2016

(45) Veröffentlichungstag

der Patenterteilung: 11.01.2024

(51) Int Cl.: **G06F 13/14 (2006.01)**

**G06F 13/20 (2006.01)**

**G06F 12/0806 (2016.01)**

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(62) Teilung in:

**11 2013 007 841.4; 11 2013 007 842.2**

(73) Patentinhaber:

**INTEL CORPORATION, Santa Clara, Calif., US**

(74) Vertreter:

**Samson & Partner Patentanwälte mbB, 80538 München, DE**

(72) Erfinder:

**Das Sharma, Debendra, Saratoga, CA, US;

Blankenship, Robert G., Tacoma, Wash., US;

Chittor, Suresh S., Portland, Oreg., US; Creta,**

**Kenneth C., Gig Harbor, Wash., US; Fleischer, Balint, Groton, Mass., US; Jen, Michelle C., Sunnyvale, Calif., US; Kumar, Mohan J., Aloha, Oreg., US; Morris, Brian S., Santa Clara, Calif., US**

(56) Ermittelter Stand der Technik:

**US 2013 / 0 268 694 A1

CN 1 03 430 161 A**

**CN 1 03 430 161 A (in maschineller

Übersetzung)**

(54) Bezeichnung: **SYSTEM, VORRICHTUNG UND VERFAHREN ZUR GEMEINSAMEN BENUTZUNG VON SPEICHER UND I/O-DIENSTEN ZWISCHEN KNOTEN**

(57) Hauptanspruch: Apparat aufweisend:

eine Steuerung (515; 515a, 515b) eines gemeinsam benutzten Speichers (505; 505a, 505b) zum:

Bedienen von Last- und Speicheroperationen, die über Datenverbindungen von mehreren unabhängigen Knoten (510a,....., 510n; 510a,....., 510e) empfangen werden, um einen Zugang zu einer gemeinsam benutzten Speicherressource vorzusehen, wobei jedem der mehreren unabhängigen Knoten (510a,.....,510n; 510a,.....,510e) Zugang zu einem entsprechenden Teil der gemeinsam benutzten Speicherressource gewährt wird; und

eine I/O-Logik zum:

Identifizieren von Übergängen zwischen Zwischenverbindungsprotokolldaten und Speicherzugangsprotokolldaten, die auf den Datenverbindungen gesendet werden, dadurch gekennzeichnet dass Übergänge zwischen Zwischenverbindungsprotokolldaten und Speicherzugangsprotokolldaten durch ein Datenstrom-Framing-Token, das zum Identifizieren der Übergänge codiert ist, identifiziert werden.

**Beschreibung****GEBIET**

**[0001]** Diese Offenbarung betrifft ein System, eine Vorrichtung und ein Verfahren zum Identifizieren von Übergängen zwischen Zwischenverbindungsprotokolldaten und Speicherzugangsprotokolldaten. Die Druckschrift US 2013/0 268 694 A1 offenbart einen externen Host sowie ein System von Switches, an das über eine PCIe-Schnittstelle mehrere PCIe-Geräte angeschlossen werden können, wobei es die PCIe-Schnittstelle den daran angeschlossenen Geräten einen direkten Speicherzugriff erlaubt.

**HINTERGRUND**

**[0002]** Fortschritte in der Halbleiterbearbeitung und im logischen Design haben eine Erhöhung der Menge an Logik ermöglicht, die auf integrierten Schaltungsvorrichtungen vorhanden sein kann. Als unmittelbare Folge haben sich Computersystemkonfigurationen von einer einzelnen oder mehreren integrierten Schaltungen zu einem System mehrfacher Kerne, mehrfacher Hardware-Threads, und mehrfacher logischer Prozessoren entwickelt, die auf einzelnen integrierten Schaltungen vorhanden sind, wie auch anderen Schnittflächen, die in solchen Prozessoren integriert sind. Ein Prozessor oder eine integrierte Schaltung weist typischerweise ein einzelnes physisches Prozessor-Die auf, wobei das Prozessor-Die eine beliebige Anzahl von Kernen, Hardware-Threads, logischen Prozessoren, Schnittstellen, Speicher, Controller-Hubs, usw. enthalten kann.

**[0003]** Infolge der besseren Möglichkeit mehr Verarbeitungsleistung in kleinere Packages einzufügen, haben kleinere Rechnervorrichtungen an Beliebtheit gewonnen. Smartphones, Tablets, ultradünne Notebooks und andere Benutzergeräte haben exponentiell zugenommen. Diese kleineren Vorrichtungen basieren jedoch auf Servern sowohl zur Datenspeicherung wie auch zur komplexen Verarbeitung, was den Formfaktor überschreitet. Folglich hat auch der Bedarf am Hochleistungsrechnermarkt (d.h., Server-Raum) zugenommen. Zum Beispiel ist in modernen Servern typischerweise zur Erhöhung der Rechenleistung nicht nur ein einzelner Prozessor mit mehrfachen Kernen vorhanden, sondern es gibt auch mehrfache physische Prozessoren (auch als mehrfache Buchsen bezeichnet). Mit steigender Verarbeitungsleistung im Zusammenhang mit der Anzahl von Vorrichtungen in einem Rechnersystem wird jedoch die Kommunikation zwischen Buchsen und anderen Vorrichtungen kritischer.

**[0004]** Tatsächlich haben sich Zwischenverbindungen von eher traditionellen Multi-Drop-Bussen, die vorwiegend elektrische Kommunikationen bewältig-

ten, zu vollständig ausgearbeiteten Zwischenverbindungsarchitekturen entwickelt, die eine schnelle Kommunikation erleichtern. Da der Verbrauch zukünftiger Prozessoren bei noch höheren Raten liegen wird, besteht leider ein entsprechender Bedarf bei den Fähigkeiten bestehender Zwischenverbindungsarchitekturen.

**[0005]** Die CN 103 430 161 A beschreibt ein Verfahren, eine Vorrichtung und ein System, die auf einer PCIE-(Peripheral Component Interconnect Express)-Switch-Kommunikation basieren, bezieht sich auf den Kommunikations- und den Rechnerbereich und wird für die Realisierung der gemeinsamen Nutzung von Daten zwischen Prozessoren durch einen PCIE-Switch verwendet. Bei dem Verfahren empfängt ein erstes Steuerungsprogramm eine von einem ersten Prozessor gesendete RAM-Anforderung. Ein zweites Steuerungsprogramm wird durch erste Markierungsinformationen in der RAM-Anforderung bestimmt und eine PCIE-Markierung des zweiten Steuerungsprogramms wird erhalten. Entsprechend der RAM-Anforderung, der PCIE-Markierung des ersten Steuerungsprogramms und der PCIE-Markierung des zweiten Steuerungsprogramms wird eine PCIE-Anforderungsnachricht erzeugt, die über den PCIE-Switch an das zweite Steuerungsprogramm gesendet wird, sodass das zweite Steuerungsprogramm die RAM-Anforderung an einen zweiten Prozessor senden kann, der von dem ersten Prozessor entsprechend der PCIE-Anforderungsnachricht besucht wird. Der erste Prozessor kann die Speicherdaten des zweiten Prozessors über den PCIE-Switch besuchen und die Daten des zweiten Prozessors abrufen. Dadurch wird der Zweck der gemeinsamen Nutzung von Daten zwischen den Prozessoren realisiert.

**[0006]** Der Erfindung liegt die Aufgabe zugrunde, einen verbesserten Zugang zu einem gemeinsam benutzten Speicher bereitzustellen.

**[0007]** Zur Lösung der Aufgabe schlägt die Erfindung einen Apparat gemäß Anspruch 1, einen Apparat gemäß Anspruch 21 und ein Verfahren gemäß Anspruch 25 vor.

**KURZE BESCHREIBUNG DER ZEICHNUNGEN**

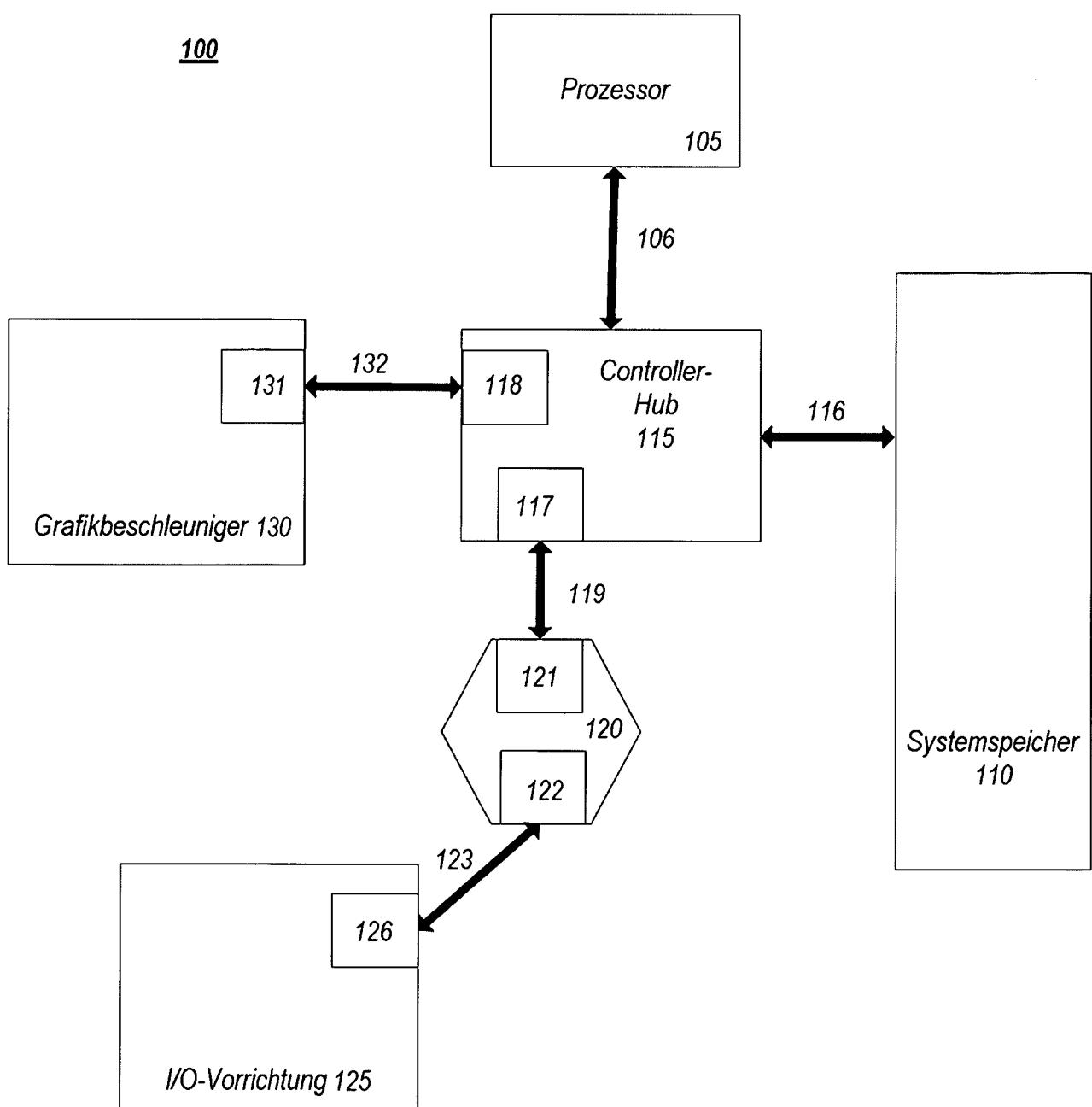

**Fig. 1** veranschaulicht eine Ausführungsform eines Rechnersystems, das eine Zwischenverbindungsarchitektur enthält.

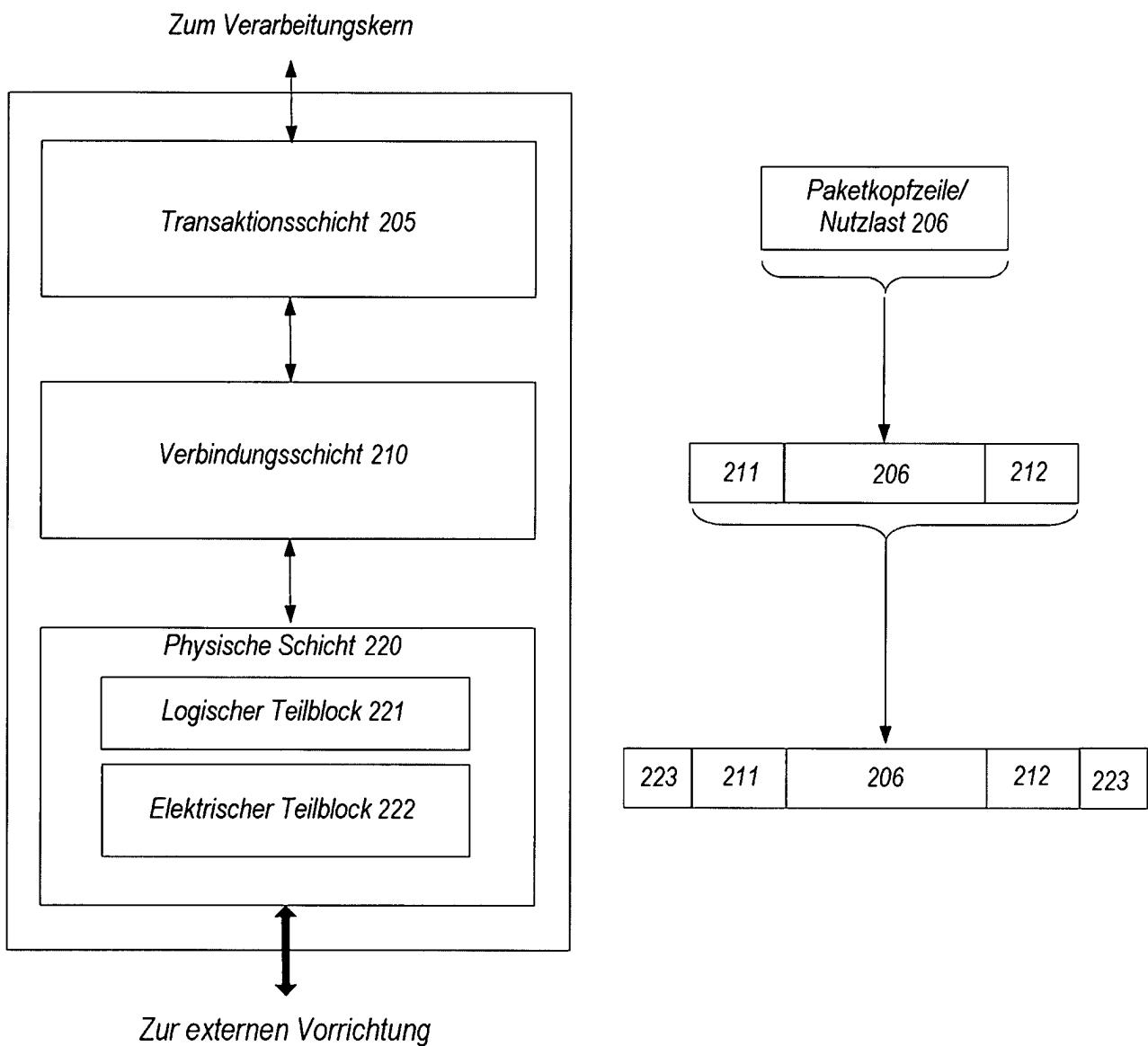

**Fig. 2** veranschaulicht eine Ausführungsform einer Zwischenverbindungsarchitektur, die einen schichtenförmigen Stapel enthält.

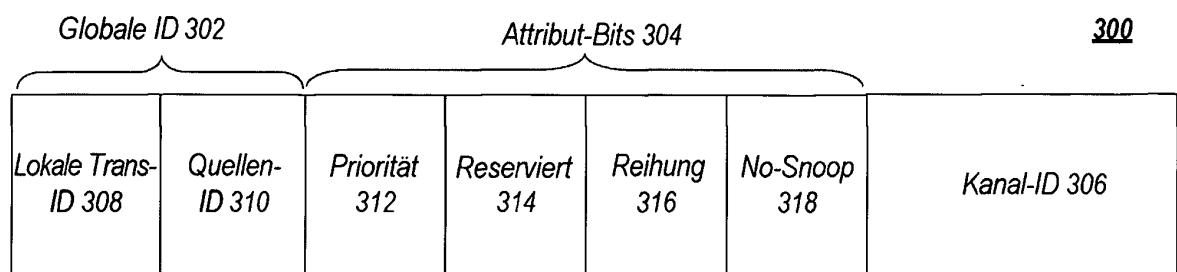

**Fig. 3** veranschaulicht eine Ausführungsform einer Anfrage oder eines Pakets, die bzw. das in einer Zwischenverbindungsarchitektur zu generieren ist.

## AUSFÜHRLICHE BESCHREIBUNG

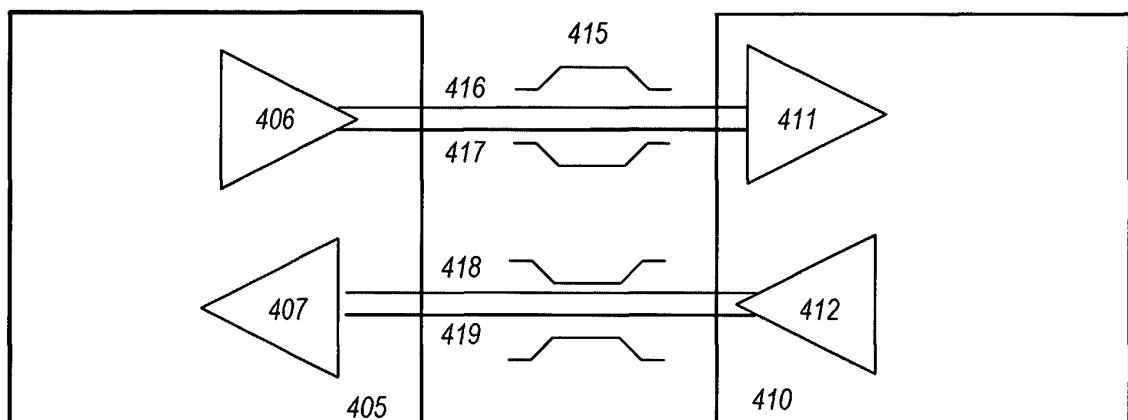

**Fig. 4** veranschaulicht eine Ausführungsform eines Sender- und Empfängerpaars für eine Zwischenverbindungsarchitektur.

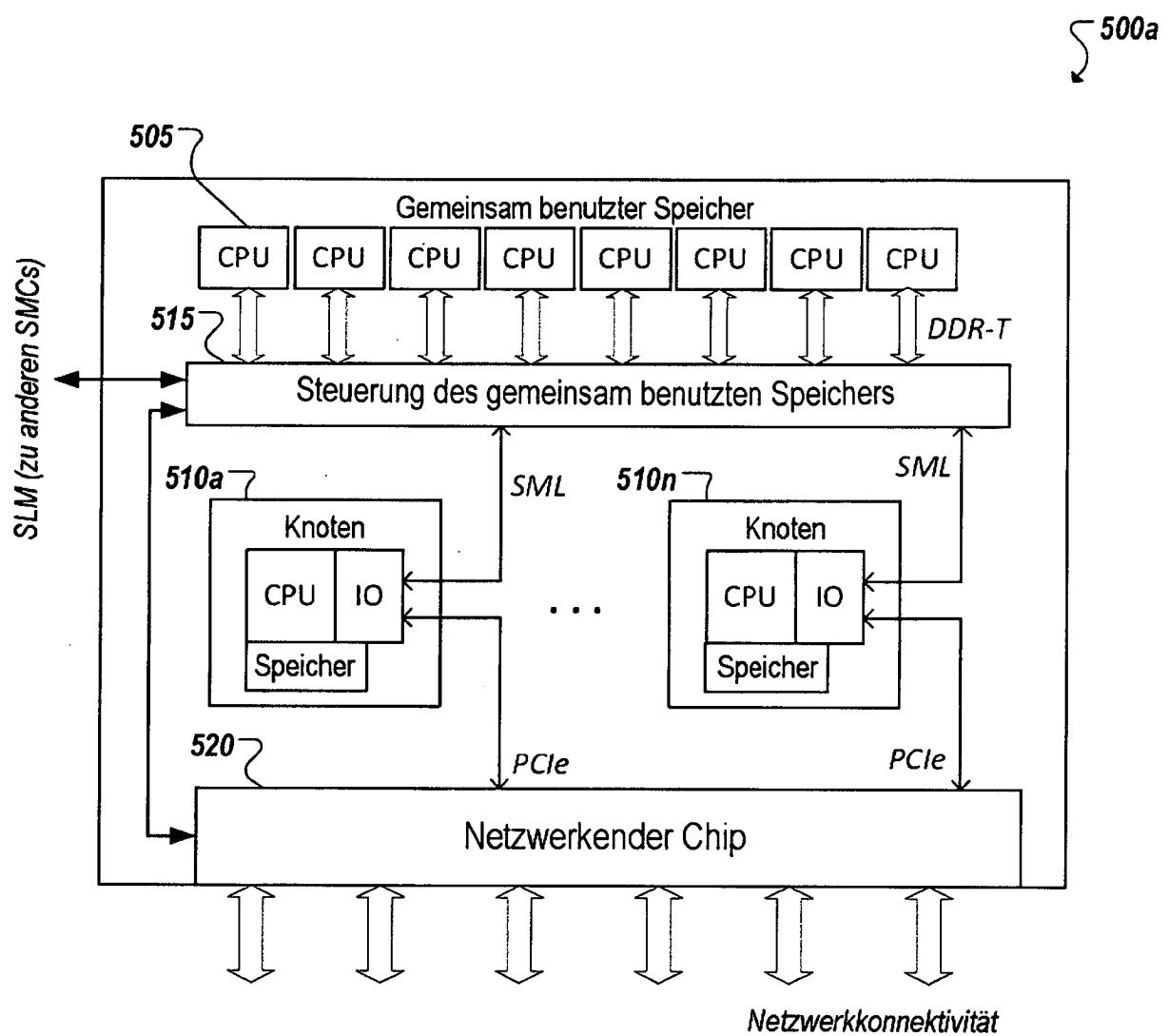

**Fig. 5A** veranschaulicht ein vereinfachtes Blockdiagramm einer Ausführungsform eines beispielhaften Knotens.

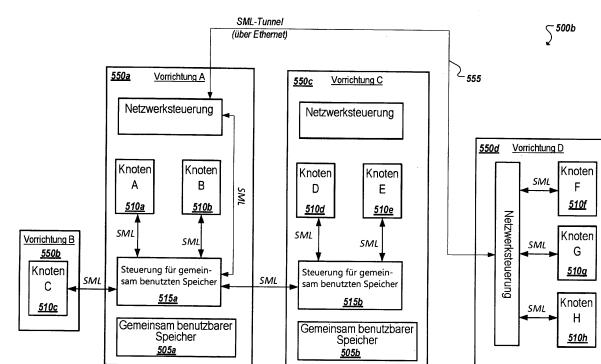

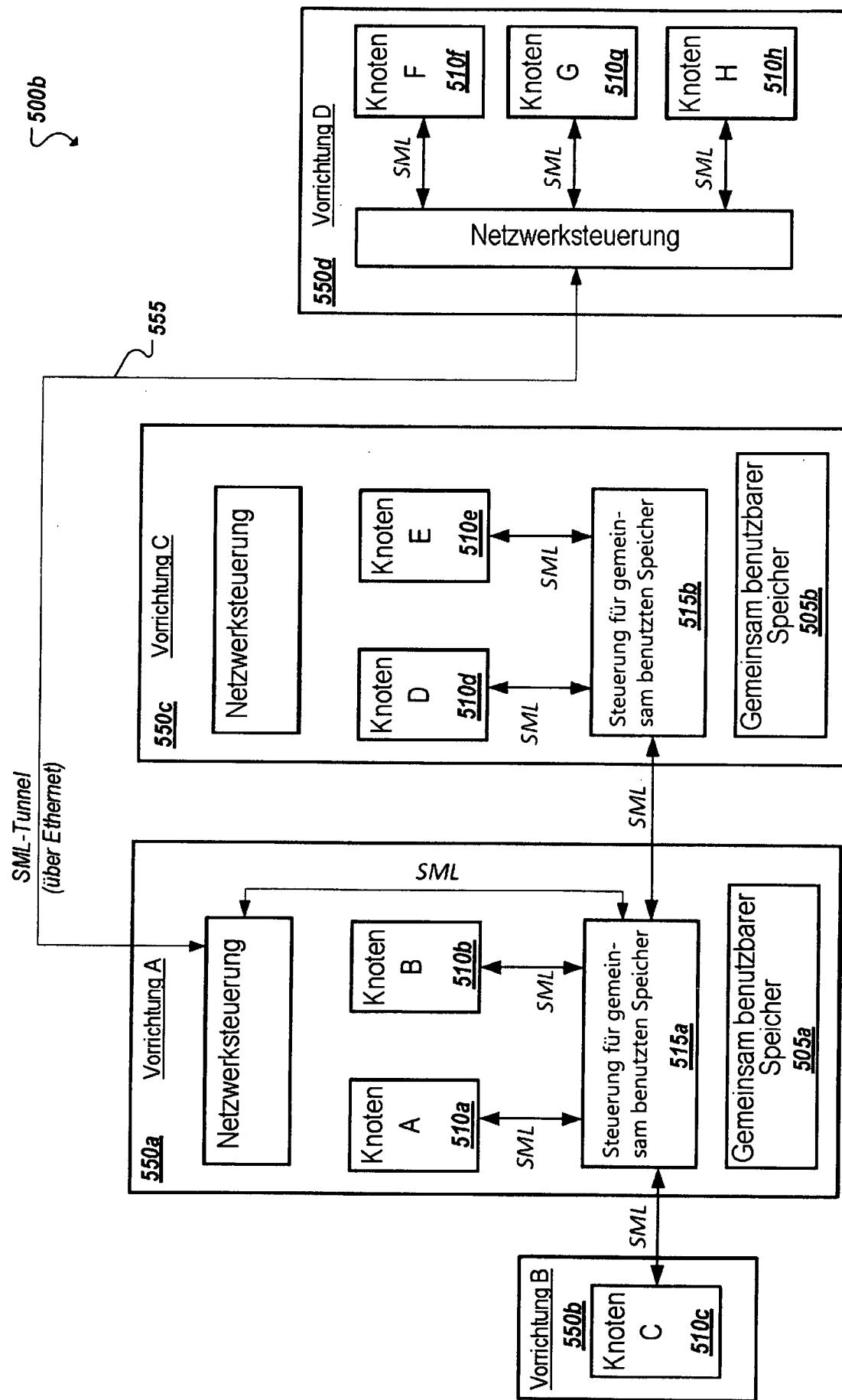

**Fig. 5B** veranschaulicht ein vereinfachtes Blockdiagramm einer Ausführungsform eines beispielhaften Systems, das mehrere Knoten enthält.

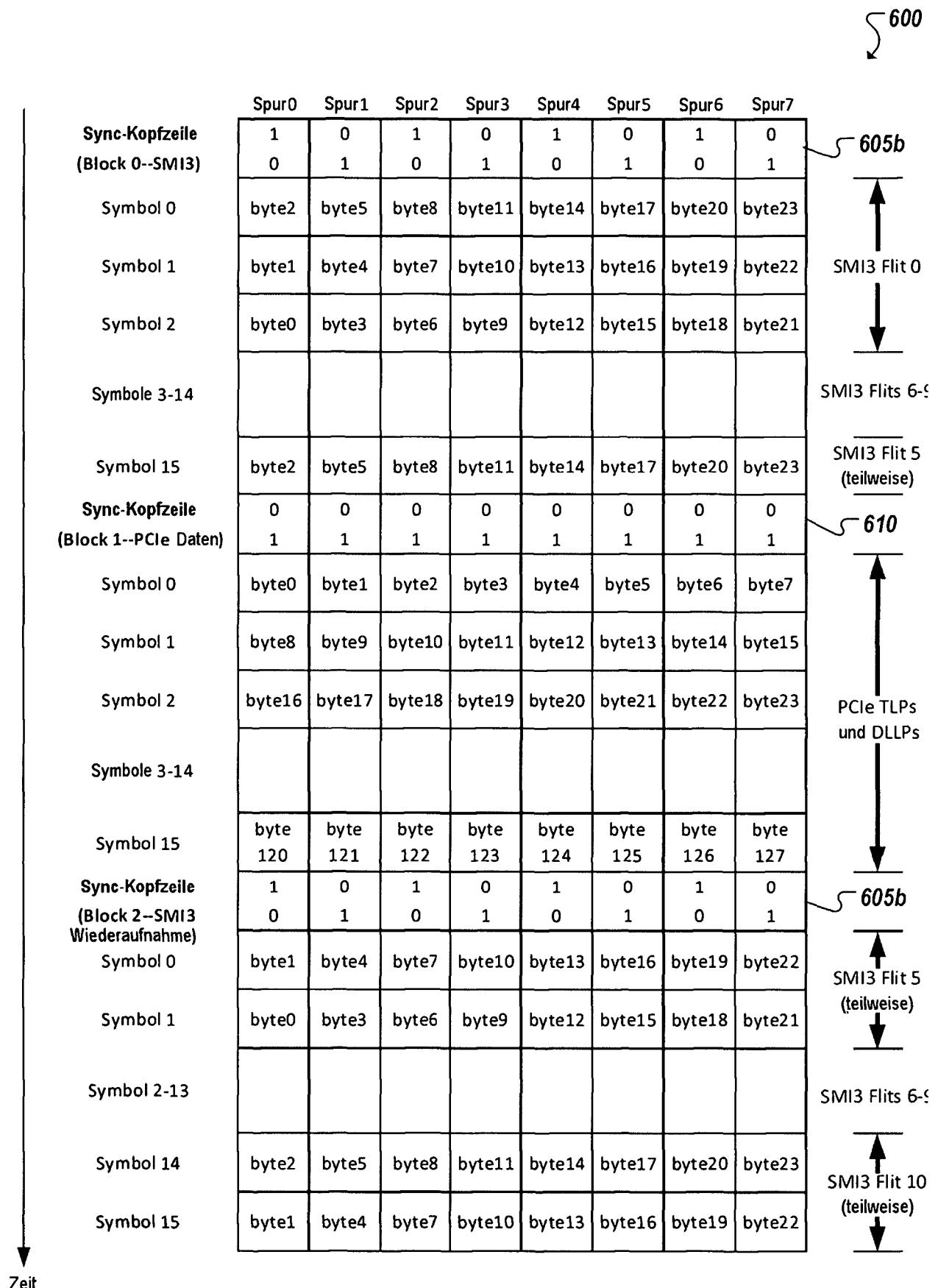

**Fig. 6** ist eine Darstellung von Daten, die gemäß einer beispielhaften, Verbindung zu einem gemeinsam benutzten Speicher übertragen werden.

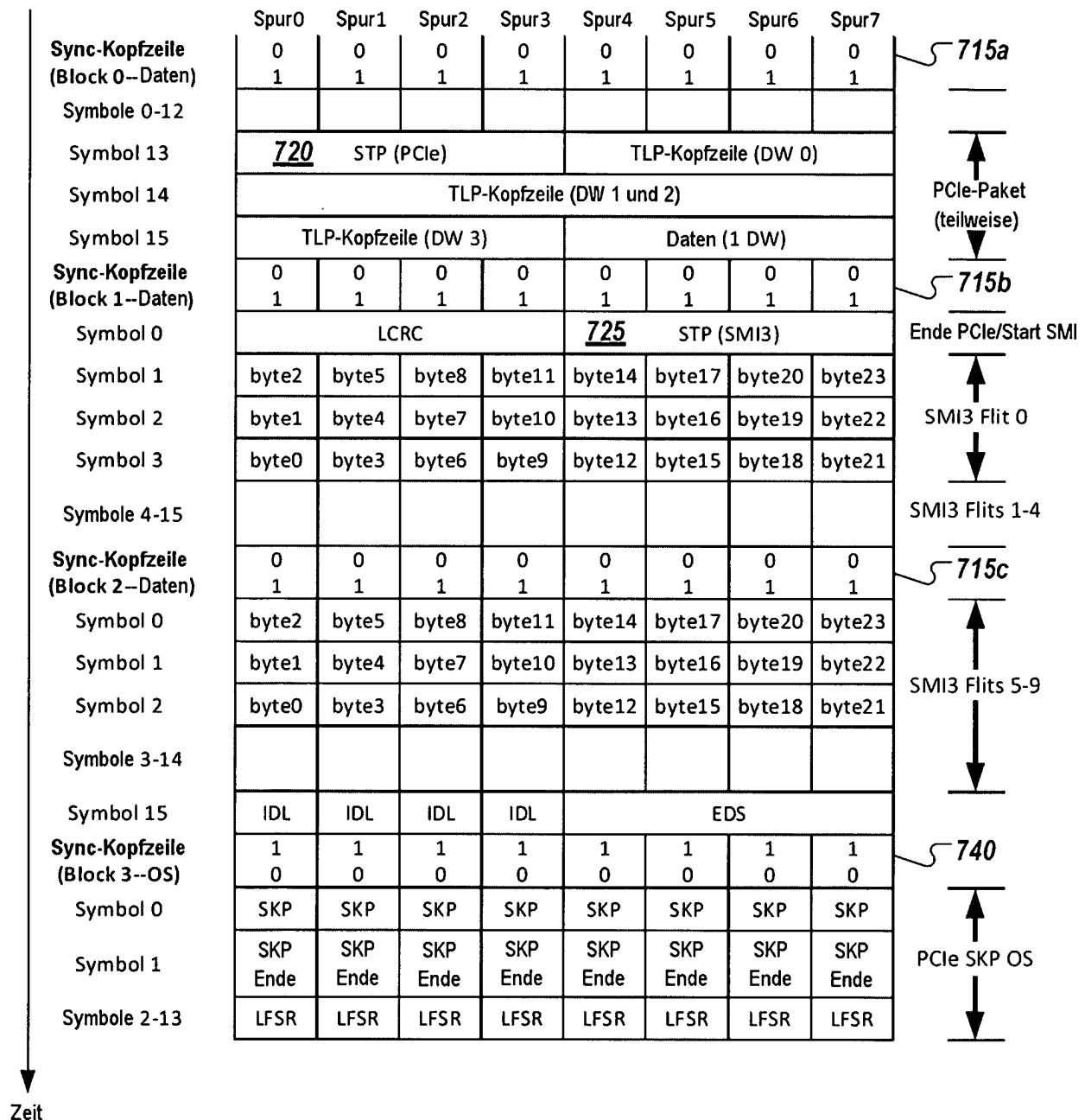

**Fig. 7A** ist eine Darstellung von Daten, die gemäß einer anderen beispielhaften, Verbindung zu dem gemeinsam benutzten Speicher übertragen werden.

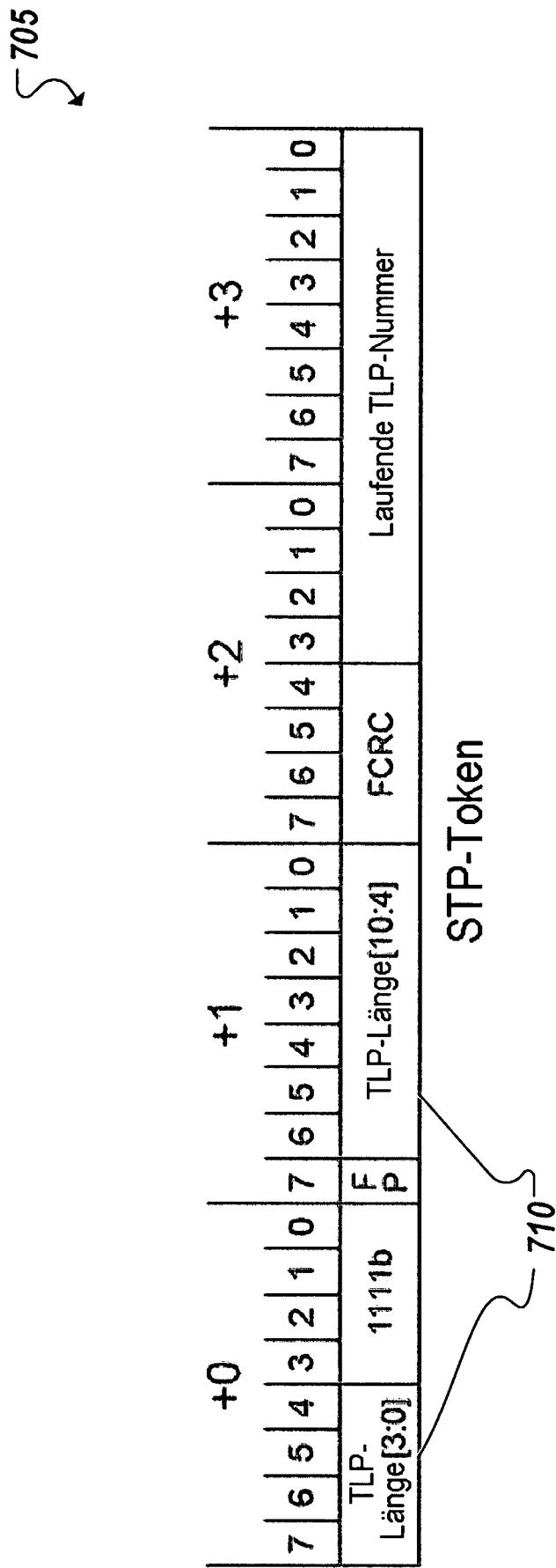

**Fig. 7B** ist eine Darstellung eines beispielhaften Beginns eines Daten-Framing-Tokens.

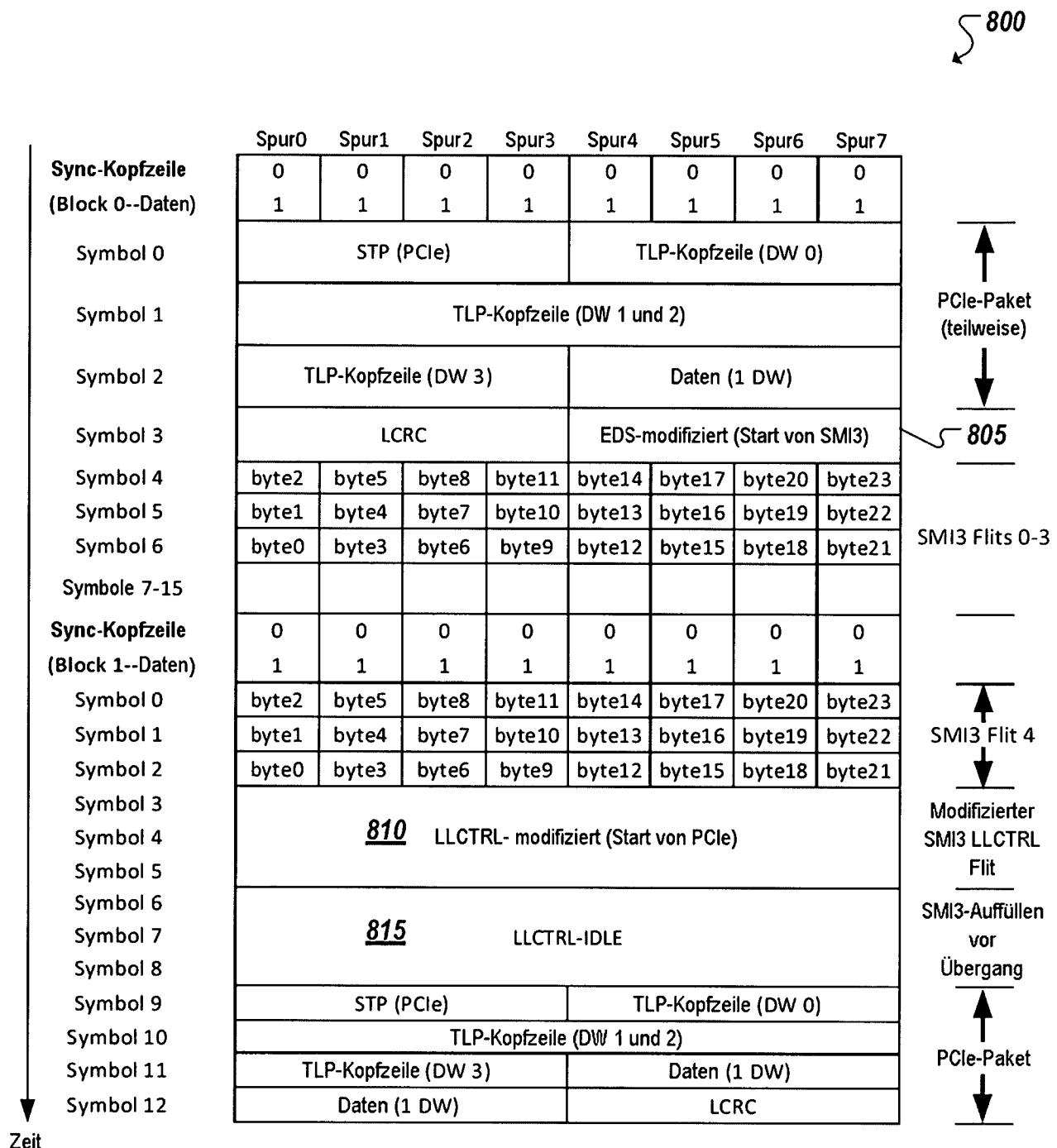

**Fig. 8** ist eine Darstellung von Daten, die gemäß einer anderen beispielhaften, Verbindung zu dem gemeinsam benutzten Speichers übertragen werden.

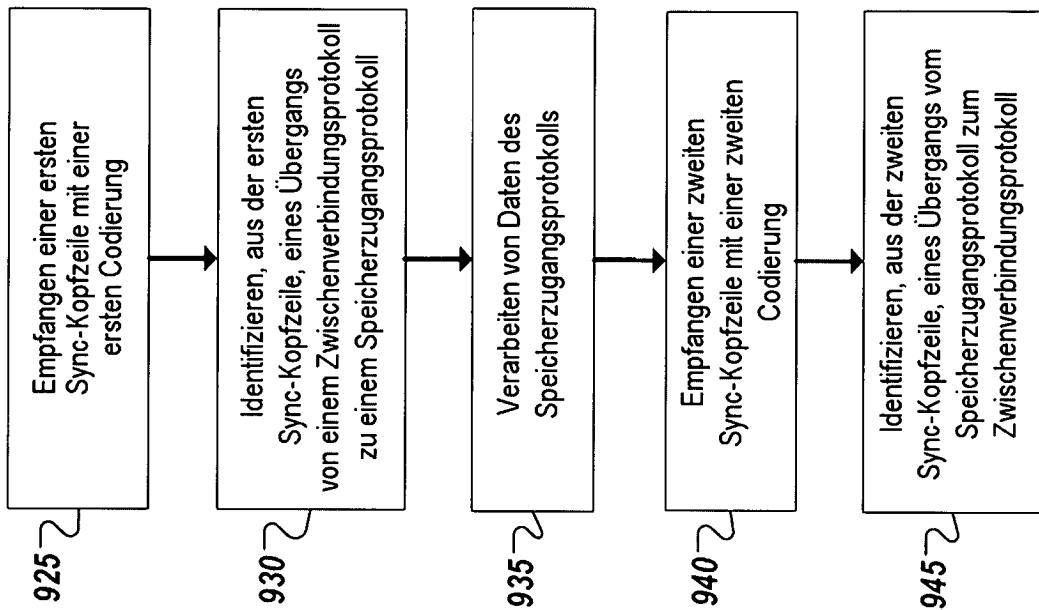

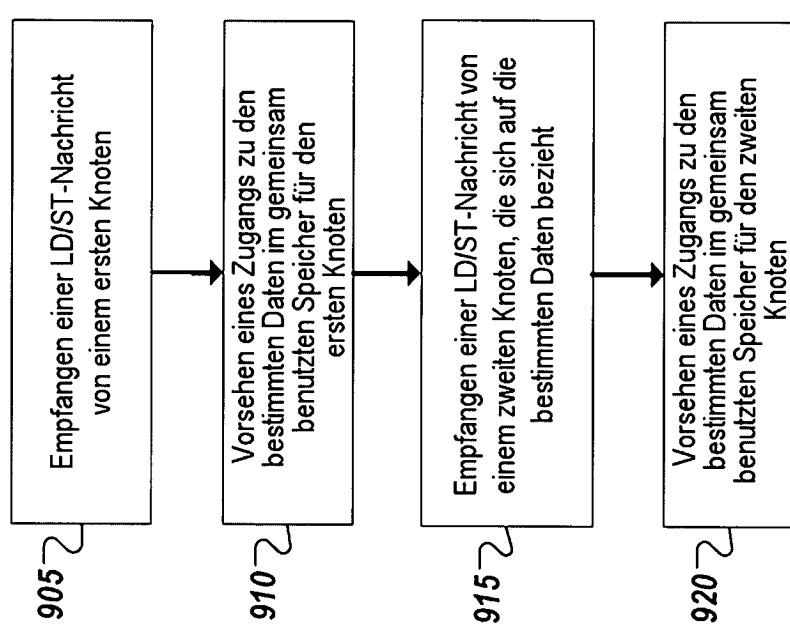

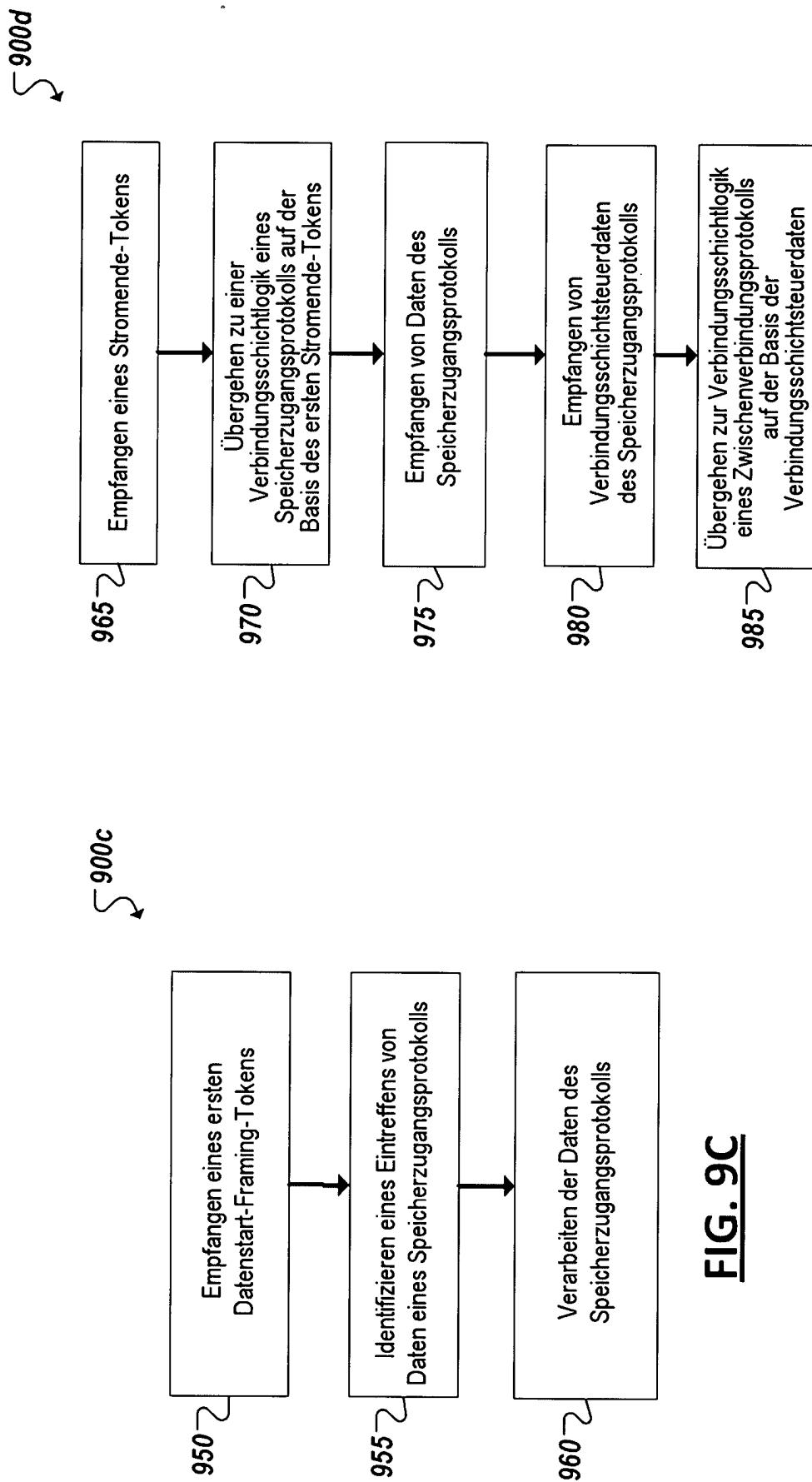

**Fig. 9A-9D** sind Ablaufdiagramme, die beispielhafte Techniken zur Speicherzugangsnachrichtenübermittlung zeigen.

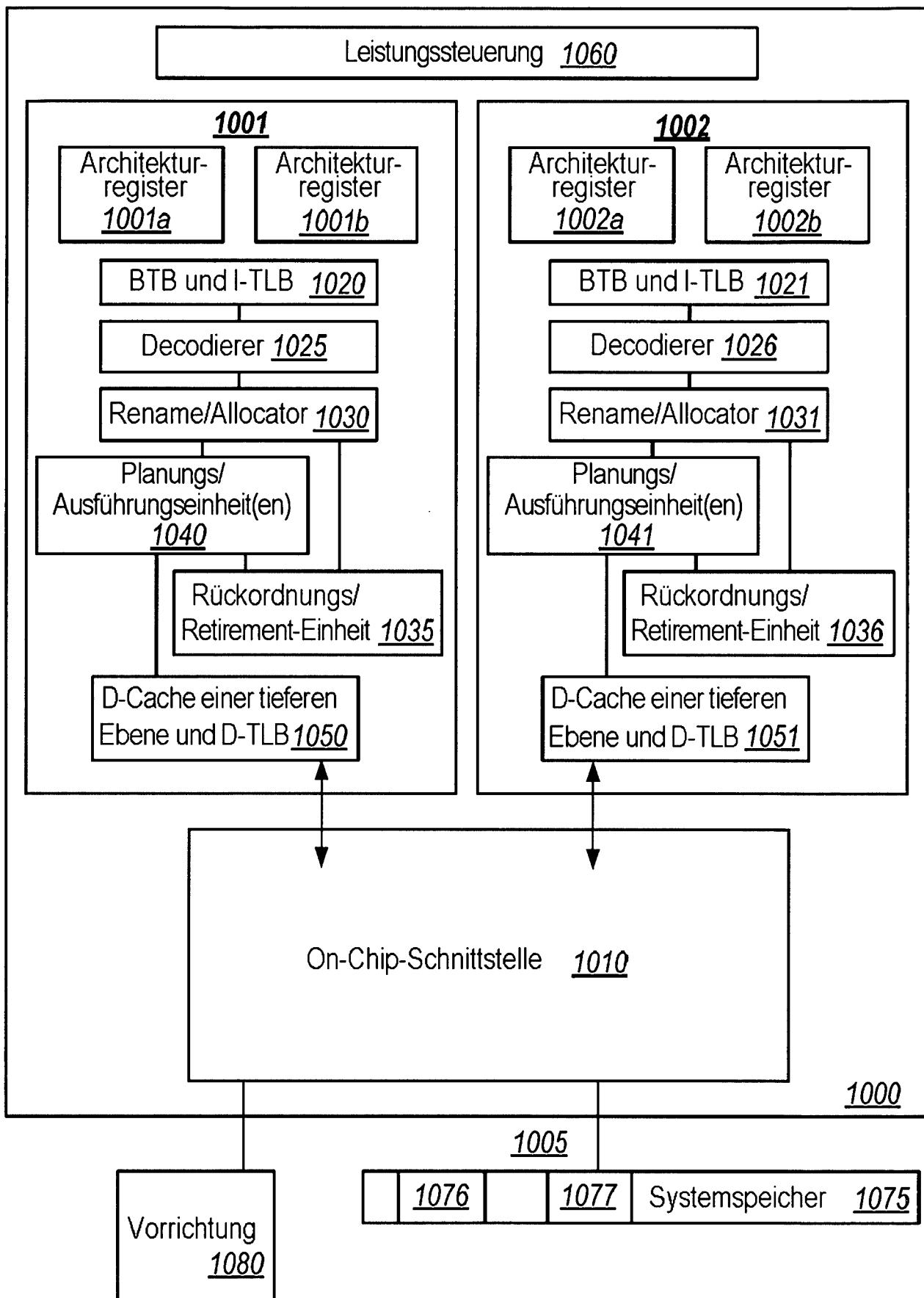

**Fig. 10** veranschaulicht eine Ausführungsform eines Blockdiagramms für ein Rechnersystem, das einen Mehrfachkern-Prozessor enthält.

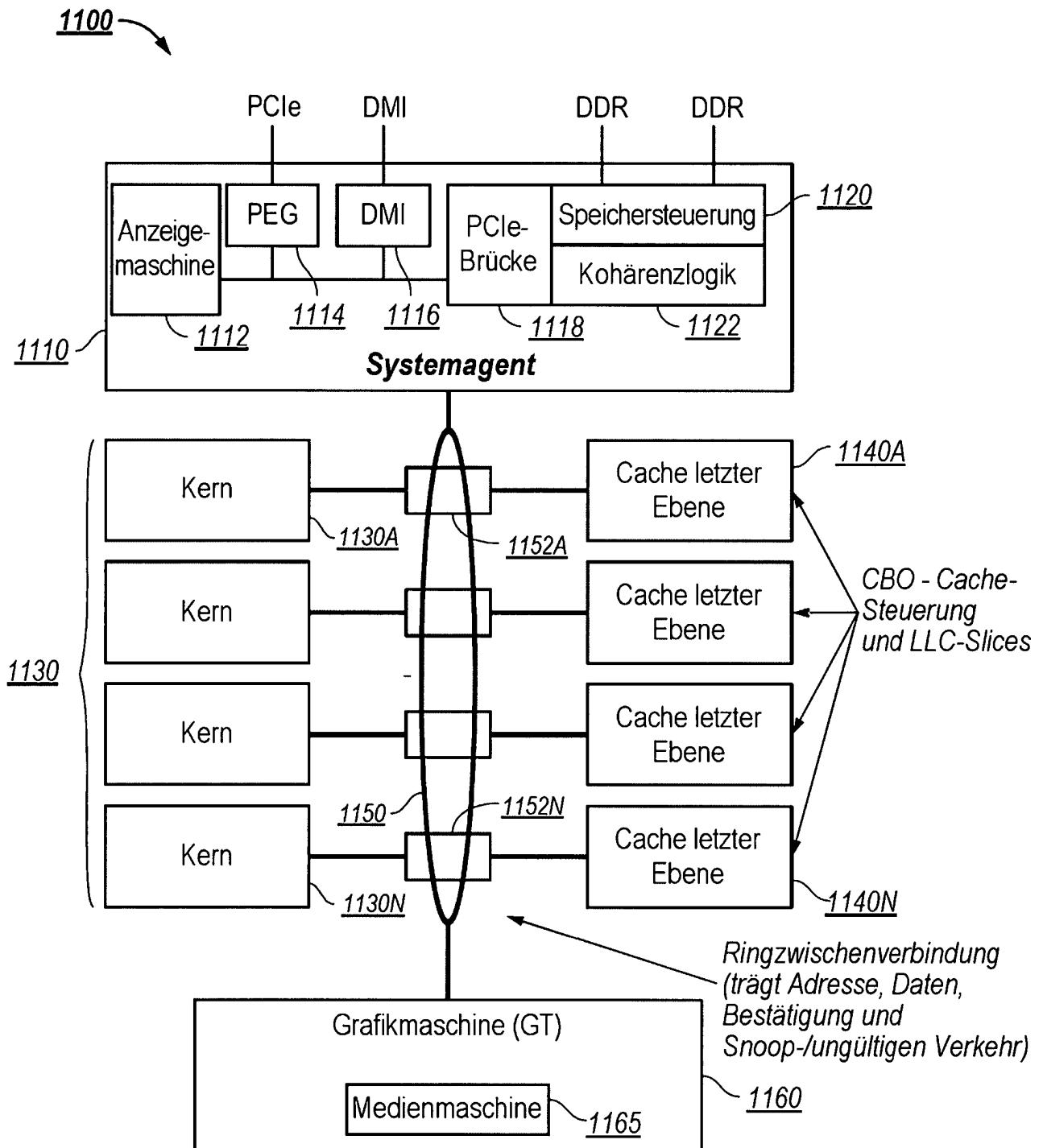

**Fig. 11** veranschaulicht eine andere Ausführungsform eines Blockdiagramms für ein Rechnersystem, das einen Mehrfachkern-Prozessor enthält.

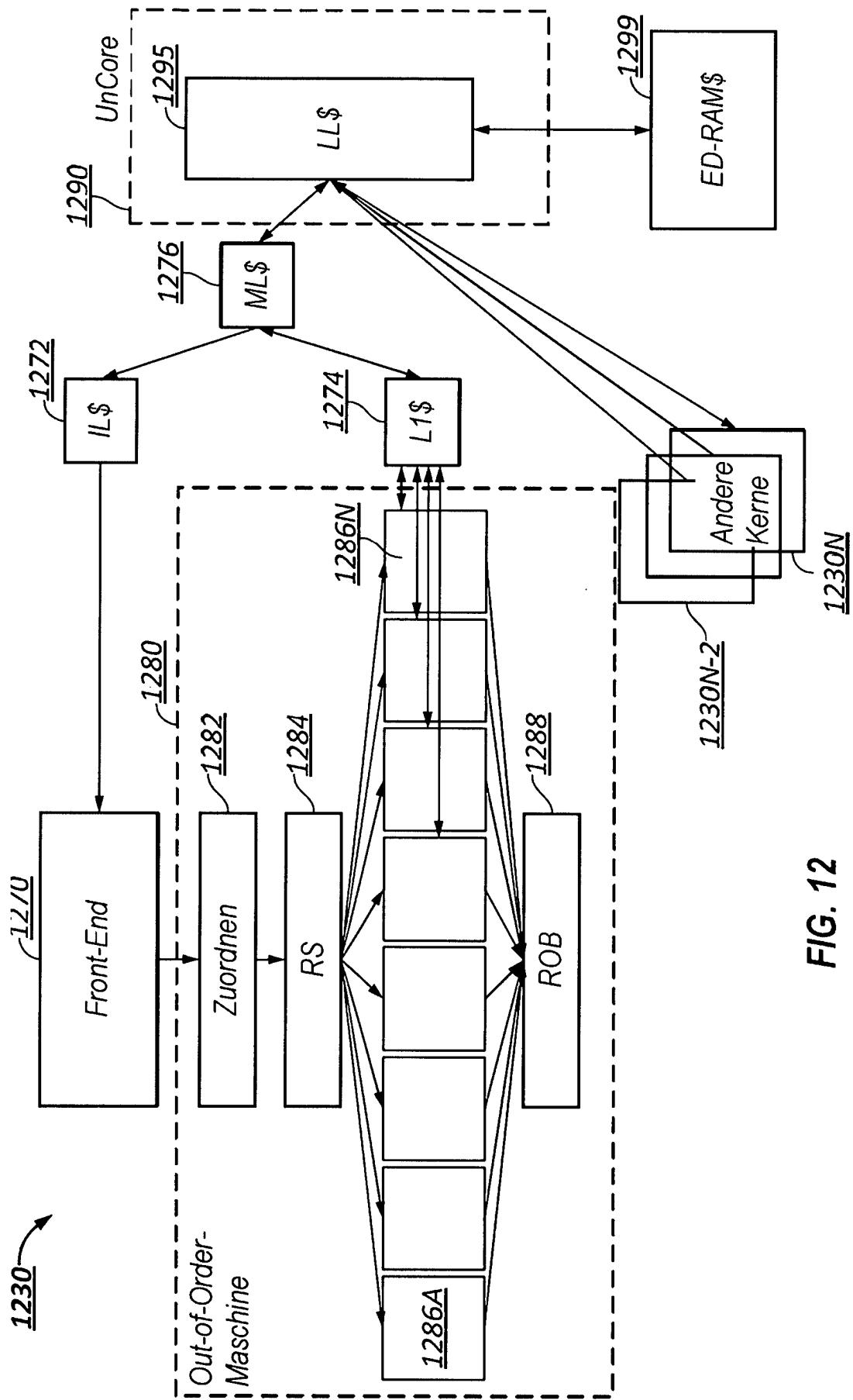

**Fig. 12** veranschaulicht eine Ausführungsform eines Blockdiagramms für einen Prozessor.

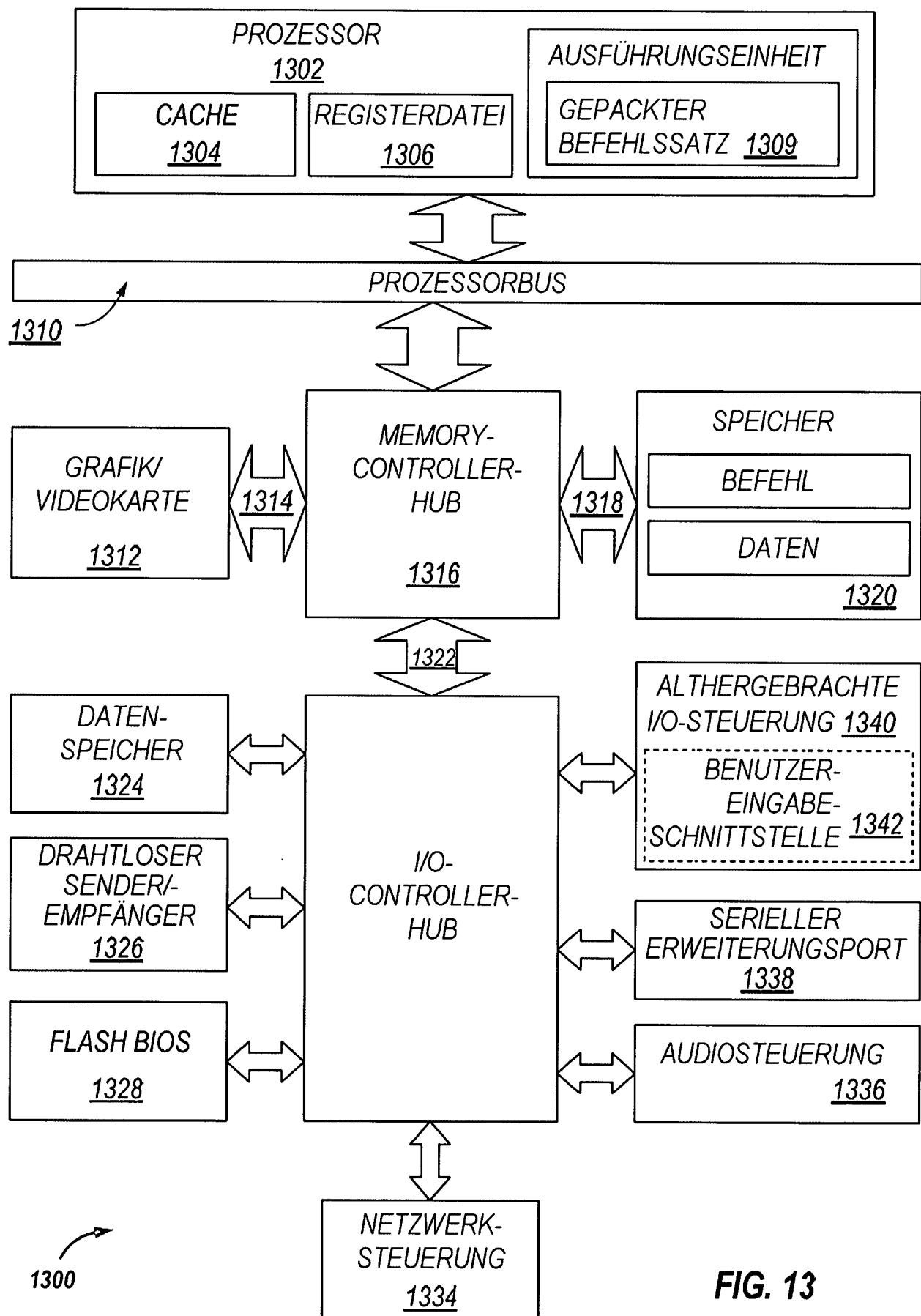

**Fig. 13** veranschaulicht eine andere Ausführungsform eines Blockdiagramms für ein Rechnersystem, das einen Prozessor enthält.

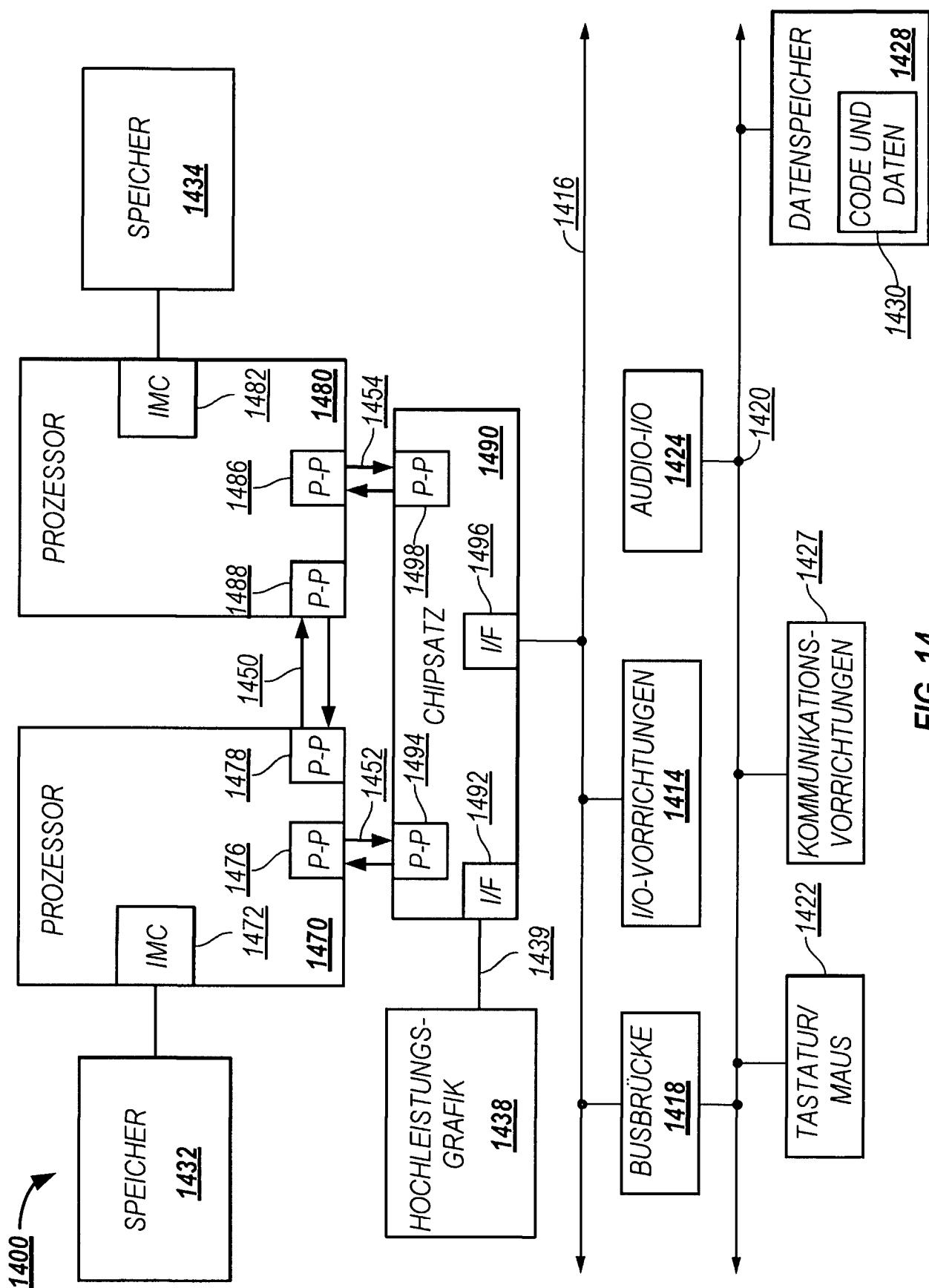

**Fig. 14** veranschaulicht eine Ausführungsform eines Blocks für ein Rechnersystem, das mehrfache Prozessoren enthält.

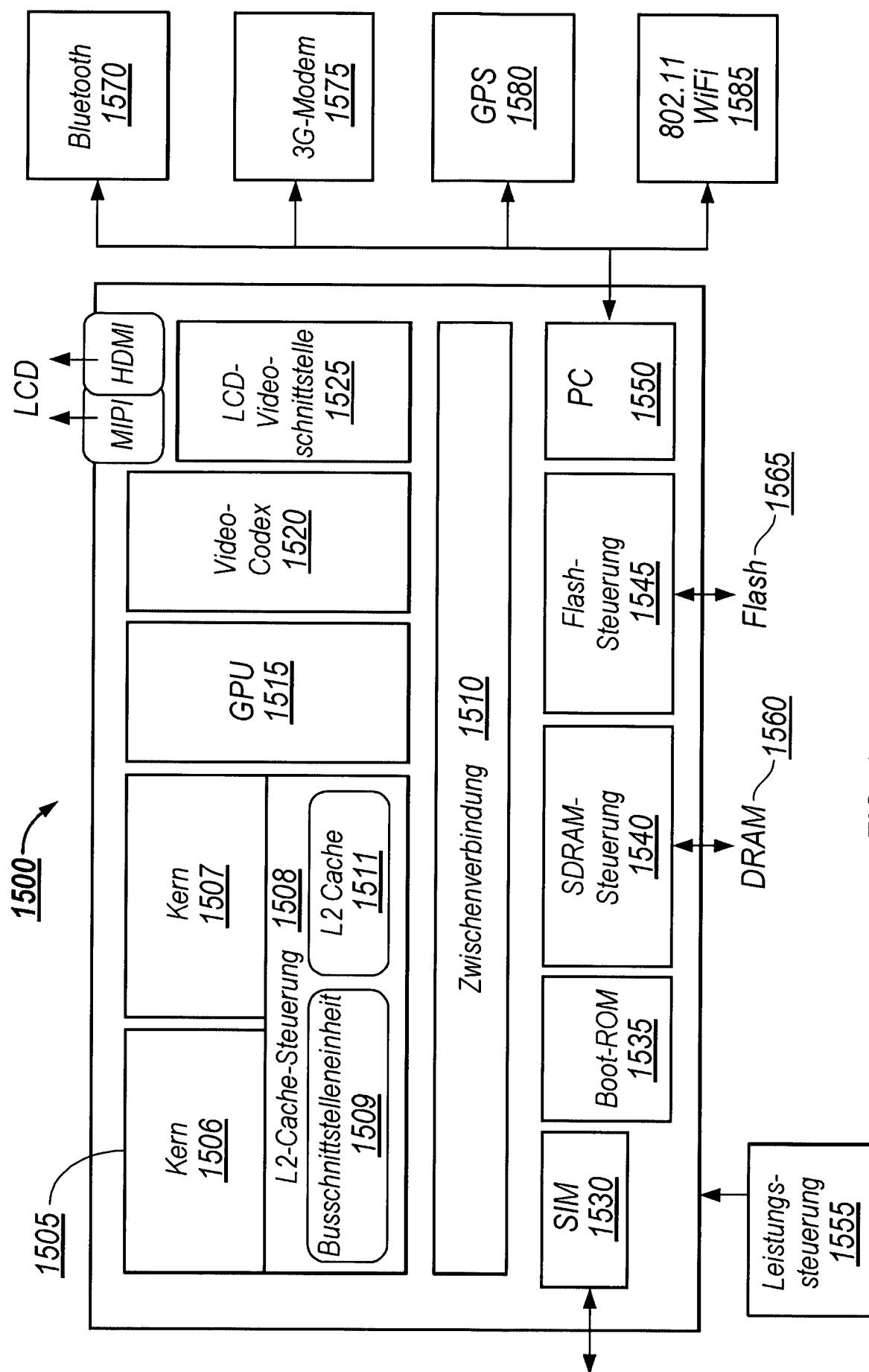

**Fig. 15** veranschaulicht ein beispielhaftes System, das als System-on-Chip (SoC) implementiert ist.

**[0008]** Gleiche Bezugszahlen und -zeichen in den verschiedenen Zeichnungen geben gleiche Elemente an.

**[0009]** In der folgenden Beschreibung sind für ein umfassendes Verständnis der vorliegenden Erfindung zahlreiche spezielle Einzelheiten angegeben, wie beispielsweise spezielle Arten von Prozessoren und Systemkonfigurationen, spezielle Hardware-Strukturen, spezielle architektonische und mikroarchitektonische Einzelheiten, spezielle Registerkonfigurationen, spezielle Befehlsarten, spezielle Systemkomponenten, spezielle Maße/Höhen, spezielle Prozessor-Pipeline-Stufen und spezieller Betrieb usw. Für den Fachmann auf dem Gebiet ist jedoch klar, dass diese speziellen Einzelheiten in der Ausführung der vorliegenden Erfindung nicht verwendet werden müssen. In anderen Beispielen sind allgemein bekannte Komponenten oder Verfahren, wie spezielle und alternative Prozessorarchitekturen, spezielle Logikschaltungen/ein spezieller Code für beschriebene Algorithmen, ein spezieller Firmware-Code, ein spezieller Zwischenverbindungsbetrieb, spezielle Logikkonfigurationen, spezielle Herstellungstechniken und -materialien, spezielle Compiler-Implementierungen, ein spezieller Ausdruck von Algorithmen in einem Code, spezielle Abschalt- und Steuerungstechniken/Logik und andere spezielle betriebliche Einzelheiten eines Computersystems nicht ausführlich beschrieben, um die vorliegende Erfindung nicht unnötig zu verschleiern.

**[0010]** Obwohl die folgenden Ausführungsformen in Bezug auf Energieeinsparung und Energieeffizienz in speziellen integrierten Schaltungen, wie Rechnerplattformen oder Mikroprozessoren, beschrieben sein können, sind andere Ausführungsformen bei anderen Arten von integrierten Schaltungen und Logikvorrichtungen anwendbar. Ähnliche Techniken und Lehren von hier beschriebenen Ausführungsformen können bei anderen Arten von Schaltungen oder Halbleitervorrichtungen angewendet werden, die auch von einer besseren Energieeffizienz und Energieeinsparung profitieren können. Zum Beispiel sind die offenbarten Ausführungsformen nicht auf Desktop-Computersysteme oder Ultrabooks™ begrenzt. Und können auch in anderen Vorrichtungen, wie in der Hand gehaltenen Vorrichtungen, Tablets, anderen dünnen Notebooks, System-on-Chip-(SOC) Vorrichtungen und eingebetteten Anwendungen verwendet werden. Einige Beispiele für in der Hand gehaltene Vorrichtungen enthalten Mobiltelefone, Internet-Protokollvorrichtungen, Digitalkameras, persönliche digitale Assistenten (PDAs) und in der Hand gehaltene PCs. Eingebettete Anwendungen enthalten typischerweise eine Mikrosteuerung, einen Digitalsignalprozessor (DSP), ein System auf einem Chip, Netzwerkcomputer (NetPC), Set-Top-Boxes, Netzwerk-Hubs, Weitverkehrsnetz- (WAN) Schalter oder jedes andere System, das die in der Folge gelehrt Funktionen und Operationen ausführen kann. Ferner sind die hier beschriebenen

Apparate, Verfahren und Systeme nicht auf physische Rechnervorrichtungen begrenzt, sondern können sich auch auf Software-Optimierungen zur Energieeinsparung und -effizienz beziehen. Wie in der folgenden Beschreibung sofort offensichtlich wird, sind die Ausführungsformen von Verfahren, Apparaten und Systemen (egal ob unter Bezugnahme auf Hardware, Firmware, Software oder eine Kombination davon) für eine Zukunft 'grüner Technologie', ausgewogen mit Leistungsüberlegungen, wesentlich.

**[0011]** Mit der Weiterentwicklung von Rechnersystemen werden die darin enthaltenen Komponenten komplexer. Infolgedessen nimmt auch die Komplexität der Zwischenverbindungsarchitektur zur Kopplung und Kommunikation zwischen den Komponenten zu um sicherzustellen, dass Bandbreitenanforderungen für einen optimalen Komponentenbetrieb erfüllt sind. Ferner verlangen unterschiedliche Marktsegmente unterschiedliche Aspekte von Zwischenverbindungsarchitekturen zur Erfüllung der Marktbedürfnisse. Zum Beispiel erfordern Server eine höhere Leistung, während das mobile Ökosystem manchmal aus Gründen der Leistungseinsparung bei der Gesamtleistung Abstriche hinnehmen kann. Dennoch ist es eine singuläre Aufgabe der meisten Matrizen, eine höchstmögliche Leistung mit einer maximalen Leistungseinsparung zu bieten. In der Folge werden zahlreiche Zwischenverbindungen besprochen, die möglicherweise von Aspekten der hier beschriebenen Erfindung profitieren würden.

**[0012]** Eine Zwischenverbindungsarchitektur enthält die Peripheral Component Interconnect (PCI) Express (PCIe) Architektur. Ein primäres Ziel von PCIe besteht darin, einen Betrieb zwischen Komponenten und Vorrichtungen von verschiedenen Verkäufern in einer offenen Architektur zu ermöglichen, wobei mehrfache Marktsegmente überspannt werden; Clients (Desktops und mobile), Server (Standard und firmeneigene) und eingebettete und Kommunikationsvorrichtungen. PCI Express ist eine Hochleistungs-, Allzweck-, I/O-Zwischenverbindung, die für eine breite Palette zukünftiger Rechner- und Kommunikationsplattformen definiert ist. Einige PCI-Attribute, wie sein Gebrauchsmodell, seine Last-Speicherarchitektur und seine Software-Schnittstellen, wurden durch seine Überarbeitungen beibehalten, während vorherige parallele Bus-Implementierungen durch eine hoch skalierbare, vollständig serielle Schnittstelle ersetzt wurden. Die jüngeren Versionen von PCI Express nutzen den Vorteil von Fortschritten in Punkt-zu-Punkt-Zwischenverbindungen, schalterbasierter Technologie und paketiertem Protokoll, um neue Leistungsebenen und Merkmale bereitzustellen. Leistungsmanagement, Dienstgüte (Quality Of Service, QoS), Hot-Plug/Hot-Swap-Unterstützung, Datenintegrität und Fehlermanagement zählen zu den weiterentwickelten Merkmalen, die von PCI Express unterstützt werden.

ment zählen zu den weiterentwickelten Merkmalen, die von PCI Express unterstützt werden.

**[0013]** Unter Bezugnahme auf **Fig. 1** ist eine Ausführungsform einer Matrix dargestellt, die aus Punkt-zu-Punkt-Verbindungen besteht, die einen Satz von Komponenten verbinden. System 100 enthält einen Prozessor 105 und einen Systemspeicher 110, der an einen Controller-Hub 115 gekoppelt ist. Der Prozessor 105 enthält jedes Verarbeitungselement, wie einen Mikroprozessor, einen Host-Prozessor, einen eingebetteten Prozessor, einen Co-Prozessor oder anderen Prozessor. Der Prozessor 105 ist an den Controller-Hub 115 durch einen Front-Side Bus (FSB) 106. In einer Ausführungsform ist der FSB 106 eine serielle Punkt-zu-Punkt-Zwischenverbindung, wie unten beschrieben. In einer anderen Ausführungsform enthält die Verbindung 106 eine serielle, differentielle Zwischenverbindungsarchitektur, die mit verschiedenen Zwischenverbindungsstandards übereinstimmt.

**[0014]** Der Systemspeicher 110 enthält jede Speichervorrichtung, wie Direktzugriffspeicher (RAM), nicht flüchtigen (NV) Speicher oder einen anderen Speicher, der für Vorrichtungen im System 100 zugänglich ist. Der Systemspeicher 110 ist durch eine Speicherschnittstelle 116 an den Controller-Hub 115 gekoppelt. Beispiele einer Speicherschnittstelle enthalten eine Doppeldatenrate- (DDR) Speicherschnittstelle, eine Dualkanal-DDR-Speicherschnittstelle und eine dynamische RAM (DRAM) Speicherschnittstelle.

**[0015]** In einer Ausführungsform ist der Controller-Hub 115 ein Root-Hub, Root-Komplex oder ein Root-Controller in einer Peripheral Component Interconnect Express (PCIe oder PCIE) Zwischenverbindungsarchitektur. Beispiele für den Controller-Hub 115 enthalten einen Chipsatz, einen Memory Controller-Hub (MCH), eine Northbridge, einen Interconnect Controller-Hub (ICH), eine Southbridge und einen Root Controller/Hub. Oftmals bezieht sich der Begriff Chipsatz auf zwei physisch getrennte Controller-Hubs, d.h., einen Memory Controller-Hub (MCH), der an einen Interconnect Controller-Hub (ICH) gekoppelt ist. Es ist zu beachten, dass derzeitige Systeme häufig den MCH mit dem Prozessor 105 integriert enthalten, während der Controller 115 mit I/O Vorrichtungen auf gleiche Weise, wie unten beschrieben, kommunizieren kann. In einigen Ausführungsformen wird optional ein Peer-zu-Peer Routing durch den Root Komplex 115 unterstützt.

**[0016]** Hier ist der Controller-Hub 115 durch eine serielle Verbindung 119 an einen Schalter/eine Brücke 120 gekoppelt. Eingangs-/Ausgangsmodule 117 und 121, die auch als Schnittstellen/Ports 117 und 121 bezeichnet werden können, enthalten/implementieren einen schichtenförmigen Protokollstapel

zum Vorsehen einer Kommunikation zwischen dem Controller-Hub 115 und dem Schalter 120. In einer Ausführungsform können mehrfache Vorrichtungen an den Schalter 120 gekoppelt werden.

**[0017]** Der Schalter/die Brücke 120 leitet Pakete-/Nachrichten von der Vorrichtung 125 stromaufwärts, d.h., eine Hierarchie nach oben hin zu einem Root-Komplex, zum Controller-Hub 115 und stromabwärts, d.h., eine Hierarchie nach unten, weg vom Root-Komplex, vom Prozessor 105 oder Systemspeicher 110 zur Vorrichtung 125. Der Schalter 120 wird in einer Ausführungsform als eine logische Zusammenstellung mehrfacher virtueller PCI-zu-PCI Überbrückungsvorrichtungen bezeichnet. Die Vorrichtung 125 enthält jede interne oder externe Vorrichtung oder Komponente, die an ein elektrisches System gekoppelt werden soll, wie eine I/O-Vorrichtung, eine Network Interface Controller (NIC), eine Erweiterungskarte, einen Audioprozessor, einen Netzwerkprozessor, ein Festplattenlaufwerk, eine Speichervorrichtung, einen CD/DVD ROM, einen Monitor, einen Drucker, eine Maus, eine Tastatur, einen Router, eine tragbare Speichervorrichtung, eine Firewire-Vorrichtung, eine Universal Serial Bus (USB) Vorrichtung, einen Scanner und andere Eingangs-/Ausgangsvorrichtungen. Häufig wird im PCIe-Jargon eine solche Vorrichtung als Endpunkt bezeichnet. Obwohl nicht im Speziellen dargestellt, kann die Vorrichtung 125 eine Brücke von PCIe zu PCI/PCI-X enthalten, um althergebrachte oder eine andere Version von PCI Vorrichtungen zu unterstützen. Endpunktvorrichtungen in PCIe sind häufig als althergebrachte, PCIe, oder Root-Komplex integrierte Endpunkte klassifiziert.

**[0018]** Es ist auch ein Grafikbeschleuniger 130 durch die serielle Verbindung 132 an den Controller-Hub 115 gekoppelt. In einer Ausführungsform ist der Grafikbeschleuniger 130 an einen MCH gekoppelt, der an einen ICH gekoppelt ist. Der Schalter 120, und somit die I/O-Vorrichtung 125, wird dann an den ICH gekoppelt. I/O-Module 131 und 118 sollen auch einen schichtenförmigen Protokollstapel für eine Kommunikation zwischen Grafikbeschleuniger 130 und Controller-Hub 115 implementieren. Ähnlich wie bei der vorangehenden Besprechung des MCH können eine Grafiksteuerung oder der Grafikbeschleuniger 130 selbst im Prozessor 105 integriert sein.

**[0019]** In Hinblick nun auf **Fig. 2** ist eine Ausführungsform eines schichtenförmigen Protokollstapels dargestellt. Der schichtenförmige Protokollstapel 200 enthält jede Form eines schichtenförmigen Kommunikationsstapels, wie einen Quick Path Interconnect (QPI) Stapel, einen PCIe-Stapel, einen Hochleistungsrechner- Zwischenverbindungsstapel der nächsten Generation oder einen anderen schichtenförmigen Stapel. Obwohl sich die unmittelbare fol-

gende Besprechung unter Bezugnahme auf **Fig. 1-4** auf einen PCIe-Stapel bezieht, können dieselben Konzepte bei anderen Zwischenverbindungsstapeln angewendet werden. In einer Ausführungsform ist der Protokollstapel 200 ein PCIe-Protokollstapel, der eine Transaktionsschicht 205, eine Verbindungsenschicht 210 und eine physische Schicht 220 enthält. Eine Schnittstelle, wie Schnittstellen 117, 118, 121, 122, 126 und 131 in **Fig. 1**, kann als Kommunikationsprotokollstapel 200 dargestellt werden. Die Darstellung als Kommunikationsprotokollstapel kann auch als Modul oder Schnittstelle bezeichnet werden, das bzw. die einen Protokollstapel implementiert/enthält.

**[0020]** PCI Express verwendet Pakete zur Kommunikation von Informationen zwischen Komponenten. In der Transaktionsschicht 205 und Datenverbindungsschicht 210 werden Pakete gebildet, um die Informationen von der sendenden Komponente zur empfangenden Komponente zu befördern. Während die gesendeten Pakete durch die anderen Schichten gehen, werden sie mit zusätzlichen Informationen erweitert, die zum Handhaben von Pakete in diesen Schichten erforderlich sind. An der Empfangsseite läuft der umgekehrte Prozess und die Pakete werden aus ihrer Darstellung in der physischen Schicht 220 in die Darstellung der Datenverbindungsschicht 210 und letztendlich (für Transaktionsschichtpakete) in die Form umgewandelt, die von der Transaktionsschicht 205 der Empfangsvorrichtung verarbeitet werden kann.

#### Transaktionsschicht

**[0021]** In einer Ausführungsform dient die Transaktionsschicht 205 zum Vorsehen einer Schnittstelle zwischen einem Verarbeitungskern einer Vorrichtung und der Zwischenverbindungsarchitektur, wie der Datenverbindungsschicht 210 und der physischen Schicht 220. In dieser Hinsicht ist eine primäre Zuständigkeit der Transaktionsschicht 205 die Zusammenstellung und Zerlegung von Paketen (d.h., Transaktionsschichtpaketen oder TLPs). Die Translationsschicht 205 verwaltet typischerweise die Credit-Based Flow Control für TLPs. PCIe implementiert geteilte Transaktionen, d.h., Transaktionen, bei welchen Anfrage und Antwort zeitlich getrennt sind, wodurch eine Verbindung anderen Verkehr befördern kann, während die Zielvorrichtung Daten für die Antwort sammelt.

**[0022]** Zusätzlich verwendet die PCIe die Credit-Based Flow Control. In diesem Schema kündigt eine Vorrichtung eine anfängliche Menge an Credits für jeden der Empfangspuffer in der Transaktionsschicht 205 an. Eine externe Vorrichtung am gegenüberliegenden Ende der Verbindung, wie der Controller-Hub 115 in **Fig. 1**, zählt die Anzahl von Credits, die von jedem TLP verbraucht wird. Eine

Transaktion kann gesendet werden, wenn die Transaktion einen Credit-Grenzwert nicht übersteigt. Bei Empfang einer Antwort wird die Credit-Menge wiederhergestellt. Ein Vorteil eines Credit-Schemas ist, dass die Latenz der Credit-Rückgabe die Leistung nicht beeinflusst, vorausgesetzt, der Credit-Grenzwert wird nicht erreicht.

**[0023]** In einer Ausführungsform enthalten vier Transaktionsadressenräume einen Konfigurationsadressenraum, einen Speicheradressenraum, einen Eingangs-/Ausgangsadressenraum und einen Nachrichtenadressenraum. Speicherraumtransaktionen enthalten eine oder mehrere Leseanfragen und Schreibanfragen zum Übertragen von Daten zu/von einer speicherabgebildeten Stelle. In einer Ausführungsform sind Speicherraumtransaktionen imstande, zwei verschiedene Adressenformate zu verwenden, z.B. ein kurzes Adressenformat, wie eine 32-Bit-Adresse, oder ein langes Adressenformat, wie eine 64-Bit-Adresse. Konfigurationsraumtransaktionen werden für einen Zugriff auf den Konfigurationsraum der PCIe-Vorrichtungen verwendet. Transaktionen zum Konfigurationsraum enthalten Leseanfragen und Schreibanfragen. Nachrichtenraumtransaktionen (oder einfach Nachrichten) sind zum Unterstützen einer Kommunikation innerhalb des Bandes zwischen PCIe-Agenten definiert.

**[0024]** Daher stellt in einer Ausführungsform die Transaktionsschicht 205 die Paketkopfzeile/Nutzlast 206 zusammen. Das Format für aktuelle Paketkopfzeilen/Nutzlasten findet sich in der PCIe-Spezifikation auf der PCIe-Spezifikationen-Website.

**[0025]** Unter Bezugnahme auf **Fig. 3** ist kurz eine Ausführungsform eines PCIe-Transaktionsdeskriptors dargestellt. In einer Ausführungsform ist der Transaktionsdeskriptor 300 ein Mechanismus zur Beförderung von Transaktionsinformationen. In dieser Hinsicht unterstützt der Transaktionsdeskriptor 300 die Identifizierung von Transaktionen in einem System. Andere mögliche Anwendungen enthalten eine Verfolgung von Modifizierungen einer vorgegebenen Transaktionsreihung und eine Zuordnung einer Transaktion mit Kanälen.

**[0026]** Der Transaktionsdeskriptor 300 enthält ein globales Kennungsfeld 302, ein Attributfeld 304 und ein Kanalkennungsfeld 306. In dem dargestellten Beispiel ist das globale Kennungsfeld 302 mit einem lokalen Transaktionskennungsfeld 308 und Quellenkennungsfeld 310 dargestellt. In einer Ausführungsform ist die globale Transaktionskennung 302 für alle ausstehenden Anfragen einzigartig.

**[0027]** Gemäß einer Implementierung ist das lokale Transaktionskennungsfeld 308 ein Feld, das von einem anfragenden Agenten generiert wird, und ist für alle ausstehenden Anfragen einzigartig, die für

diesen anfragenden Agenten vollendet werden müssen. Ferner identifiziert in diesem Beispiel die Quellenkennung 310 den anfragenden Agenten einzigartig innerhalb einer PCIe-Hierarchie. Daher sieht das lokale Transaktionskennungsfeld 308 gemeinsam mit der Quellen-ID 310 eine globale Identifizierung einer Transaktion innerhalb einer Hierarchiedomäne vor.

**[0028]** Das Attributfeld 304 spezifiziert Eigenschaften und Verhältnisse der Transaktion. In dieser Hinsicht wird das Attributfeld 304 möglicherweise zum Vorsehen zusätzlicher Informationen verwendet, die eine Modifizierung der vorgegebenen Handhabung von Transaktionen ermöglichen. In einer Ausführungsform enthält das Attributfeld 304 ein Prioritätsfeld 312, ein reserviertes Feld 314, ein Reihungsfeld 316, und ein No-Snoop-Feld 318. Hier kann ein Prioritätsteilfeld 312 von einem Initiator modifiziert werden, um der Transaktion eine Priorität zu verleihen. Das reservierte Attributfeld 314 bleibt für die Zukunft oder für eine vom Verkäufer definierte Nutzung reserviert. Mögliche Gebrauchsmodelle, die Prioritäts- oder Sicherheitsattribute verwenden, können mit Hilfe des reservierten Attributfeldes implementiert werden.

**[0029]** In diesem Beispiel wird ein Reihungsattributfeld 316 zum Zuleiten optionaler Informationen verwenden, die die Art der Reihung angeben, die vorgegebene Reihungsregeln modifizieren kann. Gemäß einer beispielhaften Implementierung gibt ein Reihungsattribut von „0“ an, dass vorgegebene Reihungsregeln gelten, wobei ein Reihungsattribut von „1“ eine entspannte Reihung angibt, wobei Schreibvorgänge Schreibvorgänge in derselben Richtung durchlaufen können und Lesevervollständigungen Schreibvorgänge in derselben Richtung durchlaufen können. Das Snoop-Attributfeld 318 wird zur Bestimmung verwendet, ob Transaktionen ausspioniert („snooped“) werden. Wie dargestellt, identifiziert das Kanal-ID-Feld 306 einen Kanal, dem eine Transaktion zugeordnet ist.

#### Verbindungsschicht

**[0030]** Die Verbindungsschicht 210, auch als Datenverbindungsschicht 210 bezeichnet, dient als Zwischenstufe zwischen der Transaktionsschicht 205 und der physischen Schicht 220. In einer Ausführungsform ist eine Zuständigkeit der Datenverbindungsschicht 210 ein Vorsehen eines zuverlässigen Mechanismus zum Austauschen von Transaktionschichtpaketen (TLPs) zwischen zwei Komponenten einer Verbindung. Eine Seite der Datenverbindungsschicht 210 akzeptiert TLPs, die von der Transaktionsschicht 205 zusammengestellt wurden, verleiht eine Paketsequenzkennung 211, d.h., eine Identifizierungsnummer oder Paketnummer, berechnet einen Fehlererkennungscode, d.h. CRC 212, und

wendet ihn an, und unterbreitet die modifizierten TLPs der physischen Schicht 220 zur Übertragung über eine physische zu einer externen Vorrichtung.

### Physische Schicht

**[0031]** In einer Ausführungsform enthält die physische Schicht 220 einen logischen Teilblock 221 und einen elektrischen Teilblock 222 zum physischen Senden eines Pakets zu einer externen Vorrichtung. Hier ist der logische Teilblock 221 für die „digitalen“ Funktionen der physischen Schicht 221 zuständig. In dieser Hinsicht enthält der logische Teilblock einen Sendeabschnitt zur Vorbereitung ausgehender Informationen, die vom physischen Teilblock 222 gesendet werden, und einen Empfangsabschnitt zum Identifizieren und Vorbereiten empfangener Informationen, bevor diese zur Verbindungsschicht 210 geleitet werden.

**[0032]** Der physische Block 222 enthält einen Sender und einen Empfänger. Dem Sender werden vom logischen Teilblock 221 Symbole zugeleitet, die der Sender serialisiert und zu einer externen Vorrichtung sendet. Dem Empfänger werden die serialisierten Symbole von einer externen Vorrichtung zugeleitet, und er wandelt die empfangenen Signale in einen Bit-Strom um. Der Bit-Strom wird entserialisiert und zum logischen Teilblock 221 geleitet. In einer Ausführungsform wird ein 8b/10b Sendungscode verwendet, wobei zehn-Bit Symbole gesendet/empfangen werden. Hier werden Spezialsymbole verwendet, um ein Paket mit Frames 223 zu versehen. Zusätzlich sieht in einem Beispiel der Empfänger auch einen Symboltakt vor, der aus dem eingehenden seriellen Strom gewonnen wird.

**[0033]** Wie oben angegeben, obwohl die Transaktionsschicht 205, die Verbindungsschicht 210 und die physische Schicht 220 in Bezug auf eine spezielle Ausführungsform eines PCIe-Protokollstapels besprochen werden, ist ein schichtenförmiger Protokollstapel nicht derart begrenzt. Tatsächlich kann jedes schichtenförmige Protokoll enthalten/implementiert sein. Als ein Beispiel enthält ein Port/eine Schnittstelle, dargestellt als ein schichtenförmiges Protokoll: (1) eine erste Schicht zum Zusammenstellen von Paketen, d.h., eine Transaktionsschicht; eine zweite Schicht zur Reihung von Paketen, d.h., eine Verbindungsschicht; und eine dritte Schicht zum Senden der Pakete, d.h., eine physische Schicht. Als ein spezielles Beispiel wird ein schichtenförmiges Protokoll einer allgemeinen Standardschnittstelle (Common Standard Interface, CSI) verwendet.

**[0034]** Unter Bezugnahme im Anschluss auf **Fig. 4** ist eine Ausführungsform einer seriellen Punkt-zu-Punkt-PCIe-Matrix dargestellt. Obwohl eine Ausführungsform einer seriellen Punkt-zu-Punkt-PCIe-Verbindung dargestellt ist, ist eine serielle Punkt-zu-

Punkt-Verbindung nicht derart begrenzt, da sie jeden Sendepfad zum Senden serieller Daten enthält. In der dargestellten Ausführungsform enthält eine grundlegende PCIe-Verbindung zwei unterschiedliche angesteuerte Niederspannungssignalpaare: ein Sendungspaar 406/411 und ein Empfangspaar 412/407. Daher enthält die Vorrichtung 405 eine Sendelogik 406 zum Senden von Daten zur Vorrichtung 410 und eine Empfangslogik 407 zum Empfangen von Daten von der Vorrichtung 410. Mit anderen Worten, in einer PCIe-Verbindung sind zwei Sendepfade, d.h., Pfade 416 und 417, und zwei Empfangspfade, d.h., Pfade 418 und 419, enthalten.

**[0035]** Ein Sendepfad bezieht sich auf jeden Pfad zum Senden von Daten, wie eine Sendeleitung, eine Kupferleitung, eine optische Leitung, einen drahtlosen Kommunikationskanal, eine Infrarot-Kommunikationsverbindung oder einen anderen Kommunikationspfad. Eine Anbindung zwischen zwei Vorrichtungen, wie Vorrichtung 405 und Vorrichtung 410, wird als Verbindung bezeichnet, wie Verbindung 415. Eine Verbindung kann eine Spur unterstützen - wobei jede Spur einen Satz unterschiedlicher Signalpaare darstellt (ein Paar zum Senden, ein Paar zum Empfangen). Zur Skalierung der Bandbreite kann eine Verbindung mehrfache Spuren zusammenfassen, die mit xN bezeichnet sind, wobei N jede unterstützte Verbindungsbreite, wie 1, 2, 4, 8, 12, 16, 32, 64 oder breiter, ist.

**[0036]** Ein unterschiedliches Paar bezieht sich auf zwei Sendepfade, wie Leitungen 416 und 417, zum Senden unterschiedlicher Signale. Als ein Beispiel, wenn die Leitung 416 von einem Niederspannungspegel zu einem Hochspannungspegel wechselt, d.h., eine ansteigende Flanke, steuert die Leitung 417 von einem hohen Logikpegel zu einem niederen Logikpegel, d.h., eine abfallende Flanke. Unterschiedliche Signale zeigen möglicherweise bessere elektrische Eigenschaften, wie eine bessere Signalintegrität, d.h., Kreuzkopplung, Spannungsüberschreitung/-unterschreitung, Ringing, usw. Dies erlaubt ein beseres Zeitsteuerungsfenster, das schnellere Sendefrequenzen ermöglicht.

**[0037]** Physische Schichten bestehender Zwischenverbindungs- und Kommunikationsarchitekturen, einschließlich PCIe, können aufgebaut werden, um gemeinsam benutzte Speicher- und I/O-Dienste in einem System vorzusehen. Üblicherweise können cachebare Speicher nicht zwischen unabhängigen Systemen unter Verwendung herkömmlicher Last-/Speicher- (LD/ST) Speichersemantik geteilt werden. Ein unabhängiges System oder ein „Knoten“, kann in dem Sinn unabhängig sein, dass es bzw. er als eine einzige logische Einheit funktioniert, von einem einzigen Betriebssystem (und/oder einem einzigen BIOS oder Virtual Machine Monitor (VMM)) gesteuert

wird und/oder eine unabhängige Fehlerdomäne hat. Ein einzelner Knoten kann eine oder mehrere Prozessorvorrichtung(en) enthalten, kann auf einer einzigen Platine oder mehreren Platinen implementiert sein und einen lokalen Speicher, einschließlich eines cachebaren Speichers, enthalten, auf den mit Hilfe von LD/ST-Semantik durch die Vorrichtungen auf demselben Knoten zugegriffen werden kann. In einem Knoten kann ein gemeinsam benutzter Speicher einen Speicherblock oder mehrere Speicherblöcke enthalten, wie einen Direktzugriffsspeicher (RAM), auf den mehrere verschiedene Prozessoren (z.B. zentrale Verarbeitungseinheiten (CPUs)) in einem Knoten zugreifen können. Ein gemeinsam benutzter Speicher kann auch den lokalen Speicher der Prozessoren oder anderer Vorrichtungen im Knoten enthalten. Die mehrfachen Vorrichtungen in einem Knoten mit einem gemeinsam benutzten Speicher können sich eine einzelne Ansicht von Daten im gemeinsam benutzten Speicher teilen. Die I/O-Kommunikation, die den gemeinsam benutzten Speicher beinhaltet, kann eine sehr geringe Latenz aufweisen und einen raschen Zugang zum Speicher durch die mehrfachen Prozessoren ermöglichen.

**[0038]** Üblicherweise hat eine gemeinsame Speicherbenutzung zwischen verschiedenen Knoten nach einem Last-/Speicherparadigma keine gemeinsame Speicherbenutzung ermöglicht. Zum Beispiel wurde in einigen Systemen eine gemeinsame Speicherbenutzung zwischen verschiedenen Knoten durch verteilte Speicherarchitekturen erleichtert. In herkömmlichen Lösungen bearbeiten Rechenaufgaben lokale Daten und wenn Daten eines anderen Knotens erwünscht sind, kommuniziert die Rechenaufgabe (die z.B. von einem anderen CPU-Knoten ausgeführt wird) mit dem anderen Knoten zum Beispiel über einen Kommunikationskanal, der einen Kommunikationsprotokollstapel, wie Ethernet, InfiniBand oder ein anderes schichtenförmiges Protokoll verwendet. In herkömmlichen Mehrfachknotensystemen muss den Prozessoren verschiedener Knoten nicht bewusst sein, wo die Daten liegen. Eine gemeinsame Datenbenutzung unter Verwendung herkömmlicher Methoden, wie über einen Protokollstapel, kann eine signifikant höhere Latenz als eine gemeinsame Speicherbenutzung in einem Knoten haben, der ein Last-/Speicherparadigma verwendet. Anstatt eines direkten Adressierens und Bearbeitens von Daten in einem gemeinsam benutzten Speicher kann ein Knoten, neben anderen Beispielen, Daten von einem anderen mit Hilfe eines bestehenden Protokoll-Handshakes wie Ethernet (oder Infiniband) anfragen und der Quellenknoten kann die Daten bereitstellen, so dass die Daten durch den anfragenden Knoten gespeichert und bearbeitet werden können.

**[0039]** In einigen Implementierungen, kann eine gemeinsam benutzte Speicherarchitektur vorgese-

hen sein, die eine gemeinsame Speicherbenutzung zwischen unabhängigen Knoten für einen ausschließlichen oder gemeinsamen Zugang unter Verwendung einer Last-/Speicher- (LD/ST) Speichersemantik ermöglicht. In einem Beispiel können die Speichersemantik (und, falls zutreffend, Verzeichnissinformationen) und I/O-Semantik (für Protokolle wie PCIe) entweder auf einen gemeinsamen Satz von Pins oder einen separaten Satz von Pins exportiert werden. In einem solchen System kann jeder von mehreren Knoten in einem System die verbesserte, gemeinsam benutzte Speicherarchitektur, um seine eigene unabhängige Fehlerdomäne (und lokalen Speicher) beizubehalten, während ein gemeinsam benutzter Speicherpool für einen Zugang durch den Knoten und eine Nachrichtübermittlung niedriger Latenz, die zwischen Knoten läuft, unter Verwendung eines Speichers nach der LD/ST-Semantik möglich ist. In einigen Implementierungen kann ein solcher, gemeinsam benutzter Speicherpool dynamisch (oder statisch) zwischen verschiedenen Knoten zugeordnet werden. Daher können die verschiedenen Knoten eines Systems als sich dynamisch ändernde Gruppen von Knoten konfiguriert werden, die bei Bedarf gemeinsam und flexibel verschiedene Aufgaben bearbeiten, welche zum Beispiel die gemeinsam benutzte Speicherinfrastruktur verwenden.

**[0040]** In Hinblick nun auf **Fig. 5A** ist ein vereinfachtes Blockdiagramm 500a dargestellt, das ein beispielhaftes System zeigt, das einen gemeinsam benutzten Speicher 505 enthält, auf den mit Hilfe von Last-/Speichertechniken von jedem der mehreren unabhängigen Knoten 510a-510n zugegriffen werden kann. Zum Beispiel kann eine Steuerung 515 des gemeinsam benutzten Speichers 505 vorgesehen sein, die Last-/Speicherzugangsanfragen der verschiedenen Knoten 510a-510n auf dem System annehmen kann. Der gemeinsam benutzte Speicher 505 kann durch Verwendung eines synchronen dynamischen Direktzugriffsspeichers (SDRAM), dualer In-line-Speichermodule (DIMM) und eines anderen nicht flüchtigen Speichers (oder flüchtigen Speichers) implementiert sein.

**[0041]** Jeder Knoten kann selbst eine oder mehrere CPU-Buchse(n) haben und kann auch einen lokalen Speicher enthalten, der von einem LD/ST-Zugang durch andere Knoten im System isoliert bleibt. Der Knoten kann mit anderen Vorrichtungen auf dem System (z.B. der Steuerung 515 des gemeinsam benutzten Speichers 505, der Netzwerksteuerung 520, einem anderen Knoten, usw.) unter Verwendung eines Protokolls oder mehrerer Protokolle, einschließlich PCIe, QPI, Ethernet, neben anderen Beispielen, kommunizieren. In einigen Implementierungen kann ein Verbindungsprotokoll des gemeinsam benutzten Speichers (SML-Protokoll) vorgesehen sein, durch das eine LD/ST-Spei-

chersemantik niedriger Latenz unterstützt werden kann. Zum Beispiel kann SML in der Kommunikation von Lese- und Schreibvorgängen eines gemeinsam benutzten Speichers 505 (durch die Steuerung 515 des gemeinsam benutzten Speichers 505) von den verschiedenen Knoten 510a-510n eines Systems verwendet werden.

**[0042]** In einem Beispiel kann die SML auf einem Speicherzugangsprotokoll, wie Scalable Memory Interconnect (SMI) der 3. Generation (SMI3), basieren. Alternativ können andere Speicherzugangsprotokolle verwendet werden, wie transaktionale Speicherzugangsprotokolle, wie, neben anderen Beispielen, ein vollständig gepuffertes DIMM (FB-DIMM), DDR transaktional (DDR-T). In anderen Fällen kann die SML auf einer nativen PCIe-Speicherlese-/schreibsemantik mit zusätzlichen Verzeichnisweiterungen basieren. Eine auf einem Speicherprotokoll basierte Implementierung der SML kann Vorteile in der Bandbreiteneffizienz bieten, da sie auf Cachezeilen-Speicherzugänge zugeschnitten ist. Während Hochleistungskommunikationsprotokolle zwischen Vorrichtungen bestehen, wie PCIe, können obere Schichten (z.B. Transaktions- und Verbindungsschichten) solcher Protokolle eine Latenz einführen, die die Anwendung des vollständigen Protokolls zur Verwendung in LD/ST-Speichertransaktionen verschlechtert, einschließlich Transaktionen, die einen gemeinsam benutzten Speicher 505 beinhalten. Ein Speicherprotokoll, wie SMI3, kann einen möglichen zusätzlichen Vorteil bedeuten, indem Zugänge mit niedriger Latenz geboten werden, da es den Großteil eines anderen Protokollstapels, wie PCIe, umgehen kann. Daher können SMI-Implementierungen SMI3 oder ein anderes Speicherprotokoll nutzen, das auf einer logischen und physischen PHY eines anderen Protokolls, wie SMI3 on PCIe, läuft.

**[0043]** Wie festgehalten wurde, kann in einigen Implementierungen eine Steuerung 515 des gemeinsam benutzten Speichers (SMC) vorgesehen sein, die eine Logik zur Bearbeitung von Last-/Speicheranfragen von Knoten 510a-510n im System enthält. Last-/Speicheranfragen können von der SMC 515 über Verbindungen empfangen werden, die die SML verwenden und die Knoten 510a-510n mit der SMC 515 verbinden. In einigen Implementierungen kann die SMC 515 als eine Vorrichtung implementiert sein, wie eine anwendungsspezifische integrierte Schaltung (ASIC), einschließlich einer Logik zum Bedienen der Zuganganfragen der Knoten 510a-510n für gemeinsam benutzte Speicherressourcen. In anderen Fällen kann die SMC 515 (wie auch der gemeinsam benutzte Speicher 505) auf einer Vorrichtung, einem Chip oder einer Platine, getrennt von einem oder mehreren (oder sogar allen) der Knoten 510a-510n liegen. Die SMC 515 kann ferner eine Logik zum Koordinieren verschiede-

ner Transaktionen der Knoten enthalten, die den gemeinsam benutzten Speicher 505 beinhalten. Zusätzlich kann die SMC einen Verzeichnisverfolgungszugang zu verschiedenen Datenressourcen führen, wie jede Cachezeile, die im gemeinsam benutzten Speicher 505 enthalten sind. Zum Beispiel kann eine Datenressource, unter anderen möglichen Beispielen, in einem gemeinsam benutzten Zugangszustand (z.B. imstande, dass mehrere Verarbeitungs- und/oder I/O-Vorrichtungen in einem Knoten gleichzeitig zugreifen (z.B. geladen oder gelesen)), einem ausschließlichen Zugangszustand (z.B. ausschließlich, wenn nicht temporär von einer einzigen Verarbeitungs- und/oder I/O-Vorrichtung in einem Knoten (z.B. für einen Speicher- oder Schreibvorgang) reserviert), einem Nicht-Cache-Zustand sein. Während ferner jeder Knoten einen direkten Zugang zu einem oder mehreren Abschnitt(en) eines gemeinsam benutzten Speichers 505 haben kann, können verschiedene Adressierungsschemata und -werte von den verschiedenen Knoten (z.B. 510a-510n) verwendet werden, was dazu führt, dass im selben gemeinsam benutzten Speicher von einem ersten Knoten gemäß einem ersten Adressenwert und einem zweiten Knoten, der auf dieselben Daten durch einen zweiten Adressenwert verweist, auf Daten (z.B. in einem Befehl) verwiesen wird. Die SMC 515 kann eine Logik enthalten, die Datenstrukturen beinhaltet, die Adressen der Knoten auf gemeinsam benutzte Speicherressourcen abbildet, so dass die SMC 515 die verschiedenen Zugangsanfragen der verschiedenen Knoten interpretieren kann.

**[0044]** Zusätzlich kann in einigen Fällen ein gewisser Teil des gemeinsam benutzten Speichers (z.B. gewisse Trennungen, Speicherblöcke, Aufzeichnungen, Dateien, usw.) gewissen Genehmigungen, Regeln und Zuordnungen unterliegen, so dass nur ein Teil der Knoten 510a-510n (z.B. durch die SMC 515) auf entsprechende Daten zugreifen kann. Tatsächlich kann jede gemeinsam benutzte Speicherressource einem entsprechenden (und in einigen Fällen anderen) Teilsatz der Knoten 510a-510n des Systems zugeordnet werden. Diese Zuordnungen können dynamisch sein und die SMC 515 kann solche Regeln und Genehmigungen (z.B. auf Anfrage, dynamisch, usw.) modifizieren, um neue oder geänderte Regeln, Genehmigungen, Knotenzuordnungen und Eigentumsrecht anzupassen, die für einen bestimmten Teil des gemeinsam benutzten Speichers 505 gelten.

**[0045]** Eine beispielhafte SMC 515 kann ferner verschiedene Transaktionen verfolgen, die Knoten (z.B. 510a-510n) im System beinhalten, die auf eine oder mehrere gemeinsam benutzte Speicherressourcen zugreifen. Zum Beispiel kann die SMC 515 Informationen für jede Transaktion eines gemeinsam benutzten Speichers 505 verfolgen, einschließlich einer

Identifizierung des (der) Knoten(s), der (die) an der Transaktion beteiligt ist (sind), des Fortlaufs der Transaktion (z.B. ob sie vollendet ist), neben anderen Transaktionsinformationen. Dies kann ermöglichen, dass einige der transaktionsorientierten Aspekte herkömmlicher verteilter Speicherarchitekturen bei der hier beschriebenen, verbesserten, gemeinsam benutzten Mehrfachknoten-Speicherarchitektur angewendet werden. Zusätzlich kann eine Transaktionsverfolgung (z.B. von der SMC) verwendet werden, eine Aufrechterhaltung oder Durchsetzung der separaten und unabhängigen Fehlerdomänen jedes entsprechenden Knoten zu unterstützen. Zum Beispiel kann die SMC die entsprechende Knoten-ID für jede laufende Transaktion in ihren internen Datenstrukturen, einschließlich im Speicher, verwalten und diese Informationen verwenden, um Zugangsrechte durchzusetzen und einzelne Fehlerdomänen für jeden Knoten zu verwalten. Wenn einer der Knoten abgeschaltet wird (z.B. aufgrund eines kritischen Fehlers, einer ausgelösten Wiederherstellungssequenz oder eines anderen Fehlers oder Ereignisses), werden daher nur dieser Knoten und seine Transaktionen, die den gemeinsam benutzten Speicher 505 beinhalten, unterbrochen (z.B. von der SMC fallengelassen) - Transaktionen der übrigen Knoten, die den gemeinsam benutzten Speicher 505 beinhalten, laufen unabhängig von dem Fehler in dem anderen Knoten weiter.

**[0046]** Ein System kann mehrfache Knoten enthalten. Zusätzlich können einige beispielhafte Systeme mehrfache SMCs enthalten. In einigen Fällen kann ein Knoten imstande sein, auf einen gemeinsam benutzten Speicher jenseits einer fernen SMC zuzugreifen, mit welcher er nicht direkt verbunden ist (d.h., die lokale SMC des Knotens ist mit der fernen SMC durch einen oder mehrere SML-Verbindungs-Hops verbunden). Die ferne SMC kann sich in derselben Platine befinden oder könnte sich in einer anderen Platine befinden. In einigen Fällen können einige der Knoten abseits des Systems sein (z.B. abseits der Platine oder abseits des Chips), aber dennoch auf einen gemeinsam benutzten Speicher 505 zugreifen. Zum Beispiel, können ein oder mehrere Knoten abseits des Systems unter Verwendung einer SML-konformen Verbindung, neben anderen Beispielen, direkt an die SMC angeschlossen sein. Zusätzlich können andere Systeme, die ihre eigene SMC und einen gemeinsam benutzten Speicher enthalten, auch mit der SMC 510 verbunden sein, um eine gemeinsame Benutzung des Speichers 505 auf Knoten zu erweitern, die zum Beispiel auf einer anderen Platine enthalten sind, die eine Schnittstelle mit der anderen SMC hat, die mit der SMC über eine SML-Verbindung verbunden ist. Ferner können Netzwerkverbindungen durchgetunnelt sein, um den Zugang auf die anderen Knoten abseits der Platine oder abseits des Chips zu erweitern. Zum Beispiel kann die SML über eine Ethernet-Verbindung (die

z.B. durch die Netzwerksteuerung 520 bereitgestellt ist) tunneln, die das beispielhafte System von **Fig. 5A** kommunikativ mit einem anderen System koppelt, das auch einen oder mehrere andere Knoten enthält, und diesen Knoten ebenso einen Zugang zur SMC 515 und dadurch zum gemeinsam benutzten Speicher 505, neben anderen Beispielen, ermöglichen.

**[0047]** Als weiteres Beispiel, wie in dem vereinfachten Blockdiagramm 500b von **Fig. 5B** dargestellt, kann eine verbesserte, gemeinsam benutzte Speicherarchitektur, die einen gemeinsamen Zugang durch mehrfache unabhängige Knoten gemäß einer LD/ST-Speichersemantik ermöglicht, flexibel ein Vorsehen einer Reihe verschiedener Mehrfachknotensystemdesigns ermöglichen. Es können verschiedene Kombinationen der mehrfachen Knoten zugeordnet werden, um Teile eines gemeinsam benutzten Speicherblocks oder mehrerer gemeinsam benutzten Speicherblöcke gemeinsam zu benutzen, die in einem beispielhaften System vorgesehen sind. Zum Beispiel kann ein anderes beispielhaftes System, das in dem Beispiel von **Fig. 5B** dargestellt ist, mehrfache Vorrichtungen 550a-550d enthalten, die zum Beispiel als separate Dies, Platinen, Chips, usw. implementiert sind, wobei jede Vorrichtung einen oder mehrere unabhängige CPU-Knoten (z.B. 510a-510h) enthält. Jeder Knoten kann seinen eigenen lokalen Speicher enthalten. Eine oder mehrere der mehrfachen Vorrichtungen 550a-550d können ferner einen gemeinsam benutzten Speicher enthalten, auf den zwei oder mehr der Knoten 510a-510h des Systems zugreifen können.

**[0048]** Das in **Fig. 5B** dargestellte System ist ein Beispiel, das zur Veranschaulichung eines Teils der Variabilität vorgesehen ist, die durch eine verbesserte, gemeinsam benutzte Speicherarchitektur erreicht werden kann, wie hier dargestellt und beschrieben. Zum Beispiel kann jede von einer Vorrichtung A 550a und Vorrichtung C 550c ein entsprechendes gemeinsam benutztes Speicherelement (z.B. 505a, 505b) enthalten. Daher kann in einigen Implementierungen jedes gemeinsam benutzte Speicherelement auf einer eigenen Vorrichtung ferner eine entsprechende Steuerung 515a, 515b des gemeinsam benutzten Speichers (SMC) enthalten. Verschiedene Kombinationen von Knoten 510a-510h können kommunikativ an jede SMC (z.B. 515a, 515b) gekoppelt sein, wodurch die Knoten Zugang zu dem entsprechenden gemeinsam benutzten Speicher (z.B. 505a, 505b) erlangen. Als ein Beispiel kann die SMC 515a von Vorrichtung A 550a mit den Knoten 510a, 510b auf Vorrichtung A unter Verwendung einer direkten Datenverbindung, die SML unterstützt, verbunden sein. Zusätzlich können andere Knoten 510c auf einer anderen Vorrichtung (z.B. Vorrichtung C 550c) auch durch eine direkte, hartverdrahtete Verbindung (die SML unterstützt) vom Knoten 510c (und/oder seiner Vorrich-

tung 550c) zur SMC 515a Zugang zum gemeinsam benutzten Speicher 505a haben. Indirekte, auf dem Netzwerk basierende und andere derartige Verbindungen können auch verwendet werden, um Knoten (z.B. 510f-510h) einer fernen Vorrichtung oder abseits der Platine (z.B. Vorrichtung D 550d) die Verwendung eines herkömmlichen Protokollstapels zu ermöglichen, um eine Schnittstelle mit der SMC 515a zu haben, um ebenso auf den gemeinsam benutzten Speicher 505a Zugang zu haben. Zum Beispiel kann ein SML-Tunnel 555 über eine Ethernet-, InfiniBand- oder andere Verbindung errichtet werden, die Vorrichtung A und Vorrichtung D koppelt. Während der Errichtung und Aufrechterhaltung kann der Tunnel einen gewissen zusätzlichen Mehraufwand und eine Latenz im Vergleich zur SML einführen, die auf anderen, weniger durch Software verwalteten physischen Verbindungen läuft, wobei der SML-Tunnel 555, wenn er errichtet ist, wie andere SML-Kanäle arbeiten und dem Knoten 510f-510h ermöglichen kann, eine Schnittstelle mit der SMC 515a über SML zu haben und auf den gemeinsam benutzten Speicher 505a zuzugreifen, wie dies jeder andere Knoten kann, der mit der SMC über eine SML-Verbindung kommuniziert. Zum Beispiel können Zuverlässigkeit und Reihung der Pakete in den SML-Kanälen entweder durch die netzwerkenden Komponenten im System durchgesetzt werden oder können Ende zu Ende zwischen den SMCs durchgesetzt werden.

**[0049]** In einem weiteren anderen Beispiel können Knoten (z.B. 515d, 515e) auf einer Vorrichtung, die sich von jener unterscheidet, die einen bestimmten Teil des gemeinsam benutzten Speichers (z.B. 505a) beherbergt, indirekt mit der entsprechenden SMC (z.B. SMC 515a) durch eine direkte Verbindung mit einer anderen SMC (z.B. 515b) verbunden sein, die selbst (z.B. unter Verwendung einer SML Verbindung) an die entsprechende SMC (z.B. 515a) gekoppelt ist. Ein Verbinden von zwei oder mehr SMCs (z.B. 515a, 515b) kann effektiv die Menge an verfügbarem gemeinsam benutzten Speicher erhöhen, die den Knoten 510a-510h auf dem System zur Verfügung steht. Zum Beispiel kann aufgrund einer Verbindung zwischen SMCs 515a, 515b im Beispiel von **Fig. 5B** in einigen Implementierungen jeder der Knoten (z.B. 510a-510c, 510f-510h), der auf einen gemeinsam benutzten Speicher 505a durch die SMC 515a zugreifen kann, auch möglicherweise auf einen gemeinsam benutzbaren Speicher 505b aufgrund der Verbindung zwischen der SMC 515a und der SMC 515b zugreifen. Ebenso kann in einigen Implementierungen jeder der Knoten, die direkt auf die SMC 515b zugreifen kann, auch auf einen gemeinsam benutzbaren Speicher 505a aufgrund der Verbindung zwischen den SMCs 515a, 515b zugreifen, neben anderen möglichen Beispielen.

**[0050]** Wie oben festgehalten wurde, kann eine verbesserte, gemeinsam benutzte Speicherarchitektur ein Verbindungsprotokoll niedriger Latenz (d.h., SML) auf der Basis eines Speicherzugangsprotokolls, wie SMI3, enthalten und vorgesehen sein, um Last-/Speicheranfragen zu erleichtern, die den gemeinsam benutzten Speicher beinhalten. Während das traditionelle SMI3 und andere Speicherzugangsprotokolle zur Verwendung in einer gemeinsamen Speicherbenutzung innerhalb eines einzigen Knotens konfiguriert sein können, kann die SML die Speicherzugangssemantik auf mehrfache Knoten erweitern, um eine gemeinsame Speicherbenutzung zwischen den mehrfachen Knoten zu ermöglichen. Ferner kann die SML möglicherweise auf jeder physischen Kommunikationsverbindung verwendet werden. Die SML kann ein Speicherzugangsprotokoll verwenden, das eine LD/ST-Speichersemantik unterstützt, die auf eine physische Schicht (und entsprechende physische Schichtlogik) aufgelegt ist, die dazu angepasst ist, verschiedene Vorrichtungen (und Knoten) miteinander zu verbinden. Zusätzlich kann eine physische Schichtlogik der SML neben anderen Merkmalen keine Paketverlust- und Fehlerwiederholungsfunktionalität vorsehen.

**[0051]** In einigen Implementierungen kann die SML durch Auflegen des SMI3 auf ein PCIe PHY implementiert sein. Eine SML-Verbindungsschicht kann (z.B. anstelle einer traditionellen PCIe-Verbindungsenschicht) vorgesehen sein, um auf eine Strömungssteuerung und andere Merkmale zu verzichten und einen Speicherzugang niedriger Latenz zu erleichtern, wie für traditionelle CPU-Speicherzugangsarchitekturen charakteristisch wäre. In einem Beispiel kann die SML-Verbindungsschichtlogik zwischen Transaktionen mit dem gemeinsam benutzten Speicher und anderen Transaktionen multiplexen. Zum Beispiel kann die SML-Verbindungsschichtlogik zwischen SMI3- und PCIe-Transaktionen multiplexen. Zum Beispiel kann das SMI3 (oder ein anderes Speicherprotokoll) auf einer PCIe (oder anderen Zwischenverbindungsprotokoll) liegen, so dass die Verbindung dynamisch zwischen SMI3- und PCIe-Transaktionen wechseln kann. Dies ermöglicht, dass in einigen Fällen traditioneller PCIe-Verkehr gleichzeitig auf derselben Verbindung wie SML-Verkehr vorhanden ist.

**[0052]** In Hinblick nun auf **Fig. 6** ist eine Darstellung 600 gezeigt, die eine erste Implementierung von SML veranschaulicht. Zum Beispiel kann die SML durch Auflegen eines SMI3 auf eine PCIe PHY implementiert sein. Die physische Schicht kann eine Standard-PCIe 128b/130b verwenden, die für alle Aktivitäten der physischen Schicht codiert, einschließlich Verbindungstraining- wie auch PCIe-Datenblöcke. Die SML kann einen Verkehr auf den Spuren (z.B. Lane0 - Lane7) der zu multiplexenden Verbindung zwischen PCIe-Paketen und SMI3-Flits vorsehen.

Zum Beispiel kann in der in **Fig. 6** dargestellten Implementierung die Sync-Kopfzeile der PCIe 128b/130b Codierung modifiziert sein und zur Anzeige verwendet werden, dass SMI3-Flits und nicht PCIe-Pakete auf den Spuren der Verbindung gesendet werden. In der traditionellen PCIe 128b/130b Codierung können gültige Sync-Kopfzeilen (z.B. 610) das Senden entweder eines 10b Musters auf allen Spuren der Verbindung (zur Anzeige, dass die Art von Nutzlast des Blocks der PCIe-Datenblock sein soll) oder eines 01b Musters auf allen Spuren der Verbindung (zur Anzeige, dass die Art von Nutzlast des Blocks der PCIe gereihte Block-satz sein soll) enthalten. In einem Beispiel einer SML kann eine alternative Sync-Kopfzeile zur Unterscheidung eines SMI3-Flit Verkehrs von PCIe-Datenblöcken und gereihten Sätzen definiert sein. In einem Beispiel, das in **Fig. 6** dargestellt ist, kann die PCIe 128b/130b Sync-Kopfzeile (z.B. 605a, 605b) mit abwechselnden 01b, 10b Mustern auf ungeraden/geraden Spuren codiert sein um anzugeben, dass SMI3-Flits gesendet werden sollen. In einer anderen alternativen Implementierung, kann die 128b/130b Sync-Kopfzeile, die für SMI3-Verkehr codiert, durch abwechselnde 10b, 01b Muster auf ungeraden/geraden Spuren, neben anderen beispielhaften Codierungen, definiert sein. In einigen Fällen können SMI3-Flits unmittelbar nach der SMI3 Sync-Kopfzeile auf einer pro-Byte-Basis gesendet werden, wobei der Übergang zwischen PCIe- und SMI3-Protokollen an der Blockgrenze erfolgt.

**[0053]** In einigen Implementierungen, wie jenen, die in dem Beispiel von **Fig. 6** gezeigt sind, kann der Übergang zwischen den Protokollen so definiert sein, dass er an der Blockgrenze erfolgt, unabhängig davon, ob er einer SMI3-Flit- oder PCIe-Paketgrenze entspricht. Zum Beispiel kann ein Block so definiert sein, dass er eine vordefinierte Datenmenge (z.B. 16 Symbole, 128 Bytes, usw.) enthält. Wenn in solchen Implementierungen die Blockgrenze nicht einer SMI3-Flit- oder PCIe-Paketgrenze entspricht, kann die Sendung eines gesamten SMI3-Flits unterbrochen werden. Ein unterbrochenes SMI3-Flit kann im nächsten SMI3-Block wiederaufgenommen werden, was durch das Senden einer anderen Sync-Kopfzeile angezeigt wird, die für SMI3 codiert ist.

**[0054]** In Hinblick nun auf **Fig. 7A** ist eine Darstellung 700 gezeigt, die eine andere beispielhafte Implementierung einer SML veranschaulicht. In dem Beispiel von **Fig. 7A** können anstelle einer Verwendung einer spezialisierten Sync-Kopfzeile, die Signalübergänge zwischen Speicherzugangs- und Zwischenverbindungsprotokollverkehr codiert, physische Schicht-Framing-Tokens verwendet werden. Ein Framing-Token (oder „Token“) kann eine Dateneinkapselung auf der physischen Schicht sein, die die Anzahl von Symbolen spezifiziert oder impliziert, die in einem Datenstrom enthalten sein soll, der mit

dem Token verknüpft ist. Folglich kann das Framing-Token angeben, dass ein Strom beginnt, wie auch implizieren, wo er enden wird, und kann daher auch zum Angeben der Stelle des nächsten Framing-Tokens verwendet werden. Ein Framing-Token eines Datenstroms kann sich im ersten Symbol (Symbol 0) der ersten Spur (z.B. Spur 0) des ersten Datenblocks des Datenstroms befinden. In dem Beispiel von PCIs können fünf Framing-Tokens definiert sein, die das TLP-Verkehrsstart- (STP) Token, Datenstromende- (EDS) Token, Schlechtes-Ende- (EDB) Token, DLLP-Start- (SDP) Token und logischen Leerlauf- (IDL) Token enthalten.

**[0055]** In dem Beispiel von **Fig. 7A** kann die SML durch Auflegen eines SMI3- oder anderen Datenzugangsprotokolls auf eine PCIe implementiert sein und der Standard-PCIe STP-Token kann so modifiziert sein, dass er einen neuen STP-Token definiert, der angibt, dass SMI3 (anstelle von TLP-Verkehr) auf den Spuren der Verbindung beginnen wird. In einigen Beispielen können Werte von Reserve-Bits des Standard-PCIe STP-Tokens modifiziert werden, um das SMI3 STP-Token in SML zu definieren. Wie ferner in **Fig. 7B** dargestellt ist, kann ein STP-Token 705 mehrere Felder enthalten, einschließlich eines 710 Feldes, das die Länge der SMI3-Nutzlast (im Sinne der Anzahl von Flits) angibt, die folgen wird. In einigen Implementierungen können eine oder mehrere Standardnutzlastlängen für TLP-Daten definiert sein. SMI3-Daten können in einigen Implementierungen so definiert sein, dass sie eine festgesetzte Anzahl von Flits enthalten, oder in anderen Fällen eine variable Anzahl von Flits enthalten, wobei in diesem Fall das Längenfeld für die Anzahl von SMI3-Flits ein Feld wird, das vernachlässigt werden kann. Ferner kann das Längenfeld für ein SMI3 STP als eine Länge definiert sein, die sich von jener der definierten TLP-Nutzlastlängen unterscheidet. Daher kann ein SMI3 STP, als ein Beispiel, auf der Basis eines Nicht-TLP-Längenwerts angegeben sein, der im STP-Längenfeld vorhanden ist. Zum Beispiel können in einer Implementierung die oberen 3-Bits des 11-Bit STP-Längenfeldes auf 111b gesetzt sein, um das SMI3 Paket anzugeben (z.B. basierend auf der Annahme, dass kein spezifikationskonformes PCIe TLP lang genug sein kann, um eine Länge aufzuweisen, wo die oberen 3 Bits des Längenfelds jeweils zu „1“ führen würden). Andere Implementierungen können andere Felder des STP-Tokens verändern oder codieren, um ein PCIe STP-Token, das eine traditionelle PCIe TLP-Datennutzlast identifiziert, von einem SMI3 STP-Token zu unterscheiden, das angibt, dass SMI3-Daten in TLP-Daten eingekapselt sind.

**[0056]** Unter erneuter Bezugnahme auf das Beispiel von **Fig. 7A** können, Sync-Kopfzeilendaten der Codierung folgen, die für eine traditionelle PCIe 128b/130b Codierung spezifiziert ist. Zum Beispiel werden bei 715a-c Sync-Kopfzeilen mit einem Wert

10b empfangen, die anzeigen, dass Datenblöcke bevorstehen. Wenn ein PCIe STP (z.B. 720) empfangen wird, wird eine PCIe-TLP-Nutzlast erwartet, und der Datenstrom wird entsprechend verarbeitet. In Übereinstimmung mit der Nutzlastlänge, die im PCIe STP 720 identifiziert ist, kann die PCIe-TLP-Nutzlast die volle zugewiesene Nutzlastlänge nutzen. Ein anderes STP-Token kann im Wesentlichen zur selben Zeit innerhalb eines Datenblocks empfangen werden, der dem Ende der TLP-Nutzlast folgt. Zum Beispiel kann bei 725 ein SMI3 STP empfangen werden, das einen Übergang von PCIe-TLP-Daten zu SMI3-Flit Daten signalisiert. Das SMI3 STP kann zum Beispiel gesendet werden, sobald ein Ende der PCIe-Paketdaten identifiziert ist.

**[0057]** In Fortsetzung mit dem Beispiel von **Fig. 7A** kann, wie bei den PCIe-TLP-Daten, das SMI3 STP 725 eine Länge der SMI3-Flit-Nutzlast definieren, die folgen soll. Zum Beispiel kann die Nutzlastlänge der SMI3-Daten der Anzahl von SMI3-Flits im Sinne von DW entsprechen, die folgen sollen. Ein Fenster (das z.B. bei Symbol 15 von Spur 3 endet), das der Nutzlastlänge entspricht, kann dadurch auf den Spuren definiert sein, in welchen nur SMI3-Daten während des Fensters gesendet werden sollen. Wenn sich das Fenster schließt, können andere Daten gesendet werden, wie ein anderes PCIe STP, das wiederbeginnt, TLP-Daten oder andere Daten, wie einen gereihten Datensatz, zu senden. Wie zum Beispiel in dem Beispiel von **Fig. 7A** dargestellt, wird ein EDS-Token nach dem Ende des SMI3-Datenfensters gesendet, das durch das SMI3 STP-Token 725 definiert ist. Das EDS-Token kann das Ende des Datenstroms signalisieren und implizieren, dass ein gereihter Blocksatz folgen wird, wie im Falle des Beispiels von **Fig. 7A**. Eine Sync-Kopfzeile 740, die 01b codiert ist, wird gesendet um anzugeben, dass ein gereihter Blocksatz gesendet werden soll. In diesem Fall wird ein gereihter PCIe-SKP-Satz gesendet. Solche gereihten Sätze können periodisch oder in eingestellten Intervallen oder Fenstern gesendet werden, so dass verschiedene Aufgaben auf PHY-Ebene und eine Koordination durchgeführt werden können, einschließlich eines Initialisierens einer Bit-Ausreichung, eines Initialisierens einer Symbolausrichtung, eines Austausches von PHY-Parametern, eines Kompensierens verschiedener Bit-Raten für zwei kommunizierende Ports, neben anderen Beispielen. In einigen Fällen kann ein angeordneter gereihter Satz gesendet werden, um ein definiertes Fenster oder einen Datenblock, der für SMI3-Flit-Daten spezifiziert ist, durch ein entsprechendes SMI3 STP-Token zu unterbrechen.

**[0058]** Obwohl im Beispiel von **Fig. 7A** nicht ausdrücklich dargestellt, kann ein STP-Token auch für einen Übergang von SMI3-Flit Daten auf der Verbindung zu PCIe-TLP-Daten verwendet werden. Zum Beispiel kann nach dem Ende eines definierten

SMI3 Fensters ein PCIe STP-Token (z.B. ähnlich dem Token 720) gesendet werden um anzugeben, dass das nächste Fenster zum Senden einer spezifizierten Menge an PCIe-TLP-Daten dient.

**[0059]** Speicherzugangs-Flits (z.B. SMI3-Flits) können in einigen Ausführungsformen in der Größe variieren, wodurch es schwierig wird vorherzusagen, wie viele Daten im entsprechenden STP-Token (z.B. SMI3 STP-Token) für die Speicherzugangsnutzlast zu reservieren sind. Als ein Beispiel, wie in **Fig. 7** dargestellt, kann das SMI3 STP 725 ein Längenfeld haben, das anzeigt, dass erwartet wird, dass 244 Bytes SMI3-Daten dem SMI3 STP 725 folgen. In diesem Beispiel jedoch sind nur zehn Flits (z.B. SMI3-Flits 0-9) zur Sendung während des Fensters bereit und diese zehn SMI3-Flits verwenden nur 240 der 244 Bytes. Daher verbleiben vier (4) Bytes leere Bandbreite und diese werden mit IDL-Token gefüllt. Dies kann insbesondere suboptimal sein, wenn PCIe-TLP-Daten in einer Warteschlange sind und auf ein Schließen des SMI3-Fensters warten. In anderen Fällen kann das für die Sendung von SMI3-Flits vorgesehene Fenster unzureichend sein, um die Menge an SMI3-Daten zu senden, die für die Spur bereit ist. Es können Entscheidungstechniken zur Bestimmung verwendet werden, wie zwischen SMI3- und PCIe-TLP-Daten entschieden wird, die gleichzeitig auf der Verbindung vorhanden sind. Ferner kann in einigen Implementierungen die Länge der SMI3-Fenster dynamisch modifiziert werden, um eine effizientere Verwendung der Verbindung zu unterstützen. Zum Beispiel kann eine Entscheidungs- oder andere Logik überwachen, wie gut die definierten SMI3-Fenster zur Bestimmung genutzt werden, ob die definierte Fensterlänge besser angeht als der für die Spur erwarteten Menge an SMI3 (und konkurrierenden PCIe-TLP-Verkehr) optimiert werden kann. Daher können in solchen Implementierungen die Längenfeldwerte von SMI3 STP-Token abhängig von der Menge an Verbindungsbandbreite, der SMI3-Flit Daten zugewiesen werden sollten (z.B. relativ zu anderen PCIe-Daten, einschließlich TLP-, DLLP-Daten und eines gereihten Datensatzes), neben anderen Beispielen, dynamisch (z.B. zwischen verschiedenen Werten) eingestellt werden.

**[0060]** In Hinblick nun auf **Fig. 8** ist eine Darstellung 800 einer anderen beispielhaften Implementierung einer SML dargestellt. In dieser alternativen Ausführungsform kann die SML verschachtelte SMI3- und PCIe-Protokolle durch ein modifiziertes PCIe-Framing-Token vorsehen. Wie oben festgehalten wurde, kann ein EDS-Token in der PCIe zum Anzeigen eines Endes eines Datenstroms und zum Anzeigen, dass der nächste Block ein gereihter Blocksatz sein wird, verwendet werden. In dem Beispiel von **Fig. 8** kann die SML eine SMI3 EDS-Token (z.B. 805) definieren, der das Ende eines TLP-Datenstroms und den Übergang zu SMI3-Flit-Sendungen

anzeigt. Ein SMI3 EDS (z.B. 805) kann durch Codieren eines Teils der reservierten Bits des traditionellen EDS-Tokens definiert werden, um anzuzeigen, dass SMI3-Daten folgen werden und nicht gereihte PCIe-Sätze oder andere Daten, die einem PCIe EDS folgen. Anders als beim traditionellen EDS-Token kann der SMI3 EDS im Wesentlichen überall in einem PCIe-Datenblock gesendet werden. Dies kann eine zusätzliche Flexibilität beim Senden von SMI3-Daten und Aufnehmen entsprechender Transaktionen mit dem gemeinsam benutzten Speicher geringer Latenz ermöglichen. Zum Beispiel kann ein Übergang von PCIe zu SMI3 mit einem einzelnen Doppelwort (DW) an Mehraufwand erfolgen. Ferner kann, wie bei traditionellen EDS-Token, ein beispielhaftes SMI3 EDS keine Länge spezifizieren, die mit den SMI3-Daten verknüpft ist, die dem Token folgen sollen. Nach einem SMI3 EDS können PCIe-TLP-Daten enden und SMI3-Flits auf der Verbindung fortfahren. Der SMI3-Verkehr kann fortfahren, bis die SMI3-Logik die Steuerung zur PCIe-Logik zurückstellt. In einigen Implementierungen bewirkt ein Senden eines SMI3 EDS, dass die Steuerung von der PCIe-Logik zur SMI3-Logik geht, die zum Beispiel auf Vorrichtungen vorgesehen ist, die mit der Verbindung verbunden sind.

**[0061]** In einem Beispiel kann SMI3 (oder ein anderes Protokoll) seine eigene Verbindungssteuerungssignalisierung zur Verwendung in der Durchführung einer Verbindungsschichtsteuerung definieren. Zum Beispiel kann in einer Implementierung die SML eine spezialisierte Version eines SMI3-Verbindungs-schichtsteuerungs- (LLCTRL) Flits (z.B. 810) definieren, der einen Übergang vom SMI3- zurück zum PCIe-Protokoll anzeigt. Wie beim SMI3 EDS kann der definierte LLCTRL-Flit (z.B. 810) bewirken, dass die Steuerung von der SMI3-Logik zur PCIe-Logik zurückgeht. In einigen Fällen, wie im Beispiel von **Fig. 8** gezeigt, kann der LLCTRL-Flit (z.B. 810) mit einer vordefinierten Anzahl von LLCTRL-Leerlauf-(LLCTRL-IDLE) Flits (z.B. 815) ausgestattet werden, bevor der Übergang zur PCIe vollendet wird. Zum Beispiel kann die Anzahl von LLCTRL-IDLE Flits 815, die zum Ausstatten des SMI3 LLCTRL-Flits 810 gesendet wird, von der Latenz zum Decodieren des definierten SMI3 LLCTRL-Flits 810, das den Übergang signalisiert, abhängen. Nach Vollendung des Übergangs zurück zur PCIe kann ein STP-Paket gesendet werden und TLP-Paketdaten können wieder auf der Verbindung unter der Steuerung der PCIe beginnen.

**[0062]** Es sollte klar sein, dass die hier beschriebenen Implementierungen als Beispiele vorgesehen sind, um gewisse Prinzipien und Merkmale zu zeigen, die in der Patentschrift offenbart sind. Es sollte klar sein, dass alternative Konfigurationen, Protokolle, und Architekturen (neben jenen, die spezifisch in den Beispielen besprochen sind) solche Prinzipien

und Merkmale verwenden und anwenden können. Als ein Beispiel für eine Alternative kann ein PCIe-Speicherlese-/schreibvorgang (z.B. anstelle eines SMI3-Protokolls) verwendet werden, der mit Verzeichnungsinformationen verstärkt ist. Die Verzeichnisinformationen können durch Reserve-Bits des PCIe-Pakets implementiert werden. In einem anderen Beispiel kann der CPU-Knoten eine Cache-Steuerung (z.B. als eine Alternative zu einer Steuerung des gemeinsam benutzten Speichers) zum Senden von Speicherlese-/schreibtransaktionen auf einer PCIe-Verbindung verwenden, zum Beispiel auf der Basis einer fernen Adressenbereichsprüfung, unter anderen möglichen Beispielen und Alternativen.

**[0063]** In Hinblick nun auf **Fig. 9A-9D** sind Ablaufdiagramme 900a-d dargestellt, die beispielhafte Techniken zur Kommunikation unter Verwendung eines MCPL zeigen. Zum Beispiel kann in **Fig. 9A** eine Last-/Speicher-Speicherzugangsnachricht von einem ersten Knoten empfangen werden 905, wobei die Nachricht bestimmte Daten eines gemeinsam benutzten Speichers anfragt. Ein Zugang zu den bestimmten Daten kann für den ersten Knoten vorgesehen werden 910. Eine zweite Last-/Speicher-Speicherzugangsnachricht kann von einem zweiten unabhängigen Knoten empfangen werden 915. Die zweite Nachricht kann eine Anfrage für einen Zugang zu denselben bestimmten Daten des gemeinsam benutzten Speichers sein und ein Zugang zu den bestimmten Daten kann für den zweiten Knoten vorgesehen werden 920. Daten im gemeinsam benutzten Speicher können somit von mehrfachen verschiedenen unabhängigen Knoten gemeinsam benutzt werden und für diese zugänglich sein.

**[0064]** In dem Beispiel von **Fig. 9B** kann eine erste Sync-Kopfzeile (wie eine PCIe-Sync-Kopfzeile) mit einer ersten Codierung empfangen werden 925. Die Codierung kann einen Übergang von einem Zwischenverbindungsprotokoll zu einem Speicherzugangspraktokoll anzeigen und der Übergang kann aus der ersten Sync-Kopfzeile identifiziert werden 930. Daten des Speicherzugangspraktokolls können nach der ersten Sync-Kopfzeile empfangen werden und die Daten können verarbeitet werden 935 (z.B. in Übereinstimmung mit dem Speicherzugangspraktokoll). In einigen Beispielen können die Speicherzugangspraktokolldaten Transaktionen enthalten, die einen gemeinsam benutzten Speicher beinhalten, der von mehreren mehrfacher unabhängigen Knoten gemeinsam benutzt wird. Eine zweite Sync-Kopfzeile kann empfangen werden 940, die eine zweite, andere Codierung enthält, die einen Übergang vom Zwischenverbindungsprotokoll anzeigt. Der Übergang vom Speicherzugangspraktokoll zurück zum Zwischenverbindungsprotokoll kann aus der zweiten Sync-Kopfzeile identifiziert werden 945.

**[0065]** In Hinblick nun auf **Fig. 9C** kann in einigen Fällen ein erster Datenstart-Token (z.B. ein PCIe STP-Token) empfangen werden 950, der einen oder mehrere Werte enthält, die zum Identifizieren eines Übergangs von einem Zwischenverbindungsprotokoll zu einem Speicherzugangsprotokoll codiert sind. Daten des Speicherzugangsprotokolls können nach dem ersten Datenstart-Token eintreffen und können identifiziert werden 955. Die Daten des Speicherzugangsprotokolls können verarbeitet werden 960. Ein Längenfeld kann im ersten Datenstart-Token enthalten sein, das anzeigt, wann Daten zu Zwischenverbindungsprotokolldaten zurückgehen. Tatsächlich kann in einigen Implementierungen das Längenfeld eines Datenstart-Tokens codiert sein, um eine Länge anzuzeigen, die den Daten des Speicherzugangsprotokolls entspricht. Ferner kann ein zweites, anderes Datenstart-Framing-Token definiert sein, das so zu interpretieren ist, dass er einem Eintreffen von Daten des Zwischenverbindungsprotokolls entspricht. Jeder von dem ersten und zweiten Datenstart-Framing-Token kann nach dem Zwischenverbindungsprotokoll (z.B. PCIe), neben anderen Beispielen, definiert sein.

**[0066]** In dem Beispiel von **Fig. 9D** kann ein Stromende-Token (z.B. ein spezialisierter PCIe EDS-Token) empfangen werden 965, der zum Anzeigen eines Übergangs zu Speicherzugangsprotokolldaten codiert ist. Das empfangene Stromende-Token kann einen Übergang 970 von der Verbindungsschichtlogik zur Verarbeitung von Zwischenverbindungsprotokolldaten zur Verbindungsschichtlogik zur Verarbeitung von Speicherzugangsprotokolldaten veranlassen. Daten des Speicherzugangsprotokolls können empfangen werden 975 und unter Verwendung der Verbindungsschichtlogik des Speicherzugangsprotokolls verarbeitet werden. Verbindungsschichtsteuerungsdaten des Speicherzugangsprotokolls können empfangen werden 980 (z.B. am Ende der Daten des Speicherzugangsprotokolls), um einen Übergang zu Daten des Zwischenverbindungsprotokolls anzuzeigen. Ein Empfang 980 der Verbindungsschichtsteuerungsdaten kann einen Übergang 985 von der Verbindungsschichtlogik des Speicherzugangsprotokolls zur Verbindungsschichtlogik des Zwischenverbindungsprotokolls veranlassen. Daten des Zwischenverbindungsprotokolls können nach den Verbindungsschichtsteuerungsdaten empfangen werden und können von der Verbindungsschichtlogik des Zwischenverbindungsprotokolls nach dem Übergang 985, neben anderen Beispielen, verarbeitet werden.

**[0067]** Es sollte festgehalten werden, dass, obwohl ein Großteil der Prinzipien und Beispiele im Zusammenhang mit PCIe und insbesondere Überarbeitungen der PCIe-Spezifikation beschrieben sind, die hier beschriebenen Prinzipien, Lösungen und Merk-

male gleichermaßen bei anderen Protokollen und Systemen anwendbar sein können. Zum Beispiel können analoge Spurfehler in anderen Verbindungen, die andere Protokolle verwenden, auf der Basis analoger Symbole, Datenströme und Token, wie auch Regeln, die für die Verwendung, Anordnung und Formatierung solcher Strukturen innerhalb von Daten spezifiziert sind, die über dies anderen Verbindungen gesendet werden, erfasst werden. Ferner können alternative Mechanismen und Strukturen (z.B. neben einem PCIe LES Register oder SKP OS) zum Vorsehen einer Spurfehlererfassung und Meldefunktionalität in einem System verwendet werden. Ferner können Kombinationen der obenannten Lösungen in Systemen angewendet werden, einschließlich, neben anderen Beispielen, Kombinationen logischer und physischer Verstärkungen an einer Verbindung und ihrer entsprechenden Logik wie hier beschrieben.

**[0068]** Es ist zu beachten, dass die oben beschriebenen Apparate, Verfahren und Systeme in jeder elektronischen Vorrichtung oder jedem System, wie oben erwähnt, implementiert sein können. Als spezielle Veranschaulichung sehen die folgenden Figuren beispielhafte Systeme zur Nutzung der Erfindung, wie hier beschrieben, vor. Da die folgenden Systeme ausführlicher beschrieben sind, ist eine Anzahl von verschiedenen Zwischenverbindungen offenbart, beschrieben und aus der vorangehenden Besprechung wieder erwähnt. Und es ist sofort offensichtlich, dass die oben beschriebenen Weiterentwicklungen bei jeder dieser Zwischenverbindungen, Matrizen oder Architekturen angewendet werden können.

**[0069]** Unter Bezugnahme auf **Fig. 10** ist eine Ausführungsform eines Blockdiagramms für ein Rechnersystem, das einen Mehrfachkern-Prozessor enthält, dargestellt. Der Prozessor 1000 enthält einen beliebigen Prozessor oder eine beliebige Verarbeitungsvorrichtung, wie einen Mikroprozessor, einen eingebetteten Prozessor, einen Digitalsignalprozessor (DSP), einen Netzwerkprozessor, einen in der Hand gehaltenen Prozessor, einen Anwendungsprozessor, einen Co-Prozessor, ein System auf einem Chip (SOC) oder eine andere Vorrichtung zur Ausführung eines Codes. Der Prozessor 1000 enthält in einer Ausführungsform zumindest zwei Kerne - Kern 1001 und 1002, die asymmetrische Kerne oder symmetrische Kerne (die dargestellte Ausführungsform) enthalten können. Der Prozessor 1000 kann jedoch eine beliebige Anzahl von Verarbeitungselementen enthalten, die symmetrisch oder asymmetrisch sein können.

**[0070]** In einer Ausführungsform bezieht sich ein Verarbeitungselement auf eine Hardware oder Logik zur Unterstützung eines Software-Thread. Beispiele von Hardware-Verarbeitungselementen ent-

halten: eine Thread-Einheit, einen Thread-Slot, einen Thread, eine Prozesseinheit, einen Kontext, eine Kontexteinheit, einen logischen Prozessor, einen Hardware-Thread, einen Kern und/oder jedes andere Element, das imstande ist, einen Zustand für einen Prozessor zu halten, wie einen Ausführungs- zustand oder architektonischen Zustand. Mit anderen Worten, ein Verarbeitungselement bezieht sich in einer Ausführungsform auf jede Hardware, die imstande ist, unabhängig mit einem Code, wie einem Software-Thread, Betriebssystem, einer Anwendung oder einem anderen Code verknüpft zu werden. Ein physischer Prozessor (oder eine Prozessorbuchse) bezieht sich typischerweise auf eine integrierte Schaltung, die möglicherweise eine beliebige Anzahl anderer Verarbeitungselemente, wie Kerne oder Hardware-Threads, enthält.