【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第4区分

【発行日】平成21年1月8日(2009.1.8)

【公開番号】特開2007-317344(P2007-317344A)

【公開日】平成19年12月6日(2007.12.6)

【年通号数】公開・登録公報2007-047

【出願番号】特願2007-28894(P2007-28894)

【国際特許分類】

|         |       |           |

|---------|-------|-----------|

| G 1 1 C | 19/28 | (2006.01) |

| G 0 9 G | 3/36  | (2006.01) |

| G 0 9 G | 3/20  | (2006.01) |

| G 0 2 F | 1/133 | (2006.01) |

| G 1 1 C | 19/00 | (2006.01) |

【F I】

|         |       |         |

|---------|-------|---------|

| G 1 1 C | 19/28 | D       |

| G 0 9 G | 3/36  |         |

| G 0 9 G | 3/20  | 6 2 2 E |

| G 0 9 G | 3/20  | 6 2 1 F |

| G 0 9 G | 3/20  | 6 7 0 E |

| G 0 9 G | 3/20  | 6 1 1 J |

| G 0 2 F | 1/133 | 5 5 0   |

| G 1 1 C | 19/00 | J       |

| G 1 1 C | 19/00 | G       |

【手続補正書】

【提出日】平成20年11月14日(2008.11.14)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

入力端子、出力端子、第1クロック端子およびリセット端子と、

前記第1クロック端子に入力される第1クロック信号を前記出力端子に供給する第1トランジスタと、

前記入力端子に入力される信号に基づいて前記第1トランジスタの制御電極を充電し、前記リセット端子に入力される信号に基づいて前記第1トランジスタの制御電極を放電することにより当該第1トランジスタを駆動する駆動回路と、

前記第1トランジスタの制御電極が放電された状態のときに、前記第1クロック信号に基づいて前記第1トランジスタの制御電極と前記出力端子との間を導通させるスイッチング回路とを備える

ことを特徴とするシフトレジスタ回路。

【請求項2】

請求項1記載のシフトレジスタ回路であって、

前記スイッチング回路は、

前記出力端子と前記第1トランジスタの制御電極との間に接続した第2トランジスタである

ことを特徴とするシフトレジスタ回路。

**【請求項 3】**

請求項 2 記載のシフトレジスタ回路であって、

前記第 2 トランジスタの制御電極は、前記第 1 クロック端子に接続している

ことを特徴とするシフトレジスタ回路。

**【請求項 4】**

請求項 2 記載のシフトレジスタ回路であって、

前記第 1 クロック信号の振幅を所定値だけ小さくしてから前記第 2 トランジスタの制御

電極に供給するレベル調整回路をさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項 5】**

請求項 4 記載のシフトレジスタ回路であって、

前記レベル調整回路は、

前記第 2 トランジスタの制御電極と前記第 1 クロック端子との間に接続し、前記第 2 ト

ランジスタの制御電極から前記第 1 クロック端子への方向を放電方向とする一方向性のス

イッチング素子を備える

ことを特徴とするシフトレジスタ回路。

**【請求項 6】**

請求項 4 または請求項 5 記載のシフトレジスタ回路であって、

前記レベル調整回路は、

前記第 2 トランジスタの制御電極と前記第 1 クロック端子との間に接続し、前記第 1 ク

ロック端子から前記第 2 トランジスタの制御電極への方向を充電方向とするようにダイオ

ード接続された第 3 トランジスタと、

前記第 1 クロック信号とは位相が異なる第 2 クロック信号が入力される制御電極を有し

、前記第 2 トランジスタの制御電極を放電する第 4 トランジスタとを備える

ことを特徴とするシフトレジスタ回路。

**【請求項 7】**

請求項 6 記載のシフトレジスタ回路であって、

前記レベル調整回路は、前記第 3 トランジスタを複数個備え、

前記複数の第 3 トランジスタは、前記第 2 トランジスタの制御電極と前記第 1 クロック

端子との間に互いに直列に接続している

ことを特徴とするシフトレジスタ回路。

**【請求項 8】**

請求項 1 から請求項 7 のいずれか記載のシフトレジスタ回路であって、

前記第 1 トランジスタの制御電極が接続するノードを入力ノードとし、前記第 1 クロック

信号とは位相が異なる第 3 クロック信号により活性化されるインバータと、

前記インバータの出力に基づいて前記第 1 トランジスタの制御電極を放電する第 5 トラ

ンジスタとをさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項 9】**

請求項 1 から請求項 7 のいずれか記載のシフトレジスタ回路であって、

前記入力端子を入力ノードとし、前記第 1 クロック信号とは位相が異なる第 3 クロック

信号により活性化されるインバータと、

前記インバータの出力に基づいて前記第 1 トランジスタの制御電極を放電する第 5 トラ

ンジスタとをさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項 10】**

請求項 8 または請求項 9 記載のシフトレジスタ回路であって、

前記第 5 トランジスタは、前記第 1 トランジスタの制御電極と前記第 1 クロック端子と

の間に接続している

ことを特徴とするシフトレジスタ回路。

**【請求項 1 1】**

請求項 8 から請求項 10 のいずれか記載のシフトレジスタ回路であって、

前記インバータは、

当該インバータの前記出力ノードと所定の第1電源端子との間に接続し、その制御電極が当該インバータの前記入力ノードとなる第6トランジスタと、

前記出力ノードと前記第3クロック信号が供給される第2クロック端子との間に接続し、当該第2クロック端子に接続した制御電極を有する第7トランジスタとを備えることを特徴とするシフトレジスタ回路。

**【請求項 1 2】**

請求項 8 から請求項 10 のいずれか記載のシフトレジスタ回路であって、

前記インバータは、

当該インバータの前記出力ノードと所定の第1電源端子との間に接続し、その制御電極が当該インバータの前記入力ノードとなる第6トランジスタと、

前記出力ノードと所定の第2電源端子との間に接続し、前記第3クロック信号が供給される第2クロック端子に接続した制御電極を有する第7トランジスタとを備えることを特徴とするシフトレジスタ回路。

**【請求項 1 3】**

請求項 1 1 または請求項 1 2 記載のシフトレジスタ回路であって、

前記インバータが非活性になるときに、当該インバータの前記出力ノードを放電する第8トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

**【請求項 1 4】**

請求項 1 3 記載のシフトレジスタ回路であって、

前記第8トランジスタは、

前記インバータの前記出力ノードと前記第1電源端子との間に接続し、前記第1クロック端子に接続した制御電極を有するものである

ことを特徴とするシフトレジスタ回路。

**【請求項 1 5】**

請求項 1 3 記載のシフトレジスタ回路であって、

前記第8トランジスタは、

前記インバータの前記出力ノードと前記第2クロック端子との間に接続し、前記第1クロック端子に接続した制御電極を有するものである

ことを特徴とするシフトレジスタ回路。

**【請求項 1 6】**

請求項 1 3 記載のシフトレジスタ回路であって、

前記第8トランジスタは、

前記インバータの前記出力ノードと前記第2クロック端子との間に接続し、前記出力ノードに接続した制御電極を有するものである

ことを特徴とするシフトレジスタ回路。

**【請求項 1 7】**

請求項 8 から請求項 10 のいずれか記載のシフトレジスタ回路であって、

前記インバータは、

当該インバータの前記出力ノードと所定の第1電源端子との間に接続し、その制御電極が当該インバータの前記入力ノードとなる第6トランジスタと、

前記出力ノードと前記第3クロック信号が供給される第2クロック端子との間に接続した第1容量素子とを備える

ことを特徴とするシフトレジスタ回路。

**【請求項 1 8】**

請求項 1 から請求項 1 7 のいずれか記載のシフトレジスタ回路であって、

前記第1クロック信号とは位相の異なる第4クロック信号に基づいて前記出力端子を放

電する第9トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項19】

請求項18記載のシフトレジスタ回路であって、

前記第9トランジスタは、

前記出力端子に接続した一の主電極、前記第4クロック信号が入力される制御電極および、前記第4クロック信号とは位相が異なる第5クロック信号が供給される他の主電極を有するものである

ことを特徴とするシフトレジスタ回路。

【請求項20】

請求項8から請求項17のいずれか記載のシフトレジスタ回路であって、

前記インバータの出力に基づいて前記出力端子を放電する第9トランジスタをさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項21】

請求項20記載のシフトレジスタ回路であって、

前記第9トランジスタは、

前記出力端子に接続した一の主電極、前記インバータの前記出力ノードに接続した制御電極および、前記第3クロック信号とは位相が異なる第4クロック信号が供給される他の主電極を有するものである

ことを特徴とするシフトレジスタ回路。

【請求項22】

請求項1から請求項21のいずれか記載のシフトレジスタ回路であって、

前記駆動回路は、

前記第1トランジスタの制御電極と所定の第1電源端子との間に接続し、前記リセット端子に接続した制御電極を有する第10トランジスタとを含む

前記第1トランジスタの制御電極と前記入力端子との間に接続し、当該入力端子に接続した制御電極を有する第11トランジスタとを備える

ことを特徴とするシフトレジスタ回路。

【請求項23】

請求項1から請求項21のいずれか記載のシフトレジスタ回路であって、

前記駆動回路は、

前記第1トランジスタの制御電極と所定の第1電源端子との間に接続し、前記リセット端子に接続した制御電極を有する第10トランジスタとを含む

前記第1トランジスタの制御電極と所定の第2電源端子との間に接続し、前記入力端子に接続した制御電極を有する第11トランジスタとを備える

ことを特徴とするシフトレジスタ回路。

【請求項24】

請求項1から請求項23のいずれか記載のシフトレジスタ回路であって、

前記出力端子と前記第1トランジスタの制御電極との間に接続する第2容量素子をさらに備える

ことを特徴とするシフトレジスタ回路。

【請求項25】

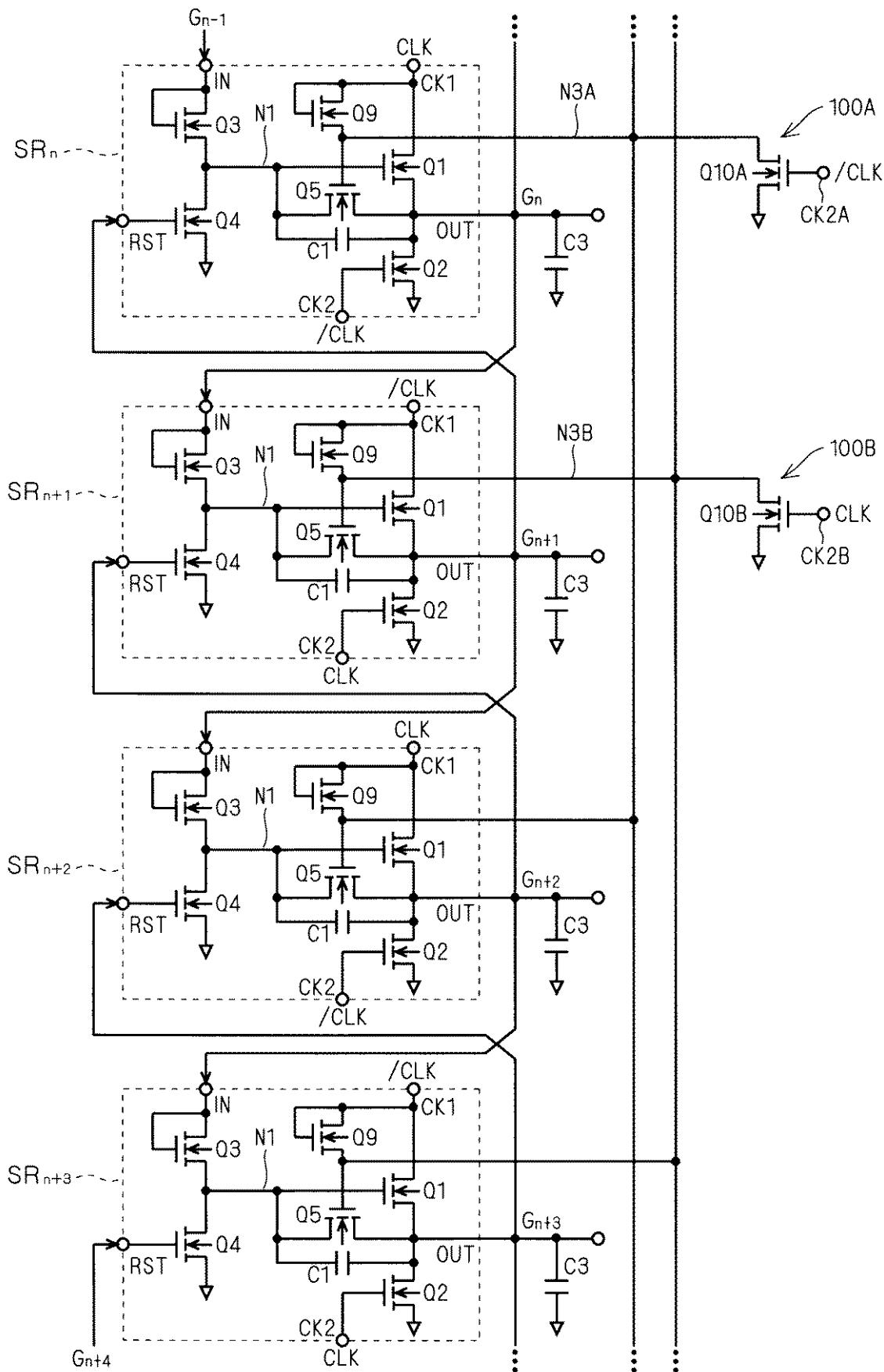

複数のシフトレジスタ回路が縦続接続して成る複数段のシフトレジスタ回路であって、

前記複数段の各段は、請求項4から請求項7のいずれか記載のシフトレジスタ回路であ

り、

前記レベル調整回路は、

2以上の段のシフトレジスタ回路により共有されている

ことを特徴とするシフトレジスタ回路。

【請求項26】

複数段から成るシフトレジスタ回路であって、

前記複数段の各段は、請求項 6 または請求項 7 記載のシフトレジスタ回路であり、

前記レベル調整回路の前記第 4 トランジスタは、

2 以上の段のシフトレジスタ回路により共有されている

ことを特徴とするシフトレジスタ回路。

【請求項 2 7】

請求項 2 5 記載のシフトレジスタ回路であって、

前記各段のシフトレジスタ回路および前記レベル調整回路の前記第 1 クロック端子に所

定のクロック信号を供給するためのクロック配線と、

前記クロック配線に前記所定のクロック信号を入力するための接続端子とをさらに備え

、

前記レベル調整回路は、

前記複数段のうち最も前記接続端子の近くで前記クロック配線に接続したものの近くに

配設されている

ことを特徴とするシフトレジスタ回路。

【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】発明の名称

【補正方法】変更

【補正の内容】

【発明の名称】シフトレジスタ回路

【手続補正 3】

【補正対象書類名】明細書

【補正対象項目名】0 1 3 0

【補正方法】変更

【補正の内容】

【0 1 3 0】

以下、実施の形態 5 の単位シフトレジスタ S R の動作について説明する。ここでは、当該単位シフトレジスタ S R が 2 相のクロック信号 C L K , / C L K により駆動されており、第 1 クロック端子 C K 1 にクロック信号 C L K が入力され、第 2 クロック端子 C K 2 にクロック / C L K が入力されると仮定する。

【手続補正 4】

【補正対象書類名】図面

【補正対象項目名】図 3 7

【補正方法】変更

【補正の内容】

【図 3 7】