(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-10212

(P2014-10212A)

(43) 公開日 平成26年1月20日(2014.1.20)

|                             |           |                  |

|-----------------------------|-----------|------------------|

| (51) Int.Cl.                | F 1       | テーマコード (参考)      |

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2 H 19 3         |

| <b>G09G 3/34</b> (2006.01)  | G09G 3/34 | J 5 C 00 6       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 6 2 2 L 5 C 08 0 |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 6 1 1 E          |

|                             | G09G 3/20 | 6 2 3 D          |

審査請求 未請求 請求項の数 5 O L (全 15 頁) 最終頁に続く

|           |                              |          |                                                |

|-----------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2012-145125 (P2012-145125) | (71) 出願人 | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号 |

| (22) 出願日  | 平成24年6月28日 (2012. 6. 28)     | (74) 代理人 | 110001737<br>特許業務法人スズエ国際特許事務所                  |

|           |                              | (74) 代理人 | 100108855<br>弁理士 蔵田 昌俊                         |

|           |                              | (74) 代理人 | 100159651<br>弁理士 高倉 成男                         |

|           |                              | (74) 代理人 | 100088683<br>弁理士 中村 誠                          |

|           |                              | (74) 代理人 | 100109830<br>弁理士 福原 淑弘                         |

|           |                              | (74) 代理人 | 100075672<br>弁理士 峰 隆司                          |

最終頁に続く

## (54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】表示品位の良好な液晶表示装置を提供することを目的とする。

【解決手段】複数のラインで構成された画面を有するO C B型の液晶表示パネルと、1フレーム期間において、前記液晶表示パネルに黒映像信号を書き込む黒書き期間と、前記黒書き期間に続いて前記液晶表示パネルに映像信号を書き込む映像書き期間と、前記映像書き期間に続いて書き込んだ映像信号を保持する映像保持期間との順序に駆動制御する制御手段と、1フレーム期間において、少なくとも前記映像保持期間に点灯し、前記液晶表示パネルを照明する照明手段と、を備え、前記制御手段は、前記映像書き期間において、前記液晶表示パネルにおける画面中央のラインから画面上側及び画面下側のラインに向かって順次映像信号を書き込むことを特徴とする液晶表示装置。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

複数のラインで構成された画面を有するO C B型の液晶表示パネルと、

1フレーム期間において、前記液晶表示パネルに黒映像信号を書き込む黒書込期間と、前記黒書込期間に続いて前記液晶表示パネルに映像信号を書き込む映像書込期間と、前記映像書込期間に續いて書き込んだ映像信号を保持する映像保持期間との順序に駆動制御する制御手段と、

1フレーム期間において、少なくとも前記映像保持期間に点灯し、前記液晶表示パネルを照明する照明手段と、を備え、

前記制御手段は、前記映像書込期間において、前記液晶表示パネルにおける画面中央のラインから画面上側及び画面下側のラインに向かって順次映像信号を書き込むことを特徴とする液晶表示装置。 10

**【請求項 2】**

前記画面中央のラインへの映像信号の書き込みが完了してから前記照明手段が点灯するまでの時間は、前記画面上側及び前記画面下側のラインへの映像信号の書き込みが完了してから前記照明手段が点灯するまでの時間より長いことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

複数のラインで構成された画面を有するO C B型の液晶表示パネルと、

1フレーム期間において、前記液晶表示パネルに黒映像信号を書き込む黒書込期間と、前記黒書込期間に続いて前記液晶表示パネルに映像信号を書き込む映像書込期間と、前記映像書込期間に續いて書き込んだ映像信号を保持する映像保持期間との順序に駆動制御する制御手段と、

1フレーム期間において、少なくとも前記映像保持期間に点灯し、前記液晶表示パネルを照明する照明手段と、を備え、

前記制御手段は、前記映像書込期間において、前記液晶表示パネルにおける画面上側及び画面下側のラインから画面中央のラインに向かって順次映像信号を書き込むことを特徴とする液晶表示装置。 20

**【請求項 4】**

前記画面中央のラインへの映像信号の書き込みが完了してから前記照明手段が点灯するまでの時間は、前記画面上側及び前記画面下側のラインへの映像信号の書き込みが完了してから前記照明手段が点灯するまでの時間より短く、

しかも、前記照明手段が点灯している期間に、前記画面上側及び前記画面下側のラインへの黒映像信号の書き込みが開始されることを特徴とする請求項3に記載の液晶表示装置。 30

**【請求項 5】**

前記液晶表示パネルは、前記画面の各ラインに同一の映像信号が書き込まれた際に、画面中央での輝度が画面上側及び画面下側での輝度より高く、画面中央を挟んで画面上側と画面下側とで対称の輝度分布を形成することを特徴とする請求項1または3に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明の実施形態は、液晶表示装置に関する。

**【背景技術】****【0 0 0 2】**

液晶表示装置は、軽量、薄型、低消費電力などの特徴を生かして、パソコンやスマートフォンなどのOA機器やテレビなどの表示装置として各種分野で利用されている。近年では、液晶表示装置は、携帯電話などの携帯端末機器や、カーナビゲーション装置、ゲーム機などの表示装置としても利用されている。

**【0 0 0 3】**

10

20

30

40

50

例えば、特許文献 1 によれば、O C B ( Optically Compensated Bend ) 型の液晶表示パネルの駆動手法として、1 フレーム期間において、黒映像信号を書き込む黒書込期間と、映像信号を書き込む映像書込期間と、書き込んだ映像信号を保持する映像保持期間との順序に駆動制御する駆動手法 ( ABC 駆動法 ) が開示されている。このような駆動手法では、1 フレーム期間の最初に黒映像が書き込まれることにより液晶分子の逆転移を防止できるとともに鮮明な画像を得ることができ、また、映像保持期間においてバックライトを点灯させるため、映像にちらつき等が起こりにくいといった利点がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2009 - 42423 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本実施形態の目的は、表示品位の良好な液晶表示装置を提供することにある。

【課題を解決するための手段】

【0006】

本実施形態によれば、

複数のラインで構成された画面を有する O C B 型の液晶表示パネルと、1 フレーム期間において、前記液晶表示パネルに黒映像信号を書き込む黒書込期間と、前記黒書込期間に続いて前記液晶表示パネルに映像信号を書き込む映像書込期間と、前記映像書込期間に続いて書き込んだ映像信号を保持する映像保持期間との順序に駆動制御する制御手段と、1 フレーム期間において、少なくとも前記映像保持期間に点灯し、前記液晶表示パネルを照明する照明手段と、を備え、前記制御手段は、前記映像書込期間において、前記液晶表示パネルにおける画面中央のラインから画面上側及び画面下側のラインに向かって順次映像信号を書き込むことを特徴とする液晶表示装置が提供される。

【0007】

また、本実施形態によれば、

複数のラインで構成された画面を有する O C B 型の液晶表示パネルと、1 フレーム期間において、前記液晶表示パネルに黒映像信号を書き込む黒書込期間と、前記黒書込期間に続いて前記液晶表示パネルに映像信号を書き込む映像書込期間と、前記映像書込期間に続いて書き込んだ映像信号を保持する映像保持期間との順序に駆動制御する制御手段と、1 フレーム期間において、少なくとも前記映像保持期間に点灯し、前記液晶表示パネルを照明する照明手段と、を備え、前記制御手段は、前記映像書込期間において、前記液晶表示パネルにおける画面上側及び画面下側のラインから画面中央のラインに向かって順次映像信号を書き込むことを特徴とする液晶表示装置が提供される。

【図面の簡単な説明】

【0008】

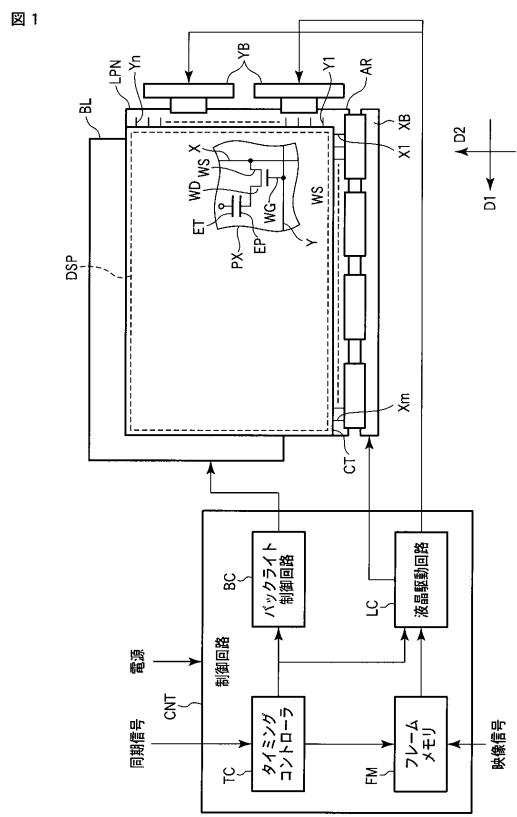

【図 1】図 1 は、本実施形態に係る液晶表示装置の構成を概略的に示す図である。

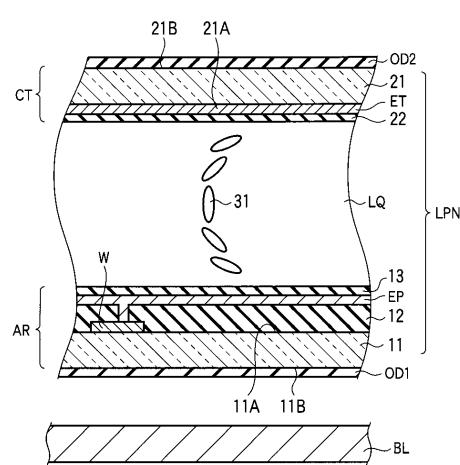

【図 2】図 2 は、図 1 に示した液晶表示装置に適用可能な O C B 型の液晶表示パネルの構成を概略的に示す断面図である。

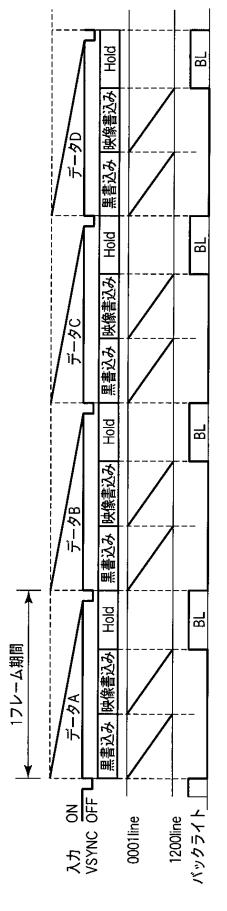

【図 3】図 3 は、図 2 に示した O C B 型の液晶表示パネルに適用可能な駆動手法を説明するための図である。

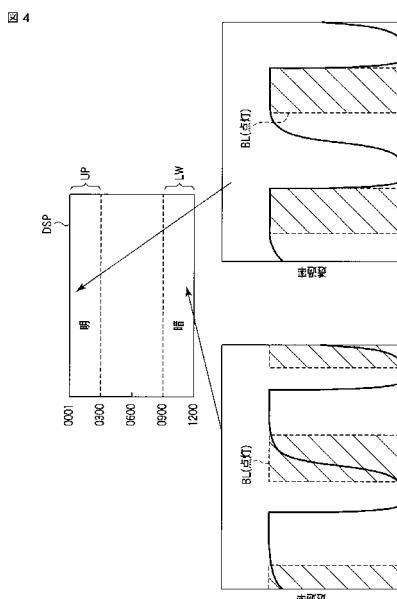

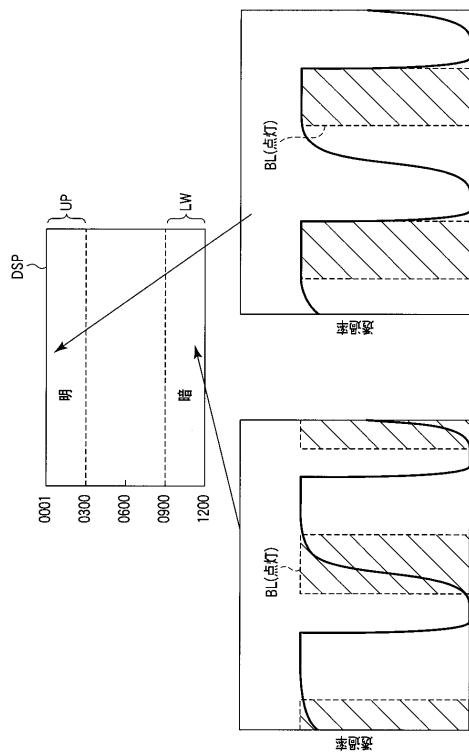

【図 4】図 4 は、画面の上部及び下部における液晶表示パネルの透過率とバックライトの点灯タイミングとの関係を説明するための図である。

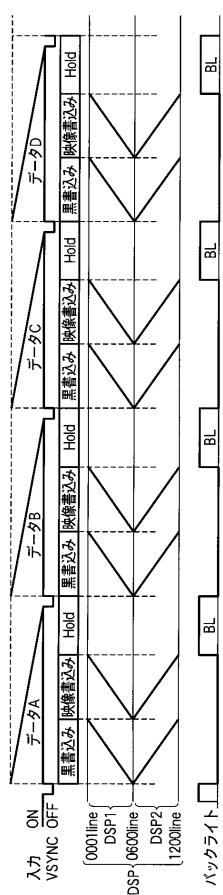

【図 5】図 5 は、第 1 実施形態の O C B 型の液晶表示パネルに適用可能な第 1 駆動手法を説明するための図である。

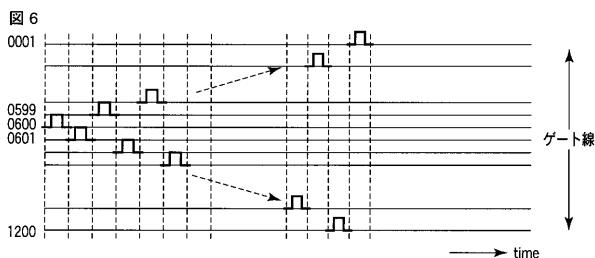

【図 6】図 6 は、画面を構成する各ラインに対応したゲート線の走査タイミングを説明するための図である。

10

20

30

40

50

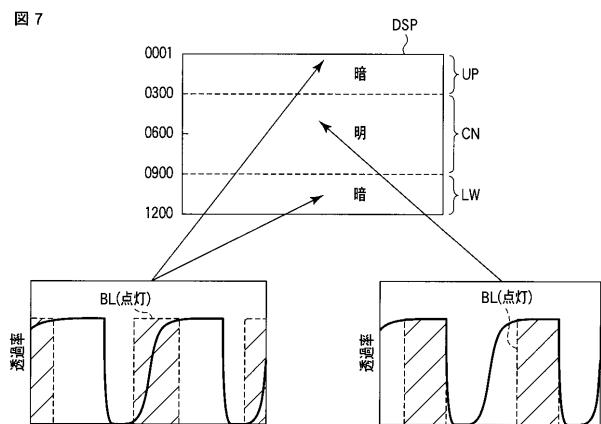

【図7】図7は、画面の上部、下部、中央部における液晶表示パネルの透過率とバックライトの点灯タイミングとの関係を説明するための図である。

【図8】図8は、第2実施形態のOCB型の液晶表示パネルに適用可能な第2駆動手法を説明するための図である。

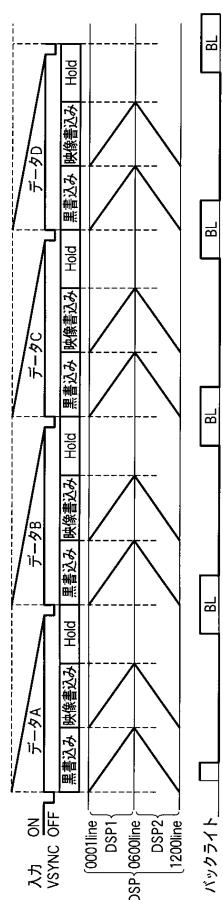

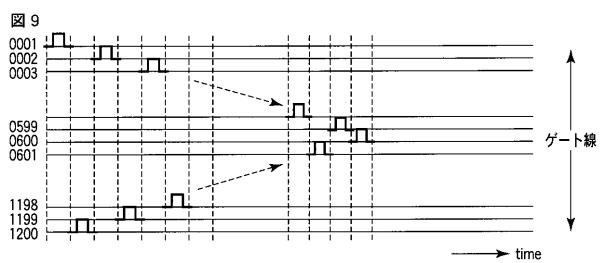

【図9】図9は、画面を構成する各ラインに対応したゲート線の走査タイミングを説明するための図である。

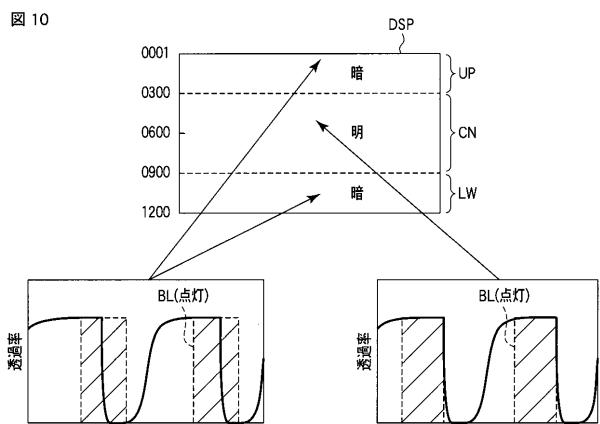

【図10】図10は、画面の上部、下部、中央部における液晶表示パネルの透過率とバックライトの点灯タイミングとの関係を説明するための図である。

**【発明を実施するための形態】**

**【0009】**

以下、本実施形態に係る液晶表示装置について図面を参照して説明する。

**【0010】**

図1は、本実施形態における液晶表示装置の構成を概略的に示す図である。すなわち、この液晶表示装置は、アクティブマトリクスタイプの液晶表示装置であって、OCB型の液晶表示パネルLPNと、液晶表示パネルLPNの駆動を制御する制御手段として機能する制御回路CNTと、液晶表示パネルLPNを照明する照明手段として機能するバックライトBLと、を備えている。

**【0011】**

液晶表示パネルLPNは、バックライトBLからのバックライト光を選択的に透過して画像を表示する透過型である。この液晶表示パネルLPNは、一対の基板、すなわちアレイ基板ARと、アレイ基板ARに対向して配置された対向基板CTと、を備えている。これらのアレイ基板ARと対向基板CTとは、図示しないシール材によって貼り合わせられている。このような液晶表示パネルLPNは、複数のラインで構成された画面DSPを有している。この画面DSPは、画像を表示するアクティブエリアに対応し、 $m \times n$ 個のマトリクス状に配置された複数の画素PXによって構成されている（但し、m及びnは正の整数である）。なお、図1においては、簡略化のため、1画素のみを図示している。

**【0012】**

アレイ基板ARは、第1方向D1に沿ってそれぞれ延出したn本のゲート線Y（Y1～Yn）、各ゲート線Yと交差するように第2方向D2に沿ってそれぞれ延出したm本のソース線X（X1～Xm）、各画素PXに配置された $m \times n$ 個のスイッチング素子W、各画素PXに配置されスイッチング素子Wに接続された $m \times n$ 個の画素電極EPなどを備えている。

**【0013】**

スイッチング素子Wは、例えば、薄膜トランジスタ（TFT）によって構成されている。スイッチング素子Wのゲート電極WGは、ゲート線Yに電気的に接続されている（あるいは、ゲート電極WGはゲート線Yと一体的に形成されている）。スイッチング素子Wのソース電極WSは、ソース線Xに電気的に接続されている（あるいは、ソース電極WSはソース線Xと一体に形成されている）。スイッチング素子Wのドレイン電極WDは、画素電極EPに電気的に接続されている。

**【0014】**

n本のゲート線Yは、それぞれゲートドライバYDに接続されている。このゲートドライバYDは、制御回路CNTによる制御に基づいてn本のゲート線Yに走査信号を供給する。また、m本のソース線Xは、それぞれソースドライバXDに接続されている。このソースドライバXDは、制御回路CNTによる制御に基づいてm本のソース線Xに映像信号（黒映像信号を含む）を供給する。なお、これらのゲートドライバYD及びソースドライバXDも本実施形態の制御手段の一部を構成する。

**【0015】**

一方、対向基板CTは、対向電極ETなどを備えている。この対向電極ETは、複数の画素PXに共通である。つまり、対向電極ETは、各画素PXの画素電極EPと向かい合っている。

10

20

30

40

50

## 【0016】

なお、図1においては、画面DSPの一画素PXのみを図示しているが、 $m \times n$ 個の画素PXの全てが同一構造である。すなわち、第1方向D1に沿って同一構造の画素PXがm個並んで配置されるとともに、第2方向D2に沿って同一構造の画素PXがn個並んで配置されている。画面DSPを構成する1ラインとは、第1方向D1に並んだm個の画素PXによって構成されるものである。1ラインの各画素PXに配置されたスイッチング素子Wのゲート電極WGは、同一のゲート線Yに接続されている。このため、スイッチング素子Wをオンさせる走査信号がゲート線Yに供給された場合には、1ラインのm個の画素PXへの映像信号の書き込みが可能となる。

## 【0017】

バックライトBLは、液晶表示パネルLPNの背面側であるアレイ基板ARと向かい合う側に配置されている。つまり、このバックライトBLは、液晶表示パネルLPNをアレイ基板ARの側から照明する。このようなバックライトBLとしては、種々の形態が適用可能であり、また、光源として発光ダイオードを利用したものや冷陰極管を利用したものなどのいずれでも適用可能であり、詳細な構造については説明を省略する。

## 【0018】

制御回路CNTは、タイミングコントローラTC、フレームメモリFM、バックライト制御回路BC、液晶駆動回路LCなどを有している。

## 【0019】

タイミングコントローラTCは、同期信号に基づいてフレームメモリFMにおける映像信号の記憶及び読み出しのタイミングを制御するのに必要な制御信号を生成する。また、このタイミングコントローラTCは、バックライト制御回路BCに対してバックライトBLの点灯及び消灯のタイミングを制御するのに必要な制御信号を生成する。さらに、このタイミングコントローラTCは、液晶駆動回路LCに対して液晶表示パネルLPNの各画素PXへの映像信号の書き込みのタイミングを制御するのに必要な制御信号を生成する。

## 【0020】

フレームメモリFMは、タイミングコントローラTCからの制御信号に基づいて、供給された映像信号を一時的に記憶する。このフレームメモリFMは、ランダムアクセスが可能なランダム・アクセス・メモリとして構成されることが望ましい。また、このフレームメモリFMは、例えば1フレーム分の映像信号を記憶した後、この記憶した映像信号が読み出されるまでに次フレームの映像信号が供給される場合があるため、約2フレーム分の記憶容量を有することが望ましい。

## 【0021】

バックライト制御回路BCは、タイミングコントローラTCからの制御信号に基づいて、バックライトBLの点灯及び消灯を制御する。

## 【0022】

液晶駆動回路LCは、ゲートドライバYDから各ゲート線Yに走査信号を供給させるのに必要な走査制御信号をゲートドライバYDに供給する。また、この液晶駆動回路LCは、フレームメモリFMに記憶された映像信号を所定の順に読み出し、必要に応じて所定の処理を施した後に、1ラインの画素PX分ずつソースドライバXDに供給する。また、この液晶駆動回路LCは、黒映像信号を生成し、1ラインの画素PX分ずつソースドライバXDに供給する。

## 【0023】

次に、OCB型の液晶表示パネルLPNの構造について、以下により詳細に説明する。

## 【0024】

図2は、図1に示した液晶表示パネルLPNの概略断面図である。

## 【0025】

液晶表示パネルLPNのアレイ基板ARは、ガラス板などの光透過性を有する絶縁基板11を用いて形成されている。このアレイ基板ARは、絶縁基板11の第1面11Aつまり対向基板CTと向かい合う側に、スイッチング素子W、絶縁膜12、画素電極EP、画

素電極 E P を覆う第 1 配向膜 1 3などを備えている。画素電極 E P は、インジウム・ティン・オキサイド (ITO) やインジウム・ジンク・オキサイド (IZO) などの光透過性を有する導電材料によって形成されている。

#### 【0026】

液晶表示パネル L P N の対向基板 C T は、ガラス板などの光透過性を有する絶縁基板 2 1 を用いて形成されている。この対向基板 C T は、絶縁基板 2 1 の第 1 面 2 1 A つまりアレイ基板 A R と向かい合う側に、対向電極 E T 、対向電極 E T を覆う第 2 配向膜 2 2などを備えている。対向電極 E T は、例えば ITO などの光透過性を有する導電材料によって形成されている。なお、対向基板 C T は、必要に応じて、ブラックマトリクスやカラーフィルタ層、オーバーコート層などを備えていても良い。

10

#### 【0027】

上述したような構成のアレイ基板 A R と対向基板 C T とは、画素電極 E P と対向電極 E T とを対向させた状態で配置され、これらの間に図示しないスペーサ（例えば、一方の基板に一体的に形成された柱状スペーサ）を介して所定のセルギャップを形成する。これらのアレイ基板 A R と対向基板 C Tとの間に形成されたセルギャップには、液晶層 L Q が保持されている。

#### 【0028】

液晶層 L Q は、正の誘電率異方性を有するとともに光学的に正の一軸性を有する液晶分子 3 1 を含む液晶組成物によって構成されている。この液晶層 L Q においては、液晶層 L Q に所定の電圧（転移電圧）を印加した所定の表示状態において、液晶分子 3 1 は、アレイ基板 A R と対向基板 C Tとの間でベンド配向している。

20

#### 【0029】

液晶表示パネル L P N の外面には、第 1 光学補償層 O D 1 及び第 2 光学補償層 O D 2 がそれぞれ配置されている。これらの第 1 光学補償素子 O D 1 及び第 2 光学補償素子 O D 2 は、上述したような液晶表示パネル L P N における液晶層 L Q に電圧を印加した所定の表示状態において、液晶層 L Q のリタデーションを光学的に補償する機能を有しており、偏光板及び位相差板などを備えて構成されている。

#### 【0030】

第 1 光学補償素子 O D 1 は、アレイ基板 A R を構成する絶縁基板 1 1 の第 2 面 1 1 B つまりバックライト B L と向かい合う面に配置されている。また、第 2 光学補償素子 O D 2 は、対向基板 C T を構成する絶縁基板 2 1 の第 2 面 2 1 B つまり観察側の面に配置されている。

30

#### 【0031】

このような OCB 型の液晶表示パネル L P N においては、液晶層 L Q を保持する第 1 配向膜 1 3 及び第 2 配向膜 2 2 は、互いに平行な方向にラビング処理されている。このような第 1 配向膜 1 3 及び第 2 配向膜 2 2 の作用により、電源投入以前の段階では、液晶分子 3 1 は、スプレイ配向している。

#### 【0032】

そして、電源投入後、表示動作以前の段階において、初期化処理が行われる。この初期化処理は、液晶層 L Q に対して転移電圧を印加するものであり、この転移電圧に対応した比較的強い電界により液晶分子 3 1 の配向状態をスプレイ配向からベンド配向に転移させる。液晶分子 3 1 の配向状態は、表示動作中、ベンド配向に維持されている。

40

#### 【0033】

表示動作において、液晶層 L Q に白画像（あるいは最高輝度に対応した階調レベルの画像）を表示するための白表示電圧が印加された際には、液晶層 L Q のミッドプレーン付近の液晶分子 3 1 が基板に略垂直に立ち上がっているのに対してアレイ基板 A R 及び対向基板 C T にそれぞれ近づくにしたがって液晶分子 3 1 が基板の法線から傾き、基板近傍の液晶分子 3 1 は基板面とほぼ平行な方向に傾いた状態となる。また、液晶層 L Q に黒画像（あるいは最低輝度に対応した階調レベルの画像）を表示する場合、白表示電圧より高い黒表示電圧（あるいは黒映像信号）が印加された際には、液晶層 L Q の液晶分子 3 1 が略垂

50

直に立ち上がった状態となる。

**【0034】**

このようなO C B型の液晶表示パネルL P Nにおいては、液晶分子3 1の配向状態は、スプレイ配向のエネルギーとベンド配向のエネルギーとが拮抗するレベル以下の電圧印加状態や電圧無印加状態が長期間続く場合に、再びベンド配向からスプレイ配向に逆転移してしまう。

**【0035】**

このため、O C B型の液晶表示パネルL P Nでは、この逆転移を防止するために、1フレーム期間内に液晶層L Qに黒表示電圧が印加される（黒挿入駆動方式）。これにより、液晶層L Qのベンド配向を維持している。

10

**【0036】**

次に、O C B型の液晶表示パネルL P Nに適用可能な駆動手法について図3を参照しながら説明する。

**【0037】**

ここでは、例えば垂直同期信号V S Y N CがONしてから一旦OFFした後に再度ONするまでの期間を1フレーム期間とする。この1フレーム期間には、黒書き込み期間、映像書き込み期間、映像保持期間（ホールド期間）が含まれる。黒書き込み期間は、液晶駆動回路L Cから液晶表示パネルL P Nに供給された黒映像信号を液晶表示パネルL P Nの各画素P Xに書き込む期間に相当する。映像書き込み期間は、液晶駆動回路L Cから液晶表示パネルL P Nに供給された映像信号を液晶表示パネルL P Nの各画素P Xに書き込む期間に相当する。ホールド期間は、各画素P Xに書き込まれた映像信号を保持する期間に相当する。

20

**【0038】**

例えば、画面D S Pが1 2 0 0本のラインによって構成されている場合、まず、同期信号V S Y N CがOFFしたタイミングで画面D S Pの最上部に位置するライン0 0 0 1への黒映像信号の書き込みが開始される。その後、ライン0 0 0 2からライン1 2 0 0へと画面D S Pの下部のラインに順次黒映像信号の書き込みが行われる（黒書き込み期間）。

30

**【0039】**

画面D S Pのすべてのラインへの黒映像信号の書き込みが完了した後、画面D S Pの最上部のライン0 0 0 1への映像信号の書き込みが開始される。ライン0 0 0 1の各画素P Xに書き込まれた映像信号は、保持される。ライン0 0 0 1への映像信号の書き込みが終了した後、ライン0 0 0 2からライン1 2 0 0へと画面D S Pの下部のラインに順次映像信号の書き込みが行われる（映像書き込み期間）。各ラインの画素P Xに書き込まれた映像信号はそれぞれ保持される。

30

**【0040】**

画面D S Pのすべてのラインへの映像信号の書き込みが完了したタイミングで、バックライトB Lが点灯する。このバックライトB Lは、黒書き込み期間及び映像書き込み期間においては消灯している。

**【0041】**

一方で、このような駆動手法の場合、画面D S Pを構成する全てのラインへの映像書き込みが完了した後にバックライトB Lを点灯するため、映像信号の書き込みが完了してからバックライトB Lが点灯されるまでの時間が画面D S Pの上部と下部とで相違している。すなわち、画面D S Pの上部のラインについては、映像信号の書き込みが完了してから十分な時間が経過した後にバックライトB Lが点灯するのに対して、画面D S Pの下部のラインについては、映像信号の書き込みが完了した直後にバックライトB Lが点灯する。

40

**【0042】**

図4に示すように、例えば、画面D S Pのライン0 0 0 1からライン0 3 0 0付近までの上部U Pにおいては、映像信号の書き込みが完了してからバックライトB Lが点灯するまでの間に、液晶分子3 1の応答速度よりも十分に長い時間が経過している。このため、液晶分子3 1の転移が完了した状態でバックライトB Lが点灯する。したがって、液晶表示パネルL P Nにおいては、映像信号に対応した透過率が得られる。

50

**【0043】**

一方で、例えば、画面DSPのライン0901からライン1200付近までの下部LWにおいては、映像信号の書き込みが完了してからバックライトBLが点灯するまでの間に、液晶分子31の応答速度よりも十分に長い時間が経過していない。このため、液晶分子31の転移が完了する前の状態でバックライトBLが点灯することがある。したがって、液晶表示パネルLPNにおいては、映像信号に対応した透過率が得られない場合がある。

**【0044】**

画面DSPの全体で白色を表示する場合、上部UPは下部LWよりも明るくなる。このように、画面DSPにおいて、上下で輝度の分布が非対称となる現象を改善することが要求される。

10

**【0045】**

そこで、本実施形態においては、面内DSPにおける輝度分布を上下対称とする最適な駆動手法を提供するものである。

**【0046】**

図5は、第1実施形態のOCB型の液晶表示パネルLPNに適用可能な第1駆動手法を説明するための図である。なお、ここでは、主として映像書き込み期間を詳細に説明し、黒書き込み期間や映像信号保持期間については詳細な説明を省略する。

20

**【0047】**

この第1駆動手法では、1フレーム期間の映像書き込み期間において、液晶表示パネルLPNにおける画面DSPの中央のラインから画面DSPの上側及び下側のラインに向かって順次映像信号を書き込むことを特徴とするものである。例えば、画面DSPが1200本のラインによって構成されている場合、ライン0001からライン0600までが画面DSPの上側半分の第1領域DSP1に相当し、ライン0601からライン1200までが画面DSPの下側半分の第2領域DSP2に相当する。

**【0048】**

このような画面DSPの構成において、画面DSPの第1領域DSP1では、ライン0600への映像信号の書き込みを行った後、順次ライン0599、ライン0598…ライン002、ライン0001へと映像信号の書き込みを行う。同様に、画面DSPの第2領域DSP2では、ライン0601への映像信号の書き込みを行った後、順次ライン0602、ライン0603…ライン1199、ライン1200へと映像信号の書き込みを行う。

30

**【0049】**

画面DSPのすべてのラインへの映像信号の書き込みが完了したタイミングで、バックライトBLが点灯する。このバックライトBLは、黒書き込み期間及び映像書き込み期間においては消灯している。

**【0050】**

なお、黒書き込み期間においては、映像書き込み期間と同一の順序で黒映像信号を書き込んでも良いが、図3を参照して説明したのと同様に、画面DSPのライン0001から下側に向かってライン1200まで順次黒映像信号を書き込んでも良いし、他の手法で黒映像信号を書き込んでも良く、特定の書き込み順序に制限されるものではない。

40

**【0051】**

上述した第1領域DSP1及び第2領域DSP2からなる画面DSPを備えた液晶表示パネルLPNに対して、第1領域DSP1及び第2領域DSP2に映像信号を書き込むためのソースドライバが単一の構成において、より具体的な映像信号の書き込み動作について説明する。

**【0052】**

図6は、画面DSPを構成する各ラインに対応したゲート線の走査タイミングを説明するための図である。

**【0053】**

例えば、画面DSPが1200本のラインによって構成されている場合、映像書き込み期間においては、まず、画面DSPの中央に位置するライン0600への映像信号の書き込みが行

50

われる。その後、ライン 0 6 0 0 よりも下側のライン 0 6 0 1 への映像信号の書き込みに続いて、ライン 6 0 0 よりも上側のライン 0 5 9 9 への映像信号の書き込みが行われる。その後は、上側のラインへの映像信号の書き込みと下側のラインへの映像信号の書き込みとが交互に行われる（ライン 0 6 0 2 ライン 0 5 9 8 ライン 0 6 0 3 ライン 0 5 9 7 … ライン 1 2 0 0 ライン 0 0 0 1）。

#### 【0054】

なお、上述した第1領域DSP1及び第2領域DSP2からなる画面DSPを備えた液晶表示パネルLPNに対して、第1領域DSP1に映像信号を書き込むための第1ソースドライバと、第2領域DSP2に映像信号を書き込むための第2ソースドライバとを具備した構成においては、第1領域DSP1への映像信号の書き込みと、第2領域DSP2への映像信号の書き込みとを同時に行ってもよい。例えば、ライン0600及びライン0601への映像信号の書き込みや、ライン0599及びライン0602への映像信号の書き込みなどはそれぞれ同時にあってもよい。このような構成の場合、映像信号の書き込み時間を短縮することができる。

10

#### 【0055】

図7は、画面DSPの上部UP、下部LW、中央部CNにおける液晶表示パネルの透過率とバックライトBLの点灯タイミングとの関係を説明するための図である。

#### 【0056】

例えば、画面DSPの中央部CNのライン0600付近においては、映像信号の書き込みが完了してからバックライトBLが点灯するまでの間に、液晶分子31の応答速度よりも十分に長い時間が経過している。このため、液晶分子31の転移が完了した状態でバックライトBLが点灯する。したがって、液晶表示パネルLPNにおいては、映像信号に対応した透過率が得られる。

20

#### 【0057】

一方で、例えば、画面DSPのライン0001からライン0300付近までの上部UP及びライン0901からライン1200付近までの下部LWにおいては、映像信号の書き込みが完了してからバックライトBLが点灯するまでの間に、液晶分子31の応答速度よりも十分に長い時間が経過していない。このため、液晶分子31の転移が完了する前の状態でバックライトBLが点灯することがある。したがって、液晶表示パネルLPNにおいては、映像信号に対応した透過率が得られない場合がある。

30

#### 【0058】

つまり、画面DSPの中央部CNのラインへの映像信号の書き込みが完了してからバックライトBLが点灯するまでの時間は、画面DSPの上部UPの側のライン及び画面DSPの下部LWの側のラインへの映像信号の書き込みが完了してからバックライトBLが点灯するまでの時間より長い。なお、画面DSPの上部UPの側のラインへの映像信号の書き込みが完了してからバックライトBLが点灯するまでの時間は、画面DSPの下部LWの側のラインへの映像信号の書き込みが完了してからバックライトBLが点灯するまでの時間と略同等である。

#### 【0059】

このため、画面DSPの各ラインに同一の映像信号、例えば、画面DSPの全体で白色を表示する白色表示電圧が書き込まれた場合、中央部CNでの輝度は、上部UP及び下部LWよりも高くなる。このとき、画面DSPの上部UP及び下部LWにおける輝度は、略同等となる。つまり、第1駆動手法を適用することにより、画面DSPの中央部CNが明るく、この中央部CNを挟んで上側と下側とで対称の輝度分布を形成することができる。したがって、良好な表示品位を得ることが可能となる。

40

#### 【0060】

次に、第2実施形態について説明する。なお、第1実施形態と同一構成については同一の参照符号を付して詳細な説明を省略する。

#### 【0061】

図8は、第2実施形態のOCB型の液晶表示パネルLPNに適用可能な第2駆動手法を

50

説明するための図である。なお、ここでは、主として映像書き込み期間を詳細に説明し、黒書き込み期間や映像信号保持期間については詳細な説明を省略する。

#### 【0062】

この第2駆動手法では、1フレーム期間の映像書き込み期間において、液晶表示パネルLPNにおける画面DSPの上側及び下側のラインから画面DSPの中央のラインに向かって順次映像信号を書き込むことを特徴とするものである。

#### 【0063】

すなわち、画面DSPの第1領域DSP1では、ライン0001への映像信号の書きを行った後、順次ライン0002、ライン0003…ライン0599、ライン0600へと映像信号の書きを行う。同様に、画面DSPの第2領域DSP2では、ライン1200への映像信号の書きを行った後、順次ライン1199、ライン1198…ライン0602、ライン0601へと映像信号の書きを行う。10

#### 【0064】

バックライトBLは、画面DSPのすべてのラインへの映像信号の書きが完了してから所定時間が経過した後に点灯する。すべてのラインへの映像信号の書きが完了してからバックライトBLが点灯するまでの時間は、液晶分子31の応答速度よりも十分に長い時間に設定されている。また、このバックライトBLは、画面DSPの中のラインへの黒書きが開始されるまでの間、点灯していることが望ましい。

#### 【0065】

なお、黒書き込み期間においては、第1実施形態と同様に、黒映像信号の書き順序については、特定の書き順序に制限されるものではない。20

#### 【0066】

上述した第1領域DSP1及び第2領域DSP2からなる画面DSPを備えた液晶表示パネルLPNに対して、第1領域DSP1及び第2領域DSP2に映像信号を書き込むためのソースドライバXDが単一の構成において、より具体的な映像信号の書き動作について説明する。

#### 【0067】

図9は、画面DSPを構成する各ラインに対応したゲート線の走査タイミングを説明するための図である。

#### 【0068】

例えば、画面DSPが1200本のラインによって構成されている場合、映像書き込み期間においては、まず、画面DSPの最上部に位置するライン0001への映像信号の書きが行われる。その後、画面DSPの最下部に位置するライン1200への映像信号の書きが行われる。続いて、ライン0002への映像信号の書き、ライン1199への映像信号の書き、ライン0003への映像信号の書き、ライン1198への映像信号の書きが順次行われる。その後は、同様にして、上側のラインへの映像信号の書きと下側のラインへの映像信号の書きとが交互に行われる（ライン0004 ライン1197 ライン0005 ライン1196…ライン0601 ライン0599 ライン0600）。

#### 【0069】

なお、上述した第1領域DSP1及び第2領域DSP2からなる画面DSPを備えた液晶表示パネルLPNに対して、第1領域DSP1に映像信号を書き込むための第1ソースドライバと、第2領域DSP2に映像信号を書き込むための第2ソースドライバとを具備した構成においては、第1領域DSP1への映像信号の書きと、第2領域DSP2への映像信号の書きとを同時にやってよい。例えば、ライン0001及びライン1200への映像信号の書きや、ライン0002及びライン1199への映像信号の書きなどはそれ同時にやってよい。このような構成の場合、映像信号の書き時間の短縮ができる。

#### 【0070】

図10は、画面DSPの上部UP、下部LW、中央部CNにおける液晶表示パネルの透過率とバックライトBLの点灯タイミングとの関係を説明するための図である。40

50

20

30

40

50

## 【0071】

例えば、画面DSPの中央部CNのライン0600付近においては、映像信号の書き込みが完了してからバックライトBLが点灯するまでの間に、液晶分子31の応答速度よりも十分に長い時間が経過している。このため、液晶分子31の転移が完了した状態でバックライトBLが点灯する。したがって、液晶表示パネルLPNにおいては、映像信号に対応した透過率が得られる。

## 【0072】

一方で、例えば、画面DSPのライン0001からライン0300付近までの上部UP及びライン0901からライン1200付近までの下部LWにおいては、映像信号の書き込みが完了してからバックライトBLが点灯するまでの間に、液晶分子31の応答速度よりも十分に長い時間が経過しているが、バックライトBLが点灯中に黒書きが開始される。このため、液晶表示パネルLPNにおいては、映像信号に対応した透過率が得られない場合がある。

10

## 【0073】

つまり、画面DSPの中央部CNのラインへの映像信号の書き込みが完了してからバックライトBLが点灯するまでの時間は、画面DSPの上部UPの側のライン及び画面DSPの下部LWの側のラインへの映像信号の書き込みが完了してからバックライトBLが点灯するまでの時間より短い。しかも、バックライトBLが点灯している期間において、画面DSPの上部UPの側のライン及び画面DSPの下部LWの側のラインへの黒映像信号の書き込みが開始される。なお、画面DSPの上部UPの側のラインでの映像信号保持期間中にバックライトBLが点灯している時間は、画面DSPの下部LWの側のラインでの映像信号保持期間中にバックライトBLが点灯している時間と略同等である。

20

## 【0074】

このため、画面DSPの各ラインに同一の映像信号、例えば、画面DSPの全体で白色を表示する白色表示電圧が書き込まれた場合、中央部CNでの輝度は、上部UP及び下部LWよりも高くなる。このとき、画面DSPの上部UP及び下部LWにおける輝度は、略同等となる。つまり、第2駆動手法を適用することにより、画面DSPの中央部CNが明るく、この中央部CNを挟んで上側と下側とで対称の輝度分布を形成することができる。したがって、良好な表示品位を得ることが可能となる。

30

## 【0075】

なお、上記した第1駆動手法と第2駆動手法との選択は、ゲート線の走査に必要な時間が1フレームに対して十分かどうかによって決定され、十分な場合は第1駆動手法が有効であり、不十分の場合は第2駆動手法が有効である。

## 【0076】

以上説明したように、本実施形態によれば、表示品位の良好な液晶表示装置を提供することができる。

## 【0077】

なお、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これらの新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これらの実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

40

## 【0078】

例えば、上記した液晶表示パネルLPNに対して、スキャンバックライトを組み合わせても良い。すなわち、複数の領域によって構成された画面DSPを備えた液晶表示パネルLPNに対して、各領域に対応して点灯領域が区画されたバックライトBLを用意し、液晶表示パネルLPNの各領域への映像信号の書き込み保持の期間に対応してバックライトBLの各点灯領域を順次切り替える構成としても良い。

## 【符号の説明】

50

## 【 0 0 7 9 】

LPN ... 液晶表示パネル

AR ... アレイ基板 CT ... 対向基板 LQ ... 液晶層

DSP ... 画面 UP ... 上部 CN ... 中央部 LW ... 下部 PX ... 画素

EP ... 画素電極 W ... スイッチング素子 ET ... 対向電極

BL ... バックライト

【 図 1 】

【 図 2 】

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

【図7】

図7

【図 8】

図 8

【図 9】

【図 10】

## フロントページの続き

|              |         |              |

|--------------|---------|--------------|

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|              | G 0 9 G | 3/20 6 4 2 B |

|              | G 0 2 F | 1/133 5 0 5  |

|              | G 0 2 F | 1/133 5 3 5  |

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100172580

弁理士 赤穂 隆雄

(74)代理人 100179062

弁理士 井上 正

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 將訓

(72)発明者 新木 盛右

埼玉県深谷市幡羅町一丁目9番地2 株式会社ジャパンディスプレイセントラル内

(72)発明者 西山 和廣

埼玉県深谷市幡羅町一丁目9番地2 株式会社ジャパンディスプレイセントラル内

(72)発明者 三木 啓央

埼玉県深谷市幡羅町一丁目9番地2 株式会社ジャパンディスプレイセントラル内

F ターム(参考) 2H193 ZA04 ZC25 ZD23 ZE02 ZE11 ZF16 ZF21 ZF31 ZG02 ZG44

ZG58 ZQ14

5C006 AF69 BB16 BB29 BC06 EA01

5C080 AA10 BB06 DD01 DD06 FF11