(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6108936号

(P6108936)

(45) 発行日 平成29年4月5日(2017.4.5)

(24) 登録日 平成29年3月17日(2017.3.17)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| HO4N 5/374 (2011.01) | HO4N 5/335 740 |

| HO4N 5/378 (2011.01) | HO4N 5/335 780 |

| HO4N 5/357 (2011.01) | HO4N 5/335 570 |

請求項の数 20 (全 21 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-91427 (P2013-91427)    |

| (22) 出願日  | 平成25年4月24日 (2013.4.24)        |

| (65) 公開番号 | 特開2014-216769 (P2014-216769A) |

| (43) 公開日  | 平成26年11月17日 (2014.11.17)      |

| 審査請求日     | 平成28年4月22日 (2016.4.22)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (72) 発明者  | 小林 大祐<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内        |

| (72) 発明者  | 大西 智也<br>東京都大田区下丸子3丁目30番2号キヤノン株式会社内        |

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システム、撮像装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が入射する電磁波に基づく電気信号を出力する、行列状に設けられた複数の電気信号出力部と、各々が前記電気信号出力部に対応して設けられ、各々が前記電気信号出力部から入力される前記電気信号をデジタル信号に変換する複数のA / D変換部と、を有する画素アレイ、および、各々が前記電気信号出力部の各列に対応して設けられた、前記デジタル信号を保持する複数の記憶部を有し、

さらに、前記電気信号出力部に駆動バイアスを供給する第1の信号線と、

前記A / D変換部から前記記憶部に前記デジタル信号を伝送する第2の信号線と、

を有する撮像装置であって、

前記第1の信号線と前記第2の信号線との間に前記電気信号出力部が設けられていることを特徴とする撮像装置。

## 【請求項 2】

各々が入射する電磁波に基づく電気信号を出力する、行列状に設けられた複数の電気信号出力部と、各々が前記電気信号出力部に対応して設けられ、各々が前記電気信号出力部から入力される前記電気信号をデジタル信号に変換する複数のA / D変換部と、を有する画素アレイ、および、各々が前記電気信号出力部の各列に対応して設けられた、前記デジタル信号を保持する複数の記憶部を有し、

さらに、前記A / D変換部に駆動バイアスを供給する第1の信号線と、

前記A / D変換部から前記記憶部に前記デジタル信号を伝送する第2の信号線と、

10

20

を有する撮像装置であって、

前記第1の信号線と前記第2の信号線との間に、前記電気信号出力部が設けられていることを特徴とする撮像装置。

【請求項3】

互いに隣接する第1の電気信号出力部と第2の電気信号出力部とを有し、

複数の第1の信号線の間に、前記第1の電気信号出力部と前記第2の電気信号出力部とが設けられていると共に、前記第1の電気信号出力部と前記第2の電気信号出力部の間に前記第2の信号線が設けられているか、

複数の第2の信号線の間に、前記第1の電気信号出力部と前記第2の電気信号出力部とが設けられていると共に、前記第1の電気信号出力部と前記第2の電気信号出力部の間に前記第1の信号線が設けられていることを特徴とする請求項1または2に記載の撮像装置。10

【請求項4】

前記記憶部が、第1の記憶部と、第2の記憶部と、を有し、

前記撮像装置が、さらに前記第2の信号線と前記記憶部との間の電気的経路に選択回路を有し、

前記複数のA/D変換部の各々が、互いに異なる列の前記電気信号出力部に対応して設けられ、

前記選択回路が、一の前記第2の信号線が伝送する、前記複数のA/D変換部の一方の前記デジタル信号を前記第1の記憶部に出力し、20

前記選択回路が、前記一の第2の信号線が伝送する、前記複数のA/D変換部の他方の前記デジタル信号を前記第2の記憶部に出力することを特徴とする請求項1～3のいずれかに記載の撮像装置。

【請求項5】

前記画素アレイが、各々が前記電気信号出力部と前記A/D変換部とを有する行列状に設けられた複数の画素を有することを特徴とする請求項1～4のいずれかに記載の撮像装置。

【請求項6】

前記画素が、前記電気信号を増幅した信号を前記A/D変換部に出力する増幅器をさらに有することを特徴とする請求項5に記載の撮像装置。30

【請求項7】

前記撮像装置が、前記増幅器に駆動バイアスを供給する第3の信号線をさらに有し、

前記第1の信号線と前記第3の信号線とを含む信号線群と、前記第2の信号線との間に、前記電気信号出力部が設けられていることを特徴とする請求項6に記載の撮像装置。

【請求項8】

1つの前記A/D変換部が、複数行の前記電気信号出力部に対応して設けられていることを特徴とする請求項1～4のいずれかに記載の撮像装置。

【請求項9】

前記画素アレイは、各々が前記電気信号を増幅した信号を前記A/D変換部に出力する複数の増幅器をさらに有し、40

1つの前記増幅器あるいは複数の前記増幅器が、前記複数行の前記電気信号出力部に対応して設けられた前記1つのA/D変換部に対応して設けられていることを特徴とする請求項8に記載の撮像装置。

【請求項10】

前記撮像装置が、前記増幅器に駆動バイアスを供給する第3の信号線をさらに有し、

前記第1の信号線と前記第3の信号線とを含む信号線群と、前記第2の信号線との間に、前記電気信号出力部が設けられていることを特徴とする請求項9に記載の撮像装置。

【請求項11】

1つの前記A/D変換部が、複数行の前記電気信号出力部および、複数列の前記電気信号出力部と、に対応して設けられていることを特徴とする請求項1～4のいずれかに記載50

の撮像装置。

【請求項 1 2】

前記撮像装置は、各々が前記電気信号を増幅した信号を前記 A / D 変換部に出力する複数の増幅器をさらに有し、

前記増幅器が、前記 1 つの A / D 変換部に対応して設けられ、

前記第 1 の信号線と前記第 2 の信号線との間に、前記増幅器が設けられていることを特徴とする請求項 1 1 に記載の撮像装置。

【請求項 1 3】

前記撮像装置が、前記増幅器に駆動バイアスを供給する第 3 の信号線をさらに有し、

前記第 1 の信号線と前記第 3 の信号線とを含む信号線群と、前記第 2 の信号線との間に前記電気信号出力部が設けられていることを特徴とする請求項 1 2 に記載の撮像装置。

【請求項 1 4】

1 つの前記 A / D 変換部が、複数行の前記電気信号出力部および、複数列の前記電気信号出力部に対応して設けられ、

前記撮像装置はさらに、前記 A / D 変換部にランプ信号を供給する第 4 の信号線を有し、

前記第 1 の信号線と前記第 4 の信号線との間に、前記 1 つの A / D 変換部が設けられていることを特徴とする請求項 1 3 に記載の撮像装置。

【請求項 1 5】

前記 A / D 変換部が、ランプ信号と前記電気信号に基づく信号とを比較した結果を示す比較結果信号を生成する比較器を有することを特徴とする請求項 1 ~ 1 4 のいずれかに記載の撮像装置。

【請求項 1 6】

前記撮像装置が、

クロック信号を計数したカウンタ信号を生成するカウンタと、

前記比較器から前記比較結果信号が入力されるメモリと、

前記カウンタから前記メモリに前記カウンタ信号を供給するカウンタ信号線と、をさらに有し、

前記第 2 の信号線および前記カウンタ信号線を含む信号線群と、前記第 1 の信号線との間に、前記電気信号出力部が設けられていることを特徴とする請求項 1 5 に記載の撮像装置。

【請求項 1 7】

前記撮像装置が、前記メモリに駆動バイアスを供給する信号線をさらに有し、

前記第 2 の信号線および前記カウンタ信号線を含む信号線群と、前記メモリに駆動バイアスを供給する前記信号線との間に、前記電気信号出力部が設けられていることを特徴とする請求項 1 6 に記載の撮像装置。

【請求項 1 8】

請求項 1 ~ 1 7 のいずれかに記載の撮像装置と、

前記撮像装置が出力する信号処理部と、を有することを特徴とする撮像システム。

【請求項 1 9】

撮像装置の駆動方法であって、

前記撮像装置は、

各々が入射する電磁波に基づく電気信号を出力する、行列状に設けられた複数の電気信号出力部と、各々が前記電気信号出力部に対応して設けられ、各々が前記電気信号出力部から入力される前記電気信号をデジタル信号に変換する複数の A / D 変換部と、を有する画素アレイ、および、各々が前記電気信号出力部の各列に対応して設けられた、前記デジタル信号を保持する複数の記憶部と、

前記電気信号出力部に駆動バイアスを供給する第 1 の信号線と、

前記 A / D 変換部から前記記憶部に前記デジタル信号を伝送する第 2 の信号線と、を有し、

10

20

30

40

50

さらに、前記画素アレイは、各々が前記電気信号を増幅した信号を前記A／D変換部に出力する複数の増幅器を有し、

前記第1の信号線と前記第2の信号線との間に、前記電気信号出力部が設けられており、

前記増幅器が、前記1つのA／D変換部に対応して設けられており、

前記駆動方法は、

前記1つのA／D変換部が、一の前記電気信号出力部の前記電気信号を増幅した信号をA／D変換している期間に、

前記増幅器が、他の前記電気信号出力部の前記電気信号の増幅を行うことを特徴とする撮像装置の駆動方法。

10

#### 【請求項20】

撮像装置の駆動方法であって、

前記撮像装置は、

各々が入射する電磁波に基づく電気信号を出力する、行列状に設けられた複数の電気信号出力部と、各々が前記電気信号出力部に対応して設けられ、各々が前記電気信号出力部から入力される前記電気信号をデジタル信号に変換する複数のA／D変換部と、を有する画素アレイ、および、各々が前記電気信号出力部の各列に対応して設けられた、前記デジタル信号を保持する複数の記憶部と、

前記A／D変換部に駆動バイアスを供給する第1の信号線と、

前記A／D変換部から前記記憶部に前記デジタル信号を伝送する第2の信号線と、

20

さらに、前記画素アレイは、各々が前記電気信号を増幅した信号を前記A／D変換部に出力する複数の増幅器を有し、

前記第1の信号線と前記第2の信号線との間に、前記電気信号出力部が設けられており、

前記増幅器が、前記1つのA／D変換部に対応して設けられており、

前記駆動方法は、

前記1つのA／D変換部が、一の前記電気信号出力部の前記電気信号を増幅した信号をA／D変換している期間に、

前記増幅器が、他の前記電気信号出力部の前記電気信号の増幅を行うことを特徴とする撮像装置の駆動方法。

30

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、入射する電磁波を電荷に変換する撮像装置、撮像システム、撮像装置の駆動方法に関する。

##### 【背景技術】

##### 【0002】

入射する電磁波を電荷に変換する撮像装置が知られている。このような撮像装置の一例として、非特許文献1には、入射光を光電変換する光電変換部と、光電変換部の出力する信号をデジタル信号に変換するA／D変換部と、を有する画素を有する撮像装置がある。

40

##### 【先行技術文献】

##### 【非特許文献】

##### 【0003】

【非特許文献1】Stuart Kleinfelder, SukHwan Lim, Xinqiao Liu, and Abbas El Gamal, "A 10000 Frames/s CMOS Digital Pixel Sensor", IEEE JOURNAL OF SOLID-STATE CIRCUITS, DECEMBER 1501, VOL. 36, NO. 12, p. 2049 - 2059

##### 【発明の概要】

50

**【発明が解決しようとする課題】****【0004】**

非特許文献1の撮像装置で、各画素に入力する、あるいは各画素から出力されるデジタル信号を伝送するデジタル信号線を、光電変換部、A/D変換部に電位を供給するアナログ信号線に近接して配置したとする。この場合、デジタル信号線が伝送するデジタル信号の電位の変動によって、アナログ信号線の電位が変動することがある。このアナログ信号線の電位の変動が、A/D変換の精度の低下を生じさせることがあった。

**【課題を解決するための手段】****【0005】**

本発明は上記の課題を解決するために為されたものであり、一の態様は、各々が入射する電磁波に基づく電気信号を出力する、行列状に設けられた複数の電気信号出力部と、各々が前記電気信号出力部に対応して設けられ、各々が前記電気信号出力部から入力される前記電気信号をデジタル信号に変換する複数のA/D変換部と、を有する画素アレイ、および、各々が前記電気信号出力部の各列に対応して設けられた、前記デジタル信号を保持する複数の記憶部を有し、さらに、前記電気信号出力部に駆動バイアスを供給する第1の信号線と、前記A/D変換部から前記記憶部に前記デジタル信号を伝送する第2の信号線と、を有する撮像装置であって、前記第1の信号線と前記第2の信号線との間に前記電気信号出力部が設けられていることを特徴とする撮像装置である。

**【0006】**

また別の態様は、各々が入射する電磁波に基づく電気信号を出力する、行列状に設けられた複数の電気信号出力部と、各々が前記電気信号出力部に対応して設けられ、各々が前記電気信号出力部から入力される前記電気信号をデジタル信号に変換する複数のA/D変換部と、を有する画素アレイ、および、各々が前記電気信号出力部の各列に対応して設けられた、前記デジタル信号を保持する複数の記憶部を有し、さらに、前記A/D変換部に駆動バイアスを供給する第1の信号線と、前記A/D変換部から前記記憶部に前記デジタル信号を伝送する第2の信号線と、を有する撮像装置であって、前記第1の信号線と前記第2の信号線との間に、前記電気信号出力部が設けられていることを特徴とする撮像装置である。

**【0007】**

また別の態様は、撮像装置の駆動方法であって、前記撮像装置は、各々が入射する電磁波に基づく電気信号を出力する、行列状に設けられた複数の電気信号出力部と、各々が前記電気信号出力部に対応して設けられ、各々が前記電気信号出力部から入力される前記電気信号をデジタル信号に変換する複数のA/D変換部と、を有する画素アレイ、および、各々が前記電気信号出力部の各列に対応して設けられた、前記デジタル信号を保持する複数の記憶部と、前記電気信号出力部に駆動バイアスを供給する第1の信号線と、前記A/D変換部から前記記憶部に前記デジタル信号を伝送する第2の信号線と、を有し、さらに、前記画素アレイは、各々が前記電気信号を増幅した信号を前記A/D変換部に出力する複数の増幅器を有し、前記第1の信号線と前記第2の信号線との間に、前記電気信号出力部が設けられており、前記増幅器が、前記1つのA/D変換部に対応して設けられており、前記駆動方法は、前記1つのA/D変換部が、一の前記電気信号出力部の前記電気信号を増幅した信号をA/D変換している期間に、前記増幅器が、他の前記電気信号出力部の前記電気信号の増幅を行うことを特徴とする撮像装置の駆動方法である。

**【0008】**

また、別の態様は、撮像装置の駆動方法であって、前記撮像装置は、各々が入射する電磁波に基づく電気信号を出力する、行列状に設けられた複数の電気信号出力部と、各々が前記電気信号出力部に対応して設けられ、各々が前記電気信号出力部から入力される前記電気信号をデジタル信号に変換する複数のA/D変換部と、を有する画素アレイ、および、各々が前記電気信号出力部の各列に対応して設けられた、前記デジタル信号を保持する複数の記憶部と、前記A/D変換部に駆動バイアスを供給する第1の信号線と、前記A/D変換部から前記記憶部に前記デジタル信号を伝送する第2の信号線と、を有し、さらに

10

20

30

40

50

、前記画素アレイは、各々が前記電気信号を増幅した信号を前記A / D変換部に出力する複数の増幅器を有し、前記第1の信号線と前記第2の信号線との間に、前記電気信号出力部が設けられており、前記増幅器が、前記1つのA / D変換部に対応して設けられており、前記駆動方法は、前記1つのA / D変換部が、一の前記電気信号出力部の前記電気信号を増幅した信号をA / D変換している期間に、前記増幅器が、他の前記電気信号出力部の前記電気信号の増幅を行うことを特徴とする撮像装置の駆動方法である。

【発明の効果】

【0009】

本発明により、A / D変換の精度の低下が生じにくい撮像装置を提供することができる。

10

【図面の簡単な説明】

【0010】

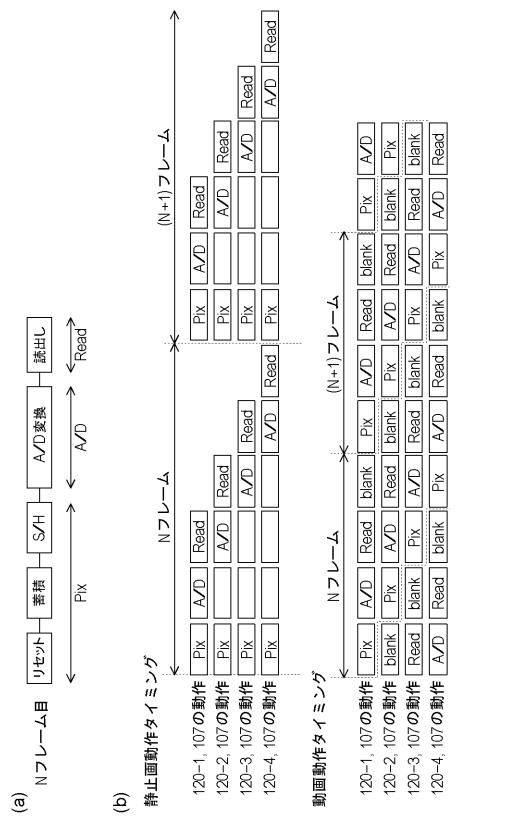

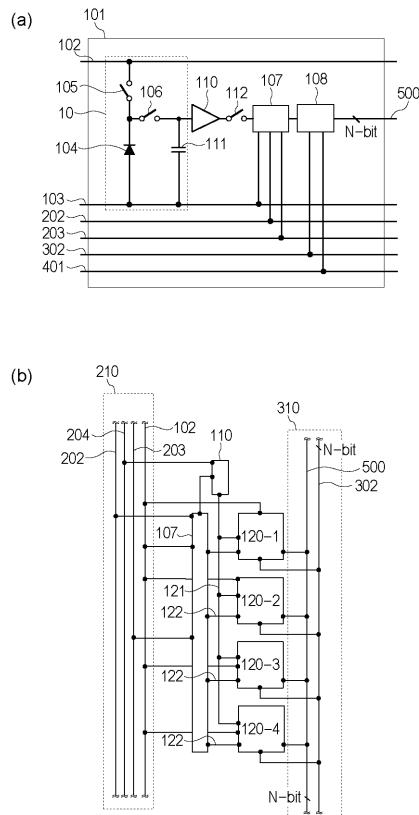

【図1】撮像装置の一例と、画素出力回路の一例を示した模式図

【図2】画素出力回路の一例の模式図と、画素出力回路の動作の一例のタイミング図

【図3】撮像装置の他の一例と、画素出力回路の他の一例を示した模式図

【図4】撮像装置の他の一例と、画素出力回路の他の一例の模式図。

【図5】撮像装置の動作の他の一例を示したタイミング図

【図6】画素出力回路の他の一例と、撮像装置の他の一例の模式図

【図7】A / D変換部の一例の模式図と、撮像装置の動作の他の一例のタイミング図。

【図8】撮像装置の他の一例と、A / D変換部の他の一例の模式図

20

【図9】撮像装置の他の一例の動作のタイミング図と、撮像装置の他の一例の模式図。

【図10】撮像システムの一例の模式図。

【発明を実施するための形態】

【0011】

(実施例1)

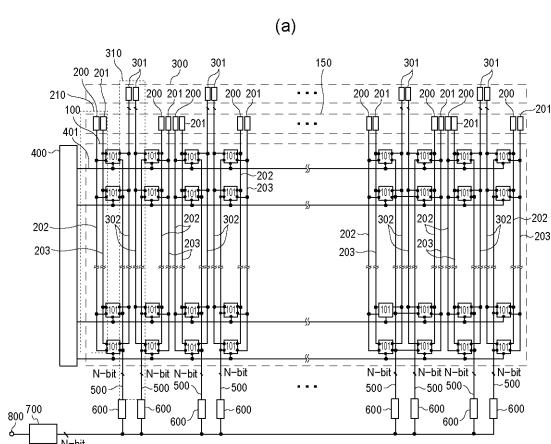

図1(a)は、本実施例の撮像装置の構成例を示す図である。

【0012】

図1(a)の画素アレイ100は、行列状に設けられた画素出力回路101を有している。駆動バイアス群150は、各画素出力回路101を駆動する駆動バイアス回路200、ランプ信号供給回路201を含む。本実施例では、列ごとに駆動バイアス回路200、ランプ信号供給回路201を備える構成である。各列に設けられた駆動バイアス線202は、対応する駆動バイアス回路200のそれぞれから、対応する列に設けられた画素出力回路101に駆動バイアスを供給する。駆動バイアスは、画素出力回路101を構成する回路によって複数のバイアスとなることもあり、電圧、あるいは電流のいずれかで供給される。また、各列に設けられたランプ信号線203は、ランプ信号供給回路201のそれぞれから、各列の画素出力回路101にランプ信号を供給する。カウンタ群300は、カウンタ回路301を含む。カウンタ回路301は、不図示のクロック信号生成部から供給されるクロック信号を計数することでカウンタ信号を生成する。さらにカウンタ回路301は生成したカウンタ信号を、画素出力回路101に供給する。本実施例では、列ごとにカウンタ回路301を備える構成であり、各列共通のカウンタ信号線302によって、各列の画素出力回路101にN-ビットのカウンタ信号を供給する。尚、カウンタ信号線302は、N-ビットに応じてN本配置される。垂直制御回路400は画素出力回路101の動作を行単位で制御する。制御信号を供給する制御信号線401は、簡単のため1本で図示しているが、駆動する回路の制御方法、あるいは画素出力回路101の選択動作に基づいて、複数本の制御信号線としてもよい。画素出力回路101から、共通出力線500を介してデジタルメモリ600にデジタル信号が outputされる。共通出力線500は、N-ビットのデジタル信号を伝送するため、1列の画素出力回路101に対しN本設けられている。デジタルメモリ600に保持されたデジタルデータは、出力部700に転送される。出力部700は、パラレル/シリアル変換機能(以下、P/S変換機能とする)を有する。出力部700は、デジタルメモリ600から転送されるN-ビットのパラレル形式の

30

40

50

デジタル信号を、シリアル形式のデジタル信号に変換する。そして、出力部 700 は、変換したシリアル形式の N - ビットのデジタル信号を出力端子 800 に出力する。出力端子 800 は、出力部 700 から出力される、シリアル形式の N - ビットのデジタル信号を出力する。デジタルメモリ 600 は、共通出力線 500 が伝送するデジタル信号を保持する記憶部である。図 1 ( a ) では、電気信号出力部 10、A / D 変換部 107 に駆動バイアスを供給する駆動バイアス線 102 が不図示であるが、アナログ信号線群 210 が設けられた領域内に、駆動バイアス線 202 と並行して設けられている。

#### 【 0013 】

図 1 ( b ) は、画素出力回路 101 に含まれる回路ブロックの配置例である。画素出力回路 101 は、電気信号出力部 10、A / D 変換部 107、画素内メモリ 108 を有する。駆動バイアス線 102 は、電気信号出力部 10、A / D 変換部 107 に駆動バイアスを供給する。駆動バイアス線 202 は、A / D 変換部 107 に駆動バイアスを供給する。ランプ信号線 203 は、A / D 変換部 107 にランプ信号を供給する。カウンタ信号線 302 のカウンタ信号が、画素内メモリ 108 に出力される。画素内メモリ 108 は、A / D 変換部 107 が output するラッチ信号の信号値が変化した時のカウント値のカウンタ信号を保持する。この保持したカウンタ信号が、画素出力回路 101 が output するデジタル信号である。画素内メモリ 108 は、保持したデジタル信号を、制御信号線 401 から出力される制御信号に基づいて、共通出力線 500 に出力する。本実施例のデジタル信号線群 310 はカウンタ信号線 302、共通出力線 500 を含む。本実施例のアナログ信号線群 210 は、駆動バイアス線 102、202、ランプ信号線 203 を含む。画素内メモリ 108 は、例えば SRAM ( Static Random Access Memory ) の構成であっても良い。

#### 【 0014 】

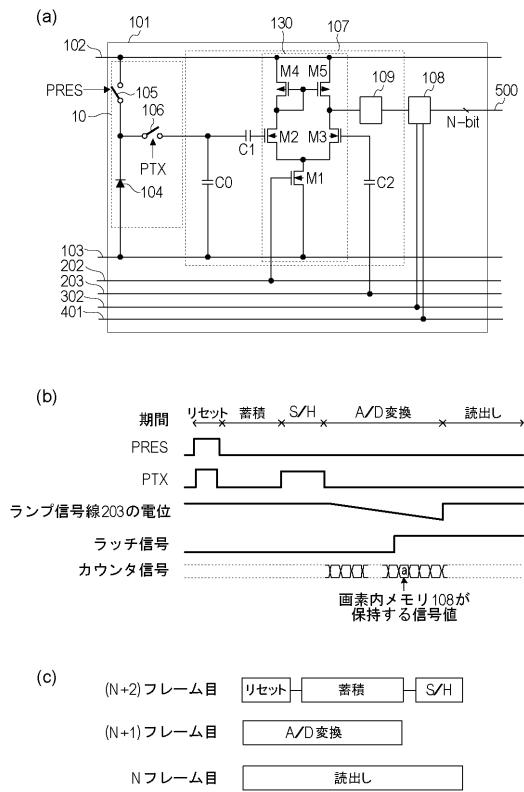

図 2 ( a ) を参照しながら、電気信号出力部 10 と A / D 変換部 107 について説明する。図 2 ( a ) は画素出力回路 101 の構成の一例である。電気信号出力部 10 は、光電変換部 104、スイッチ 105、スイッチ 106 を有する。スイッチ 105 は、垂直制御回路 400 から出力される信号 P R E S の信号値に基づいて、駆動バイアス線 102 と光電変換部 104 の導通、非導通を切り替える。スイッチ 106 は、垂直制御回路 400 から出力される信号 P T X の信号値に基づいて、光電変換部 104 と A / D 変換部 107 の導通、非導通を切り替える。スイッチ 106 が導通すると、光電変換部 104 から A / D 変換部 107 に、入射光を光電変換して生成した信号が output される。以下、光電変換部 104 が入射光を光電変換して生成した信号を、光電変換信号と表記する。光電変換部 104 は本実施例の入射する電磁波に基づく電荷を生成する変換部である。

#### 【 0015 】

A / D 変換部 107 は、容量素子 C0、C1、C2、比較器 130、ラッチ部 109 を有する。光電変換部 104 が output した光電変換信号は、容量素子 C0、C1 に与えられる。容量素子 C0 は、一方のノードには光電変換信号が与えられ、他方のノードには、電源線 103 から接地電位が与えられる。比較器 130 は、トランジスタ M1、M2、M3、M4、M5 を有する。トランジスタ M2 の入力ノードには、光電変換信号が容量素子 C1 を介して与えられる。一方、トランジスタ M3 の入力ノードには、ランプ信号線 203 から容量素子 C2 を介してランプ信号が与えられる。ランプ信号は、時間に依存して電位が変化する信号である。比較器 130 は、光電変換信号とランプ信号とを比較した結果を示す比較結果信号をラッチ部 109 に出力する。駆動バイアス線 202 は、トランジスタ M1 の入力ノードに駆動バイアスを供給する。また、駆動バイアス線 102 は、トランジスタ M4、M5 のそれぞれの一方のノードに電位を供給する。

#### 【 0016 】

図 2 ( b ) は、図 2 ( a ) で示した画素出力回路 101 の動作の一例を示したタイミング図である。リセット期間に、垂直制御回路 400 は信号 P R E S、P T X を H i g h レベル ( 以下、H レベルと表記する ) とする。これにより、スイッチ 105、106 が導通するため、光電変換部 104 の電位がリセットされる。また、スイッチ 105、106 が

10

20

30

40

50

導通することによって、容量素子C0、C1のそれぞれの一方のノードの電位がリセットされる。トランジスタM2、M3の入力ノードの電位についても、不図示のリセット回路により、リセットされる。トランジスタM2の入力ノードのリセットは、例えば、トランジスタM2の入力ノードと、トランジスタM2のドレインとなるノードとを短絡させればよい。同様に、トランジスタM3の入力ノードのリセットについても、トランジスタM3の入力ノードと、トランジスタM3のドレインとなるノードとを短絡させればよい。

#### 【0017】

垂直制御回路400が信号PRES, PTXをそれぞれL0Wレベル(以下、Lレベルと表記する)と、光電変換部104では入射光に基づく電荷の蓄積が行われる。光電変換部104が電荷を蓄積する蓄積期間が終了すると、垂直制御回路400は信号PTXをHレベルとする。これにより、光電変換信号が容量素子C0、C1に出力される。また、光電変換信号が容量素子C1を介してトランジスタM2の入力ノードに出力される。その後、垂直制御回路400は、信号PTXをLレベルとする。この信号PTXがHレベルとなってからLレベルとなるまでの期間が、サンプルホールド期間(図2(b)ではS/Hと表記している)である。

10

#### 【0018】

サンプルホールド期間の後、ランプ信号供給回路201は、ランプ信号の、時間に依存した電位の変化を開始する。比較器130がラッチ部109に出力する比較結果信号の信号値が変化すると、ラッチ部109が画素内メモリ108に出力するラッチ信号の信号値がLレベルからHレベルに変化する。画素内メモリ108は、ラッチ信号の信号値がLレベルからHレベルに変化した時のカウンタ信号(図2(b)ではaとして示している)を保持する。その後、ランプ信号供給回路201は、ランプ信号の、時間に依存した電位の変化を終了する。このランプ信号供給回路201が、ランプ信号の、時間に依存した電位の変化を行わせている期間がA/D変換期間である。A/D変換期間が終了した後、垂直制御回路400は、制御信号線401の信号値を変化させて、画素内メモリ108から、保持したデジタル信号を共通出力線500に出力させる。この垂直制御回路400が、各画素出力回路101からデジタル信号を順次、共通出力線500に出力させている期間が、読み出し期間である。

20

#### 【0019】

図2(c)は、画素出力回路101において、異なるフレームの光電変換信号を並列で処理する場合の駆動タイミングである。図2(c)に示した、リセット、蓄積、S/H、A/D変換、読み出しの各期間は、図2(b)に示した各期間と対応している。図2(c)に示した動作は、Nフレーム目の読み出し期間と、(N+1)フレーム目のA/D変換期間と、を重ねた動作である。また、図2(c)に示した動作は、(N+1)フレーム目のA/D変換期間と、(N+2)フレーム目のリセット期間、蓄積期間と、を重ねた動作である。図2(c)に示した動作では、A/D変換部107と電気信号出力部10が並行して動作する。A/D変換部107が動作しているため、デジタル信号線群310であるカウンタ信号線302、共通出力線500の電位が変化する。

30

#### 【0020】

デジタル信号線群310とアナログ信号線群210とが近接して設けられている場合、デジタル信号線群310とアナログ信号線群210との間の寄生容量を介して、一方の電位の変動が、他方の電位に変動を生じさせる。特に、デジタル信号線群310は、アナログ信号線群210に比べて高い周波数で電位が変化するため、デジタル信号線群310の電位の変動が、アナログ信号線群210の電位の変動を生じさせやすい。

40

#### 【0021】

本実施例の形態では、デジタル信号の伝送によって、駆動バイアス線102、202、ランプ信号線203の電位に変動が生じる。駆動バイアス線102、202の電位に変動が生じた場合には、比較器130のトランジスタM1に流れる電流量が変動することによって、比較器130の比較動作の精度の低下が生じる。また、ランプ信号線203の電位に変動が生じた場合には、ランプ信号の線形性が低下することによって、比較器130の

50

比較動作の精度の低下が生じる。比較器 130 の比較動作の精度の低下は、A/D 変換部 107 の A/D 変換精度の低下に繋がる。従って、駆動バイアス線 102、202、ランプ信号線 203 に電位の変動が生じると、A/D 変換部 107 の A/D 変換精度が低下する。

【0022】

本実施例では、駆動バイアス線 102、202 とランプ信号線 203 とのアナログ信号線群 210 と、カウンタ信号線 302 と共に出力線 500 とのデジタル信号線群 310 とが、電気信号出力部 10 を挟むように設けられている。これにより、本実施例の撮像装置は、デジタル信号線群 310 の電位の変動によるアナログ信号線群 210 の電位の変動が生じにくい。よって、デジタル信号線群 310 の電位の変動による A/D 変換精度の低下を低減することができる。また、駆動バイアス線 102 は、光電変換部 104、容量素子 C0、C1 のリセット電位を与える。本実施例の撮像装置は、デジタル信号線群 310 の電位の変動による駆動バイアス線 102 の電位の変動が生じにくいため、光電変換部 104 のリセット電位の変動を低減することができる。

【0023】

本実施例では、駆動バイアス線 102、202、ランプ信号線 203 を含むアナログ信号線群 210 と、カウンタ信号線 302、共通出力線 500 を含むデジタル信号線群 310 が電気信号出力部 10 を挟むように設けている形態を説明した。本実施例は、この形態に限定されるものではなく、第 1 の信号線である駆動バイアス線 102 あるいは駆動バイアス線 202 と、第 2 の信号線である共通出力線 500 と、が電気信号出力部 10 を挟むように設けている形態であれば良い。本実施例は、アナログ信号線群 210 が駆動バイアス線 102、202、ランプ信号線 203 を含む例を説明した。アナログ信号線群 210 は、他の信号線を含んでいても良く、例えば、電源線 103 をさらに含んでいても良い。電源線 103 は、光電変換部 104、容量素子 C0 に電源を供給している。従って、デジタル信号線群 310 の電位の変動による電源線 103 の電位の変動を生じにくくすることで、光電変換信号の変動を低減することができる。また、アナログ信号線群 210 は、画素内メモリ 108 に電位を供給するバイアス線を含んでいても良い。つまり、アナログ信号線群 210 が、電気信号出力部 10、A/D 変換部 107、画素内メモリ 108 の各々に電位を供給する信号線を含む形態であっても良い。

【0024】

本実施例では、図 1 (a) のように、複数のアナログ信号線群 210 の間に複数の電気信号出力部 10 が挟まれて設けられている。また、複数のアナログ信号線群 210 に挟まれた複数の電気信号出力部 10 の間に、デジタル信号線群 310 が設けられている。他の見方をすれば、複数のデジタル信号線群 310 の間に複数の電気信号出力部 10 が挟まれて設けられている。また、複数のデジタル信号線群 310 に挟まれた複数の電気信号出力部 10 の間に、アナログ信号線群 210 が設けられている。

【0025】

尚、本実施例では、図 2 (c) のように、A/D 変換部 107 と電気信号出力部 10 が並行して動作する例を説明した。本実施例はこの形態には限定されない。

【0026】

尚、本実施例では、列ごとにデジタルメモリ 600 を設ける構成を示したが、行ごとにデジタルメモリ 600 を設ける構成としても良い。

【0027】

また、本実施例では、駆動バイアス線 102、202 とランプ信号線 203 のそれぞれが、同じ列の画素出力回路 101 に共通して電気的に接続される構成を示した。他の形態として、駆動バイアス線 102、202 とランプ信号線 203 のそれぞれが、同じ行の画素出力回路 101 に共通して電気的に接続されるようにしても良い。

【0028】

また、本実施例では、カウンタ回路 301 が各列に設けられている構成を示したが、全ての画素出力回路 101 に共通のカウンタ信号を出力するカウンタ回路 301 を 1 つ設け

10

20

30

40

50

る構成としても良い。この形態の場合は、画素内メモリ 108 が、A / D 変換期間の開始時のカウンタ信号の信号値と、ラッチ信号の信号値が変化した時のカウンタ信号の信号値と、を保持するようにすればよい。そして、画素内メモリ 108、デジタルメモリ 600、出力部 700 のいずれかで、A / D 変換期間の開始時のカウンタ信号の信号値と、ラッチ信号の信号値が変化した時のカウンタ信号の信号値との差の信号を得るようすればよい。

#### 【 0029 】

また、本実施例では、ランプ信号の電位の変化が直線的な形態を説明した。他の形態として、ランプ信号の電位が階段状に変化する形態であっても良い。このランプ信号の電位が階段状に変化する形態も、時間に依存して電位が変化する形態に含まれる。

10

#### 【 0030 】

また、本実施例では、A / D 変換部 107 が、ランプ信号を用いた A / D 変換を行う形態を基に説明した。本実施例は他に、逐次比較型、パイプライン型など、他の A / D 変換形式であっても適用できる。例えば、逐次比較型の A / D 変換であれば、ランプ信号線 203 の代わりに、光電変換信号と逐次比較する電位を生成するための基準電位を供給する信号線を設ければよい。つまり、デジタル信号を伝送するデジタル信号線群 310 と、電気信号出力部 10、A / D 変換部 107 を駆動する電位を供給するアナログ信号線群 210 と、を有する形態であれば、本実施例を適用することができる。

#### 【 0031 】

光電変換部 104 は入射する電磁波に基づく電荷を生成する変換部の一例である。入射する電磁波に基づく電荷を生成する変換部は他に、例えば、X 線、赤外線といった入射する電磁波に基づく電荷を生成する形態であってもよい。

20

#### 【 0032 】

##### ( 実施例 2 )

本実施例の撮像装置について、実施例 1 と異なる点を中心に説明する。

#### 【 0033 】

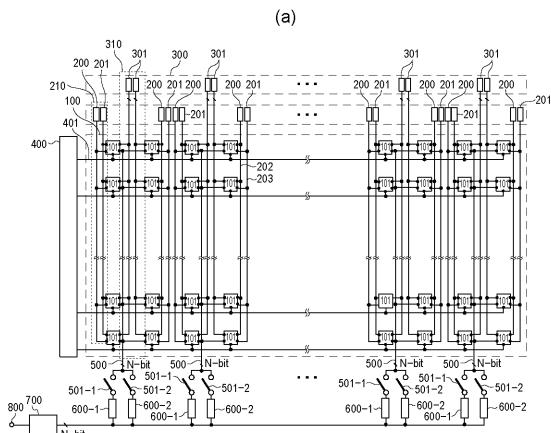

図 3 ( a ) は、本実施例の撮像装置の構成例を示す図である。図 1 ( a ) に示した構成との違いは、1 つの共通出力線 500 を、互いに隣接する 2 列の画素出力回路 101 と共有している点である。

#### 【 0034 】

30

それぞれの共通出力線 500 には、不図示の制御部によって導通、非導通が制御されるスイッチ 501-1、501-2 を介して、各列の画素出力回路 101 が output するデジタル信号を保持するデジタルメモリ 600-1、600-2 が電気的に接続されている。デジタルメモリ 600-1、600-2 は画素出力回路 101 の列に対応して設けられている。スイッチ 501-1、501-2 は、共通出力線 500 に出力されるデジタル信号の出力先を、デジタルメモリ 600-1、600-2 のいずれかから選択する選択回路である。デジタルメモリ 600-1 は、一方の列の画素出力回路 101 の画素信号に基づくデジタル信号を保持する第 1 の記憶部である。また、デジタルメモリ 600-2 は、他方の列の画素出力回路 101 の画素信号に基づくデジタル信号を保持する第 2 の記憶部である。

40

#### 【 0035 】

図 3 ( b ) は、本実施例の画素出力回路 101 の一例を示した図である。図 1 ( b ) に示した画素出力回路 101 と異なるのは、図 3 ( b ) の画素出力回路 101 が、画素内メモリ 108 と共に出力線 500 との導通、非導通を切り替えるスイッチ 502 を有する点である。スイッチ 502 は、垂直制御回路 400 から出力される指示信号に基づいて、導通、非導通を切り替える。垂直制御回路 400 は、共通出力線 500 を共有する画素出力回路 101 の間でスイッチ 502 を導通させる期間を排他的に異ならせる。これにより、共通出力線 500 には、2 列の画素出力回路 101 から順次、デジタル信号が出力される。

#### 【 0036 】

50

共通出力線 500 を共有する一方の画素出力回路 101 のスイッチ 502 が導通すると、不図示の制御部がスイッチ 501-1 を導通させる。これにより、デジタルメモリ 600-1 が、共通出力線 500 を共有する一方の画素出力回路 101 のデジタル信号を保持する。また、共通出力線 500 を共有する他方の画素出力回路 101 のスイッチ 502 が導通すると、不図示の制御部がスイッチ 501-2 を導通させる。これにより、デジタルメモリ 600-2 が、共通出力線 500 を共有する他方の画素出力回路 101 のデジタル信号を保持する。

#### 【0037】

本実施例では、互いに隣接する 2 列の画素出力回路 101 で共通出力線 500 を共有する。これにより、図 1 (a) に示した構成と比較して共通出力線 500 の配線数を 1/2 に減らすことができる。これによって、例えば、共通出力線 500 の配線数を減らした分、光電変換部 104 の開口率を高くしたり、画素アレイ 100 の面積を縮小したりすることができる。特に、N-ビットのデジタル信号を画素出力回路 101 からデジタルメモリ 600 にパラレルに伝送する場合には、共通出力線 500 は N 本の配線となる。よって、本実施例のように 2 列の画素出力回路 101 で共通出力線 500 を共有すると、N 本の配線を減らすことができる。本実施例では、2 列の画素出力回路 101 が 1 つの共通出力線 500 を共有する形態を説明したが、この形態に限定されるものではなく、複数列の画素出力回路 101 が 1 つの共通出力線 500 を共有する形態であれば良い。

#### 【0038】

尚、駆動バイアス線 202、ランプ信号線 203、カウンタ信号線 302 についても、隣接する列で共有する構成によって同様の効果が得られる。一方、画素アレイ 100 の外に配置しているデジタルメモリ 600 についても、隣接する列で共有する構成でもよい。デジタルメモリ 600 の領域の面積を低減できる。

#### 【0039】

(実施例 3)

本実施例の撮像装置について、実施例 1 と異なる点を中心に説明する。

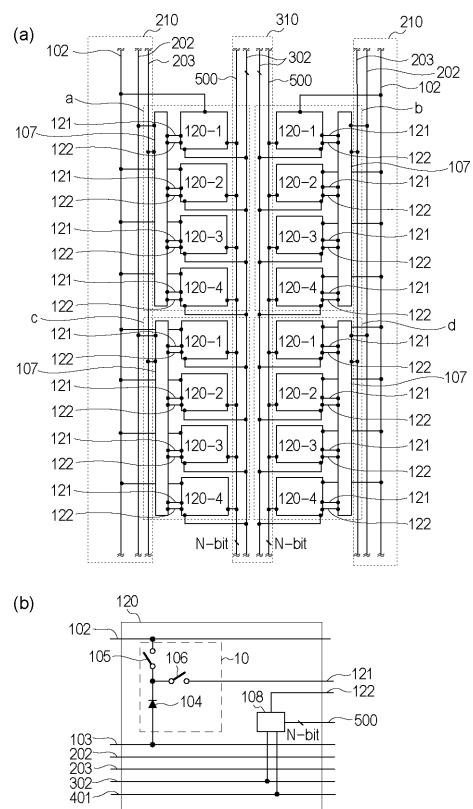

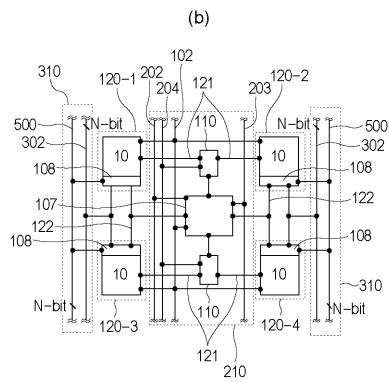

#### 【0040】

図 4 (a) は、本実施例の撮像装置の構成例を示す図である。図 1 (a) に示した撮像装置との違いは、図 4 (a) に示した撮像装置では、1 つの A/D 変換部 107 を 4 行の画素出力回路 120 で共有している点である。図 4 (a) で示した各ブロック a ~ d はそれぞれ、4 つの画素出力回路 120 と 1 つの A/D 変換部 107 を有している。図 4 (a) の撮像装置は、A/D 変換部 107 と画素出力回路 120 とを電気的に接続する、光電変換信号出力線 121 とラッチ信号線 122 とを有する。

#### 【0041】

図 4 (b) は、本実施例の画素出力回路 120 の構成例を示す図である。A/D 変換部 107 は実施例 1 と同様の構成とし、ラッチ部 109 から出力されるラッチ信号は、ラッチ信号線 122 を介して画素出力回路 120 に入力される。光電変換信号は、スイッチ 106 が導通すると、光電変換信号出力線 121 を介して A/D 変換部 107 へ入力される。

#### 【0042】

次に、図 5 (a)、図 5 (b) を用いて、本実施例の動作を説明する。

#### 【0043】

図 5 (a) は図 4 (a) に示した撮像装置の動作の一例である。図 5 (a) に示したリセット、蓄積、S/H、A/D 変換、読み出しの各期間は、図 2 (b) に示した各動作に対応している。

#### 【0044】

図 5 (b) は、静止画と動画のそれぞれの動作タイミングについて、1 つの A/D 変換部 107 を共有する、ブロック a の画素出力回路 120-1 ~ 120-4 の動作と、A/D 変換部 107 の動作と、を表した図である。図 5 (b) では、リセット、蓄積、S/H の期間を  $P_{i \times}$  として表している。同様に図 5 (b) では、A/D 変換の期間を  $A/D$ 、

10

20

30

40

50

読み出しの期間を *Read* として表している。

【0045】

静止画動作タイミングでは、本実施例の撮像装置は、すべての画素出力回路 120 の蓄積期間を同時とするグローバルシャッタ動作を行っている。図 5 (b) に示した動作では、蓄積期間を含む  $P_i \times$  期間の開始と終了とのそれを、画素出力回路 120-1 ~ 120-4 で同時としている。

【0046】

$P_i \times$  期間の後、A/D 変換部 107 は、画素出力回路 120-1 の光電変換信号の A/D 変換を行う。A/D 変換後の読み出し期間に、A/D 変換部 107 が生成した、画素出力回路 120-1 の光電変換信号に基づくデジタル信号が共通出力線 500 に出力される。また、画素出力回路 120-1 の光電変換信号に基づくデジタル信号の読み出し期間に、A/D 変換部 107 が画素出力回路 120-2 の光電変換信号の A/D 変換を行う。以降、同様に、K 行目の画素出力回路 120 の光電変換信号に基づくデジタル信号の読み出し期間に、A/D 変換部 107 が (K+1) 行目の画素出力回路 120 の光電変換信号の A/D 変換を行う。

10

【0047】

静止画動作タイミングでは、撮像装置はグローバルシャッタ動作を行っていたが、動画動作タイミングではローリングシャッタ動作としている。つまり、画素出力回路 120-1 の  $P_i \times$  期間が終了後に、画素出力回路 120-2 の  $P_i \times$  期間が開始される。また、動画動作タイミングでは、画素出力回路 120 のそれぞれに、読み出し期間後に、電気信号出力部 10 と画素内メモリ 108 が動作しない期間である *blank* 期間を設けている。そして、動画動作タイミングでは、*blank* 期間の後に、次のフレームの  $P_i \times$  期間を設けている。

20

【0048】

本実施例では、1 つの A/D 変換部 107 を 4 つの画素出力回路 120 で共有する。これにより、A/D 変換部 107 の面積を低減することができる。

【0049】

本実施例においても、実施例 1 と同様に、デジタル信号線群 310 とアナログ信号線群 210 とが電気信号出力部 10 を挟むように設けられている。これにより、実施例 1 と同様の効果を得ることができる。

30

【0050】

尚、本実施例では、1 つの A/D 変換部 107 を 4 つの画素出力回路 120 を共有していた。本実施例はこの形態に限定されるものではなく、1 つの A/D 変換部 107 を複数の画素出力回路 120 で共有する構成であれば適用できる。

【0051】

また、本実施例では、図 5 (c) に示した動画動作タイミングで、 $P_i \times$  期間が、A/D 変換期間、*Read* 期間と同じ長さであるとして説明した。本実施例はこの形態に限定されるものではなく、*Blank* 期間を短縮して、その分、 $P_i \times$  期間を長くするようにしても良い。

【0052】

40

(実施例 4)

本実施例の撮像装置について、実施例 1 と異なる点を中心に説明する。

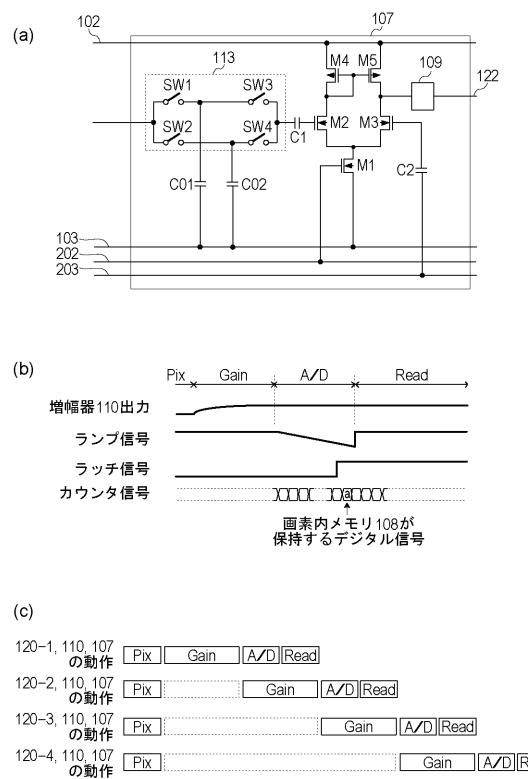

【0053】

図 6 (a) は、本実施例の画素出力回路 101 の構成例を示す図である。図 1 (a) に示した構成との違いは、図 6 (a) に示した画素出力回路 101 が増幅器 110 を有している点である。

【0054】

本実施例では、容量素子 111 が光電変換信号を保持する。そして、容量素子 111 の保持した光電変換信号が増幅器 110 に入力される。増幅器 110 は光電変換信号を増幅して生成した信号を、スイッチ 112 を介して A/D 変換部 107 に出力する。

50

## 【0055】

光電変換信号の信号値が、好適にA/D変換を行える信号範囲より小さい場合であることがある。本実施例の撮像装置では、このような場合であっても、増幅器110で光電変換信号を増幅することによって、A/D変換部107に出力される信号を、好適にA/D変換を行える信号範囲内とすることができます。

## 【0056】

本実施例においても、デジタル信号線群310とアナログ信号線群210の配置は実施例1と同様とすることができます。よって、実施例1と同様の効果を得ることができます。

## 【0057】

(実施例5)

10

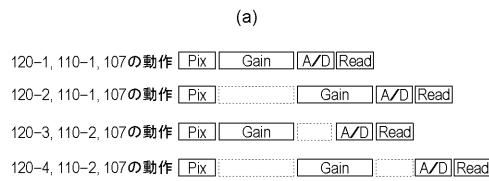

本実施例の撮像装置について、実施例3と異なる点を中心に説明する。

## 【0058】

図6(b)は、本実施例の撮像装置の構成例を示す図である。図6(b)に示した撮像装置では、増幅器110を、4つの画素出力回路120で共有している。増幅器110には、駆動バイアス線204から、増幅器110を駆動する駆動バイアスが供給される。本実施例の撮像装置では、駆動バイアス線204と、デジタル信号線群310とが、電気信号出力部10を挟むように設けられている。画素出力回路120の構成は、図4(b)に示したものと同様とすることができます。

## 【0059】

図7(a)は、本実施例におけるA/D変換部107の構成例である。図2(a)との違いは、図7(a)のA/D変換部107が、スイッチ群113と容量素子C01、C02を有している点である。スイッチ群113は、スイッチSW1～4を有する。増幅器110が出力する信号はスイッチSW1、SW2に与えられる。スイッチSW1が導通すると、容量素子C01が増幅器110の出力する信号を保持する。また、スイッチSW2が導通すると、容量素子C02が増幅器110の出力する信号を保持する。スイッチSW3が導通すると、容量素子C01が保持した信号が、容量素子C1を介してトランジスタM2の入力ノードに入力される。また、スイッチSW4が導通すると、容量素子C02が保持した信号が、容量素子C1を介してトランジスタM2の入力ノードに入力される。

20

## 【0060】

図7(b)は、図6(b)に示した撮像装置の、1つの画素出力回路120の動作を表した図である。図7(b)に示した、Pixel、A/D、Readの各期間は、図5(a)で述べた各期間と同様である。Gain期間は、増幅器110が、光電変換信号を増幅するとともに、スイッチ群113に信号を出力している期間である。

30

## 【0061】

図7(c)は、図6(b)に示した撮像装置における静止画動作のタイミング図である。本実施例では、増幅器110が光電変換信号を増幅する期間(以下、Gain期間)が、A/D変換期間とRead期間の期間を合わせた期間と同じとしている。

## 【0062】

本実施例の撮像装置は実施例3と同様、グローバルシャッタ動作を行っている。画素出力回路120-1～120-4のPixel期間の後、増幅器110が画素出力回路120-1の光電変換信号を増幅するGain期間が開始される。Gain期間では、スイッチ群113のうち、スイッチSW1が導通して、容量素子C01が増幅器110の出力する信号を保持する。画素出力回路120-1の光電変換信号を増幅した信号のA/D変換期間では、スイッチSW1が非導通となり、スイッチSW3が導通する。図7(c)のタイミング図では、撮像装置は、画素出力回路120-1の光電変換信号に基づく信号のA/D変換期間と、画素出力回路120-2の光電変換信号のGain期間とを重ねて動作する。画素出力回路120-2の光電変換信号を増幅するGain期間では、スイッチ群113のうちスイッチSW2が導通して、容量素子C02が増幅器110の出力する信号を保持する。画素出力回路120-2の光電変換信号を増幅した信号のA/D変換期間では、スイッチSW2が非導通となり、スイッチSW4が導通する。

40

50

## 【0063】

以降同様に、画素出力回路120-3、120-4の各々の光電変換信号についても、Gain期間とA/D変換期間とが重なるように動作する。これにより、複数の画素出力回路120の各々の光電変換信号に基づくデジタル信号を、増幅器110とA/D変換部107の動作期間を全く重ねない場合に比して短い期間で生成することができる。

## 【0064】

本実施例の撮像装置においても、図4(a)のように、電気信号出力部10を挟んで、デジタル信号線群310とアナログ信号線群210とが設けられている。これにより、実施例1と同様の効果を得ることができる。さらに、増幅器110を駆動する、第3の信号線である駆動バイアス線204を含むアナログ信号線群210と、デジタル信号線群310とが、電気信号出力部10を挟むように設けられている。これは、駆動バイアス線204をデジタル信号線群310に近接して配すると、デジタル信号線群310の電位の変動によって、駆動バイアス線204の電位も変動するためである。駆動バイアス線204の電位の変動は、増幅器110の増幅率の変動を生じさせる。増幅器110の増幅率が変動することによって、同じ信号値の光電変換信号を増幅したとしても、増幅器110の出力する信号の信号値が異なってしまう。よって、増幅器110の増幅率の変動を低減するため、増幅器110を駆動する駆動バイアス線204と、デジタル信号線群310とが、電気信号出力部10を挟むように設けられていることが好ましい。

## 【0065】

本実施例では、A/D変換部107がスイッチ群113と容量素子C01、C02を有している。これにより、画素出力回路120-1の光電変換信号を増幅した信号のA/D変換期間と、画素出力回路120-2の光電変換信号のGain期間とを重ねることができる。よって、複数の画素出力回路120の各々の光電変換信号を増幅した信号に基づくデジタル信号を生成する期間を、A/D変換部107がスイッチ群113を有さない形態に比して短縮することができる。

## 【0066】

本実施例では、1つの増幅器110を複数の画素出力回路120で共有する形態を説明した。これにより、各画素出力回路120が増幅器110を有する形態に比して、画素出力回路120と増幅器110を合わせた回路面積を減らすことができる。一方で、A/D変換部107では、図4(a)に示した形態に比して、スイッチ群113、容量素子C01、C02を設けている分、回路面積が増大している。従って、1つの増幅器110の回路面積が、スイッチ群113、容量素子C01、C02の回路面積よりも大きい場合には、複数の画素出力回路120で1つの増幅器110を共有することで、画素アレイの回路面積を減らすことができる。

## 【0067】

尚、本実施例では、増幅器110が、画素出力回路120のそれぞれの信号を増幅して、A/D変換部107に出力する動作を説明した。他の形態として、増幅器110の、光電変換信号が入力される入力部に加算機能を備え、複数の画素出力回路120の光電変換信号を加算した光電変換信号を増幅してA/D変換部107に出力する形態であっても良い。

## 【0068】

本実施例では、A/D変換期間とRead期間の合計期間が、Gain期間と同じである形態を説明したが、本実施例はこの形態に限定されない。例えば、A/D変換期間を短縮する場合には、デジタル信号のビット数を減らせば良い。また、画素出力回路からシリーズ形式でデジタル信号が出力される場合には、デジタル信号のビット数を減らすによって、Read期間を短縮することができる。

## 【0069】

本実施例ではこれまで、4つの画素出力回路120で1つの増幅器110を共有する形態を説明した。他の形態として、2つの画素出力回路120で1つの増幅器110を共有する形態について説明する。

10

20

30

40

50

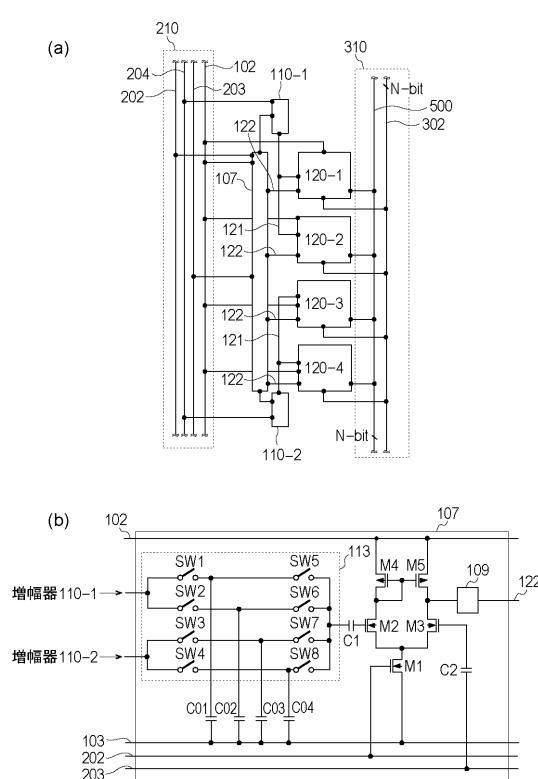

## 【0070】

図8(a)は、2つの画素出力回路120が増幅器110を共有する形態である。画素出力回路120-1、120-2は、増幅器110-1を共有している。画素出力回路120-3、120-4は、増幅器110-2を共有している。増幅器110-1、110-2はそれぞれ、画素出力回路120から出力される光電変換信号を増幅した信号を、A/D変換部107に出力する。増幅器110-1、110-2は共通の駆動バイアス線204から駆動バイアスが供給される。

## 【0071】

図8(b)は、図8(a)に示した撮像装置のA/D変換部107の構成例である。スイッチ群113は、スイッチSW1～SW8を有する。また、A/D変換部107は、容量素子C01～C04を有している。増幅器110-1が outputする信号は、スイッチSW1、SW2に入力される。不図示の制御部がスイッチSW1を導通させている場合には、容量素子C01が増幅器110-1の出力する信号を保持する。一方、不図示の制御部がスイッチSW2を導通させている場合には、容量素子C02が増幅器110-1の出力する信号を保持する。同様に、不図示の制御部がスイッチSW3、SW4をそれぞれ導通させると、容量素子C03、C04のそれぞれが増幅器110-2の出力する信号を保持する。

10

## 【0072】

不図示の制御部がスイッチSW1を非導通とし、スイッチSW5を導通させると、容量素子C01が保持した信号がスイッチSW5と容量素子C1を介して、トランジスタM2の入力ノードに出力される。他の容量素子C02～C04についても同様に、それぞれの容量素子C02～C04に対応するスイッチSW2～SW4が非導通となり、それぞれの容量素子C02～C04に対応するスイッチSW6～SW8を導通させる。これにより、それぞれの容量素子C02～C04が保持した信号が、それぞれの容量素子C02～C04から、容量素子C1を介してトランジスタM2に出力される。

20

## 【0073】

図9(a)は、図8(a)に示した撮像装置の動作を表した図である。画素出力回路120-1～120-4のPi期間は、画素出力回路120-1～120-4の間で開始と終了を同時としている。増幅器110-1は、画素出力回路120-1の光電変換信号を増幅した信号を、スイッチSW1を介して容量素子C01に出力する。増幅器110-2は、画素出力回路120-2の光電変換信号を増幅した信号を、スイッチSW3を介して容量素子C03に出力する。増幅器110-1のGain期間の開始と終了は、増幅器110-2のGain期間の開始と終了に対し、それぞれ同時としている。

30

## 【0074】

不図示の制御部は、スイッチSW1、SW3を非導通とし、スイッチSW5を導通させる。これによりA/D変換部107は、画素出力回路120-1の光電変換信号を増幅した信号のA/D変換を開始する。一方、増幅器110-1は画素出力回路120-2の光電変換信号を増幅した信号を、スイッチSW2を介して容量素子C02に出力する。また、増幅器110-2は、画素出力回路120-4の光電変換信号を増幅した信号を、スイッチSW4を介して容量素子C04に出力する。

40

## 【0075】

不図示の制御部は、画素出力回路120-1の光電変換信号を増幅した信号のA/D変換期間が終了すると、スイッチSW5を非導通とし、スイッチSW7を導通させる。これにより、A/D変換部107は、画素出力回路120-3の光電変換信号を増幅した信号のA/D変換を開始する。

## 【0076】

図8(a)に示した撮像装置では、増幅器110-1、110-2のGain期間を重ねることができる。一方、図6(b)に示した撮像装置では、画素出力回路120-1のGain期間が終了してから、画素出力回路120-2のGain期間を開始していた。よって、図8(a)に示した撮像装置では、複数の画素出力回路120の各々の光電変換

50

信号を増幅するのに要する期間を、図 6 ( b ) に示した撮像装置に比して短縮することができる。

【 0 0 7 7 】

また、図 8 ( a ) に示した撮像装置では、スイッチ SW 1 ~ SW 8 を有するスイッチ群 113 と、容量素子 C 0 1 ~ C 0 4 を A / D 変換部 107 が有する。これにより、同一の増幅器 110 に光電変換信号を順次出力する複数の画素出力回路 120 において、一方の画素出力回路 120 の光電変換信号に基づく信号の A / D 変換期間と、他方の画素出力回路 120 の光電変換信号の Gain 期間とを重ねることができる。これは、図 6 ( b ) に示した撮像装置と同様である。

【 0 0 7 8 】

図 8 ( a ) に示した撮像装置においても、アナログ信号線群 210 と、デジタル信号線群 310 とが、電気信号出力部 10 を挟んで設けられている。よって、実施例 1 と同様の効果を得ることができる。

【 0 0 7 9 】

( 実施例 6 )

本実施例の撮像装置について、実施例 5 と異なる点を中心に説明する。

【 0 0 8 0 】

図 9 ( b ) は、本実施例の撮像装置の構成例を示す図である。本実施例の撮像装置は、図 8 ( a ) に示した撮像装置と同様、2 行 2 列の 4 つの画素出力回路 120 で 2 つの増幅器 110 と、1 つの A / D 変換部 107 を共有する。図 8 ( a ) に示した撮像装置との違いは、A / D 変換部 107 と増幅器 110 を 2 行 2 列の 4 つの画素出力回路 120 で共有している点である。

【 0 0 8 1 】

2 行 2 列の 4 つの画素出力回路 120 で増幅器 110 、 A / D 変換部 107 を共有した場合の利点を述べる。デジタル信号線群 310 では、N - ビットのデジタル信号をパラレル形式で伝送するためには N 本の信号線を用いる。一方で、アナログ信号線群 210 の駆動バイアス線は、供給する電位の値ごとに 1 本の配線とすることができる。従って、デジタル信号線群 310 は、アナログ信号線群 210 に対して配線数が多くなる傾向にある。従って、図 4 ( a ) の撮像装置の場合、2 列の画素出力回路 120 に対応するデジタル信号線群 310 の幅が、2 列の画素出力回路 120 に対応するアナログ信号線群 210 の幅に対し、長くなる傾向にある。一方で、光学特性の観点から、画素出力回路 120 の列間隔は一定であることが好ましい。よって、2 列の画素出力回路 120 に対応するデジタル信号線群 310 の幅と、2 列の画素出力回路 120 に対応するアナログ信号線群 210 の幅と、の長さの差は、撮像装置の設計上の制約となることがある。

【 0 0 8 2 】

図 9 ( b ) の撮像装置では、駆動バイアス線 202 、 204 を含む信号線群と、ランプ信号線 203 との間に、増幅器 110 、 A / D 変換部 107 が設けられている。デジタル信号線群 310 に比して幅の短いアナログ信号線群 210 の領域内に、増幅器 110 、 A / D 変換部 107 が設けられている。これにより、デジタル信号線群 310 の幅と、増幅器 110 、 A / D 変換部 107 を含んだアナログ信号線群 210 の幅と、の長さの差が小さくなる。これにより、画素出力回路 120 の列間隔を一定にしやすくすることができる。

【 0 0 8 3 】

また、図 9 ( b ) の撮像装置では、隣り合う行の画素出力回路 120 同士で、画素内メモリ 108 が向き合うように配置されている。これにより、A / D 変換部 107 と、2 行の画素出力回路 120 の各々の画素内メモリ 108 とを電気的に接続するラッチ信号線 122 との配線長を、画素出力回路 120 - 3 のレイアウトを画素出力回路 120 - 1 と同じとした場合に比して短くすることができる。また、カウンタ信号線 302 と 2 行の画素出力回路 120 の各々の画素内メモリ 108 との電気的経路についても、画素出力回路 120 - 3 のレイアウトを画素出力回路 120 - 1 と同じとした場合に比して短くすること

10

20

30

40

50

ができる。よって、図9(b)の撮像装置は、画素出力回路120-3のレイアウトを画素出力回路120-1と同じとした場合に比して、2行2列の画素出力回路120の回路面積を縮小できる効果を有する。

【0084】

また、図9(b)の撮像装置では、駆動バイアス線202、204を含む信号線群と、第4の信号線であるランプ信号線203とが、増幅器110、A/D変換部107を挟んで設けられている。これにより、図9(b)の撮像装置は、ランプ信号線203の時間に依存して電位が変化しても、駆動バイアス線202の電位が変動しにくい効果を有する。

【0085】

また、図9(b)の撮像装置では、増幅器110の入力部に加算機能を持たせることにより、隣り合う2列の画素出力回路120の光電変換信号の加算を行うことができる。

【0086】

(実施例7)

図10は、実施例1～実施例6のいずれかの撮像装置を有する撮像システムである。

【0087】

図10において、撮像システムはレンズの保護のためのバリア151、被写体の光学像を撮像装置154に結像させるレンズ152、レンズ152を通った光量を可変にするための絞り153を有する。さらに撮像システムは、撮像装置154より出力される信号の処理を行う出力信号処理部155を有する。撮像装置154から出力される信号は、被写体を撮影した画像を生成するための撮像信号である。出力信号処理部155は撮像装置154から出力される撮像信号を必要に応じて各種の補正、圧縮を行って画像を生成する。レンズ152、絞り153は撮像装置154に光を集光する光学系である。

【0088】

図10に例示した撮像システムはさらに、画像データを一時的に記憶する為のバッファメモリ部156、外部コンピュータ等と通信する為の外部インターフェース部157を有する。さらに撮像システムは、撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体159、記録媒体159に記録または読み出しを行うための記録媒体制御インターフェース部158を有する。さらに撮像システムは、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部1510を有する。

【0089】

図10に示した撮像システムが有する撮像装置154は、実施例1～実施例6で述べた形態とすることができます。これにより、図10の撮像システムの撮像装置154においても、実施例1～実施例6で述べた効果を得ることができる。

【符号の説明】

【0090】

- 101 画素出力回路

- 150 駆動バイアス群

- 200 駆動バイアス回路

- 201 ランプ信号供給回路

- 210 アナログ信号線群

- 300 カウンタ群

- 301 カウンタ回路

- 310 デジタル信号線群

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 大屋 武

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 松永 隆志

(56)参考文献 特開2006-203736 (JP, A)

特開平6-232744 (JP, A)

特開2003-219274 (JP, A)

特開2003-115584 (JP, A)

国際公開第2011/091896 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H04N 5/374

H04N 5/357

H04N 5/378