(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7395285号**

**(P7395285)**

(45)発行日 令和5年12月11日(2023.12.11)

(24)登録日 令和5年12月1日(2023.12.1)

(51)国際特許分類

G 0 6 F 15/78 (2006.01)

G 0 6 F 21/70 (2013.01)

F I

G 0 6 F 15/78

G 0 6 F 21/70

G 0 6 F 15/78

5 1 8 F

21/70

5 1 7

請求項の数 19 外国語出願 (全34頁)

(21)出願番号 特願2019-156394(P2019-156394)

(22)出願日 令和1年8月29日(2019.8.29)

(65)公開番号 特開2020-77368(P2020-77368A)

(43)公開日 令和2年5月21日(2020.5.21)

審査請求日 令和4年8月29日(2022.8.29)

(31)優先権主張番号 62/724,581

(32)優先日 平成30年8月29日(2018.8.29)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 16/293,543

(32)優先日 平成31年3月5日(2019.3.5)

(33)優先権主張国・地域又は機関

米国(US)

|          |                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------|

| (73)特許権者 | 517023736<br>ヴァレックス イメージング コーポレーション<br>アメリカ合衆国 ユタ州 84104-4205 ソルト レイク シティ サウス<br>バイオニア ロード 1678 |

| (74)代理人  | 110000877<br>弁理士法人 R Y U K A 国際特許事務所                                                            |

| (72)発明者  | マイケル ルドルフ メイラー<br>アメリカ合衆国 ユタ州 84104-ソルトレイクシティー サウス バイオニア<br>ロード 1678                            |

| (72)発明者  | インター ジン<br>アメリカ合衆国 ユタ州 84104-ソルトレイクシティー サウス バイオニア<br>最終頁に続く                                     |

(54)【発明の名称】 耐タンパ回路

**(57)【特許請求の範囲】****【請求項1】**

デバイスであって、

前記デバイスを外部コンポーネントに実装するように構成された実装構造と、

第1の回路と、

前記第1の回路に電気的に接続された耐タンパ回路であって、前記デバイスが前記外部コンポーネントから取り外されたときに前記第1の回路の少なくとも1つの機能を無効にするように構成され、これにより、前記デバイスがリセットされるまで、前記デバイスを前記外部コンポーネントに再実装したときに前記第1の回路の前記少なくとも1つの機能を再び有効にしない、前記耐タンパ回路と、

を含み、

前記第1の回路は前記外部コンポーネントを制御するように構成されている、デバイス。

**【請求項2】**

前記第1の回路の前記少なくとも1つの機能には、前記外部コンポーネントを制御する前記第1の回路の機能が含まれる、請求項1に記載のデバイス。

**【請求項3】**

前記実装構造に結合されたハウジングをさらに含み、

前記ハウジングは、前記デバイスが前記外部コンポーネントに実装されたときに前記耐タンパ回路を作動解除するアクセスを制限するように構成されている、請求項1または2に記載のデバイス。

**【請求項 4】**

前記耐タンパ回路は、

前記実装構造に結合されたスイッチであって、前記デバイスが前記外部コンポーネントから取り外されたときに切り替わるように構成された前記スイッチを含む、請求項 1 から 3 のいずれか一項に記載のデバイス。

**【請求項 5】**

前記スイッチは、前記外部コンポーネント上に実装されたときに前記外部コンポーネントの構造によって切り替えられるように構成されている、請求項 4 に記載のデバイス。

**【請求項 6】**

前記耐タンパ回路は、

前記デバイス内に配置された電源であって、前記デバイスが前記外部コンポーネントから取り外されたことを検出した後に電力を供給するように構成された前記電源と、

前記第 1 の回路の前記少なくとも 1 つの機能を無効にするように構成された無効化回路と、を含み、

前記スイッチは、前記デバイスが前記外部コンポーネントから取り外されたときに前記電源を前記無効化回路に電気的に接続するように構成されている、請求項 4 または 5 に記載のデバイス。

**【請求項 7】**

前記第 1 の回路はプロセッサを含み、

前記耐タンパ回路は、前記デバイスが前記外部コンポーネントから取り外されたときに、前記プロセッサが用いるメモリの少なくとも一部を消去するように構成されている、請求項 1 から 6 のいずれか一項に記載のデバイス。

**【請求項 8】**

前記プロセッサが用いる前記メモリの少なくとも一部は、前記プロセッサと一体化されたメモリを含む、請求項 7 に記載のデバイス。

**【請求項 9】**

前記プロセッサが用いる前記メモリの少なくとも一部は暗号情報を記憶する、請求項 7 または 8 に記載のデバイス。

**【請求項 10】**

前記デバイスは、×線システムに付随するエレクトロニクスの一部であり、

前記外部コンポーネントは前記×線システムの×線管である、請求項 1 から 9 のいずれか一項に記載のデバイス。

**【請求項 11】**

前記デバイスは、×線システムに付隨するコンポーネント認証システムの一部である、請求項 1 から 10 のいずれか一項に記載のデバイス。

**【請求項 12】**

方法であつて、

デバイスによって、前記デバイスが前記デバイスの外部のコンポーネントから取り外されたことを検出することと、

前記デバイスが前記コンポーネントから取り外されたことを検出したことに応じて、前記デバイスの回路の少なくとも 1 つの機能を無効にし、これにより、前記デバイスがリセットされるまで、前記デバイスを前記コンポーネントに再実装したときに前記回路の前記少なくとも 1 つの機能を再び有効にしないことと、を含み、

前記デバイスの前記回路の前記少なくとも 1 つの機能は、前記デバイスの外部の前記コンポーネントを制御する機能を含む、方法。

**【請求項 13】**

前記デバイスによって、前記デバイスが前記コンポーネントから取り外されたことを検出することは、前記デバイスの構造と前記デバイスの外部の前記コンポーネントの構造との物理的分離を検出することを含む、請求項 12 に記載の方法。

**【請求項 14】**

10

20

30

40

50

前記デバイスの前記回路の少なくとも1つの機能を無効にすることは、

内部電源から無効化回路に電力供給することと、

前記無効化回路を用いて前記デバイスの前記回路の前記少なくとも1つの機能を無効に

することと、を含む、請求項13に記載の方法。

**【請求項15】**

前記デバイスによって、前記デバイスが前記コンポーネントから取り外されたことを検出することは、前記デバイスの構造と前記デバイスの外部の前記コンポーネントの構造との物理的分離を検出することを含む、請求項12から14のいずれか一項に記載の方法。

**【請求項16】**

前記デバイスを前記コンポーネント上に取り付けることと、

前記デバイスを前記コンポーネントに取り付けた後に、前記デバイスの前記回路の少な

くとも1つの機能を無効にするように構成された耐タンパ回路を作動状態にすることと、

をさらに含む、請求項12から15のいずれか一項に記載の方法。

**【請求項17】**

前記デバイスをリセットすることをさらに含み、前記デバイスが前記コンポーネントから取り外されたことを検出する段階の後、前記デバイスの前記回路の少なくとも1つの機能は、前記デバイスを前記コンポーネントに取り付けた後、前記デバイスがリセットされ

るまで無効にされたままである、請求項16に記載の方法。

**【請求項18】**

デバイスであって、

デバイスによって、前記デバイスが前記デバイスの外部のコンポーネントから取り外さ

れたことを検出するための手段と、

前記手段が、前記デバイスが前記コンポーネントから前記取り外されたことを検出した

ことに応じて、前記デバイスの回路の少なくとも1つの機能を無効にし、これにより、前

記デバイスがリセットされるまで、前記デバイスを前記コンポーネントに再実装したとき

に前記回路の前記少なくとも1つの機能を再び有効にしないための手段と、を含み、

前記デバイスの前記回路の前記少なくとも1つの機能は、前記デバイスの外部の前記コン

ポーネントを制御する機能を含む、デバイス。

**【請求項19】**

前記デバイスの前記コンポーネントからの物理的分離を検出するための手段と、

前記手段が前記デバイスの前記コンポーネントからの物理的分離を検出したことに応じ

て、前記回路のメモリの少なくとも一部を消去するための手段と、をさらに含む、請求項

18に記載のデバイス。

**【発明の詳細な説明】**

**【背景技術】**

**【0001】**

システムは種々の異なるデバイスから形成され得る。製造業者、システムインテグレータなどは、認定コンポーネントを用いた特定のシステムをデザインして取り付ける場合がある。しかし、サードパーティー供給業者が、同様のシステム上のデバイスと交換したり、使用済みコンポーネントまたはサードパーティー製コンポーネントを取り付けたりする

ことがあり、その結果、性能問題が生じ及び／またはシステムのコンポーネントが損傷す

る場合がある。

**【図面の簡単な説明】**

**【0002】**

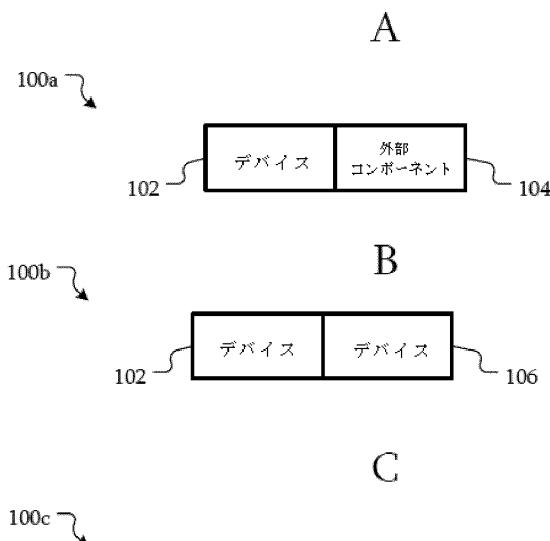

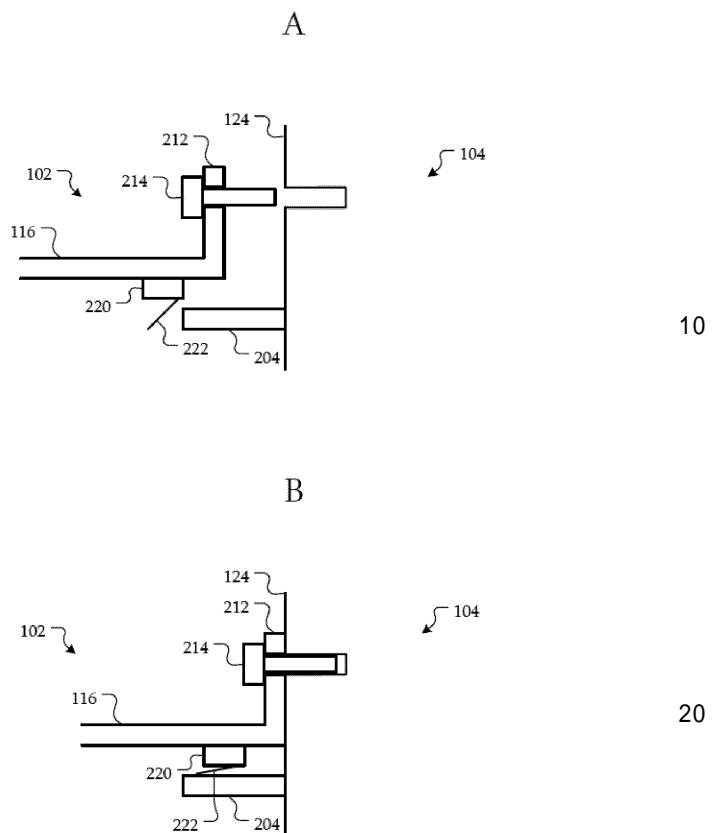

【図1】図1A～図1Cは、いくつかの実施形態により耐タンパ回路を伴うデバイスを含

むシステムのブロック図である。

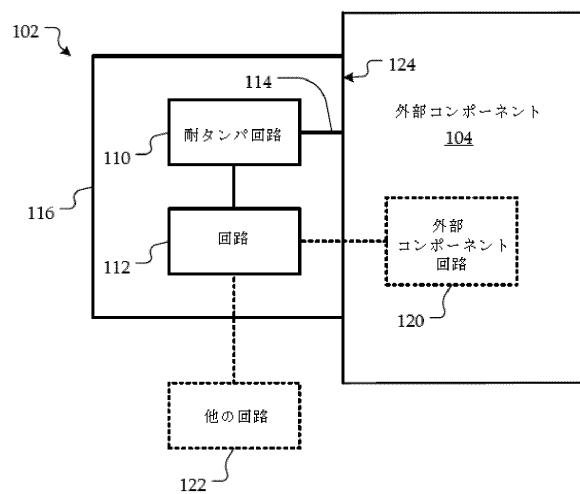

【図2】いくつかの実施形態による耐タンパ回路を伴うデバイスのブロック図である。

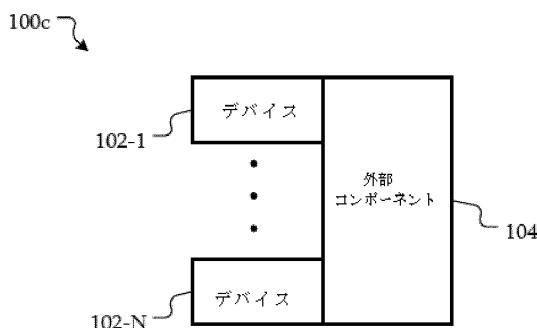

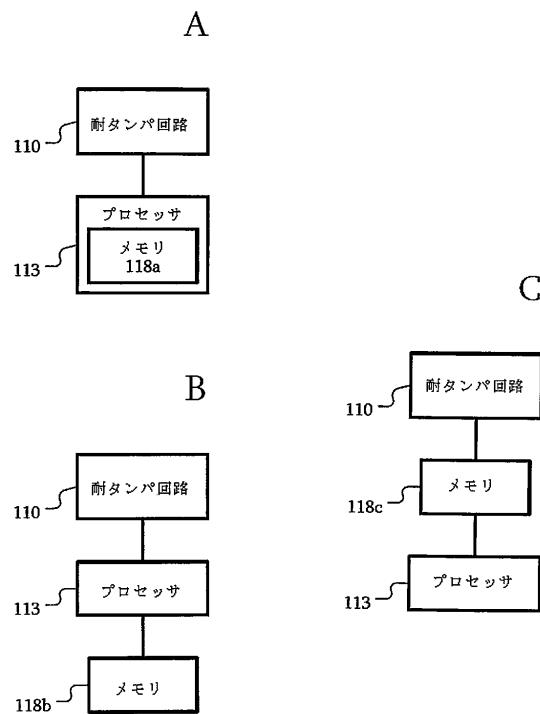

【図3】図3A～図3Cは、いくつかの実施形態による耐タンパ回路を伴うデバイスの回

路のブロック図である。

【図4】図4A～図4Bは、いくつかの実施形態により耐タンパ回路を伴うデバイスを外

10

20

30

40

50

部コンポーネント上に実装することを例示する断面図である。

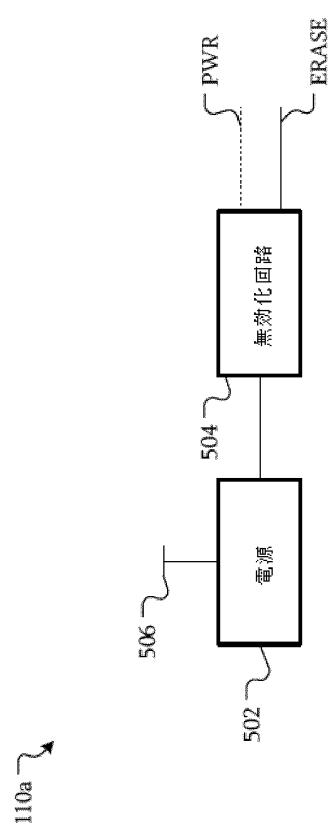

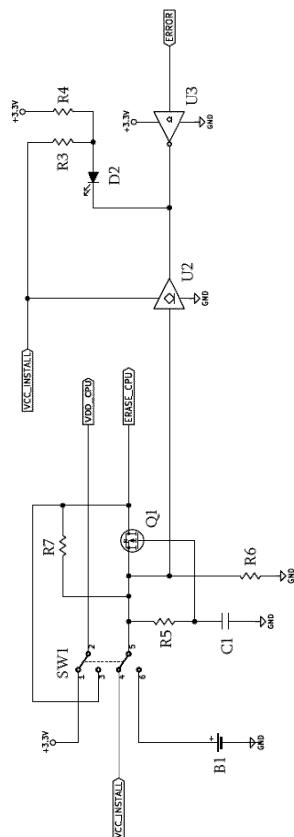

【図 5 A】いくつかの実施形態による耐タンパ回路の概略回路図である。

【図 5 B】いくつかの実施形態による耐タンパ回路の概略回路図である。

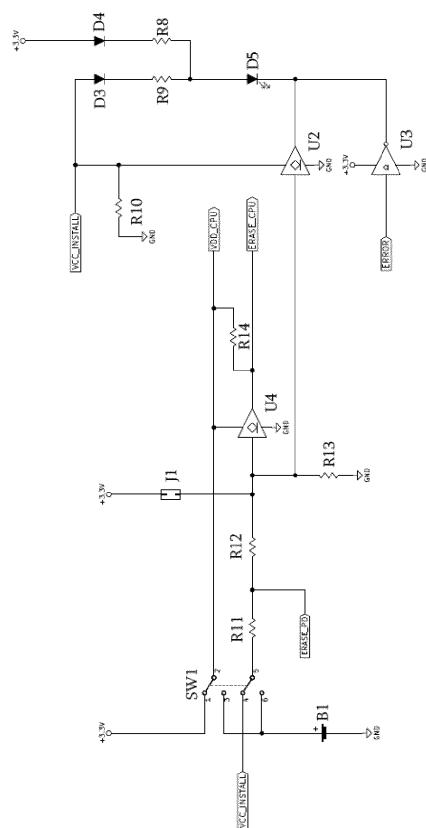

【図 5 C】いくつかの実施形態による耐タンパ回路の概略回路図である。

【図 5 D】いくつかの実施形態による耐タンパ回路の概略回路図である。

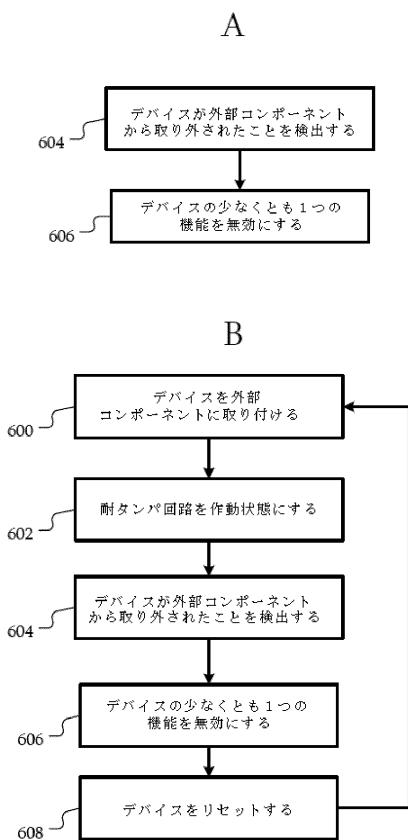

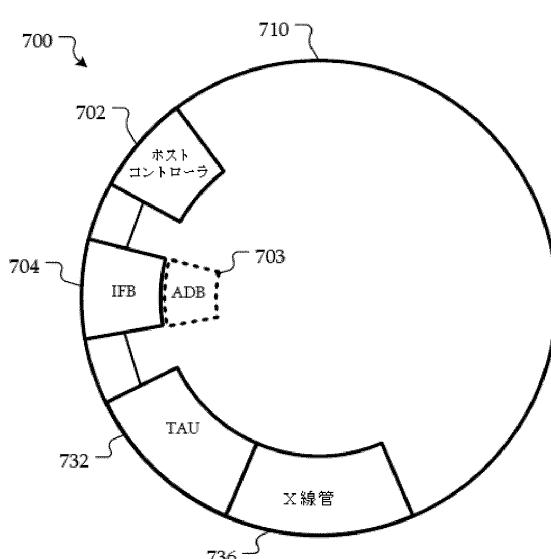

【図 6】図 6 A ~ 図 6 B は、いくつかの実施形態により耐タンパ回路を伴うデバイスを動作させる技術を示すフローチャートである。

【図 7】いくつかの実施形態による x 線システムのブロック図である。

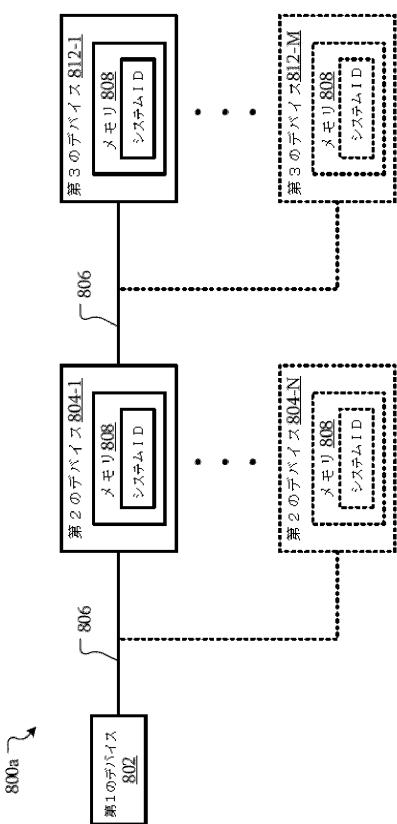

【図 8 A】いくつかの実施形態による認証システムを含むシステムのブロック図である。

10

【図 8 B】いくつかの実施形態による認証システムを含むシステムのブロック図である。

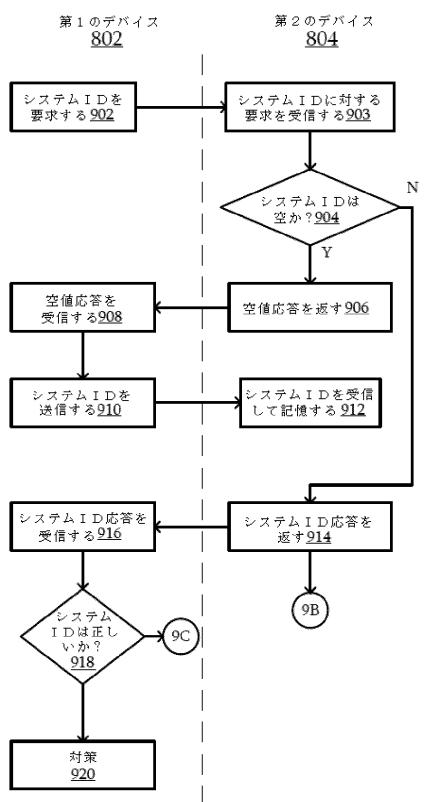

【図 9 A】いくつかの実施形態により認証システムを動作させる技術の例を示すフローチャートである。

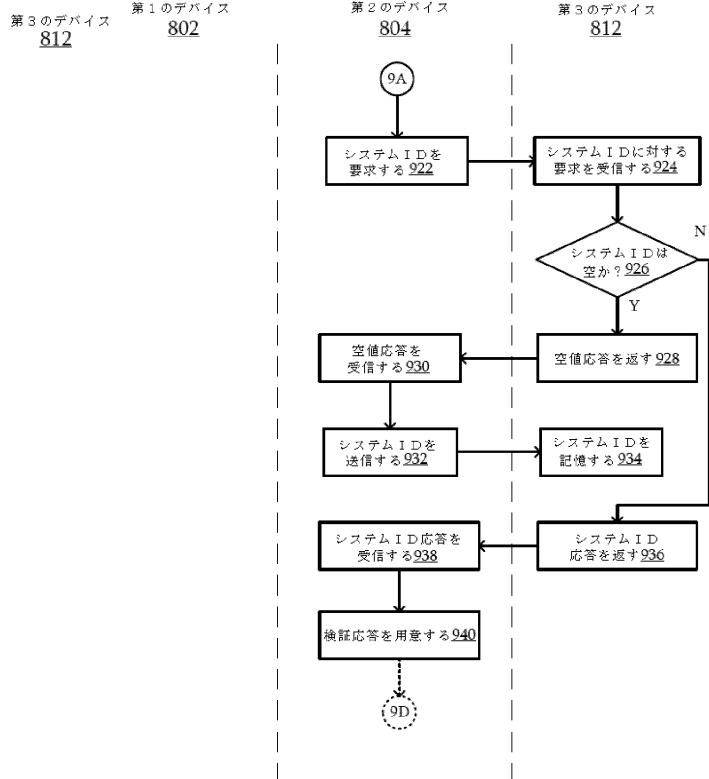

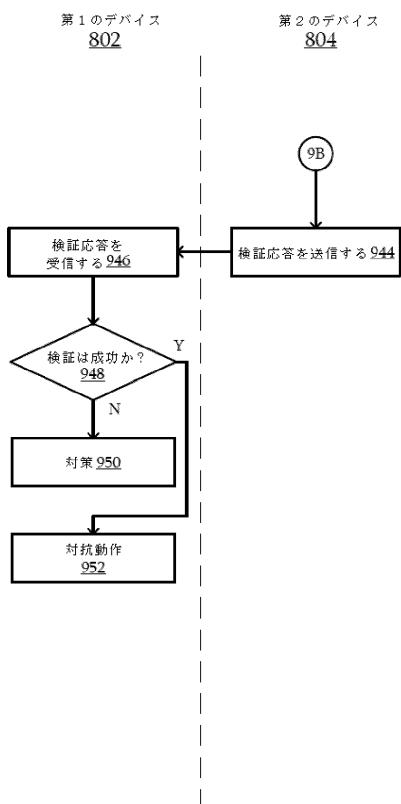

【図 9 B】いくつかの実施形態により認証システムを動作させる技術の例を示すフローチャートである。

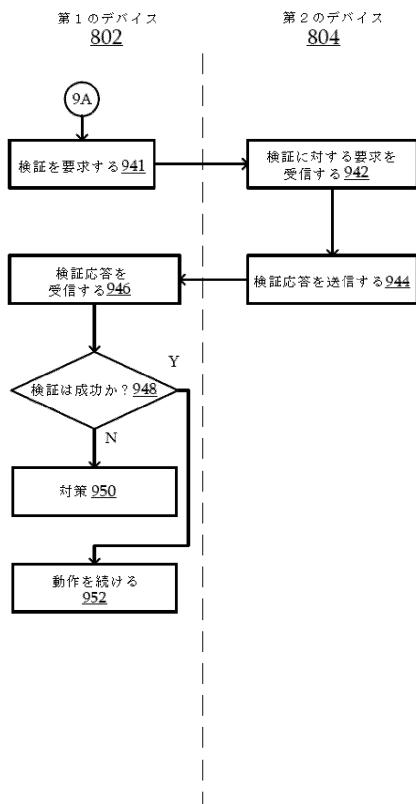

【図 9 C】いくつかの実施形態により認証システムを動作させる技術の例を示すフローチャートである。

【図 9 D】いくつかの実施形態により認証システムを動作させる技術の例を示すフローチャートである。

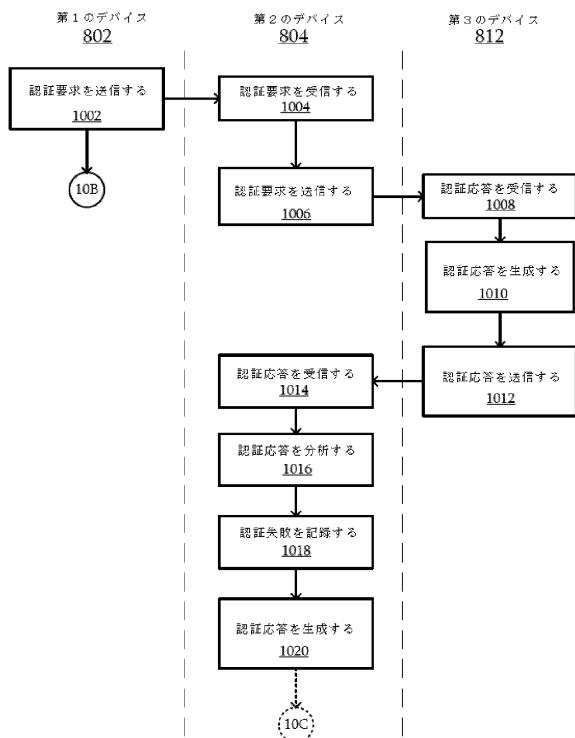

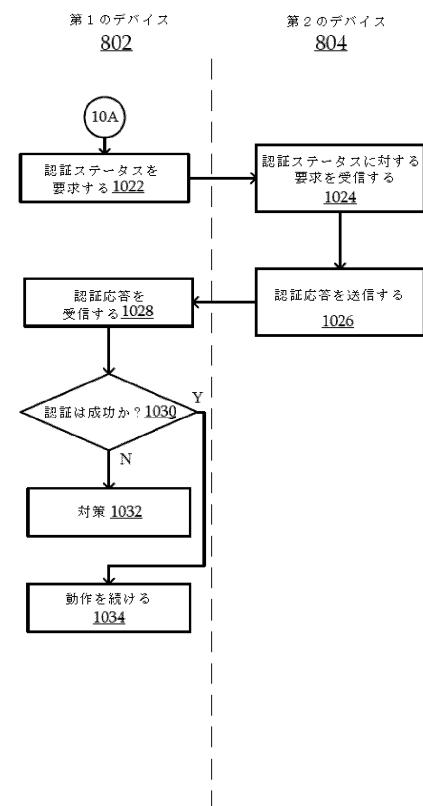

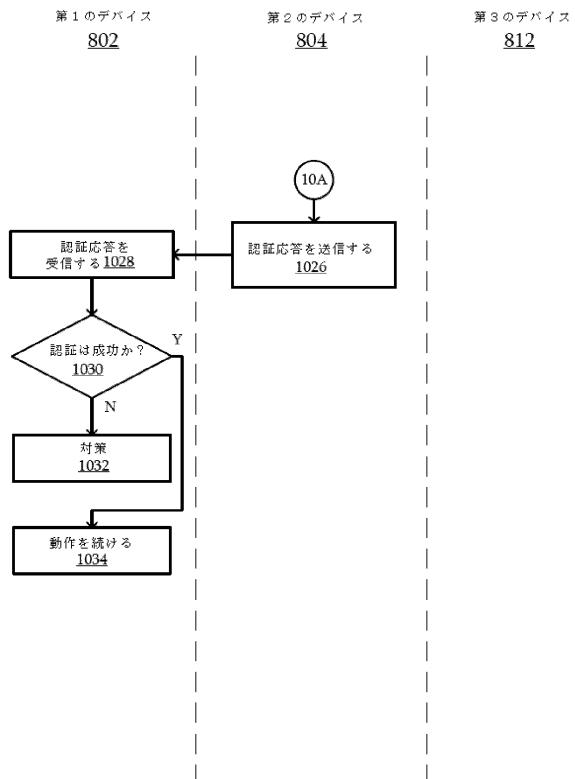

【図 10 A】いくつかの実施形態により認証システムを動作させる技術の例を示すフローチャートである。

20

【図 10 B】いくつかの実施形態により認証システムを動作させる技術の例を示すフローチャートである。

【図 10 C】いくつかの実施形態により認証システムを動作させる技術の例を示すフローチャートである。

#### 【発明を実施するための形態】

##### 【0003】

本発明の任意の実施形態について詳細に説明する前に、本発明は適用の際に、以下の説明で述べるかまたは以下の図面で例示する構成の詳細及びコンポーネントの配置に限定されないことを理解されたい。本発明は、他の実施形態が可能であり、また種々の仕方で実施または実行することが可能である。フローチャート及びプロセスに示した数は、ステップ及び動作を説明する際に明瞭にするために与えており、必ずしも特定の順番またはシーケンスを示すものではない。別に定義がない限り、用語「or」は、代替案の選択（たとえば、論理和演算子、または排他的 or）または代替案の組み合わせ（たとえば、結合演算子、及び / または、論理的 or、またはプール OR）を指すことができる。

30

##### 【0004】

いくつかの実施形態は全般的に、コンポーネントから取り外されたときにコンポーネント認証システムを無効にするメカニズム、方法、及びシステムに関する。いくつかの実施形態は全般的に、スイッチ及び無効化コンポーネント及び / または回路に関する。

##### 【0005】

コンピュータ断層撮影 (CT) 及び x 線システムなどのシステムでサードパーティー製コンポーネントが使用されることを阻止しようとして、電子デバイスが用いられる場合がある。しかし、このような電子デバイスは、x 線管などの古いコンポーネント、損傷したコンポーネント、磨耗したコンポーネントを含むシステムから取り外される場合がある。次に電子デバイスがサードパーティー製管または使用済み管に取り付けられて、相手先ブランド製造者 (OEM) システムで用いるように販売される場合がある。たとえば、サードパーティーは、電子デバイスを取り外すことができる古い x 線管、使用済み x 線管、または損傷した x 線管にアクセスする場合がある。そして電子デバイスを新しい管、使用済み管、またはサードパーティー製管に取り付けて、管がシステム内で純正管を装うことができるようになることができる。

40

##### 【0006】

50

本明細書で説明するように、耐タンパ回路はコンポーネントまたは電子デバイス自体の取り外しは阻止し得ないが、デバイスの機能の少なくとも一部から全部を無効にし得る（たとえば、認証または他の機能を無効にすること、構成情報を削除することなど）。その結果、製造業者または認定されたサービス担当者にデバイスを再プログラムしてもらわない限り、電子デバイスはこれらの機能を実行し得ない。したがって、認定されていないパーティは、もはや電子デバイスを再使用すること及び機能の一部から全部にアクセスすることはでき得ない。後により詳細に説明するように、機能の一部から全部を失う効果は、警告メッセージが出ることから電子デバイスまたは電子デバイスを含むシステムが無効になることまでの様々な効果につながり得る。

#### 【0007】

いくつかの実施形態では、X線システムにおいて、製造業者がデザイン及び作製したX線管には、画像化が適切で管に損傷を与えることなく機能するために管補助ユニット（TAU）とともに用いるべき管特定情報が含まれていてもよい。その管特定情報は、TAUの不揮発性ランダムアクセスメモリ（NVRAM）（たとえば、フラッシュメモリまたは固体記憶装置）内にあってもよい。TAUに記憶された情報の一部は管に固有であるため、そのTAUを異なる管に交換するつもりであったとしたら、その管特定情報はもはやその特定のX線管には一致しない。不一致によって、画質の問題が生じ、及び／または使用されていれば修理不可能なX線管損傷が生じる可能性がある。耐タンパ回路によって、異なるX線管の間でTAUが交換されてシステムに間違った管特定情報が与えられる可能性が低減または排除され得る。

10

#### 【0008】

図1A～図1Cは、いくつかの実施形態による耐タンパ回路を伴うデバイスを含むシステムのブロック図である。図2は、いくつかの実施形態による耐タンパ回路を伴うデバイスのブロック図である。

20

#### 【0009】

図1A及び図2を参照すると、システム100aには、外部コンポーネント104上に実装されるように構成されたデバイス102が含まれる。デバイス102には耐タンパ回路110及び回路112が含まれる。

#### 【0010】

デバイス102の例としては、カスタマイズされたコンポーネント、ファームウェア、ソフトウェア、データなどが含まれ得る回路112を伴うデバイスが挙げられる。ファームウェアまたはソフトウェアには、外部コンポーネント104の他の回路122または回路120との独自の通信及び／または制御技術を実施する命令が含まれていてもよい。他の実施形態では、データには認証情報、暗号情報、性能データなどが含まれていてもよい。デバイス102の特定の例としては、システムに対する認証回路、X線管に対する制御回路などが挙げられる。

30

#### 【0011】

外部コンポーネント104には、純粋な構造コンポーネント及び／またはいくつかの機能を伴う回路が含まれていてもよい。たとえば、いくつかの実施形態では、外部コンポーネント104は、デバイス102を含むシステムのハウジングである。デバイス102を、そのハウジングに実装してもよく、したがって外部コンポーネント104に実装してもよい。

40

#### 【0012】

デバイス102には、デバイス102が外部コンポーネント104に実装されたときに耐タンパ回路110を作動解除するアクセスを制限するように構成されたハウジング116が含まれている。たとえば、ハウジング116には、耐タンパ回路110及び回路112を囲むシールされたケースが含まれていてもよい。ハウジング116が外部コンポーネント104に実装されると、ハウジング116及び外部コンポーネント104（たとえば、外部コンポーネント104の壁124）の組み合わせによって、耐タンパ回路110及び回路112が完全に囲まれ得る。いくつかの実施形態では、組み合わせによって耐タン

50

パ回路 110 及び回路 112 を十分に囲んで、ハウジング 116 を著しく変更または破壊することなく耐タンパ回路 110 または回路 112 にアクセスすることを防止してもよい。耐タンパ回路 110 または回路 112 にアクセスすることが、デバイス 102 が外部コンポーネント 104 から取り外されたことよりはるかに難しくなるように、ハウジング 116 及び外部コンポーネント 104 の組み合わせを構成してもよい。

#### 【0013】

デバイス 102 には、回路 112 に電気的に接続された耐タンパ回路 110 が含まれる。耐タンパ回路 110 は、デバイス 102 が外部コンポーネント 104 から取り外されたときに、回路 112 の少なくとも 1 つの機能を無効にするように構成されている。詳細には、耐タンパ回路 110 はカップリング 114 を通して外部コンポーネント 104 に結合されている。このカップリング 114 は、機械的、電気的、光学的、磁気的、他の同様のカップリング、またはこのようなカップリングの組み合わせであってもよい。たとえば、デバイス 102 が外部コンポーネント 104 に実装されたときにスイッチを切り替えてよい。切り替えるということは、オン状態からオフ状態へトグルすることまたはオフ状態からオン状態へトグルすることを指すことができる。スイッチは機械的または磁気的に切り替え可能なポールを有していてもよい。スイッチの状態は、デバイス 102 が外部コンポーネント 104 に実装されているか否かまたは外部コンポーネントから取り外されているか否かに応じて変化してもよい。他の実施形態では、スイッチは、デバイス 102 を外部コンポーネントに実装するために用いる留め具が取り外されたときに状態を変えてよい。他の実施形態では、外部コンポーネント 104 の一部を通して、たとえば壁 124 の金属部分を通して電気回路を形成してもよい。デバイス 102 が外部コンポーネントから取り外されたことを、その回路における断線によって検出してもよい。デバイス 102 が外部コンポーネント 104 から取り外されたことを、耐タンパ回路 110 が検知し得る構成の例として、いくつかの回路及び構造を用いてきたが、耐タンパ回路 110 は取り外しを他の方法で検知してもよい。

#### 【0014】

本明細書で説明する実施形態は、デバイス 102 が、システム 100a、外部コンポーネント回路 120、他の回路 122、またはそれらが実装された及び／もしくは付随する別のコンポーネントまたはデバイスと物理的に対のままでいなければならないどんな場合で用いてよい。この意味において、対でいるとは、デバイスに物理的に接触し、近接し、連絡し、組み込まれる等を意味することができる。

#### 【0015】

耐タンパ回路 110 が外部コンポーネント 104 から取り外されたことが検知されたことに応じて、回路 112 の少なくとも 1 つの機能を無効にするように耐タンパ回路 110 を構成してもよい。回路 112 の特定の機能としては、汎用処理の能力、特定のデータを用いること、認証要求に適切に応答できることなどを挙げてもよい。いくつかの実施形態では、回路 112 に記憶されたデータを消去してもよい。データには、暗号情報、認証情報、識別情報、動作情報、ファームウェア、ソフトウェアなどが含まれていてもよい。いくつかの実施形態では、回路 112 の不揮発性メモリを消去して、少なくとも 1 つの機能を無効にしてもよい。他の実施形態では、回路 112 の動作に影響するヒューズを溶断して、少なくとも 1 つの機能を無効にしてもよい。いくつかの実施形態では少なくとも 1 つの機能を無効にし得るが、他の実施形態では、耐タンパ回路 110 を回路 112 またはデバイス全体 102 のすべての機能を無効にするように構成してもよい。

#### 【0016】

いくつかの実施形態では、回路 112 は外部コンポーネントを制御するように構成されている。回路 112 を外部コンポーネント回路 120 に結合してもよい。特定の例では、回路 112 には X 線管に対する制御回路が含まれていてもよい。外部コンポーネント回路 120 としては、アノード、カソード、フィラメント、放射体、モータ、ステアリングエレクトロニクス、フォーカシングエレクトロニクス、または X 線管の一部であり得る他の回路を挙げてもよい。

10

20

30

40

50

**【 0 0 1 7 】**

いくつかの実施形態では、再使用を阻止するための他の技術を、無線周波数識別センサ（R F I D）、光センサ、近接センサ、バーコードリーダ、管シリアル番号もしくは他の識別特徴を処理するカメラ、トリップワイヤ、耐タンパ実装、またはこのような技術の任意の組み合わせによってトリガることができる。これらの技術は、本明細書で説明したように耐タンパ回路 110 が回路 112 の少なくとも 1 つの機能を無効にできることと対にことができる。

**【 0 0 1 8 】**

図 1 B 及び図 2 を参照すると、いくつかの実施形態では、外部コンポーネント 104 は別のデバイス 106 であってもよい。たとえば、デバイス 106 は、システム制御コンポーネントとシステムの他のコンポーネントとの間のインターフェースをもたらすように構成されたインターフェース回路基板であってもよい。特定の例では、デバイス 106 は、 $\times$  線システムに対するシステム制御装置と特定のサブシステム（たとえば、 $\times$  線発生サブシステム、電力サブシステム、検出器サブシステム、冷却サブシステム、ユーザインターフェースサブシステムなど）との間の制御及び / または通信を変換するインターフェース基板であってもよい。

10

**【 0 0 1 9 】**

デバイス 102 は、認証情報を記憶し、認証機能を実行し、システム制御装置とシステム 100 b のデバイス 106 または他のサブシステムなどとの間の認証をネゴシエートするように構成された認証ドーターボード（A D B）であってもよい。

20

**【 0 0 2 0 】**

図 1 C を参照すると、いくつかの実施形態では、2 つ以上のデバイス 102 を外部コンポーネント 104 に実装してもよい。この例では、N 個のデバイス 102 が外部コンポーネント 104 に実装されている。デバイス 102 - 1 ~ 102 - N は同じであっても、類似であっても、または異なっていてもよい。しかし、デバイス 102 - 1 ~ 102 - N の一部から全部には、本明細書で説明する耐タンパ回路 110 が含まれていてもよい。

**【 0 0 2 1 】**

いくつかの実施形態では、耐タンパ回路 110 によって、サードパーティによるかまたはサードパーティ製コンポーネント上のデバイス 102 の再使用、変更、不正変更、交換、または再取付けが阻止される。前述したように、デバイス 102 は認証システムの一部であってもよい。認証システムは、システム内のコンポーネント（デバイス 102、外部コンポーネント 104、または別のコンポーネントであってもよい）が、暗号化された課題質問をコンポーネント上の暗号電子デバイスに出すことによって、純正の製造業者コンポーネントまたは O E M コンポーネントであるか否かを判定するように構成してもよい。

30

**【 0 0 2 2 】**

特定の例では、デバイス 102 には暗号電子デバイスが回路 112 の一部として含まれていてもよい。デバイス 102 には外部コンポーネント 104 を制御する回路が含まれる。暗号電子デバイスを純正コンポーネントから取り外して偽造コンポーネント上に取り付けることができるならば、認証システムの意図を無視することができる。しかし、デバイス 102 が取り外されると耐タンパ回路 110 はトリガされる。無効にされる回路 112 の少なくとも 1 つの機能としては認証機能、認証情報などを挙げてもよい。耐タンパ回路 110 がトリガされた後は、暗号電子デバイスはもはや認証要求に適切に応答することはない。その結果、システム 100 には、デバイス 102 及び / または外部コンポーネント 104 はもはや純正の製造業者または O E M コンポーネントであると信頼することはできないという表示が出る。

40

**【 0 0 2 3 】**

いくつかの実施形態では、O E M にとってサービス契約は大きな収入源となり得る。本明細書で説明する耐タンパ回路 110 を O E M が用いて、サードパーティ製造業者または再販業者が競合品もしくは代替品、または非互換コンポーネントが取り付けられること

50

(性能及び患者の安全性の問題につながり得る)を低減させるまたは無くすことができる。

#### 【0024】

図3A～図3Cは、いくつかの実施形態による耐タンパ回路を伴うデバイスの回路のブロック図である。これらの実施形態では、回路には、耐タンパ回路110(前述したものと同様である)、プロセッサ113、及びメモリ118が含まれる。プロセッサ113及びメモリ118は、前述した回路112の例である。

#### 【0025】

プロセッサ113は、汎用プロセッサ、デジタルシグナルプロセッサ(DSP)、特定用途向け集積回路、マイクロコントローラ、プログラマブルロジックデバイス、ディスクリート回路、このようなデバイスの組み合わせなどであってもよい。プロセッサ113には、レジスタ、キャッシュメモリ、揮発性メモリ、不揮発性メモリ、処理コアなどの内部部分が含まれていてもよく、またアドレス及びデータバスインターフェース、割込みインターフェースなどの外部インターフェースが含まれていてもよい。1つのプロセッサ113のみを例示しているが、複数のプロセッサ113が存在してもよい。加えて、プロセッサ113を内部及び外部コンポーネントに接続するために、ロジックチップセット、ハブ、メモリコントローラ、通信インターフェースなどの他のインターフェースデバイスを含めてよい。

10

#### 【0026】

プロセッサ113はメモリ118に結合されている。メモリ118には、前述したように、暗号情報、認証情報、識別情報、動作情報、ファームウェア、ソフトウェアなどのデータが含まれる。耐タンパ回路110は、デバイス102が外部コンポーネント104から取り外されたときに、プロセッサ113が用いるメモリ118の少なくとも一部を消去する構成されている。いくつかの実施形態では、消去はこのようなデータのすべてであってもよい。他の実施形態では、消去はデバイス102を動作不能にする十分な量及び質のデータであってもよい(たとえば暗号キーなどの秘密情報の消去)。

20

#### 【0027】

図3Aを参照すると、いくつかの実施形態では、プロセッサ113にはオンチップそうでなければ集積メモリ118aが含まれる。その結果、耐タンパ回路110がメモリ118aの少なくとも一部を消去したとき、消去されたメモリはプロセッサ113と一体化されたメモリである。

30

#### 【0028】

図3Bを参照すると、いくつかの実施形態では、耐タンパ回路110はプロセッサ113に結合されている。プロセッサ113は外部メモリ118bに結合されている。プロセッサ113を作動させてプロセッサ113に外部メモリ118bの少なくとも一部を消去するコマンドを実行させるように、耐タンパ回路110を構成してもよい。たとえば、耐タンパ回路110は、プロセッサにメモリ118bの一部を消去する割込みサービスルーチンを実行させてもよい。別の例では、メモリ118bの一部を消去するように具体的にデザインされたモードでプロセッサ113を起動するように、耐タンパ回路110を構成してもよい。プロセッサ113はメモリ118bに直接結合されていると例示しているが、他の実施形態では、メモリコントローラなどの他の介在回路が存在していてもよい。

40

#### 【0029】

図3Cを参照すると、いくつかの実施形態では、プロセッサ113にアクセスすることなくメモリ118cにアクセスするように、耐タンパ回路110を構成してもよい。したがって、メモリ118cを制御することによってメモリの一部を消去するように、耐タンパ回路110を構成してもよい。

#### 【0030】

耐タンパ回路110、プロセッサ113、及びメモリ118の種々の構成について上述してきたが、他の実施形態では、耐タンパ回路110、プロセッサ113、及びメモリ118を、プロセッサ113が用いるメモリ118部分を耐タンパ回路110によって消去し得るような任意の方法で結合してもよい。

50

### 【0031】

図4A～図4Bは、いくつかの実施形態により耐タンパ回路を伴うデバイスを外部コンポーネント上に実装することを例示する断面図である。図4Aに例示するのは、デバイス102が外部コンポーネント104に実装される前またはデバイス102が外部コンポーネント104から取り外された後のデバイス102及び外部コンポーネント104の状態である。図4Bに例示するのは、デバイス102が外部コンポーネント104に実装されたときのデバイス102及び外部コンポーネント104の状態である。

### 【0032】

図4A及び図4Bを参照すると、いくつかの実施形態では、デバイス102にはハウジング116が含まれる。デバイス102にはスイッチ220が含まれる。スイッチ220はハウジング116に結合されている。デバイス102の実装構造の一例としてハウジング116を例示しているが、他の実施形態では、実装構造はハウジング116以外の構造であってもよい。実装構造は、デバイスが外部コンポーネント104に対して動かされたときにデバイス102とともに残る任意の構造、基板、コンポーネントなどであってもよい。ハウジングにはフランジ212が含まれる。ハウジング116を外部コンポーネント104の壁124に取り付けるために留め具214を用いてもよい。例としてフランジ212及び留め具214などのコンポーネントを実装することを用いているが、他の実施形態では異なる実装技術を用いてもよい。

10

### 【0033】

スイッチ220は、デバイス102が外部コンポーネント104から取り外されたときに切り替わるように構成されている。デバイス102が図4Aに例示した状態にあるとき、スイッチ220のポール222は第1の状態にある。特定の例では、スイッチ220はモーメンタリーノーマルクローズスイッチであってもよい。したがって、図4Aに例示した状態では、スイッチ220は閉じている。

20

### 【0034】

図4Bに例示するようにデバイス102が外部コンポーネント104に実装されると、外部コンポーネント104の構造体204によってスイッチ220のポール222が切り替わる。したがって、スイッチ220は開いている。

### 【0035】

いくつかの実施形態では、構造体204は突出部、壁、リブ、ガセット、留め具などである。デバイス102が外部コンポーネント104に実装されたときに構造体204によってスイッチの状態220がトグルされるように、構造体204は外部コンポーネント104上に配置されている。

30

### 【0036】

デバイス102、外部コンポーネント104、及びスイッチ220の特定の構造を一例として用いてきたが、スイッチ220を、実装された第1の状態及び取り外された第2の状態にする任意のメカニズム及び付随する構造を用いてもよい。詳細には、耐タンパ回路110にアクセスして、耐タンパ回路110を無効にし得るか、そうでなければ前述したように耐タンパ回路110が回路112の少なくとも1つの機能を無効にすることを阻止し得る前に、スイッチ220が状態を変えるように、メカニズム及び付随する構造を形成してもよい。

40

### 【0037】

加えて、スイッチ220を機械的に切り替える必要はない。たとえば、スイッチ220を磁気的に切り替えてよい。デバイス102が外部コンポーネント104に実装されるかまたは外部コンポーネント104から取り外されるとスイッチ220が状態を変えるように、構造体204にはスイッチ220の構造に従う磁石または強磁性体が含まれていてもよい。

### 【0038】

一例として単一のスイッチ220を用いているが、他の実施形態では、異なる場所及び/または異なる構成の複数のスイッチ220を用いてもよい。いくつかの実施形態では、

50

これらのスイッチ 220 のうちのいずれか 1 つを耐タンパ回路 110 が用いて、回路 112 の少なくとも 1 つの機能を無効にしてもよい。

#### 【 0039 】

図 5 A ~ 図 5 D は、いくつかの実施形態による耐タンパ回路の概略回路図である。図 5 A を参照すると、耐タンパ回路 110 a には電源 502 及び無効化回路 504 が含まれる。電源 502 は、無効化回路 504 及び潜在的に回路 112 の一部が用い得る電力を発生させるように構成されている。

#### 【 0040 】

電源 502 はデバイス 102 内に配置されている。電源 502 は、デバイス 102 が外部コンポーネント 104 から取り外されたことが検出された後で電力を供給するように構成されている。電源 502 には、電池、キャパシタ、スーパー・キャパシタ、またはデバイス 102 内に配置され得る任意の他のエネルギー貯蔵装置が含まれていてもよい。いくつかの実施形態では、電源 502 を外部電源 506 によって充電してもよい。

10

#### 【 0041 】

いくつかの実施形態では、電源 502 には、デバイス 102 が外部コンポーネント 104 から取り外されたときに、電源 502 を耐タンパ回路 110 の他のコンポーネントに接続するスイッチが含まれていてもよい。

#### 【 0042 】

無効化回路 504 は、回路 112 の少なくとも 1 つの機能を無効にするように構成された回路である。この例では、無効化回路 504 には E R A S E 出力が含まれる。E R A S E 出力は、メモリを消去するかそうでなければ少なくとも 1 つの機能を無効にする消去コマンドを開始する回路 112 のプロセッサ、メモリなど上での E R A S E 入力に結合された信号である。

20

#### 【 0043 】

いくつかの実施形態では、電力 P W R を回路 112 のいくつかのコンポーネントに与えてもよい。詳細には、デバイス 102 が外部コンポーネント 104 から取り外されているときに、デバイス 102 を外部電源に接続しなくてもよいまたは外部電源を無効にしてよい。その代わりに、電源 502 は、無効化回路 504 が回路 112 の少なくとも 1 つの機能を無効にできるようにするために必要な電力を供給してもよい。

#### 【 0044 】

図 5 B を参照すると、耐タンパ回路 110 b には電池 B1 及びスイッチ SW1 が含まれる。単一の電池 B1 を例示しているが、他の実施形態では複数の電池を用いてもよい。スイッチ SW1 は 2 極 / 双投スイッチ (D P D T) である。スイッチ SW1 の結合は、例示した状態において、3.3V が V D D \_ C P U に結合されて、E R A S E - C P U に対して接続が形成されないようにされる。他方の状態では、V D D \_ C P U 及び E R A S E - C P U の両方とも電池 B1 に結合される。

30

#### 【 0045 】

V D D \_ C P U は、回路 112 の一部であり得るプロセッサに対する電源である。E R A S E \_ C P U は、回路 112 のプロセッサにそのメモリの一部または全部を消去するように命令する信号である。その結果、回路 112 の少なくとも 1 つの機能が無効にされ得る。対応するデバイス 102 が外部コンポーネント 104 に実装されたときの状態で、スイッチ SW1 を例示している。取り外されると、スイッチ SW1 は他方の状態に移行して、V D D \_ C P U を通してプロセッサに電力を供給し、E R A S E \_ C P U を通して消去信号を供給する。

40

#### 【 0046 】

アイソレータ I は、バッテリー B1 をスイッチから切断するように構成された取り外し可能な構造である。定位置にある時、バッテリー B1 は切断されスイッチ SW1 に電力を供給しない。したがって、E R A S E \_ C P U は作動しない。アイソレータ I は、取り付けられている間は定位置にあって耐タンパ回路 110 b を無効にすることができます。

#### 【 0047 】

50

図示された他の回路は、様々な状態に対して状態表示器を提供し得る。R 1 は VDD\_CPU に結合され、AND ゲート U 1 への入力をプルダウンする。AND ゲート U 1 への他の入力は、エラー信号 ERROR\_N である。デバイス 102 が取り付けられつつあり、3.3V 電力が印加されるとき、スイッチ SW 1 は図示とは反対の状態にある。ただし、アイソレータ I が存在するため、バッテリーは ERASE\_CPU を作動させない。VDD\_CPU は 3.3V に結合されず、R 1 によってプルダウンされる。したがって、AND ゲート U 1 の出力はローであり、LED\_D 1 がオンとなる。デバイス 102 が適切に取り付けられると、スイッチ SW 1 は図示の状態に変化し、VDD\_CPU は 3.3V にセットされる。ERROR\_N がローであることで示されるエラーがないと仮定すると、AND ゲート U 1 出力はハイに切り替わる。出力がハイであるため、LED\_D 1 がオフとなる。その結果、取り付け者は、スイッチ SW 1 が図示の状態となるように装置 102 が取り付けられたとの視覚的表示を受ける。

#### 【0048】

取り付けが行われたら、アイソレータ I を取り外すことができる。ERROR\_N は、AND ゲート U 1 の出力及び LED\_D 1 をオンとするかどうかの制御を行う。このようにして、LED\_D 1 はエラー表示器としての役割を果たす。しかしながら、デバイス 102 が取り外されると、スイッチ SW 1 は状態を変化させ、VDD\_CPU 及び ERASE\_CPU を作動させる。

#### 【0049】

一例において、スイッチ SW 1 は、閉状態においてバッテリー B 1 が ERASE\_CPU に結合される通常閉 (NC) 2 極双投 (DPDT) スイッチである。このスイッチは通常閉じており (NC)、デバイス 102 が取り付けられて外部コンポーネント 104 の機能によりスイッチが押されるときなど、スイッチが押されたとき開いた状態とすることができる。

#### 【0050】

図 5C を参照すると、動作は図 5B の動作と同様であり得る。ただし、VCC\_INS\_TALL は、取り付けられている間、3.3V が作動しない場合に供給される電源の電圧である。レジスタ R 3 及び R 4 は、VCC\_INS\_TALL または 3.3V のいずれかに対し LED\_D 2 と直列である。したがって、LED\_D 2 のカソードがローにプルダウンされると、LED\_D 2 がオンになる。バッファ U 2 はオープンドレインバッファである。インバータ U 3 はオープンドレインインバータである。したがって、U 2 への入力がローである場合、または U 3 への入力がハイである場合、LED\_D 2 がオンになる。

#### 【0051】

スイッチがデバイスの取り付けられた状態のデバイスにあるとき、ERASE\_CPU、並びにレジスタ R 5、R 6、R 7、及びトランジスタ Q 1 に結合されたノードはグラウンドにプルダウンされ、トランジスタ Q 1 はオフである。しかしながら、デバイス 102 が外部コンポーネント 104 から取り外されると、スイッチ SW 1 の状態が変わり、ノード N 1 の電圧が上昇し、C 1 が充電されるまで ERASE\_CPU がパルス出力を行う。メモリの一部を消去して少なくとも 1 つの機能を無効にするのに十分なパルスを提供するために、R 5 及び C 1 が選択される。

#### 【0052】

図 5D を参照すると、U 2、U 3、レジスタ R 8、R 9、及び R 10、ダイオード D 3、D 4、並びに LED\_D 5 の動作は、図 5C における動作と同様であり得る。ここで、ダイオード D 3 及び D 4 は、VCC\_INS\_TALL を 3.3V から分離する。耐タンパ回路 110d の動作は、図 5C の耐タンパ回路 110c の動作と同様であってもよい。

#### 【0053】

電源電圧の例として 3.3V が使用されたが、他の実施形態では、電源電圧は異なっていてもよい。

#### 【0054】

図 6A 及び図 6B は、いくつかの実施形態による耐タンパ回路を備えたデバイスを動作

させる技術を示すフローチャートである。図 6 A を参照すると、604において、外部コンポーネント 104 からのデバイス 102 の取り外しが検出される。上述のように、様々な技術を使用して、デバイス 102 の取り外しを検出することができる。例えば、スイッチの状態の変化、磁場の変化、回路の切断などによって、デバイス 102 が外部コンポーネント 104 から取り外されつつあるかどうかが示される。

#### 【0055】

606 では、デバイス 102 の少なくとも 1 つの機能が無効化される。上述のように、データの消去、プロセッサなどのコンポーネントの無効化などにより、少なくとも 1 つの機能が無効化され得る。無効化を行うために、様々な形態の耐タンパ回路 110 を使用することができる。

10

#### 【0056】

いくつかの実施形態では、デバイス 102 の取り外しの検出は、デバイス 102 の構造と外部コンポーネント 104 の構造との物理的分離を検出することを含み得る。例えば、スイッチ 220 は、デバイス 102 が外部コンポーネント 104 に対して移動した場合を検出し得る。

#### 【0057】

図 6 B を参照すると、600において、デバイス 102 が外部コンポーネント 104 に取り付けられる。例えば、権限を与えられた取り付け、部品の交換、及び / またはシステムのメンテナンスの間に、デバイス 102 が準備され、外部コンポーネント 104 に搭載され得る。取り付け中、耐タンパ回路 110 は解除され得る。例えば、上述のように、絶縁テープなどの取り外し可能なアイソレータ I を、電源 502 の接点と無効化回路 504 の間に配置することができる。

20

#### 【0058】

602 では、耐タンパ回路 110 を作動可能とすることができます。例えば、デバイス 102 が取り付けられた時点で絶縁テープを取り外すことにより、耐タンパ回路 110 を作動可能とすることができます。絶縁テープを取り外す前は、耐タンパ回路 110 を作動させることなくデバイス 102 を繰り返し搭載し取り外すことができる。しかし、一旦絶縁テープが取り外されると、耐タンパ回路 110 が作動可能となり、デバイス 102 を外部コンポーネント 104 から取り外す、すべての試みが検出され、動作 604 及び 606 においてデバイス 102 の回路 112 の少なくとも 1 つの機能を無効にするために用いられ得る。

30

#### 【0059】

耐タンパ回路 110 がトリガされ、回路 112 の少なくとも 1 つの機能が無効にされると、デバイス 102 は 608 でリセットされ得る。デバイス 102 のリセットは、権限を与えられた方法で再び取り付けまたは操作できる状態に、デバイス 102 を戻す動作を含む。例えば、デバイス 102 は、権限を与えられた修理拠点に返送されてもよい。デバイス 102 が、回路 112 の少なくとも 1 つの機能の無効化がなされていないデバイス 102 と同様の状態になるよう、消去されたデータのデバイス 102 への復元、無効化されたコンポーネントの再作動可能化、無効化されたコンポーネントの交換、上記アイソレータ I の再取り付けなどが行われ得る。デバイス 102 の権限を与えられた修理拠点への返送が一例として用いられたが、デバイス 102 のリセットは、権限を与えられた修理技術者が適切なデータ及び / またはコンポーネントを用いて実行することができる。権限を与えられていない当事者は、適切なデータ及び / またはコンポーネントを持っていない可能性があり、デバイス 102 を動作状態に復元することはできない。

40

#### 【0060】

図 7 はいくつかの実施形態による X 線システムのブロック図である。X 線システム 700 は、ホストコントローラ 702、インターフェースボード (IFB) 704、管補助ユニット (TAU) 732、及び X 線管 736 を含む。これらのコンポーネントは、回転可能なガントリ 710 に搭載されてもよい。

#### 【0061】

50

いくつかの実施形態では、デバイス 102 は IFB704 であるか、IFB704 の一部である。外部コンポーネント 104 はガントリ 710 であってもよい。したがって、IFB704 がガントリから取り外される場合、IFB704 の少なくとも 1 つの機能は、インターフェースボードがガントリ 710 から取り外された場合、無効にされ得る。IFB704 は、少なくとも 1 つの機能を無効化するために消去され得るファームウェア、ソフトウェア、較正データ、キー、ID、または他の暗号情報などの秘密情報を含み得る。

#### 【0062】

いくつかの実施形態では、デバイス 102 は、IFB704 に搭載された認証ドーター ボード (ADB) 703 である。外部コンポーネント 104 は IFB704 であり得る。上記のような情報は ADB703 が IFB704 から取り外された場合は削除される。

10

#### 【0063】

いくつかの実施形態では、デバイス 102 は TAU732 である。TAU732 は X 線管 736 に取り付けられてもよい。外部部品 104 は X 線管 736 であってもよい。したがって、TAU732 が X 線管 736 から取り外される場合、少なくとも TAU732 の 1 つの機能を無効にすることができる。TAU732 は、IFB704 または ADB703 と同様に消去され得るデータまたはファームウェアを含み得る。

#### 【0064】

いくつかの実施形態において、ホストコントローラ 702 は、ガントリ 710、IFB704、X 線管 736 などのコンポーネントの動作を、TAU732 を介して制御するように構成される。これらのコンポーネントは例として用いられるが、画像検出器、高電圧 (HV) 発生器、熱交換器などの他のコンポーネントが存在してもよい。ホストコントローラ 702 はまた、システム 700 の制御を指示することに加えて、IFB704 と通信し、識別、認証などの様々なアクションを実行するように構成されてもよい。

20

#### 【0065】

上述のように、いくつかの実施形態では、IFB704 は ADB703 を含む。この構造は、既存の CT システムへの ADB703 の組み込みをより容易とし得る。IFB704 は、ホストコントローラ 702 への通信リンク及び TAU732 への別の通信リンクを有する。ADB703 は、ホストコントローラ 702 及び TAU732 の両方との暗号化通信を可能とする暗号認証ハードウェア / ファームウェアを含む。IFB704 は ADB703 を保持し、それに電力を供給し、通信を ADB703 のネイティブ通信プロトコルに変換するデバイスである。

30

#### 【0066】

TAU732 は、IFB704 / ADB703 との暗号化通信を可能とする暗号認証ハードウェア / ファームウェアを含み、X 線管 736 に取り付けられている。病院が、TAU732 が取り付けられた新しい X 線管を設置する場合、IFB704 / ADB703 は、それが純正メーカーの X 線管または OEM の X 線管であることの確認を TAU732 に要求することができる。

#### 【0067】

いくつかの実施形態では、TAU732 の認証ユニットは X 線管 736 に搭載されているが、認証ユニットは X 線管 736 の一体化された部分であってもよい。耐タンパ回路 110 はその認証ユニットの一部である。同様に、元の取り付け場所から取り外した後に使用不可にすることが有益である、X 線検出器若しくは撮像装置、アクセラレータ、または他のデバイスなどの他のコンポーネントには、デバイス 102 が含まれる場合がある。これらのそれぞれは、関連付けられた耐タンパ回路 110 を有し得る。

40

#### 【0068】

特定の例では、別のシステムへの転売を目的とした、X 線若しくはマンモグラフィシステムからの使用済みの X 線管、X 線検出器、または撮像装置の取り外しが防止され得る。デバイス 102 を取り外すと、耐タンパ回路 110 のスイッチがトリガされ、認証機能を無効にし、ファームウェアを使用不能とし、通信またはデバイス 102 のさらなる使用を

50

許容するその他すべての重要な機能を阻止し得る。

**【 0 0 6 9 】**

いくつかの実施形態では、元の購入者にのみファームウェア／ソフトウェア（S W / F W）またはハードウェアの使用を許可するライセンス契約の下で特定の企業に販売された T A U 7 3 2、X線管 7 3 6、検出器、または他のデバイスソフトウェアのソフトウェア／ファームウェア（F W / S W）使用許諾を、耐タンパ回路 1 1 0 を使用して強化することもできる。そのような実施形態では、デバイスが取り外されると、それぞれの F W / S W が自動的に消去される。

**【 0 0 7 0 】**

回転式ガントリ 7 1 0 を備えた C T システムが X 線システム 7 0 0 の例として用られてきたが、X 線システム 7 0 0 は他の形態をとることもできる。

10

**【 0 0 7 1 】**

いくつかの実施形態は、一般に、暗号化された形式のシステム識別子（I D）（またはデバイス I D）をコンポーネントに使用するメカニズム、方法、及びシステムに関する。

**【 0 0 7 2 】**

いくつかの実施形態では、製造業者または O E M は、コンポーネントの取り付けが権限なしにシステムになされたことを、本明細書で説明されるメカニズム、方法、及びシステムによって、検出することができる。現在、サードパーティのサプライヤは、システム上のコンポーネントを使用済みの O E M コンポーネントまたはサードパーティのコンポーネントに入れ替えることができる。これにより、保証の問題、品質の問題、及び撮像システムの場合は画質の問題、診断の問題、及び誤診が発生する可能性がある。本明細書で説明される実施形態では、そのような権限を与えられていないコンポーネントの変更を検出し、システムの完全性を保証することが可能である。

20

**【 0 0 7 3 】**

本明細書に記載されているようなシステムがない場合、サードパーティは使用済みのコンポーネントを購入して顧客に販売し、O E M サービス契約に対し低価格で優位に立つことができる。それに対して、本明細書で説明する実施形態により、O E M ホストシステムは、そのコンポーネントが許可なく交換されているかどうかを判断し、及び／または、患者の診断に影響する撮像システムのコンポーネントの交換など、動作に影響するおそれがある古い、旧式の、または危険にさらされたコンポーネントのシステムへの取り付けを防ぐことができる。欠陥のある、または最適に機能しないコンポーネントは、誤診につながる可能性があり、極端な場合、患者に永久的な損害を与え、さらには死に至る可能性がある。

30

**【 0 0 7 4 】**

図 8 A、図 8 B はいくつかの実施形態による認証システムを含むシステムのブロック図である。図 8 A を参照すると、システム 8 0 0 a は、第 1 のデバイス 8 0 2 及び第 2 のデバイス 8 0 4 を含む。デバイス 8 0 2 及び 8 0 4 は、通信リンク 8 0 6 を介して結合される。通信リンクは、デバイス 8 0 2 及び 8 0 4 が通信できる任意の媒体であり得る。例えば、通信リンク 8 0 6 は、シリアルリンク、パラレルリンク、及び M o d b u s、C A N b u s などの自動化通信リンク、周辺機器相互接続エクスプレス（P C I e）、不揮発性メモリエクスプレス（N V M e）などのコンピュータバス、及び／またはイーサネット（登録商標）ネットワーク、ファイバチャネルネットワークなどのようなネットワークを含むことができる。

40

**【 0 0 7 5 】**

第 2 のデバイス 8 0 4 は、不揮発性メモリ 8 0 8 を含む。メモリ 8 0 8 は、スタティックランダムアクセスメモリ（S R A M）、フラッシュメモリ、電気的消去可能プログラマブル読み出し専用メモリ（E E P R O M）、磁気ストレージなどの任意の様々な不揮発性メモリを含むことができる。特に、メモリ 8 0 8 は、その少なくとも一部に一回限り書き込み（ワンタイム書き込み）方式で動作可能な部分を含む。メモリ 8 0 8 は、ワンタイム書き込み用に構成されていない他の不揮発性メモリ及び／または D D R 、D D R 2 、D D

50

R3、DDR4などの様々な規格に準拠したダイナミックランダムアクセスメモリ(DRAM)、ダブルデータレート同期ダイナミックランダムアクセスメモリ(DDR SDRAM)などの揮発性メモリを含むことができる。

#### 【0076】

ワンタイム書き込みであることは、メモリ808の一部が通常の書き込み操作で1回書き込み可能であることを意味する。一部の実施形態では、ワンタイム書き込みメモリ808は、他の手段によって消去することができない。その結果、メモリ808に記憶された値を変更するには、メモリ808を交換する必要がある。しかし、他の実施形態では、メモリ808全体を消去することによりメモリ808の一部を消去することができる。

#### 【0077】

メモリ808は、システム識別子(ID)をワンタイム書き込み部分に記憶するように構成される。システムIDは、システム800aに関連付けられた識別子である。システムIDは、普遍的に一意のID(UUID)またはグローバルに一意のID(GUID)であることにより、システム800aに一意であり得る。すべてのデバイス804及び812のシステムIDは同じであってもよい。しかしながら、他の実施形態では、特定のデバイス804または812のシステムIDは、システム800a及びそのデバイス804または812の両方に固有であり得る。いくつかの実施形態では、システムIDは、システム800aに固有の部分、特定のデバイス804または812に固有の部分、及び特定のデバイスタイプ804または812などを含み得る。

#### 【0078】

システムIDの値は、様々な形態を取り得る。例えば、システムIDは、保存されたデータがシステムIDである元の形式で存在する場合がある。ただし、他の例では、システムIDが暗号化された形式、システムIDのハッシュ、またはシステムIDの他の表現がシステムIDとして保存され、適切な復号化またはその他の操作により、それにふさわしい取扱いがなされる。

#### 【0079】

以下でさらに詳細に説明するように、システムIDは、システム800a内のデバイス804に記憶することができる。第1のデバイス802は、第2のデバイス804または第3のデバイス812に記憶されたシステムIDが、システム800aに関連付けられたシステムIDなどの予想されるシステムIDと一致することを検証できる。システムIDの一貫性は、第2のデバイス804または第3のデバイス812が、システム800aに意図され、最初に取り付けられた真正なコンポーネントであることを示し得る。システムIDが一致しない場合、デバイス804または812は権限を与えられていない当事者によって提供または取り付けられている可能性がある。その結果、同じメーカーの他のシステムまたはサードパーティーからのデバイスとの交換を検出し得る。

#### 【0080】

いくつかの実施形態では、第1のデバイス802は、複数の第2のデバイス804-1から804-Nに結合され得る。各第2のデバイス804は、ゼロから複数の第3のデバイス812-1から812-Mに結合され得る。

#### 【0081】

図9A～図10Cは、いくつかの実施形態による認証システムを動作させる技術の例を示すフローチャートである。システムを動作させる技術の以下の説明では、図8Aの第1のデバイス802、第2のデバイス804、及び第3のデバイス812の動作が例として用いられる。

#### 【0082】

図8A及び図9Aを参照すると、902において、第1のデバイス802は、第2のデバイス804に記憶されたシステムIDを求める要求を第2のデバイスに送信する。第2のデバイス804は、903で要求を受信する。この送信及び他の同様の動作は、通信リンク806を介して起こり得る。

#### 【0083】

10

20

30

40

50

904において、第2のデバイス804は、第2のデバイスに記憶されたシステムIDが空の値を有するかどうかを判定する。空の値は、第2のデバイス804がメモリ808にシステムIDを記憶していない状態を表す。実際の値はメモリ808に記憶されない場合がある。その代わりに、フラグ、レジスタ、状態などが、システムIDがメモリ808にプログラムされていないことを示す。そのような表示を確認することは、システムIDが空の値を有するかどうかを判定することの一部であり得る。第2のデバイス804のプロセッサは、システムID、フラグ、レジスタ、状態などの読み取りを試みて判定を行うように構成されてもよい。

#### 【0084】

906では、空の値に基づく応答が第1のデバイス802に送信される。いくつかの実施形態では、応答は特定の意味を有するシステムIDであり得る。例えば、すべてゼロまたはすべて1は、システムIDの空の値として指定され得る。他の実施形態では、システムIDの特定の1つ以上の値が空の値として指定されてもよい。その特定の値は、第2のデバイス804または第2のデバイス804のタイプに固有、システム800aまたはシステム800aのタイプに固有などであり得る。どの場合も、その値は、第2のデバイス804がシステムIDを記憶していないことまたはシステムIDが空の値であることを示していると第1のデバイス802が認識する値である。

10

#### 【0085】

他の実施形態では、空値応答は、実際のシステムIDを送信するために使用されるものとは異なるタイプのメッセージであってもよい。例えば、空の値の応答はエラーメッセージであってよい。エラーメッセージは、システムIDが空であることを示すエラー番号またはコードを有することができる。

20

#### 【0086】

908では、空の値の応答が第1のデバイス802によって受信される。これに応答して、第1のデバイス802は、910でシステムIDを第2のデバイス804に送信する。第2のデバイス804は、912でシステムIDを受信し、それをメモリ808のワンタイム書き込み部分に記憶する。一旦システムIDを記憶すると、メモリ808は、上述のような特別なステップなしに異なるシステムIDによる再プログラムを行うことはできない。その結果、第2のデバイス804はシステム800aとペアリングされる。第2のデバイス804がシステム800aから取り外されて別のシステムに取り付けられた場合、全く同じシステムであっても、システムIDは一致しないであろう。

30

#### 【0087】

904でシステムIDが第2のデバイス804に記憶されると決定された場合、914でシステムIDに基づく応答が第1のデバイス802に返えされる。例えば、第2のデバイス804はシステムIDを読み取り、それを暗号化し、暗号化されたシステムIDを第1のデバイス802に送信することができる。

#### 【0088】

第1のデバイス802は、第2のデバイス804に記憶されたシステムIDに基づく応答を916で受信し、第2のデバイス804に記憶されたシステムIDが実際のシステムIDと一致することを応答が示すかどうかを918で判定する。例えば、第1のデバイス802は、応答からシステムIDを読み取り、暗号化された応答を復号化するなどしてシステムIDを抽出し、それを第1のデバイス802に記憶されたシステムIDと比較することができる。上記のように、システムIDは様々な形式で記憶または暗号化することができる。比較は、様々な形式に適した方法で実行できる。

40

#### 【0089】

第2のデバイス804からの応答によって示されるシステムIDが正しくない場合、第2のデバイス804が応答しない若しくはタイムアウトする場合、または第2のデバイス804が不適切な応答を返す場合には、対策が920で実行される。対策は様々な形態を取り得る。例えば、いくつかの実施形態では、システム800aをシャットダウンし、デバイス802、804、816などを一時的または永続的に無効にすること、特定の

50

機能を無効にすること、動作範囲を縮小または制限することなどができる。他の実施形態では、不一致であるシステムIDに関する通知、警告、またはその他の通信を、システム800aのユーザに提供し、ネットワーク経由報告することなどができる。他の実施形態では、不一致であるシステムIDに関連する情報は、第1のデバイス802及び／または第2のデバイス804のメモリ808に記録され得る。関連情報は、第1のデバイス802及び／または第2のデバイス804、システムIDが一致しなかった回数、不一致のシステムID、916で受信された応答全体などの、タイムスタンプ、モデル番号及び／またはシリアル番号を含み得る。

#### 【0090】

いくつかの実施形態では、914で、システムIDに基づく応答が第2のデバイス804から第1のデバイス802に送信されるとき、通信を暗号化できる。例えば、第1のデバイス802及び第2のデバイス804の間に安全な通信リンクを確立すること、応答またはその一部を暗号化すること、第2のデバイス804に記憶されるシステムIDを暗号化することなどができる。その結果、盗聴者が第2のデバイス804から正しいシステムID応答を取得することをより困難とし得る。

10

#### 【0091】

システム800aは、関連する第2のデバイス804の下流にある第3の1つ以上のデバイス812を含む階層システムであってもよい。いくつかの実施形態では、第1のデバイス802と第3のデバイス812との間の通信の一部または全部が、関連付けられた第2のデバイス804を通過するか、または第2のデバイス804によって操作され得る。しかし、他の実施形態では、システムIDに関連する通信のみが、関連付けられた第2のデバイス804を通過するか、または第2のデバイス804によって操作され得る。

20

#### 【0092】

いくつかの実施形態では、第2のデバイス804と第3のデバイス812との間の相互作用は、第1のデバイス802及び第2のデバイス804に関して説明した動作と同じまたは同様であり得る。すなわち、第2のデバイス804がシステムIDを記憶した後は、第2のデバイス804及び第3のデバイス812の間で、システムIDの要求、空の場合における記憶、及び検証を行うことができる。

#### 【0093】

図8A、図9A、及び図9Bを参照すると、いくつかの実施形態では、914で第2のデバイス804がシステムID応答を送信した後は、第2のデバイス804は上記で説明した動作を図9Bに関して開始し得る。第3のデバイス812に記憶されたシステムIDの要求は、922で第2のデバイス804から第3のデバイス812に送信され得る。第3のデバイス812は、924で第3のデバイス812に記憶されたシステムIDに対する要求を受信し得る。926及び928では、図9Aの904及び906での動作と同様に、第3のデバイス812は、システムIDが空の値であるかまたは記憶されていないかを判定し、そうである場合、空の値の応答を返す。930及び932では、図9Aの908及び910での動作と同様に、第2のデバイス803は、第3のデバイス812に記憶されたシステムIDが空の値を有することを示す応答を受信し、応答としてシステムIDを送信する。934で、第3のデバイス812は、メモリ808にシステムIDを記憶する。936及び938では、914及び916での動作と同様に、第3のデバイス812は、第3のデバイス812に記憶されたシステムIDに基づく応答を送信し、その応答は第2のデバイス804により受信される。第2のデバイス804及び第3のデバイス812の動作は、第1のデバイス802及び第2のデバイス804の動作と同様であると説明されたが、他の実施形態では、動作は異なってもよい。例えば、システムIDのエンコーディング、送信で使用される暗号化、応答の形式、特定のプロトコルなどは異なるものが使用されてもよい。

30

#### 【0094】

940において、第2のデバイス804は、第3のデバイス812からの応答に基づいて検証応答を準備することができる。いくつかの実施形態では、検証応答は、第3のデバ

40

50

イス 8 1 2 自体からのシステム ID 応答を含むことができる。他の実施形態では、第 2 のデバイス 8 0 4 は、図 9 A の 9 1 8 における第 1 のデバイス 8 0 2 の相互作用と同様に、第 3 のデバイス 8 1 2 に記憶されたシステム ID が第 2 のデバイス 8 0 4 に記憶されたシステム ID と一致するかどうかを判定してもよい。検証応答は、第 3 のデバイス 8 1 2 に記憶されたシステム ID が正しいシステム ID であるかどうかの表示を含むことができる。

#### 【 0 0 9 5 】

図 8 A 及び図 9 A ~ 図 9 C を参照すると、いくつかの実施形態では、9 1 8 で第 2 のデバイス 8 0 4 に記憶されたシステム ID が正しいシステム ID であると判定されると、第 1 のデバイス 8 0 2 は 9 4 1 で第 2 のデバイス 8 0 4 に検証要求を送信し得る。9 4 2 で、第 2 のデバイス 8 0 4 は検証要求を受信する。上述のように、第 2 のデバイス 8 0 4 は、9 4 0 で検証応答を準備することができる。この検証応答は、9 4 4 で、第 2 のデバイス 8 0 4 によって第 1 のデバイス 8 0 2 に送信され得る。第 1 のデバイス 8 0 2 は検証応答を 9 4 6 で受信し、検証が成功したかどうかの判定を応答に基づいて 9 4 8 で行う。検証が成功した場合、動作は 9 5 2 に続く。

#### 【 0 0 9 6 】

しかし、検証が成功しなかった場合、9 5 0 で対策を実行することができる。対策は 9 2 0 に関して説明された対策と同様であり得る。しかしながら、検証応答は第 3 のデバイス 8 1 2 に関する付加情報を得るために、対策は第 3 のデバイス 8 1 2 にも当てはまる。例えば、第 3 のデバイス 8 1 2 は無効にされてもよく、第 3 のデバイス 8 1 2 を識別する通知が提供されてもよい。

#### 【 0 0 9 7 】

図 8 A、図 9 A、図 9 B、及び図 9 D を参照すると、いくつかの実施形態では、第 2 のデバイス 8 0 4 が 9 4 0 で検証応答を準備した後は、第 2 のデバイス 8 0 4 は、9 4 1 で送信される要求を待たずに 9 4 4 で検証応答を第 1 のデバイス 8 0 2 に送信することができる。9 4 6、9 4 8、9 5 0、及び 9 5 2 における第 1 のデバイス 8 0 2 の動作は、上述のものと同様であり得る。

#### 【 0 0 9 8 】

第 1 のデバイス 8 0 2 と第 2 のデバイス 8 0 4 の動作は、第 1 のデバイス 8 0 2 と 1 つの第 2 のデバイス間の通信の文脈で説明したが、第 1 のデバイス 8 0 2 と複数の第 2 のデバイス 8 0 4 - 1 から 8 0 4 - N との間で同じまたは同様の通信が発生し得る。すなわち、第 1 のデバイス 8 0 2 は、第 2 のデバイス 8 0 4 - 1 ~ 8 0 4 - N のそれについてシステム ID を要求し、上述のものと同様の動作を行うことができる。異なる第 2 のデバイス 8 0 4 - 1 ~ 8 0 4 - N に対する動作は、順次または並行して実行され得る。判定は、第 2 のデバイス 8 0 4 - 1 ~ 8 0 4 - N のうちの 1 つのみ、第 2 のデバイス 8 0 4 - 1 ~ 8 0 4 - N の一部、または第 2 のデバイス 8 0 4 - 1 ~ 8 0 4 - N のすべての応答に基づいてもよい。システム ID の一致または不一致の結果は、異なる第 2 のデバイス 8 0 3 - 1 から 8 0 4 - N に対し、同じ、類似、または異なる場合がある。第 2 のデバイス 8 0 4 と第 3 のデバイス 8 1 2 との間で説明される動作は、複数の第 3 のデバイス 8 1 2 との間で同様に実行され得る。さらに、3 層階層が例として用いられたが、デバイスの階層は、第 1 のデバイス 8 0 2 がシステム ID について他のデバイスに問い合わせを行うシステム 8 0 0 a の一部であり得る。

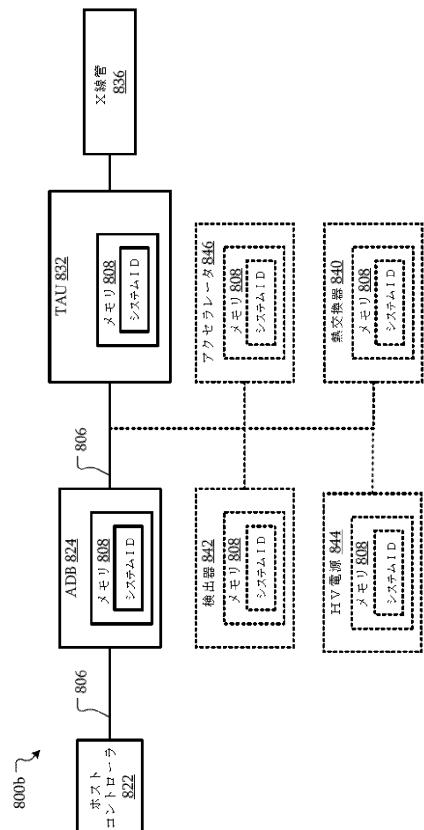

#### 【 0 0 9 9 】

図 8 B を参照すると、いくつかの実施形態では、X 線システム 8 0 0 b は、ホストコントローラ 8 2 2、A D B 8 2 4、T A U 8 3 2、及び X 線管 8 3 6 を含む。ホストコントローラ 8 2 2 は、X 線システム 8 0 0 b のシステムコントローラであり得る。ホストコントローラ 8 2 2 は、図 8 A の第 1 のデバイス 8 0 2 としての役割を果たし、図 9 A ~ 図 9 D に記載された関連付けられた動作を行ふことができる。

#### 【 0 1 0 0 】

A D B 8 2 4 は、システム 8 0 0 b のシステム ID 及び認証動作を管理する回路であつてもよい。A D B 8 2 4 は、メモリ 8 0 8 を含むことができる。A D B 8 2 4 は、図 8 A

10

20

30

40

50

の第2のデバイス804としての役割を果たし、図9A～図9Dに記載された関連付けられた動作を行うことができる。

#### 【0101】

T A U 8 3 2 は、X線管836の動作を制御するように構成された回路である。例えば、T A U 8 3 2 は、カソード電圧／電流、アノード電圧／電流、フィラメント電圧／電流、焦点調節電子機器、ステアリング電子機器、モータなどを、特定のX線管836に依拠して制御するように構成され得る。T A U 8 3 2 は、メモリ808を含み、図8Aの第3のデバイス812としての役割を果たし、図9A～図9Dに記載された関連付けられた動作を行うことができる。

#### 【0102】

T A U 8 3 2 は、本明細書に記載のシステムIDを使用して動作することができるX線システム800bのデバイスの例として用いられているが、X線システム800bの他のデバイスも同様に動作することができる。例えば、熱交換器840、検出器842、高電圧(HV)電源844、加速器846などは、本明細書で説明されるシステムIDを使用して動作し得る。

10

#### 【0103】

いくつかの実施形態では、初期化または設置時に、システムIDは、ホストコントローラ822からADB824に送信されてメモリ808に記憶されることができる。ADB824は、同様に、それらのデバイスの対応するメモリ808に記憶するために他のデバイス832、840、842、844、846、848などにシステムIDを伝播することができる。したがって、システム800bのデバイスは、そのシステム800bとペアリングされることができる。通常の動作では、デバイスは、正しいシステムIDを報告し、システム800bは、動作を継続することができる。しかしながら、部品が異なる既存のシステムIDによって不正に交換された場合、上述した対策が実行されてもよい。

20

#### 【0104】

いくつかの実施形態では、ホストコントローラは、ADB824を使用し、残りの製造業者またはシステム800bにおけるOEMのコンポーネントと通信する。いくつかの実施形態では、システム800bとペアリングされるコンポーネントのみがADB824及びT A U 8 3 2 である。

30

#### 【0105】

X線システム800bにおける本明細書に記載のシステムIDの使用は、システム800bの安全性及び／または寿命を向上させることができる。特に、システム800bのコンポーネントは、その特定のX線システム800bについて位置合わせ、校正、またはそうでなければ構成されることがある。システム800bが最初に設置されるとき、X線システム800bの様々なデバイスの空のシステムIDは、その特定のX線システム800bに固有のシステムIDに初期化されることがある。X線システム800bにおけるデバイスが異なるシステムIDを有する他のシステムからのデバイスと交換される場合、X線システム800bの動作は、同じでない場合があり、X線管836などのデバイスによって危険になることがある。上述したように、X線システム800bは、そのような状況が検出された場合、ユーザに通知し、X線システム800bまたはコンポーネントをシャットダウンなどの対策を講じることができる。その結果、X線システム800bが誤った結果及び／または危険な動作状態をもたらす可能性がある方法で動作する機会を低減または排除することができる。

40

#### 【0106】

いくつかの実施形態では、本明細書に記載のシステムIDの記憶及び検証は、製造業者またはベンダの顧客がコンポーネント自体またはサードパーティーを介して交換する能力を制限することができる。検証プロセスは、ADB824、T A U 8 3 2 などが正規の製造業者またはOEM製品であり且つ他のX線システムとの間で交換されていないかどうかを確認するために検査する。それは、サードパーティーのサービス組織が使用済みのX線管を公開市場で購入し、それらを改修してから病院などの顧客に販売することを防止する

50

。製造業者、ベンダ、システムインテグレータなどは、望ましくない結果または危険な結果をもたらす可能性がある、それらのシステムが他のシステムからのデバイスによって変更される機会を低減することができる。

#### 【0107】

いくつかの実施形態では、本明細書に記載のシステムIDの使用は、再加工されたデバイスが意図されていないシステムに設置される機会を低減することができる。例えば、システムとペアリングされ且つシステムIDを有するデバイスは、修理、更新などのために返却されることがある。デバイスは、元のシステムIDによってプログラミングされることができるかまたはシステムIDがそのまま残されることができる。その結果、そのデバイスが顧客または設置者に提供されると、システムIDは、元のシステムのシステムIDと一致する。デバイスが他のシステムに設置されている場合、同様のシステムまたは同じ種類のシステムであっても、システムIDは一致せず、上述した対策が実行されることがある。いくつかの実施形態では、既知の顧客または設置者が同じシステムにデバイスを再設置する場合、システムIDは、プログラミングされないままにすることができる。

10

#### 【0108】

図8A及び図9A - 図10Cを参照すると、いくつかの実施形態では、上述した948における検証の成功後に認証動作が実行されることができる。例えば、1002において、第1のデバイス802は、認証要求を第2のデバイス804に送信する。1004において、認証要求は、第2のデバイス804によって受信される。第2のデバイス804は、1006において、認証要求を第3のデバイス812に送信する。

20

#### 【0109】

第3のデバイス812は、1008において認証要求を受信する。1010において、第3のデバイスは、認証応答を生成し、1012において、その認証応答を第2のデバイス804に送信する。

#### 【0110】

第2のデバイス804は、1014において、第3のデバイス812から認証応答を受信する。第2のデバイス804は、1016において認証応答を分析し、1018において故障を記録し、1020において自身の認証応答を生成する。1020において生成された認証応答は、1つ以上の第3のデバイス812から受信した認証応答または認証応答(複数)及び第2のデバイス804自身の認証応答を集約することができる。

30

#### 【0111】

1022において、第1のデバイス802は、図10Bに示すように1024において第2のデバイスによって受信された認証状態の要求を送信することができる。それに応答して、第2のデバイス804は、1026において第1のデバイス802に認証応答を送信する。あるいは、第2のデバイス804は、図10A及び図10Cに示すように、1020における生成後に1026において第1のデバイス802に認証応答を送信してもよい。

#### 【0112】

1028において認証応答が受信されると、1030において、認証が成功したかどうかを判定するために応答が分析されることができる。成功した場合、1034において動作を継続することができる。成功しない場合、上述した対策と同様に1032において対策が講じられる。

40

#### 【0113】

様々な異なる技術を使用して、デバイス804及び812を認証することができる。いくつかの実施形態では、認証は、隠し番号を使用するチャレンジを使用して実行されることができる。暗号化アルゴリズムは、初期化ベクトル(IV)及び暗号化鍵(key)を使用することができる。第1のデバイス802及び/または第2のデバイス804は、そのIV及びkeyを使用してチャレンジ(数学的問題)を作成し、それを下流の第2のデバイス804または第3のデバイス812に送信することができる。そのデバイスがkey及びIVを有する場合、同じ数学的問題を実行して同じ結果を取得することができる。

50

そして、「チャレンジ」された第2のデバイス804または第3のデバイス812は、暗号化された形式でその数学的问题への「回答」を返送することができ、元のコンポーネントは、それが正しくチャレンジに回答していることを確認することができる。正解で応答した場合、第1のデバイス802及び／または第2のデバイス804は、対応する第2のデバイス804または第3のデバイス812を真正部品として扱うことができる。

#### 【0114】

いくつかの実施形態では、I V及びk e yは、暗号認証集積回路の制限されたメモリに保持される。例えば、A T S H A集積回路は、そのような制限されたメモリを含むことができ、暗号化された通信に関連する計算を実行することができる。I V及びk e yがそのような制限されたメモリに記憶されている場合、認証操作は、より安全なものとすることができます。

10

#### 【0115】

いくつかの実施形態では、認証プロセスが使用され、必要な全てのコンポーネントがシステムにあり、特定の顧客のために設計され、及び／または純正製造業者またはO E Mコンポーネントであることを確認することができる。異なる顧客は、サードパーティーが1人の顧客向けに設計されたコンポーネントを取得して他人に販売することができないように、顧客固有の暗号化鍵を所有することができる。いかなる欠落コンポーネントも、それらが存在しないかどうかを認証しないため、認証プロセスに失敗する。認証プロセスは、サードパーティーがシステムの部品を供給することを防止することができる。完全コンピュータ断層撮影（C T）システムが5つの製造業者またはO E Mコンポーネントを有するように設計されているが、そのうちの4つのみが正規であり、5つ目がサードパーティーから供給されている場合、認証プロセスは、その5つ目のコンポーネントを真正ではないと特定する。

20

#### 【0116】

上述したように、システム800aには、2つ以上の第2のデバイス804及び2つ以上の第3のデバイス812が存在してもよい。単一の第2のデバイス804及び単一の第3のデバイス812に関して説明したようにこれらのそれぞれと認証を行う。

30

#### 【0117】

図8Aのシステム800aは、例示として使用されたが、図10A-図10Cに関して上述した認証動作は、図8BのX線システム800bなどの他のシステムによって実装されてもよい。

#### 【0118】

いくつかの実施形態は、以下を備えるデバイス102を含む。すなわち、デバイス102を外部コンポーネント104に取り付けるように構成された取り付け構造、第1の回路112、及び第1の回路112に電気的に接続され且つデバイス102が外部コンポーネント104から取り外された場合に第1の回路112の少なくとも1つの機能を無効化するように構成された耐タンパ回路、である。いくつかの実施形態では、外部コンポーネント104は、壁、ハウジング、または第1の回路112によって制御されない他の構造を含んでいてもよい。

40

#### 【0119】

いくつかの実施形態では、第1の回路112は、外部コンポーネント104を制御するように構成される。いくつかの実施形態では、第1の回路112の少なくとも1つの機能は、外部コンポーネント104の制御に関係しない機能を含む。

#### 【0120】

いくつかの実施形態では、第1の回路112の少なくとも1つの機能は、外部コンポーネント104を制御する第1の回路112の機能を含む。

#### 【0121】

いくつかの実施形態では、デバイス102は、取り付け構造に結合されたハウジング116をさらに備え、ハウジング116は、デバイス102が外部コンポーネント104に取り付けられたときに耐タンパ回路を解除するためにアクセスを制限するように構成され

50

る。

**【 0 1 2 2 】**

いくつかの実施形態では、耐タンパ回路 110 は、取り付け構造 116 に結合され且つデバイス 102 が外部コンポーネント 104 から取り外されたときに切り替わるように構成されたスイッチ 220 または SW1 を備える。

**【 0 1 2 3 】**

いくつかの実施形態では、スイッチ 220 または SW1 は、外部コンポーネント 104 に取り付けられた場合に外部コンポーネント 104 の構造によって切り替わるように構成される。

**【 0 1 2 4 】**

いくつかの実施形態では、耐タンパ回路 110 は、デバイス 102 の内部に配置され且つ外部コンポーネント 104 からのデバイス 102 の取り外しを検出した後に電力を供給するように構成された電源 502 と、第 1 の回路 112 の少なくとも 1 つの機能を無効化するように構成された無効化回路 504 とを備え、スイッチ 220 または SW1 は、デバイス 102 が外部コンポーネント 104 から取り外されると、電源 502 を無効化回路 504 に電気的に接続するように構成される。

**【 0 1 2 5 】**

いくつかの実施形態では、第 1 の回路 112 は、プロセッサ 113 を含み、耐タンパ回路 110 は、デバイス 102 が外部コンポーネント 104 から取り外されると、プロセッサ 113 によって使用されるメモリ 118 または 808 の少なくとも一部を消去するよう構成される。

**【 0 1 2 6 】**

いくつかの実施形態では、プロセッサ 113 によって使用されるメモリ 118 または 808 の少なくとも一部は、プロセッサ 113 と統合されたメモリ 118 または 808 を備える。

**【 0 1 2 7 】**

いくつかの実施形態では、プロセッサ 113 によって使用されるメモリ 118 または 808 の少なくとも一部は、暗号化情報を記憶する。

**【 0 1 2 8 】**

いくつかの実施形態では、デバイス 102 は、X 線システムに関連付けられた電子機器の一部であり、外部コンポーネント 104 は、X 線システム 700 または 800b の X 線管 736 または 836 である。

**【 0 1 2 9 】**

いくつかの実施形態では、デバイス 102 は、X 線システム 700 または 800b に関連付けられたコンポーネント認証システムの一部である。

**【 0 1 3 0 】**

いくつかの実施形態は、デバイス 102 によってデバイス 102 の外部のコンポーネント 104 からのデバイス 102 の取り外しを検出することと、コンポーネント 104 からのデバイス 102 の取り外しを検出することに応答して、デバイス 102 の回路 112 の少なくとも 1 つの機能を無効化することとを備える方法を含む。

**【 0 1 3 1 】**

いくつかの実施形態では、デバイス 102 によってコンポーネント 104 からのデバイス 102 の取り外しを検出することは、デバイス 102 の構造とデバイス 102 の外部のコンポーネント 104 の構造との物理的分離を検出することを備える。

**【 0 1 3 2 】**

いくつかの実施形態では、デバイス 102 の回路 112 の少なくとも 1 つの機能を無効化することは、内部電源 502 から無効化回路 504 に給電することと、無効化回路 504 を使用してデバイス 102 の回路の少なくとも 1 つの機能を無効化することとを備える。

**【 0 1 3 3 】**

いくつかの実施形態では、デバイス 102 によってコンポーネント 104 からのデバイ

10

20

30

40

50

ス102の取り外しを検出することは、デバイス102の構造とデバイス102の外部のコンポーネント104の構造との物理的分離を検出することを備える。

#### 【0134】

いくつかの実施形態では、本方法は、さらに、デバイス102をコンポーネント104に設置することと、デバイス102の回路の少なくとも1つの機能を無効化するように構成された耐タンパ回路110を作動可能にすることを備える。

#### 【0135】

いくつかの実施形態では、本方法は、さらに、デバイス102の回路112の少なくとも1つの機能を無効化するように構成された耐タンパ回路110をリセットすることを備える。

10

#### 【0136】

いくつかの実施形態は、デバイスによってデバイスの外部のコンポーネントからのデバイスの取り外しを検出する手段と、コンポーネントからのデバイスの取り外しを検出する手段に応答してデバイスの回路の少なくとも1つの機能を無効化する手段とを備えるデバイスを含む。検出する手段の例は、耐タンパ回路110、スイッチ220またはSW1などを含む。デバイスの回路の少なくとも1つの機能を無効化する手段の例は、耐タンパ回路110、プロセッサ113、メモリ118または808などを含む。

#### 【0137】

いくつかの実施形態では、デバイスは、さらに、コンポーネントからのデバイスの物理的分離を検出する手段と、コンポーネントからのデバイス102の物理的分離を検出する手段に応答して回路のメモリの少なくとも一部を消去する手段とを備える。コンポーネントからのデバイスの物理的分離を検出する手段の例は、耐タンパ回路110、スイッチ220またはSW1などを含む。回路のメモリの少なくとも一部を消去する手段の例は、耐タンパ回路110、プロセッサ113、メモリ118または808などを含む。

20

#### 【0138】

いくつかの実施形態は、第2のデバイス804に記憶されたシステム識別子(ID)の要求を第2のデバイス804において第1のデバイス802から受信することと、第2のデバイス804に記憶されたシステムIDが空の値を有するかどうかを第2のデバイス804によって判定することと、第2のデバイス804に記憶されたシステムIDが空の値を有しない場合、第2のデバイス804に記憶されたシステムIDに基づく応答を第2のデバイス804によって第1のデバイス802に送信することとを備える方法を含む。

30

#### 【0139】

いくつかの実施形態では、本方法は、さらに、第2のデバイス804に記憶されたシステムIDが空の値を有する場合、第2のデバイス804に記憶されたシステムIDが空の値を有することを、第2のデバイス804によって第1のデバイス802に通信することを備える。

#### 【0140】

いくつかの実施形態では、本方法は、さらに、システムIDを第1のデバイス802から第2のデバイス804によって受信することと、第1のデバイス802から受信したシステムIDを、第2のデバイス804に記憶されたシステムIDとして第2のデバイス804によって記憶することとを備える。

40

#### 【0141】

いくつかの態様では、第1のデバイス802から受信したシステムIDを、第2のデバイス804に記憶されたシステムIDとして第2のデバイス804によって記憶することは、第1のデバイス802から受信したシステムIDを第2のデバイス804によってワントライムライトメモリ808に記憶することを備える。

#### 【0142】

いくつかの実施形態では、第2のデバイス804に記憶されたシステムIDに基づく応答を第2のデバイス804によって第1のデバイス802に送信することは、第2のデバイス804に記憶されたシステムIDを暗号化することと、暗号化されたシステムIDを

50

第2のデバイス804によって第1のデバイス802に送信することとを備える。

**【0143】**

いくつかの実施形態では、本方法は、さらに、第3のデバイス812に記憶されたシステムIDに対する要求を第2のデバイス804によって第3のデバイス812に送信することと、第3のデバイス812に記憶されたシステムIDに対する要求に対する応答を第2のデバイス804によって第3のデバイス812から受信することとを備える。

**【0144】**

いくつかの実施形態では、本方法は、さらに、第3のデバイス812に記憶されたシステムIDに対する要求に対する応答に基づく応答を第2のデバイス804によって第1のデバイス802に送信することとを備える。 10

**【0145】**

いくつかの実施形態では、本方法は、さらに、第3のデバイス812に記憶されたシステムIDが空の値を有するかどうかを第3のデバイス812によって判定することと、第3のデバイス812に記憶されたシステムIDが空の値を有する場合、第3のデバイス812に記憶されたシステムIDが空の値を有することを第3のデバイス812によって第2のデバイス804に通信することとを備える。

**【0146】**

いくつかの実施形態では、本方法は、さらに、第2のデバイス804から受信したシステムIDを第3のデバイス812に記憶されたシステムIDとして第3のデバイス812によって記憶することとを備える。 20

**【0147】**

いくつかの実施形態では、第2のデバイス804は、X線システム800b用の認証デバイスであり、第3のデバイス812は、X線システム800bのX線管836用の制御デバイスである。

**【0148】**

いくつかの実施形態は、第2のデバイス804に記憶されたシステム識別子(ID)に対する要求を第1のデバイス802から第2のデバイス804に送信することと、第2のデバイス804に記憶されたシステムIDに対する要求に対する応答を第1のデバイス802によって第2のデバイス804から受信することと、第2のデバイス804に記憶されたシステムIDが第2のデバイス804を含むシステムの正しいシステムIDであるかどうかを第1のデバイス802によって判定することと、第2のデバイス804に記憶されたシステムIDが第2のデバイス804を含むシステムの正しいシステムIDであるかどうかに基づいて、第2のデバイス804を含むシステムを第1のデバイス802によって動作させることと、を備える方法を含む。 30

**【0149】**

いくつかの実施形態では、第2のデバイス804を含むシステム動作させることは、第2のデバイス804に記憶されたシステムIDが第2のデバイス804を含むシステムの正しいシステムIDではない場合、対策を有効にすることとを備える。

**【0150】**

いくつかの実施形態では、対策は、第2のデバイス804を無効化すること、第2のデバイス804を含むシステムを無効化すること、第2のデバイス804に記憶されたシステムID及び第2のデバイス804を含むシステムの正しいシステムIDがユーザに一致しない旨の警告を提示することのうちの少なくとも1つを含む。 40

**【0151】**

いくつかの実施形態では、第2のデバイス804を含むシステムを動作させることは、第2のデバイス804に記憶されたシステムIDが第2のデバイス804を含むシステムの正しいシステムIDと一致する場合、第2のデバイス804に従属するデバイスの検証の要求を第1のデバイス802によって第2のデバイス804に送信することとを備える。

**【0152】**

いくつかの実施形態では、本方法は、さらに、第2のデバイス804に従属するデバイ

スの検証の要求に対する応答を第2のデバイス804から第1のデバイス802によって受信することを備え、第2のデバイス804を含むシステムを動作させることは、第2のデバイス804に従属する少なくとも1つのデバイスの検証の要求に対する応答に基づいてシステムを動作させることを備える。

#### 【0153】

いくつかの実施形態では、第2のデバイス804は、X線システム800b用の認証デバイスであり、第2のデバイス804に従属する少なくとも1つのデバイスは、X線システム800bのX線管836用の制御デバイスである。

#### 【0154】

いくつかの実施形態では、本方法は、さらに、第2のデバイス804の認証要求を第1のデバイス802から第2のデバイス804に送信することと、第2のデバイス804の認証要求に対する応答を第1のデバイス802によって第2のデバイス804から受信することとを備え、第2のデバイス804を含むシステムを動作させることは、第2のデバイス804の認証要求に対する応答に基づいて第2のデバイス804を含むシステムを動作させることを備える。

10

#### 【0155】

いくつかの実施形態は、デバイスに記憶されたシステム識別子(ID)に対する要求を第1の外部デバイスから受信する手段と、デバイスに記憶されたシステムIDが空の値を有するかどうかを判定する手段と、デバイスに記憶されたシステムIDが空の値を有しない場合、デバイスに記憶されたシステムIDに基づく応答を第1のデバイスに送信する手段とを備えるデバイスを含む。システム識別子に対する要求を第1の外部デバイスから受信する手段及びシステムIDに基づく応答をデバイスに送信する手段の例は、第2のデバイス804、第3のデバイス812などを含む。

20

#### 【0156】

いくつかの実施形態では、デバイスは、さらに、第2の外部デバイスに記憶されたシステムIDの要求を第2の外部デバイスに送信する手段と、第2の外部デバイスに記憶されたシステムIDに対する要求に対する応答を第3のデバイスから受信する手段とを備える。システムIDに対する要求を第2の外部デバイスに送信する手段及びシステムIDに対する要求に対する応答を第3のデバイスから受信する手段の例は、第2のデバイス804、第3のデバイス812などを含む。

30

#### 【0157】

いくつかの実施形態は、上述した方法を実施するために実行されるように構成された複数の命令を含む少なくとも1つの非一時的コンピュータ可読記憶媒体を含む。

#### 【0158】

上記提供した概要は例示であり、決して限定することを意図するものではない。上述した例に加えて、図面、以下の詳細な説明、及び添付の特許請求の範囲を参照することにより、本発明のさらなる態様、特徴、及び利点が明らかになるであろう。

#### 【0159】

回路は、ハードウェア、ファームウェア、プログラムコード、実行可能コード、コンピュータ命令、及び/またはソフトウェアを含むことができる。非一時的コンピュータ可読記憶媒体は、信号を含まないコンピュータ可読記憶媒体とすることができます。

40

#### 【0160】

上述した動作は、様々な回路において実装されてもよい。例えば、動作は、これらに限定されるものではないが、ロジックチップ、トランジスタ、または他のコンポーネントを含むカスタム超大規模集積(VLSI)回路またはゲートアレイを備えるハードウェア回路として実行されてもよい。動作はまた、これらに限定されるものではないが、フィールドプログラマブルゲートアレイ(FPGA)、プログラマブルアレイロジック、プログラマブルロジックデバイスまたは同様のデバイスを含むプログラマブルハードウェアデバイスにおいて実行されてもよい。

#### 【0161】

50

「例」または「実施形態」への本明細書を通した言及は、実施例に関連して記載される特定の特徴、構造、または特性が本発明の少なくとも1つの実施形態に含まれることを意味する。したがって、本明細書を通した様々な場所における「例」または「実施形態」という語句の出現は、必ずしも全てが同じ実施形態を指しているわけではない。

#### 【0162】

さらにまた、記載された特徴、構造、または特性は、1つ以上の実施形態において適切な方法で組み合わせることができる。以下の説明において、本発明の実施形態の完全な理解を提供するために、多数の特定の詳細（例えば、レイアウト及び設計の例）が提供される。しかしながら、当業者は、本発明が1つ以上の特定の詳細を用いることなく、または他の方法、コンポーネント、レイアウトなどを用いて実施される得ることを認識するであろう。他の例では、周知の構造、コンポーネント、または動作は、本発明の態様を不明瞭にすることを回避するために詳細には図示も記載もされていない。

#### 【0163】

ミーンズプラスファンクション形式で具体的に記載された要素は、必要に応じて、米国特許法第112条第6パラグラフにしたがって、本明細書に記載された対応する構造、材料、または作用及びその均等物を包含するものと解釈されることが意図される。

#### 【0164】

前述の例は、1つ以上の特定用途における本発明の原理の例示であるが、形態、使用法及び実装の詳細の多数の変更は、本発明の原理及び概念から逸脱することなく、発明能力を行使することなく行われることができることが当業者にとって明らかであろう。したがって、本発明が限定されることはない。本発明の様々な特徴及び利点は、以下の特許請求の範囲に記載されている。

#### 〔項目1〕

デバイスであって、

前記デバイスを外部コンポーネントに実装するように構成された実装構造と、

第1の回路と、

前記第1の回路に電気的に接続された耐タンパ回路であって、前記デバイスが前記外部コンポーネントから取り外されたときに前記第1の回路の少なくとも1つの機能を無効にするように構成された前記耐タンパ回路と、を含む、前記デバイス。

#### 〔項目2〕

前記第1の回路は前記外部コンポーネントを制御するように構成されている、項目1に記載のデバイス。

#### 〔項目3〕

前記第1の回路の前記少なくとも1つの機能には、前記外部コンポーネントを制御する前記第1の回路の機能が含まれる、項目2に記載のデバイス。

#### 〔項目4〕

前記実装構造に結合されたハウジングをさらに含み、

前記ハウジングは、前記デバイスが前記外部コンポーネントに実装されたときに前記耐タンパ回路を作動解除するアクセスを制限するように構成されている、項目1に記載のデバイス。

#### 〔項目5〕

前記耐タンパ回路は、

前記実装構造に結合されたスイッチであって、前記デバイスが前記外部コンポーネントから取り外されたときに切り替わるように構成された前記スイッチを含む、項目1に記載のデバイス。

#### 〔項目6〕

前記スイッチは、前記外部コンポーネント上に実装されたときに前記外部コンポーネントの構造によって切り替えられるように構成されている、項目5に記載のデバイス。

#### 〔項目7〕

前記耐タンパ回路は、

10

20

30

40

50

前記デバイス内に配置された電源であって、前記デバイスが前記外部コンポーネントから取り外されたことを検出した後に電力を供給するように構成された前記電源と、

前記第1の回路の前記少なくとも1つの機能を無効にするように構成された無効化回路と、を含み、

前記スイッチは、前記デバイスが前記外部コンポーネントから取り外されたときに前記電源を前記無効化回路に電気的に接続するように構成されている、項目5に記載のデバイス。

#### [項目8]

前記第1の回路はプロセッサを含み、

前記耐タンパ回路は、前記デバイスが前記外部コンポーネントから取り外されたときに前記プロセッサが用いるメモリの少なくとも一部を消去するように構成されている、項目1に記載のデバイス。

10

#### [項目9]

前記プロセッサが用いる前記メモリの少なくとも一部は、前記プロセッサと一体化されたメモリを含む、項目8に記載のデバイス。

#### [項目10]

前記プロセッサが用いる前記メモリの少なくとも一部は暗号情報を記憶する、項目8に記載のデバイス。

#### [項目11]

前記デバイスは、x線システムに付随するエレクトロニクスの一部であり、

前記外部コンポーネントは前記x線システムのx線管である、項目1に記載のデバイス。

20

#### [項目12]

前記デバイスは、x線システムに付隨するコンポーネント認証システムの一部である、項目1に記載のデバイス。

#### [項目13]

方法であって、

デバイスによって、前記デバイスが前記デバイスの外部のコンポーネントから取り外されたことを検出することと、

前記デバイスが前記コンポーネントから取り外されたことを検出したことに応じて、前記デバイスの回路の少なくとも1つの機能を無効にすることと、を含む、前記方法。

30

#### [項目14]

前記デバイスによって、前記デバイスが前記コンポーネントから取り外されたことを検出することは、前記デバイスの構造と前記デバイスの外部の前記コンポーネントの構造との物理的分離を検出することを含む、項目13に記載の方法。

#### [項目15]

前記デバイスの前記回路の少なくとも1つの機能を無効にすることは、

内部電源から無効化回路に電力供給することと、

前記無効化回路を用いて前記デバイスの前記回路の前記少なくとも1つの機能を無効にすることと、を含む、項目14に記載の方法。

40

#### [項目16]

前記デバイスによって、前記デバイスが前記コンポーネントから取り外されたことを検出することは、前記デバイスの構造と前記デバイスの外部の前記コンポーネントの構造との物理的分離を検出することを含む、項目13に記載の方法。

#### [項目17]

前記デバイスを前記コンポーネント上に取り付けることと、

前記デバイスの前記回路の少なくとも1つの機能を無効にするように構成された耐タンパ回路を作動状態にすることと、をさらに含む、項目13に記載の方法。

#### [項目18]

前記デバイスの前記回路の少なくとも1つの機能を無効にするように構成された耐タンパ回路をリセットすることをさらに含む、項目13に記載の方法。

50

【項目 19】デバイスであって、デバイスによって、前記デバイスが前記デバイスの外部のコンポーネントから取り外されたことを検出するための手段と、前記手段が、前記デバイスが前記コンポーネントから前記取り外されたことを検出したことに応じて、前記デバイスの回路の少なくとも 1 つの機能を無効にするための手段と、を含む、前記デバイス。【項目 20】前記デバイスの前記コンポーネントからの物理的分離を検出するための手段と、前記手段が前記デバイスの前記コンポーネントからの物理的分離を検出したことに応じて、前記回路のメモリの少なくとも一部を消去するための手段と、をさらに含む、項目 19 に記載のデバイス。

10

【図面】

【図 1】

【図 2】

20

20

30

40

50

【図3】

【図4】

【図5 A】

【図5 B】

10

20

30

40

50

【図 5 C】

【図 5 D】

10

20

30

40

【図 6】

【図 7】

50

【図 8 A】

【図 8 B】

10

20

30

40

【図 9 A】

【図 9 B】

50

【図 9 C】

【図 9 D】

10

20

30

40

【図 10 A】

【図 10 B】

50

【図 10C】

10

20

30

40

50

---

フロントページの続き

ロード 1678

(72)発明者 リンカーン シー ジョリー

アメリカ合衆国 ユタ州 84104 ソルトレイクシティ サウス パイオニア ロード 1678

(72)発明者 クリストファー デイヴィッド ギンツトン

アメリカ合衆国 ユタ州 84104 ソルトレイクシティ サウス パイオニア ロード 1678

審査官 三坂 敏夫

(56)参考文献 特開平03-051976 (JP, A)

特開2006-318074 (JP, A)

特開2007-018401 (JP, A)

特開2018-055598 (JP, A)

特開2018-049813 (JP, A)

欧州特許出願公開第01840964 (EP, A1)

特開2009-266143 (JP, A)

特開平8-240884 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G06F 15/78

G06F 21/70