(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6533129号

(P6533129)

(45) 発行日 令和1年6月19日(2019.6.19)

(24) 登録日 令和1年5月31日(2019.5.31)

(51) Int.Cl.

G 11 C 15/04 (2006.01)

F 1

G 11 C 15/04 631M

G 11 C 15/04 631E

請求項の数 16 (全 43 頁)

(21) 出願番号 特願2015-168522 (P2015-168522)

(22) 出願日 平成27年8月28日 (2015.8.28)

(65) 公開番号 特開2017-45495 (P2017-45495A)

(43) 公開日 平成29年3月2日 (2017.3.2)

審査請求日 平成30年5月10日 (2018.5.10)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 渡邊 直也

東京都江東区豊洲三丁目2番24号 ルネ

サスエレクトロニクス株式会社内

(72) 発明者 伊賀上 太

東京都小平市上水本町五丁目20番1号

ルネサスシステムデザイン株式会社内

審査官 堀田 和義

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が T C A M (Ternary Content Addressable Memory) セルアレイを含む複数のサブアレイを備え、

各前記サブアレイは、前記 T C A M セルアレイの行ごとに格納された複数のデータのうち、入力されたサーチデータの対応部分に一致するものを検索し、前記行ごとに一致または不一致という検索結果を出力し、

各前記サブアレイは、前記 T C A M セルアレイの全てのデータがドントケアであることに基づいて検索動作前にあらかじめ設定された、対応する第 1 の制御信号が活性化されている場合には、前記 T C A M セルアレイについて検索を行わずに、一致という検索結果を前記行ごとに出力する、半導体装置。

## 【請求項 2】

各前記サブアレイは、

前記 T C A M セルアレイの行にそれぞれ設けられ、対応する行の各 T C A M セルが接続された複数のマッチ線と、

前記 T C A M セルアレイの列にそれぞれ設けられた複数のサーチ線と、

検索時に、前記複数のサーチ線に前記サーチデータの対応部分を供給するサーチ線ドライバと、

前記複数のマッチ線にそれぞれ対応し、各々が検索時に、対応するマッチ線の電位に従つて検索結果を出力する複数のマッチアンプと、

10

20

前記複数のマッチ線にそれぞれ対応し、各々が検索時に、対応するマッチ線をプリチャージする複数のプリチャージ回路と、

制御論理回路とを含み、

前記制御論理回路は、前記第1の制御信号が活性化されている場合には、前記サーチ線ドライバおよび前記複数のプリチャージ回路が動作しないように制御し、

各前記マッチアンプは、前記第1の制御信号が活性化されている場合には、対応する前記マッチ線の電位によらず一致という検索結果を出力するように構成される、請求項1に記載の半導体装置。

#### 【請求項3】

各前記サブアレイは、前記第1の制御信号を出力する第1のレジスタを含む、請求項2に記載の半導体装置。 10

#### 【請求項4】

各前記サブアレイは、前記TCA Mセルアレイの行ごとに設けられ、各々が、第2の制御信号を出力する複数の第2のレジスタを含み、

前記マッチアンプは、対応する前記第2の制御信号が活性化されている場合には、前記第1の制御信号が活性化されていても、不一致という検索結果を出力するように構成される、請求項3に記載の半導体装置。

#### 【請求項5】

各前記サブアレイは、前記TCA Mセルアレイの行ごとに設けられ、各々が第3の制御信号を出力する複数の第3のレジスタを含み、 20

各前記プリチャージ回路は、対応する前記第3の制御信号が活性化されている場合には、前記第1の制御信号が活性化されていなくても、対応する前記マッチ線をプリチャージせず、

各前記マッチアンプは、対応する前記第3の制御信号が活性化されている場合には、前記第1の制御信号が活性化されていなくても、対応する前記マッチ線の電位によらず一致という検索結果を出力する、請求項3に記載の半導体装置。

#### 【請求項6】

各前記サブアレイは、

前記TCA Mセルアレイの行ごとに設けられ、各々が、第2の制御信号を出力する複数の第2のレジスタと、 30

前記TCA Mセルアレイの行ごとに設けられ、各々が、第3の制御信号を出力する複数の第3のレジスタとを含み、

各前記プリチャージ回路は、対応する前記第2および第3の制御信号の少なくとも一方が活性化されている場合には、前記第1の制御信号が活性化されていなくても、対応する前記マッチ線をプリチャージせず、

各前記マッチアンプは、対応する前記第2の制御信号が活性化されておらず、対応する前記第3の制御信号が活性化されている場合には、前記第1の制御信号が活性化されていなくても、対応する前記マッチ線の電位によらず一致という検出結果を出力し、

各前記マッチアンプは、対応する前記第2の制御信号が活性化されている場合には、前記第1の制御信号および対応する前記第3の制御信号のいずれかが活性化されていても、対応する前記マッチ線の電位によらず不一致という検出結果を出力する、請求項3に記載の半導体装置。 40

#### 【請求項7】

前記TCA Mセルアレイは、列方向に並ぶ第1のセルアレイと第2のセルアレイとに区分され、

前記サーチ線ドライバは、

前記第1のセルアレイに隣接して設けられ、前記第1のセルアレイに前記サーチデータの対応部分を供給する第1のドライバと、

前記第2のセルアレイに隣接して設けられ、前記第2のセルアレイに前記サーチデータの対応部分を供給する第2のドライバとを含む、請求項2に記載の半導体装置。 50

**【請求項 8】**

前記半導体装置は、

各前記サブアレイを構成する前記 T C A M セルアレイの行ごとにデータを書込む際に、共通のマッチ線に接続された全ての T C A M セルにドントケアが書込まれた特定行があるか否かを判定するデータ判定回路をさらに備え、

前記データ判定回路は、前記特定行に対応する前記第 3 の制御信号が活性化されるように、前記特定行に対応する前記第 3 のレジスタの値を設定する、請求項 5 に記載の半導体装置。

**【請求項 9】**

各前記サブアレイは、さらに、

10

前記 T C A M セルアレイの行ごとに設けられ、各々が、第 3 の制御信号を出力する複数の第 3 のレジスタと、

前記複数の第 3 のレジスタからそれぞれ出力された複数の前記第 3 の制御信号が全て活性化されている場合に、活性化された前記第 1 の制御信号を生成して出力する論理回路とを含む、請求項 2 に記載の半導体装置。

**【請求項 10】**

前記制御論理回路は、各前記プリチャージ回路の動作を制御するためのプリチャージイネーブル信号を生成し、

各前記サブアレイは、前記 T C A M セルアレイの複数行ごとに設けられ、各々が、前記プリチャージイネーブル信号および前記第 1 の制御信号を整形し、整形後の前記プリチャージイネーブル信号および前記第 1 の制御信号を前記複数行に対応する前記プリチャージ回路および前記マッチアンプにそれぞれ供給する複数のバッファアンプ部をさらに含み、

20

各前記バッファアンプ部は、対応する前記複数行に設けられた前記第 3 のレジスタが出力する前記第 3 の制御信号が全て活性化されている場合には、出力する整形後の前記第 1 の制御信号を活性化とともに、出力する整形後の前記プリチャージイネーブル信号を非活性化することによって対応する各前記プリチャージ回路が動作しないように制御する、請求項 5 に記載の半導体装置。

**【請求項 11】**

前記半導体装置への電源供給後、いずれの前記サブアレイの前記 T C A M セルにもデータが書き込まれていない状態において、各前記サブアレイの前記第 1 の制御信号および複数の前記第 2 の制御信号がいずれも活性状態となるように、各前記第 1 のレジスタおよび各前記第 2 のレジスタの値が初期設定される、請求項 4 に記載の半導体装置。

30

**【請求項 12】**

前記半導体装置への電源供給後、いずれの前記サブアレイの前記 T C A M セルにもデータが書き込まれていない状態において、各前記サブアレイの前記第 1 の制御信号および複数の前記第 3 の制御信号がいずれも活性状態となるように、各前記第 1 のレジスタおよび各前記第 3 のレジスタの値が初期設定される、請求項 5 に記載の半導体装置。

**【請求項 13】**

前記半導体装置への電源供給後、いずれの前記サブアレイの前記 T C A M セルにもデータが書き込まれていない状態において、各前記サブアレイの前記第 1 の制御信号および各前記サブアレイの前記第 2 の制御信号および複数の前記第 3 の制御信号がいずれも活性状態となるように、各前記第 1 のレジスタおよび各前記第 2 のレジスタおよび各前記第 3 のレジスタの値が初期設定される、請求項 6 に記載の半導体装置。

40

**【請求項 14】**

各前記サブアレイの前記 T C A M セルアレイへの書き込みデータの配列順および前記データの配列順を定められた規則に従って変更するデータ配列変更回路をさらに備える、請求項 1 に記載の半導体装置。

**【請求項 15】**

互いに行方向に並び、共通のエントリに対応する複数の前記サブアレイは、バイ二分検索方式で順番に検索を行うように構成され、

50

各前記サブアレイは、最初のステージで検索を行うサブアレイを除いて、前記T C A Mセルアレイの行ごとに設けられ、各々が、前ステージのサブアレイの対応する行の検索結果を格納する複数のDフリップフロップを含み、

前記複数のDフリップフロップが設けられた各前記サブアレイにおいて、各前記プリチャージ回路は、対応する前記Dフリップフロップに不一致の検索結果が格納されている場合には、対応する前記マッチ線をプリチャージせず、

前記複数のDフリップフロップが設けられた各前記サブアレイにおいて、各前記マッチアンプは、対応する前記Dフリップフロップに不一致の検索結果が格納されている場合には、前記第1の制御信号が活性化されていても、不一致の検索結果を出力するように構成される、請求項2に記載の半導体装置。 10

#### 【請求項16】

前記サブアレイから出力された検索結果に基づいて、前記サーチデータの検索結果を出力するプライオリティ・エンコーダをさらに備える、請求項1に記載の半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この発明は、半導体装置に関し、たとえば、T C A M (Ternary Content Addressable Memory)装置を備えた半導体装置に好適に用いられるものである。

##### 【背景技術】

##### 【0002】

連想メモリまたはC A M (内容参照メモリ:Content Addressable Memory)と呼ばれる記憶装置は、記憶しているデータワードの中から検索ワードに一致しているものを検索し、一致しているデータワードが見つかった場合は、そのアドレスを出力するものである。 20

##### 【0003】

C A MにはB C A M (Binary CAM)とT C A M (Ternary CAM)とがある。B C A Mの各メモリセルは“0”か“1”かのいずれかの情報を記憶する。一方、T C A Mの場合には、各メモリセルは、“0”および“1”の他に“ドントケア(Don't Care)”の情報を記憶可能である。“ドントケア”は“0”および“1”的どちらでも良いことを示す。

##### 【0004】

T C A M装置は、インターネットなどのネットワーク用のルータにおいてアドレス検索およびアクセス制御のために幅広く利用されている。大容量化に対応するために、T C A M装置は、通常、複数のサブアレイを有し、各サブアレイに対して同時にサーチ動作が実行される構成となっている。たとえば、非特許文献1は、ビルディングブロック(Building Block)と呼ばれるサブアレイがワード線方向に8個、ビット線方向に4個配列されている。 30

##### 【0005】

T C A M装置は、入力サーチデータ(入力パケット)とT C A Mセルデータとを一斉に比較することができるので、全ての検索用途においてR A M (Random Access Memory)よりも高速である。しかしながら、検索時にサーチ電流が発生するために消費電力の増大が問題となっている。 40

##### 【0006】

特開2003-272386号公報(特許文献1)は、低消費電力化のためにマッチ線方向に並ぶ複数のサブアレイがバイオペライン方式で連結された構成のT C A M装置を開示する。この文献のT C A M装置では、後続するステージでは、前ステージで一致したエントリのみ検索が実行される。

#### 【先行技術文献】

##### 【特許文献】

##### 【0007】

【特許文献1】特開2003-272386号公報

##### 【非特許文献】

**【0008】**

【非特許文献1】H. Miyatake 他2名、"A design for high-speed low-power CMOS fully parallel content-addressable memory macros"、IEEE J. Solid-State Circuits, Vol.36, pp. 956-968, June 2001

**【発明の概要】****【発明が解決しようとする課題】****【0009】**

T C A M 装置では、ドントケアに設定された T C A M セルがある範囲に固まって存在する場合がある。たとえば、サブアレイの一部のマッチ線に接続された T C A M セルが全てドントケアに設定されていることがしばしば生じる。より顕著な場合には、サブアレイを構成する全 T C A M セルがドントケアに設定されている場合もある。このような場合には、サーチ結果が自明（サーチデータによらず必ずヒット（一致）になる）であるので、サーチ動作のために電流を無駄に消費してしまう。

**【0010】**

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

**【課題を解決するための手段】****【0011】**

一実施形態による半導体装置は、各々が T C A M セルアレイを含む複数のサブアレイを備える。各サブアレイは、入力サーチデータのうちの対応部分の検索を行う。各サブアレイは、対応する第1の制御信号が活性化されている場合には、検索を行わずに、一致という検索結果をエントリごとに output する。

**【発明の効果】****【0012】**

上記の実施形態によれば、T C A M 装置の消費電流を低減することができる。

**【図面の簡単な説明】****【0013】**

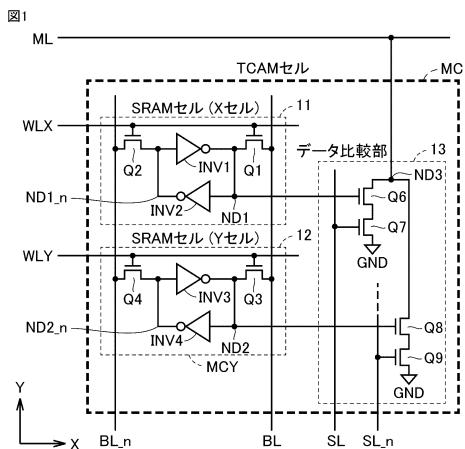

【図1】T C A M セルの構成の一例を示す回路図である。

【図2】図1のXセルおよびYセルの記憶内容とT C A M セルデータとの対応関係を表形式で示す図である。

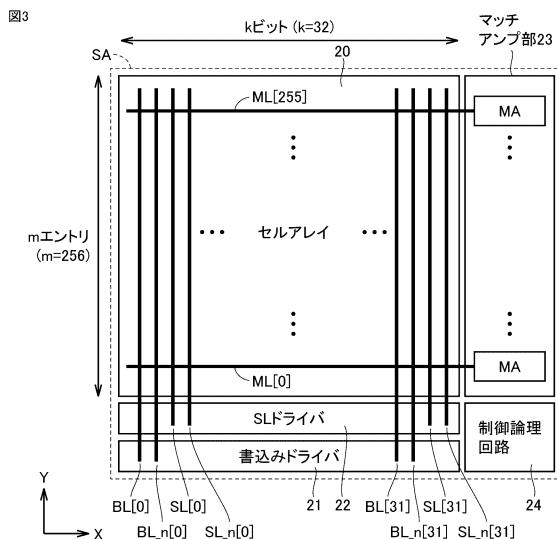

【図3】T C A M 装置を構成する1つのサブアレイの構成を示すブロック図である。

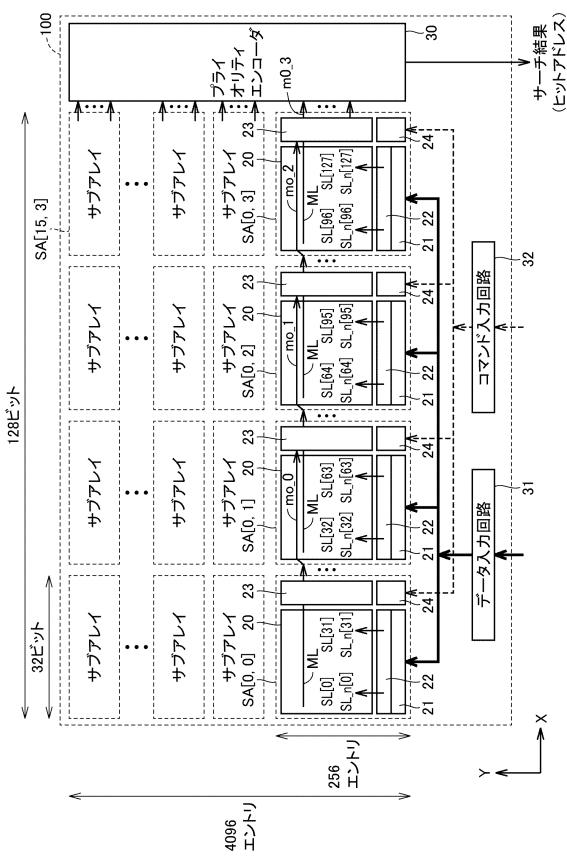

【図4】T C A M 装置の構成を示すブロック図である。

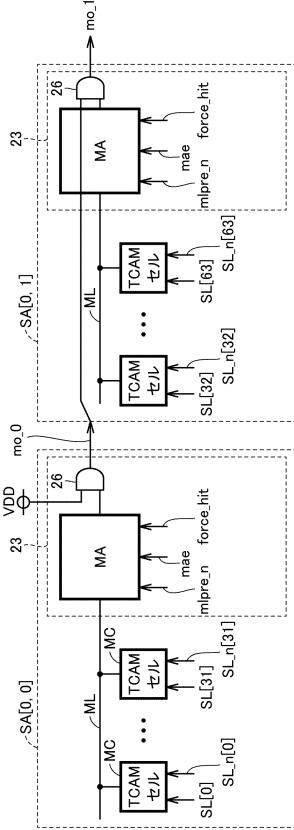

【図5】各マッチアンプの検出結果のAND演算について説明するための図である。

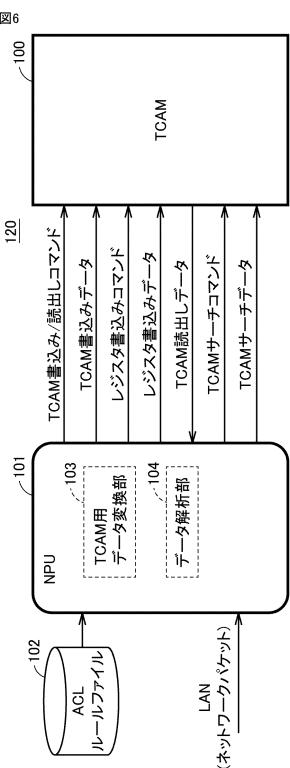

【図6】データ検索システムの全体構成を示すブロック図である。

【図7】A C L ルールファイルの一例を表形式で示す図である。

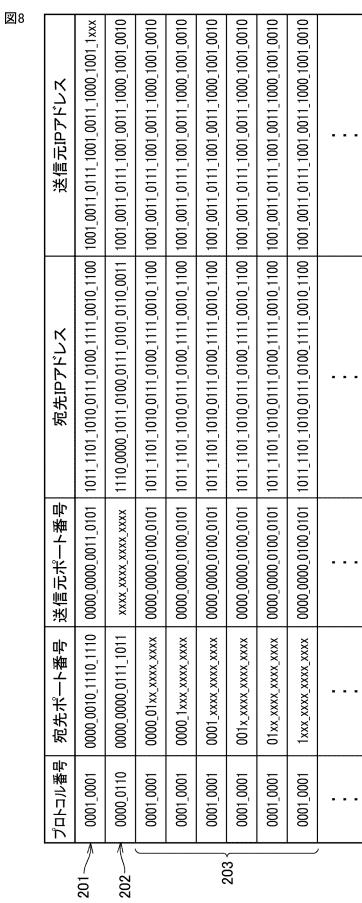

【図8】図7のA C L を変換することによって得られたT C A M 用データの一例を示す図である。

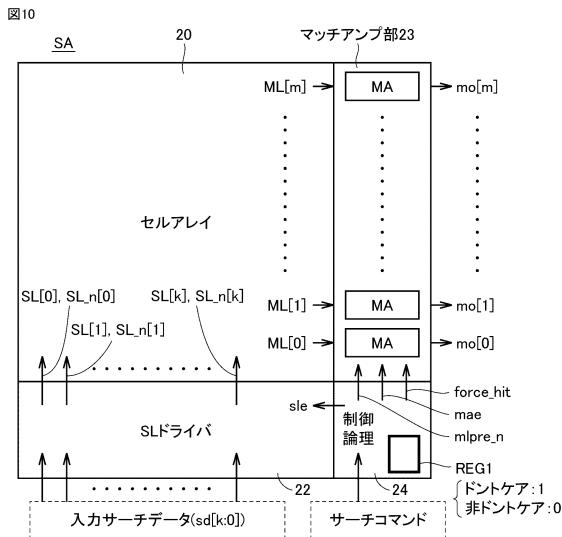

【図9】A C L に基づく変換データが書き込まれたT C A M 装置の記憶状態を模式的に示す図である。

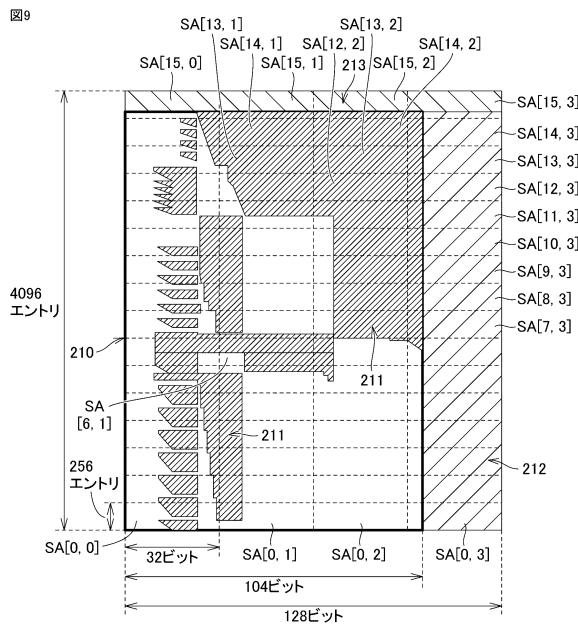

【図10】第1の実施形態によるT C A M 装置において、サブアレイの構成を示すブロック図である。

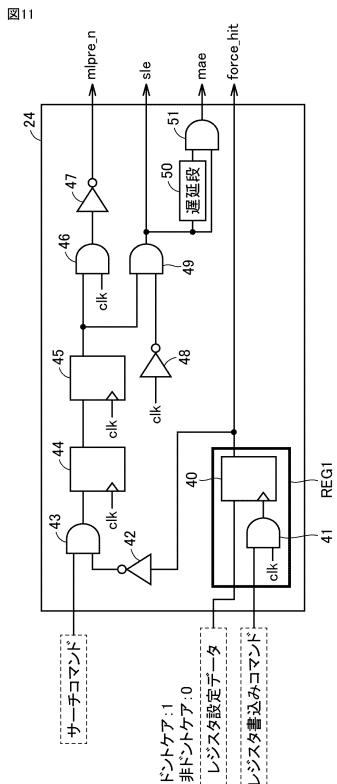

【図11】図10の制御論理回路のうち、サーチ動作に関係する部分の構成を示す回路図である。

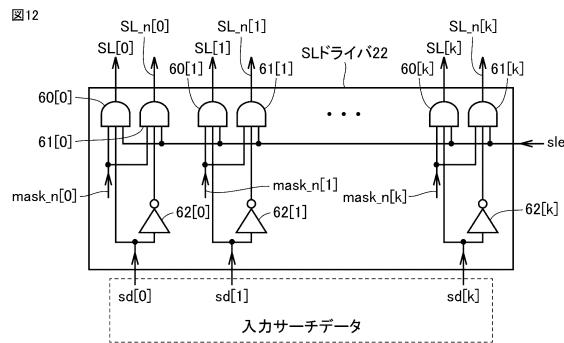

【図12】図10のサーチ線ドライバの構成の一例を示す回路図である。

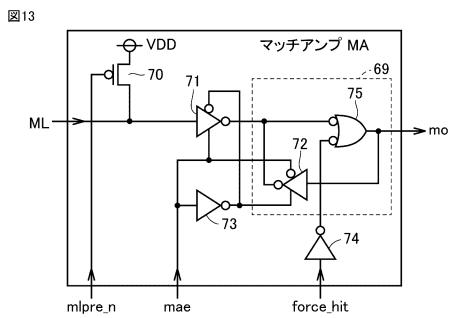

【図13】図10のマッチアンプの構成の一例を示す回路図である。

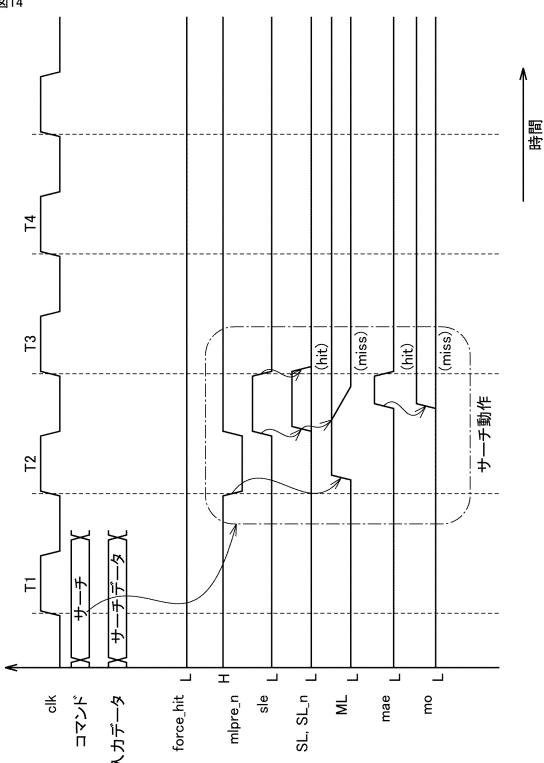

【図14】図10のサブアレイに設けられたレジスタREG1に非ドントケアを表す“0”が格納されているときのサーチ動作を示すタイミング図である。

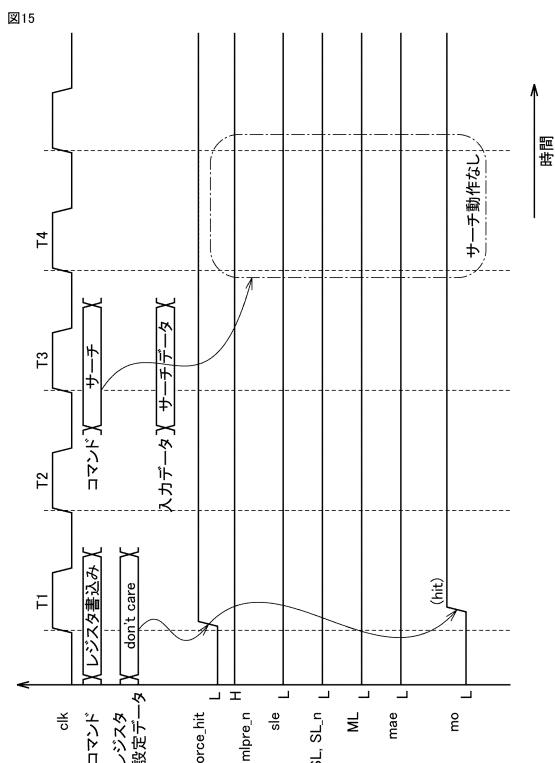

【図15】図10のサブアレイに設けられたレジスタREG1にドントケアを表すデータ“1”が格納されているときのサーチ動作を示すタイミング図である。

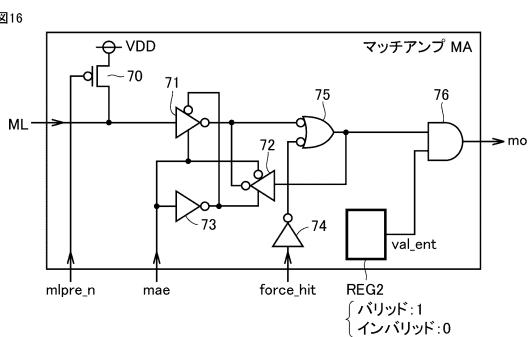

【図16】図10のマッチアンプの変形例を示す回路図である。

10

20

30

40

50

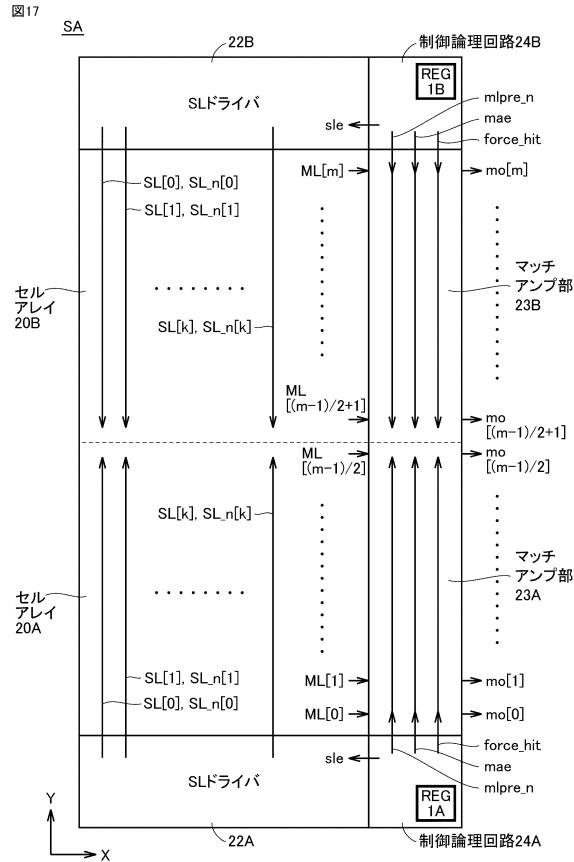

【図17】第2の実施形態によるTCA M装置において、サブアレイSAの構成を示すブロック図である。

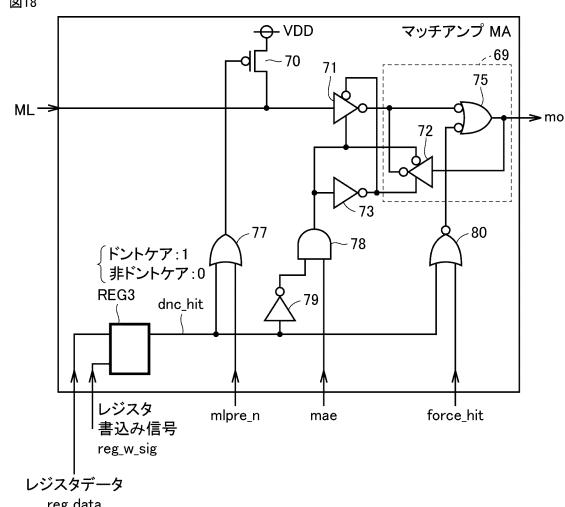

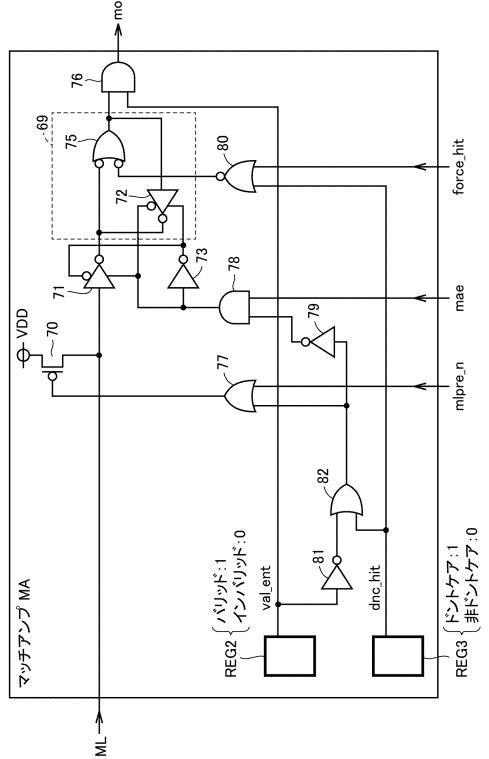

【図18】第3の実施形態によるTCA M装置において、マッチアンプMAの構成を示す回路図である。

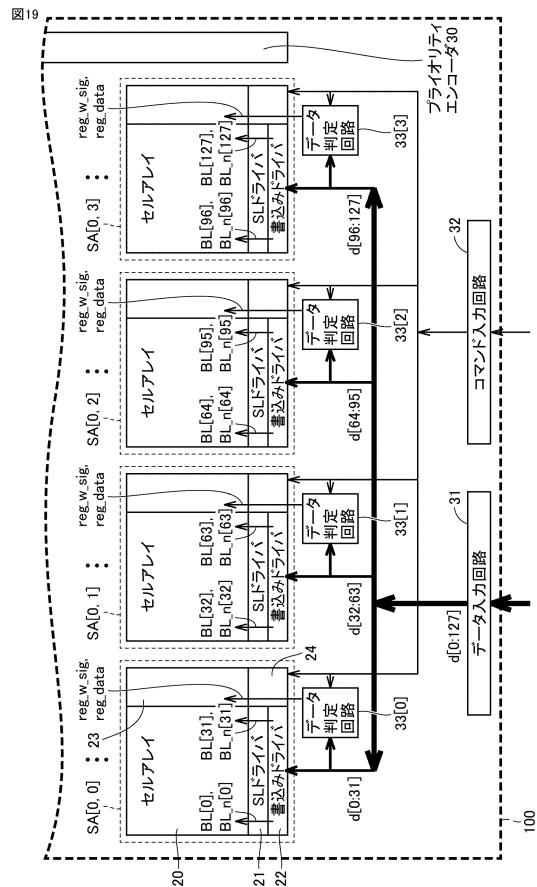

【図19】第3の実施形態によるTCA M装置の構成を示すブロック図である。

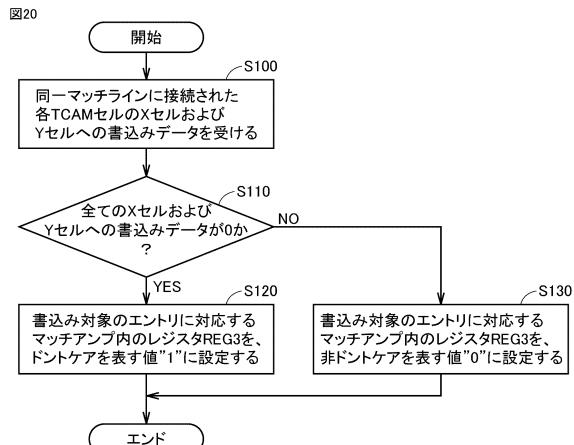

【図20】図19のデータ判定回路33の動作を示すフローチャートである。

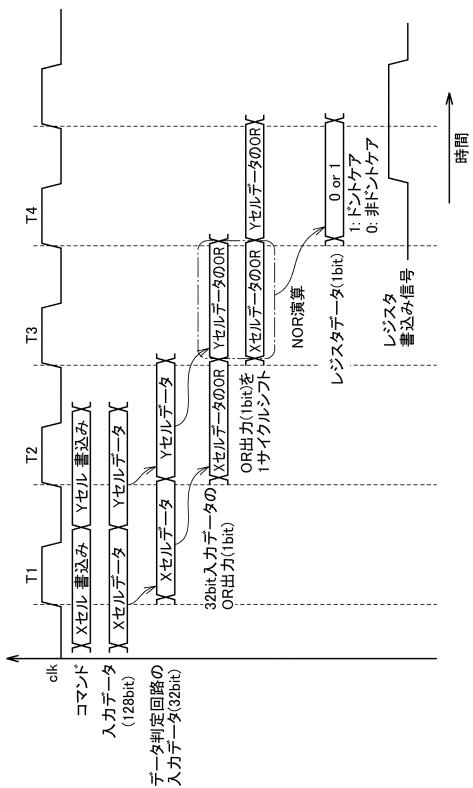

【図21】第3の実施形態のTCA M装置において、図18のレジスタREG3へのデータ書き込み手順を示すタイミング図である。

【図22】図18のマッチアンプMAの変形例を示すブロック図である。

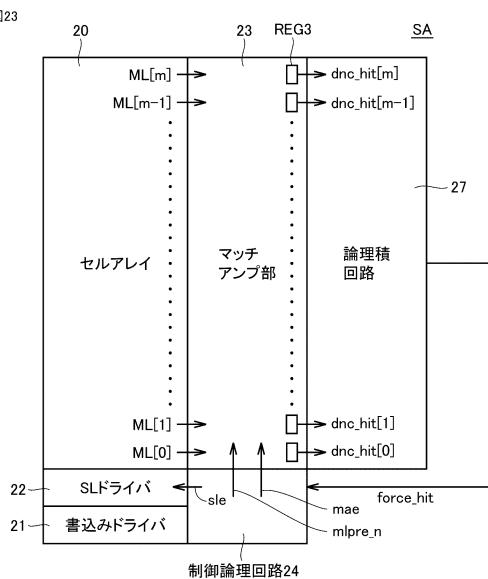

【図23】第4の実施形態によるTCA M装置において、サブアレイの構成を模式的に示すブロック図である。 10

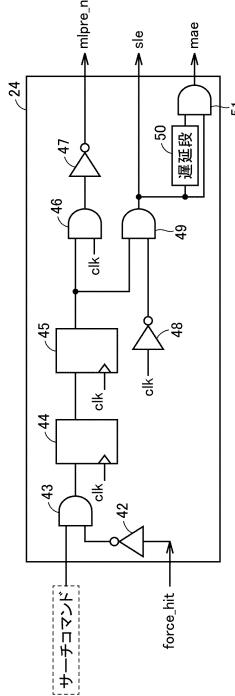

【図24】図23の制御論理回路24において、検索動作に関係する部分の構成を示す回路図である。

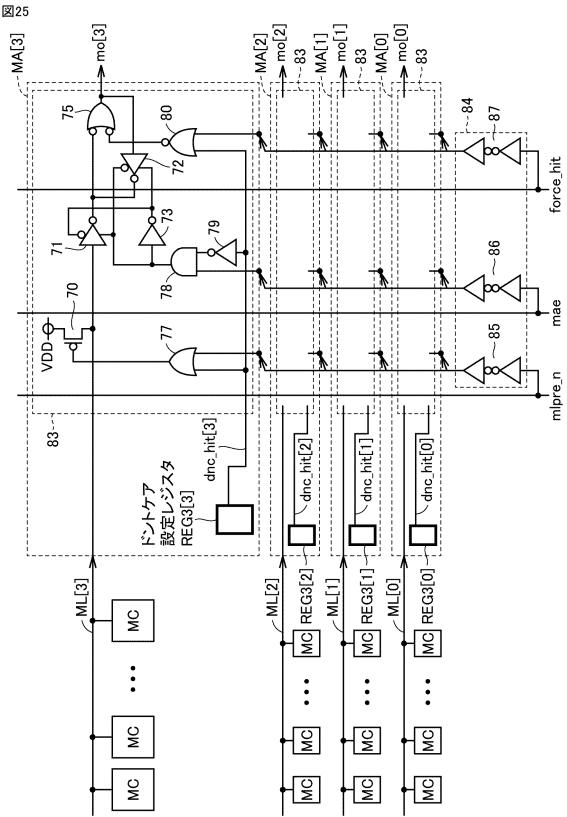

【図25】制御論理回路24からの出力信号のために用いられるバッファアンプの配置について説明するための図である。

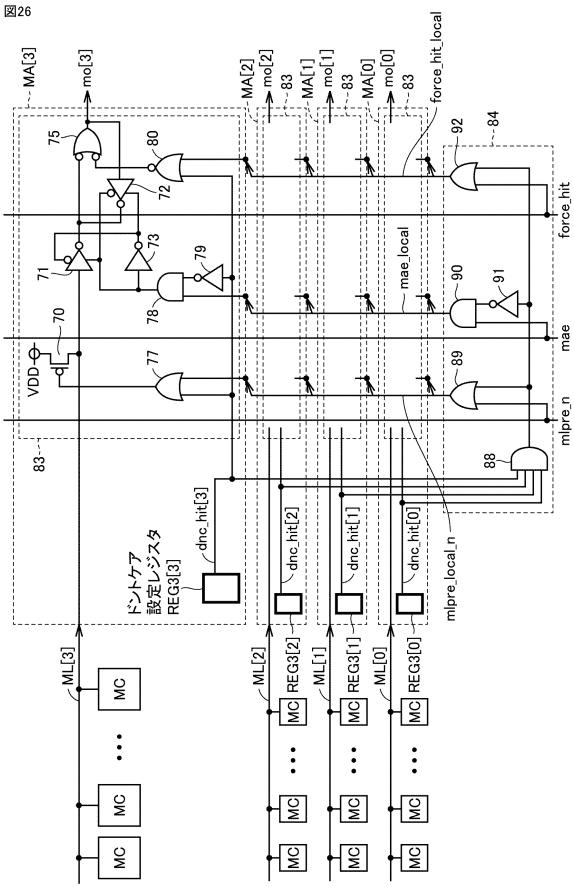

【図26】第5の実施形態のTCA M装置において、バッファアンプ部の構成を説明するための図である。

【図27】電源立ち上げ後において、各レジスタREG1, REG2, REG3へのデータ書き込みの手順について説明するための図である。 20

【図28】入力データの配列変換について説明するための図である。

【図29】第7の実施形態の検索システムの構成を示すブロック図である。

【図30】データ配列変換の対象となるTCA M用データの一例が書き込まれたTCA M装置の記憶状態を模式的に示す図である。

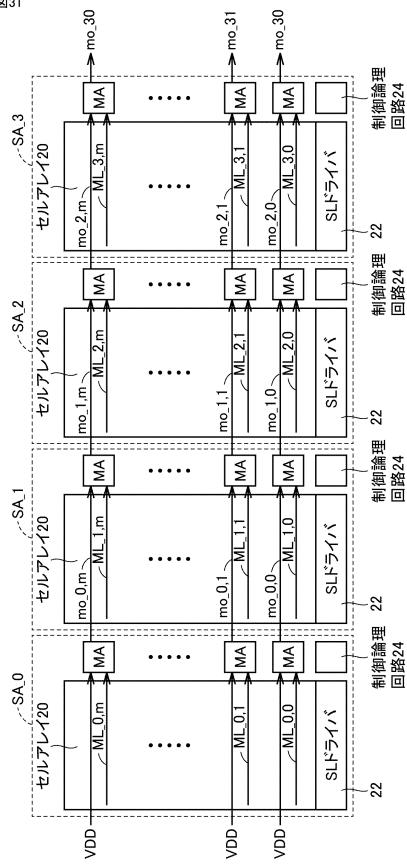

【図31】第8の実施形態によるTCA M装置の構成を示すブロック図である。

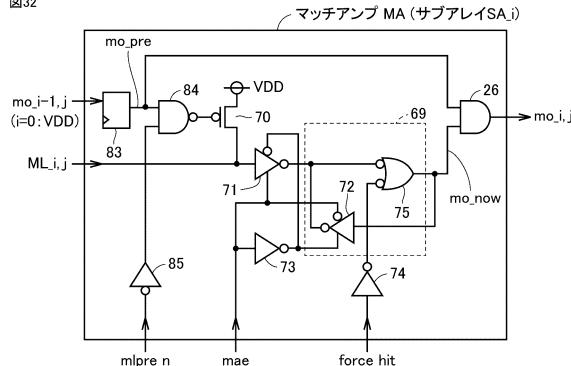

【図32】図31のマッチアンプMAの構成例を示す回路図である。

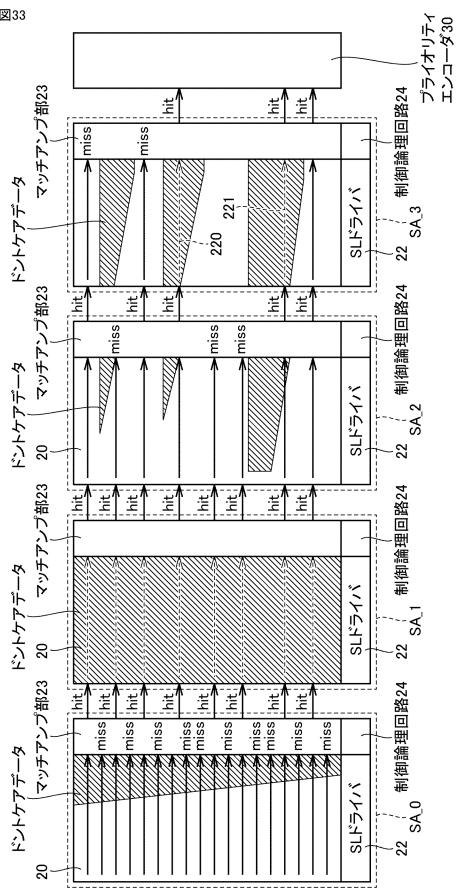

【図33】図31のTCA M装置の動作を説明するための図である。

#### 【発明を実施するための形態】

##### 【0014】

以下、各実施形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰返さない。 30

##### 【0015】

<各実施形態に共通する構成>

##### [TCA Mセルの構成]

図1は、TCA Mセルの構成の一例を示す回路図である。図1を参照して、TCA Mセル(メモリセルMCとも称する)は、2個のSRAMセル(Static Random Access Memory Cell)11, 12と、データ比較部13とを含む。SRAMセル11をXセルとも称し、SRAMセル12をYセルとも称する。Xセル11は、内部の記憶ノード対ND1, ND1\_nに互いに相補となる(一方が“1”的とき他方が“0”となる)1ビット(bit)のデータを記憶する。Yセル12は、内部の記憶ノード対ND2, ND2\_nに互いに相補となる1ビットのデータを記憶する。 40

##### 【0016】

TCA Mセルは、ビット線対BL, BL\_n、サーチ線対SL, SL\_n、マッチ線ML、およびワード線WLX, WLYと接続される。ビット線対BL, BL\_nは、図3のTCA Mセルアレイ20の列方向(Y方向)に延在し、列方向に配列された複数のTCA Mセルによって共有される。サーチ線対SL, SL\_nは、TCA Mセルアレイ20の列方向(Y方向)に延在し、列方向に配列された複数のTCA Mセルによって共有される。マッチ線MLは、TCA Mセルアレイ20の行方向(X方向)に延在し、行方向に配列された複数のTCA Mセルによって共有される。ワード線WLX, WLYは、TCA Mセルアレイ20の行方向(X方向)に延在し、行方向に配列された複数のTCA Mセルによって共有される。 50

## 【0017】

Xセル11は、インバータINV1, INV2と、NチャネルMOS (Metal Oxide Semiconductor) ドレインQ1, Q2とを含む。インバータINV1は、記憶ノードND1\_nから記憶ノードND1へ向かう方向が順方向となるように、記憶ノードND1と記憶ノードND1\_nの間に接続される。インバータINV2は、INV1と並列かつ逆方向に接続される。MOSトランジスタQ1は、記憶ノードND1とビット線BLとの間に接続される。MOSトランジスタQ2は、記憶ノードND1\_nとビット線BL\_nとの間に接続される。MOSトランジスタQ1, Q2のゲートは、ワード線WLXと接続される。

## 【0018】

Yセル12は、インバータINV3, INV4と、MOS (Metal Oxide Semiconductor) ドレインQ3, Q4とを含む。インバータINV3は、記憶ノードND2\_nから記憶ノードND2へ向かう方向が順方向となるように、記憶ノードND2と記憶ノードND2\_nの間に接続される。インバータINV4は、INV3と並列かつ逆方向に接続される。MOSトランジスタQ3は、記憶ノードND2とビット線BLとの間に接続される。MOSトランジスタQ4は、記憶ノードND2\_nとビット線BL\_nとの間に接続される。MOSトランジスタQ3, Q4のゲートは、ワード線WLYと接続される。

## 【0019】

データ比較部13は、NチャネルMOSトランジスタQ6～Q9を含む。MOSトランジスタQ6, Q7はマッチ線MLとの接続点であるノードND3と接地ノードGNDとの間に直列に接続される。MOSトランジスタQ8, Q9は、ノードND3と接地ノードGNDとの間に直列に、かつ、直列接続されたMOSトランジスタQ6, Q7の全体と並列に接続される。MOSトランジスタQ6, Q8のゲートは、記憶ノードND1, ND2とそれぞれ接続される。MOSトランジスタQ7, Q9のゲートは、サーチ線SL, SL\_nとそれぞれ接続される。

## 【0020】

図2は、図1のXセルおよびYセルの記憶内容とTCAMセルデータとの対応関係を表形式で示す図である。

## 【0021】

図2および図3を参照して、TCAMセルは、2ビットのSRAMセルを用いて、“0”、“1”、“x”(ドントケア: don't care)の3値を格納することができる。具体的に、Xセル11の記憶ノードND1に“1”が格納され、Yセル12の記憶ノードND2に“0”が格納されているとき、TCAMセルには“0”が格納されているとする。Xセル11の記憶ノードND1に“0”が格納され、Yセル12の記憶ノードND2に“1”が格納されているとき、TCAMセルには“1”が格納されているとする。Xセル11の記憶ノードND1に“0”が格納され、Yセル12の記憶ノードND2に“0”が格納されているとき、TCAMセルには“x”(ドントケア)が格納されているとする。Xセル11の記憶ノードND1に“1”が格納され、Yセル12の記憶ノードND2に“1”が格納されている場合は使用しない。

## 【0022】

上記のTCAMセルの構成によれば、サーチデータが“1”(すなわち、サーチ線SLが“1”、かつ、サーチ線SL\_nが“0”)であり、TCAMデータが“0”(記憶ノードND1が“1”、かつ、記憶ノードND2が“0”)である場合には、MOSトランジスタQ6, Q7がオン状態となるために、プリチャージされたマッチ線MLの電位が接地電位まで引き抜かれる。サーチデータが“0”(すなわち、サーチ線SLが“0”、かつ、サーチ線SL\_nが“1”)であり、TCAMデータが“1”(記憶ノードND1が“0”、かつ、記憶ノードND2が“1”)である場合には、MOSトランジスタQ8, Q9がオン状態となるために、プリチャージされたマッチ線MLの電位が接地電位まで引き抜かれる。すなわち、サーチデータとTCAMデータとが不一致の場合には、マッチ線MLの電位は接地電位まで引き抜かれる。

10

20

30

40

50

**【0023】**

逆に、入力されたサーチデータが“1”であり、かつ、T C A Mデータが“1”または“x”的場合、もしくは、サーチデータが“0”であり、かつ、T C A Mデータが“0”または“X”的場合（すなわち、両者が一致する場合）、プリチャージされたマッチ線M Lの電位（電源電位V D D レベル）は維持される。

**【0024】**

上記のように、T C A Mでは、1つのエントリ（行）に対応するマッチ線M Lに接続された全てのT C A Mセルのデータが入力サーチデータと一致しない限り、マッチ線M Lに蓄えられた電荷が引き抜かれる。このため、T C A Mでの検索は高速であるが、消費電流が大きいという問題がある。

10

**【0025】****[サブアレイの構成]**

図3は、T C A M装置を構成する1つのサブアレイの構成を示すブロック図である。図3を参照して、サブアレイS Aは、T C A Mセルアレイ2 0（単にセルアレイとも称する）と、書き込みドライバ2 1と、サーチ線（S L）ドライバ2 2と、マッチアンプ部2 3と、制御論理回路2 4とを含む。サブアレイS Aは、さらに、図1のワード線W L X, W L Yを駆動するためのワード線ドライバ（不図示）を含む。

**【0026】**

セルアレイ2 0は、行列状（m行；k列）に配列されたT C A Mセルを含む。図3のセルアレイ2 0は、行数（エントリ数）mが2 5 6であり、列数（ビット数）kが3 2の場合が示されている。

20

**【0027】**

セルアレイ2 0の各列に対応して、k個（k = 3 2）のビット線対（B L [ 0 ] , B L \_ n [ 0 ] から B L [ k - 1 ] , B L \_ n [ k - 1 ] まで）と、k個（k = 3 2）のサーチ線対（S L [ 0 ] , S L \_ n [ 0 ] から S L [ k - 1 ] , S L \_ n [ k - 1 ] まで）とが設けられる。セルアレイ2 0の各行に対応して、m本（m = 2 5 6）のマッチ線（M L [ 0 ] から M L [ m - 1 ] まで）と、図示しないm本のXセル用のワード線（W L X [ 0 ] から W L X [ m - 1 ] まで）と、図示しないm本のYセル用のワード線（W L Y [ 0 ] から W L Y [ m - 1 ] まで）とが設けられている。

**【0028】**

30

書き込みドライバ2 1は、書き込み時に、ビット線対B L , B L \_ nを介して各T C A Mセルに書き込みデータを供給する。サーチ線ドライバ2 2は、検索時に、サーチ線対S L , S L \_ nを介して各T C A Mセルにサーチデータを供給する。制御論理回路2 4は、サブアレイS A全体の動作を制御する。たとえば、制御論理回路2 4は、検索時には、サーチコマンドを受け取り、サーチ線ドライバ2 2と、マッチアンプ部2 3に制御信号を出力することによって、サーチ線ドライバ2 2、マッチアンプ部2 3、およびプリチャージ回路の動作を制御する。

**【0029】**

マッチアンプ部2 3は、セルアレイの行にそれぞれ対応する複数のマッチアンプM Aを含む。マッチアンプM Aは、検索時に、対応するマッチ線M Lの電位に基づいて、対応するT C A Mセルデータと入力サーチデータの対応部分とが一致するか否かを検出する。この実施形態では、マッチアンプM Aは、検索時に対応するマッチ線M Lをプリチャージするためのプリチャージ回路を含む。

40

**【0030】****[T C A Mの構成]**

図4は、T C A M装置の構成を示すブロック図である。図4を参照して、T C A M装置1 0 0は、行列状に配列された複数のサブアレイS Aと、プライオリティ・エンコーダ3 0と、データ入力回路3 1と、コマンド入力回路3 2とを含む。

**【0031】**

図4のT C A M装置が実現している検索テーブルサイズは、1エントリ（1行）のビッ

50

ト長が 128 ビット (bit) であり、総エントリ数が 4096 エントリ (entry) である。T C A M 装置 100 は、16 行 4 列のサブアレイ S A [ 0 , 0 ] ~ S A [ 15 , 3 ] に分割されている。各サブアレイ S A のサイズは、総エントリ数は 256 エントリ、1 エントリのビット長は 32 ビットになる。これらの数字は一例であって、T C A M 装置の構成はこれに限られるものでない。

#### 【 0032 】

すでに説明したサーチ線対 S L , S L\_n 、ビット線対 B L , B L\_n 、マッチ線 M L 、およびワード線は、各サブアレイごとに配設されている。たとえば、サブアレイ S A [ 0 , 0 ] には、サーチ線対 S L [ 0 ] , S L\_n [ 0 ] からサーチ線対 S L [ 31 ] , S L\_n [ 31 ] までが設けられる。<sup>10</sup> サブアレイ S A [ 0 , 1 ] には、サーチ線対 S L [ 32 ] , S L\_n [ 32 ] からサーチ線対 S L [ 63 ] , S L\_n [ 63 ] までが設けられる。サブアレイ S A [ 0 , 2 ] には、サーチ線対 S L [ 64 ] , S L\_n [ 64 ] からサーチ線対 S L [ 95 ] , S L\_n [ 95 ] までが設けられる。サブアレイ S A [ 0 , 3 ] には、サーチ線対 S L [ 96 ] , S L\_n [ 96 ] からサーチ線対 S L [ 127 ] , S L\_n [ 127 ] までが設けられる。

#### 【 0033 】

図 4 において、1 エントリのサーチデータ全体および 1 エントリの T C A M セルデータ（書き込みデータ）全体に対して、マッチ線 M L は 32 ビット単位で 4 分割された構成になっている。このため、マッチアンプ部 23 には、図 5 で説明するように、各マッチアンプ M A の検出結果の論理積をとるための A N D ゲート（図 5 の参照符号 26）が行ごとに設けられている。<sup>20</sup>

#### 【 0034 】

データ入力回路 31 は、データ書込み時には、書き込みデータを外部（たとえば、図 6 のネットワーク・プロセッサ・ユニット）から受信し、受信した書き込みデータを対応するサブアレイの S A の書き込みドライバ 21 に出力する。データサーチ時には、サーチデータを外部から受信し、受信したサーチデータを対応するサブアレイ S A のサーチ線ドライバ 22 に出力する。

#### 【 0035 】

コマンド入力回路 32 は、書き込みコマンド、サーチコマンドなどの各種コマンドを外部から受信し、受信したコマンドを対応するサブアレイ S A の制御論理回路 24 に出力する。<sup>30</sup>

#### 【 0036 】

プライオリティ・エンコーダ 30 は、各エントリごとのサーチ結果（入力サーチデータと T C A M データとが一致したか否か）を隣接するサブアレイ S A [ 0 , 3 ] , S A [ 1 , 3 ] , ... , S A [ 15 , 3 ] から受け取る。プライオリティ・エンコーダ 30 は、ヒットアドレス（サーチデータと一致した T C A M データが格納されているエントリアドレス）を出力する、複数のエントリがヒット（一致）した場合には、プライオリティ・エンコーダ 30 は、優先度の高いヒットエントリのアドレスを出力する。

#### 【 0037 】

[ 同一エントリの複数のマッチアンプの検出結果の A N D 演算について ]<sup>40</sup>

図 5 は、各マッチアンプの検出結果の A N D 演算について説明するための図である。図 5 では代表的にサブアレイ S A [ 0 , 0 ] , S A [ 0 , 1 ] の 1 つのエントリのみ示されているが、他のエントリおよび他のサブアレイについても同様である。

#### 【 0038 】

図 5 に示すように、各サブアレイ S A のマッチアンプ部 23 は、行ごとに、マッチアンプ M A の後段に設けられた A N D ゲート 26 を含む。ただし、プライオリティ・エンコーダ 30 から最も離れたサブアレイ S A [ 0 , 0 ] , [ 1 , 0 ] , ... に設けられた A N D ゲート 26 は、一方の入力ノードに “H” レベルの電位（電源電位 V D D ）が入力されることによって、バッファとして機能している。以下、図 4 および図 5 を参照して、サブアレイ S A [ 0 , 0 ] ~ S A [ 0 , 3 ] の 1 つのエントリを例に挙げて、A N D ゲート 26 の<sup>50</sup>

動作について説明する。

#### 【0039】

図4および図5を参照して、まず、サブアレイSA[0,0]～SA[0,3]の各々において、サーチ線対SL, SL\_nを介して入力されたサーチデータの対応部分と、TCAMセルデータとの比較が行われる。各サブアレイSAのマッチアンプMAは、対応するマッチ線MLの電位（入力サーチデータの対応部分とTCAMセルデータとが全て一致する場合：“H”レベル、少なくとも1つも不一致がある場合：“L”レベル）を検出する。

#### 【0040】

次に、サブアレイSA[0,0]のマッチアンプMAの検出結果は、サブアレイ[0,0]のマッチアンプ部に設けられたバッファとして用いられるANDゲート26を通過した後に、マッチアンプ出力信号mo\_0として、隣接するサブアレイSA[0,1]に転送される。サブアレイSA[0,1]のマッチアンプ部23に設けられたANDゲート26は、上記のマッチアンプ出力信号mo\_0と、サブアレイSA[0,1]のマッチアンプMAの検出結果との論理積を演算する。この演算結果は、マッチアンプ出力信号mo\_1として、隣接するサブアレイSA[0,2]に転送される。10

#### 【0041】

以下同様に、サブアレイSA[0,2]のマッチアンプ部23に設けられたANDゲート26は、上記のマッチアンプ出力信号mo\_1と、サブアレイSA[0,2]のマッチアンプMAの検出結果との論理積を演算する。この演算結果は、マッチアンプ出力信号mo\_2として、隣接するサブアレイSA[0,3]に転送される。サブアレイSA[0,3]のマッチアンプ部23に設けられたANDゲート26は、上記のマッチアンプ出力信号mo\_2と、サブアレイSA[0,3]のマッチアンプMAの検出結果との論理積を演算する。この演算結果は、マッチアンプ出力信号mo\_3として、プライオリティ・エンコーダ30に入力される。20

#### 【0042】

##### [データ検索システムの構成]

図6は、データ検索システムの全体構成を示すブロック図である。図6のブロック図は、インターネットなどのネットワーク用のルータに設けられたデータ検索システム120の構成を示す。30

#### 【0043】

ネットワークトラフィックの品質向上やネットワークセキュリティ管理を目的として、ネットワークシステムにはACL (Access Control List) が使われている。ACL ルールファイルはネットワーク管理者によって作成され、記憶装置102に格納される。

#### 【0044】

データ検索システム120は、ACLに記載されたルールのもとに、LAN (Local Area Network) を介して入力されたネットワークパケットが、通過を許可すべきパケットか通過を拒否するパケットなのかを即座に判断する。すなわち、データ検索システム120には、入力してきたパケットがACL内のどのルールに対応しているかを高速に検索する能力が必要となり、その処理には一般的にTCAM装置100を利用したデータ検索システム120が利用されている。40

#### 【0045】

具体的に、データ検索システム120は、TCAM装置100とNPU (Network Processor Unit) 101とを含む。NPU101は、TCAM装置100の動作を制御するためのものであり、TCAM装置100に対して、各種コマンド（書き込みコマンド、読み出しコマンド、サーチコマンドなど）および各種データ（書き込みデータ、サーチデータなど）を出力する。さらに、TCAM装置100には制御レジスタが設けられており、TCAM装置100は、この制御レジスタ用のコマンドおよびデータも出力する。

#### 【0046】

図6において、TCAM装置100のみが1つの半導体装置として構成されていてもよ50

いし、T C A M装置100とN P U (Network Processor Unit) 101とを併せて1つの半導体装置として構成されていてもよい。

#### 【0047】

ネットワーク管理者が作成したA C Lルールファイルは、N P U 1 0 1のデータ変換部103においてT C A M用のデータに変換され、変換後のデータがT C A M装置内部に格納される。T C A M装置100は、ネットワークパケットに含まれるI Pアドレスなどに基づくサーチデータと、T C A M装置内部に格納されている全てのデータとを同時に比較できる能力を有している。ただし、T C A Mの検索動作には大電流を発生してしまうデメリットがある。T C A M装置を搭載するネットワークシステムおよびデータ検索システムでは、低消費電力化が課題となっている。

10

#### 【0048】

[ A C L ルールファイルおよび対応する T C A M 用データの例について ]

図7は、A C L ルールファイルの一例を表形式で示す図である。図7では、A C L が3行のみ示されているが、実際にはより多数の行によってA C L ルールファイルが構成される。図7に示すように、A C L は、ネットワークから入力されたパケットのプロトコル番号、宛先ポート番号、送信元ポート番号、宛先I Pアドレス、および送信元I Pアドレスをチェックするためのものである。これらのチェック要素は、範囲指定が可能となっている。

#### 【0049】

たとえば、図7の参照符号201で示された行は、送信元I Pアドレスについて範囲指定されている。具体的に、“147.121.56.152/29”は、アドレス32ビットのうち上位29ビットを固定し、残り3ビットをマスク(wild card)とした表現である。すなわち、147.121.56.152～147.121.56.255の範囲が指定されている。宛先I Pアドレスについても、同様の範囲指定記載が可能である。

20

#### 【0050】

図7の参照符号202で示された行は、送信元ポート番号について範囲指定されている。すなわち、“0：65535”的表現によって、0～65535の範囲が指定されている。

#### 【0051】

図7の参照符号203で示された行は、宛先ポート番号が範囲指定されている。すなわち、“1024：65535”的表現によって、1024～65535の範囲が指定されている。

30

#### 【0052】

図8は、図7のA C Lを変換することによって得られたT C A M用データの一例を示す図である。

#### 【0053】

図8を参照して、1つのルールは、プロトコル番号が8ビット、宛先ポート番号が16ビット、送信元ポート番号が16ビット、宛先I Pアドレスが32ビット、送信元I Pアドレスが32ビットの合計104ビットのデータで構成される。図中の“x”は、ドントケア(don't care)データ(wild cardデータ)を示す。ドントケアデータは、“1”または“0”的どちらにでも一致するデータのことである。

40

#### 【0054】

図8の参照符号201, 202, 203で示された行の表記は、図7の参照符号201, 202, 203で示された行のA C L ルールにそれぞれ対応している。参照符号203で示すように、A C L ルールでは1行の範囲指定ルール(1024～65535)であったものが、T C A M用データに変換すると6行のデータになる場合がある。さらに、宛先ポート番号と送信元ポート番号などの複数の要素が範囲指定ルールとなった場合には、T C A Mに必要な行数がより一層増加してしまう。たとえば、宛先ポート番号と送信元ポート番号ともに1024～65535の領域指定ルールであるとすると、T C A M装置には36行のデータ領域が必要となる。したがって、A C L に領域指定ルールが多く含まれて

50

いる場合には、T C A M用データにはドントケア (don't care) データが多く含まれることが分かる。

#### 【 0 0 5 5 】

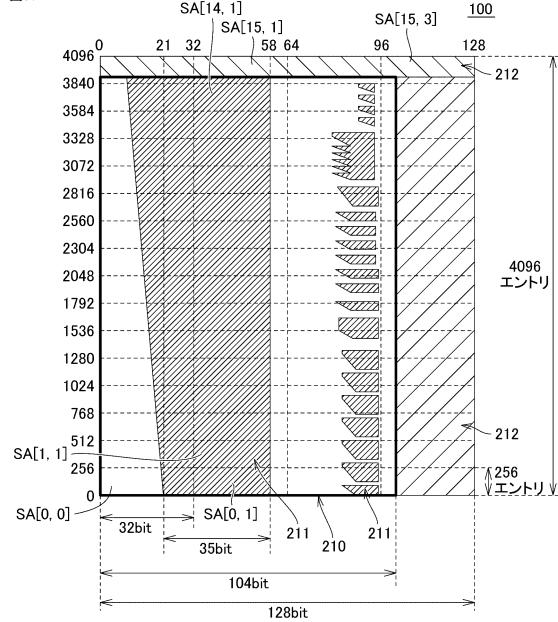

図9は、A C Lに基づく変換データが書込まれたT C A M装置の記憶状態を模式的に示す図である。図9では、範囲指定ルールの多いA C LルールファイルがT C A M装置の記憶領域に書込まれた状態が示されている。

#### 【 0 0 5 6 】

図9のT C A M装置は4 0 9 6エントリの記憶領域を有し、1エントリあたり1 2 8ビットのデータを記憶可能である。T C A M装置全体は、1 6行4列の合計6 4個のサブアレイS A [ 0 , 0 ] ~ S A [ 1 5 , 3 ]に区分される。

10

#### 【 0 0 5 7 】

T C A M装置の記憶領域のうち図9の太枠で囲まれた領域2 1 0が、A C Lに基づく変換データが書き込まれた領域である。データが書き込まれた領域2 1 0のビット幅は、1 0 4ビットであり、図8で説明した5つのチェック要素(プロトコル番号：8ビット、宛先ポート番号：1 6ビット、送信元ポート番号：1 6ビット、宛先I Pアドレス：3 2ビット、送信元I Pアドレス：3 2ビット)に対応している。太枠の領域2 1 0のうち、狭い間隔の斜線のハッチングが付された領域2 1 1は、ドントケアデータの領域を示しており、残りの領域は“0”および“1”的データ領域を示す。

#### 【 0 0 5 8 】

1 0 4ビットのA C Lルールに対して、T C A M装置のビット幅は1 2 8ビットなので、T C A M装置にはデータの埋まらない2 4ビット幅の領域2 1 2ができてしまう。この領域2 1 2のT C A Mセルには、ドントケアデータが格納される。

20

#### 【 0 0 5 9 】

さらに、T C A M装置の総エントリ数が4 0 9 6エントリであるのに対して、ルール数が不足している場合には、データが埋まらない1 2 8ビット幅の空き領域2 1 3が存在する。この空き領域は、インバリッドエントリ(Invalid Entry)(検索非対象エントリとも称する)として設定される。インバリッドエントリの領域は、サーチ時に必ずミス(miss:不一致)になる。

#### 【 0 0 6 0 】

具体的に、図9のT C A Mでは、サブアレイS A [ 1 4 , 1 ] , S A [ 1 2 , 2 ] , S A [ 1 3 , 2 ] , S A [ 1 4 , 2 ] , S A [ j , 3 ] (j = 7 ~ 1 4)については、各サブアレイ内の全てのセルデータがドントケアであるため、これらのサブアレイの全ての行のサーチ結果は自明である(全てヒット(hit)となる)。図9のサブアレイS A [ 1 5 , 1 ] , S A [ 1 5 , 2 ] , S A [ 1 5 , 3 ]については、当該サブアレイの各行は、ドントケアのセルデータのみによって構成されているか、インバリッドエントリに該当するかのいずれかであるので、これらのサブアレイの各行のサーチ結果は自明である。ところが、従来のT C A Mでは、サーチコマンドが入力されると全てのサブアレイに対してサーチ動作が実行されるので、上記のようにサーチ結果が自明のサブアレイに対してもサーチ動作が実行されてしまう。このために、無駄に電流を消費してしまうという問題があった。

30

#### 【 0 0 6 1 】

<第1の実施形態>

第1の実施形態では、T C A M装置内のサーチ結果が自明な領域、具体的にはドントケア(don't care)データ領域のサーチ動作を停止させながらも、正常なサーチ結果を出力する技術が提供される。これによって、従来技術において無駄に消費してしまう電流を削減することができるので、より低消費電力なT C A M装置ならびにT C A M装置を用いたデータ検索システムを提供することができる。以下、図面を参照して具体的に説明する。

#### 【 0 0 6 2 】

[サブアレイの構成]

図10は、第1の実施形態によるT C A M装置において、サブアレイの構成を示すプロ

40

50

ック図である。図10を参照して、図10のサブアレイSAは、レジスタREG1をさらに含む点で、図3のサブアレイSAと異なる。図10では、レジスタREG1は、制御論理回路24の内部に設けられているように図示しているが、制御論理回路24の外部に設けられていても構わない。図10のその他の構成は図3の場合と同様であるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。図10ではデータ検索に関する部分を主として記載しているので、データ書き込みに関する書き込みドライバ21は図示していない。

#### 【0063】

レジスタREG1は、TCAMセルアレイ20の全てのデータがドントケアである場合にハイレベル“H”（この明細書では“1”とする）に設定され、少なくとも1つがドントケアでない場合（「非ドントケア」と称する）にロー・レベル“L”（この明細書では“0”とする）に設定される。具体的には、TCAMセルアレイ20内の全てのデータがドントケアであるか否かの解析をTCAM装置内の専用回路が行い、当該専用回路が、解析結果に基づいてレジスタREG1の値を設定するようにしてよい。もしくは、上記の解析を外部（たとえば、図6のNPU101のデータ解析部104）で行い、解析結果を外部からレジスタREG1に書き込むようにしてもよい。

#### 【0064】

制御論理回路24は、レジスタREG1に設定された論理レベルに応じて、サーチ動作を制御するための制御信号（sle, force\_hit, mae, m1pre\_n）を生成する。以下、図11～図15を参照して、具体的に説明する。

#### 【0065】

##### [サーチ系制御回路の構成]

図11は、図10の制御論理回路のうち、サーチ動作に関係する部分の構成を示す回路図である。図10および図11を参照して、制御論理回路24は、レジスタREG1と、インバータ42, 47, 48と、ANDゲート43, 49, 51と、Dフリップフロップ44, 45と、遅延段50とを含む。レジスタREG1は、Dフリップフロップ40と、ANDゲート41とを含む。

#### 【0066】

レジスタ設定データは、レジスタ書き込みコマンドが“H”レベルに活性化されると、クロック信号clkの立ち上がり時に（すなわち、ANDゲート41の出力が“H”になると）、Dフリップフロップ40に書き込まれる。サブアレイ内の全セルのデータがドントケアの場合に、Dフリップフロップ40には“1”（“H”レベル）が書き込まれ、非ドントケアの場合に、Dフリップフロップ40には“0”（“L”レベル）が書き込まれる。レジスタ設定データおよびレジスタ書き込みデータは、TCAM装置の外部（たとえば、図6のNPU101など）から与えられる。レジスタ設定データの書き込みは、たとえば、TCAM装置の起動時に行われる。

#### 【0067】

Dフリップフロップ40の出力信号は、制御信号force\_hitとしてマッチアンプ部23の各マッチアンプMAに入力される。Dフリップフロップの出力は、さらに、インバータ42を介してANDゲート43に入力される。

#### 【0068】

サーチコマンドは、ANDゲート43、フリップフロップ44, 45、ANDゲート46、およびインバータ47を順に介して、マッチ線プリチャージ信号m1pre\_nとしてマッチアンプ部23に出力される。上記のANDゲート43の他方の入力ノードにはインバータ42によって反転された制御信号force\_hitが入力される。上記のフリップフロップ44, 45のクロック端子にはクロック信号clkが入力される。上記のANDゲート46の他方の入力ノードには、クロック信号clkが入力される。

#### 【0069】

上記のフリップフロップ45の出力信号は、さらに、ANDゲート49を介して、サーチ線イネーブル信号sleとしてサーチ線ドライバ22に出力される。ANDゲート49

10

20

30

40

50

の他方の入力ノードには、クロック信号  $c\ l\ k$  をインバータ 4 8 によって反転した信号が入力される。

#### 【 0 0 7 0 】

上記の AND ゲート 4 9 の出力信号は、さらに、遅延段 5 0 を介して AND ゲート 5 1 の第 1 の入力ノードに入力されるとともに、遅延段 5 0 を介さずに直接 AND ゲート 5 1 の第 2 の入力ノードに入力される。AND ゲート 5 1 の出力信号は、マッチアンプイネーブル信号  $m\ a\ e$  としてマッチアンプ部 2 3 の各マッチアンプ MA に入力される。

#### 【 0 0 7 1 】

上記の回路構成によれば、制御信号  $f\ o\ r\ c\ e\_h\ i\ t$  は、レジスタ REG 1 の設定値に従って、レジスタ REG 1 の設定値が “1” の場合は “H” レベルとなり、レジスタ REG 1 の設定値が “0” の場合は “L” レベルとなる。サーチ動作制御用の制御信号 ( $s\ l\ e$ ,  $m\ a\ e$ ,  $m\ l\ p\ r\ e\_n$ ) は、レジスタ REG 1 の設定値およびサーチコマンドに従って変化する。

10

#### 【 0 0 7 2 】

具体的に、レジスタ REG 1 の格納データが “L” (非ドントケア) であり、かつ、サーチコマンドが “H” レベルに活性化された場合には、最初に、マッチ線プリチャージ信号  $m\ l\ p\ r\ e\_n$  が “L” レベルに活性化される。次に、サーチ線イネーブル信号  $s\ l\ e$  が “H” レベルに活性化される。最後に、マッチアンプイネーブル信号  $m\ a\ e$  が “H” レベルに活性化される。

#### 【 0 0 7 3 】

逆に、レジスタ REG 1 の設定データが “H” (ドントケア) の場合には、サーチコマンドが “H” レベルに活性化されたとしても、マッチ線プリチャージ信号  $m\ l\ p\ r\ e\_n$  は “H” レベル (非活性状態) を維持し、サーチ線イネーブル信号  $s\ l\ e$  は “L” レベル (非活性状態) を維持し、マッチアンプイネーブル信号  $m\ a\ e$  は “L” レベル (非活性状態) を維持する。

20

#### 【 0 0 7 4 】

##### [ サーチ線ドライバの構成および動作 ]

図 1 2 は、図 1 0 のサーチ線ドライバの構成の一例を示す回路図である。図 1 0 および図 1 2 を参照して、サーチ線ドライバ 2 2 は、サーチ線イネーブル信号  $s\ l\ e$  が “H” レベルに活性化されたときに、入力サーチデータ  $s\ d\ [i]$  ( $i = 0, 1, \dots, k$ ) をサーチ線  $S\ L\ [i]$  に出力するとともに、入力サーチデータ  $s\ d\ [i]$  の論理レベルを反転した信号を相補のサーチ線  $S\ L\_n\ [i]$  に出力する。

30

#### 【 0 0 7 5 】

具体的に、サーチ線ドライバ 2 2 は、サーチ線  $S\ L\ [0] \sim S\ L\ [k]$  にそれぞれ対応する AND ゲート  $6\ 0\ [0] \sim 6\ 0\ [k]$  と、サーチ線  $S\ L\_n\ [0] \sim S\ L\_n\ [k]$  にそれぞれ対応する AND ゲート  $6\ 1\ [0] \sim 6\ 1\ [k]$  と、インバータ  $6\ 2\ [0] \sim 6\ 2\ [k]$  とを含む。サーチ線イネーブル信号  $s\ l\ e$  は、AND ゲート  $6\ 0\ [0] \sim 6\ 0\ [k]$  および AND ゲート  $6\ 1\ [0] \sim 6\ 1\ [k]$  に共通に入力される。さらに、AND ゲート  $6\ 0\ [i]$  ( $i = 0, 1, \dots, k$ ) には、対応するサーチデータ  $s\ d\ [i]$  、および対応するマスク信号  $m\ a\ s\ k\_n\ [i]$  が入力される。AND ゲート  $6\ 0\ [i]$  ( $i = 0, 1, \dots, k$ ) の出力信号はサーチ線  $S\ L\ [i]$  に送信される。AND ゲート  $6\ 1\ [i]$  ( $i = 0, 1, \dots, k$ ) には、対応するサーチデータ  $s\ d\ [i]$  を反転した信号、および対応するマスク信号  $m\ a\ s\ k\_n\ [i]$  が入力される。

40

#### 【 0 0 7 6 】

上記構成によれば、たとえば、サーチ線イネーブル信号  $s\ l\ e$  が “H” レベルに活性化され、かつ、入力データ  $s\ d\ [i]$  が “H” レベル (“1”) である場合には、サーチ線  $S\ L\ [i]$  の電圧が “H” レベルとなり、サーチ線  $S\ L\_n\ [i]$  の電圧が “L” レベルとなる。サーチ線イネーブル信号  $s\ l\ e$  が “H” レベルに活性化され、かつ、入力データ  $s\ d\ [i]$  が “L” レベル (“0”) である場合には、サーチ線  $S\ L\ [i]$  の電圧が “L” レベルとなり、サーチ線  $S\ L\_n\ [i]$  の電圧が “H” レベルとなる。マスクサーチ (50

サーチ動作をマスクする動作モード)の場合、マスク信号`mask_n[i]`( $i = 0, 1, \dots, k$ )が“L”レベルに活性化されると、サーチ線`SL[i]`の電圧が“L”レベルとなり、サーチ線`SL_n[i]`の電圧が“L”レベルとなる。

#### 【0077】

##### [マッチアンプの構成および動作]

図13は、図10のマッチアンプの構成の一例を示す回路図である。図10および図13を参照して、マッチアンプMAは、プリチャージ回路としてのPチャネルMOSトランジスタ70と、インバータ71～74と、論理ゲート(NANDゲート)75とを含む。図13では、プリチャージ回路としてのMOSトランジスタ70がマッチアンプMAの内部にあるように図示しているが、MOSトランジスタ70はマッチアンプMAの外部に設けられていても構わない。

#### 【0078】

以下、上記の構成要素の接続について説明する。MOSトランジスタ70は、対応するマッチ線MLと電源電位VDDを与える電源ノードとの間に接続される。MOSトランジスタ70のゲートには、マッチ線プリチャージ信号`m1pre_n`が入力される。マッチ線MLは、さらに、インバータ71の入力ノードに接続される。インバータ71の出力ノードは、論理ゲート75の第1の入力ノードに接続される。論理ゲート75の第2の入力ノードには、インバータ74を介して制御信号`force_hit`が入力される。論理ゲート75の出力ノードは、インバータ72を介して論理ゲート75の第1の入力ノードに接続される。マッチアンプイネーブル信号`mae`およびその論理レベルをインバータ73によって反転させた信号は、インバータ71, 72の駆動電源ノードに接続される。マッチアンプイネーブル信号`mae`が非活性状態(“L”レベル)のとき、インバータ71は非動作状態となり、インバータ72は動作状態となる。マッチアンプイネーブル信号`mae`が活性状態(“H”レベル)のとき、インバータ71は動作状態となり、インバータ72は非動作状態となる。

#### 【0079】

次に、図13のマッチアンプMAの回路動作について説明する。最初に、( $i$ )制御論理回路24のレジスタREG1が“L”レベル(非ドントケアを表す)に設定されている場合について説明する。この場合、制御信号`force_hit`は“L”レベルであるので、論理ゲート75はインバータとして機能する。

#### 【0080】

まず、マッチ線プリチャージ信号`m1pre_n`が活性化される(“L”レベルになる)ことによって、MOSトランジスタ70が導通する。これによって、マッチ線MLが電源電位VDDまで充電される(プリチャージされる)。

#### 【0081】

マッチ線プリチャージ信号`m1pre_n`が非活性化された後に、図10のサーチ線イネーブル信号`sle`が活性化される(“H”レベルになる)ことによって、サーチ線対`SL, SL_n`にサーチデータが入力される。これによって、マッチ線MLの電位がサーチ結果(入力サーチデータの対応部分とTCAMセルデータとの比較結果)に依存して変化する。すなわち、一致(ヒット:hit)の場合、マッチ線MLの電位は電源電位VDD(“H”レベル)のまま維持され、不一致(ミス:miss)の場合、マッチ線MLの電荷が接地ノードに放電されるのでマッチ線のML電位は接地電位(“L”レベル)に変化する。

#### 【0082】

次に、マッチアンプイネーブル信号`mae`が活性化される(“H”レベルになる)。これによって、サーチ結果に基づくマッチ線MLの電位が、インバータ71および論理ゲート75(インバータと同等)を介してマッチアンプ出力信号`mo`として出力される。マッチアンプイネーブル信号`mae`が非活性化される(“L”レベルになる)と、インバータとして機能する論理ゲート75とインバータ72とによって構成されるラッチ回路69に、サーチ結果に基づくマッチ線MLの電位が保持される。

#### 【0083】

10

20

30

40

50

一方、(i) レジスタ REG1 が “H” レベル（ドントケアを表す）に設定されている場合には、制御信号 force(hit) は “H” レベルであるので、マッチアンプ MA の出力信号 mo (論理ゲート 75 の出力信号) は、“H” レベル（一致(hit) を表す）に固定される。さらに、この場合、マッチ線プリチャージ信号 m1pre\_n は “H” レベル（非活性状態）であるので、マッチ線 ML のプリチャージは行われない。サーチ線イネーブル信号 s1e は “L” レベル（非活性状態）であるので、サーチ線対 SL, SL\_n はいずれも “L” レベルに固定されたままである（サーチ線ドライバ 22 は動作しない）。マッチアンプイネーブル信号 mae は “L” レベル（非活性状態）であるので、インバータ 71 は非動作状態である。

## 【0084】

10

## [サーチ動作の一例]

以下、ある 1 つのサブアレイにおけるサーチ動作の例について、図 14 および図 15 のタイミング図を参照して説明する。

## 【0085】

20

## (レジスタ REG1 に “0” が格納されている場合)

図 14 は、図 10 のサブアレイに設けられたレジスタ REG1 に非ドントケアを表す “0” が格納されているときのサーチ動作を示すタイミング図である。図 14 において、各サイクルはクロック信号 CLK のポジティブエッジから次のポジティブエッジまでの期間である。制御論理回路 24 から出力される制御信号 force(hit) は、“L” レベルである。

## 【0086】

図 14 を参照して、T1 サイクルへ切替わる付近で (T1 サイクルの 1 つ前のサイクルの後半から T1 サイクルの前半にかけて)、サーチコマンドとサーチデータとが TCA M 装置に入力される。T1 サイクルの最初のクロック信号 CLK の立上がりにおいて、サーチコマンドとサーチデータとが制御論理回路 24 に取り込まれる。このサーチコマンドに応答して、次の T2 サイクルの前半で制御論理回路 24 は、マッチ線プリチャージ信号 m1pre\_n を活性化する (“L” レベルにする)。これによって、マッチ線 ML が電源電位 VDD まで充電される (プリチャージされる)。

## 【0087】

30

サーチコマンドに応答して、T2 サイクルの後半で、制御論理回路 24 はサーチ線イネーブル信号 s1e を活性化する (“H” レベルにする)。サーチ線イネーブル信号 s1e が活性化する前に、マッチ線プリチャージ信号 m1pre\_n は非活性化される (“H” レベルになる)。サーチ線イネーブル信号 s1e の活性化によってサーチ線ドライバ 22 が活性化され、サーチ線ドライバ 22 はサーチデータ sd をサーチ線対 SL, SL\_n に転送する。この結果、マッチ線 ML に接続された全ての TCA M セルのセルデータと、サーチ線対 SL, SL\_n を介して転送されたサーチデータ sd とが一致した場合には (ヒット)、マッチ線 ML の電位は電源電位 VDD (“H” レベル) に維持される。マッチ線 ML に接続された TCA M セルの格納値のうち 1 つでも、転送されたサーチデータ sd と一致しない場合には (ミス)、マッチ線 ML にプリチャージされた電荷が放電されるために、マッチ線 ML の電位は接地電位 (“L” レベル) に変化する。

40

## 【0088】

サーチコマンドに応答して、T2 サイクルの後半において、さらに、制御論理回路 24 は、サーチ線イネーブル信号 s1e を活性化した後でかつ非活性化する前に、マッチアンプイネーブル信号 mae を活性化する (“H” レベルにする)。これによって、行 (エントリ) ごとに、マッチアンプ MA からマッチ線 ML の電位に基づく信号 (サーチ結果) が出力される。同一のエントリに対応する複数のサブアレイ (マッチアンプ MA) でのサーチ結果は、AND 演算された後にプライオリティ・エンコーダ 30 に入力される。

## 【0089】

50

次の T3 サイクルにおいて、制御論理回路 24 がマッチアンプイネーブル信号 mae を非活性化する (“L” レベルにする) ことによって、各マッチ線 ML で検出されたサーチ

結果は、対応するマッチアンプMA内のラッチ回路69に保持される。さらに、T3サイクルにおいて、プライオリティ・エンコーダ30は、ヒットアドレス(サーチ結果)を出力する。ヒットアドレスが複数存在する場合には、最も優先度の高いものが outputされる。

#### 【0090】

(レジスタREG1に“1”が格納されている場合)

図15は、図10のサブアレイに設けられたレジスタREG1にドントケアを表すデータ“1”が格納されているときのサーチ動作を示すタイミング図である。

#### 【0091】

図15を参照して、電源立ち上げ時などにおいて、最初に(図15では、T1サイクルの1つ前のサイクルの後半からT1サイクルの前半にかけて)、レジスタ書込みコマンドとドントケアを表すレジスタ設定データ(“H”レベル)とがTCAM装置に入力される。T1サイクルの最初のクロック信号clkの立上がりにおいて、レジスタ設定データ(“H”レベル)は、対応するサブアレイSAのレジスタREG1に書込まれる。これによって、制御信号force\_hitが“H”レベルになり、各マッチアンプMAの出力信号moが“H”レベル(ヒットを表す)に固定される。10

#### 【0092】

サーチ動作時において、最初に(図15では、T2サイクルの後半からT3サイクルの前半にかけて)、サーチコマンドとサーチデータとがTCAM装置に入力される。レジスタREG1に“L”レベルが設定されている場合には、T3サイクルの最初のクロック信号clkの立上がりにおいて、サーチコマンドが制御論理回路24に取り込まれ、次のT4サイクルにおいてサーチ動作が実行される(図14参照)。しかしながら、レジスタREG1に“H”レベルが設定されている場合には、サーチコマンドが制御論理回路24に取り込まれることはない。このため、次のT4サイクルにおいて、サーチ動作が開始されない。20

#### 【0093】

このように、ある1つのサブアレイの全てのTCAMセルのセルデータがドントケアを表すデータの場合には、レジスタREG1が“H”レベル(“1”)に設定される。この結果、当該サブアレイの各マッチアンプMAの出力が“H”レベル(ヒット)に固定されるとともに、当該サブアレイではサーチ動作(マッチ線のプリチャージおよびサーチ線ドライバの動作)が実行されないようになるので、省電力化を図ることができる。30

#### 【0094】

[マッチアンプの構成の変形例]

たとえば、図9のTCAM装置のサブアレイSA[15,1], SA[15,2], SA[15,3]については、データが格納されていないインバリッドエントリを含んでいる。すなわち、これらのサブアレイの各行は、全てのセルデータがドントケアに設定されているか、インバリッドエントリに該当するかのいずれかである。したがって、各行(エントリ)のサーチ結果は自明である。このような場合においても、図10の制御論理回路24内のレジスタREG1を“H”レベル(“1”)に設定することによって、当該サブアレイではサーチ動作を行わないようにすることによって、低消費電力化を図ることができる。ただし、これらのサブアレイのうちインバリッドエントリに該当する行に関しては、マッチアンプMAがサーチ結果として“L”レベル(ミス)を出力するように変更する必要がある。40

#### 【0095】

以下、上記のように、インバリッドエントリではサーチ結果としてミスを出力するように変更されたマッチアンプMAの構成について説明する。なお、図9で説明したように、インバリッドエントリ(Invalid Entry)とは、TCAM装置の総エントリのうちデータが格納されていない空きエントリを意味し、検索非対象エントリとなっている。一方、バリッドエントリ(Valid Entry)とは、TCAM装置の総エントリのうちデータが格納されている検索対象エントリである。

#### 【0096】

50

図16は、図10のマッチアンプの変形例を示す回路図である。図16のマッチアンプMAは、ANDゲート76とレジスタREG2をさらに含む点で、図10のマッチアンプと異なる。レジスタREG2は、サブアレイの対応する行(エントリ)がインバリッドエントリの場合に“L”レベル(この明細書では“0”とする)に設定され、バリッドエントリの場合に“H”レベル(この明細書では“1”とする)に設定される。レジスタREG2は、サブアレイSAの行ごとにマッチアンプMAに対応して設けられていればよいので、必ずしも図16のようにマッチアンプMAの内部に設けられている必要はない。上記のレジスタREG2の値の設定は、TCAM装置内部の専用回路が行ってもよいし、TCAM装置の外部(たとえば、図6のNPU101)から行うようにしてもよい。

## 【0097】

10

ANDゲート76は、レジスタREG2から出力された制御信号val\_entと論理ゲート75の出力信号とのAND演算結果を、マッチアンプMAの出力信号moとして出力する。図16のその他の構成は図10の場合と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

## 【0098】

20

上記構成によれば、図10および図11で説明したレジスタREG1が、ドントケアを表す“H”レベルの値(“1”)に設定されていた場合であっても、インバリッドエントリに対応するマッチアンプMAのレジスタREG2を“L”レベルの値(“0”)に設定することによって、マッチアンプMAの出力信号moを“L”レベル(ミス)にすることができる。したがって、あるサブアレイの各行が、全てドントケアのセルデータによって構成されているか、インバリッドエントリに該当し、“1”または“0”的データを格納するTCAMセルが含まれていない場合には、当該サブアレイでのサーチ動作を停止させた上で、各マッチアンプMAからヒット(ドントケアの場合)またはミス(インバリッドエントリの場合)を正常に出力させることができる。この結果、当該サブアレイの消費電力を低減させることができる。

## 【0099】

## [第1の実施形態の効果]

上記の実施形態によれば、サーチ結果が自明なサブアレイは、サーチ動作を行わないようにしたうえで、当該サブアレイから正常なサーチ結果を出力するように制御できる。具体的に、サブアレイに含まれるすべてのTCAMセルのデータがドントケアである場合には、各マッチアンプMAからヒットを表わす“H”レベルの信号が出力される。サブアレイの各行が、全てドントケアのセルデータによって構成されているか、インバリッドエントリに該当するかのいずれかである場合には、ドントケアの場合に対応するマッチアンプMAからヒットを表す“H”レベルの信号が出力され、インバリッドエントリの場合に対応するマッチアンプからミスを表す“L”レベルの信号が出力される。この結果、当該サブアレイの各マッチアンプMAは、マッチ線のプリチャージ電流および動作電流を発生しないので、TCAM装置の消費電力を低減させることができる。

30

## 【0100】

さらに、サーチ結果が自明なサブアレイに対してサーチ動作を行わないことによって、サーチ動作時のピーク電流を低減させ、急激な電流変化を抑制することができる。さらに、急激な電流変化を抑制することによって、TCAM装置を搭載した半導体チップに供給する電源電圧の揺らぎを低減することができ、この結果、サーチ特性が安定した高品質なTCAM装置を実現することができる。さらに、TCAM装置の消費電流およびサーチ動作時のピーク電流の削減によって、TCAM装置に接続する外部電源装置の必要能力(すなわち、電流の供給能力および応答性能など)を軽減することができるので、安価で高品質なデータ検索システムを実現することができる。

40

## 【0101】

## &lt;第2の実施形態&gt;

## [TCAMサブアレイの構成]

図17は、第2の実施形態によるTCAM装置において、サブアレイSAの構成を示す

50

ブロック図である。図17に示すサブアレイSAは、列方向(Y方向)の両端に配置された2個の制御論理回路24A, 24Bと、列方向(Y方向)の両端に配置された2個のサーチ線ドライバ22A, 22Bとを含む点で、図10のサブアレイSAと異なる。図17では図示していないが、書き込みドライバについても列方向(Y方向)の両端に配置されている。

#### 【0102】

第0行から第( $m - 1$ ) / 2行までのTCAMセル(セルアレイ20Aと称する)は、これらのTCAMセル(セルアレイ20A)に隣接するSLドライバ22A、マッチアンプ部23A、および制御論理回路24Aによって制御される。

#### 【0103】

セルアレイ20Aがドントケアのデータのみを格納している場合には、制御論理回路24Aに設けられたレジスタREG1Aに“H”レベルの値(“1”)が設定される。この場合、制御論理回路24Aから出力される制御信号force\_hitは“H”レベル(“1”)となるので、マッチアンプ部23Aに設けられたマッチアンプ(不図示)からの出力信号mo[0] ~ mo[( $m - 1$ ) / 2]は“H”レベル(ヒット)に固定される。

#### 【0104】

第( $m - 1$ ) / 2 + 1行から第m行までのTCAMセル(セルアレイ20Bと称する)は、これらのTCAMセル(セルアレイ20B)に隣接するSLドライバ22B、マッチアンプ部23B、および制御論理回路24Bによって制御される。

#### 【0105】

セルアレイ20Bがドントケアのデータのみを格納している場合には、制御論理回路24Bに設けられたレジスタREG1Bに“H”レベルの値(“1”)が設定される。この場合、制御論理回路24Bから出力される制御信号force\_hitは“H”レベル(“1”)となるので、マッチアンプ部23Bに設けられたマッチアンプ(不図示)からの出力信号mo[( $m - 1$ ) / 2 + 1] ~ mo[m]は“H”レベル(ヒット)に固定される。

#### 【0106】

図17のサブアレイSAのマッチアンプ部23A, 23Bに設けられた各マッチアンプ(不図示)は、図16で説明したレジスタREG2を有するマッチアンプMAの構成としてもよい。この場合、サブアレイSAのセルアレイ20A, 20Bのうちインパリッドエントリに該当する行のマッチアンプからの出力信号moは“L”レベル(ミス)となる。

#### 【0107】

図17のその他の点は、図10などで説明した第1の実施形態の場合と同様であるので、同一または相当する部分については同一の参照符号を付して説明を繰返さない。

#### 【0108】

##### [第2の実施形態の効果]

上記の構成のサブアレイを備えたTCAM装置によれば、第1の実施形態のTCAM装置と同様の効果を奏するとともに、さらに次のような効果を奏する。まず、第1の実施形態の図10の構成のサブアレイに比べて、総エントリ(行)数が半分の領域に対してドントケア領域か否かの設定が可能になる。したがって、ドントケア領域が比較的小さなACルールファイルに対しても省電力化を図ることができる。

#### 【0109】

さらに、図10の構成のサブアレイSAを複数配置する場合には、デザインルールの制約のために、サーチ線ドライバ22などのドライバ回路とセルアレイ20Aとが近接しないように、隣合うサブアレイSAの間にある程度の間隔を設ける必要がある。これに対して、図17の構成のサブアレイSAを複数配置する場合には、各サブアレイSAのサーチ線ドライバ22Aおよび制御論理回路24Aを、隣接するサブアレイSAのサーチ線ドライバ22Bおよび制御論理回路24Bに近接して配置することができるので、隣合うサブアレイの間隔を図10の場合ほどあけなくてもよいというメリットがある。

#### 【0110】

10

20

30

40

50

## &lt;第3の実施形態&gt;

たとえば、図9のサブアレイSA[6, 1], SA[13, 1]については、サブアレイ内の全ての行のTCA Mセルがドントケアに設定されているわけではないので、図10および図11で説明したレジスタREG1を“H”レベル(“1”)に設定することはできない。しかしながら、一部の行のTCA Mセルについては全てドントケアに設定されているので、これらの一部の行についてはサーチ結果がヒットになることは自明である。

## 【0111】

そこで、第3の実施形態のTCA M装置は、サブアレイの行ごとに、マッチ線MLのプリチャージを停止し、マッチアンプMAの回路動作を行わないよう制御可能にしたものである。これによって一層の低消費電力化を図ることができる。以下、図面を参照して具体的に説明する。10

## 【0112】

## [マッチアンプの構成および動作]

図18は、第3の実施形態によるTCA M装置において、マッチアンプMAの構成を示す回路図である。図18のマッチアンプMAは、レジスタREG3、ORゲート77、ANDゲート78、およびインバータ79をさらに含む点で、図13のマッチアンプMAと異なる。さらに、図18のマッチアンプMAは、インバータ74に代えてNORゲート80を含む点で図13のマッチアンプMAと異なる。

## 【0113】

マッチ線MLを介してマッチアンプMAに接続された全てのTCA Mセルのセルデータがドントケアに設定されている場合には、レジスタREG3は“H”レベル(この明細書では“1”に対応する)に設定される。マッチ線MLを介してマッチアンプMAに接続されているTCA Mセルのうち少なくとも1つのセルデータがドントケアでない場合には、レジスタREG3は“L”レベル(この明細書では“0”に対応する)に設定される。レジスタREG3は、サブアレイSAの行ごとにマッチアンプMAに対応して設けられていればよいので、必ずしも図18のようにマッチアンプMAの内部に設けられている必要はない。20

## 【0114】

ORゲート77は、レジスタREG3から出力された制御信号dnc(hit)とマッチ線プリチャージ信号mlpre\_nとのOR演算を実行し、演算結果をPチャネルMOSトランジスタ70のゲートに出力する。したがって、レジスタREG3の設定値に従う制御信号dnc(hit)が“H”レベルのときは、MOSトランジスタ70はオフ状態に固定されるので、マッチ線MLのプリチャージは生じない。30

## 【0115】

ANDゲート78は、レジスタREG3から出力された制御信号dnc(hit)の論理レベルをインバータ79によって反転させた値とマッチアンプイネーブル信号maeとのAND演算を行う。ANDゲート78のAND演算結果と、このAND演算結果の論理レベルをインバータ73によって反転させた信号とが、インバータ71, 72の駆動電源ノードに供給される。したがって、レジスタREG3の設定値に従う制御信号dnc(hit)が“H”レベルの場合には、インバータ71は非動作状態となり、インバータ72は動作状態となるので、マッチ線MLの電位は後段の回路に出力されず、マッチ線MLの電位のラッチも行われない。40

## 【0116】

NORゲート80は、レジスタREG3から出力された制御信号dnc(hit)と制御信号force(hit)とのNOR演算を行い、演算結果を論理ゲート75(NANDゲート)の第2の入力ノードに入力する。したがって、レジスタREG3(制御信号dnc(hit))が“H”レベルに設定されているときは、マッチアンプMAの出力信号mo(論理ゲート75の出力信号)は、“H”レベル(一致(hit)を表す)に固定される。

## 【0117】

以上のように、レジスタREG3(制御信号dnc(hit))が“H”レベルに設定さ50

れているときは、レジスタ REG1 が “L” レベルに設定されていたとしても、マッチアンプ MA の出力信号 m\_o を “H” レベル（ヒット）に固定するとともに、マッチ線 ML のプリチャージおよびマッチアンプ MA の回路動作を停止させることができる。

#### 【0118】

図 18 のその他の構成および動作は図 13 と同様であるので、同一または相当する部分に同一の参照符号を付して説明を繰り返さない。たとえば、制御論理回路 24 に設けられたレジスタ REG1 とマッチアンプ MA に設けられたレジスタ REG3 とが共に “L” レベル（非ドントケアを表す）に設定されている場合には、マッチアンプ MA とマッチ線 ML を介して接続された TCAM セルについては通常のサーチ動作が行われる。制御論理回路 24 に設けられたレジスタ REG1 が “H” レベル（ドントケアを表す）に設定されている場合には、サブアレイ全体のサーチ動作が停止される。10

#### 【0119】

##### [レジスタ REG3 へのデータ設定方法]

以下、図 18～図 21 を参照して、レジスタ REG3 へのデータ設定方法について説明する。

#### 【0120】

図 18 に示すように、レジスタ REG3 には、レジスタ書き込み信号 reg\_w\_sig とレジスタデータ reg\_data とが入力される。レジスタ REG3 は、レジスタ書き込み信号 reg\_w\_sig が活性化されたときに、レジスタデータ reg\_data を格納する。レジスタ書き込み信号 reg\_w\_sig およびレジスタデータ reg\_data は、TCAM 装置内部の専用回路から与えてもよいし、TCAM 装置外部のプロセッサ（たとえば、図 6 の NPU101）から与えてもよい。20

#### 【0121】

特に、TCAM 装置内部に専用回路（図 19 のデータ判定回路 33）を設けた場合には、当該専用回路は、TCAM 装置へのデータ書き込み時に、共通のマッチ線 ML に接続された全ての TCAM セルへの書き込みデータがドントケアであるか否かを判定し、判定結果に基づいて即座にレジスタ REG3 に書き込みを行うことができる。都合がよい。当該専用回路は、共通のマッチ線 ML に接続された全ての TCAM セルがドントケアに設定される場合に、レジスタ REG3 を “H” レベル（“1”）に設定し、そうでない場合に、レジスタ REG3 を “L” レベル（“0”）に設定する。30

#### 【0122】

これに対して、TCAM 装置の外部のプロセッサによってレジスタ REG3 の設定を行う場合には、TCAM 装置へのデータ書き込み後に、外部のプロセッサが TCAM 装置からエントリごとにデータを読み出して、上記の判定条件が満たされているか否かを判定することになる。したがって、TCAM 装置内部に専用回路を設けるよりも、余計に手間がかってしまう。

#### 【0123】

以下、上記の専用回路（図 19 のデータ判定回路 33）の動作について、図面を参照して詳しく説明する。

#### 【0124】

図 19 は、第 3 の実施形態による TCAM 装置の構成を示すブロック図である。図 19 の TCAM 装置は、データ判定回路 33[0]～33[3]（総称する場合または不特定のものを示す場合にデータ判定回路 33 と記載する）をさらに含む点で、図 4 の TCAM 装置と異なる。40

#### 【0125】

図 19 に示すように、データ判定回路 33[0] は、サブアレイ SA[0, 0], SA[1, 0], SA[2, 0], ... に対応して設けられる。データ判定回路 33[0] は、コマンド入力回路 32 を介して入力された書き込みコマンドを検出したとき、対応するサブアレイへの書き込みデータ d[0 : 31] に基づいて、同一行（エントリ）の全ての書き込みデータがドントケアであるという条件が満たされているか否かを判定する。データ判定回50

路 33 [ 0 ] は、上記の判定条件が満たされている場合に、当該行に対応するレジスタ REG3 を “H” レベル（ドントケアを表す）に設定する。

#### 【0126】

同様に、データ判定回路 33 [ 1 ] は、サブアレイ SA [ 0 , 1 ] , SA [ 1 , 1 ] , SA [ 2 , 1 ] , … に対応して設けられ、対応するサブアレイへの書き込みデータ d [ 32 : 63 ] に基づいて、対応するサブアレイの各レジスタ REG3 の設定を行う。データ判定回路 33 [ 2 ] は、サブアレイ SA [ 0 , 2 ] , SA [ 1 , 2 ] , SA [ 2 , 2 ] , … に対応して設けられ、対応するサブアレイへの書き込みデータ d [ 64 : 95 ] に基づいて、対応するサブアレイの各レジスタ REG3 の設定を行う。データ判定回路 33 [ 3 ] は、サブアレイ SA [ 0 , 3 ] , SA [ 1 , 3 ] , SA [ 2 , 3 ] , … に対応して設けられ、対応するサブアレイへの書き込みデータ d [ 96 : 127 ] に基づいて、対応するサブアレイの各レジスタ REG3 の設定を行う。

10

#### 【0127】

図 20 は、図 19 のデータ判定回路 33 の動作を示すフローチャートである。図 19 および図 20 を参照して、TCAM セルへのデータ書き込み時に、データ入力回路 31 は、エントリごとに、各 TCAM セルの X セル（図 1 参照）用の書き込みデータを出力し、次に Y セル用の書き込みデータを出力する。データ入力回路 31 から順次出力された X セル用および Y セル用の書き込みデータ d [ 0 : 31 ] , d [ 32 : 63 ] , d [ 64 : 95 ] , d [ 96 : 127 ] は、32 ビットごとに対応するサブアレイ SA の書き込みドライバ 21 に入力され、書き込みドライバ 21 から各ビット線対 BL , BL\_n に出力される。X セル用および Y セル用の書き込みデータ d [ 0 : 31 ] , d [ 32 : 63 ] , d [ 64 : 95 ] , d [ 96 : 127 ] は、32 ビットごとに対応するデータ判定回路 33 に入力される。言い替えると、データ判定回路 33 は、同一マッチラインに接続された書き込み対象である TCAM セルの X セルおよび Y セル用の書き込みデータを順次受信する（ステップ S100）。

20

#### 【0128】

次に、データ判定回路 33 は、受信した 32 ビットの X セル用の書き込みデータの全ビットと 32 ビットの Y セル用の書き込みデータの全ビットとが全て “0” であるという条件が満たされているか否かを判定する（ステップ S110）。具体的には、データ判定回路 33 は、X セル用の書き込みデータの全ビットの OR 演算を行い、さらに、Y セル用の書き込みデータの全ビットの OR 演算を行う。データ判定回路 33 は、これらの OR 演算の演算結果の NOR 演算を実行し、最終的に得られた値が “1”（ドントケア）であるか “0”（非ドントケア）であるかを判定する。

30

#### 【0129】

上記の X セル用データおよび Y セル用データの全ビットが “0” であるという判定条件が満たされている場合、すなわち、上記の論理演算によって最終的に得られた値が “1”（ドントケア）である場合（ステップ S110 で YES）、データ判定回路 33 は、書き込み対象のエントリに対応するレジスタ REG3 を、ドントケアを表す値 “1”（“H” レベル）に設定する（ステップ S120）。レジスタ REG3 に値 “1” を設定するタイミングは、TCAM セルにデータを書込むタイミングと同じでよい。

40

#### 【0130】

逆に、上記の判定条件が満たされていない場合、すなわち、上記の論理演算によって最終的に得られた値が “0”（非ドントケア）である場合（ステップ S110 で NO）、データ判定回路 33 は、書き込み対象のエントリに対応するレジスタ REG3 を、非ドントケアを表す値 “0”（“L” レベル）に設定する（ステップ S130）。

#### 【0131】

図 21 は、第 3 の実施形態の TCAM 装置において、図 18 のレジスタ REG3 へのデータ書き込み手順を示すタイミング図である。図 21 において、各サイクルはクロック信号 CLK のポジティブエッジから次のポジティブエッジまでの期間である。

#### 【0132】

図 19 および図 21 を参照して、最初に、T1 サイクルへ切替わる付近で（T1 サイク

50

ルの 1 つ前のサイクルの後半から T 1 サイクルの前半にかけて)、X セル用の書き込みデータ(128 ビット)と X セルへの書き込みを指令するためのコマンドとが、それぞれ、データ入力回路 3 1 とコマンド入力回路 3 2 とに入力される。データ入力回路 3 1 は、入力された X セル用データ(128 ビット)を、32 ビットごとに分割し、分割後の X セル用データ(32 ビット)の各々を対応するサブアレイ SA および対応するデータ判定回路 3 3 に出力する。コマンド入力回路 3 2 は、入力されたコマンド(X セルへの書き込み)を各サブアレイ SA および各データ判定回路 3 3 に出力する。T 1 サイクルにおいて、各データ判定回路 3 3 は、対応する 32 ビット分の X セル用データを取り込む。

#### 【 0 1 3 3 】

次に、T 2 サイクルへ切替わる付近で(T 1 サイクルの後半から T 2 サイクルの前半にかけて)、Y セル用の書き込みデータ(128 ビット)と Y セルへの書き込みを指令するためのコマンドとが、それぞれ、データ入力回路 3 1 とコマンド入力回路 3 2 とに入力される。データ入力回路 3 1 は、入力された Y セル用データ(128 ビット)を、32 ビットごとに分割し、分割後の Y セル用データ(32 ビット)の各々を対応するサブアレイ SA および対応するデータ判定回路 3 3 に出力する。コマンド入力回路 3 2 は、入力されたコマンド(Y セルへの書き込み)を各サブアレイ SA および各データ判定回路 3 3 に出力する。

#### 【 0 1 3 4 】

T 2 サイクルにおいて、各データ判定回路 3 3 は、対応する 32 ビット分の Y セル用の書き込みデータを取り込む。さらに、各データ判定回路 3 3 は、T 1 サイクルで取り込んだ X セル用データの全ビットの OR 演算を行い、演算結果(“0”または“1”)を、たとえば、データ判定回路 3 3 ごとに設けられた 2 ビットのシフトレジスタの第 1 ビット目に保持する。

#### 【 0 1 3 5 】

次の T 3 サイクルにおいて、X セル用データの OR 演算結果は、シフトレジスタの第 2 ビット目にシフトされる。各データ判定回路 3 3 は、T 2 サイクルで取り込んだ Y セル用データの全ビットの OR 演算を行い、演算結果(“0”または“1”)を、上記のシフトレジスタの第 1 ビット目に保持する。その後、各データ判定回路 3 3 は、対応するシフトレジスタの第 1 ビット目と第 2 ビット目との NOR 演算を行う(すなわち、T 2 サイクルで得られた X セル用データの OR 演算結果と T 3 サイクルで得られた Y セル用データの OR 演算結果との NOR 演算がさらに実行される)。以上の論理演算の最終的な結果が“1”的場合は、32 ビットの X セル用データおよび 32 ビットの Y セル用データの各ビットは全て“0”であること、すなわち、32 ビットの書き込みデータの全ビットがドントケアであることがわかる。

#### 【 0 1 3 6 】

次の T 4 サイクルにおいて、データ判定回路 3 3 は、NOR 演算結果をレジスタデータ reg\_data として、対応するサブアレイ SA の各レジスタ REG 3 に出力する。データ判定回路 3 3 は、T 4 サイクルのクロック信号 clk のネガティブエッジで、書き込み対象エントリに対応するマッチアンプ MA に設けられたレジスタ REG 3 に供給されるレジスタ書き込み信号 reg\_w\_sig を活性化する(“H”レベルにする)。この結果、書き込み対象エントリの TCAM セルの値が全てドントケアの場合には、レジスタ REG 3 に“1”(“H”レベル)が設定され、そうでない場合(非ドントケアの場合)には、レジスタ REG 3 に“0”(“L”レベル)が設定される。レジスタ書き込み信号 reg\_w\_sig をクロック信号 clk のネガティブエッジで発生させる理由は、セットアップ時間およびホールド時間を十分に確保するためである。

#### 【 0 1 3 7 】

##### [ マッチアンプの変形例 ]

図 2 2 は、図 1 8 のマッチアンプ MA の変形例を示すブロック図である。図 2 2 のマッチアンプ MA は、対応する行がデータの格納されていないインバリッドエントリの場合にも適用可能なものである。

#### 【 0 1 3 8 】

10

20

30

40

50

具体的に、図22のマッチアンプMAは、レジスタREG2、ANDゲート76、インバータ81、およびORゲート82をさらに含む点で図18のマッチアンプMAと異なる。

#### 【0139】

レジスタREG2は、サブアレイの対応する行がインバリッドエントリの場合に“L”レベル（この明細書では“0”とする）に設定され、バリッドエントリの場合に“H”レベル（この明細書では“1”とする）に設定される。レジスタREG2は、サブアレイSAの行ごとにマッチアンプMAに対応して設けられていればよいので、必ずしも図22のようにマッチアンプMAの内部に設けられている必要はない。上記のレジスタREG2の値の設定は、TCAM装置内部の専用回路が行ってもよいし、TCAM装置の外部（たとえば、図6のNPU101）から行うようにしてもよい。10

#### 【0140】

ANDゲート76は、レジスタREG2から出力された制御信号val\_entと論理ゲート75の出力信号とのAND演算結果を、マッチアンプMAの出力信号moとして出力する。したがって、レジスタREG1の設定値が“1”（ドントケア）であるか、または、レジスタREG3の設定値が“1”（ドントケア）であったとしても、レジスタREG2の設定値が“0”（インバリッド）であれば、レジスタREG2のインバリッド設定が優先されるため、マッチアンプMAの出力信号moを“L”レベル（ミス）にすることができる。20

#### 【0141】

ORゲート82は、レジスタREG3から出力された制御信号dnc\_hitと、レジスタREG2から出力された制御信号val\_entの論理レベルをインバータ81によって反転させた値とのOR演算を行う。

#### 【0142】

ORゲート77は、ORゲート82の出力値とマッチ線プリチャージ信号mlpre\_nとのOR演算を実行し、演算結果をPチャネルMOSトランジスタ70のゲートに出力する。したがって、レジスタREG3の設定値に従う制御信号dnc\_hitが“H”レベル（ドントケア）の場合、および／または、レジスタREG2の設定値に従う制御信号val\_entが“L”レベル（インバリッド）の場合に、MOSトランジスタ70はオフ状態に固定されるので、マッチ線MLのプリチャージは生じない。30

#### 【0143】

ANDゲート78は、ORゲート82の出力値の論理レベルをインバータ79によって反転させた値とマッチアンプイネーブル信号maeとのAND演算を行う。ANDゲート78のAND演算結果と、このAND演算結果の論理レベルをインバータ73によって反転させた信号とが、インバータ71, 72の駆動電源ノードに供給される。したがって、レジスタREG3の設定値に従う制御信号dnc\_hitが“H”レベル（ドントケア）の場合、および／または、レジスタREG2の設定値に従う制御信号val\_entが“L”レベル（インバリッド）の場合には、インバータ71は非動作状態となり、インバータ72は動作状態となるので、マッチ線MLの電位は後段の回路に出力されず、マッチ線MLの電位のラッチも行われない。40

#### 【0144】

図22のその他の構成は図18の場合と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

#### 【0145】

このように、マッチアンプMAに対応する行がインバリッドエントリの場合にもサーチ結果が自明（ミスになる）であるため、マッチ線MLのプリチャージ動作が停止され、マッチアンプMAの回路動作が停止される。この場合には、マッチアンプMAの出力信号が“L”レベル（ミス）に固定されることによって、正常なサーチ結果が出力される。

#### 【0146】

図22において、インバータ81およびORゲート82を設けないような変形例も可能50

である。すなわち、レジスタ REG 2 から出力された制御信号 `v_a1_ent` は、AND ゲート 76 にのみ入力される。この場合、レジスタ REG 2 を “0” (インバリッド) に設定しただけでは、対応するマッチ線 ML のプリチャージを停止したり、マッチアンプ MA の回路動作を停止したりすることができない。したがって、レジスタ REG 2 を “0” (インバリッド) に設定した場合には、必ず、レジスタ REG 3 を “1” (ドントケア) に設定する必要がある。

#### 【0147】

##### [第3の実施形態の効果]

上記のとおり、サブアレイ内の全てのセルデータがドントケアでない場合であっても、全セルデータがドントケアである行（以下、「ドントケアエントリ」と称する）を含んでいる場合、もしくは、データが設定されていないインバリッドエントリを含んでいる場合には、当該行のサーチ結果は自明である。このような場合には、当該行（ドントケアエントリまたはインバリッドエントリ）のマッチ線 ML のプリチャージ動作が停止され、マッチアンプ MA の回路動作が停止される。これによって、TCA M 装置の消費電力を低減させることができる。そして、ドントケアエントリに対応するマッチアンプ MA からの出力信号を “H” レベル（ヒット）に固定し、インバリッドエントリに対応するマッチアンプ MA からの出力信号を “L” レベル（ミス）に固定することによって、正常なサーチ動作を行うことができる。

#### 【0148】

第3の実施形態の TCA M 装置によれば、サブアレイ内にドントケアエントリまたはインバリッドエントリが散在している場合に有効な低消費電力化手段を与えることができる。

#### 【0149】

##### <第4の実施形態>

第4の実施形態の TCA M 装置では、図 10 および図 11 で説明した、サブアレイ全体のサーチ動作を停止可能にするためのレジスタ REG 1 が設けられていない場合について説明する。この場合、図 18 および図 22 で説明したマッチアンプ MA ごとに設けられているレジスタ REG 3 の設定値に基づいて、サブアレイ全体のサーチ動作を停止するか否かが判定される。以下、図面を参照して詳しく説明する。

#### 【0150】

##### [サブアレイの構成]

図 23 は、第4の実施形態による TCA M 装置において、サブアレイの構成を模式的に示すブロック図である。図 23 のサブアレイ SA は、制御論理回路 24 内のレジスタ REG 1 が設けられておらず、このレジスタ REG 1 に代えて論理積回路 27 が設けられている点で、図 10 のサブアレイ SA と異なる。図 23 のその他の構成は図 10 と同様であるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

#### 【0151】

論理積回路 27 は、TCA M セルアレイ 20 の行ごとに（マッチ線 ML ごとに）設けられたレジスタ REG 3 [0] ~ REG 3 [m] のそれぞれの設定値 `d_nc_hit[0] ~ d_nc_hit[m]` の論理積を演算し、演算結果を制御信号 `force_hit` として出力する。制御信号 `force_hit` は、制御論理回路 24 に入力される。既に説明したように、レジスタ REG 3 は、サブアレイ内の対応する行のセルデータが全てドントケアであるときに “1” (“H” レベル）に設定され、そうでない場合に “0” (“L” レベル）に設定される。したがって、サブアレイ内の全てのセルデータがドントケアの場合に制御信号 `force_hit` は “H” レベル（“1”）になり、そうでない場合に制御信号 `force_hit` は “L” レベル（“0”）になる。

#### 【0152】

##### [制御論理回路の構成]

図 24 は、図 23 の制御論理回路 24 において、検索動作に関する部分の構成を示す回路図である。図 24 の制御論理回路 24 は、レジスタ REG 1 を含まない点で図 11 の

10

20

30

40

50

制御論理回路 24 と異なる。図 24 の場合、インバータ 42 への入力される制御信号 `force_hi_t` は、図 23 の論理積回路 27 から与えられる。

#### 【0153】

さらに、図 24 の場合、制御信号 `force_hi_t` は制御論理回路 24 から各マッチアンプ MA に出力されない。したがって、図 18 および図 22 のマッチアンプ MA では、NOR ゲート 80 に代えて、レジスタ REG3 から出力された制御信号 `dnc_hi_t` の論理レベルを反転するためのインバータが設けられる。このインバータの出力信号が論理ゲート 75 に入力される。図 24 のその他の構成は図 11 と同様であるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

#### 【0154】

10

##### [第 4 の実施形態の効果]

上記の構成によれば、サブアレイ内の全てのセルデータがドントケアに設定されており、これによって、サブアレイ内の行ごとに設けられたレジスタ REG3 が全てドントケアに設定されている場合には、自動的にサブアレイのサーチ動作を停止することができる。図 19 ~ 図 21 で説明したように、レジスタ REG3 の値の設定については、データ判定回路 33 を用いて自動的に行うことができるので、レジスタ REG1 の値を設定するために、TCA M 装置へのデータ書き込み後に TCA M セルデータの内容を解析する必要がないというメリットがある。

#### 【0155】

20

変形例として、図 10 および図 11 で説明したレジスタ REG1 と、図 23 の論理積回路 27 とのいずれも設けないという構成が考えられる。しかし、この変位例の構成において、サブアレイ内の全てのセルデータがドントケアに設定されていた場合には、全てのマッチ線 ML のプリチャージ動作を停止し、全てのマッチアンプ MA の回路動作を停止することはできるけれども、サーチ線ドライバ 22 の動作を停止することができない。上記の実施形態では、全てのサーチ動作が停止可能か否かを判定するために、論理積回路 27 が設けられている。

#### 【0156】

##### <第 5 の実施形態>

##### [バッファアンプ部の構成について]

図 25 は、制御論理回路 24 からの出力信号のために用いられるバッファアンプの配置について説明するための図である。

30

#### 【0157】

図 11 の制御論理回路 24 から出力された制御信号 `force_hi_t`、マッチ線プリチャージ信号 `m1pre_n`、およびマッチアンプイネーブル信号 `mae` は、サブアレイ内の全てのマッチアンプ MA に出力される。したがって、サブアレイごとのエントリ数が多い場合には、バッファアンプを設ける必要がある。このため、図 25 の場合には、4 個のマッチアンプ MA ごとにバッファアンプ部 84 が設けられている。

#### 【0158】

図 25 を参照して、バッファアンプ部 84 は、4 個のマッチアンプ MA [0], MA [1], MA [2], MA [3] に対応して設けられ、バッファ 85, 86, 87 を含む。マッチ線プリチャージ信号 `m1pre_n` は、バッファ 85 によって整形された後に、対応する 4 個のマッチアンプ MA [0], MA [1], MA [2], MA [3] の各々の OR ゲート 77 に入力される。マッチアンプイネーブル信号 `mae` は、バッファ 86 によって整形された後に、対応する 4 個のマッチアンプ MA [0], MA [1], MA [2], MA [3] の各々の AND ゲート 78 に入力される。制御信号 `force_hi_t` は、バッファ 87 によって整形された後に、対応する 4 個のマッチアンプ MA [0], MA [1], MA [2], MA [3] の各々の NOR ゲート 80 に入力される。

40

#### 【0159】

なお、図 25 では、マッチアンプ MA [0], MA [1], MA [2] について、それぞれレジスタ REG3 [0], REG3 [1], REG3 [2] を除く部分の回路部分 8

50

3は、マッチアンプMA[3]の回路部分83と同一構成であるので、図示を省略している。

#### 【0160】

##### [バッファアンプ部の変形例]

図26は、第5の実施形態のTCA M装置において、バッファアンプ部の構成を説明するための図である。図26のバッファアンプ部84は、低消費電力化のために、図25のバッファアンプ部84の構成を変更したものである。

#### 【0161】

具体的に、図26のバッファアンプ部では、図25のバッファに代えて論理ゲートを設けることによって、入力波形の整形機能に加えて論理演算が可能になっている。すなわち、図26のバッファアンプ部84では、バッファ85に代えてORゲート89が設けられ、バッファ86に代えてANDゲート90およびインバータ91が設けられ、バッファ87に代えてORゲート92が設けられている。10

#### 【0162】

さらに、図26のバッファアンプ部84は、対応するマッチアンプMA[0]～MA[3]に設けられたレジスタREG3[0]～REG3[3]から出力された制御信号dnc\_hit[0]～dnc\_hit[3]のAND演算を行うANDゲート88を含む。ANDゲート88は、レジスタREG3[0]～REG3[3]から出力された制御信号dnc\_hit[0]～dnc\_hit[3]が全てドントケアを表す“H”レベル(設定値“1”に対応)の場合、“H”レベルの信号を出力する。20

#### 【0163】

ORゲート89は、マッチ線プリチャージ信号m1pre\_nとANDゲート88の出力信号とのOR演算結果を、局所的なマッチ線プリチャージ信号m1pre\_local\_nとして、対応するマッチアンプMA[0]～MA[3]に出力する。ANDゲート90は、マッチアンプイネーブル信号maeと、ANDゲート88の出力信号の論理レベルをインバータ91によって反転させた信号とのAND演算結果を、局所的なマッチアンプイネーブル信号mae\_localとして、対応するマッチアンプMA[0]～MA[3]に出力する。ORゲート92は、制御信号force\_hitとANDゲート88の出力信号とのOR演算結果を、局所的な制御信号force\_hit\_localとして、対応するマッチアンプMA[0]～MA[3]に出力する。30

#### 【0164】

したがって、対応するレジスタREG3[0]～REG3[3]から出力された制御信号dnc\_hit[0]～dnc\_hit[3]が全てドントケアを表す“H”レベル(“1”に対応する)の場合、局所的なマッチ線プリチャージ信号m1pre\_local\_nは“H”レベルに固定され、局所的なマッチアンプイネーブル信号mae\_localは“L”レベルに固定される。さらに、この場合、局所的な制御信号force\_hit\_localは“H”レベルに固定される。このため、これらの局所的な制御信号を伝達するための配線の充放電に要する電流消費を低減することができる。さらに、上記のバッファアンプ部は、第1～第4の実施形態においても必要な回路を変形したものであるので、実質的な面積の増加はほとんど生じない。40

#### 【0165】

##### <第6の実施形態>

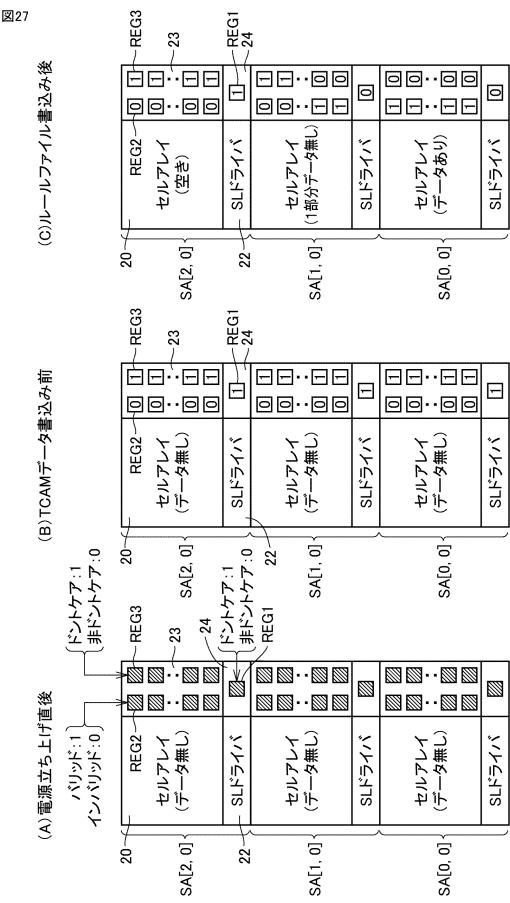

図27は、電源立ち上げ後において、各レジスタREG1, REG2, REG3へのデータ書き込みの手順について説明するための図である。図27では、3つのサブアレイSA[0, 0], SA[1, 0], SA[2, 0]が代表的に示されている。各サブアレイには、図10および図11で説明したレジスタREG1が制御論理回路24に設けられ、図18および図22で説明したレジスタREG2, REG3が行ごとに設けられる。

#### 【0166】

レジスタREG1は、サブアレイ全体のセルデータがドントケア(“1”)であるか、そうでない非ドントケア(“0”)であるかを設定するためのものである。レジスタRE50

G 2 は、対応する行が各 T C A M セルにデータが書込まれたバリッドエントリ（“ 1 ”）であるか、データ書き込まれていないインバリッドエントリ（“ 0 ”）であるかを示すものである。レジスタ R E G 3 は、対応する行のセルデータが全てドントケア（“ 1 ”）であるか、そうでない非ドントケア（“ 0 ”）であるかを設定するためのものである。

#### 【 0 1 6 7 】

各レジスタへのデータの書き込みは、T C A M 装置内部の専用回路（たとえば、図 1 9 のデータ判定回路 3 3 ）から行ってもよいし、T C A M 装置外部のプロセッサ（たとえば、図 6 の N P U 1 0 1 ）から行ってもよい。

#### 【 0 1 6 8 】

図 2 7 ( A ) を参照して、電源立ち上げ直後には、全てのレジスタ R E G 1 , R E G 2 , R E G 3 が不定状態となっている。図 2 7 ( A ) において、レジスタが不定状態であることを、ハッチングを付して示している。10

#### 【 0 1 6 9 】

図 2 7 ( B ) を参照して、T C A M 装置にデータを書込む前の初期状態において、各レジスタ R E G 1 に “ 1 ” ( ドントケア ) が設定され、各レジスタ R E G 2 に “ 0 ” ( インバリッド ) が設定され、各レジスタ R E G 3 に “ 1 ” ( ドントケア ) が設定される。

#### 【 0 1 7 0 】

図 2 7 ( C ) は、T C A M 装置に A C L ルールファイルを書き込んだ後の状態（サーチ可能状態）を模式的に表すものである。図 2 7 ( C ) に示すように、サブアレイ S A [ 0 , 0 ] の全ての行の T C A M セルには、データが書き込み済みである。サブアレイ S A [ 1 , 0 ] の一部の行の T C A M セルにはデータが書き込まれていない。サブアレイ S A [ 2 , 0 ] のいずれの行の T C A M セルにもデータは書き込まれていない。20

#### 【 0 1 7 1 】

ある行の T C A M セルにデータを書込む際には、当該行に対応するレジスタ R E G 2 の値は “ 0 ” ( インバリッド ) から “ 1 ” ( バリッド ) に変更され、レジスタ R E G 3 の値は、多くの場合、“ 1 ” ( ドントケア ) から “ 0 ” ( 非ドントケア ) に変更される。ただし、当該行の全てのセルデータがドントケアの場合には、レジスタ R E G 3 の値は “ 1 ” のまま維持される。さらに、サブアレイ内のいずれかの T C A M セルに “ 1 ” または “ 0 ” の値（すなわち、ドントケア以外）を書き込んだ時点で、レジスタ R E G 1 の値は “ 1 ” ( ドントケア ) から “ 0 ” ( 非ドントケア ) に変更される。30

#### 【 0 1 7 2 】

以上の手順に従って、各レジスタへのデータ書き込みが行われた結果、図 2 7 ( C ) に示すように、全行の T C A M セルにデータが書き込まれたサブアレイ S A [ 0 , 0 ] については、レジスタ R E G 1 は “ 0 ” ( 非ドントケア ) に設定され、各レジスタ R E G 2 は “ 1 ” ( バリッド ) に設定され、各レジスタ R E G 3 は “ 0 ” ( 非ドントケア ) に設定される。各行に対応するマッチアンプ M A は、各 T C A M セルに書込まれたデータとサーチデータの対応部分との比較結果に基づいて、“ H ” レベル（マッチ）または “ L ” レベル（ミス）の信号を出力する。

#### 【 0 1 7 3 】

一部の行の T C A M セルのデータ書き込みが行われたサブアレイ S A [ 1 , 0 ] については、レジスタ R E G 1 は “ 0 ” ( 非ドントケア ) に設定される。データ書き込みが行われたバリッドエントリに対応するレジスタ R E G 2 および R E G 3 はそれぞれ “ 1 ” ( バリッド ) および “ 0 ” ( 非ドントケア ) に設定される。これらの行に対応するマッチアンプ M A はサーチ結果に基づく信号（“ H ” レベル（マッチ）または “ L ” レベル（ミス））を出力する。40

#### 【 0 1 7 4 】

一方、サブアレイ S A [ 1 , 0 ] において、データ書き込みが行われていないインバリッドエントリに対応するレジスタ R E G 2 および R E G 3 の値は、それぞれ初期設定された “ 0 ” ( インバリッド ) および “ 1 ” ( ドントケア ) のまま変更がない。これらの行に対応するマッチアンプ M A は、レジスタ R E G 2 の値 “ 0 ” ( インバリッド ) に従って “ L ”50

” レベル（ミス）の信号を出力する。さらに、これらの未使用の領域については、レジスタ REG2 および REG3 の値が “0”（インバリッド）および “1”（ドントケア）にそれぞれ設定されていることによって、マッチ線 ML のプリチャージ動作が停止され、マッチアンプ MA の回路動作が停止される。これによって、T CAM 装置の消費電力を低減させることができる。

#### 【 0175 】

サブアレイ内の全 T CAM セルについてデータ書き込みが行われていないサブアレイ SA [ 2 , 0 ] については、レジスタ REG1 , REG2 , REG3 の値は、それぞれ初期設定された “1”（ドントケア）、“0”（インバリッド）、および “1”（ドントケア）のまま変更がない。各行に対応するマッチアンプ MA はレジスタ REG2 の値 “0”（インバリッド）に従って “L” レベル（ミス）の信号を出力する。レジスタ REG1 の値が “1”（ドントケア）に設定されていることによって、サブアレイ SA [ 2 , 0 ] のサーチ動作を停止することができるので（すなわち、マッチ線 ML のプリチャージ、マッチアンプ MA の回路動作、およびサーチ線ドライバ 22 のいずれも停止することができる）、消費電流を低減することができる。10

#### 【 0176 】

このように、各レジスタ REG1 , REG2 , REG3 の値を初期設定し、T CAM セルへのデータ書き込み時に、書き込みデータの値に応じて各レジスタ REG1 , REG2 , REG3 の値を変更することによって、効率良く容易に各レジスタの値が設定可能になる。20

#### 【 0177 】

なお、マッチアンプ MA が図 22 のように構成されていれば、レジスタ REG3 の値が “0”（非ドントケア）に設定されていても、レジスタ REG2 の値が “0”（インバリッド）に設定されておれば、マッチ線 ML のプリチャージおよびマッチアンプ MA の回路動作を停止することができる。したがって、この場合には、図 27 (B) の初期設定において、各レジスタ REG3 の値を “0”（非ドントケア）に設定してもよい。20

#### 【 0178 】

##### < 第 7 の実施形態 >

上述した第 1 ~ 第 6 の実施形態で説明した T CAM 装置の低消費電力化技術は、各サブアレイのマッチ線 ML に接続された T CAM セルが全てドントケア (don't care) に設定されている場合にのみ適用することができる。したがって、ドントケアに設定された比較的多数の T CAM セルが連続して並んでいたとしても、これらの T CAM セルが 2 つのマッチ線に跨っており、各マッチ線には “1” または “0” に設定された T CAM セルも含まれている場合には、前述した低消費電力化技術を適用することはできない。30

#### 【 0179 】

第 7 の実施形態では、上記のような場合に、T CAM セルデータの配列を変更することによって、前述の低消費電力化技術を適用可能にするものである。以下、図面を参照して詳しく説明する。なお、以下の説明で用いる入力データのビット幅、入力データの分割数などは一例であって、この例に限られるものではない。

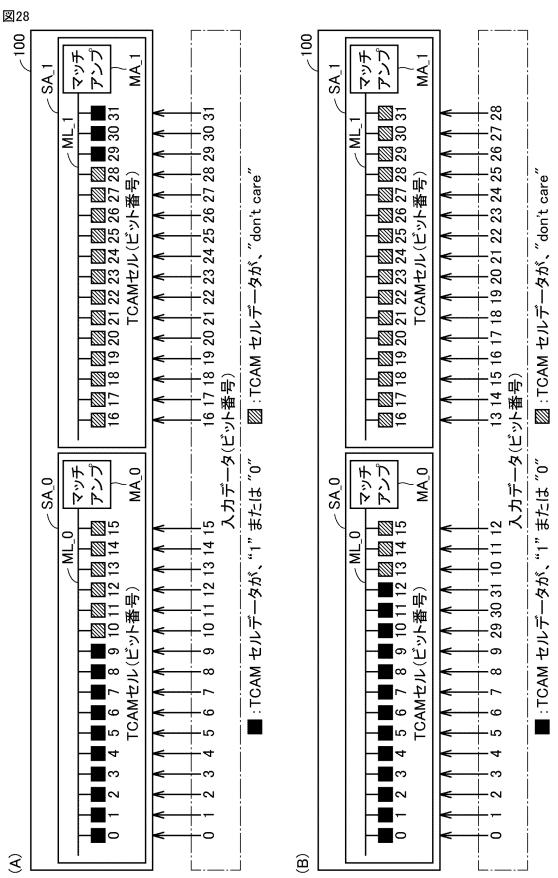

#### 【 0180 】

図 28 は、入力データの配列変換について説明するための図である。図 28 (A) では、入力データのビット幅が 32 ビットの場合に、配列変換を行わずにそのままの順序で 2 個のサブアレイ SA\_0 , SA\_1 に入力される例が示されている。すなわち、データ書き込み時に、32 ビットの書き込みデータのうち前半の 16 ビットの書き込みデータ（ビット番号 0 ~ 15 ）がサブアレイ SA\_0 の 16 個の T CAM セル（ビット番号 0 ~ 15 ）にそれぞれ書き込まれ、後半の 16 ビットの書き込みデータ（ビット番号 16 ~ 31 ）がサブアレイ SA\_1 の 16 個の T CAM セル（ビット番号 16 ~ 31 ）にそれぞれ書き込まれる。サーチ時についても同様に、32 ビットの入力サーチデータのうち前半の 16 ビットのサーチデータ（ビット番号 0 ~ 15 ）がサブアレイ SA\_0 の 16 個の T CAM セル（ビット番号 0 ~ 15 ）にそれぞれ入力され、後半の 16 ビットのサーチデータ（ビット番号 16 ~ 31 ）がサブアレイ SA\_1 の 16 個の T CAM セル（ビット番号 16 ~ 31 ）にそれ40

50

それ入力される。

#### 【0181】

ここで、データの配列変換を行わない場合には、図28(A)に示すように、ビット番号0からビット番号9までと、ビット番号29からビット番号31までの各TCAMセル(図中の黒四角)には、“1”または“0”的データが書き込まれているものとする。ビット番号10からビット番号28までの連続する19個のTCAMセル(図中のハッチングされた四角)の各々にはドントケアを表すデータが書き込まれているものとする。この場合、ドントケアを表すデータビット数は16以上あって連続しているが、これらのドントケアを表すデータが格納されたTCAMセルは、サブアレイSA\_0とサブアレイSA\_1とに跨っている。このために、各マッチ線ML\_0, ML\_1には、ドントケアに設定されたTCAMセル以外に“0”または“1”に設定されたTCAMセルも接続されているので、前述の低消費電力化技術を適用することができない。10

#### 【0182】

図28(B)の例は、図28(A)の例でデータ配列を変更することによって、サブアレイSA\_0のマッチ線ML\_1に接続された全てのTCAMセルがドントケアに設定されているようにしたものである。これによって、前述の低消費電力化技術が適用可能になる。具体的に、入力データ(書き込みデータおよびサーチデータ)のうちビット番号29~31の部分の配列順を繰り上げて、これらのデータがビット番号10~12のTCAMセルにそれぞれ入力されるようにデータ配列が変更される。さらに、入力データのうちビット番号10~28の部分の配列順を繰り下げて、これらのデータがビット番号13~31のTCAMセルにそれぞれ入力されるようにデータ配列が変更される。この結果、図28(B)に示すように、サブアレイSA\_1のマッチ線ML\_1に接続された全てのTCAMセル(ビット番号16~31)をドントケア(図中のハッチングされた四角)に設定することができるので、前述の低消費電力化技術(マッチ線ML\_1のプリチャージの停止およびマッチアンプMA\_1の動作停止)を実現することができる。20

#### 【0183】

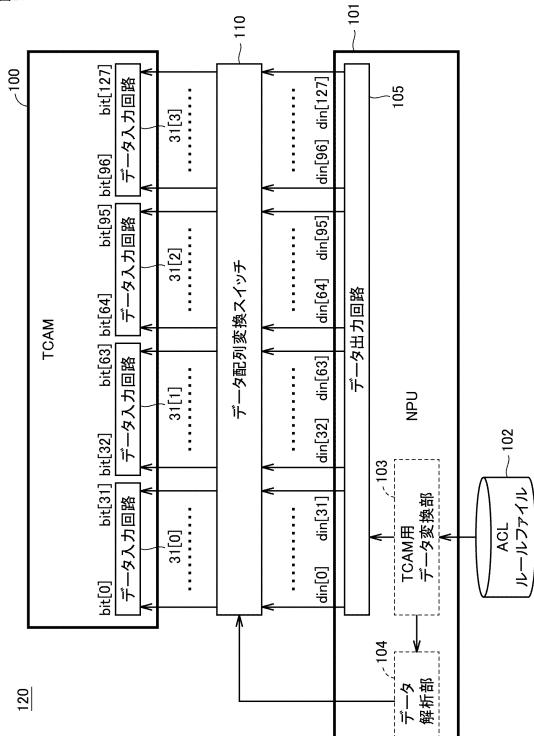

図29は、第7の実施形態の検索システムの構成を示すブロック図である。図29の検索システム120は、データ配列を変換するためのスイッチ回路110(以下、データ配列変換スイッチと称する)をさらに含む点で図6の検索システム120と異なる。図29には、入力データdinのビット数が128ビットの場合の例が示されている。30

#### 【0184】

図29を参照して、NPU(Network Processor Unit)101のデータ変換部103において、記憶装置102に格納されていたACLルールファイルはTCAM用データに変換される。TCAM用データは、“0”、“1”、および“ドントケア”(“1”でも“0”でもよい)の3値で構成される。TCAM用データは、入力データdin[0:127]として、NPU101のデータ出力回路105からデータ配列変換スイッチ110に入力される。

#### 【0185】

データ配列変換スイッチ110は、予め定められた規則に従って、入力データdin[0:127](書き込みデータおよびサーチデータ)の配列順を入れ替える。データ配列変換スイッチ110は、配列順の変更後の入力データをTCAM装置100のデータ入力回路31[0]~31[3]に入力する。図29の場合、データ入力回路31[0]~31[3]は、各サブアレイに対応して4つに分割されている(たとえば、データ入力回路31[0]はビット(bit)番号0~31に対応している)。データ配列変換スイッチ110における変換規則は、NPU101のデータ解析部104によって、TCAM用データの解析結果に基づいて定められる。40

#### 【0186】

図30は、データ配列変換の対象となるTCAM用データの一例が書き込まれたTCAM装置の記憶状態を模式的に示す図である。図30の記憶状態を表す図面は、図9に対応するものであり、図9と異なる点は、ドントケアデータが格納される領域211(図中で50

間隔の狭いハッチングが付された領域) の配置である。図 3 0 のその他の点は図 9 と同様であるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

#### 【 0 1 8 7 】

図 3 0 の T C A M 用データの配列の場合、ドントケアを表す領域のビット幅はサブアレイ S A のビット幅である 3 2 ビットを超えている部分があるが、1 つのサブアレイ S A のビット幅全体に亘ってドントケアに設定された部分がないので、これまで説明した第 1 ~ 第 6 の実施形態の低消費電力化技術を適用できない。

#### 【 0 1 8 8 】

そこで、たとえば、ビット番号 2 6 ~ 3 1 の部分の全データとビット番号 5 8 ~ 6 3 の部分の全データとを図 2 9 のデータ変換配列スイッチを用いて入れ替える。これによって 10 、ビット番号 3 2 ~ 6 3 の部分の 1 6 個のサブアレイ S A [ 0 , 1 ] , S A [ 1 , 1 ] ~ S A [ 1 5 , 1 ] について、インバリッドエントリを除く T C A M セルデータを全てドントケアにすることができる。この結果、サブアレイ S A [ 0 , 1 ] , S A [ 1 , 1 ] ~ S A [ 1 5 , 1 ] の各々について、レジスタ R E G 1 を “ 1 ” ( ドントケア ) に設定することによってサーチ動作を停止することができる。サブアレイ S A [ 1 5 , 1 ] についてはインバリッドエントリのレジスタ R E G 2 を “ 0 ” ( インバリッド ) に設定することによって、マッチアンプ M A の出力信号を “ L ” レベル ( ミス ) にすることができる。

#### 【 0 1 8 9 】

以上のとおり第 7 の実施形態では、サブアレイのビット幅以上のデータ幅でドントケアに設定された領域が、インバリッドエントリを除く T C A M 装置の全エントリについて存在する場合において、低消費電力化を可能にする技術を開示した。この場合、サブアレイのマッチ線に接続された T C A M セルが全てドントケアに設定されていなくても、各マッチ線に対応するビット番号に応じてデータ配列を入れ替えることによって、これまでの実施形態で説明した低消費電力化技術が適用可能になる。よって、低消費電力の検索システムを構築するためには、各マッチ線がどのビット番号に対応しているかを仕様書などでユーザに公開するのが望ましい。

#### 【 0 1 9 0 】

上記の実施形態では、T C A M 装置の全エントリについてデータ配列の変更を行ったが、データ配列変更するためのスイッチ回路をサブアレイ S A ごとに設ければ、サブアレイに属するエントリ単位でデータ配列の変更を行うことも可能である。

#### 【 0 1 9 1 】

##### < 第 8 の実施形態 >

第 1 ~ 第 7 の実施形態では、全サブアレイがほぼ同じタイミングでサーチ動作を行い、各サブアレイの出力信号に基づいてプライオリティ・エンコーダがサーチ結果を出力していた。第 8 の実施形態では、行方向に並ぶ( よって、共通のエントリに対応する ) 複数のサブアレイがパイプライン方式で順番に検索を行うように構成された例を開示する。この場合、各サブアレイは、前段のサブアレイのサーチ動作の終了後にサーチ動作を開始する。

#### 【 0 1 9 2 】

図 3 1 は、第 8 の実施形態による T C A M 装置の構成を示すブロック図である。図 3 1 の T C A M 装置では、4 個のサブアレイ S A \_ 0 ~ S A \_ 3 が代表的に示され、プライオリティ・エンコーダは図示していない。サーチ動作は、サブアレイ S A \_ 0 、サブアレイ S A \_ 1 、サブアレイ S A \_ 2 、サブアレイ S A \_ 3 の順に実行される。各サブアレイ S A は  $m + 1$  本のマッチ線 M L を有する。

#### 【 0 1 9 3 】

図 3 1 に示すように、サブアレイ S A \_ 0 においてマッチ線 M L \_ 0 , j (  $j = 1 , 2 , \dots , m$  ) のサーチ後の電位と電源電位 V D D とが、対応するマッチアンプ M A に入力され、このマッチアンプ M A から出力信号 m o \_ 0 , j が出力される。同様に、サブアレイ S A \_ i (  $i = 1 , 2 , 3$  ) において、マッチ線 M L \_ i , j (  $j = 1 , 2 , \dots , m$  ) のサーチ後の電位と、前段のサブアレイ S A \_ i - 1 の同一エントリの出力信号 m o \_ i -

10

20

30

40

50

1, j とが、対応するマッチアンプMAに入力され、このマッチアンプMAから出力信号 $m_o\_i, j$ が出力される。

#### 【0194】

図32は、図31のマッチアンプMAの構成例を示す回路図である。図32のマッチアンプMAは、図31のサブアレイSA\_i ( $i = 0, 1, 2, 3$ )において、マッチ線ML\_i, j ( $j = 1, 2, \dots, m$ )に接続されたマッチアンプの構成例を示している。図32では、図13のマッチアンプMAの構成を変更したものを示しているが、図16、図18、図22のいずれのマッチアンプMAについても同様に変更することができる。

#### 【0195】

具体的に、図32のマッチアンプMAは、図13（もしくは、図16、図18、または、図22）のマッチアンプMAに、Dフリップフロップ83、NANDゲート84、インバータ85、ANDゲート26をさらに追加したものである。Dフリップフロップ83およびANDゲート26は、図32ではマッチアンプMAの内部に設けられているように図示されているが、エントリごとにマッチアンプMAにそれぞれ対応して設けられていればよいので、マッチアンプMAの外部に設けられていても構わない。

#### 【0196】

Dフリップフロップ83は、前ステージのサブアレイの対応する行のマッチアンプMAの出力信号 $m_o\_pre$ （前サイクルのサーチ結果）を保持する。ただし、サーチ期間の最初にサーチ動作を行うサブアレイSA\_0（すなわち、 $i = 0$ ）については、前段の対応する行のマッチアンプMAの出力信号に代えて、電源電位VDDが入力される。

#### 【0197】

図13などの変更前の回路においてPチャネルMOSトランジスタ70のゲートに入力されていた信号は、インバータ85によって論理レベルを反転させた後に、NANDゲート84の第1の入力ノードに入力されるように変更される。NANDゲート84の第1の入力ノードには、上記のDフリップフロップ83の出力信号 $m_o\_pre$ （前サイクルのサーチ結果）が入力される。NANDゲート84の演算結果は、MOSトランジスタ70のゲートに入力される。

#### 【0198】

したがって、上記のDフリップフロップ83の出力信号 $m_o\_pre$ （前サイクルのサーチ結果）が“L”レベル（ミス）の場合は、MOSトランジスタ70のゲートには、“H”レベルの信号が入力される。この結果、MOSトランジスタ70は常にオフとなってマッチ線MLのプリチャージが停止する。

#### 【0199】

ANDゲート26は、上記のDフリップフロップ83の出力信号 $m_o\_pre$ （前サイクルのサーチ結果）と、図13（もしくは、図16、図18、または、図22）に示す変更前の構成のマッチアンプMAの場合の出力信号 $m_o\_now$ とのAND演算を行い、演算結果をマッチアンプMAの出力信号 $m_o$ として出力する。ANDゲート26は、図5のANDゲートに対応するものであり、図5のANDゲート26をマッチアンプMA内に取り込んだものと考えることができる。

#### 【0200】

したがって、上記のDフリップフロップ83の出力信号 $m_o\_pre$ （前サイクルの対応する行のサーチ結果）が“L”レベル（ミス）の場合には、ANDゲート26の出力信号（すなわち、マッチアンプMAの出力信号 $m_o$ ）は“L”レベル（ミス）となる。図32にその他の点は、図13（もしくは、図16、図18、または、図22）のマッチアンプMAと同様であるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

#### 【0201】

図33は、図31のTCAM装置の動作を説明するための図である。各マッチアンプMAにおいてハッチングを付した領域は、TCAMセルデータがドントケアになっていることを示す。

10

20

30

40

50

**【0202】**

第1サイクルにおいて、サブアレイSA\_0がサーチ動作を行う。各エントリのサーチ結果(ヒット(hit)の場合“1”、ミス(miss)の場合“0”)は、次段のサブアレイSA\_1のマッチアンプ部23の対応する行のDフリップフロップ83に格納される。図32で説明したようにDフリップフロップ83に“0”が格納されている場合には、次の第2サイクルにおいて対応する行のマッチ線MLプリチャージが停止される。

**【0203】**

第2サイクルにおいて、通常は、サブアレイSA\_1の各行のうち前段のサブアレイSA\_0のサーチ動作でヒットになった行のみサーチ動作が行われる。しかしながら、図33の場合、サブアレイSA\_1の全TCA Mセルデータがドントケアに設定されているので、レジスタREG1を“1”(ドントケア)に設定することによって、サブアレイSA\_1全体のサーチ動作が停止される。第1サイクルでヒットとなったエントリの出力信号は、自動的にヒットとなり、次段のサブアレイSA\_2のマッチアンプ部23の対応するDフリップフロップには“1”が書き込まれる。その他のDフリップフロップには“0”が書き込まれる。

10

**【0204】**

第3サイクルにおいて、サブアレイSA\_2の各行のうち、サブアレイSA\_1からヒットを表す信号が入力された行についてのみサーチ動作が行われる。Dフリップフロップ83に“0”が格納されている行については、マッチ線プリチャージが停止される。サブアレイSA\_2においてサーチ結果がヒットとなった行については、次段のサブアレイSA\_3のマッチアンプ部23の対応するDフリップフロップ83に“1”が格納される。サブアレイSA\_3のその他の行のDフリップフロップ83には“0”が格納される。

20

**【0205】**

第4サイクルにおいて、サブアレイSA\_3のTCA Mセルアレイについて検索動作が行われる。この場合、前段のサブアレイSA\_2からヒットを表す信号が入力された行のうちで、マッチ線220, 221に対応する行を除いたものについてサーチ動作が行われる。マッチ線220, 221に接続されたTCA Mセルは全てドントケアに設定されているので、レジスタREG3に“1”(ドントケア)を設定することによって、これらのマッチ線220, 221のプリチャージおよび対応するマッチアンプMAの回路動作が停止される。マッチ線220, 221に接続されたマッチアンプMAからはプライオリティ・エンコーダ30にヒットを表す信号が自動的に出力される。その他のサーチ動作が行われた行のマッチアンプMAからもサーチ結果がプライオリティ・エンコーダ30に出力される。

30

**【0206】**

このように、第8の実施形態では、第1～第7の実施形態で説明した低消費電力化技術に組合せて、行方向に並ぶ複数のサブアレイをパイプライ方式で順番に検索することによって、前サイクルでヒットとなったエントリのみサーチ動作を行うようとする。これによって、さらに消費電力を低減することができる。

**【0207】**

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

40

**【符号の説明】****【0208】**

11 SRAMセル(Xセル)、12 SRAMセル(Yセル)、13 データ比較部、20 セルアレイ、21 書込みドライバ、22 サーチ線ドライバ、23 マッチアンプ部、24 制御論理回路、27 論理積回路、30 プライオリティ・エンコーダ、31 データ入力回路、32 コマンド入力回路、33 データ判定回路、40, 44, 45, 83 フリップフロップ、69 ラッチ回路、84 バッファアンプ部、85, 86, 87 バッファ、100 TCA M装置、102 記憶装置、103 データ変換部

50

、104 データ解析部、105 データ出力回路、110 スイッチ回路（データ配列変換スイッチ）、120 データ検索システム、220, 221, ML マッチ線、BL ビット線対、MA マッチアンプ、MC TCAMセル、ND1, ND2 記憶ノード、REG1, REG2, REG3 レジスタ、SA サブアレイ、SL サーチ線対、VDD 電源電位、WLX, WLY ワード線、clk クロック信号、d 書込みデータ、force\_hi\_t 制御信号、mae マッチアンプイネーブル信号、m1pre マッチ線プリチャージ信号、mo 出力信号、sd 入力サーチデータ、sle サーチ線イネーブル信号。

【図1】

【図2】

| SRAMセル(Xセル) | SRAMセル(Yセル) | TCAMセルデータ        |

|-------------|-------------|------------------|

| "1"         | "0"         | "0"              |

| "0"         | "1"         | "1"              |

| "0"         | "0"         | "x" (don't care) |

| "1"         | "1"         | 不使用              |

【図3】

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

| プロトコル番号 | 宛先ポート番号 | 送信元ポート番号   | 宛先IPアドレス | 送信元IPアドレス         |

|---------|---------|------------|----------|-------------------|

| 201     | 17      | 750:750    | 53:53    | 183.167.79.44/32  |

| 202     | 6       | 123:123    | 0:65535  | 224.180.117.99/32 |

| 203     | 17      | 1024:65535 | 69:69    | 183.167.79.44/32  |

| :       | :       | :          | :        | :                 |

【図8】

【図10】

〔 図 9 〕

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図17】

【 図 1 8 】

【図19】

【 図 2 0 】

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

【図25】

【図26】

【図27】

【 図 2 8 】

【図29】

図29

【図30】

図30

【図31】

図31

【図32】

図32

【図33】

図33

---

フロントページの続き

(56)参考文献 特開2005-228461(JP,A)

特開昭63-31091(JP,A)

特開2002-197873(JP,A)

特開2000-228090(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 15 / 04