(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-170893

(P2009-170893A)

(43) 公開日 平成21年7月30日(2009.7.30)

(51) Int.Cl.

H01L 23/52 (2006.01)

H01L 21/301 (2006.01)

F 1

H01L 23/52

H01L 21/78

H01L 21/78

テーマコード(参考)

Z

Q

M

審査請求 未請求 請求項の数 3 O L 外国語出願 (全 14 頁)

(21) 出願番号 特願2008-313895 (P2008-313895)

(22) 出願日 平成20年12月10日 (2008.12.10)

(31) 優先権主張番号 11/953,541

(32) 優先日 平成19年12月10日 (2007.12.10)

(33) 優先権主張国 米国(US)

(71) 出願人 500575824

ハネウェル・インターナショナル・インコ

ーポレーテッド

アメリカ合衆国ニュージャージー州079

62-2245, モーリスタウン, コロン

ピア・ロード 101, ピー・オー・ボッ

クス 2245

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】可撓性半導体組立体を製造する方法

(57) 【要約】 (修正有)

【課題】複数の半導体ダイが形成されたウエーハから、少ない工程で半導体ダイグループからなる集積回路パッケージを作製する方法を提供する。

【解決手段】半導体ダイのグループからなる可撓性半導体組立体を製造する半導体パッケージの製造方法において、2種類の半導体ダイ102, 104が形成された半導体ウエーハ100の一面に可撓性誘電体膜を貼着する工程と、半導体ダイ102, 104間の相互電気的接続を行い、かつ半導体ダイ102, 104間を可撓性誘電体膜の表面に達するまで切断することで可撓性誘電体膜で接続されたダイグループ106を形成する工程と、ダイグループ106間を切断することで半導体100を複数のダイグループ106に分離する工程からなる。

【選択図】図1a

平面図

**【特許請求の範囲】****【請求項 1】**

複数の半導体ダイを備え且つ第1の側部及び第2の側部を定めるウェーハから集積回路パッケージを作製する方法であって、

前記集積回路パッケージを形成する目的とした少なくとも2つの隣接する半導体ダイのグループを電気的に相互接続する可撓性誘電体膜を前記ウェーハの第1の側部に取り付けてウェーハ組立体を形成する段階と、

1つ又はそれ以上の屈曲領域を形成するために前記第2の側部からウェーハ材料を除去し、該ウェーハ材料が前記ウェーハの前記可撓性誘電体膜の深さまで実質的に除去され、更に前記グループ内の少なくとも2つの隣接する半導体ダイの間で除去されるようにする段階と、

前記半導体ダイのグループを前記ウェーハ組立体に接続する前記ウェーハ材料及び可撓性膜材料を除去することによって、前記集積回路パッケージを個別分離する段階と、を含む方法。

**【請求項 2】**

前記可撓性誘電体膜を取り付ける段階が、

前記可撓性誘電体膜を貫通して前記少なくとも2つの隣接する半導体ダイに至るまでバイアを生成する段階と、

前記バイア内に導電性材料を堆積させる段階と、

前記バイアの間に導電性相互接続ルートを形成して相互接続インターフェースを生成する段階と、

を含む、

請求項1に記載の方法。

**【請求項 3】**

可撓性絶縁材料の複数の連続する層を第1の連続する層が前記ウェーハに取り付けられ、後続の各連続する層がその前の連続する層に取り付けられるように取り付けて、前記可撓性誘電体膜を形成する段階と、

前記各層が取り付けられた後、(i)前記可撓性絶縁材料層の1つ又はそれ以上を貫通するバイアを生成する段階、(ii)前記バイア内部に導電性材料を堆積させる段階、及び(iii)前記バイア間に導電性相互接続ルートを形成して相互接続インターフェースを生成する段階によって、電気的相互接続部を生成する段階と、

を更に含む、

請求項2に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体に関し、より具体的には可撓性半導体組立体の製造に関する。

**【背景技術】****【0002】**

磁力計又は加速度計などの或る種のセンサは、3軸で検知するように設計されている。通常これらの軸は直交しており、従って、センサ軸のうちの1つは電子部品を装着するのに使用されるプリント基板(PCB)又は他の組立体と垂直に装着することが必要である。3軸センサを生成する1つの方法は、可撓性相互接続部によって接続された2つ又はそれ以上の半導体ダイからなる集積回路を形成することである。可撓性相互接続部は、半導体ダイの1つが他のダイに対し直角になるように90°の角度に曲げることができる。米国特許第7,067,352号には、このような組立体が記載されており、当該特許は引用により全体が本明細書に組み込まれる。半導体デバイスをこのようにして配列すると、通常、シリコン効率(例えば、シリコンスペースの効率的な利用)が高くなり、半導体デバイス間の必要な相互接続の長さがより短くなり、結果として、半導体デバイス間を信号が移動するのに要する時間が短縮される。より短い相互接続長さはまた、寄生容量及び寄

生抵抗が減少し、よって消費電力が低減される。

【0003】

現在のところ、可撓性半導体組立体を形成するには、当該組立体で使用するための個々の半導体ダイは、可撓性フィルムを取り付けて相互接続を形成できるようになる前に、組立体治具内にギャザリングされて互いに対し正確に位置決めされることが必要となる。このプロセスでは、ダイをギャザリングして正確に配置するための特別なピックアンドプレース装置を必要とし、可撓性相互接続部によって接続されるダイを必要とする3軸センサ又は他の何れかの半導体組立体の製造に時間及びコストが付加される。従って、可撓性半導体組立体をより効率的に製造する方法が求められる。

【先行技術文献】

10

【特許文献】

【0004】

【特許文献1】米国特許第7,067,352号公報

【発明の概要】

【0005】

可撓性半導体組立体を製造する方法が記載される。本発明の1つの実施形態は、固体ウェーハから集積回路パッケージを作製する方法の形態をとることができる。ウェーハは、互いに隣接して配列された少なくとも2つの半導体ダイを備えることができる。少なくとも2つのダイは、集積回路パッケージの一部を形成することを目的とする。可撓性誘電体膜がウェーハの第1の側部に取り付けられ、ウェーハ組立体を形成することができる。可撓性誘電体膜は、少なくとも2つの隣接する半導体ダイのグループを電気的に相互接続することができる。次いで、ウェーハ材料がウェーハの第2の側部から除去されて、1つ又はそれ以上の屈曲領域を形成することができ、ここでグループ化されたダイ間のウェーハ材料は、ウェーハ絶縁材料の深さまで実質的に除去される。次いで集積回路パッケージは、半導体ダイのグループをウェーハ組立体の残りに接続するウェーハ材料及び可撓性膜材料を除去することによって個別分離することができる。最後に、可撓性誘電体膜は、2つの半導体ダイが互いに或る角度（好ましくは90°）で配置されるように、1つ又はそれ以上の屈曲領域で曲げることができる。本方法は、事前に個別分離された個々の半導体ダイが可撓性相互接続部の施工前に機械的デバイスによって互いに対し正確な関係で配列されることを必要とせず、むしろ、可撓性相互接続部は、半導体ダイの複数のグループを保持する固体ウェーハに直接施工することができる。本方法は作製ステップを削減し、製造コストを低減させる。

20

【0006】

30

これら並びに他の態様及び利点は、添付図面を適切に参照しながら以下の詳細な説明を読むことによって当業者には明らかになるであろう。更に、この要約は単なる実施例であり、請求項に記載された本発明の範囲を限定するものではない点は理解される。

【図面の簡単な説明】

【0007】

40

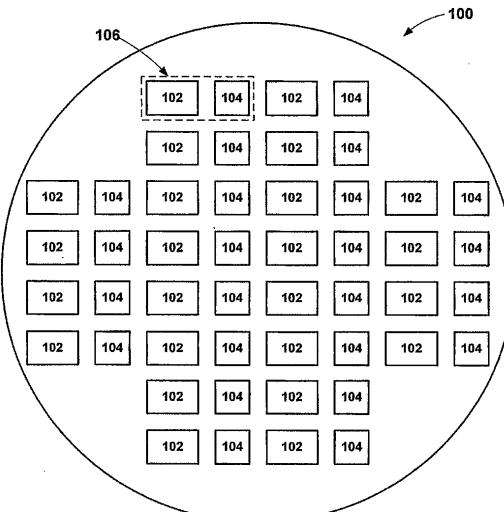

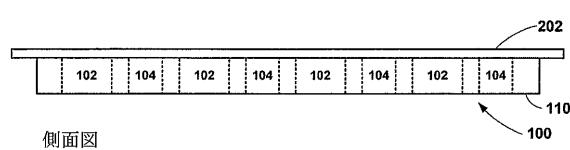

【図1a】標準的な半導体ウェーハの平面図である。

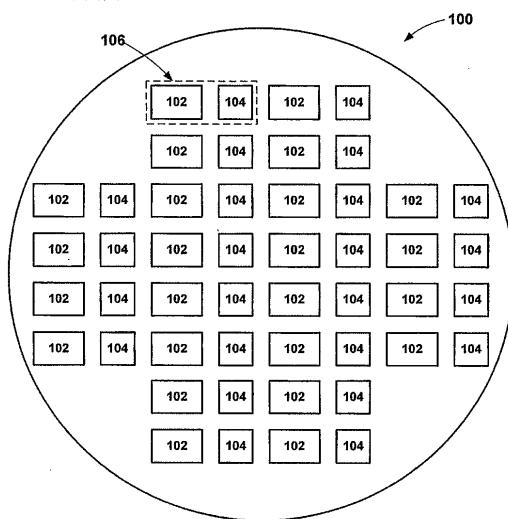

【図1b】標準的な半導体ウェーハの側面図である。

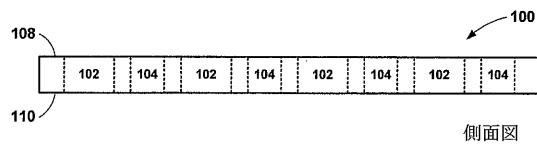

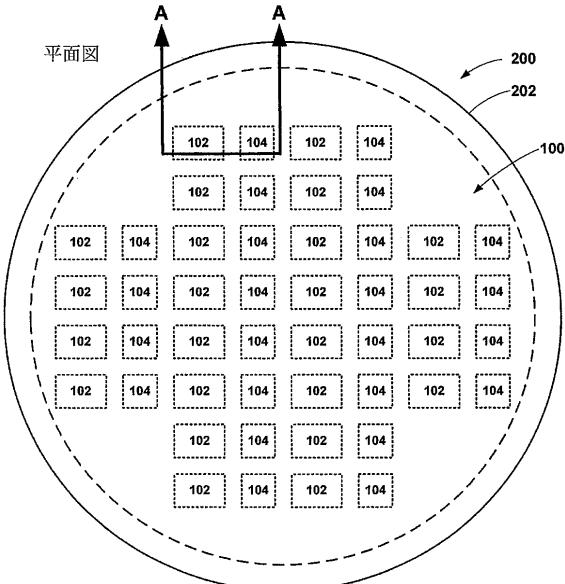

【図2a】半導体ウェーハ組立体の平面図である。

【図2b】半導体ウェーハ組立体の側面図である。

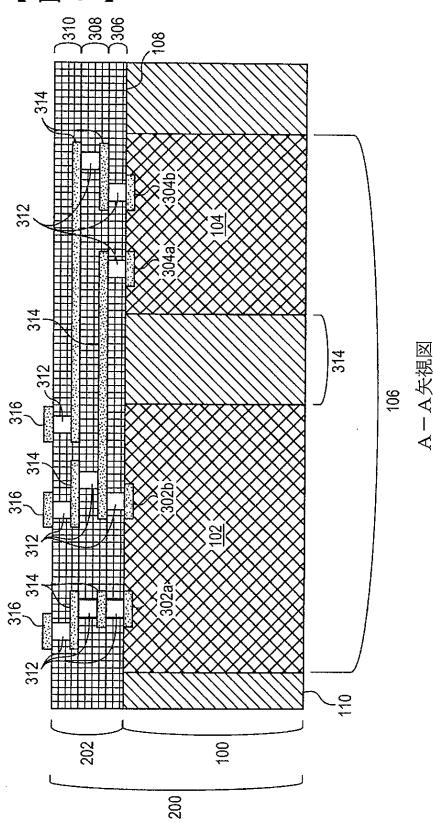

【図3】半導体ウェーハ組立体内の半導体ダイのグループの断面図である。

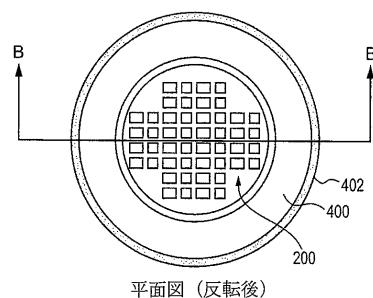

【図4a】ダイシングテープフレームに固定された半導体ウェーハ組立体の平面図である。

。

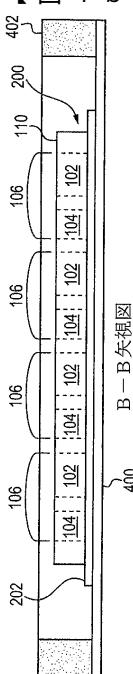

【図4b】ダイシングテープフレームに固定された半導体ウェーハ組立体の断面図である。

。

【図5】ダイシングテープフレームに固定され且つチャックによって保持された半導体ウェーハ組立体の断面図である。

【図6】可撓性集積回路パッケージの側面図である。

50

【図7】可撓性集積回路パッケージの側面図である。

【図8】可撓性集積回路パッケージを作成する方法を表すフローチャートである。

【発明を実施するための形態】

【0008】

図1aは、標準的な半導体ウェーハ100の平面図である。ウェーハ100は、ダイ102及びダイ104のような複数の半導体ダイを含む。例えば、各ダイ102は、3次元集積回路センサ組立体内のX-Y軸センサを対象としたものとすることができます。同様に各ダイ104は、同じ集積回路センサ組立体内のZ軸センサを対象としたものとすることができます。同時に、ダイ102及びダイ104のペアは、集積回路パッケージを形成することを目的としたダイグループ106の一部とみなすことができる。図1aでは1つのダイグループ106のみが強調して表示されているが、ウェーハ100全体では多くのダイグループが存在することができる。

【0009】

X-Y軸センサとして機能する標準的なダイ102は、約1.5mm×1.6mmの大きさとすることができますが、ダイ102は、本明細書に記載の本発明に悪影響を及ぼすことなく、数桁大きく又は小さくすることができます。Z軸センサとして機能する標準的なダイ104は、約0.7mm×1.6mmの大きさとすることができますが、ダイ104は、本明細書に記載の本発明に悪影響を及ぼすことなく、数桁大きく又は小さくすることができます。標準的なウェーハ100は、300ミクロンから800ミクロンの厚みとすることができますが、ウェーハは、ハンドリングステップ中のダイ102及び104の破損の低減の一助とするにより厚く形成するか、或いは、その後のダイ・シニングステップの必要性を低減又は排除するより薄く形成することができます。標準的なウェーハ100は、100mmから300mmの間の直径とすることができますが、本発明に影響することなくより大きく或いはより小さくすることができます。

【0010】

図1bは、標準的な半導体ウェーハの側面図である。ウェーハは、第1の側部108及び第2の側部110を有する。ウェーハの第1の側部108は、半導体ダイ102及び104の上側とみなすことができ、ここでは各ダイは、多くの公知の方法の1つによって構成された集積回路を備える。例えば、集積回路は、成膜、リソグラフィ、及びマスキング、エッチング、打ち込み、及び/又は拡散の技法によってペア・ウェーハ上に構成することができます。

【0011】

図2aは、半導体ウェーハ組立体200の平面図である。図2aでは、可撓性誘電体膜202がウェーハ100の第1の側部108に取り付けられ、ウェーハ組立体200を生成している。図2bは、半導体ウェーハ組立体200の側面図である。通常、可撓性誘電体膜202は、パッシベーション被膜として、或いは層間絶縁層として使用することができます。材料を含むことができる。好ましい実施形態において、可撓性誘電体膜202は、ポリイミド材料を含むことができる。液晶ポリマー材料のような他の可撓性材料を使用してもよい。使用される材料は、図5から図7で説明される折り畳み領域での屈曲を可能にするのに十分な可撓性があり、また、後続のあらゆる薄膜作製プロセスにおいて使用される処理温度及び化学物質にも耐えることもできる。

【0012】

図3は、半導体ウェーハ組立体200内の半導体ダイ102及び104のグループ106の断面図である。単なる例証として、取り付けられる可撓性誘電体膜202は、第1の層306、第2の層308、及び第3の層310の3つの層として示される。可撓性誘電体膜202は、代替として、単層或いは3つよりも多い又は少ない層からなる複数層からなることができる。ダイ102及び104は、電気的相互接続パッド302a、302b及び304a、304bそれぞれと共に形成されて示される。ダイ102及び104は、2つよりも多い又は少ない電気的相互接続パッドを各々有することができ、パッドは、ウェーハ100の通常の製作プロセスの一部として形成することができる。パッド302a

10

20

30

40

50

及び 302b は、半導体ダイ 102 内の集積回路への電気的接続を形成する。同様に、パッド 304a 及び 304b は、半導体ダイ 104 内の集積回路への電気的接続を形成する。

### 【0013】

図 3 は更に、層 306、308、及び 310 の間並びに層 306 とダイ 102 及び 104 との間の電気的相互接続部を形成する複数の個別バイアを示す。層 306、308、及び 310 上の様々なバイア間の電気的相互接続部を形成する複数のルート 314 が更に示される。図 3 におけるルート及びバイアの特定の配置は、単に例証として示され、ある位置、層、又は相互接続ポイントへのこのような配置を限定することを意味するものではない。

10

### 【0014】

図 3 に示された可撓性誘電体膜 202 は、3 つの層 306、308、及び 310 を備えているが、半導体ダイ 102 及び 104 の外部及び内部の相互接続要件に応じて、膜 202 内により少ない層又は更なる層を作成してもよい。層は、各々同じ材料で作製することができ、或いは異なる可撓性材料を含むことができる。一例として、層 306、308、310 はポリイミド誘電体を用いて形成することができ、ルート 314 及びバイア 312 は、銅、アルミニウム、金、又は白金の導電体とすることができます。

### 【0015】

1 つの実施形態において、可撓性誘電体膜 202 は、オートクレーブ内の加圧及び加温下でウェーハ 200 の第 1 の側部 108 に積層された層 306 を備えることができる。積層後、可撓性誘電層 306 は、後続の薄膜処理のための新しい平坦面を提供することができる。また、ウェーハ 200 の第 1 の側部 108 上に可撓性誘電体膜 202 を作成する他の方法を使用してもよい。例えば、層 306 はスピノン加工とすることができます。

20

### 【0016】

可撓性誘電体膜 202 の第 1 の層 306 が作成された後、第 1 の層 306 の上面からダイパッド 302a、302b、304a、及び 304b まで下がって 1 つ又はそれ以上のバイア 312 を作成することができる。通常、フォトリソグラフィプロセスを利用して、バイア 312 を作成することができる。他の公知の処理方法を利用してバイア 312 を作成してもよい。

### 【0017】

例えばプランケット堆積により、可撓性誘電体膜 202 の第 1 の層 306 の上面の上に可撓性導電層を堆積することができる。プランケット堆積は、蒸着、スパッタリング、メッキなどの公知の物理的堆積技法により、或いは化学蒸着 (CVD) のような化学的堆積技法により施工することができる。導電性層は、銅、アルミニウム、金、白金のような金属、或いは他のこのような導電性材料を含むことができる。導電性金属に加えて、他の相互接続材料を使用してもよい。

30

### 【0018】

プランケット堆積は、導電性材料をバイア 312 内及び層 306 の上面に堆積させる。次にパターン形成プロセスにより、層 306 の上面から導電性材料の堆積部分が選択的に除去され、半導体ダイ 102 及び 104 を相互接続することができる導電体ルートを形成することができる。図 3 に示すように、パターン形成プロセスが第 1 の層 306 の上面から導電性材料の一部を除去し、電気的相互接続パッド及びルート 314 が形成される。

40

### 【0019】

パターン形成ステップが完了した後、可撓性膜 202 の第 2 の層 308 を堆積することができる。第 2 の層 308 は、第 1 の層 41 と同じ材料を含むことができ、或いは異なる可撓性材料を含むことができる。第 2 の層 308 は、積層又はスピノン施工のような公知の方法によって堆積することができる。次いで、上述の誘電体堆積プロセス、並びに作製、導電体堆積、及び相互接続パターン形成のプロセスを繰り返し、可撓性誘電体膜 202 の第 2 の層 308 のための付加的な電気的相互接続部を形成することができる。

### 【0020】

50

図3に示すように、第2の層308は、選択された位置でバイア312を含み、各バイア312には、導電性材料が堆積されている。電気的相互接続ルート314を用いて、ボンディングパッド及び隣接する上層310への電気的相互接続部が形成される。例示的に、可撓性誘電体膜202の上層310は最終のパッシベーション被膜である。任意選択的に、最終のパッシベーション被膜は、ワイヤボンディングパッド316、或いは半田ボール又はバンプのような外部電気接続を行う他の手段を含むことができ、これらは図6及び図7を参照して更に論議される。

【0021】

図3には電気的相互接続部のみが示されているが、レジスタ又はキャパシタのような薄膜受動素子もまた可撓性誘電体膜202の1つ又はそれ以上の層内に含めることができる。通常、受動素子は、(ウェーハの側部108上の)半導体ダイ102及び104の上面の直ぐ上にある可撓性誘電体膜202の領域に配置され、ダイ104とダイ104との間の領域314の上には配置されない。これは、受動素子が可撓性誘電体膜202の素子の他の部分ほどは可撓性ではない可能性があり、従って、可撓性誘電体膜202の屈曲されない区域に受動素子を設置することで、屈曲中の受動素子への損傷を防ぐことができるためである。しかしながら、屈曲プロセス後の可撓性誘電体膜202の曲率が、受動素子が損傷を受けず正常に作動できるようなものである場合には、受動素子は、領域314の上方の可撓性誘電体膜202の領域内に配置することができる。

10

【0022】

電気的相互接続部が可撓性フィルム202内に生成された後、屈曲領域を生成し、ダイグループ106を個別分離することができる。図4a、図4b、及び図5は、屈曲領域を作成してダイグループを個別分離するための本方法の好ましい実施形態を示す。図4aは、接着性ダイシングテープ400によってダイシングテープフレーム402に固定された半導体ウェーハ組立体200の平面図である。図4bは、ダイシングテープフレーム402に固定された半導体ウェーハ組立体200の断面図である。図4a及び図4bは、屈曲領域を生成することができ且つダイグループを個別分離することができるようとする、ウェーハ組立体200を保持する好ましい方法を示す。図4a及び図4bによれば、ダイシングテープ400は、当該技術分野で一般に知られた方法によって、堅固に延伸してダイシングフレーム402に取り付けることができる。ウェーハ組立体200を反転し、ダイシングテープ400上に存在する接着剤によりダイシングテープ400に固定することができる。

20

30

【0023】

代替として、ウェーハ組立体200は、他の手段により保持することもできる。例えば、ウェーハ組立体200は、ダイシングテープ400以外の手段によってダイシングテープフレーム402以外の作業表面に固定することができる。例えば、当該技術分野で公知の多くのダイボンディング接着ペーストの1つのような結合剤(図示せず)を用いて、ウェーハ組立体200を別代替の作業表面(図示せず)に保持することができる。代替として、結合剤は、ダイボンディングフィルムとすることができます。結合剤は、ウェーハ組立体200を作業表面に付加する何らかの材料とすることができます。別の実施形態では、ウェーハ組立体200は、真空などの他の手段によって作業表面に直接付加することができる。このような実施形態では、結合剤は必要ではない可能性がある。ウェーハ組立体200は、作業表面に直接に接触することができ、或いは真空固定の場合のガスケット材料のような中間材料により分離することができる。

40

【0024】

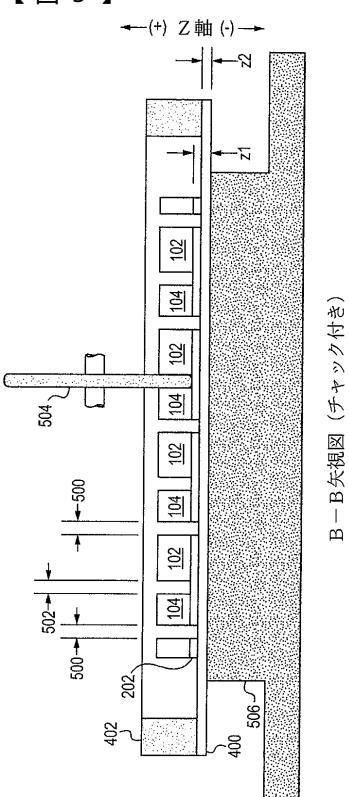

図5は、ダイシングテープフレーム402に固定された半導体ウェーハ組立体200の断面図であり、ダイシングテープフレーム402は、真空チャック506のような作業表面に固定されている。チャック506は、何れかの好適な設計のものとすることができます、多くのものは、ダイシングテープフレームを保持する当該技術において公知である。ダイグループ106を利用可能な個別のデバイスに分離するために、グループ106は、ウェーハ組立体200から分離する必要がある。好ましい実施形態において、グループ106

50

は、ダイシングソー 504 を用いて個別分離され、ダイシングテープフレーム 402 はチャック 504 によって保持される。代替として、ウェーハ組立体 200 が上述のような代替の作業表面に直接又は間接的に取り付けられる間、グループ 106 はダイシングソー 504 を用いて個別分離することができる。

【0025】

個別分離プロセスの間、ダイ 102 とダイ 104 との間の屈曲ギャップ 502 を最初に生成することができる。ギャップ 502 を生成するため、ダイシングソー 504 の深さは、最初に、チャック 506 の上部からの相対高さ  $z_1$  に設定することができる。この高さに設定されていると、ダイシングソー 504 を用いて、ダイ 102 とダイ 104 との間のウェーハ材料を除去するが、ダイ 102 とダイ 104 とを相互接続する可撓性誘電体膜 202 を除去しないようにすることができる。ダイシングソー 504 の  $z$  軸高さは、ギャップ 502 内のウェーハ材料の実質的に全てが除去されるように設定することができる。代替として又は付加的に、ダイシングソー 504 が可撓性膜層 202 を損傷しないように、ウェーハ材料の僅かな層が可撓性膜層 202 の上に残ることができる。ギャップ 502 内のウェーハ材料のあらゆる残りの層は、屈曲ギャップ 502 の領域内の可撓性膜層 202 の所望の屈曲特性に影響を及ぼさないように十分に薄くなければならない。別の代替手段として、ウェーハ材料の全てがダイ 102 とダイ 104 との間で完全に除去されるのを確保するために、ダイシングソー 504 がギャップ 502 内の可撓性膜層の僅かの部分を除去できるようにすることができる。ダイシングソーは、屈曲ギャップ 502 を生成する好みしい方法であるが、他の方法を使用してもよい。例えば、エッチングを用いて、ウェーハ材料を実質的に可撓性膜 202 の深さにまで除去することができる。レーザアブレーションのような、他の材料除去方法を使用してもよい。

10

20

30

【0026】

ダイ 102 及び / 又はダイ 104 の最終厚み及び相対間隔が可撓性膜 202 の最小許容曲げ半径を決定付けることができるので、屈曲ギャップ 502 の所望の幅は、該最終厚みによって左右される可能性がある。屈曲ギャップ 502 は、最も好ましくは、一般的なダイシングソーのブレード幅に一致し且つ標準的な 3 軸センサパッケージで使用されるダイ間の適切な屈曲半径を可能にするような、35ミクロン幅とすることができます。しかしながら、屈曲ギャップ 502 の幅は、適度に 10ミクロンから 100ミクロンの範囲内とすることができる。必要に応じて、より大きなギャップ幅も実施可能である。ダイシングソーを用いて形成される屈曲ギャップ 502 の幅の通常の範囲は、10ミクロンから 50ミクロンであるが、より幅広のソーを用いることにより、或いはギャップ 502 内にソーを複数回通過させることによって、より大きなギャップ幅を生成することができる。エッチングの結果としての屈曲ギャップ 502 幅の通常の範囲は、10ミクロンから 100ミクロンである。

【0027】

屈曲ギャップ 502 が生成された後、ダイグループ 106 は、カットパス 500 のようなカットパスを生成することによって互いに、及びウェーハ 200 から分離することができる。カットパス 500 を生成するために、ダイシングソー 504 はチャック 506 の上から相対高さ  $z_2$  に設定することができる。この高さに設定されていると、ダイシングソー 504 を用いて、個々のダイグループ 106 間のウェーハ材料及び可撓性膜層 202 を除去することができる。ダイシングソー 504 の  $z$  軸高さは、カットパス 500 内の可撓性膜層 202 の実質的に全てが除去されるように設定することができる。代替として、或いは付加的に、存在する場合にはダイシングテープ 400 の一部も除去されるようにダイシングソー 504 の  $z$  軸高さを設定することができ、ダイグループ 106 が互いから確実に分離されるようになる。

40

【0028】

図 5 では、カットパス 500 が 1 軸のみで示されているが、カットパス 500 は、1つよりも多くの軸に向けることができ、これによりダイグループ 106 の全ての側部が、残りのウェーハ組立体 200 から分離されるようになる点を理解されたい。更に、ダイグル

50

10 プ 1 0 6 を個別分離するための操作の順序は、記載された通りにする必要はない点を理解されたい。例えば、ダイシングソー 5 0 4 は、最初にカットパス 5 0 0 を生成し、次いで屈曲ギャップ 5 0 2 を生成することができる。代替として或いは付加的に、ダイシングソー 5 0 4 は、カットパス 5 0 0 の生成と屈曲ギャップ 5 0 2 の生成とを交互にすることができます。更に、ダイシングソー 5 0 4 は、所望の最終 z 1 又は z 2 高さに達する前に、順次的に深くなる z 軸高さで複数の切断を行うことができる。また、z 1 及び z 2 として本明細書で示されたダイシングソー 5 0 4 の相対的な z 軸位置は、チャック 5 0 6 の上部に対する寸法として定義される必要はない。代わりに、ダイシングソー 5 0 4 の z 軸位置は、図示の何れかの表面、或いはウェーハ組立体 2 0 0 及びチャック 5 0 6 から独立した絶対又は相対座標システムに対して定義することができる。また、ウェーハ組立体 2 0 0 が代替の作業表面に直接又はダイシングテープ及びダイシングテープフレームのような中間デバイスを介して固定される場合、ギャップ 5 0 2 及びカットパス 5 0 0 は、ダイシングソー 5 0 4 によって同様に形成することができる。

#### 【 0 0 2 9 】

個別分離に加え、ウェーハ組立体 2 0 0 又は個別分離したグループ 1 0 6 がチャック 5 0 6 又は代替の作業表面に固定されている場合に他の操作を行うことができる。例えば、ダイ 1 0 2 及びダイ 1 0 4 の一方又は両方は、裏面研削により、或いは、レーザアブレーション又はエッチングのような他の材料除去操作によってシニング加工することができる。通常、半導体ダイ 1 0 2 及び 1 0 4 の第 1 の表面 1 0 8 上の活性層は、1 0 ミクロン未満の深さがあり、これはダイの全体の厚みよりもかなり薄く、従って、半導体ダイ 1 0 2 及び 1 0 4 はこれらの全体の厚みを減少させるようシニング加工することができる。シニング加工は、個別分離の前、その間、或いはその後に行うことができる。

#### 【 0 0 3 0 】

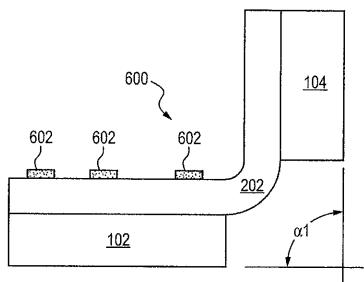

20 図 6 は、ダイグループ 1 0 6 から作成することができる可撓性集積回路パッケージ 6 0 0 の側面図である。IC パッケージ 6 0 0 は、例えば、X - Y 多軸センサデバイスとして機能するダイ 1 0 2 及び Z - 軸センサデバイスとして機能するダイ 1 0 4 を備え、この両方が可撓性膜 2 0 2 内部の相互接続部によって電気的に接続された 3 軸センサパッケージとすることができます。IC パッケージ 6 0 0 は、ダイ 1 0 4 が、ダイ 1 0 2 に対して或る角度 1 (好ましくは 90 度) であるようにダイグループ 1 0 6 をダイギャップ 5 0 2 で屈曲させることによって形成することができる。標準的な 3 軸センサパッケージでは、IC パッケージ 6 0 0 (又は下記の IC パッケージ 7 0 0 ) の全高は約 1.1 mm とすることができるが、他の IC パッケージでの寸法はかなり変わるべきである。

#### 【 0 0 3 1 】

30 IC パッケージ 6 0 0 は、他のデバイスに IC パッケージ 6 0 0 を電気的に接続する手段を含む。図 6 に示されるように、IC パッケージ 6 0 0 は、複数のワイヤボンディングパッド 6 0 2 を含むことができる。ワイヤボンディングパッド 6 0 2 は、他のデバイスへのワイヤ接続に対応するように分配することができる。ワイヤボンディングパッド 6 0 2 は、可撓性膜 2 0 2 内部の相互接続部によって、ダイ 1 0 2 及び 1 0 4 に電気的に接続することができる。この接続により、ダイ 1 0 2 及び 1 0 4 との間の信号の入出力及び / 又は電力供給及び接地が可能となる。図 6 のワイヤボンディングパッド 6 0 2 の位置及び個数は、単なる例証として提供されている。ワイヤボンディングパッド 6 0 2 の位置は、設計要件に応じて変わることができる。好ましくは、ワイヤボンディングパッド 6 0 2 は、図 6 に表されるように IC パッケージ 6 0 0 の片面に配置される。

#### 【 0 0 3 2 】

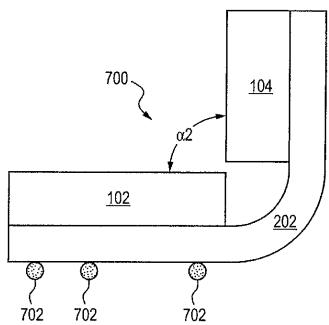

40 図 7 は、ダイグループ 1 0 6 から生成することができる、別の可撓性集積回路パッケージ 7 0 0 の側面図である。IC パッケージ 7 0 0 は、例えば、X - Y 多軸センサデバイスとして機能するダイ 1 0 2 及び Z - 軸センサデバイスとして機能するダイ 1 0 4 を備え、両方が可撓性膜 2 0 2 内の相互接続部によって電気的に接続された 3 軸センサパッケージとすることができます。IC パッケージ 7 0 0 は、ダイ 1 0 4 が、ダイ 1 0 2 に対して或る角度 1 (好ましくは 90 度) であるようにダイグループ 1 0 6 をダイギャップ 5 0 2 で

屈曲させることによって形成することができる。

【0033】

ICパッケージ700は、他のデバイスにICパッケージ700を電気的に接続する手段を含む。図7に示すように、ICパッケージ700は、フリップチップ構造で形成することができ、複数の半田ボール702又はICパッケージ700への電気的接続を確立する他の手段を含むことができる。例えば、半田ボール702は、代わりに半田バンプ、金バンプ、導電性接着剤バンプとすることができます。半田ボール702は、他のデバイスへのワイヤ接続に対応するように分配することができます。半田ボール702は、可撓性膜202内部の相互接続部によって、ダイ102及び104に電気的に接続することができる。この接続により、ダイ102及び104との間の信号の入出力及び/又は電力供給及び接地が可能となる。図7における半田ボール702の位置及び個数は、単に例証としてのみ提供される。半田ボール702の位置は、設計要件に応じて変わることができる。好ましくは、半田ボール702は、図7に表されるようにICパッケージ700の片面に配置される。

10

【0034】

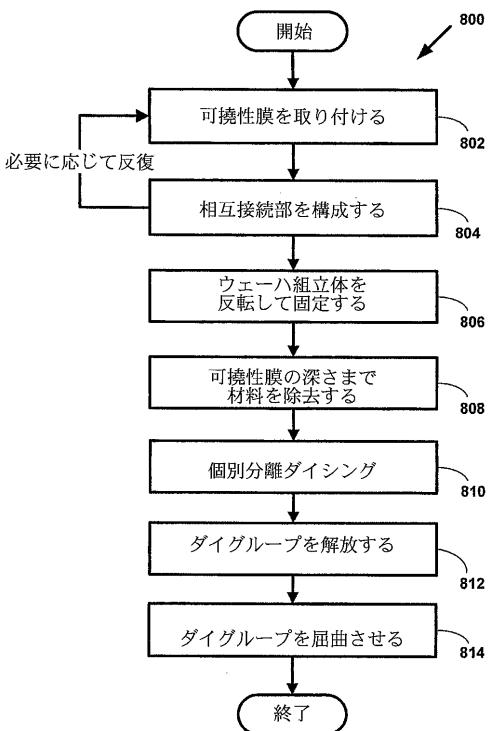

図8は、ICパッケージ600又は700のような可撓性集積回路パッケージを作成する好ましい方法800を表すフローチャートである。ブロック802で、可撓性膜202又は可撓性膜202の層306のような可撓性膜が、ウェーハ100のようなウェーハに取り付けられ、ウェーハ組立体200のようなウェーハ組立体を形成する。図2及び図3に関連して記載された方法を用いて、可撓性膜をウェーハに取り付けることができる。ブロック804で、電気的相互接続部が、例えば図3に関して前述されたように可撓性膜の上又は内部に構成される。可撓性膜の層を施工し、相互接続部を形成するステップは、必要に応じて反復して、適切な電気的相互接続部を生成することができる。

20

【0035】

ブロック806で、例えば図4、図4b、及び図5に関して論じたように、ウェーハ組立体が反転されて、ダイシングテープフレーム402及びダイシングテープ400と共にダイシングチャック506のような作業表面に固定することができる。ブロック808で、ダイ間のウェーハ材料を除去し、図5に関して示された屈曲ギャップ502のような屈曲ギャップを生成するようにすることができます。ブロック810で、個々のダイグループを互いに及び残りのウェーハ組立体に接続するウェーハ材料及び可撓性膜材料の実質的に全てを除去することによって、ダイグループ106のようなダイグループを個別分離することができる。ブロック812で、更なる処理を容易にするためにインジェクタ・ピンを用いて、個別分離されたダイグループをダイシングテープフレーム又は代替の作業表面から解放することができる。代替として、ダイグループ内の1つ又はそれ以上のダイを作業表面に固定されたままにしながら、各ダイグループ内の残りのダイを作業表面への固定取付から解放し、ダイグループの後の屈曲を容易にすることができます。ダイグループは、固定方法に対して適切な手段を用いて解放することができる。例えば、UV反応結合剤を用いて、ウェーハ組立体を作業表面に最初に固定する場合には、UV光を使用してダイ又はダイグループを解放することができます。ウェーハ組立体を作業表面に最初に固定するために、真空が使用される場合には、真空源の選択的除去を利用して、ダイ又はダイグループを解放することができる。他の可能性としては、熱反応性結合剤及び化学的応答性結合剤が挙げられる。

30

【0036】

ブロック814で、可撓性膜層は、例えば図6及び図7に関連して示されるような各ダイグループ内の個々のダイが互いに対し或る角度になるように屈曲することができる。屈曲は、垂直固定又はダイパッケージを屈曲させる現在公知の手段又は将来開発される何れかの手段を用いて行うことができる。

40

【0037】

例示された実施形態は単に実施例と理解すべきであり、本発明の範囲を限定するものと解釈すべきではない。請求項は、別途その旨指定されない限り、記載の順序又は要素に限

50

定されるものとして読み取るべきではない。従って、添付の請求項の範囲及び精神の範囲内にある全ての実施形態及びこれらの均等物は、本発明として特許請求される。

【符号の説明】

【0038】

- 100 半導体ウェーハ

- 102、104 半導体ダイ

- 106 ダイグループ

- 108 第1の側部

- 110 第2の側部

【図1a】

平面図

【図1b】

【図2a】

平面図

【図2b】

【図3】

### A-A矢視図

【 図 4 a 】

### 平面図 (反転後)

【図4b】

## B-B 矢視図

【図5】

### B-B 矢視図 (チヤツク付き)

【図 6】

【図 7】

【図 8】

---

フロントページの続き

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100147681

弁理士 夫馬 直樹

(72)発明者 デーヴィッド・アール・シェイド

アメリカ合衆国ウィスコンシン州 54701, オークレール, フェアファックス・ストリート 3

721

【外國語明細書】

2009170893000001.pdf