(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6368128号

(P6368128)

(45) 発行日 平成30年8月1日(2018.8.1)

(24) 登録日 平成30年7月13日(2018.7.13)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO4N 5/3745 (2011.01) | HO4N 5/3745   |

| HO4N 5/347 (2011.01)  | HO4N 5/347    |

| HO4N 5/378 (2011.01)  | HO4N 5/378    |

| HO4N 9/07 (2006.01)   | HO4N 9/07 A   |

| HO1L 27/146 (2006.01) | HO1L 27/146 A |

請求項の数 15 (全 22 頁)

(21) 出願番号 特願2014-81435 (P2014-81435)

(22) 出願日 平成26年4月10日 (2014.4.10)

(65) 公開番号 特開2015-204469 (P2015-204469A)

(43) 公開日 平成27年11月16日 (2015.11.16)

審査請求日 平成29年4月10日 (2017.4.10)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像素子及び撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素が2次元状に配列された画素部と、前記画素部の画素を行単位で選択し、該選択した行の画素から信号を出力させる走査手段とを有する撮像素子であって、前記画素は、それぞれ、

入射光量に応じた信号電荷を発生する光電変換手段と、電荷を保持する保持手段と、

前記画素が前記走査手段により選択された行に含まれる場合に、前記光電変換手段で発生した信号電荷を前記保持手段に転送する転送手段と、

前記保持手段に転送された信号電荷に応じた画素信号を出力する出力手段と、

前記走査手段により複数行ずつ選択し、該選択した行の画素から出力される画素信号を列毎に混合して読み出す混合読み出しモードにおいて得られる画素信号の出力レンジを、前記保持手段の容量に応じて補正する補正手段と、を有し、

前記混合読み出しモードにおいて前記選択される複数行の内、予め決められた行を除く画素の保持手段の容量が、前記予め決められた行の画素の保持手段の容量より大きいことを特徴とする撮像素子。

## 【請求項 2】

前記予め決められた行を除く行の画素の保持手段を、前記予め決められた行の画素の保持手段よりも大きい容量の保持手段で構成したことを特徴とする請求項1に記載の撮像素子。

**【請求項 3】**

前記各画素の保持手段は、複数の電荷保持部と、該複数の電荷保持部の間の接続、非接続を切り替える切替手段とを有し、

前記混合読み出しモードにおいて、前記予め決められた行を除く行の画素の前記複数の電荷保持部を前記切替手段により接続することにより、前記保持手段の容量を大きくすることを特徴とする請求項1に記載の撮像素子。

**【請求項 4】**

前記各画素は、更に、隣接する行の画素の保持手段との接続、非接続を切り替える切替手段を有し、

前記混合読み出しモードにおいて、前記切替手段により、前記予め決められた行を除く行の画素の前記保持手段を、前記選択した複数行に隣接する行の画素の保持手段と接続することにより、前記保持手段の容量を大きくすることを特徴とする請求項1に記載の撮像素子。10

**【請求項 5】**

前記切替手段により、隣接する列と異なる数の画素の保持手段に接続することを特徴とする請求項4に記載の撮像素子。

**【請求項 6】**

前記混合読み出しモードにおいて、予め決められた複数の列毎に、前記選択した行の画素から出力された信号を加算する加算手段を更に有し、

前記切替手段により、前記複数の列の内、予め決められた列に接続する保持手段の数よりも、前記予め決められた列を除く列に接続する保持手段の数を多くしたことを特徴とする請求項4に記載の撮像素子。20

**【請求項 7】**

前記予め決められた列は、前記複数の列の内、中央の列であることを特徴とする請求項6に記載の撮像素子。

**【請求項 8】**

前記予め決められた行は、前記選択した複数行の内、中央の行であることを特徴とする請求項1乃至7のいずれか1項に記載の撮像素子。

**【請求項 9】**

複数の画素が2次元状に配列された画素部と、前記画素部の画素を行単位で選択し、該選択した行の画素から信号を出力させる走査手段とを有する撮像素子であって、30

前記画素は、それぞれ、

入射光量に応じた信号電荷を発生する光電変換手段と、

電荷を保持する1つの容量からなる保持手段と、

前記画素が前記走査手段により選択された行に含まれる場合に、前記光電変換手段で発生した信号電荷を前記保持手段に転送する転送手段と、

前記保持手段に転送された信号電荷に応じた画素信号を出力する出力手段とを有し、

前記走査手段により複数行ずつ選択し、該選択した行の画素から出力される画素信号を列毎に混合して読み出す混合読み出しモードにおいて前記選択される複数行の内、予め決められた行を除く画素の電荷を転送する保持手段の容量が、前記予め決められた行の画素の電荷を転送する保持手段の容量より大きいことを特徴とする撮像素子。40

**【請求項 10】**

前記走査手段は、更に、1行ずつ画素を選択して、行毎に画素の信号を出力させる順次読み出しモードによる駆動を行い、該順次読み出しモードと前記混合読み出しモードのいずれかに切り替えて、前記画素部を駆動することを特徴とする請求項1乃至9のいずれか1項に記載の撮像素子。

**【請求項 11】**

前記混合読み出しモードにおいて得られる画素信号の出力レンジを、前記保持手段の容量に応じて補正する補正手段を更に有することを特徴とする請求項9に記載の撮像素子。

**【請求項 12】**

前記画素部にベイヤー配列のカラーフィルタが配され、

前記混合読み出しモードにおいて、前記走査手段は、同色のカラーフィルタが配された

画素の行を選択することを特徴とする請求項1乃至1\_1のいずれか1項に記載の撮像素子

。

**【請求項13】**

前記混合読み出しモードにおいて、前記保持手段の容量が、前記カラーフィルタの色ご

とに異なることを特徴とする請求項1\_2に記載の撮像素子。

**【請求項14】**

請求項1乃至1\_3のいずれか1項に記載の撮像素子と、

前記撮像素子から出力された画素信号を処理する処理手段と

を有することを特徴とする撮像装置。

10

**【請求項15】**

複数の画素が2次元状に配列された画素部と、前記画素部の画素を行単位で選択し、

該選択した行の画素から信号を出力させる走査手段とを有する撮像素子であって、

前記画素は、それぞれ、

入射光量に応じた信号電荷を発生する光電変換手段と、

電荷を保持する保持手段と、

前記画素が前記走査手段により選択された行に含まれる場合に、前記光電変換手段で

発生した信号電荷を前記保持手段に転送する転送手段と、

前記保持手段に転送された信号電荷に応じた画素信号を出力する出力手段と、を有し

20

前記走査手段により複数行ずつ選択し、該選択した行の画素から出力される画素信号を

列毎に混合して読み出す混合読み出しモードにおいて前記選択される複数行の内、予め決

められた行を除く画素の保持手段の容量が、前記予め決められた行の画素の保持手段の容

量より大きいことを特徴とする撮像素子と、

前記混合読み出しモードにおいて得られる画素信号の出力レンジを、前記保持手段の容

量に応じて補正する処理を含む、前記撮像素子から出力された画素信号を処理する処理手

段と、

を有することを特徴とする撮像装置。

**【発明の詳細な説明】**

30

**【技術分野】**

**【0001】**

本発明は、撮像素子及び該撮像素子を用いた撮像装置に関するものである。

**【背景技術】**

**【0002】**

近年のデジタルカメラのC M O S撮像素子は高画素化が進む一方で、例えば1920x1080

画素の画像を30fpsまたは60fpsで出力するFull HD動画のように、高画素の画像を高フレ

ームレートで出力する撮影のニーズも高まっている。

**【0003】**

このようなニーズに対し、高画素のC M O S撮像素子を用いて高フレームレート撮影を

達成させるための低画素化手法として、間引き処理が知られている。間引き処理では、特

定の周期で画素から信号を読み出さないように駆動制御することで低画素化し、データレ

ートを下げることで高フレームレート化を実現している。この処理では特定の周期で画素

から信号を読み出さないので、撮像される画像の特徴として、被写体のエッジ検出に有利

である反面、折り返しノイズの一種であるモアレが目立ちやすい。

40

**【0004】**

そこで、モアレを低減する手法として、間引き処理では読み出されない画素の信号を、

隣接する画素の信号と混合し、低画素化して出力する手法がいくつか提案されている。特

許文献1に開示されている画素混合処理は、行選択回路によって複数行を同時に選択し、

選択された複数行の信号を同時に出力することで複数行の画素信号の混合処理を行ってい

50

る。上記手法では複数画素の混合出力を得ることで、モアレを低減し、またランダムノイズを収束させる効果もある。以上の効果から、一般的には単純な間引き処理より、CMOS撮像素子内で画素信号を混合し、低画素化を行う画素混合処理のほうが画質の点で優れている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010-259027号公報

【発明の概要】

【発明が解決しようとする課題】

10

【0006】

しかし、画素混合処理では、被写体のエッジがぼやけてしまい、解像感の低い画像となってしまう。

【0007】

本発明は上記問題点を鑑みてなされたものであり、撮像素子から低画素化して画像を読み出す場合に、モアレを低減しつつ、解像感の高い画質の画像を得ることを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、複数の画素が2次元状に配列された画素部と、前記画素部の画素を行単位で選択し、該選択した行の画素から信号を出力させる走査手段とを有する撮像素子であって、本発明の前記画素は、それぞれ、入射光量に応じた信号電荷を発生する光電変換手段と、電荷を保持する保持手段と、前記画素が前記走査手段により選択された行に含まれる場合に、前記光電変換手段で発生した信号電荷を前記保持手段に転送する転送手段と、前記保持手段に転送された信号電荷に応じた画素信号を出力する出力手段と、前記走査手段により複数行ずつ選択し、該選択した行の画素から出力される画素信号を列毎に混合して読み出す混合読み出しモードにおいて得られる画素信号の出力レンジを、前記保持手段の容量に応じて補正する補正手段と、を有し、前記混合読み出しモードにおいて前記選択される複数行の内、予め決められた行を除く画素の保持手段の容量が、前記予め決められた行の画素の保持手段の容量より大きいことを特徴とする。

20

【発明の効果】

30

【0009】

本発明によれば、撮像素子から低画素化して画像を読み出す場合に、モアレを低減しつつ、解像感の高い画質の画像を得ることができる。

【図面の簡単な説明】

【0010】

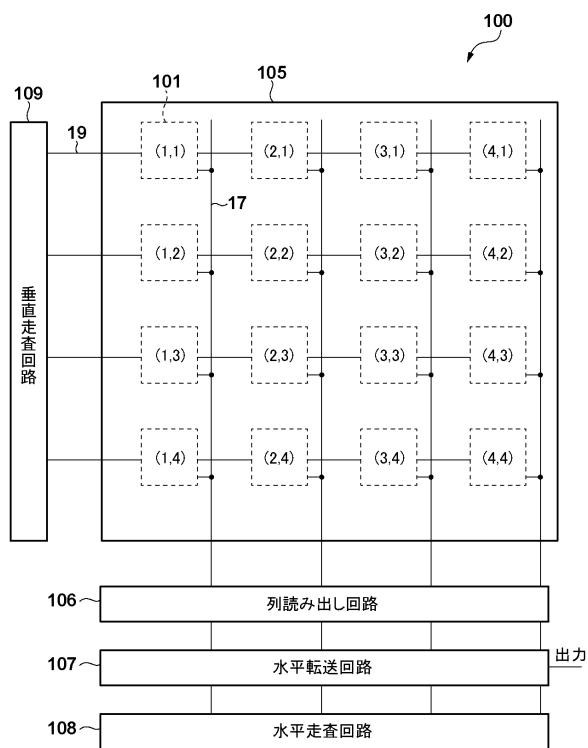

【図1】本発明の第1の実施形態における撮像素子の構成を示す図。

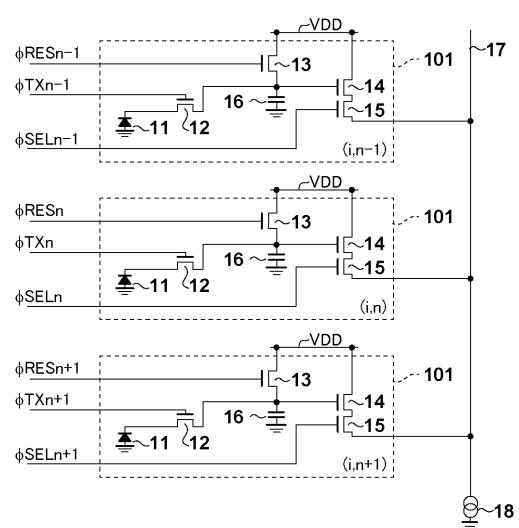

【図2】第1の実施形態における画素の回路構成を示す図。

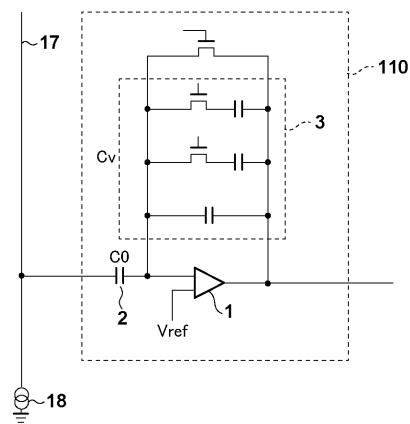

【図3】第1の実施形態における補正回路の回路構成を示す図。

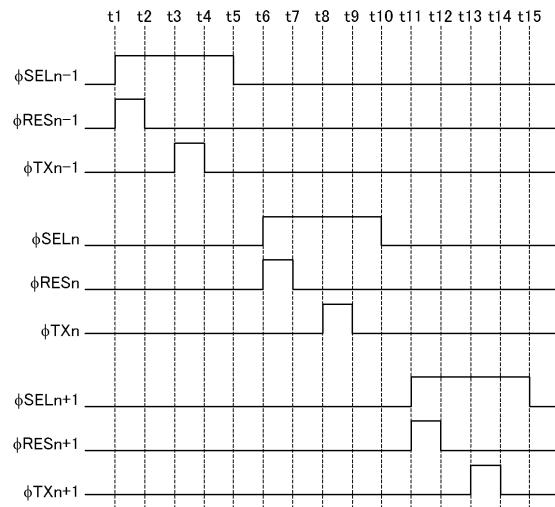

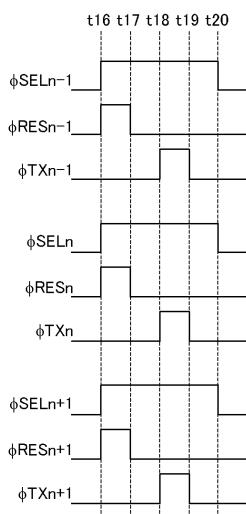

【図4】第1の実施形態における通常読み出しモード時の駆動を示すタイミングチャート。

。

40

【図5】第1の実施形態における加算読み出しモード時の駆動を示すタイミングチャート。

。

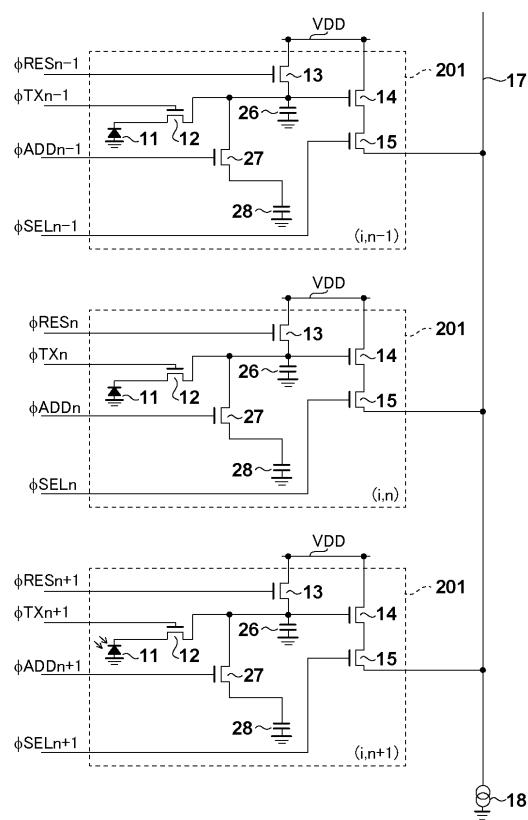

【図6】第2の実施形態における画素の回路構成を示す図。

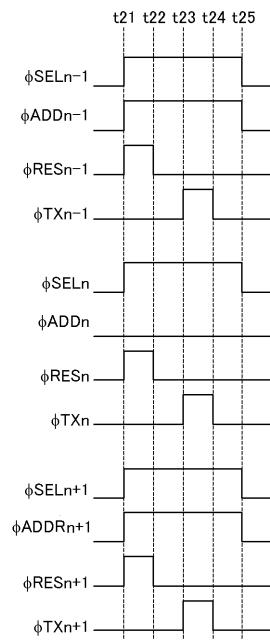

【図7】第2の実施形態における加算読み出しモード時の駆動を示すタイミングチャート。

。

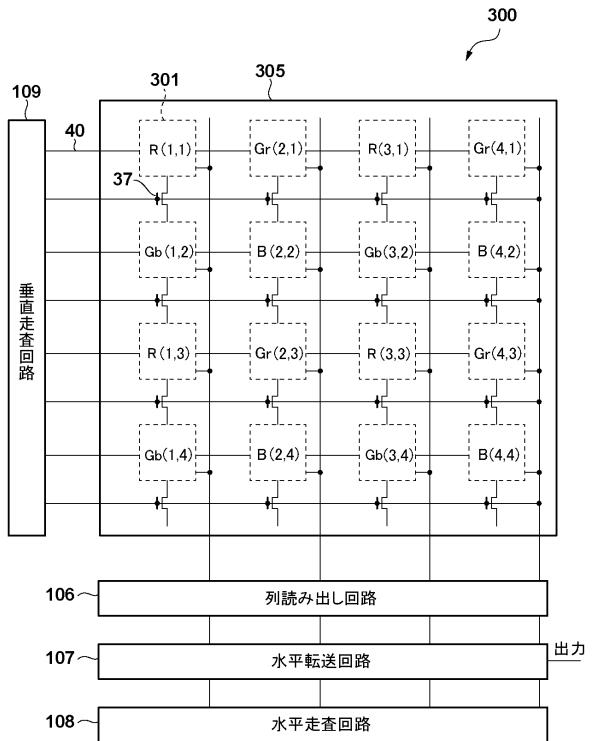

【図8】第3の実施形態における撮像素子の構成を示す図。

【図9】第3の実施形態における画素の回路構成を示す図。

【図10】第3の実施形態における加算読み出しモード時の駆動を示すタイミングチャート。

。

【図11】第4の実施形態における画素の回路構成を示す図。

50

【図12】第4の実施形態における加算読み出しモード時の駆動を示すタイミングチャート。

【図13】第5の実施形態における加算読み出しモード時の駆動を説明するための図。

【図14】第6の実施形態における撮像装置の概略構成図。

【発明を実施するための形態】

【0011】

以下、添付図面を参照して本発明を実施するための最良の形態を詳細に説明する。

【0012】

<第1の実施形態>

以下、本発明の第1の実施形態について、図1から図5を参照しながら説明する。図1は、第1の実施形態における撮像素子100の概略構成を示す図であり、CMOSイメージセンサを用いている。撮像素子100は、画素部105と、画素回路の列毎に設けられた複数の列回路からなる列読み出し回路106と、水平転送回路107と、水平走査回路108と、垂直走査回路109を有している。10

【0013】

画素部105は、2次元状に配列された複数の画素101を有する。図1では説明のために $4 \times 4$ の画素101(*i*, *j*) (*i* = 1 ~ 4, *j* = 1 ~ 4)を示しているが、実際にはより多数の画素から構成されている。画素101は、行毎に共通の駆動制御線19を通して駆動され、リセット信号と撮像信号を列毎に設けられた垂直出力線17に出力する。20

【0014】

垂直走査回路109は、駆動制御線19を通して画素101を駆動し、行単位でリセット信号と撮像信号の読み出しを制御する。列読み出し回路106は、垂直出力線17に出力されたリセット信号と撮像信号の差分から列毎に光電変換信号を抽出し、水平転送回路107に出力する。水平転送回路107は、水平走査回路108によって駆動され、列読み出し回路106から出力された1行分の光電変換信号を順次出力する。20

【0015】

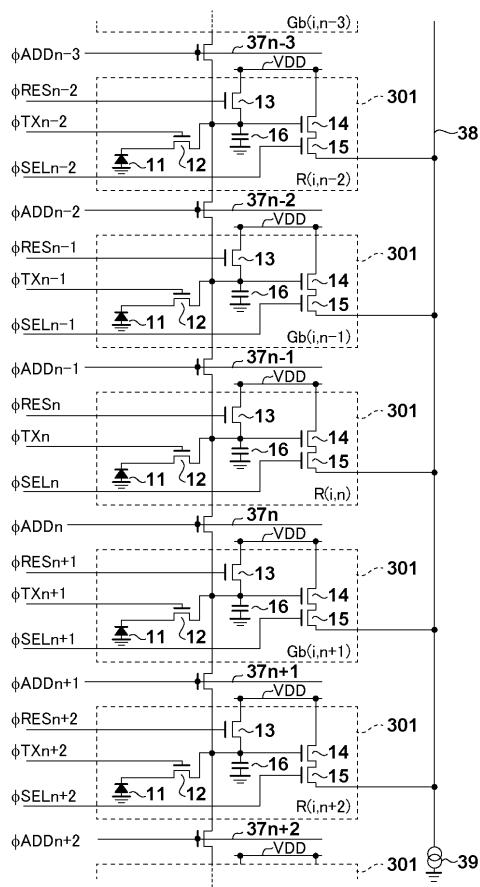

次に、画素101の詳細な構成について図2を用いて説明する。図2は、第1の実施形態における画素101の回路構成を示している。各画素101は、フォトダイオード(PD)11、転送スイッチ12、リセットスイッチ13、ソースフォロワアンプ(SF)14、行選択スイッチ15、フローティングディフェュージョン部(FD)16(保持手段)を有している。30

【0016】

PD11は、光電変換により入射光量に応じた電荷を発生させ、蓄積する。PD11に蓄積された電荷は、転送スイッチ12によってFD16への転送が行われる。リセットスイッチ13は、PD11及びFD16に蓄積されている不要電荷のリセットを制御する。

【0017】

FD16に蓄積された信号電荷は、その容量値に応じて電圧変換され、SF14のゲートに信号電圧として入力される。行選択スイッチ15は、SF14の出力の垂直出力線17への接続を制御する。行選択スイッチ15で選択された行のSF14は、列読み出し回路106が有する負荷定電流源18によって垂直出力線17を介して駆動され、ゲートに入力された信号電圧に応じた信号を出力する。40

【0018】

転送スイッチ12に対して信号TX、リセットスイッチ13に対して信号RES、行選択スイッチ15に対して信号SELを垂直走査回路109から供給することで、画素101の駆動が行われる。なお、以下の説明において、「n行目の」信号または構成を特定して説明する場合には、信号または構成を示す参照番号の後ろに添字nを付して説明する。例えば、「n行目の信号TX」は、添字nを付して「信号TXn」と記載する。同様に、「n-1行目」には添字n-1、「n+1行目」には添字n+1を付して記載する。

【0019】

50

20

30

40

50

本第1の実施形態では、1行ずつ画素信号を出力させる通常読み出しモードと、複数行の画素101から同時に信号を出力させる加算読み出しモードを有する。そして、選択されたモードに応じて、垂直走査回路109は画素部105に対して、行選択スイッチ15のON/OFF制御を行う。

#### 【0020】

具体的には、通常読み出しモードを行う場合、垂直走査回路109が信号SELを出力する画素行の行選択スイッチ15のみをONする。例えばn行目の画素101(i, n)の信号出力を行う場合は、SELnを「H」とし、行選択スイッチ15をONする。

#### 【0021】

一方で、加算読み出しモード(混合読み出しモード)では、画素出力混合を行う複数行分の画素101の行選択スイッチ15を同時にONする。例えばn-1行、n行、n+1行目の3画素の混合出力を得たい場合、SELn-1、SELn、SELn+1を同時に「H」にし、行選択スイッチ15n-1、15n、15n+1をONする。これにより、垂直出力線17には3つのSF14n-1、14n、14n+1が同時に接続され、画素出力混合が行われる。この時、得られる画像の解像感を高めるために、出力信号の混合を行う画素の、中心画素の信号の重み付けを行う。例えば垂直方向に3つの画素101(i, n-1)、101(i, n)、101(i, n+1)の混合出力信号を得る際に、中心画素101(i, n)の信号の重み付けを行う場合は、次のように構成する。即ち、FD16n-1、16n、16n+1の容量値Cn-1、Cn、Cn+1の比率を2:1:2とする。このような容量値となるようにFD16を構成すると、FD16n-1、16n、16n+1の電荷電圧変換率は1:2:1となる。

#### 【0022】

このように、加算読み出しモード(混合読み出しモード)において、垂直方向に3つの画素101ずつ出力信号を混合して読み出す場合に、上下の行の画素101(i, n-1)、101(i, n+1)のFD16の容量値を中央の行の画素101(i, n)よりも大きくしておく。これにより、読み出す3行のうち、中央の行の画素の信号に重み付けした低画素化手法が可能となる。なお、このように3行ずつ読み出す場合、 $n = 3 \times k + 2$ (k=0, 1, 2, ...)となる。

#### 【0023】

ところで、画素101(i, n-1)、101(i, n)、101(i, n+1)の電荷電圧変換率が1:2:1の場合、信号の出力レンジも1:2:1となる。よって通常読み出しモード時の上下の行の画素101(i, n-1)、101(i, n+1)の出力レンジは、中央の行の画素101(i, n)の出力レンジに対して1/2となる。また、加算読み出しモード時の出力レンジは、通常読み出しモード時の中央の画素101(i, n)の出力レンジに対して2/3となる。

#### 【0024】

そこで、第1の実施形態では、列読み出し回路106の列毎に、出力レンジを揃える補正回路110を設ける。図3は、列読み出し回路106に設けられた補正回路110の構成を示す図である。補正回路110は、列アンプ1と、クランプ容量2と、可変容量3を有している。列アンプ1には、クランプ容量2と、可変容量3が図3に示されるように接続され、垂直出力線17に出力された信号にゲインをかけて出力する。クランプ容量2と可変容量3は、この2つの容量の比率で列アンプ1の増幅率を決定することが可能である。例えば、クランプ容量2の容量値をC0、可変容量3の容量値をCvとすると、1.5倍のゲインをかけたい場合はCv=2/3×C0とする。

#### 【0025】

なお、列読み出し回路106に設けられた補正回路110により出力レンジの補正を行う代わりに、撮像素子100の出力後段の、例えば画像処理部(不図示)などに補正手段を設けて行うことも可能である。従って、他の出力レンジ補正手段を利用する場合には、補正回路110は無くてもよい。

#### 【0026】

10

20

30

40

50

次に、図4と図5を参照して、図2に示す回路構成を有する画素101の、第1の実施形態における通常読み出しモード時の駆動と加算読み出しモード時の駆動について説明する。

#### 【0027】

図4は、通常読み出しモード時の駆動を示すタイミングチャートであり、 $n - 1$ 行目から $n + 1$ 行目までの画素信号を1行ずつ順次読み出す駆動を行う。まず、時刻 $t_1$ から $t_5$ の期間において、信号SEL $n - 1$ が「H」とされることで、行選択スイッチ15 $n - 1$ がONする。この期間では、 $n - 1$ 行目の画素信号が outputされる。

#### 【0028】

また、時刻 $t_1$ から $t_2$ の期間では、信号RES $n - 1$ が「H」とされ、リセットスイッチ13 $n - 1$ がONし、FD16 $n - 1$ にリセット電圧が与えられる。時刻 $t_2$ から $t_3$ の期間では、FD16 $n - 1$ のリセット電圧がSF14 $n - 1$ 、垂直出力線17を通して補正回路110に出力される。時刻 $t_3$ から $t_4$ の期間では、信号TX $n - 1$ が「H」とされ、転送スイッチ12 $n - 1$ がONし、被写体像の撮影によってPD11 $n - 1$ に蓄積された信号電荷が、FD16 $n - 1$ に転送される。時刻 $t_4$ から $t_5$ の期間では、転送後のFD16 $n - 1$ の信号電圧がSF14 $n - 1$ 、垂直出力線17を通して補正回路110に出力される。なお、 $n - 1$ 行目の信号出力、すなわち画素101 $n - 1$ の信号出力では、補正回路110でかけるゲインは2倍なので、 $Cv = 1 / 2 \times C_0$ に設定する。

#### 【0029】

これらの駆動によって1行分の画素101( $i, n - 1$ )から信号出力が行われる。同様にして、時刻 $t_6$ から $t_{10}$ において $n$ 行目の信号出力、時刻 $t_{11}$ から $t_{15}$ において $n + 1$ 行目の信号出力が行われる。 $n$ 行目の信号出力、すなわち画素101( $i, n$ )の信号出力では、かけるゲインは1倍なので、 $Cv = C_0$ に設定する。また、 $n + 1$ 行目の信号出力、すなわち画素101( $i, n + 1$ )の信号出力では、かけるゲインは2倍なので、 $Cv = 1 / 2 \times C_0$ に設定する。

#### 【0030】

次に、加算読み出しモードの駆動について説明する。図5は、加算読み出しモード時の駆動を示すタイミングチャートである。まず、時刻 $t_{16}$ から $t_{20}$ の期間において、信号SEL $n - 1$ 、SEL $n$ 、SEL $n + 1$ が「H」とされることで、各行選択スイッチ15 $n - 1$ 、15 $n$ 、15 $n + 1$ がONする。この期間では、 $n - 1$ 行、 $n$ 行、 $n + 1$ 行目の垂直方向3画素の信号の混合出力が行われる。ただし、画素部105がベイヤー配列のカラーフィルタを持つ場合は、1行おきに配列された同色のカラーフィルタを持つ画素101の出力信号混合を行う。

#### 【0031】

時刻 $t_{16}$ から $t_{17}$ の期間では、信号RES $n - 1$ 、RES $n$ 、RES $n + 1$ が「H」とされ、各リセットスイッチ13 $n - 1$ 、13 $n$ 、13 $n + 1$ がONし、FD16 $n - 1$ 、16 $n$ 、16 $n + 1$ にリセット電圧が与えられる。時刻 $t_{17}$ から $t_{18}$ の期間では、FD16 $n - 1$ 、16 $n$ 、16 $n + 1$ のリセット電圧が各SF14 $n - 1$ 、14 $n$ 、14 $n + 1$ を通して垂直出力線17で混合され、補正回路110に出力される。

#### 【0032】

時刻 $t_{18}$ から $t_{19}$ の期間では、信号TX $n - 1$ 、TX $n$ 、TX $n + 1$ が「H」とされ、各転送スイッチ12 $n - 1$ 、12 $n$ 、12 $n + 1$ がONする。これにより、被写体像の撮影によってPD11 $n - 1$ 、11 $n$ 、11 $n + 1$ に蓄積された信号電荷が、各FD16 $n - 1$ 、16 $n$ 、16 $n + 1$ に転送される。この期間では、FD16 $n - 1$ 、16 $n$ 、16 $n + 1$ に信号電荷が転送されるので、画素101毎のFD容量C $n - 1$ 、C $n$ 、C $n + 1$ に依存した電圧変動が各FD16 $n - 1$ 、16 $n$ 、16 $n + 1$ で発生する。時刻 $t_{19}$ から $t_{20}$ の期間では、転送後のFD16 $n - 1$ 、16 $n$ 、16 $n + 1$ の信号電圧が各SF14 $n - 1$ 、14 $n$ 、14 $n + 1$ を通して垂直出力線17で平均化され、補正回路110に出力される。なお、画素101( $i, n - 1$ )、101( $i, n$ )、101( $i, n + 1$ )の混合出力では、補正回路110でかけるゲインは1.5倍なので、 $Cv$

10

20

30

40

50

= 2 / 3 \* C 0 に設定する。

#### 【0033】

これらの駆動によって 3 行分の画素 101 の出力信号混合が行われる。同様にして、図には示していないが、n + 2 ~ n + 4 行目、n + 5 ~ n + 7 行目といったように、3 行ずつの出力信号混合が順次行われる。

#### 【0034】

以上のように、3 つの SF14n - 1、14n、14n + 1 の同時接続による出力信号の混合は、ゲートに入力される電圧の値を平均化することになる。従って、FD16n - 1 及び 16n + 1 の容量をあらかじめ FD16n より大きく設定しておくことで、中心画素の出力を重み付けした混合が可能である。

10

#### 【0035】

なお、上記では、垂直方向 3 つの画素の出力信号混合について示したが、例えば 4 画素の出力信号混合で、1 : 3 : 3 : 1 に重み付けした混合出力信号を得たい場合は、FD 容量値の比を 3 : 1 : 1 : 3 に設定すればよい。また、5 画素の出力信号混合で、1 : 4 : 6 : 4 : 1 に重み付けした混合出力信号を得たい場合は、FD 容量値の比を 12 : 3 : 2 : 3 : 1 に設定すればよい。

#### 【0036】

上記の重み付けの比率はガウシアンフィルターの例であるが、これらの比率は、得たい画質、すなわち解像感、モアレの程度に応じて決定されるのが好適である。また、例えば 3 画素の出力信号混合時に重み付けの重心を端側にずらしたい場合は、FD 容量の容量比を 1 : 2 : 2 のように設定してもよい。

20

#### 【0037】

上記の通り第 1 の実施形態によれば、混合読み出しを行う際に、出力信号を混合する画素の中央にある画素の FD 容量に対して端側に位置する画素の FD 容量を大きく設定することで、中央にある画素からの信号に重みを付けた混合出力信号を得ることができる。これにより、モアレを低減しつつ解像感の高い画像を得ることが期待できる。

#### 【0038】

##### <第 2 の実施形態>

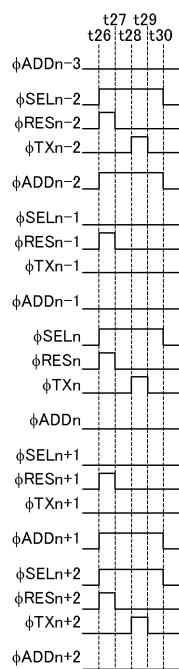

次に、本発明の第 2 の実施形態について、図 6 から図 8 を参照しながら説明する。第 2 の実施形態では、通常読み出しモードと加算読み出しモードで FD 容量を切り替える画素回路構成をとっている。なお、撮像素子 100 の構成は第 1 の実施形態で図 1 を参照して説明したものと同様であるので、詳細な説明を省略する。

30

#### 【0039】

図 6 は、第 2 の実施形態における画素 201 の回路構成を示している。第 1 の実施形態における画素 101 の回路構成との違いは、図 2 の FD16 に相当する FD26 の容量を同一とし、更に追加容量 28 を設け、容量切替スイッチ 27 により FD26 と追加容量 28（複数の電荷保持部）の接続 / 非接続を切り替える点である。その他の構成は、図 2 に示すものと同様であるため、同じ参考番号を付して説明を省略する。なお、以下の説明において、「n 行目の」信号または構成を特定して説明する場合には、信号または構成を示す参考番号の後ろに添字 n を付して説明する。例えば、「n 行目の信号 TX」は、添字 n を付して「信号 TXn」と記載する。同様に、「n - 1 行目」には添字 n - 1、「n + 1 行目」には添字 n + 1 を付して記載する。

40

#### 【0040】

通常読み出しモードでは、FD26 のみを使用することで通常読み出しモードの画素 201 每の電荷電圧変換率を揃えている。よって、第 2 の実施形態の通常読み出しモードでは補正回路 110 を用いた画素毎の出力レンジの補正を行わない。

#### 【0041】

一方、加算読み出しモード時には、画素 201 每に FD 容量を異ならせる手法として、第 2 の実施形態の画素 201 (i, n - 1)、201 (i, n)、201 (i, n + 1) は、上述したように、容量を増加させるための追加容量 28 と容量切替スイッチ 27 を有

50

している。容量切替スイッチ27は、垂直走査回路109からの駆動信号ADDによって駆動され、加算読み出しモード時に容量を増加させたい画素201のFD26と追加容量28を接続する。なお、加算読み出しモード時に用いる補正回路110は、第1の実施形態で図3を参照して説明した構成と同様のため、説明を省略する。

#### 【0042】

次に、加算読み出しモードの駆動について説明する。ここでは、3行分の画素201( $i, n-1$ )、 $201(i, n)$ 、 $201(i, n+1)$ の出力信号の混合を行う例について説明する。なお、通常読み出しモードではADDを使用せず、第1の実施形態の図4に示す駆動と同様であるため説明を省略する。

#### 【0043】

図7は、第2の実施形態における加算読み出しモード時の駆動を示すタイミングチャートである。まず、時刻t21からt25の期間において、信号SELn-1、SELn、SELn+1を「H」とすることで、各行の選択スイッチ15n-1、15n、15n+1がONする。この期間では、n-1行目、n行目、n+1行目の3画素の信号の混合が行われる。ただし、画素部105がベイヤー配列のカラーフィルタを持つ場合は、1行おきに配列された同色のカラーフィルタを持つ画素101の出力信号を混合する。

#### 【0044】

このとき、信号ADDn-1、ADDn+1を「H」とし、3行の中央であるn行目の画素201nのFD容量に対して、n-1行目及びn+1行目のFD容量を増加させる。ここでFD26の容量をCd、追加容量28の容量をCeとおくと、n行目のFD容量はCd、一方、n-1行目及びn+1行目のFD容量はCd+Ceとなる。これにより、中央の行の画素201の信号に重み付けされた混合出力が可能となる。

#### 【0045】

時刻t21からt22の期間では、信号RESn-1、RESn、RESn+1が「H」とされ、各リセットスイッチ13n-1、13n、13n+1がONし、対応するFD26n-1、26n、26n+1にリセット電圧が与えられる。また信号ADDが「H」となっているn-1行目とn+1行目では、追加容量28n-1、28n+1も同時にリセットされる。

#### 【0046】

時刻t22からt23の期間では、各FD26n-1、26n、26n+1のリセット電圧が各SF14n-1、14n、14n+1を通して垂直出力線17で平均化され、補正回路110に出力される。

#### 【0047】

時刻t23からt24の期間では、信号TXn-1、TXn、TXn+1が「H」とされ、各転送スイッチ12n-1、12n、12n+1がONする。これにより、被写体像の撮影によってPD11n-1、11n、11n+1に蓄積された信号電荷が各FD26n-1、26n、26n+1に転送される。この時、n-1行、n+1行目ではFD26n-1、26n+1と同時に追加容量28n-1、28n+1に対しても蓄積される。

#### 【0048】

ここで、PD11n-1、11n、11n+1の信号電荷をQa、Qb、Qcとするところ、各SF14n-1、14n、14n+1のゲートに入力される信号電圧は、それぞれQa/(Cd+Ce)、Qb/Cd、Qc/(Cd+Ce)となる。

#### 【0049】

時刻t24からt25の期間では、上記信号電圧が垂直出力線17で平均化され、補正回路110に出力される。通常読み出しモード時のFD容量Cdの出力レンジに揃えたい場合は、かけるゲインは $3 \times Cd \times (Cd + Ce) / (3 \times Cd + Ce)$ 倍なので、 $Cv = (3 \times Cd + Ce) / \{3 \times Cd \times (Cd + Ce)\} \times Co$ に設定する。

#### 【0050】

これらの駆動によって3行分の画素201の出力信号の混合が行われる。同様にして、

10

20

30

40

50

図には示していないが、 $n + 2 \sim n + 4$  行目、 $n + 5 \sim n + 7$  行目といったように、3 行ずつの出力信号の混合が順次行われる。

#### 【0051】

第2の実施形態では、画素に FD 容量を切り替える手段を設けることで、通常読み出しモードでは画素毎の電荷電圧変換率を揃え、加算読み出しモードでは容量値を画素毎に変えることによる重み付け混合出力を達成している。そのため、第1の実施形態で行っていた、通常読み出しモードでの列読み出し回路 106 または撮像素子 100 の出力後での出力レンジの補正是不要となる。

#### 【0052】

なお、FD 容量を拡大させる手法として、転送スイッチ 12 が ON した際の寄生容量を利用することも可能である。すなわち、加算読み出しモード時に、混合出力を行う期間  $t_{24} \sim t_{25}$  に信号  $TX_{n-1}$ 、 $TX_{n+1}$  を「H」とし、転送スイッチ 12  $n-1$ 、 $12n+1$  を ON させておく。これにより、画素  $\underline{201}(i, n-1)$ 、 $201(i, n+1)$  の FD 容量を拡大させる。この間、信号  $TX_n$  は「L」にし、転送スイッチ 12  $n$  は OFF にする。

#### 【0053】

上記の通り第2の実施形態によれば、容量を増加させるための追加容量 28 と容量切替スイッチ 27 を画素 201 に設ける構成とし、通常読み出しモード時には画素毎に容量値の等しい FD 26 を利用する。これにより、通常読み出しモード時の画素毎の出力レンジを揃えることが可能となった。さらに、追加容量 28 の容量の接続を画素毎に設定することで、重み付け比率を変更することができる。

#### 【0054】

##### <変形例>

上述した加算読み出しモード時の駆動例では  $n$  行目の追加容量  $28n$  を使用しなかったが、重み付けの比率を変更するのに利用してもよい。例えば追加容量  $28n-1$ 、 $28n$ 、 $28n+1$  の容量をそれぞれ  $2 \times Cd$ 、 $Cd$ 、 $2 \times Cd$  となるよう画素毎に設定しておく。そして、解像感の高い画像を得たい場合は、 $n$  行目の追加容量  $28n$  を使用せず、図 7 に示す駆動を行う。この時、 $n$  行目の FD 容量は  $Cd$ 、 $n-1$  行目、 $n+1$  行目の FD 容量は  $3 \times Cd$  となり、重み付け比率  $1 : 3 : 1$  が得られる。この場合、補正回路 110 でかけるゲインは  $1.8$  倍となる。

#### 【0055】

一方、モアレの低減を優先したい場合には、加算読み出しモード時に信号 ADDn も「H」とする。この時、 $n$  行目の FD 容量は  $2 \times Cd$ 、 $n-1$  行目、 $n+1$  行目の FD 容量は  $3 \times Cd$  となり、重み付け比率  $2 : 3 : 2$  が得られる。ここで、補正回路 110 でかけるゲインは  $1.8 / 7$  倍となる。

#### 【0056】

このように、 $n$  行目の追加容量  $28n$  の容量を  $n-1$  行、 $n+1$  行目の追加容量  $28n-1$ 、 $28n+1$  の容量より小さく設定しておくことで、重み付けの比率を変更することが可能となる。

#### 【0057】

##### <第3の実施形態>

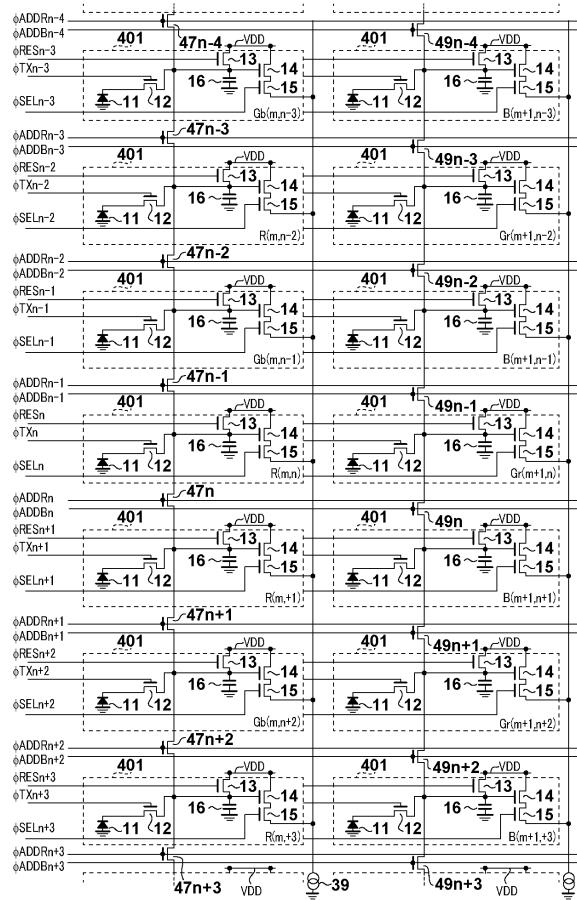

次に、本発明の第3の実施形態について、図 8 から図 10 を参照しながら説明する。図 8 は、第3の実施形態における撮像素子 300 の概略構成を示す図であり、ここでは、CMOS イメージセンサを用いている。第3の実施形態では、より単純な画素の回路構成で FD 容量を切り替える手法として、隣接する画素同士を容量切替スイッチ 37 でつなぐ構成としている。また、第3の実施形態では、図 8 に示すように、画素部 305 にベイヤー配列のカラーフィルタが設けられているものとする。

#### 【0058】

図 9 は、第3の実施形態における画素 301 の回路構成を示している。なお、第1の実施形態で図 2 を参照して説明した構成と同様の構成には、同じ参照番号を付して説明を省

10

20

30

40

50

略する。以下の説明において、「 $n$  行目の」信号または構成を特定して説明する場合には、信号または構成を示す参照番号の後ろに添字 $n$ を付して説明する。例えば、「 $n$  行目の信号 TX」は、添字 $n$ を付して「信号 TX $n$ 」と記載する。同様に、「 $n - 1$  行目」には添字 $n - 1$ 、「 $n + 1$  行目」には添字 $n + 1$ を付して記載する。

#### 【0059】

第3の実施形態における画素301の回路構成の大きな特徴は、上下に隣接する画素301のFD同士を接続するように容量切替スイッチ37が設けられていることである。すなわち、 $n$ 行目の画素301( $i, n$ )に着目すると、FD16nには、2つの容量切替スイッチ37 $n - 1$ 、37 $n$ が接続されている。なお、画素301( $i, n$ )はRのカラーフィルタをもつ画素とする。

10

#### 【0060】

画素301 $n$ は、容量切替スイッチ37 $n - 1$ を通して隣接画素のFD16 $n - 1$ 、また、容量切替スイッチ37 $n$ を通して隣接画素のFD16 $n + 1$ を追加容量として利用可能である。ただし、ベイヤー配列のカラーフィルタを有する場合、加算画素群は最も近い同色同士となる。よって、第3の実施形態において、 $n$ 行目の画素301( $i, n$ )を中心とした3画素で出力信号の混合を行う場合、Rのカラーフィルタを持つ画素301( $i, n - 2$ )、301( $i, n + 2$ )が混合画素となる。なお、列読み出し回路106の補正回路110は第1の実施形態で図3を参照して説明した構成と同様のため、説明を省略する。

#### 【0061】

図10は、第3の実施形態における加算読み出しモード時の駆動を示すタイミングチャートである。まず時刻 $t_{26}$ から $t_{30}$ の期間において、信号SEL $n - 2$ 、SEL $n$ 、SEL $n + 2$ を「H」とすることで、各行の選択スイッチ15 $n - 2$ 、15 $n$ 、15 $n + 2$ がONする。この期間では、 $n - 2$ 行目、 $n$ 行目、 $n + 2$ 行目の3画素の信号の混合出力が行われる。また、信号ADD $n - 2$ 、ADD $n + 1$ を「H」とすることで容量切替スイッチ37 $n - 2$ 、37 $n + 1$ がONし、FD16 $n - 2$ 、16 $n + 2$ に対し、それぞれFD16 $n - 1$ 、16 $n + 1$ を追加容量として接続する。なお、FD16 $n - 1$ 、16 $n + 1$ を有する画素301( $i, n - 1$ )、301( $i, n + 1$ )はGbのカラーフィルタを持ち、期間 $t_{26} \sim t_{30}$ では読み出しを行わないでFD16 $n - 1$ 、16 $n + 1$ を利用可能である。

20

#### 【0062】

ここで、FD16 $n - 3 \sim 16n + 3$ の容量が全てCfで等しい値であるとすると、 $n$ 行目のFD容量はCf、一方 $n - 2$ 行目、 $n + 2$ 行目のFD容量は $2 \times C_f$ となる。ところで、容量拡大用FDとして利用するFDは、FD16 $n - 1$ の代わりにFD16 $n - 3$ を、FD16 $n + 1$ の代わりにFD16 $n + 3$ を用いても良い。その際にはADD $n - 2$ 、ADD $n + 1$ を「L」とし、代わりにADD $n - 3$ とADD $n + 2$ を「H」とする。これにより、画素301( $i, n - 2$ )、301( $i, n$ )、301( $i, n + 2$ )の加算において、中心に位置する画素301( $i, n$ )の信号に重み付けされた混合出力が可能となる。

30

#### 【0063】

時刻 $t_{26}$ から $t_{27}$ の期間では、信号RES $n - 2$ 、RES $n$ 、RES $n + 2$ が「H」とされ、各リセットスイッチ13 $n - 2$ 、13 $n$ 、13 $n + 2$ がONし、対応するFD16 $n - 2$ 、16 $n$ 、16 $n + 2$ にリセット電圧が与えられる。また同期間に、FD16 $n - 1$ 、16 $n + 1$ に対応する各リセットスイッチ13 $n - 1$ 、13 $n + 1$ を駆動する信号RES $n - 1$ 、RES $n + 1$ を「H」としている。

40

#### 【0064】

なお、リセットそのものは容量切替スイッチ37 $n - 2$ 、37 $n + 1$ を通してリセットスイッチ13 $n - 2$ 、13 $n + 2$ で行うことも可能である。リセットスイッチ13 $n - 2$ 、13 $n + 2$ が複数のFD16のリセットを十分にドライブすることが可能ならば、信号RES $n - 1$ 、RES $n + 1$ は「L」でもよい。

50

**【0065】**

時刻  $t_{27}$  から  $t_{28}$  の期間では、 $FD_{16n-2}$ 、 $16n$ 、 $16n+2$  のリセット電圧が各  $SF_{14n-2}$ 、 $14n$ 、 $14n+2$  を通して垂直出力線 38 で平均化され、補正回路 110 に出力される。

**【0066】**

時刻  $t_{28}$  から  $t_{29}$  の期間では、信号  $TX_{n-2}$ 、 $TX_n$ 、 $TX_{n+2}$  が「H」とされ、各転送スイッチ  $12n-2$ 、 $12n$ 、 $12n+2$  がONする。これにより、被写体像の撮影によって  $PD_{11n-2}$ 、 $11n$ 、 $11n+2$  に蓄積された信号電荷が各  $FD_{16n-2}$ 、 $16n$ 、 $16n+2$  に転送される。この時、 $n-2$  行目の画素 301 ( $i, n-2$ ) では  $FD_{16n-2}$  と同時に  $FD_{16n-1}$  に対しても蓄積され、 $n+2$  行目の画素 301 ( $i, n+2$ ) では  $FD_{16n+2}$  と同時に  $FD_{\underline{16}n+1}$  に対しても蓄積される。10

**【0067】**

ここで、 $PD_{11n-2}$ 、 $11n$ 、 $11n+2$  の信号電荷を  $Q_b$ 、 $Q_d$ 、 $Q_f$  とする、各  $SF_{14n-2}$ 、 $14n$ 、 $14n+2$  のゲートに入力される信号電圧は、それぞれ  $Q_b / (2 \times C_f)$ 、 $Q_d / C_f$ 、 $Q_f / (2 \times C_f)$  となる。

**【0068】**

時刻  $t_{29}$  から  $t_{30}$  の期間では、上記信号電圧が垂直出力線 38 で平均化され、補正回路 110 に出力される。通常読み出しモード時の FD 容量  $C_f$  の出力レンジに揃えたい場合は、かけるゲインは 1.5 倍なので、 $C_v = 2 / 3 \times C_0$  に設定する。20

**【0069】**

なお、画素 301 ( $i, n-2$ )、301 ( $i, n+2$ ) の FD 容量は、容量切替スイッチ  $37n-2$ 、 $37n+1$  を ON した際の寄生容量や  $SF_{14n-1}$ 、 $\underline{14}n+1$  の寄生容量の変動など、様々な影響を受ける。よって補正回路 110 でかけるゲインは、上記寄生容量の影響を踏まえたゲイン設定を行うことが好適である。これらの駆動によって 3 行分の画素 301 の出力信号混合が行われる。同様にして、Gb 画素の出力信号混合が行われる。

**【0070】**

Gb 画素の出力信号混合時には R 画素の  $FD_{16}$  を容量増加用 FD として利用可能である。Gb 画素の加算読み出しモードの駆動は R 画素と同等のため詳細な説明を省略するが、 $n-2$ 、 $n$ 、 $n+2$  行目の R 画素の出力信号混合の次に行う Gb 画素は  $n+1$ 、 $n+3$ 、 $n+5$  行目となる。その次に  $n+4$ 、 $n+6$ 、 $n+8$  行目の R 画素の出力信号混合を行い、 $n=n+2$  とされ順次行われていく。これにより低画素化を行った際の R 画素と Gb 画素の色重心ピッチを等間隔に揃えることが可能である。30

**【0071】**

第 3 の実施形態のように、FD 容量を増加させるための FD として読み出しに使用されない隣接画素の FD を利用することで、第 2 の実施形態の回路構成と比較して追加容量 28 を削減することができ、画素レイアウトに貢献できる。

**【0072】**

また、第 3 の実施形態の画素の回路構成では、容量切替スイッチ 37 を複数画素に亘って利用することで複数の  $FD_{16}$  と接続可能であり、様々な重み付け比率を作り出すことが可能である。例えば、 $n-2$  行目の  $FD_{16n-2}$  に対して  $FD_{16n-3}$ 、 $\underline{16}n-1$  の 2 つを接続し、 $n+2$  行目の  $FD_{\underline{16}n+2}$  に対して  $FD_{16n+1}$ 、 $\underline{16}n+3$  の 2 つを接続する。この時、FD 容量は  $n-2$  行目、 $n$  行目、 $n+2$  行目でそれぞれ  $3 \times C_f$ 、 $C_f$ 、 $3 \times C_f$  となり、重み付け比率 1 : 3 : 1 が得られる。ここで、補正回路 110 でかけるゲインは 1.8 倍となる。40

**【0073】**

< 第 4 の実施形態 >

次に、本発明の第 4 の実施形態について、図 11、図 12 を参照しながら説明する。ベイラー配列では、R 画素、B 画素と比較して G 画素のサンプリング周波数が高く、モアレ

が発生しにくい傾向がある。そこで第4の実施形態では、G画素の出力信号混合時に、中心画素の重み付けをR画素、B画素に対して強くすることを行う。

#### 【0074】

図11は第4の実施形態における画素401の回路構成を示している。なお、第4の実施形態における回路構成は、第3の実施形態で図9を参照して説明した回路構成と、以下の点で異なる。即ち、R-Gb列の容量切替スイッチ47と、Gr-B列の容量切替スイッチ49を駆動する信号をそれぞれ独立させていることである。この構成により、R-Gr行の加算読み出しモード時に、R列とGr列で重み付けの比率を個別に設定することが可能となる。同様に、Gb-B行の加算読み出しモード時に、Gb列とB列で重み付けの比率も個別に設定することが可能となる。

10

#### 【0075】

具体的な駆動については図12を用いて後述するが、R-Gb列の容量切替スイッチ47とGr-B列の容量切替スイッチ49は、それぞれ垂直走査回路109から供給される駆動信号ADDR、ADDDBによって駆動される。なお、第1の実施形態で図2を参照して説明した構成と同様の構成には、同じ参照番号を付して説明を省略する。以下の説明において、「n行目の」及び/または「m列目の」信号または構成を特定して説明する場合には、信号または構成を示す参照番号の後ろに添字n及び・またはmを付して説明する。例えば、「n行目の信号TX」は、添字nを付して「信号TXn」と記載する。同様に、「n-1行目」には添字n-1、「n+1行目」には添字n+1を付して記載する。また、「n行目、m列目の画素401」には、更に添字mを付して、「画素401(m, n)」と記載する。

20

#### 【0076】

次に、画素401の駆動について図12のタイミングチャートを参照して説明する。なお、列読み出し回路106の補正回路110は第1の実施形態と同様であるため、詳細な説明を省略する。図12(a)は第4の実施形態における加算読み出しモードのうち、R-Gr行を読み出す際の駆動を示すタイミングチャート、図12(b)はGb-B行を読み出す際の駆動を示すタイミングチャートである。

#### 【0077】

まず、時刻t31からt35の期間においてR-Gr行を読み出すが、信号SELn-2、SELn、SELn+2が「H」とされることで、各行選択スイッチ15n-2、15n、15n+2がONする。この期間では、n-2行、n行、n+2行目の3画素の信号の混合出力が行われる。

30

#### 【0078】

また、R画素401(m, n-2)のFD16n-2、R画素401(m, n+2)のFD16n+2に対して信号ADDRn-2及びADDRn+1を「H」とすることで容量切替スイッチ47n-2、47n+1がONする。これにより、R画素401(m, n-2)にGb画素401(m, n-1)のFD16n-1が、また、R画素401(m, n+2)にGb画素401(m, n+1)のFD16n+1がそれぞれ接続される。

#### 【0079】

一方、Gr画素401(m+1, n-2)のFD16n-2に対して、信号ADDDBn-3及びADDDBn-2を「H」とすることで容量切替スイッチ49n-3、49n-2がONする。これにより、Gr画素401(m+1, n-2)にB画素401(m+1, n-3)のFD16n-3及びB画素401(m+1, n-1)のFD16n-1が接続される。また、Gr画素401(m+1, n+2)のFD16n+2に対して、信号ADDDBn+1及びADDDBn+2を「H」とすることで容量切替スイッチ49n+1、49n+2がONする。これにより、Gr画素401(m+1, n+2)にB画素401(m+1, n+1)のFD16n+1及びB画素401(m+1, n+3)のFD16n+3が接続される。

40

#### 【0080】

ここで、FD16n-3～16n+3の容量が全てCfで等しい値であるとすると、n

50

行目の FD 容量は Cf、一方 n - 2 行目、n + 2 行目の FD 容量は R 画素では  $2 \times Cf$ 、Gr 画素では  $3 \times Cf$  となる。よって重み付け比率は R 画素で 1 : 2 : 1、Gr 画素で 1 : 3 : 1 となり、Gr 画素の中心画素の重み付けを、R 画素より強くすることが可能となる。以降の説明では、R - Gb 列、Gr - B 列共に共通の駆動が行われる。

#### 【0081】

時刻 t31 から t32 の期間では、信号 RESn-2、RESn、RESn+2 が「H」とされ、各リセットスイッチ 13n-2、13n、13n+2 が ON し、対応する FD16 にリセット電圧が与えられる。また同期間に、FD16n-3、16n-1、16n+1、16n+3 に対応する各リセットスイッチ 13n-3、13n-1、13n+1、13n+3 を駆動する信号 RESn-3、RESn-1、RESn+1、RESn+3 を「H」としている。10

#### 【0082】

なお、第 3 の実施形態でも触れたように、リセットスイッチ 13n-2、13n+2 が複数の FD16 のリセットを十分にドライブ可能ならば、信号 RESn-3、RESn-1、RESn+1、RESn+3 は「L」でもよい。

#### 【0083】

時刻 t32 から t33 の期間では、FD16n-2、16n、16n+2 のリセット電圧が各 SF14 を通して垂直出力線 38 で平均化され、補正回路 110 に出力される。

#### 【0084】

時刻 t33 から t34 の期間では、信号 TXn-2、TXn、TXn+2 が「H」とされ、各転送スイッチ 12n-2、12n、12n+2 が ON する。これにより、被写体像の撮影によって PD11n-2、11n、11n+2 に蓄積された信号電荷が各 FD16n-2、16n、16n+2 に転送される。20

#### 【0085】

この時、画素 401(m, n)、401(m+1, n) の PD11n から転送された信号電荷は R 画素、Gr 画素共に、それぞれ対応する FD16n に蓄積される。一方、画素 401(m, n-2) の PD11n-2 から転送された信号電荷は、FD16n-2 及び 16n-1 に、また、画素 401(m+1, n-2) の PD11n-2 から転送された信号電荷は、FD16n-3、16n-2、16n-1 に蓄積される。同様に、画素 401(m, n+2) の PD11n+2 から転送された信号電荷は、FD16n+1 及び 16n+2 に、また、画素 401(m+1, n+2) の PD11n+2 から転送された信号電荷は、FD16n+1、16n+2、16n+3 に蓄積される。30

#### 【0086】

ここで、PD11n-2、11n、11n+2 の信号電荷を Qb、Qd、Qf とすると、各 SF14n-2、14n、14n+2 のゲートに入力される信号電圧は、R - Gb 列ではそれぞれ  $Qb / (2 \times Cf)$ 、 $Qd / Cf$ 、 $Qf / (2 \times Cf)$  となる。一方、Gr - B 列ではそれぞれ  $Qb / (3 \times Cf)$ 、 $Qd / Cf$ 、 $Qf / (3 \times Cf)$  となり、R - Gb 列に対して Gr - B 列の中心画素の重み付けがより強く行われている。

#### 【0087】

時刻 t34 から t35 の期間では、上記信号電圧が垂直出力線 38 で重み付け平均化され、補正回路 110 に出力される。R - Gb 列の補正回路 110 において、通常読み出しモード時の FD 容量 Cf の出力レンジに揃えたい場合は、かけるゲインは 1.5 倍なので、 $Cv = 2 / 3 \times Co$  に設定する。一方、Gr - B 列の補正回路 110 においては、かけるゲインは 1.8 倍なので、 $Cv = 5 / 9 \times Co$  に設定する。これらの駆動によって単位画素 3 行分の重み付け出力信号混合が行われ、次の行の加算読み出し行として、 $n = n + 3$  となり、Gb - B 行の加算読み出し駆動が行われる。40

#### 【0088】

図 12(b) は第 4 の実施形態における加算読み出しモードのうち、Gb - B 行を読み出す際の駆動を示すタイミングチャートである。なお、図 12(b) は一部を除き、図 12(a) の駆動と同様なので、異なる点のみを詳細に説明する。50

**【0089】**

R - G r 行の読み出しでは、G r 画素の重み付け比率を ADD B で制御していた。即ち、図12(a)のt31～t35の期間では、ADD B n - 3 と ADD B n + 2 を「H」とし、R 画素に対して G r 画素の中心の重み付け比率を強めていた。

**【0090】**

これに対し、G b - B 行の読み出しでは、G b 画素の重み付け比率を ADD R で制御する。よって、図12(b)のt36～t40の期間では、ADD R n - 3 と ADD R n + 2 を「H」とすることで、B 画素に対して G b 画素の中心の重み付け比率を強めている。

**【0091】**

その他の駆動については図12(a)と同様であり、R 画素と同等の重み付け比率1:2:1での出力信号の混合がB 画素で行われる。このとき、G r - B 列の補正回路110において、通常読み出しモード時のFD容量Cf の出力レンジに揃えたい場合は、かけるゲインは1.5倍なので、Cv = 2/3 × C0 に設定する。また、G r 画素と同等の重み付け比率1:3:1での出力信号の混合がG b 画素で行われる。このとき、R - G b 列の補正回路110においては、かけるゲインは1.8倍なので、Cv = 5/9 × C0 に設定する。

**【0092】**

以上のように、容量切替スイッチの駆動をR - G b 列とG r - B 列で独立させ、信号 ADD R 、 ADD B を用いて制御することで、RB 画素に対して G 画素の中心画素信号の重み付け比率を強くすることが可能となる。

**【0093】**

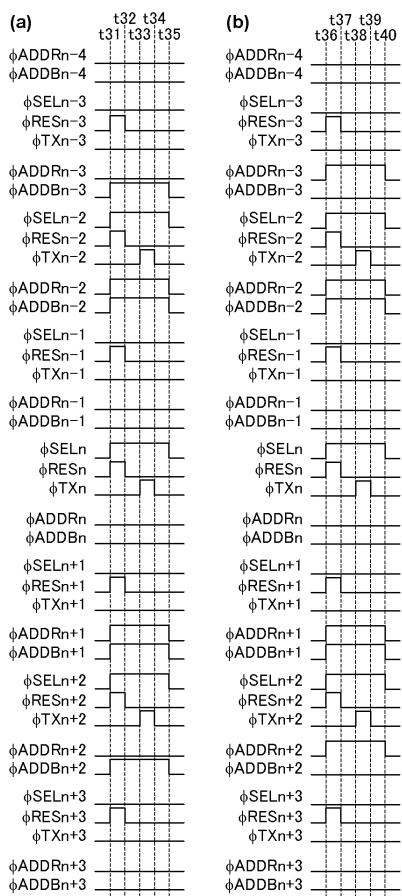

## &lt;第5の実施形態&gt;

本発明の第5の実施形態について、図13を参照しながら説明する。第4の実施形態ではR - G b 列とG r - B 列で容量切替スイッチ47、49の駆動信号を独立させていた。第5の実施形態では、更に、水平方向の3画素の出力信号の混合を考慮して、中心側の画素列と左右に位置する画素列で容量切替スイッチの駆動信号を独立させる例を示す。このような構成を探ることにより、水平方向に対しても中心画素の重み付けが達成可能となる。なお、第5の実施形態における画素501の回路構成は、第4の実施形態で図11を参考して説明した画素401の回路構成と同様であるため、詳細な説明を省略する。また、加算読み出しモード時の駆動は、容量切替スイッチの駆動信号を除いて同様であるため、相違点のみを説明する。

**【0094】**

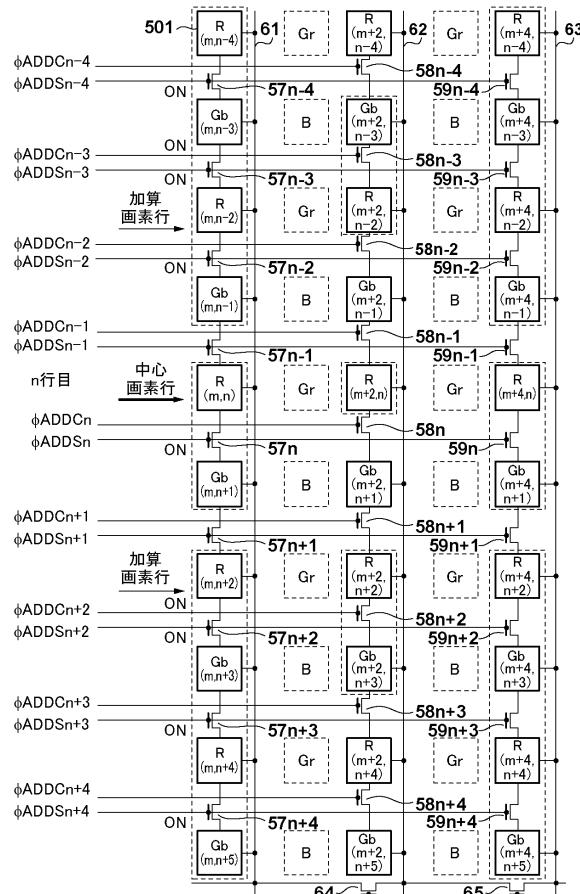

図13は、3×3のR 画素501(m, n - 2)、501(m, n)、501(m, n + 2)、501(m + 2, n - 2)、501(m + 2, n)、501(m + 2, n + 2)、501(m + 4, n - 2)、501(m + 4, n)、501(m + 4, n + 2)の加算読み出しモード時の、容量切替スイッチ57n - 4～57n + 4、58n - 4～58n + 4、59n - 4～59n + 4の駆動を説明する図である。加えて図13では、垂直方向の重み付け比率1:2:1に加えて、水平方向に対しても重み付け比率1:2:1で画素出力信号の混合を行う例を示している。なお、図13では、R 画素501を読み出す際に混合に関係の無いG r - B 列の画素は点線で示している。

**【0095】**

R 画素501(m + 2, n)を混合する画素の中心とした場合、中心の列に位置するR 画素501(m + 2, n - 2)、501(m + 2, n)、501(m + 2, n + 2)と左の列に位置するR 画素501(m, n - 2)、501(m, n)、501(m, n + 2)と、右の列に位置するR 画素501(m + 4, n - 2)、501(m + 4, n)、501(m + 4, n + 2)の重み付け比率を変更する。そこで、R 画素501(m + 2, n - 2)、501(m + 2, n)、501(m + 2, n + 2)を含む画素列の容量切替スイッチ58n - 4～58n + 4には信号 ADD C を供給し、駆動する。

**【0096】**

10

20

30

40

50

R 画素  $501(m+2, n)$  の行を  $n$  行目とした場合、 $n$  行目の加算読み出しモードの期間では、ADD C  $n - 3$ 、ADD C  $n + 2$  を「H」とすることで容量切替スイッチ  $58n - 3$ 、 $58n + 2$  がONする。この時、各画素のFD容量を  $C_f$  とおくと、R 画素  $501(m+2, n-2)$ 、 $501(m+2, n)$ 、 $501(m+2, n+2)$  のFD容量はそれぞれ  $2 \times C_f$ 、 $C_f$ 、 $2 \times C_f$  となる。

#### 【0097】

一方で、R 画素  $501(m, n-2)$ 、 $501(m, n)$ 、 $501(m, n+2)$  を含む画素列の容量切替スイッチ  $57n - 4 \sim 57n + 4$  には信号 ADD S を供給し、駆動する。 $n$  行目の加算読み出しモードの期間では、ADD S  $n - 4$ 、ADD S  $n - 3$ 、ADD S  $n - 2$ 、ADD S  $n$ 、ADD S  $n + 2$ 、ADD S  $n + 3$ 、ADD S  $n + 4$  を「H」とする。これにより、容量切替スイッチ  $57n - 4 \sim 57n - 2$ 、 $57n$ 、 $57n + 2 \sim 57n + 4$  がONする。この時、R 画素  $501(m, n-2)$ 、 $501(m, n)$ 、 $501(m, n+2)$  のFD容量はそれぞれ  $4 \times C_f$ 、 $2 \times C_f$ 、 $4 \times C_f$  となる。

#### 【0098】

また、R 画素  $501(m+4, n-2)$ 、 $501(m+4, n)$ 、 $501(m+4, n+2)$  を含む画素列の容量切替スイッチ  $59n - 4 \sim 59n + 4$  には容量切替スイッチ  $57n - 4 \sim 57n + 4$  と同様、信号 ADD S を供給し、駆動する。この時、R 画素  $501(m+4, n-2)$ 、 $501(m+4, n)$ 、 $501(m+4, n+2)$  のFD容量はそれぞれ  $4 \times C_f$ 、 $2 \times C_f$ 、 $4 \times C_f$  となる。

#### 【0099】

ここで、水平方向の画素行でのFD容量に注目すると、中心画素行であるR 画素  $501(m, n)$ 、 $501(m+2, n)$ 、 $501(m+4, n)$  のFD容量はそれぞれ  $2 \times C_f$ 、 $C_f$ 、 $2 \times C_f$  となる。一方、中心画素行に対して上側に位置する画素行のR 画素  $501(m, n-2)$ 、 $501(m+2, n-2)$ 、 $501(m+4, n-2)$  のFD容量はそれぞれ  $4 \times C_f$ 、 $2 \times C_f$ 、 $4 \times C_f$  となる。また、中心画素行に対して下側に位置する画素行のR 画素  $501(m, n+2)$ 、 $501(m+2, n+2)$ 、 $501(m+4, n+2)$  のFD容量についてもそれぞれ  $4 \times C_f$ 、 $2 \times C_f$ 、 $4 \times C_f$  となる。よって、中心画素信号の重み付けが垂直方向に加えて水平方向に対しても達成できる。この時、通常読み出しモード時のFD容量  $C_f$  の出力レンジに揃えたい場合は、かけるゲインは  $9 / 4$  倍なので、 $C_v = 4 / 9 \times C_0$  に設定する。

#### 【0100】

以上より、垂直出力線  $61 \sim 63$  に出力された時点で、あらかじめ水平方向に対して重み付けが行われているので、単純な加算回路を列回路  $106$  に設けることで垂直方向水平方向共に中心画素信号を重み付けした混合出力が得られる。

#### 【0101】

単純な加算回路の例としては、混合出力を得たい列の各垂直出力線  $61$ 、 $62$ 、 $63$  に対して図  $13$  に示すように接続スイッチ  $64$ 、 $65$  を設け、ONして連結させることで、垂直出力線  $61 \sim 63$  を1つの出力線として扱う。この状態で加算読み出しモードを行うことで、9つのR 画素  $501(m, n-2)$ 、 $501(m, n)$ 、 $501(m, n+2)$ 、 $501(m+2, n-2)$ 、 $501(m+2, n)$ 、 $501(m+2, n+2)$ 、 $501(m+4, n-2)$ 、 $501(m+4, n)$ 、 $501(m+4, n+2)$  は1つの出力線に同時出力となり、列読み出し回路  $106$  に対して出力信号混合が行われる。

#### 【0102】

また、列読み出し回路  $106$  で混合を行うことも可能である。その場合は、列読み出し回路  $106$  の列毎に読み出された信号を格納するS/H容量を設け、出力信号混合を行いたい列の各S/H容量をスイッチなどで連結させることでも達成可能である。ここで用いるS/H容量は、通常読み出しモードで使用するS/H容量を利用してもよい。

#### 【0103】

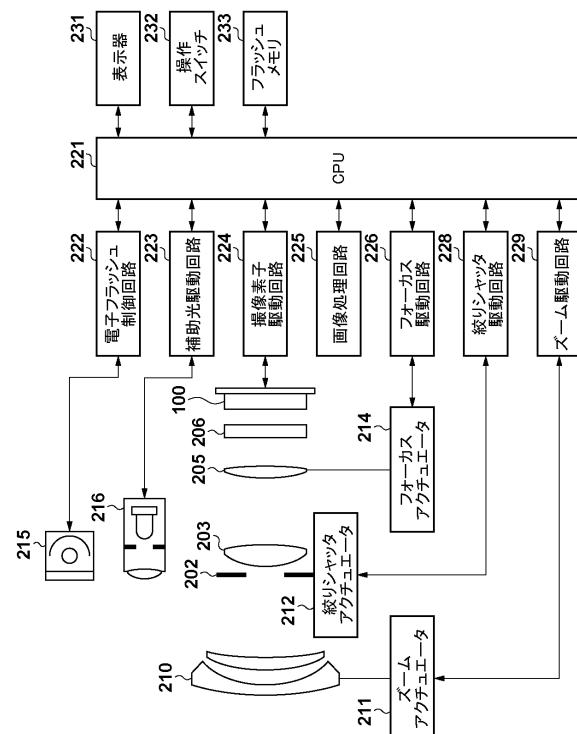

< 第6の実施形態 >

次に、本発明の第6の実施形態について説明する。図14は本発明の第1～第5の実施形態における撮像素子を有する撮像装置であるカメラの概略構成を示したものである。図14において、第1レンズ群210は結像光学系の先端に配置され、光軸方向に進退可能に保持される。絞り兼用シャッタ202は、その開口径を調節することで撮影時の光量調節を行うほか、静止画撮影時には露光秒時調節用シャッタとしての機能も備える。第2レンズ群203は、絞り兼用シャッタ202と一緒に光軸方向に進退し、第1レンズ群210の進退動作との連動により、変倍作用（ズーム機能）を実現することができる。

#### 【0104】

第3レンズ群205（フォーカスレンズ）は、光軸方向の進退により焦点調節を行う。光学的ローパスフィルタ206は、撮影画像の偽色やモアレを軽減するための光学素子である。撮像素子100は、2次元CMOSフォトセンサとその周辺回路からなり、結像光学系の結像面に配置される。上述した第1レンズ群210、絞り兼用シャッタ202、第2レンズ群203、第3レンズ群205、光学的ローパスフィルタ206は、結像光学系を構成している。

#### 【0105】

ズームアクチュエータ211は、不図示のカム筒を回動することで、第1レンズ群210ないし第2レンズ群203を光軸方向に進退駆動し、変倍操作を行う。絞りシャッタアクチュエータ212は、絞り兼用シャッタ202の開口径を制御して撮影光量を調節すると共に、静止画撮影時の露光時間制御を行う。フォーカスアクチュエータ214は、第3レンズ群205を光軸方向に進退駆動して焦点調節を行う。

#### 【0106】

撮影時の被写体照明用電子フラッシュ215で、キセノン管を用いた閃光照明装置が好適だが、連続発光するLEDを備えた照明装置を用いても良い。AF補助光発光部216は、所定の開口パターンを有したマスクの像を、投光レンズを介して被写界に投影し、暗い被写体あるいは低コントラスト被写体に対する焦点検出能力を向上させる。

#### 【0107】

カメラ内CPU221は、カメラ本体の種々の制御を司り、演算部、ROM、RAM、A/Dコンバータ、D/Aコンバータ、通信インターフェイス回路等を有する。CPU221は、ROMに記憶された所定のプログラムに基づいて、カメラが有する各種回路を駆動し、AF、撮影、画像処理と記録等の一連の動作を実行する。また、本実施形態では、結像光学系の状態に応じた焦点検出補正値も記憶されている。

#### 【0108】

焦点検出補正値は、第3レンズ群205の位置に対応したフォーカス状態、第1レンズ群210の位置に対応したズーム状態、結像光学系のFナンバー毎に複数用意されている。そして、撮像素子100の出力信号を用いて後述する焦点調節を行う際には、結像光学系の第1レンズ群210、第3レンズ群205の位置及びFナンバーに対応した最適な焦点検出補正値が選択される構成となっている。

#### 【0109】

なお本実施形態では、焦点検出補正値をCPU221に記憶するように構成したが、本発明はこれに限るものではない。例えば、交換レンズ式の撮像装置においては、結像光学系を有する交換レンズが不揮発性メモリを有し、そのメモリに上述の焦点検出補正値を記憶してもよい。この場合には、結像光学系の状態に応じて、焦点検出補正値を撮像装置に送信すればよい。

#### 【0110】

電子フラッシュ制御回路222は、撮影動作に同期して電子フラッシュ215を点灯制御する。補助光駆動回路223は、焦点検出動作に同期してAF補助光発光部216を点灯制御する。撮像素子駆動回路224は、撮像素子100の撮像動作を制御するとともに、取得した画像信号をA/D変換してCPU221に送信する。画像処理回路225は、撮像素子100が取得した画像の変換、カラー補間、JPEG圧縮等の処理を行う。

#### 【0111】

10

20

30

40

50

フォーカス駆動回路 226 は、焦点検出結果に基づいてフォーカスアクチュエータ 214 を駆動制御し、第3レンズ群 205 を光軸方向に進退駆動して焦点調節を行う。絞りシャッタ駆動回路 228 は、絞りシャッタアクチュエータ 212 を駆動制御して絞り兼用シャッタ 202 の開口を制御する。ズーム駆動回路 229 は、撮影者のズーム操作に応じてズームアクチュエータ 211 を駆動する。

#### 【0112】

LCD等の表示器 231 は、カメラの撮影モードに関する情報、撮影前のプレビュー画像と撮影後の確認用画像、焦点検出時の焦点検出領域の指標や合焦状態表示画像等を表示する。操作スイッチ群 232 は、電源スイッチ、レリーズ(撮影トリガ)スイッチ、ズーム操作スイッチ、撮影モード選択スイッチ等で構成される。着脱可能なフラッシュメモリ 233 は、撮影済み画像を記録する。

#### 【0113】

以上、本発明の好ましい実施形態について説明したが、本発明はこれらの実施形態に限定されず、その要旨の範囲内で種々の変形及び変更が可能である。

#### 【符号の説明】

#### 【0114】

11：フォトダイオード(PD)、12：転送スイッチ、14：ソースフォロワアンプ(SF)、16：フローティングディフュージョン部(FD)、57、58、59：容量切替スイッチ、64、65：接続スイッチ、100：撮像素子、101：画素、105：画素部、106：列読み出し回路、109：垂直走査回路、109：垂直走査回路、107：水平転送回路、108：水平走査回路。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 田仲 祐士

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 松永 隆志

(56)参考文献 特開2014-217021(JP,A)

特開2005-332880(JP,A)

特開2006-174325(JP,A)

特開2011-023825(JP,A)

特開2010-193437(JP,A)

特開2013-157889(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225-5/378

H04N 9/00-9/11

H01L 27/146