US 20120179942A1

# (19) United States (12) Patent Application Publication NAGADOMI et al.

## (10) Pub. No.: US 2012/0179942 A1 (43) Pub. Date: Jul. 12, 2012

#### (54) MEMORY SYSTEM

- Inventors: Yasushi NAGADOMI, Yokohama-Shi (JP); Daisaburo Takashima, Yokohama-Shi (JP); Kosuke Hatsuda, Tokyo (JP); Shinichi Kanno, Tokyo (JP)

- (73) Assignee: Kabushiki Kaisha Toshiba, Minato-ku (JP)

- (21) Appl. No.: 13/426,696

- (22) Filed: Mar. 22, 2012

#### **Related U.S. Application Data**

(63) Continuation of application No. 12/513,860, filed on May 7, 2009, now Pat. No. 8,156,393, filed as application No. PCT/JP2007/072898 on Nov. 28, 2007.

#### (30) Foreign Application Priority Data

Nov. 30, 2006 (JP) ..... 2006-322868

## Publication Classification

- (51) Int. Cl. *G06F 11/26* (2006.01)

- (52) U.S. Cl. ..... 714/718; 714/E11.159

#### (57) ABSTRACT

To provide a memory system which determines a memory state such as an exhaustion level and allows a memory to be efficiently used.

The memory system includes a NAND type flash memory 1 in which data can be electrically written/erased, a nonvolatile memory 2 which counts the number of erase operations of the NAND type flash memory 1 and retains the number of erase operations and a maximum number of erase operations, and a controller 3 which has a connection interface 31 to be given a self-diagnosis command from a computer 4, and retrieves the number of erase operations and the maximum number of erase operations from the nonvolatile memory 2 based on the self-diagnosis command and outputs the number of erase operations and the maximum number of erase operations to the computer 4 through the connection interface 31.

### - MEMORY SYSTEM

## DISPLAY EXAMPLE OF EXHAUSTION LEVEL OF MEMORY SYSTEM

FIG. 16

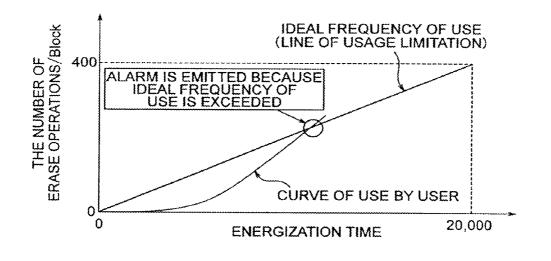

## RELATIONSHIP BETWEEN ENERGIZATION TIME AND THE NUMBER OF ERASE OPERATIONS

MAXIMUM ENERGIZATION TIME = 20,000 HOURS LIMITING NUMBER OF Program/Erase = 400/Blocks ⇒ USAGE LIMITATION GRAPH IS CREATED AS BELOW, AND ALARM IS EMITTED WHEN USE BY USER EXCEEDS THIS LINE

#### MEMORY SYSTEM

#### CROSS REFERENCE TO RELATED APPLICATIONS

**[0001]** This application is a continuation application of and claims the benefit of priority under 35 U.S.C. §120 for U.S. Ser. No. 12/513,860, filed May 7, 2009, pending, which is a National Stage application of PCT/JP2007/072898, filed Nov. 28, 2007, and claims benefit of priority under 35 U.S.C. §119 from JP 2006-322868, filed Nov. 30, 2006, the entire contents of each of which are incorporated herein by reference.

#### TECHNICAL FIELD

[0002] The present invention relates to a memory system.

#### BACKGROUND ART

**[0003]** In recent years, semiconductor memories have been used in various areas such as a main storage of a large-scale computer, a personal computer, a home electric appliance, a mobile phone, and the like. Particularly, a flash memory has such characteristics that data is not erased even if it is powered off, and it has a structure suitable for high integration, and used in information apparatuses such as a mobile phone and a digital camera.

[0004] Types of Flash EEPROM nonvolatile memory are mainly an NOR type and an NAND type. As for the NOR type, a read rate is high, the number of read operations is about 10<sup>13</sup>, and it is used as an instruction code storage. However, the NOR type has a small effective bandwidth for writing, and therefore not suitable for file recording. As for the NAND type, although an access rate is low compared to the NOR type, high integration is allowed, a large number of bits can be stored or erased at the same time is large, and written data can be captured in burst and programming is allowed in page units having many bits. Therefore, the NAND type memory has a large effective bandwidth, and is used for a memory card, a USB memory, a memory of a mobile phone, a memory of a portable music player, and the like. Recently, it is also considered as a replacement of a hard disk (hereinafter referred to as an HDD).

**[0005]** One problem in a case where the NAND type flash memory is as a replacement of an HDD is a problem of system lifetime. An HDD is equipped with a Self-Monitoring, Analysis and Reporting Technology (commonly known as SMART), which is a self-diagnosis function intended for early detection of a failure of the HDD itself and failure prediction, and thereby can notify a user of failure rate. Many of currently manufactured HDDs have this SMART, and predict a failure rate from items including a temperature, an operating time, a spin-up time, the number of alternate sectors (spare areas in which a sector causing bad data is arranged), and the like.

**[0006]** If an NAND type flash memory is also considered to need reliability equivalent to HDDs, it requires a self-diagnosis function like SMART. However, reason of failure in the NAND type flash memory is different from that of the HDDs. Due to characteristics of recoding media of HDDs, they have no limit on the number of write operations, but is susceptible to heat. Further, since they are machine components, there is a problem of aged deterioration of mechanical operation. On the other hand, the NAND type flash memory has little machine components, but consideration should be given to a failure caused by bad data due to an excessive number of store/erase operations. Therefore, a new criterion of system lifetime is needed in consideration of the number of store/ erase operations specific to the NAND type flash memory.

[0007] A limit on the number of store/erase operations of the NAND type flash memory will be described. For writing (storing/erasing) in a flash memory, high voltage is applied between a substrate and a gate such that electrons are injected and released into a floating gate. If this is performed many times, gate oxide film around the floating gate is deteriorated, and if it is left as is for a long time, the electrons injected into the floating gate get out therefrom, and data is destroyed. In other words, as the number of write operations increases, retention characteristics degrade. The number of write operations of current flash memories is about  $10^5$ , which is less than that of other nonvolatile memories. Therefore, if it is used as a replacement of an HDD, it is considered that data may be destroyed due to the limit of the number of store/erase operations, causing a trouble of the system. As a measure against such a limit on the number of store/erase operations, wear leveling is performed in which the number of erase operations is counted and a threshold value is set for each block, and physical address translation is performed between a block whose number of erase operations is large and a block whose number of erase operations is small, so that the numbers of store/erase operations are averaged.

[0008] Limit on the number of store/erase operations affects not only writing but also reading. During reading from the NAND type flash memory, high voltage is repeatedly applied to a non-selected cell (in view of block units, all pages except a target to be read), causing read disturb in which electrons enter in the floating gate through the gate oxide film and thus change a threshold voltage of a cell so that data is destroyed. In addition, during use, the gate oxide film is degraded due to storing/erasing, and accordingly read disturb occurs more frequently. Recently, NAND type flash memories have been developed to have more advanced multivalued memorization in which more than one bit information is stored in one cell, and therefore the effect of the read disturb seems to be larger. To prevent such read disturb, it is required to perform rewriting in (refresh) a block whose number of read operations is large so as to return a threshold voltage to its original state, which affects the number of store/erase operations.

[0009] There has been proposed a storage device which determines a memory state of a flash memory or the like, including: a memory having a main memory area and a spare memory area; display means; and processing means, wherein, when the number of rewrite operations in each address of the main memory area reaches a specified number, information stored in the address is transferred to the spare memory area; and when a remaining capacity of the spare memory area reaches a specified remaining capacity, the display means is driven to notify an operator or the like of a time to replace the memory (see, for example, Japanese Patent Laid-Open No. 2000-181805). However, in such a storage device, an end of memory lifetime for writing is determined to be reached and the memory is replaced in a state where the number of write operations in the spare memory area is still small. Therefore, the memory cannot be efficiently used.

#### DISCLOSURE OF THE INVENTION

Problems to be Solved by the Invention

**[0010]** An object of the present invention is to provide a memory system which determines a memory state such as an exhaustion level and allows a memory to be efficiently used.

#### Means for Solving the Problems

**[0011]** A memory system according to one aspect of the present invention includes: a first memory in which data can be electrically written/erased; a second memory which counts the number of erase operations of the first memory and retains the number of erase operations and a maximum number of erase operations of the first memory; and a controller which is connected to be given a self-diagnosis command from an outside through a connection interface, and which retrieves the number of erase operations and the maximum number of erase operations to the outside through the connection interface.

**[0012]** Further, a memory system according to one aspect of the present invention includes: a first memory in which data can be electrically written/erased; a second memory which monitors an amount of writing and an amount of reading with respect to the first memory, and retains the amount of writing based on a capacity of the first memory and a limiting number of write operations; and a controller which is connected to be given a self-diagnosis command from an outside through a connection interface, and which retrieves the amount of writing from the second memory based on the self-diagnosis command and outputs the amount of writing, the amount of reading, and the limiting amount of reading, and the limiting to the outside through the connection interface.

Advantages of the Invention

**[0013]** According to the present invention, a memory state such as an exhaustion level can be determined, and a memory can be efficiently used.

#### BRIEF DESCRIPTION OF THE DRAWINGS

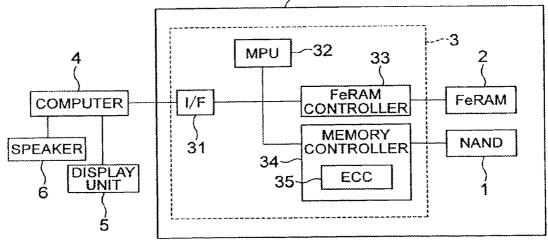

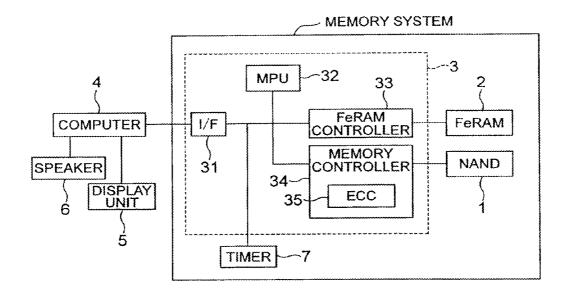

**[0014]** FIG. **1** is a schematic configuration diagram of a memory system according to a first embodiment of the present invention;

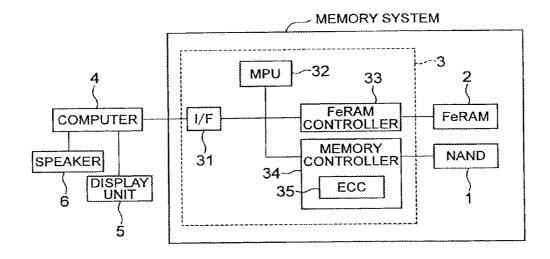

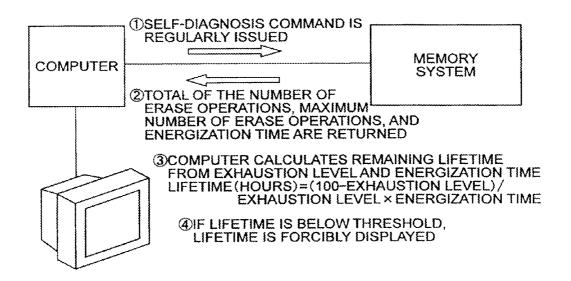

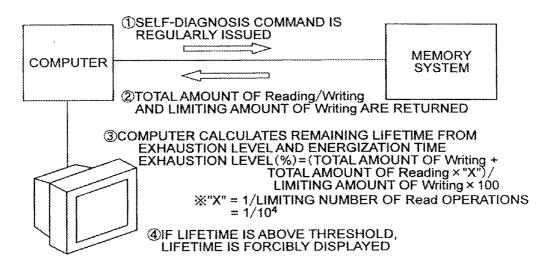

**[0015]** FIG. **2** is a diagram which illustrates operations of each unit associated with exhaustion level calculation and alarm notification;

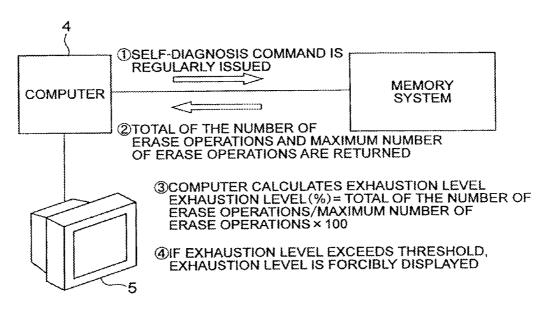

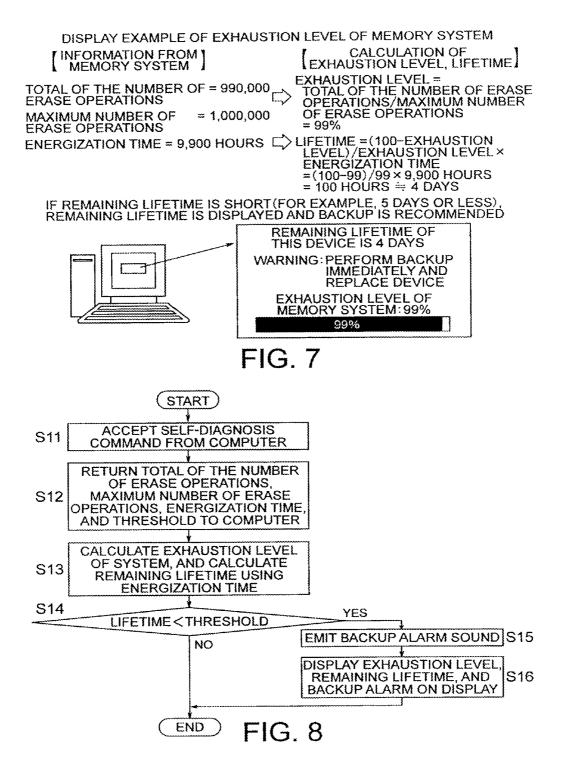

**[0016]** FIG. **3** is a diagram which shows one example of backup alarm display;

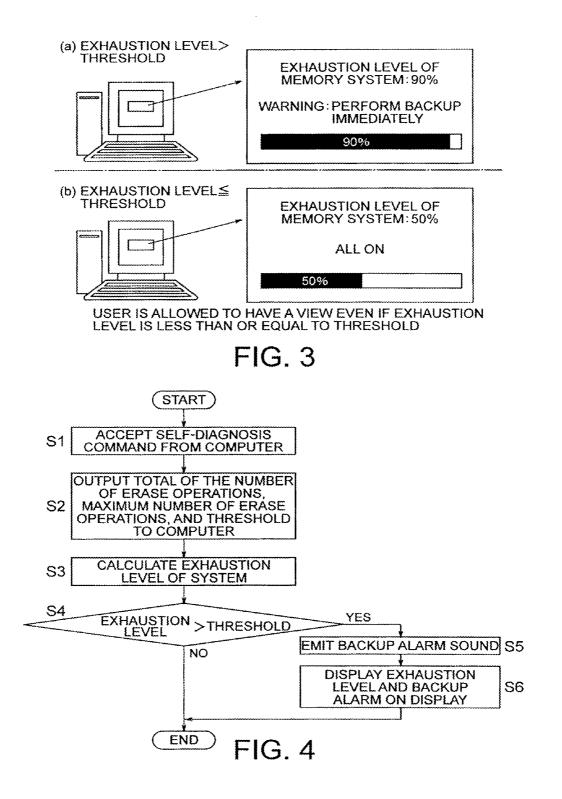

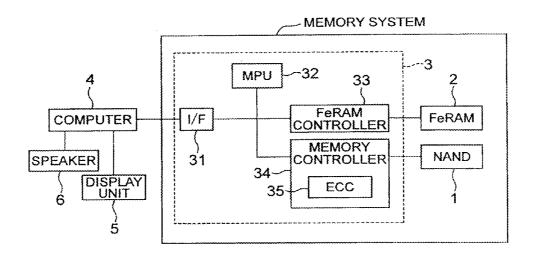

**[0017]** FIG. **4** is a diagram which shows a flow of exhaustion level calculation and notification to a user;

**[0018]** FIG. **5** is a schematic configuration diagram of a memory system according to a second embodiment of the present invention;

**[0019]** FIG. **6** is a diagram which illustrates each unit associated with exhaustion level calculation and alarm notification;

**[0020]** FIG. **7** is a diagram which shows one example of backup alarm display;

**[0021]** FIG. **8** is a diagram which shows a flow of exhaustion level calculation and notification to a user;

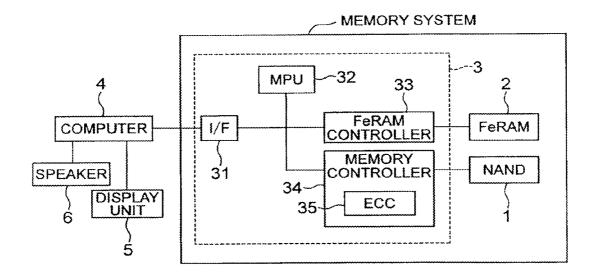

**[0022]** FIG. **9** is a schematic configuration diagram of a memory system according to a third embodiment of the present invention;

**[0023]** FIG. **10** is a diagram which illustrates each unit associated with exhaustion level calculation and alarm notification;

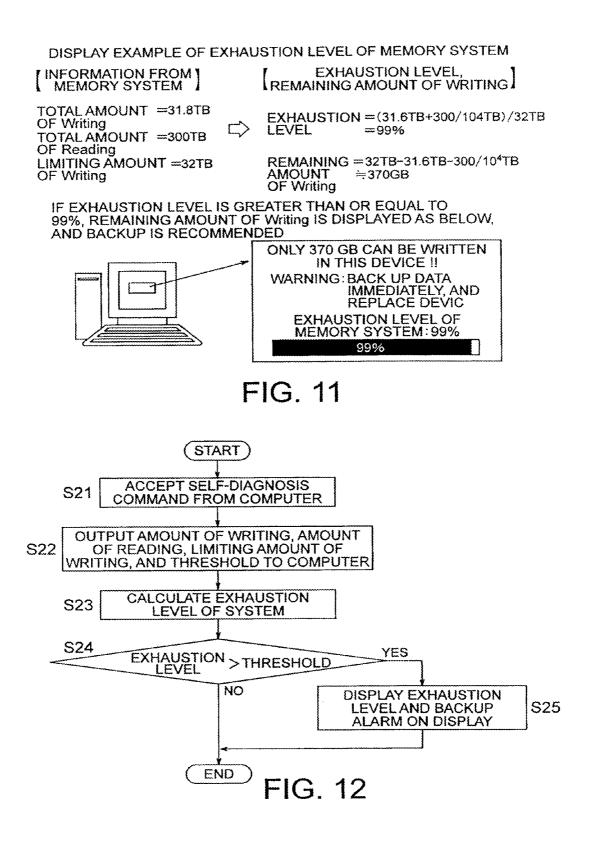

**[0024]** FIG. **11** is a diagram which shows one example of backup alarm display;

**[0025]** FIG. **12** is a diagram which shows a flow of exhaustion level calculation and notification to a user;

**[0026]** FIG. **13** is a schematic configuration diagram of a memory system according to a fourth embodiment of the present invention;

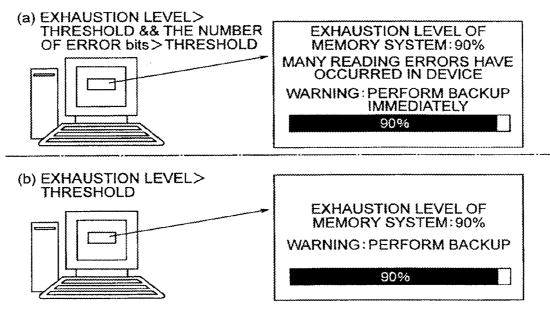

**[0027]** FIG. **14** is a diagram which shows one example of backup alarm display;

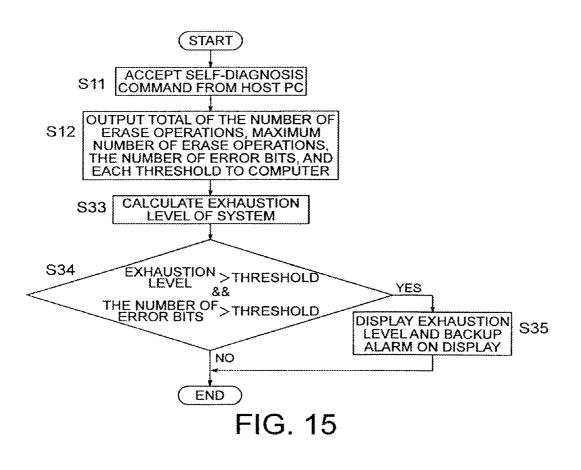

**[0028]** FIG. **15** is a diagram which shows a flow of exhaustion level calculation and notification to a user:

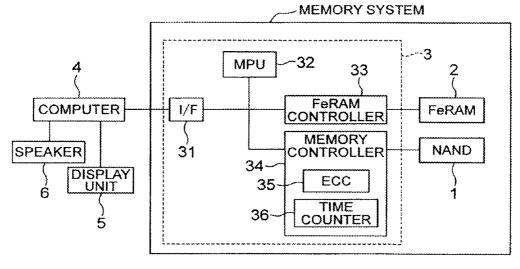

**[0029]** FIG. **16** is a schematic configuration diagram of a memory system according to a fifth embodiment of the present invention;

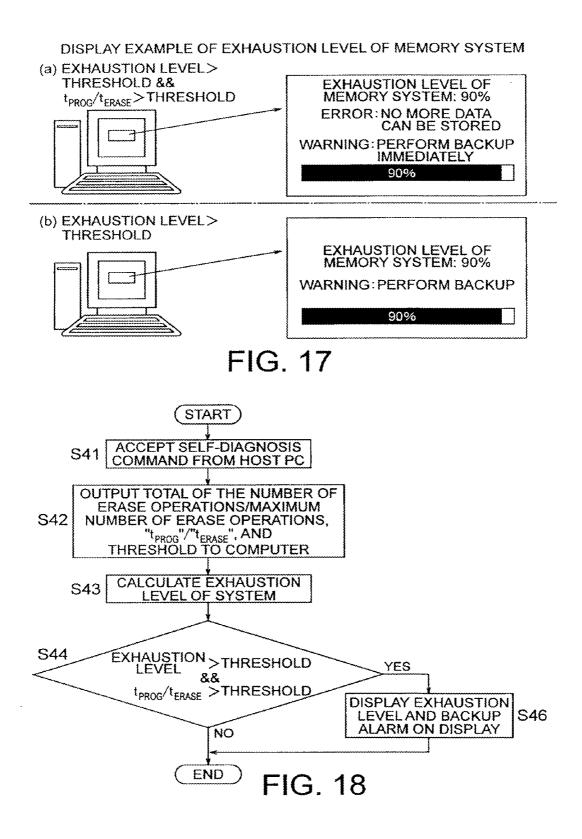

**[0030]** FIG. **17** is a diagram which shows one example of backup alarm display;

**[0031]** FIG. **18** is a diagram which shows a flow of exhaustion level calculation and notification to a user;

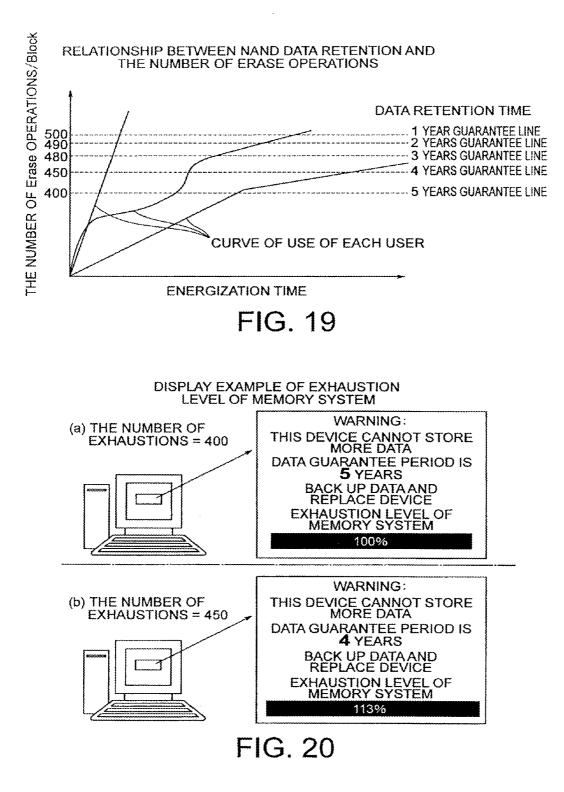

**[0032]** FIG. **19** is a graph which shows a relationship between the number of erase operations and data retention period;

**[0033]** FIG. **20** is a diagram which shows one example of backup alarm display; and

**[0034]** FIG. **21** is a graph which shows an ideal frequency of use.

## BEST MODE FOR CARRYING OUT THE INVENTION

**[0035]** Hereinafter, a memory system according to embodiments of the present invention will be described based on the drawings.

#### First Embodiment

FIG. 1 shows a schematic configuration of a memory system according to the first embodiment of the present invention. The memory system includes an NAND type flash memory 1, a nonvolatile memory (FeRAM) 2, and a controller 3. The memory system is connected to a computer 4 through a connection interface 31 included in the controller 3. A display unit (display) 5 and a speaker 6 are connected to the computer 4.

[0036] The FeRAM 2 has a counter (not shown), and for wear leveling, counts the number of erase operations in each block of the NAND type flash memory 1 as well as retaining a total of the number of erase operations. In addition, it retains a maximum number of erase operations and a threshold of exhaustion level of the NAND type flash memory 1. The exhaustion level will be described later. The maximum number of erase operations is obtained here from (limiting number of store/erase operations in each block of the NAND type flash memory 1)×(total number of blocks of the NAND type flash memory 1). In addition, FeRAM 2 also has a function as a cache for high-speed reading/writing of the NAND type flash memory 1.

[0037] The controller 3 has the connection interface 31, a processing unit (MPU) 32, a FeRAM controller 33, and a memory controller 34. The FeRAM controller 33 controls transferring data retained by the FeRAM 2, and the memory controller 34 controls transferring data to the NAND type flash memory 1. In addition, the memory controller 34 includes an error correction circuit (ECC) 35. When an incorrect value is stored in the NAND type flash memory 1, the

memory controller **34** can detect this error and correct it to a correct value. In the NAND type flash memory **1**, wear leveling is performed such that the number of store/erase operations in each block is averaged.

[0038] As shown in FIG. 2, a self-diagnosis command is regularly issued from the computer 4 to this memory system. The processing unit 32 receives the self-diagnosis command through the connection interface 31, and performs control to output a total of the number of erase operations, a maximum number of erase operations, and a threshold of exhaustion level which are retained by the FeRAM 2 to the computer 4 through the connection interface 31. The computer 4 calculates an exhaustion level of the NAND type flash memory 1 based on the total of the number of erase operations and the maximum number of erase operations. The exhaustion level is a ratio of the total of the number of erase operations to the maximum number of erase operations. If this exhaustion level is greater than or equal to the threshold, the exhaustion level and a backup alarm are displayed on the display unit 5 as shown in FIG. 3(a) so that a user is notified of them. The exhaustion level is calculated and displayed in percentage here. In addition, an alarm sound is emitted from the speaker 6 to give notification to the user. In addition, the user can optionally display the exhaustion level on the display unit 5. If the exhaustion level is less than or equal to the threshold, the exhaustion level is displayed as shown in FIG. 3(b). Of course, various representations may be used as a notification to a user. For example, it goes without saying that a circle graph, a line graph, various words and colors, and other indications can be used.

**[0039]** FIG. **4** shows a process flow of calculation of an exhaustion level of the NAND type flash memory **1** and notification of the exhaustion level to a user.

[0040] (Step S1) The processing unit 32 accepts a self-diagnosis command issued by the computer 4.

**[0041]** (Step S2) A total of the number of erase operations, the maximum number of erase operations, and a threshold of exhaustion level are retrieved from the FeRAM 2 and outputted to the computer 4.

**[0042]** (Step S3) The exhaustion level is calculated by the computer **4**.

[0043] (Step S4) Whether or not the calculated exhaustion level is greater than the threshold is determined. If it is less than or equal to the threshold, the process is terminated. If it is greater than the threshold, the process proceeds to step S5. [0044] (Step S5) A backup alarm sound is emitted from the speaker 6.

[0045] (Step S6) The exhaustion level and a backup alarm are displayed on the display unit 5. The step S5 of emitting an alarm sound and the step S6 of displaying an alarm may be replaced with each other.

**[0046]** In the above description, the exhaustion level is calculated from the total of the number of erase operations. However, since the number of erase operations in each block is averaged by wear leveling, an exhaustion level may be calculated from the number of erase operations in each block and a maximum number of erase operations.

**[0047]** In the NAND type flash memory **1**, the numbers of rewrite operations are evenly distributed among blocks by wear leveling so that the number of rewrite operations with respect to a whole memory area is increased. A notification of an exhaustion level of the NAND type flash memory **1** can be provided to a user at any time. Backup is recommended when the exhaustion level exceeds a predetermined threshold and

comes close to the end of a system lifetime, so that data loss can be prevented before it happens.

**[0048]** As described above, according to the memory system of the first embodiment, a memory state such as an exhaustion level can be determined, and a memory can be efficiently used.

#### Second Embodiment

**[0049]** FIG. **5** shows a schematic configuration of a memory system according to the second embodiment of the present invention. This memory system is configured to further include a timer **7** in addition to the memory system of the first embodiment shown in FIG. **1**. The timer **7** measures an energization time of this memory system. The measured energization time is retained in the FeRAM **2**.

**[0050]** As shown in FIG. **6**, a self-diagnosis command is regularly issued from the computer **4** to this memory system. The processing unit **32** receives the self-diagnosis command through the connection interface **31**, and performs control to output a total of the number of erase operations, a maximum number of erase operations, and an energization time, and a remaining lifetime which are retained by the FeRAM **2** to the computer **4** through the connection interface **31**. The remaining lifetime will be described later.

[0051] The computer 4 calculates an exhaustion level of the NAND type flash memory 1 based on the total of the number of erase operations and the maximum number of erase operations. Further, it calculates the remaining lifetime from the exhaustion level and the energization time. The exhaustion level is a ratio of the total of the number of erase operations to the maximum number of erase operations. A remaining lifetime is represented as (100–exhaustion level)/exhaustion level×energization time. For example, when maximum number of erase operations=1,000,000, total of the number of erase operations=990,000, and energization time=9,900 hours, remaining lifetime equals 100 hours.

[0052] If the remaining lifetime is less than a predetermined threshold, the exhaustion level, the remaining lifetime, and a backup alarm are displayed on the display unit 5 as shown in FIG. 7 so that a user is notified of them. The exhaustion level is calculated and displayed in percentage, and the remaining lifetime is calculated and displayed in units of days. In addition, an alarm sound may be emitted from the speaker 6 to give notification to the user. In addition, the user can optionally display the exhaustion level and the remaining lifetime on the display unit 5.

**[0053]** FIG. **8** shows a process flow of calculation of an exhaustion level and a lifetime of the NAND type flash memory **1** and notification of them to a user.

[0054] (Step S11) The processing unit 32 accepts a selfdiagnosis command issued by the computer 4.

**[0055]** (Step S12) A total of the number of erase operations, the maximum number of erase operations, an energization time, and a threshold of a remaining lifetime are retrieved from the FeRAM 2 and outputted to the computer 4.

**[0056]** (Step S13) The exhaustion level and the remaining lifetime are calculated by the computer 4.

[0057] (Step S14) Whether or not the calculated remaining lifetime is less than the threshold is determined. If it is greater than or equal to the threshold, the process is terminated. If it is less than the threshold, the process proceeds to step S15.

[0058] (Step S15) A backup alarm sound is emitted from the speaker 6.

**[0059]** (Step S16) The exhaustion level, the remaining lifetime, and a backup alarm are displayed on the display unit 5. **[0060]** In the above description, the exhaustion level is calculated from the total of the number of erase operations. However, since the number of erase operations in each block is averaged by wear leveling, an exhaustion level may be calculated from the number of erase operations in each block and a maximum number of erase operations.

**[0061]** In the NAND type flash memory **1**, the numbers of rewrite operations are evenly distributed among blocks by wear leveling so that the number of rewrite operations with respect to a whole memory area is increased. A notification of an exhaustion level of the NAND type flash memory **1** can be provided to a user at any time. Backup is recommended when the exhaustion level exceeds a predetermined threshold and comes close to the end of a system lifetime, so that data loss can be prevented before it happens. Further, a remaining lifetime is displayed, so that the user can replace a memory system in an efficient way.

**[0062]** As described above, according to the memory system of the second embodiment, a memory state such as a remaining lifetime can be determined, and a memory can be efficiently used.

#### Third Embodiment

**[0063]** FIG. **9** shows a schematic configuration of a memory system according to the third embodiment of the present invention. The memory system has a configuration similar to the first embodiment shown in FIG. **1**. In the memory system according to the first embodiment, an exhaustion level is calculated from a maximum number of erase operations and a total of the number of erase operations. However, in the present embodiment, an exhaustion level is calculated from an amount of writing into the NAND type flash memory **1** and an amount of reading therefrom.

[0064] The FeRAM 2 has a management table of a capacity of access to the NAND type flash memory 1, which retains an amount of writing, an amount of reading, and a threshold of an exhaustion level. In addition, it retains a limiting amount of writing of the NAND type flash memory 1. As used herein, a limiting amount of writing is defined as (a limiting number of store/erase operations in each block of the NAND type flash memory 1)×(a total capacity of the NAND type flash memory 1), multiplied by an efficiency of saving data as a weight, wherein the efficiency of saving data is an amount of erasing of the NAND type flash memory with respect to an amount of writing from the computer 4, and is predicted by simulation. The limiting amount of writing may have a margin to allow a minimum backup, startup, shutdown, and the like.

**[0065]** As shown in FIG. **10**, a self-diagnosis command is regularly issued from the computer **4** to this memory system. The processing unit **32** receives the self-diagnosis command through the connection interface **31**, and performs control to output an amount of writing, an amount of reading, a limiting amount of writing, and a threshold of exhaustion level which are retained by the FeRAM **2** to the computer **4** through the connection interface **31**. The computer **4** calculates an exhaustion level of the NAND type flash memory **1** based on the amount of writing, the amount of reading, and the limiting amount of writing.

**[0066]** The exhaustion level (%) can be calculated as (amount of writing+amount of reading×'x")/limiting amount of writing×100, wherein "x" is derived from the number of read operations by which read disturb occurs. For example, in

a case where read disturb is caused by  $10^4$  read operations, it is assumed that refresh occurs once with respect to an amount of reading which is a block capacity x  $10^4$ , and thus "x" can be set to  $10^{-4}$ .

[0067] If this exhaustion level is greater than or equal to the threshold, the exhaustion level and a backup alarm are displayed on the display unit 5 as shown in FIG. 11 so that a user is notified of them. In addition, an alarm sound may be emitted from the speaker 6 to give notification to the user. In addition, the user can optionally display the exhaustion level on the display unit 5.

**[0068]** FIG. **12** shows a process flow of calculation of an exhaustion level of the NAND type flash memory **1** and notification of the exhaustion level to a user.

[0069] (Step S21) The processing unit 32 accepts a selfdiagnosis command issued by the computer 4.

**[0070]** (Step S22) A limiting amount of writing, an amount of reading, an amount of writing, and a threshold of exhaustion level are retrieved from the FeRAM 2 and outputted to the computer 4.

[0071] (Step S23) The exhaustion level is calculated by the computer 4.

[0072] (Step S24) Whether or not the calculated exhaustion level is greater than the threshold is determined. If it is less than or equal to the threshold, the process is terminated. If it is greater than the threshold, the process proceeds to step S25. [0073] (Step S25) The exhaustion level and a backup alarm are displayed on the display unit 5.

**[0074]** In the NAND type flash memory 1, the numbers of rewrite operations are evenly distributed among blocks by wear leveling so that the number of rewrite operations with respect to a whole memory area is increased. A notification of an exhaustion level of the NAND type flash memory 1 can be provided to a user at any time. Backup is recommended when the exhaustion level exceeds a predetermined threshold and comes close to the end of a system lifetime, so that data loss can be prevented before it happens. Further, since refresh is also taken into account, the exhaustion level can be obtained more precisely.

**[0075]** As described above, according to the memory system of the third embodiment, a memory state such as an exhaustion level can be determined, and a memory can be efficiently used.

**[0076]** Although an exhaustion level is calculated using an amount of writing and an amount of reading in the present embodiment, an exhaustion level may be obtained from an amount of writing without use of an amount of reading.

#### Fourth Embodiment

**[0077]** FIG. **13** shows a schematic configuration of a memory system according to the fourth embodiment of the present invention. The memory system has a configuration similar to the first embodiment shown in FIG. **1**. Although the memory system according to the first embodiment calculates an exhaustion level from the maximum number of erase operations, and determines whether or not to display an alarm based on the exhaustion level, the number of error bits is considered in addition to an exhaustion level in the present embodiment.

**[0078]** The FeRAM **2** has a counter (not shown), and counts the number of erase operations of the NAND type flash memory **1** and retains a total of the number of erase operations. In addition, it retains a maximum number of erase operations and a threshold of exhaustion level of the NAND

type flash memory 1. The maximum number of erase operations is obtained here from (limiting number of store/erase operations in each block of the NAND type flash memory 1)×(total number of blocks of the NAND type flash memory 1). In addition, the number of error bits in each block is managed, and the number of error bits in a block having a maximum number of error bits and a threshold of the number of error bits are retained. Since in the NAND type flash memory 1, wear leveling is performed such that the number of write operations in each block is averaged, the number of error bits to be retained may be the number of error bits in any block.

**[0079]** A self-diagnosis command is regularly issued from the computer **4** to this memory system. The processing unit **32** receives the self-diagnosis command through the connection interface **31**, and performs control to output a total of the number of erase operations, a maximum number of erase operations, the number of error bits, and each threshold which are retained by the FeRAM **2** to the computer **4** through the connection interface **31**. The computer **4** calculates an exhaustion level of the NAND type flash memory **1** based on the total of the number of erase operations and the maximum number of erase operations.

[0080] If this exhaustion level is greater than or equal to a predetermined threshold and the number of error bits is greater than or equal to a predetermined threshold, the exhaustion level, a backup alarm, and a message to the effect that many errors have occurred are displayed on the display unit **5** as shown in FIG. **14**(*a*) so that a user is notified of them. As shown in FIG. **14**(*b*), only the exhaustion level and the backup alarm may be displayed. Further, a degree of forcing of a backup alarm to be displayed may be increased in a stepwise manner depending on the case of "exhaustion level>threshold" or the case of "exhaustion level>threshold && the number of bits>threshold". Further, an alarm sound may be emitted from the speaker **6** to give notification to the user.

**[0081]** FIG. **15** shows a process flow of calculation of an exhaustion level of the NAND type flash memory **1** and notification of the exhaustion level to a user.

[0082] (Step S31) The processing unit 32 accepts a selfdiagnosis command issued by the computer 4.

**[0083]** (Step S32) A total of the number of erase operations, the maximum number of erase operations, the number of error bits, and thresholds are retrieved from the FeRAM 2 and outputted to the computer 4.

[0084] (Step S33) The exhaustion level is calculated by the computer 4.

**[0085]** (Step S34) Whether or not the calculated exhaustion level is greater than a predetermined threshold and whether or not the number of error bits is greater than a predetermined threshold are determined. If both the exhaustion level and the number of error bits are greater than their thresholds, the process proceeds to step S35. If at least one of them is less than or equal to its threshold, the process is terminated.

**[0086]** (Step S**35**) The exhaustion level and a backup alarm are displayed on the display unit **5**.

**[0087]** In the above description, the exhaustion level is calculated from the total of the number of erase operations. However, since the number of erase operations in each block is averaged by wear leveling, an exhaustion level may be calculated from the number of erase operations in each block and a maximum number of erase operations.

**[0088]** The number of error bits in each block of the NAND type flash memory 1 may be monitored and retained in the FeRAM 2, the number of blocks in which the number of error bits exceeds a predetermined threshold may be obtained by the computer 4, and a degree of forcing of a backup alarm to be displayed may be increased in a stepwise manner according to the obtained number of blocks.

**[0089]** In the NAND type flash memory **1**, the numbers of rewrite operations are evenly distributed among blocks by wear leveling so that the number of rewrite operations with respect to a whole memory area is increased. A notification of an exhaustion level of the NAND type flash memory **1** can be provided to a user at any time. Backup is recommended when the exhaustion level exceeds a predetermined threshold and comes close to the end of a system lifetime, so that data loss can be prevented before it happens. Further, since the number of error bits is also taken into account, timing for backup can be obtained more precisely.

**[0090]** As described above, according to the memory system of the fourth embodiment, a memory state such as an exhaustion level can be determined, and a memory can be efficiently used.

#### Fifth Embodiment

**[0091]** FIG. **16** shows a schematic configuration of a memory system according to the fifth embodiment of the present invention. This memory system is configured to further include a time counter **36** provided in the memory controller **34** of the memory system of the first embodiment shown in FIG. **1**. The time counter **36** measures times required for storing/erasing in the NAND type flash memory **1** (which are referred to as " $t_{PROG}$ " and " $t_{ERASE}$ " respectively). The measured " $t_{PROG}$ " hu " $t_{ERASE}$ " are retained in the FeRAM **2**.

**[0092]** During a store (erase) operation of the NAND type flash memory, a verify operation for verifying whether data has been written or not is performed after data is stored (erased). If data has been incorrectly written, store (erase)/ verify operations are repeated so that correct data is written. As a fatigue level of the NAND type flash memory increases (an exhaustion level increase), the number of store (erase)/ verify operations increases, and with it, " $t_{PROG}$ " (" $t_{ERASE}$ ") increases. In the present embodiment, these " $t_{PROG}$ " and " $t_{ERASE}$ " are taken into account in addition to an exhaustion level.

**[0093]** A self-diagnosis command is regularly issued from the computer 4 to this memory system. The processing unit 32 receives the self-diagnosis command through the connection interface 31, and performs control to output a total of the number of erase operations, a maximum number of erase operations, a storing time ("t<sub>*PROG*</sub>"), an erasing time ("t<sub>*ERASE*</sub>"), and each threshold which are retained by the FeRAM 2 to the computer 4 through the connection interface 31. The computer 4 calculates an exhaustion level of the NAND type flash memory 1 based on the total of the number of erase operations.

**[0094]** If this exhaustion level is greater than or equal to a predetermined threshold, and the storing time (" $t_{PROG}$ ") and the erasing time (" $t_{ERASE}$ ") are greater than or equal to respective predetermined thresholds, the exhaustion level, a backup alarm, and an error are displayed on the display unit **5** as shown in FIG. **17**(*a*) so that a user is notified of them. As shown in FIG. **17**(*b*), only the exhaustion level and the backup

alarm may be displayed. Further, a degree of forcing of a backup alarm to be displayed may be increased in a stepwise manner depending on the case of "exhaustion level>threshold" or the case of "exhaustion level>threshold && "t<sub>PROG</sub>"/"t<sub>ERASE</sub>">threshold". Further, an alarm sound may be emitted from the speaker **6** to give notification to the user.

**[0095]** FIG. **18** shows a process flow of calculation of an exhaustion level of the NAND type flash memory **1** and notification of the exhaustion level to a user.

[0096] (Step S41) The processing unit 32 accepts a selfdiagnosis command issued by the computer 4.

[0097] (Step S42) A total of the number of erase operations, the maximum number of erase operations, a storing/erasing time (" $t_{PROG}$ "/" $t_{ERASE}$ "), and thresholds are retrieved from the FeRAM 2 and outputted to the computer 4.

[0098] (Step S43) The exhaustion level is calculated by the computer 4.

**[0099]** (Step S44) Whether or not the calculated exhaustion level is greater than a predetermined threshold and whether or not the storing/erasing time (" $t_{PROG}$ "/" $t_{ERASE}$ ") is greater than a predetermined threshold are determined. If both the exhaustion level and the storing/erasing time (" $t_{PROG}$ "/" " $t_{ERASE}$ ") are greater than their thresholds, the process proceeds to step S45. If at least one of them is less than or equal to its threshold, the process is terminated.

**[0100]** (Step S45) The exhaustion level and a backup alarm are displayed on the display unit 5.

**[0101]** It has been described that the exhaustion level is calculated from the total of the number of erase operations. However, since the number of erase operations in each block is averaged by wear leveling, an exhaustion level may be calculated from the number of erase operations in each block and a maximum number of erase operations.

**[0102]** In the NAND type flash memory **1**, the numbers of rewrite operations are evenly distributed among blocks by wear leveling so that the number of rewrite operations with respect to a whole memory area is increased. A notification of an exhaustion level of the NAND type flash memory **1** can be provided to a user at any time. Backup is recommended when the exhaustion level exceeds a predetermined threshold and comes close to the end of a system lifetime, so that data loss can be prevented before it happens. Further, since a time required for the verify operation is also taken into account, timing for backup can be obtained more precisely.

**[0103]** As described above, according to the memory system of the fifth embodiment, a memory state such as an exhaustion level can be determined, and a memory can be efficiently used.

**[0104]** Any of the above described embodiments is just one example, and should not be considered to be restrictive. For example, when the number of erase operations of the NAND type flash memory 1 exceeds a limiting number of erase operations, a notification of a data retention period (a data guarantee period) may be provided to a user. As shown in FIG. 19, a data retention period based on the number of erase operations is determined from characteristics of the NAND type flash memory, and is retained in the FeRAM 2. When the number of erase operations in each block of the NAND type flash memory 1 which is being monitored by the FeRAM 2 becomes 400, the data guarantee period passes over a line of five years, and therefore the computer 4 displays the data guarantee period and a backup alarm on the display unit 5 as shown in FIG. 20(*a*) so that a user is notified of them. When

the number of erase operations becomes 450 after further writing, the data guarantee period passes over a line of four years, and therefore the data guarantee period is made shorter and displayed as four years as shown in FIG. 20(b) so that the user is notified of it. Thereby, a notification that possibility of data loss has been increased is provided to the user, and reliability of the memory system can be improved. Although it has been described that a data guarantee period according to the number of erase operations in each block is displayed, a data guarantee period may be displayed based on a total of the number of erase operations.

[0105] Further, in the second embodiment, an ideal frequency of use which is determined from a maximum energization time and a limiting number of store/erase operations as shown in FIG. 21 may be compared with a user's frequency of use, and a notification that the memory has been used to an excessive degree may be provided to the user when the user's frequency of use exceeds the ideal frequency of use. The number of erase operations in each block, a maximum number of erase operations, a present energization time, and a maximum energization time are retained in the FeRAM 2, and are outputted to the computer 4 when a self-diagnosis command is accepted. The number of write operations are varied depending on blocks, because an amount of writing is increased due to initialization and the like in an early use stage, or the numbers of write operations are not yet completely distributed in an even manner among blocks by wear leveling. For this reason, an alarm is not displayed even if an ideal frequency of use is exceeded when a total of the number of erase operations is small, and an alarm is displayed, for example, when the total of the number of erase operations becomes half or more of the limiting number of store/erase operations.

**[0106]** In the fourth and fifth embodiments, an exhaustion level based on a total of the number of erase operations is calculated, but an exhaustion level based on an amount of writing and an amount of reading may be calculated as described in the third embodiment.

**[0107]** The nonvolatile memory **2** in the memory system of the above described embodiments may be an MRAM, a PRAM, or an RRAM instead of the FeRAM. Or, it may be composed of a DRAM or SRAM, which is a volatile memory. However, if it is composed of a volatile memory, management information needs to be saved in the NAND type flash memory **1**, which is a nonvolatile memory, each time the memory system is powered off.

**[0108]** A self-diagnosis command may be issued every time the computer **4** is started up.

- 1. A memory system comprising:

- a first memory in which data can be electrically written/ erased;

- a second memory which retains a number of erase operations and a maximum number of erase operations of the first memory; and

- a controller configured to receive a self-diagnosis command through a connection interface, and retrieve the number of erase operations and the maximum number of erase operations from the second memory in response to receiving self-diagnosis command and output the number of erase operations and the maximum number of erase operations and threshold of an exhaustion level through the connection interface.

2. The memory system according to claim 1, wherein the threshold of an exhaustion level is calculated by division of the number of erase operations by the maximum number of erase operations.

3. The memory system according to claim 1, wherein the second memory retains data guarantee period information of the first memory associated with the number of erase operations, and the controller outputs the data guarantee period information in response to receiving the self-diagnosis command.

**4**. The memory system according to claim **1**, wherein the second memory is non-volatile random access memory.

5. The memory system according to claim 1, wherein the number of erase operations of the first memory is retained for each block of the first memory.

- **6**. A memory system comprising:

- a first memory in which data can be electrically written/ erased;

- a second memory which counts the number of erase operations of the first memory and retains the number of erase operations and a maximum number of erase operations of the first memory;

- a timer configured to measure an operation time; and

- a controller configured to receive a self-diagnosis command through a connection interface, and retrieve from the second memory in response to receiving self-diagnosis command and output the number of erase operations, the maximum number of erase operations, operation time and threshold of remaining lifetime through the connection interface.

7. The memory system according to claim 6, wherein the second memory further retinas a maximum operating time of the first memory, and the controller further outputs the maximum operating time in response to the self-diagnosis command.

**8**. The memory system according to claim **6**, wherein the second memory is non-volatile random access memory.

**9**. The memory system according to claim **6**, wherein a number of erase operations of the first memory is retained for each block of the first memory.

**10**. A memory system comprising:

a memory in which data can be electrically written/erased;

a controller configured to receive a self-diagnosis command through a connection interface, and output a number of erase operations, a maximum number of erase operations, and threshold of an exhaustion level of the memory through the connection interface in response to receiving self-diagnosis command.

11. The memory system according to claim 10, wherein further comprising a second memory which retain the number of erase operations and the maximum number of erase operations of the first memory.

**12.** The memory system according to claim **11**, wherein the second memory is non-volatile random access memory.

13. The memory system according to claim 10, wherein the threshold of an exhaustion level is calculated by division of the number of erase operations by the maximum number of erase operations.

14. A system comprising:

a host device;

a memory system electronically connected to the host device;

the memory system comprising;

- a command interface configured to receive self-diagnosis command from the host device

- a memory in which data can be electrically written/erased;

- a controller configured to receive a self-diagnosis command through a connection interface, and output a number of erase operations, a maximum number of erase operations, and threshold of an exhaustion level of the memory through the connection interface in response to receiving self-diagnosis command.

**15**. The system according to claim **14**, wherein the host device calculate an exhaustion level based on the number of erase operations and the maximum number of erase operation of the memory, and determine if the calculated exhaustion level is greater than threshold of an exhaustion level.

**16**. The system according to claim **15**, wherein the host device output alarm signal if the calculation exhaustion level is greater than the threshold of an exhaustion level.

**17**. The system according to claim **15**, wherein the host device further comprising the display, and the host device displays the exhaustion level of the first memory on the display.

\* \* \* \* \*