**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.

G11C 7/10 (2006.01)

G11C 7/12 (2006.01)

(11) 공개번호

10-2007-0029193

(43) 공개일자

2007년03월13일

(21) 출원번호 10-2006-7026035

(22) 출원일자 2006년12월11일

심사청구일자 없음

번역문 제출일자 2006년12월11일

(86) 국제출원번호 PCT/US2005/015858

(87) 국제공개번호

WO 2006/001910

국제출원일자 2005년05월05일

국제공개일자

2006년01월05일

(30) 우선권주장 10/865,274 2004년06월10일 미국(US)

(71) 출원인

프리스케일 세미컨덕터, 임크.

미합중국 텍사스 (우편번호 78735) 오스틴 월리암 캐논 드라이브 웨스트 6501(72) 발명자

라마라주, 라빈드라라즈

미국 78681 텍사스주 라운드 락 에반스 드라이브 7014

호크스트라, 조지 피.

미국 78750 텍사스주 오스틴 플라워 센트 코트 11705

켄카르, 프레샌트 유.

미국 78736 텍사스주 오스틴 커니페 코브 6501(74) 대리인

주성민

백만기

이중희

전체 청구항 수 : 총 34 항

(54) 데이터 유지 래치를 갖는 메모리 장치

(57) 요약

메모리 장치는 복수 개 쌍의 상보형 비트 라인(200, 202)과 복수의 래치 회로를 포함한다. 복수 개 쌍의 상보형 비트 라인 각 쌍은 메모리 셀의 열(31, 37)에 결합된다. 래치 회로 각각은 데이터 라인에 결합된 입력과, 그 데이터 라인의 값에 따른 상보형 래치 값들을 제공하는 제1 출력과 제2 출력을 갖는다. 복수의 래치들 각각에서, 제1 출력은 한 쌍의 복수 개 비트 라인 중 제1 비트 라인에 결합되어 제1 비트 라인의 값이 메모리 장치의 동작 동안 제1 출력에 의해 연속해서 결정되고, 제2 출력은 그 쌍의 제2 비트 라인에 결합되어 제2 비트 라인의 값이 메모리 장치의 동작 동안 제2 출력에 의해 연속해서 결정된다.

대표도

도 3

## 특허청구의 범위

### 청구항 1.

메모리 장치로서,

비트 라인;

상기 비트 라인에 결합되는 메모리 셀의 열; 및

데이터 라인에 결합되는 입력과, 상기 데이터 라인의 값에 따른 래치 값은 제공하는 출력을 갖는 래치 회로로서, 상기 출력은 상기 비트 라인에 결합되어 상기 비트 라인의 값이 상기 메모리 장치의 동작 동안 상기 출력에 의해 연속해서 결정되는 래치 회로를 포함하는

메모리 장치.

### 청구항 2.

제1항에 있어서,

상기 비트 라인은 기입 비트 라인인 메모리 장치.

### 청구항 3.

제2항에 있어서,

판독 비트 라인을 더 포함하며, 상기 메모리 셀의 열은 상기 판독 비트 라인에 결합되는 메모리 장치.

### 청구항 4.

제1항에 있어서,

제2 비트 라인을 더 포함하며, 상기 제2 비트 라인은 상기 비트 라인에 대한 상보형 비트 라인이고, 상기 메모리 셀의 열은 상기 제2 비트 라인에 결합되는 메모리 장치.

### 청구항 5.

제4항에 있어서,

상기 래치 회로는 제2 출력을 포함하고, 상기 제2 출력은 상기 제2 비트 라인에 결합되어 상기 제2 비트 라인의 값이 메모리 장치의 동작 동안 상기 제2 출력에 의해 연속해서 결정되는

메모리 장치.

### 청구항 6.

제1항에 있어서,

상기 래치 회로는 한 쌍의 교차 결합되는(cross coupled) 인버터를 포함하고;

상기 래치 회로의 출력은 상기 인버터 쌍 중 제1 인버터의 입력, 및 상기 인버터 쌍 중 제2 인버터의 출력에 결합되는

메모리 장치.

### 청구항 7.

제6항에 있어서,

상기 래치 회로는, 상기 래치 회로의 출력에 접속되는 출력과, 상기 인버터 쌍 중 상기 제1 인버터의 입력 및 상기 인버터

쌍 중 상기 제2 인버터의 출력에 접속되는 입력을 갖는, 제3 인버터를 포함하는

메모리 장치.

### 청구항 8.

제1항에 있어서,

상기 래치 회로는 클럭 신호를 수신하는 제2 입력을 포함하고, 상기 래치 회로의 출력에서의 상기 래치 값은 상기 클럭 신

호의 상태 변경에 의해 결정되는 소정의 시점에서 상기 데이터 라인의 값에 따른 값을 변동시키는

메모리 장치.

### 청구항 9.

제8항에 있어서,

상기 비트 라인의 값은 상기 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서 상기 데이터 라인상의 값에만 응답

하여 변동되는

메모리 장치.

### 청구항 10.

제8항에 있어서,

상기 메모리 셀의 열에 있는 메모리 셀에 결합되어, 기입 신호를 상기 메모리 셀에 전달하기 위한 워드 라인과;

상기 워드 라인에 결합되는 출력을 포함하여 상기 기입 신호를 제공하는 워드 라인 생성 회로-상기 워드 라인 생성 회로는

클럭 신호를 수신하는 입력을 포함하고, 상기 기입 신호는 상기 워드 라인 생성 회로의 입력에서 수신된 상기 클럭 신호의

상태 변경에 의해 결정되는 소정의 시점에서 상태를 변경시킴-

를 더 포함하고;

상기 워드 라인 생성 회로에서 수신된 클럭 신호와, 상기 래치의 제2 입력에서 수신된 클럭 신호는 공통 클럭 신호로부터 생성되는

메모리 장치.

### 청구항 11.

제10항에 있어서,

상기 래치 회로의 출력에서의 값은 제1 상태에서 제2 상태로의 상기 공통 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서 상기 데이터 라인의 값에 따른 값을 변동시키고;

상기 기입 신호는, 상기 제1 상태에서 상기 제2 상태로의 상기 공통 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서, 비기입 상태에서 기입 상태로 변경되는

메모리 장치.

### 청구항 12.

제11항에 있어서,

상기 기입 신호는, 상기 제1 상태에서 상기 제2 상태로의 상기 공통 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서, 기입 상태에서 비기입 상태로 변경되는

메모리 장치.

### 청구항 13.

제1항에 있어서,

제2 비트 라인;

상기 제2 비트 라인에 결합되는 메모리 셀의 제2 열;

제2 데이터 라인에 결합되는 제2 입력과, 상기 제2 데이터 라인의 값에 따른 래치 값을 제공하는 제2 출력을 갖는 제2 래치 회로로서, 상기 제2 래치 회로의 상기 제2 출력은 상기 제2 비트 라인에 결합되어 상기 제2 비트 라인의 값이 메모리 장치의 동작 동안 상기 제2 출력에 의해 연속해서 결정되는 제2 래치 회로를 더 포함하는

메모리 장치.

### 청구항 14.

제13항에 있어서,

상기 메모리 셀의 열은 상기 메모리 셀의 제2 열에 있는 메모리 셀과 동일한 행에 위치되는 메모리 셀을 포함하는

메모리 장치.

### 청구항 15.

제1항에 있어서,

상기 비트 라인의 값은 상기 데이터 라인의 값에만 응답하여 변동되는

메모리 장치.

### 청구항 16.

제1항에 있어서,

상기 메모리 장치는 멀티-포트 레지스터 파일을 특징으로 하는 메모리 장치.

### 청구항 17.

제1항에 있어서,

상기 출력은 상기 비트 라인에 결합되어 상기 비트 라인의 값이 상기 열의 메모리 셀에 대한 모든 메모리 판독들을 포함하는 상기 메모리 장치의 동작 동안 상기 출력에 의해 연속해서 결정되는

메모리 장치.

### 청구항 18.

제1항의 메모리 장치를 포함하는 집적 회로로서,

상기 집적 회로는 프로세서 코어를 더 포함하는 집적 회로.

### 청구항 19.

제1항에 있어서,

상기 메모리 셀의 열에 있는 메모리 셀들에 대한 판독 및 기입은 메모리 장치의 동작 동안 수행되는 메모리 장치.

### 청구항 20.

메모리 장치를 동작시키는 방법으로서,

메모리 셀의 열에 있는 메모리 셀들에 대해 복수의 판독 및 복수의 기입을 실행하기를 포함하여 메모리 장치를 동작시키는 단계;

상기 동작 단계 동안 래치 출력을 이용하여 상기 메모리 셀의 열에 결합되는 비트 라인 값을 연속해서 제어하는 단계

를 포함하는 메모리 장치를 동작시키는 방법.

## 청구항 21.

제20항에 있어서,

제1 상태에서 제2 상태로의 클럭 신호의 상태 변경의 의해 결정되는 소정의 시점에서 래치 입력의 값에 응답하여 상기 래치 출력의 값을 변동시키는 단계

를 더 포함하는 방법.

## 청구항 22.

제20항에 있어서,

상기 메모리 셀의 옆에 있는 한 메모리 셀에 값을 기입하는 단계를 더 포함하고, 상기 기입 단계는 상기 비트 라인의 상태를 변경시키기를 포함하는 방법.

## 청구항 23.

제22항에 있어서,

상기 기입 단계는 비기입 상태에서 기입 상태로의 상기 메모리 셀에 결합되는 기입 라인의 상태를 변경시키기를 포함하는 방법.

## 청구항 24.

제23항에 있어서,

상기 비트 라인의 상태를 변경시키기는 제1 상태에서 제2 상태로의 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서 상기 상태를 변경시키기를 포함하고;

상기 기입 라인의 상태를 변경시키기는 상기 제1 상태에서 상기 제2 상태로의 상기 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서 상기 상태를 변경시키기를 포함하는 방법.

## 청구항 25.

제24항에 있어서,

상기 기입 단계는 상기 제2 상태에서 상기 제1 상태로의 상기 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서 상기 기입 상태에서 상기 비기입 상태로의 상기 기입 라인의 상태를 변경시키기를 더 포함하는 방법.

## 청구항 26.

제22항에 있어서,

상기 기입 단계는 상기 제1 상태에서 상기 제2 상태로의 상기 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서 상기 기입 상태에서 상기 비기입 상태로의 상기 기입 라인의 상태를 변경시키기를 더 포함하는 방법.

## 청구항 27.

제22항에 있어서,

상기 기입 단계는 제1 상태에서 제2 상태로의 상기 비트 라인의 상태를 변경시키기를 포함하고, 상기 방법은

상기 기입 단계 이후에, 상기 메모리 셀의 열에 있는 한 메모리 셀에 다른 값을 기입하는 단계를 더 포함하고, 상기 다른 값을 기입하는 단계는 상기 비트 라인의 상태를 변경시키기를 포함하고, 상기 기입의 상태와 상기 다른 값을 기입한 상태 중간에서 상기 열의 한 메모리 셀에 대해 다른 기입을 수행하지 않으며;

상기 비트 라인은 상기 기입의 상태를 변경한 시점에서 상기 다른 값을 기입한 상태로 변경한 시점까지 상기 제2 상태로 유지되는 방법.

## 청구항 28.

제27항에 있어서,

상기 기입 단계 이후부터 상기 다른 값을 기입하는 단계 전까지 상기 열의 메모리 셀에 대한 값을 판독하는 단계를 더 포함하고, 상기 비트 라인은 판독할 메모리 셀의 값에 상관없이 상기 제2 상태에서 유지되는 방법.

## 청구항 29.

제20항에 있어서,

상기 동작 단계 동안, 상기 래치 출력으로 상기 메모리 셀의 열에 결합되는 제2 비트 라인의 값을 연속해서 제어하는 단계를 더 포함하고, 상기 제2 비트 라인은 상기 비트 라인의 상보형 비트 라인인 방법.

## 청구항 30.

제20항에 있어서,

상기 메모리 장치를 동작시키는 단계는 메모리 셀의 제2 열에 있는 메모리 셀들에 대해 복수의 판독 및 복수의 기입을 수행하는 단계를 더 포함하고, 상기 방법은

상기 동작 단계 동안, 제2 래치 출력으로 상기 메모리 셀의 제2 열에 결합되는 제2 비트 라인의 값을 연속해서 제어하는 단계를 더 포함하는 방법.

## 청구항 31.

메모리 장치로서,

비트 라인;

상기 비트 라인에 결합되는 메모리 셀의 열; 및

데이터 라인에 결합되는 입력과, 상기 데이터 라인의 값에 따른 래치 값을 제공하는 출력을 갖는 래치 회로를 포함하고, 상기 출력은 상기 비트 라인에 접속되는 메모리 장치.

### 청구항 32.

제31항에 있어서,

제2 비트 라인;

상기 제2 비트 라인에 결합되는 메모리 셀의 제2 열; 및

제2 데이터 라인에 결합되는 제2 입력과, 상기 제2 데이터 라인의 값에 따른 래치 값을 제공하는 제2 출력을 갖는 제2 래치 회로를 더 포함하고, 상기 제2 출력은 상기 제2 비트 라인에 접속되는 메모리 장치.

### 청구항 33.

메모리 장치로서,

복수 개 쌍의 상보형 비트 라인-상기 복수의 쌍 각각이 메모리 셀의 열에 결합됨-; 및

복수의 래치 회로-상기 래치 회로 각각은 데이터 라인에 결합되는 입력과, 상기 데이터 라인의 값에 따른 상보형 래치 값을 제공하는 제1 출력과 제2 출력을 갖음-;

를 포함하고, 상기 복수의 래치 각각에서, 상기 제1 출력은 상기 복수의 쌍 중 어느 한 쌍의 제1 비트 라인에 결합되어 상기 제1 비트 라인의 값이 메모리 장치의 동작 동안 상기 제1 출력에 의해 연속해서 결정되고, 상기 제2 출력은 상기 쌍의 제2 비트 라인에 결합되어 상기 제2 비트 라인의 값이 메모리 장치의 동작 동안 상기 제2 출력에 의해 연속해서 결정되는

메모리 장치.

### 청구항 34.

메모리 장치로서,

비트 라인;

상기 비트 라인에 결합되는 메모리 셀의 열; 및

데이터 라인에 결합되는 입력과, 상기 데이터 라인의 값에 따른 래치 값을 제공하는 출력을 갖는 래치 회로를 포함하고, 상기 출력은 비트 라인에 결합되어, 상기 비트 라인의 값은, 상기 출력에서의 값이 메모리 장치의 동작 동안 변동되는 경우에 한해, 변동하는 메모리 장치.

명세서

#### 기술분야

본 발명은 접적 회로에 관한 것으로, 보다 구체적으로는 메모리 장치에 관한 것이다.

#### 배경기술

멀티-포트(multi-port) 메모리 장치에서, 메모리 판독 및 메모리 기입 동작은 이런 동작을 수행하는데 필요한 시간에 상당히 영향을 받는다. 기입 동작 동안, 입력 데이터 단언 시간(assertion time)은 메모리 장치의 속성에 연관된 디코드 지역에 따라 변할 수 있다. 예를 들어, 입력 데이터의 종속성에 연관된 불확실성에 의해, 단언 시간이 불충분할 경우, 오류(false) 데이터가 메모리에 기입됨으로 인한 프로세서 고장이 일어날 수 있다.

## 발명의 상세한 설명

따라서, 메모리 성능을 개선시키는 메모리 설계가 필요하다.

### 실시예

일 실시예에서, 메모리 장치는 비트 라인, 메모리 셀의 열, 래치 회로를 포함한다. 메모리 셀의 열은 비트 라인에 결합된다. 래치 회로는 데이터 라인에 결합된 입력과, 그 데이터 라인의 값에 따른 래치 값을 제공하는 출력을 갖는다. 그 출력은 비트 라인에 결합되어, 비트 라인의 값이 메모리 장치의 동작 동안 출력에 의해 연속해서 결정된다.

일 실시예는 메모리 장치를 동작시키는 방법에 관한 것이다. 메모리 셀의 열에 있는 메모리 셀들에 대해 복수의 판독 및 복수의 기입을 수행한다. 비트 라인의 값이 메모리 셀의 열에 결합되어, 메모리 장치의 동작 동안 이 비트 라인의 값이 래치 출력에 의해 연속해서 제어된다. 일 실시예에서, 래치 출력의 값은 제1 상태에서 제2 상태로의 클럭 신호의 상태의 변경에 의해 결정되는 소정의 시점에서 래치 입력의 값에 응답하여 변경될 수 있다. 일 실시예에서, 메모리 셀의 열에 있는 한 메모리 셀에 소정 값이 기입될 수 있으며, 그 기입은 예컨대, 비트라인의 상태를 변경시키기를 포함한다. 일 실시예에서, 메모리 셀의 열에 있는 한 메모리 셀에 소정 값이 기입될 수 있으며, 그 기입은 예컨대, 기입 라인의 상태를 비기입 상태에서 기입 상태로 변경시키기를 포함한다.

일 실시예에서, 메모리 장치는 비트 라인, 메모리 셀의 열, 및 래치 회로를 포함한다. 메모리 셀의 열은 비트 라인에 결합된다. 래치 회로는 데이터 라인에 결합되는 입력과, 그 데이터 라인의 값에 따른 래치 값을 제공하는 출력을 갖는다. 그 출력은 비트 라인에 접속된다.

일 실시예에서, 메모리 장치는 복수 개 쌍의 상보형 비트 라인과 복수의 래치 회로를 포함한다. 복수 개 쌍의 상보형 비트 라인 각 쌍은 메모리 셀의 열에 결합된다. 래치 회로 각각은 데이터 라인에 결합된 입력과, 그 데이터 라인의 값에 따른 상보형 래치 값을 제공하는 제1 출력과 제2 출력을 포함한다. 복수의 래치 회로의 각각의 래치에서, 제1 출력은 한 쌍의 복수 개 비트 라인 중 제1 비트 라인에 결합되어 제1 비트 라인의 값이 메모리 장치의 동작 동안 제1 출력에 의해 연속해서 결정되고, 제2 출력은 그 쌍의 중 제2 비트 라인에 결합되어 제2 비트 라인의 값이 메모리 장치의 동작 동안 제2 출력에 의해 연속해서 결정된다.

일 실시예에서, 메모리 장치는 비트 라인, 메모리 셀의 열, 및 래치 회로를 포함한다. 메모리 셀의 열은 비트 라인에 결합된다. 래치 회로는 데이터 라인에 결합되는 입력과, 그 데이터 라인의 값에 따른 래치 값을 제공하는 출력을 갖는다. 그 출력은 비트 라인에 결합되어, 비트 라인의 값은, 출력에서의 값이 메모리 장치의 동작 동안 변하는 경우에 한해, 변동한다.

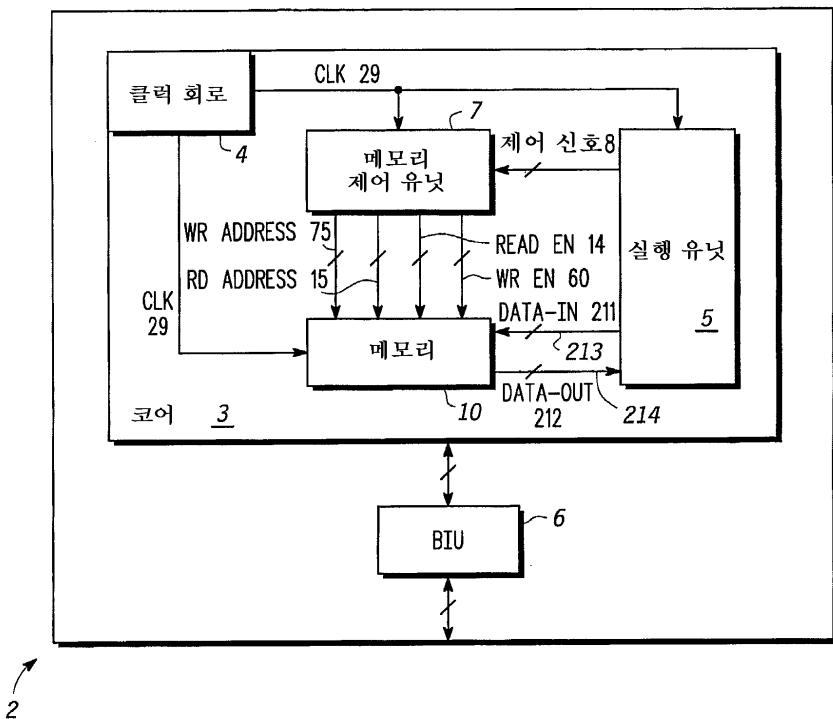

도 1은 본 발명의 일 실시예에 따른 집적 회로(2)를 예시한다. 집적 회로(2)는 코어(3) 및 버스 인터페이스 유닛(6:BIU)을 포함한다. 코어(3)는 클럭 회로(4), 실행 유닛(5), 메모리 제어 유닛(7), 및 메모리(10)를 포함한다. 일 실시예에서, 코어(3)는 예컨대, 프로세서 코어일 수 있고, 메모리(10)는 예컨대, 멀티-포트 레지스터 파일을 특징으로 하고 있다.

일 실시예에서, 집적 회로(2)의 정상 동작 동안, 메모리(10)는 실행 유닛(5)으로부터 메모리 제어 유닛(7)에 제공된 제어 신호(8)에 기초하여 기입 액세스 또는 판독 액세스된다. 제어 신호(8)는 메모리 판독 동작 또는 메모리 기입 동작을 개시하는데 이용될 수 있다. 실행 유닛(5)은 예컨대, 메모리(10)에 데이터를 저장하거나 메모리(10)로부터 데이터를 판독하기 위한 제어 신호(8)를 발행하는 중앙 처리 장치(CPU), 또는 디지털 신호 처리 장치일 수 있다. 클럭 신호(29)(CLK 29)는, 일 실시예에서, 데이터가 메모리(10)에 기입되거나, 메모리(10)로부터 판독될 수 있는 시점을 결정하기 위한 타이밍 메커니즘으로서 이용되며, 클럭 회로(4)로부터 메모리 제어 유닛(7)에, 실행 유닛(5)에, 및 메모리(10)에 제공된다. 메모리 제어 유닛(7)은 클럭 신호(29)와, 실행 유닛(5)으로부터의 제어 신호(8)를 수신하고, 실행 유닛(5)이 판독 동작 또는 기입 동작을 요청하는지 여부에 기초하여, 기입 인에이블 신호(60)(WR EN 60) 또는 판독 인에이블 신호(14)(READ EN 14)를 단언한다(assert).

판독 동작 동안, RD ADDRESS 15, 및 READ EN 14가 메모리 제어 유닛(7)으로부터 메모리(10)에 제공된다. 메모리(10)는 READ EN 14를 수신하고, RD ADDRESS 15에 의해 지정된 메모리 주소 위치를 인에이블시킨다. RD ADDRESS 15에 의해 지정된 메모리 주소 위치에 있는 데이터가 메모리(10)로부터 판독되고 데이터 라인들(214)을 통해 DATA-OUT (212)으로서 실행 유닛(5)에 제공된다.

기입 동작 동안, WR ADDRESS 75, 및 WR EN 60은 메모리 제어 유닛(7)으로부터 메모리(10)에 제공된다. 메모리(10)는 WR EN 60을 수신하고, 기입 동작을 위해 WR ADDRESS 75에 의해 지정된 메모리 주소 위치를 인에이블시킨다. 실행 유닛(5)으로부터의 데이터(DATA-IN 211)가 데이터 라인들(213)을 통해 메모리(10)에 제공되어, WR ADDRESS 75에 의해 지정된 메모리(10)의 메모리 주소 위치에 기입된다. 집적 회로(2)는 다른 실시예에서 다른 구성을 가질 수 있다.

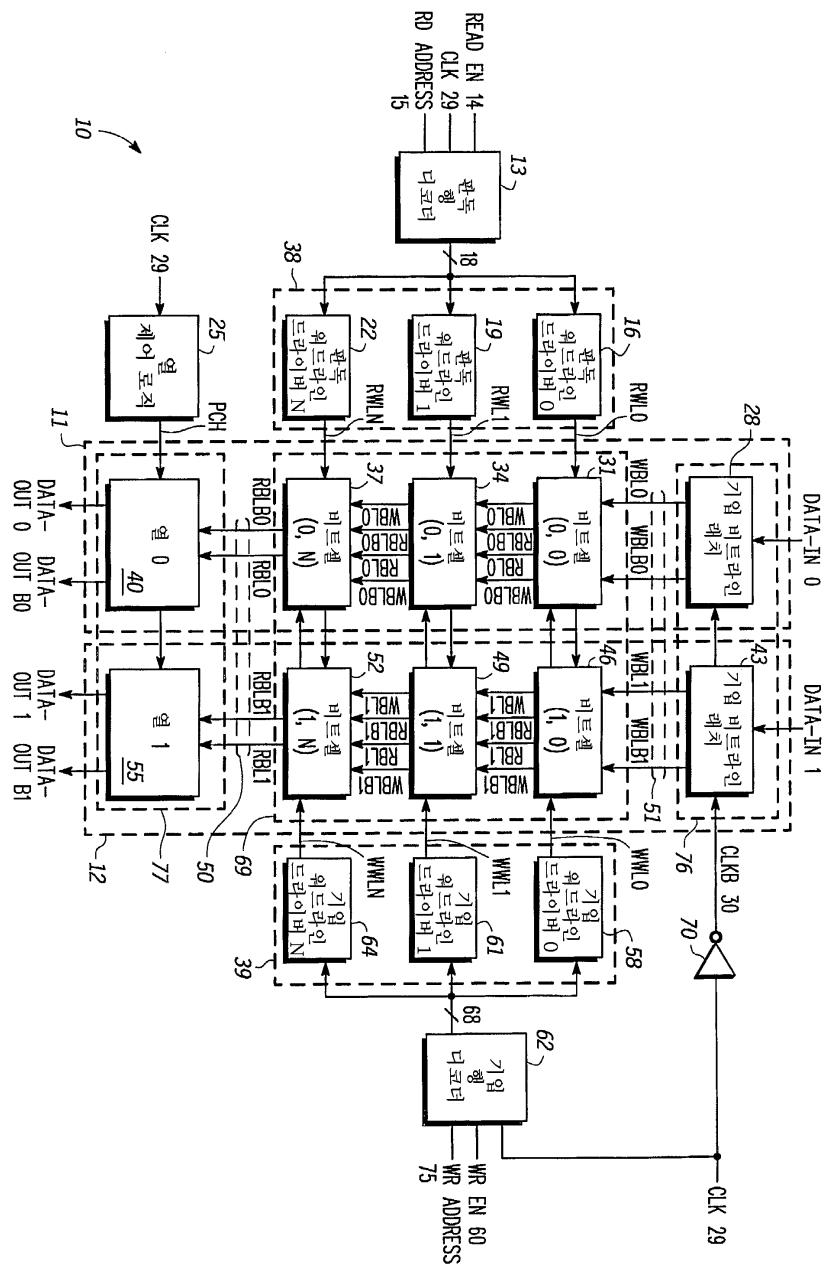

도 2는 본 발명의 일 실시예에 따른 메모리(10)를 예시한다. 메모리(10)는 판독 행(row) 디코더(13), 판독 워드 라인 드라이버들(38), 기입 워드 라인 드라이버들(39), 기입 비트라인 래치들(76), 열 제어 로직(25), 열 어레이 회로(11), 열 어레이 회로(12), 인버터(70), 기입 행 디코더(62), 및 열 회로(77)를 포함한다. 판독 워드 라인 드라이버들(38)은 판독 워드 라인 드라이버(16), 판독 워드 라인 드라이버(19), 및 판독 워드 라인 드라이버(22)를 포함한다. 기입 워드 라인 드라이버들(39)은 기입 워드 라인 드라이버(58), 기입 워드 라인 드라이버(61), 및 기입 워드 라인 드라이버(64)를 포함한다. 열 어레이 회로(11)는 기입 비트라인 래치(28), 비트셀(메모리 셀)(31), 비트셀(34), 비트셀(37), 및 열 회로(40)를 포함한다. 열 어레이 회로(12)는 기입 비트라인 래치(43), 비트셀(46), 비트셀(49), 비트셀(52), 및 열 회로(55)를 포함한다. 설명을 쉽게 하기 위해, 비트셀(46), 비트셀(49), 비트셀(52), 비트셀(31), 비트셀(34), 및 비트셀(37)은 비트셀 어레이(69)로서 지칭될 수 있고, 기입 워드 라인 드라이버들(39), 및 기입 행 디코더(62)는 워드 라인 생성 회로로서 지칭될 수 있다. 도시된 일 실시예에서, 비트셀(31)은 비트셀(46)과 동일한 행에 위치된다.

일 실시예에서, 판독 동작 동안, 메모리(10)의 판독 행 디코더(13)는 메모리 제어 유닛(7)(도 1)으로부터 판독 인에이블 신호(14)와 판독 주소(15)를 수신하고, 클럭 회로(4)(도 1)로부터 클럭 신호(29)를 수신한다. 판독 행 디코더(13)는 판독 주소(15)를 디코딩하고, 비트셀 어레이(69) 중 판독 액세스를 위해 인에이블할 비트셀의 행을 판정한다. 비트셀 어레이(69)는 비트셀의 행 또는 열을 하나 이상 포함할 수 있다. 판독 행 디코더(13)는, 판독 워드 라인 드라이버들(38) 중 디코딩된 행 주소에 대응하는 적어도 하나의 판독 워드 라인 드라이버에 행 인에이블 신호(18)를 출력한다. 판독 워드 라인 드라이버들(38) 중 디코딩된 행 주소에 대응하는 판독 워드 라인 드라이버는 비트셀의 선택된 행 또는 행들에 제공되는 판독 워드 라인 신호를 단언한다. 예시된 실시예에서, 판독 워드 라인 드라이버(16), 판독 워드 라인 드라이버(19), 또는 판독 워드 라인 드라이버(22)는 판독 워드 라인 신호들 RWL0, RWL1, RWLN 중 어느 하나를 각각 단언한다. 비트셀의 선택된 행은 판독 비트 라인 신호들(RBL0 및 RBLB0)을 열 회로(40)에 대한 입력으로서, 판독 비트 라인 신호들(RBL1 및 RBLB1)을 열 회로(55)에 대한 입력으로서 제공한다. 비트셀 어레이(69)가 비트셀의 다수 행을 갖는 경우에, 판독 비트 라인 신호들(RBL0 및 RBLB0)과 판독 비트 라인 신호들(RBL1 및 RBLB1)은, 열 회로(40)와 열 회로(55)에 대한 입력으로서 제공되기 이전에, 비트셀의 추가 행 또는 행들에 제공될 수 있다. 마찬가지로, 비트셀 어레이(69)가 비트셀의 다수 열을 갖는 경우에, 판독 워드 라인 신호들(RWL0, RWL1, 및 RWLN)이 비트셀의 추가 열 또는 열들에 제공될 수 있다.

열 회로(40) 및 열 회로(55)는 판독 비트 라인 신호들(RBL0 및 RBLB0) 및 판독 비트 라인 신호들(RBL1 및 RBLB1)을 각각 수신한다. 열 회로(40)는 판독 비트 라인 신호들(RBL0 및 RBLB0)을 이용하여 출력 데이터(DATA-OUT 0 및 DATA-OUT B0)를 생성하고, 열 회로(55)는 판독 비트 라인 신호들을 이용하여 출력 데이터(DATA-OUT 1 및 DATA-OUT B1)를 생성한다. 그 출력 데이터는 도 1에 도시된 실행 유닛(5) 등의 실행 유닛에 추가 처리를 위해 제공될 수 있다. 메모리(10)의 다른 실시예가 도 2에 도시된 것들에만 한정되지 않고, 단일 열 어레이 회로(11) 또는 복수의 열 어레이 회로를 포함할 수 있다.

일 실시예에서, 기입 동작 동안, 기입 행 디코더(62)는 기입 인에이블 신호(60), 클럭 신호(29), 및 기입 주소(75)를 수신한다. 기입 행 디코더(62)는 기입 주소(75)를 디코딩하고, 기입 액세스를 위해 비트셀의 어느 행을 인에이블할지를 판정한다. 기입 행 디코더(62)는 기입 워드 라인 드라이버들(39) 중 디코딩된 행 주소에 대응하는 적어도 하나의 기입 워드 라인 드라이버에 행 인에이블 신호(68)를 출력한다. 기입 워드 라인 드라이버들(39) 중 디코딩된 행 주소에 대응하는 기입 워드 라인 드라이버는 비트셀의 선택된 행 또는 행들에 제공되는 기입 워드 라인 신호를 단언한다. 예시된 실시예에서, 기입 워드 라인 드라이버(58), 기입 워드 라인 드라이버(61), 및 기입 워드 라인 드라이버(64)는 기입 워드 드라이버들(39)을 비트셀 어레이(69)에 결합시키는 기입 워드 라인들을 통해, 기입 워드 라인 신호들 WWL0, WWL1, 및 WWLN 중 어느 하나를 각각 단언한다. 일 실시예에서, 기입 워드 라인 신호는 예컨대, 클럭 신호(29)의 상태 변경에 의해 결정된 소정의 시점에서, 비기입 상태에서 기입 상태로 변동할 수 있다. 예컨대, 실행 유닛(5)(도시 생략)으로부터 제공될 수 있는 입력 데이터(DATA-IN 0 및 DATA-IN 1)가 비트라인 래치들(76)(기입 비트라인 래치(28) 및 기입 비트라인 래치(43))에 전달된다. 기입 비트라인 래치들(76)은 입력 데이터와, 인버터(70)에 의해 반전된 반전 클럭 신호(29)(CLKB 30)를 수신한다. 기입 비트라인

래치들(76)은, CLKB 30을 이용하여 입력 데이터를 기입 비트라인 래치들(76)을 비트셀 어레이(69)에 결합시키는 기입 비트라인으로의 기입 비트라인 신호들 WBL0, WBL1과 기입 비트 라인 신호의 상보형 신호 WBLB0, WBLB1들로 구동한다. 기입 비트라인 신호들은 비트셀 어레이(69) 중 비트셀의 선택된 행에 기입된다. 비트셀 어레이(69)가 비트셀의 다수 행을 갖는 경우, 기입 비트 라인 신호들(WBL0 및 WBLB0), 및 기입 비트 라인 신호들(WBL1 및 WBLB1)은 비트셀의 추가 행 또는 행들에 제공될 수 있다. 마찬가지로, 비트셀 어레이(69)가 비트셀의 다수 열을 갖는 경우, 기입 워드 라인 신호들(WWL0, WWL1, 및 WWLN)이 비트셀의 추가 열 또는 열들에 제공될 수 있다. 메모리(10)는 다른 실시예에서 다른 구성을 가질 수 있다.

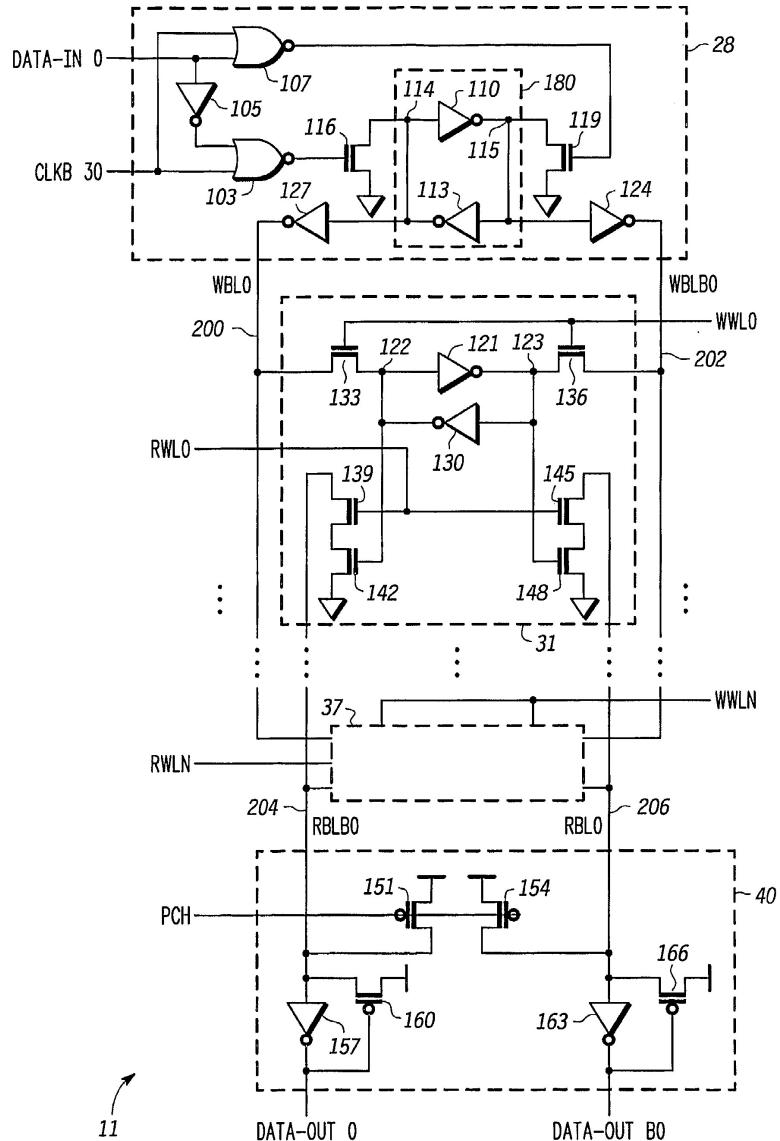

도 3은 열 어레이 회로(11)의 일 실시예를 예시한다. 예시된 바와 같이, 열 어레이 회로(11)는 기입 비트라인 래치(28), 비트셀(31), 비트셀(37), 및 열 회로(40)를 포함한다. 기입 비트라인 래치(28)는, 비트셀(31)과 비트셀(37)에 기입 비트라인(200)과 기입 비트라인(202)을 통해 결합된다. 일 실시예에서, 기입 비트라인(202)은 기입 비트라인(200)의 상보형 비트라인이다. 비트셀(31) 및 비트셀(37)은 팬독 비트 라인(204)과 팬독 비트라인(206)을 통해 열 회로(40)에 결합된다. 다른 실시예에서, 추가 비트셀이 열 어레이 회로(11)에 추가될 수 있다. 도 3에는 비트셀(34)이 도시되어 있지 않다.

기입 동작 동안, 열 어레이 회로(11)의 기입 비트라인 래치(28)는 인버터(70)로부터의 클럭바 신호(30)(CLKB 30)와, 실행 유닛(5)(도 1)으로부터의 입력 데이터(DATA-IN 0)를 수신한다. NOR 게이트(107)는 DATA-IN 0과 클럭바 신호(30)를 NOR시키고, 그 출력을 NMOS 트랜지스터(119)에 제공한다. NOR 게이트(103)는 클럭바 신호(30)와 입력 데이터 DATA-IN 0의 반전 신호를 NOR시키고, 그 출력을 NMOS 트랜지스터(116)에 제공한다.

일반적으로, DATA-IN 0과 클럭바 신호(30)는 단언 또는 단언해제(deassertion) 값의 범위를 취할 수 있다. 일 실시예에서, 클럭바 신호(30)는 하이(high)이고, NOR 게이트(107)의 출력과 NOR 게이트(103)의 출력은 로우(low)이다. 결과적으로, NMOS 트랜지스터(119)와 NMOS 트랜지스터(116)는 턴오프되고, 인버터(113)와 교차 결합되는(cross coupled) 인버터(100)를 포함하는 래치(180)가, 이전에 래치(180)에 기입되었던 데이터 값을, 만약에 그 값이 존재한다면, 능동적으로 이를 유지한다.

일 실시예에서, 클럭바 신호(30)가 로우이고 DATA-IN 0이 하이일 때, NOR 게이트(107)의 출력은 로우이고, NOR 게이트(103)의 출력은 하이이다. 결과적으로, NMOS 트랜지스터(116)는 턴오프되고, NMOS 트랜지스터(116)는 턴온되고, 노드(114)는 로우로 풀링되고, 인버터(110)의 출력은 하이이다. 인버터(110)의 출력이 인버터(113) 및 인버터(124)에 의해 반전된다. 인버터(113)는 인버터(110)의 출력을 반전시키고, 그 출력을 인버터(127)에 제공한다. 기입 비트라인 신호 WBL0으로서 기입 비트라인(200)상으로 전이되는 인버터(127)의 출력은 하이이다. 기입 비트라인 바 신호 WBLB0으로서 기입 비트라인(202)상으로 전이되는 인버터(124)의 출력은 로우이다. 기입 비트라인 신호 WBL0, 및 기입 비트라인 신호 WBLB0 모두가 비트셀(31)에 제공된다.

일 실시예에서, 클럭바 신호(30)가 로우이고 DATA-IN 0이 로우일 때, NOR 게이트(107)의 출력은 하이이고, NOR 게이트(103)의 출력은 로우이다. 결과적으로, NMOS 트랜지스터(119)는 턴온되고, NMOS 트랜지스터(116)는 턴오프된다. NMOS 트랜지스터(119)가 온되기 때문에, 노드(115)는 로우로 풀링되고, 인버터(113)의 출력은 하이이다. 기입 비트라인 바 신호 WBLB0으로서 기입 비트라인(202)상으로 전이되는 인버터(124)의 출력은 하이이고, 기입 비트라인 신호 WBL0으로서 기입 비트라인(204)상으로 전이되는 인버터(127)의 출력은 로우이다. 따라서, 기입 비트라인 래치(28)의 출력에서의 기입 비트라인 신호 WBL0과 기입 비트라인 바 신호 WBLB0의 값들은, 클럭바 신호(30)의 상태 변경에 의해 결정되는 소정의 시점에서 입력 데이터 라인에서의 DATA-IN 0의 값에 따른 값들을 변동시킨다. 마찬가지로, 기입 비트라인(200)과 기입 비트라인(202)의 기입 기입 비트라인 신호 WBL0과 기입 비트라인 바 신호 WBLB0의 값들은, 클럭 신호의 상태 변경에 의해 결정되는 소정의 시점에서 입력 데이터 라인에서의 값 DATA-IN 0에 대응하여 변동할 수 있다. 기입 비트라인 신호 WBL0과 기입 비트라인 바 신호 WBLB0은 비트셀(31)에 제공된다.

비트셀(31)은 인버터(127)의 출력으로부터의 기입 비트라인 신호 WBL0을 NMOS 트랜지스터(133)의 전류 단자에서 수신하고, 인버터(124)의 출력으로부터의 기입 비트라인 바 신호 WBLB0을 NMOS 트랜지스터(136)의 전류 단자에서 수신한다. NMOS 트랜지스터(133)와 NMOS 트랜지스터(136)의 제어 단자에 제공되는 기입 워드 라인 신호 WWL0이 하이일 경우, NMOS 트랜지스터(133)와 NMOS 트랜지스터(136)는 턴온된다. 노드(122)가 기입 비트 라인(200)상으로 전이되었던 값까지 풀링되고, 노드(123)가 기입 비트라인(202)상으로 전이되었던 값까지 풀링된다. 따라서, WWL0이 하이일 때, 비트셀(31)은 입력 데이터 DATA-IN 0을 저장하고, 이는 열 어레이 회로(11)에 입력으로서 제공된다. WWL0이 로우일 때, NMOS 트랜지스터(133)와 NMOS 트랜지스터(136)는 턴오프되고, 기입 비트라인(200)과 기입 비트라인(202)으로부터 기입된 데이터 값을 인버터(121)와 인버터(130)를 이용하여 저장한다.

판독 동작 동안, 판독 워드 라인(208)상의 판독 워드 라인 신호 RWL0은 하이이고, NMOS 트랜지스터(139)와 NMOS 트랜지스터(145)는 턴온된다. 노드(122)에 저장된 값의 반전 값과 노드(123)에 저장된 값의 반전 값이 NMOS 트랜지스터(142)와 NMOS 트랜지스터(148)를 각각 이용하여, 판독 비트라인 바 신호 RBLB0로서 판독 비트라인((204)에와, 판독 비트라인 신호 RBL0로서 판독 비트라인(206)에 전달된다. 열 회로(40)에 대한 입력으로서 제공되는 프리차지 신호(PCH;precharge signal)가 하이일 때, PMOS 트랜지스터(151)와 PMOS 트랜지스터(154)가 턴오프되고, 판독 비트라인(204)상의 판독 비트라인 신호 RBLB0의 값이 인버터(157)에 제공되고, 판독 비트라인(206)상의 판독 비트라인 신호 RBL0의 값이 인버터(163)에 제공된다. 인버터(157)의 출력이 출력 데이터 DATA-OUT 0로서 실행 유닛(도시 생략)에 와, PMOS 트랜지스터(160)의 제어 단자에 제공된다. 마찬가지로, 인버터(163)의 출력이 출력 데이터(DATA-OUT B0)로서 실행 유닛(도시 생략)에 와, PMOS 트랜지스터(166)의 제어 단자에 제공된다. 판독 비트라인 신호 RBL0과 판독 비트라인 신호 RBLB0의 값들에 따라, PMOS 트랜지스터(160) 또는 PMOS 트랜지스터(166) 중 어느 하나가 턴오프될 수 있다. 다른 실시예에서, 기입 비트라인 래치(28), 비트셀(31), 비트셀(37), 및/또는 열 회로(40)가 다른 구성을 가질 수 있다. 도시된 실시예에서, DATA0-IN 0 신호는 싱글-엔디드(single-ended) 신호이지만, 다른 실시예에서, 이것은 차동(differential) 신호 등의 다른 형태의 신호일 수 있다.

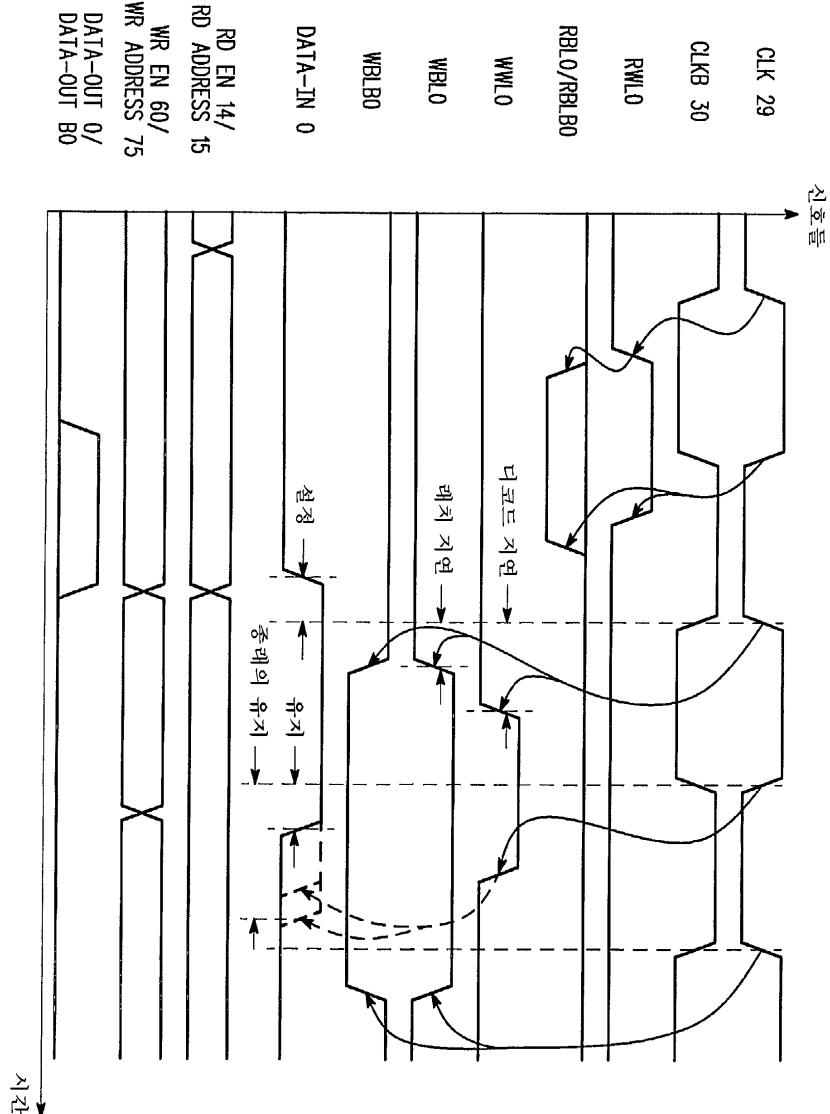

도 4는 본 발명의 일 실시예에 따른 비트셀(31)에 대해 기입과 판독을 실현하기 위한 다양한 신호를 나타내는 타이밍도를 예시한다. 일 실시예에 도시된 바와 같이, 판독 동작 동안, 판독 인에이블 신호(14)와 클럭 신호(29)가 하이일 때, 판독 워드 라인 신호 RWL0은 하이이다. 판독 워드 라인 신호 RWL0이 예컨대, 판독 행 디코더(13)와 판독 워드 라인 드라이버들(38)에 의해 야기된 지연 이후에 하이로 어설트될 수 있다. 일단 판독 워드 라인 신호 RWL0이 하이인 경우, 판독 비트라인 신호 RBL0이 로우이고 판독 비트라인 바 신호 RBLB0이 하이이거나, 판독 비트라인 신호 RBL0이 하이이고 판독 비트라인 바 신호 RBLB0이 로우이다. 판독 비트라인 신호 RBL0 또는 판독 비트라인 바 신호 RBLB0이 로우일 때, DATA-OUT 0 또는 DATA-OUT B0가 하이이다. 클럭 신호(29)가 로우일 때, 판독 워드 라인 신호 RWL0이 로우이고, 판독 비트 라인 신호 RBL0과 판독 비트라인 바 신호 RBLB0이 하이이고, DATA-OUT 0과 DATA-OUT B0이 로우이다.

도 4에 예시된 바와 같이, DATA-IN 0 및 클럭 신호(29)가 하이(클럭바 신호(30)가 로우임)일 때, 기입 비트라인 신호 WBL0이 하이이고 기입 비트라인 바 신호 WBLB0이 로우이다. 기입 동작 동안, 기입 인에이블 신호(60)와 클럭 신호(29)가 하이일 때, 기입 워드 라인 신호 WWL0이 하이이다. 기입 워드 라인 신호 WWL0이 예컨대, 기입 행 디코더(62)와 기입 워드 라인 드라이버들(39)에 의해 야기된 지연 이후에 어설트될 수 있다. 클럭 신호(29)가 로우일 때, 기입 워드 라인 신호 WWL0이 로우이다.

도 4의 타이밍도로부터 인식할 수 있는 바와 같이, 디코드 지연은 기입 워드 라인 신호 WWL0의 단언에 대한 클럭 신호(29)의 단언과 연관된다. 래치 지연은 기입 비트라인 신호 WBL0의 단언에 대한 클럭 신호(29)의 단언과 연관된다. 일 실시예에서, 기입 동작 동안, 기입 비트라인 신호 WBL0은 기입 워드 라인 신호 WWL0이 로우일 때까지 하이 값으로 유지된다. 마찬가지로, 기입 비트라인 바 신호 WBLB0은 기입 워드 라인 신호 WWL0이 로우일 때까지 로우 값으로 유지된다. DATA-IN 0은 클럭 신호(29)가 로우일 때까지 하이로 유지된다. 예시된 바와 같이, DATA-IN 0 단언 시점은 기입 워드 라인 신호 WWL0과 연관된 디코드 지연에 따른다.

상기 명세서에서는, 본 발명을 특정한 실시예들을 참조하여 기술하였다. 하지만, 당업자는 다양한 수정 및 변경이 상술된 본 발명의 범위 내에서 하기의 클레임에서 행해질 수 있다. 따라서, 명세서 및 도면은 제한적인 의미보다는 예시적인 의미로 간주되며, 모든 이런 수정들은 본 발명의 범위 내에 포함되는 것으로 의도된다.

이점, 다른 장점, 및 문제에 관한 해법이 특정한 실시예에 관련하여 상기 기술되었다. 하지만, 다른 이점, 장점, 또는 해법을 생성하거나 보다 두드러지게 할 수 있는 이점, 장점, 문제에 관한 해법과 임의 요소(들)이 모든 청구항 또는 임의 청구항에서 결정적인 요구되는, 또는 필수적인 특징 또는 요소로서 구성되는 것은 아니다.

## 도면의 간단한 설명

본 발명을 일례를 들어 기술하고 있으며, 동일 부호가 동일 소자를 나타내는 첨부한 도면에만 한정되지 않는다.

도 1은 본 발명의 일 실시예에 따른 집적 회로의 블록도.

도 2는 본 발명의 일 실시예에 따른 메모리를 예시.

도 3은 본 발명의 일 실시예에 따른 열 어레이 회로를 예시.

도 4는 본 발명의 일 실시예에 따른 다양한 신호들을 나타내는 타이밍도.

당업자는 도면의 소자들이 간략하고 명료하게 예시되어 있지만, 반드시 일정한 비율로 도시되어 있지 않음을 인식할 것이다. 예를 들어, 도면의 소자들 중 일부의 치수를 본 발명의 일 실시예의 이해를 증진시키기 위해 다른 소자에 비해 확대할 수 있다.

도면

도면1

도면2

도면3

도면4