(12) 发明专利

(10) 授权公告号 CN 111312736 B

(45) 授权公告日 2023.10.24

(21) 申请号 202010118252.X

(74) 专利代理机构 北京信慧永光知识产权代理

(22) 申请日 2015.02.20

有限责任公司 11290

(65) 同一申请的已公布的文献号

专利代理人 曹正建 陈桂香

申请公布号 CN 111312736 A

(51) Int.CI.

(43) 申请公布日 2020.06.19

H01L 27/146 (2006.01)

(30) 优先权数据

H04N 25/778 (2023.01)

2014-038584 2014.02.28 JP

(56) 对比文件

(62) 分案原申请数据

CN 102034835 A, 2011.04.27

201580009596.4 2015.02.20

CN 102956660 A, 2013.03.06

(73) 专利权人 索尼公司

CN 101290943 A, 2008.10.22

地址 日本国东京都港区港南1-7-1

审查员 张虹

(72) 发明人 加藤菜菜子 若野寿史 大竹悠介

权利要求书1页 说明书15页 附图13页

(54) 发明名称

成像装置和电子设备

(57) 摘要

提供了一个或者多个像素共享结构的成像装置和电子设备。所述共享像素结构包括多个光电转换装置或者光电二极管。所述共享像素结构中的每个光电二极管都位于矩形区域内。所述共享像素结构还包括多个共享晶体管。所述共享像素结构中的所述共享晶体管位于与所述共享像素结构的所述光电转换装置相邻。所述矩形区域可以具有两条短边和两条长边，所述共享晶体管位于沿着所述长边中的一条长边。另外，可以沿着与所述矩形区域的所述长边平行的方向延伸一个或者多个所述晶体管的长度。

1.一种光检测装置,所述光检测装置包括:

第一单元,所述第一单元包括第一多个光电二极管和第一多个转移晶体管;

第二单元,所述第二单元包括第二多个光电二极管和第二多个转移晶体管,

其中,所述第二单元与所述第一单元相邻;

第三单元,所述第三单元包括第一重置晶体管、第一放大晶体管、第一选择晶体管、以及第一晶体管,其中,在平面图中,所述第三单元位于所述第一单元和所述第二单元之间,所述第一单元的所述第一多个光电二极管共用所述第一放大晶体管,并且所述第一放大晶体管和所述第一重置晶体管具有共同的源极漏极区域;以及

第四单元,所述第四单元包括第二重置晶体管、第二放大晶体管、第二选择晶体管、以及第二晶体管,其中,在所述平面图中,所述第二单元的所述第二多个光电二极管共享所述第二放大晶体管,并且所述第二单元位于所述第三单元和所述第四单元之间。

2.根据权利要求1所述的光检测装置,其中,所述第一单元的所述第一多个光电二极管位于第一矩形区域内,所述第一矩形区域具有两条短边和两条长边,并且所述第三单元与所述第一矩形区域的所述长边中的一条长边相邻。

3.根据权利要求2所述的光检测装置,其中,所述第三单元的至少一个晶体管沿着与所述第一矩形区域的所述长边平行的线布置。

4.根据权利要求2所述的光检测装置,其中,所述第三单元的所述第一放大晶体管的沿着与所述第一矩形区域的所述长边平行的方向的长度比所述第三单元的其它晶体管的至少一者的沿着与所述第一矩形区域的所述长边平行的方向的长度长。

5.根据权利要求2所述的光检测装置,其中,所述第一单元的所述第一多个光电二极管是光电转换元件组,所述光电转换元件组包括位于所述第一矩形区域内的共享单元,以及其中,所述第三单元包括相对于所述光电转换元件组大体对称的像素晶体管组。

6.根据权利要求1所述的光检测装置,其中,所述第一晶体管为虚设晶体管。

7.根据权利要求2所述的光检测装置,其中,所述第三单元的所述第一选择晶体管的沿着与所述第一矩形区域的所述长边平行的方向的长度比所述第三单元的其它晶体管的至少一者的沿着与所述第一矩形区域的所述长边平行的方向的长度长。

8.根据权利要求2所述的光检测装置,其中,所述第一单元的所述第一多个光电二极管包括至少八个光电二极管,并且所述第一多个光电二极管中的每个光电二极管位于所述第一矩形区域内。

9.根据权利要求2所述的光检测装置,其中,所述第三单元中的至少一个晶体管位于所述第一矩形区域的外部。

10.一种电子设备,所述电子设备包括:

根据权利要求1至9中任一项所述的光检测装置。

## 成像装置和电子设备

[0001] 本申请是申请日2015年2月20日,申请号201580009596.4,发明名称为“成像装置和电子设备”的分案申请。

### 技术领域

[0002] 本公开涉及一种成像装置和一种电子设备,具体涉及可以改善随机噪声的固态成像装置和电子设备。

[0003] 相关申请的交叉引用

[0004] 本申请要求2014年2月28日提交的日本优先权专利申请JP 2014-038584的权益,其内容以引用的方式全部并入本文。

### 背景技术

[0005] 在专利文献1中,公开了一种背照式CMOS图像传感器,该图像传感器采用像素共享布局措施来应对PRNU(光子响应非均匀性;灵敏度非均匀性)。像素晶体管(以下称为像素Tr.)分为两组,并且Tr.对称布置。

[0006] 该技术旨在通过相对于光电二极管(以下称为PD)对称布置放大Tr.(以下称为AMP)、选择Tr.(以下称为SEL)、和重置Tr.(以下称为RST)使对来自两组之间的晶体管(Tr.)的多晶硅的背面侧的入射光的反射量和吸收量相等。

[0007] [引用列表]

[0008] [专利文献]

[0009] PTL1:JP 2013-62789A

### 发明内容

[0010] 技术问题

[0011] 然而,根据专利文献1中公开的技术,由于像素Tr.分为两组,因此不能加长晶体管中的每个晶体管的L-长度。因此,可能会加重RN(随机噪声)问题。

[0012] 更具体地,在将AMP和SEL布置在第一组并且将两个Tr.布置在第二组的情况下,第一组需要3个源极-漏极,第二组需要3个源极-漏极,即,总共需要六个源极-漏极。此时,由于光刻线宽度受到限制,并且处理多晶硅和接触孔、确保隔离击穿电压等受到限制,加长Tr.的L-长度受到限制。具体地,在微型化的情况下,这种状态的影响相当严重,并且,由于AMP的L-长度较短,所以RN容限可能会恶化。

[0013] 鉴于上述情况,实现了本公开,并且,通过本公开,可以改善随机噪声容限。

[0014] 问题的解决方案

[0015] 根据本技术的实施例的固态成像装置包括:包括矩形形状的共享单元的光电转换元件组和在光电转换元件组的长边方向上布置成一组的像素晶体管组,其中,像素晶体管组中的各个像素晶体管布置为相对于光电转换元件组大体对称。

[0016] 像素晶体管组中包括虚设晶体管。

- [0017] 像素晶体管组布置在从光电转换元件组的矩形形状的共享单元偏移开的位置处。

- [0018] 像素晶体管组中包括的放大晶体管的L-长度比像素晶体管组中包括的其它晶体管的L-长度长。

- [0019] 像素晶体管组中包括的放大晶体管的L-长度是光电转换元件组的间距的0.6倍至1.4倍。

- [0020] 像素晶体管组中包括的选择晶体管的L-长度比像素晶体管组中包括的其它晶体管的L-长度长。

- [0021] 阵接触进一步设置在光电转换元件组和紧挨着光电转换元件组定位的另一光电转换元件组之间。

- [0022] 阵接触进一步设置在像素晶体管组和紧挨着像素晶体管组定位的另一像素晶体管组之间。

- [0023] 固态成像装置是背照式的。

- [0024] 根据本公开的实施例的电子设备包括：

- [0025] 固态成像装置，该固态成像装置包括具有矩形形状的共享单元的光电转换元件组和在光电转换元件组的长边方向上布置成一组的像素晶体管组，其中，像素晶体管组中的各个像素晶体管布置为相对于光电转换元件组大体对称；

- [0026] 信号处理电路，该信号处理电路用于处理从固态成像装置输出的输出信号；以及

- [0027] 光学系统，该光学系统用于以入射光照射固态成像装置。

- [0028] 像素晶体管组中包括虚设晶体管。

- [0029] 像素晶体管组布置在从光电转换元件组的矩形形状的共享单元偏移开的位置处。

- [0030] 像素晶体管组中包括的放大晶体管的L-长度比像素晶体管组中包括的其它晶体管的L-长度长。

- [0031] 像素晶体管组中包括的放大晶体管的L-长度是光电转换元件组的间距的0.6倍至1.4倍。

- [0032] 阵接触进一步设置在光电转换元件组和紧挨着光电转换元件组定位的另一光电转换元件组之间。

- [0033] 阵接触进一步设置在像素晶体管组和紧挨着像素晶体管组定位的另一像素晶体管组之间。

- [0034] 固态成像装置是背照式的。

- [0035] 根据本技术的实施例，光电转换元件组包括矩形形状的共享单元和在光电转换元件组的长边方向上布置成一组的像素晶体管组。进一步地，像素晶体管组的各个像素晶体管布置为相对于光电转换元件组大体对称。

- [0036] 本发明的有益效果

- [0037] 根据本技术的实施例，形成晶体管的多晶硅可以相对于二极管大体对称地布置。进一步地，根据本技术的实施例，可以减少随机噪声。

- [0038] 注意，在本发明中列举的效果只是示例。本技术的效果不限于本说明书所列举的效果，并且可以包括另外的效果。

## 附图说明

- [0039] 图1是图示了采用了本技术的固态成像装置的示例示意性配置的框图；

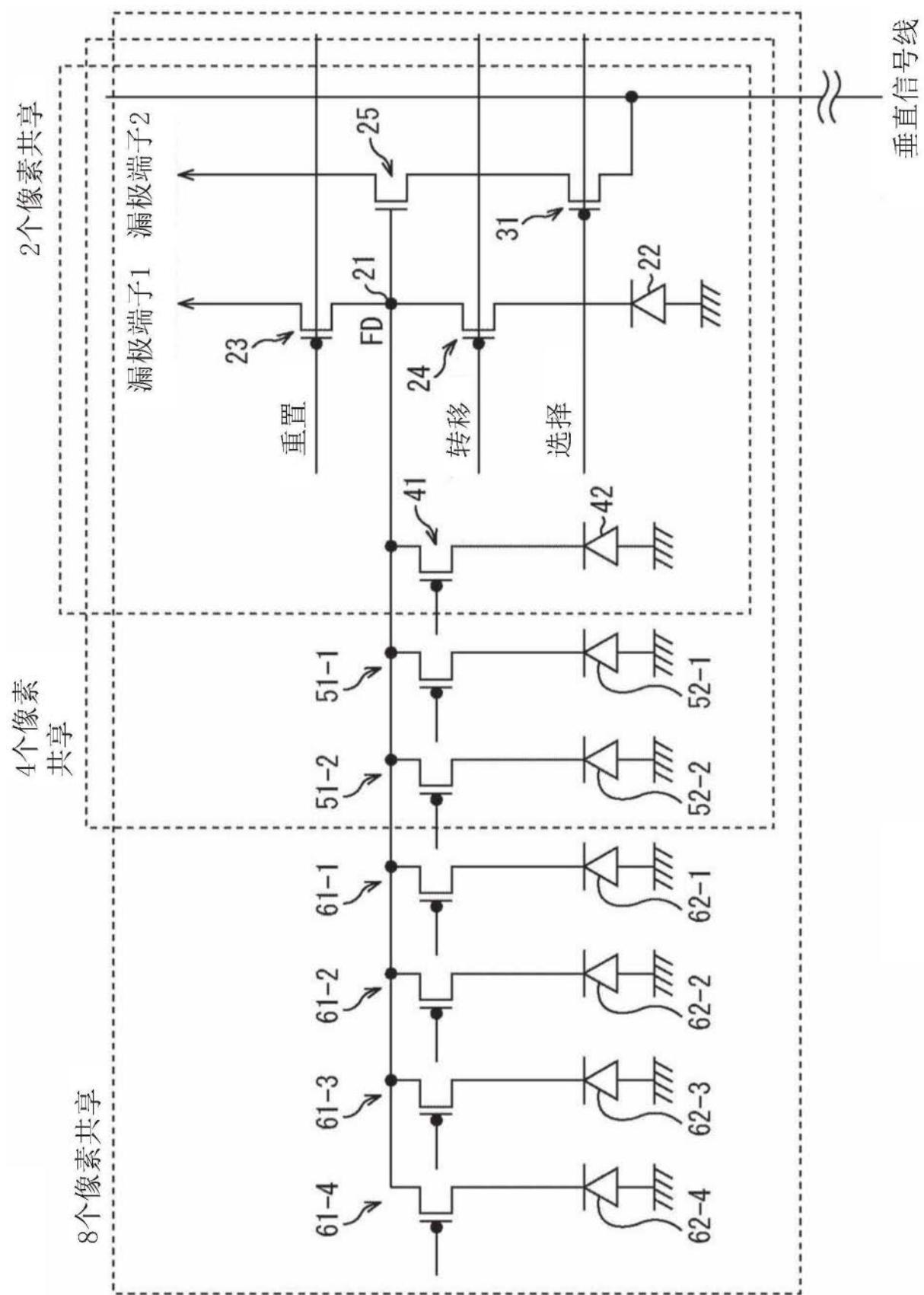

- [0040] 图2是图示了包括三个晶体管的像素的示例性配置的电路图；

- [0041] 图3是图示了包括四个晶体管的像素的示例性配置的电路图；

- [0042] 图4是图示了具有共享像素结构的像素的示例性配置的电路图；

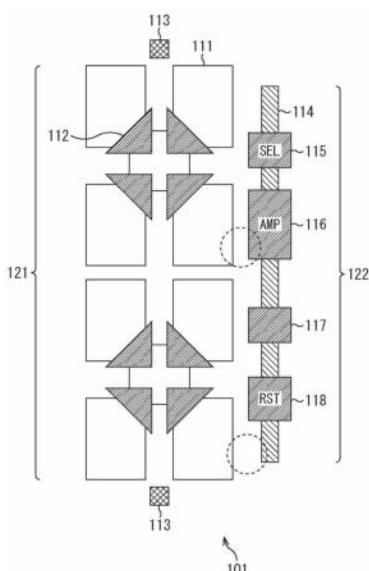

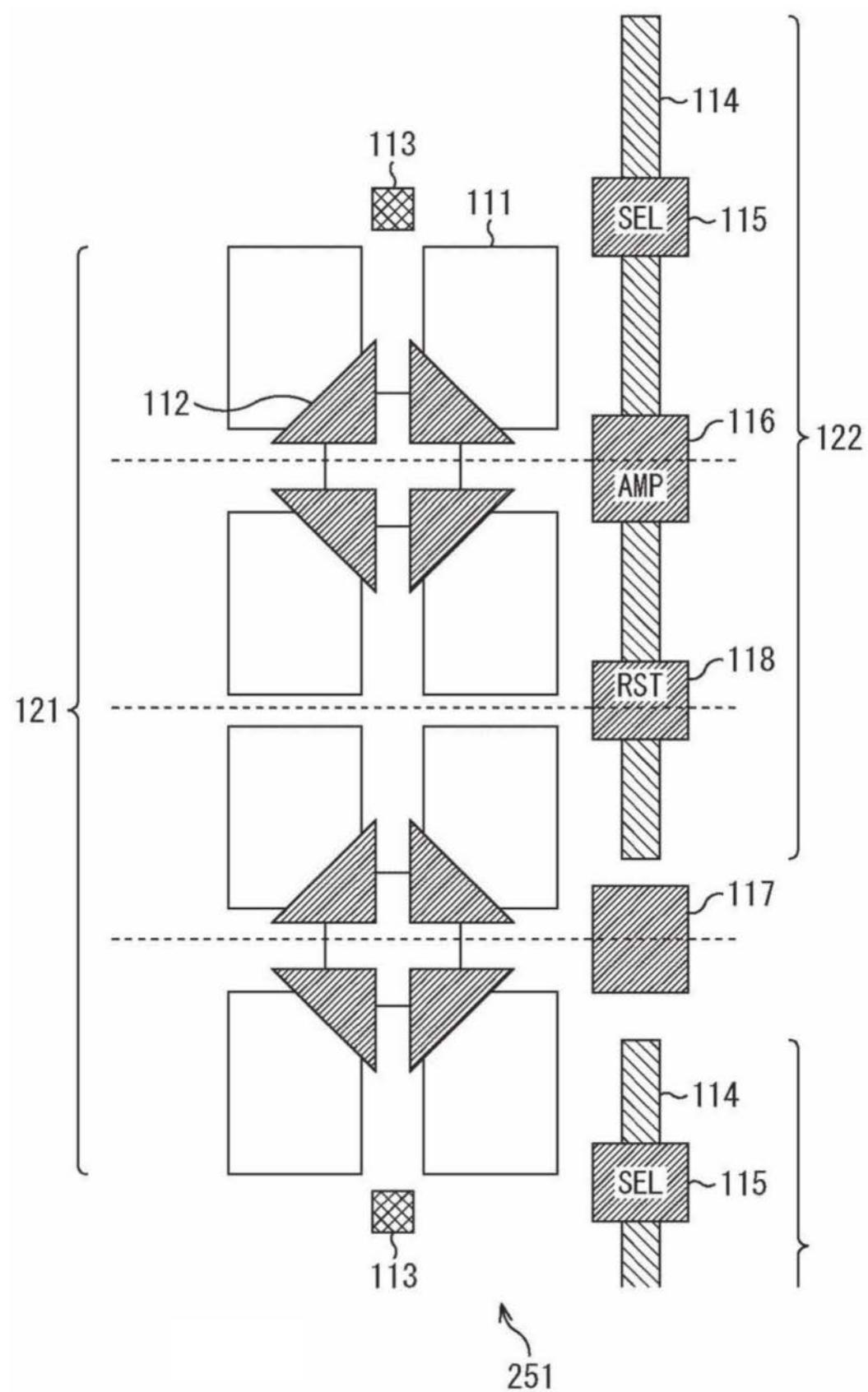

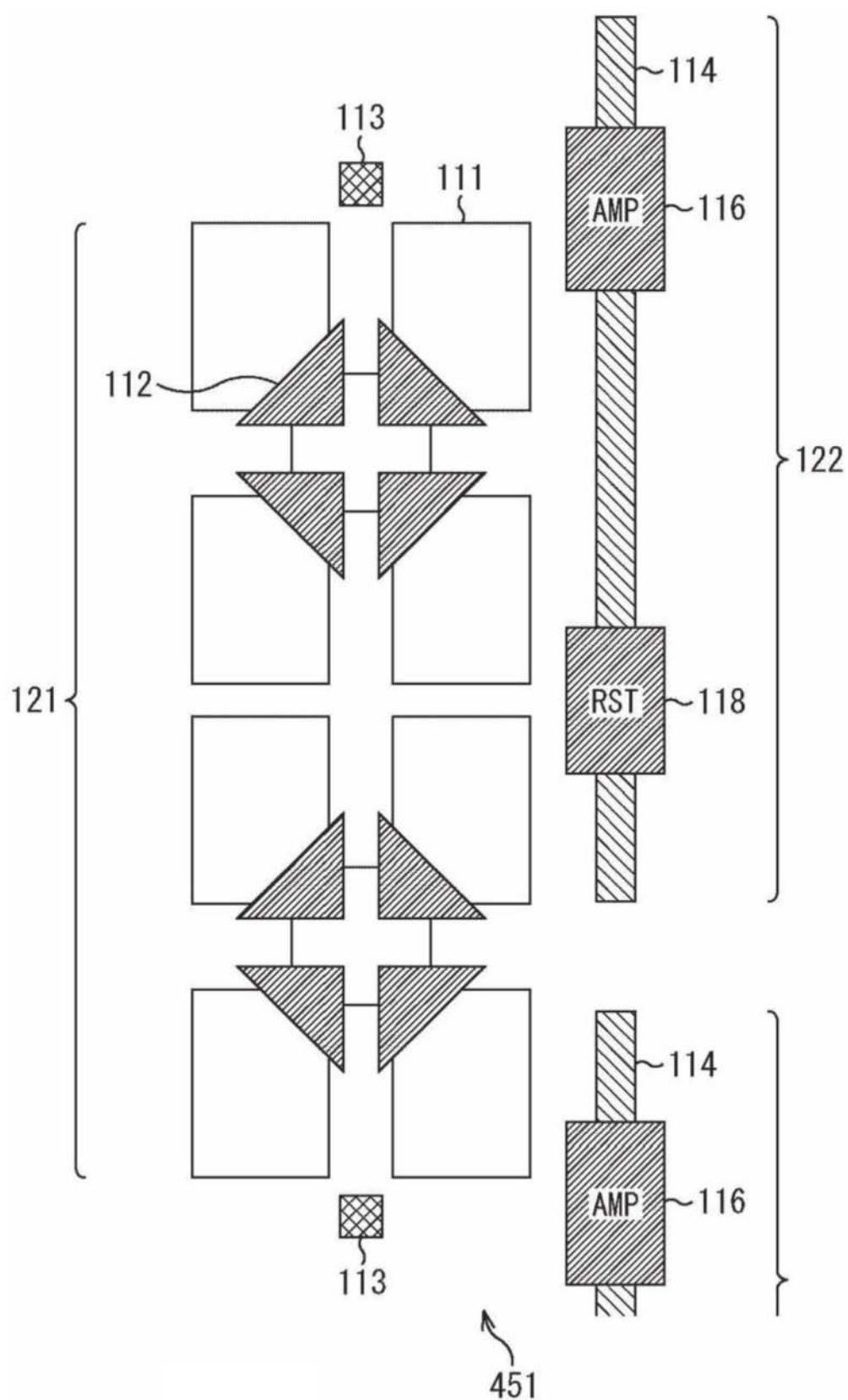

- [0043] 图5是图示了采用了本技术的固态成像装置的第一示例性配置的图；

- [0044] 图6是图示了晶体管的不同布置示例的图；

- [0045] 图7是图示了晶体管的另一不同布置示例的图；

- [0046] 图8是图示了晶体管的又一不同布置示例的图；

- [0047] 图9是图示了采用了本技术的固态成像装置的第二示例性配置的图；

- [0048] 图10是图示了采用了本技术的固态成像装置的第三示例性配置的图；

- [0049] 图11是图示了采用了本技术的固态成像装置的第四示例性配置的图；

- [0050] 图12是图示了晶体管的另一不同布置示例的图；以及

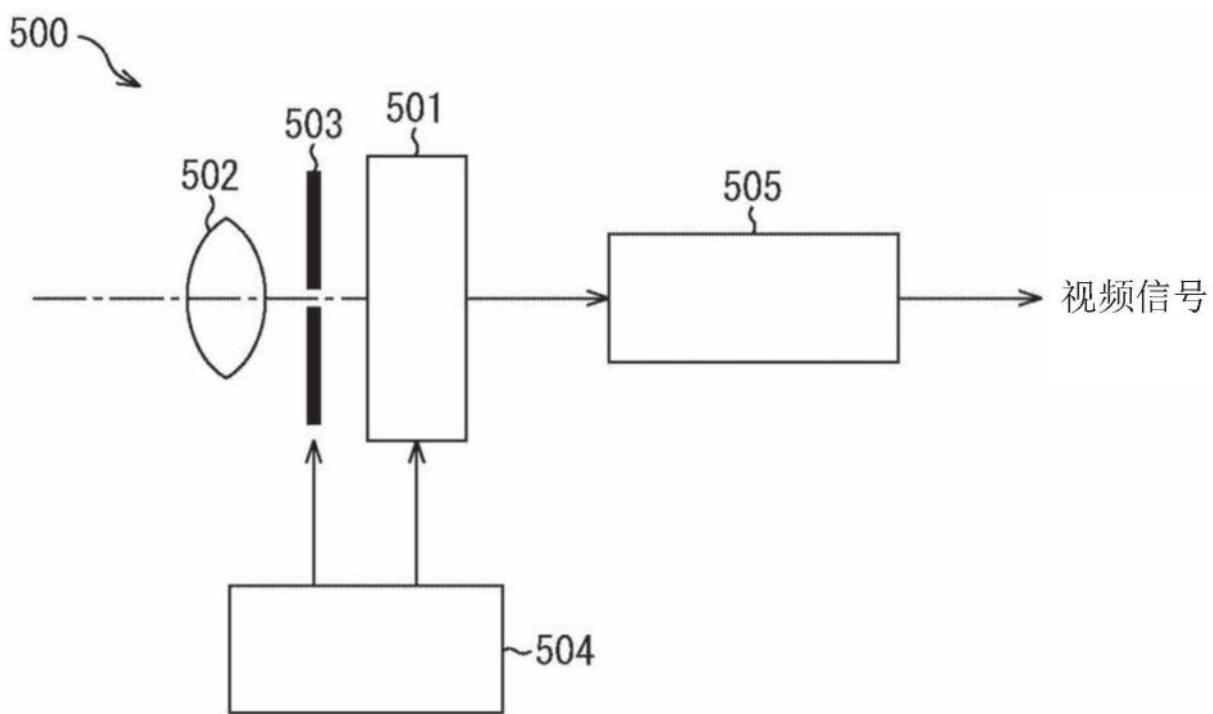

- [0051] 图13是图示了采用了本技术的电子设备的示例性配置的框图。

## 具体实施方式

[0052] 下面将对实施本公开的实施例(以下称为实施例)进行详细描述。注意，将按照以下顺序进行说明。

- [0053] 0、固态成像装置的示意性配置的示例

- [0054] 1、第一实施例(4个Tr.类型和8个像素共享的示例)

- [0055] 2、第二实施例(4个晶体管类型和2个像素共享的示例)

- [0056] 3、第三实施例(4个晶体管类型和16个像素共享的示例)

- [0057] 4、第四实施例(3个晶体管类型和8个像素共享的示例)

- [0058] 5、第五实施例(电子设备的示例)

- [0059] 0、固态成像装置的示意性配置的示例

- [0060] <固态成像装置的示意性配置的示例>

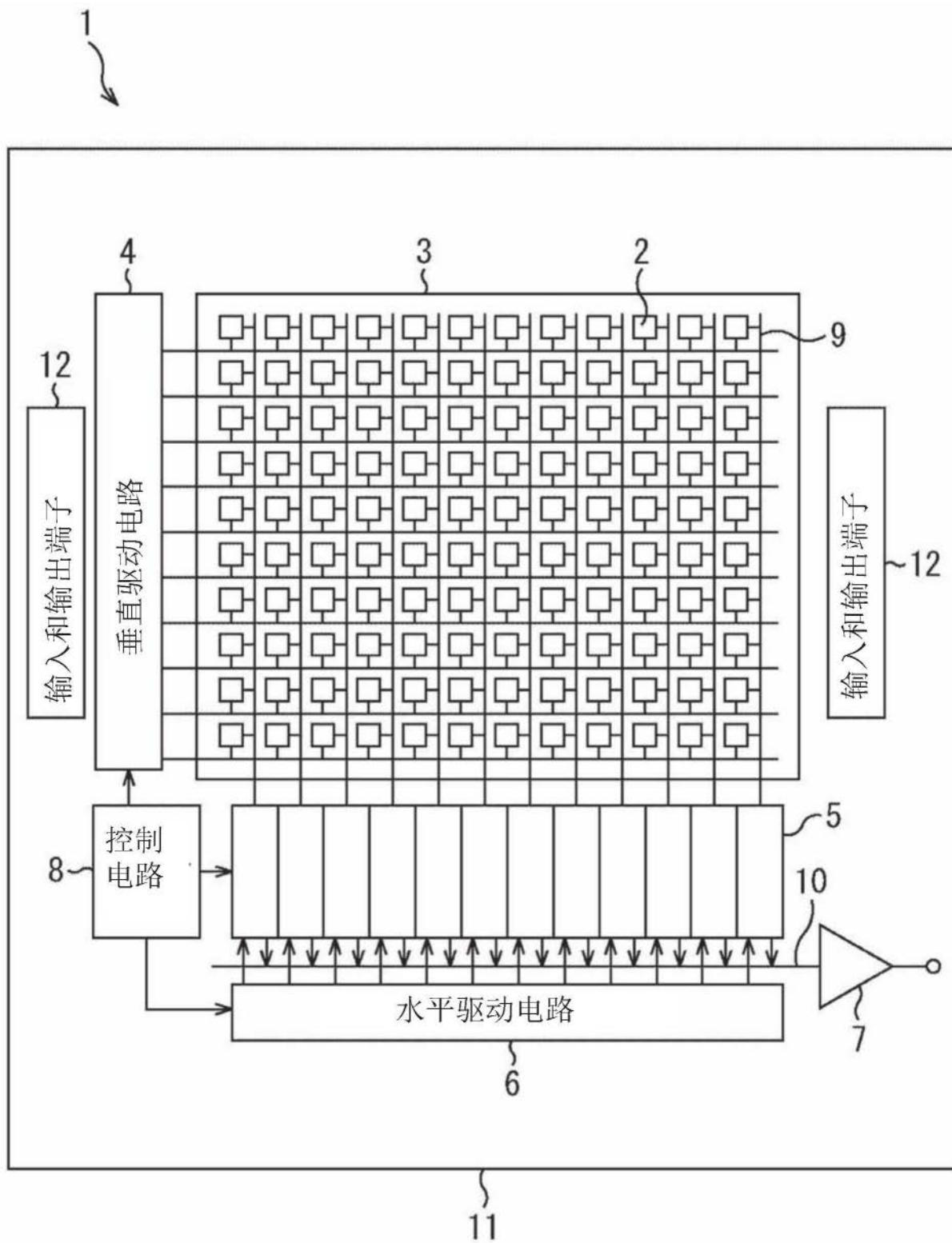

[0061] 图1是图示了应用于本技术的各个实施例的CMOS(互补金属氧化物半导体)固态成像装置的示意性配置的示例的图。

[0062] 如图1所示，固态成像装置(装置芯片)1包括像素区域(所谓的成像区域)3和外围电路。在像素区域3中，包括多个光电转换元件的像素2规则地二维排列在半导体衬底11上(例如，硅衬底)。

[0063] 像素2包括光电转换元件(例如，光电二极管)和多个像素晶体管(所谓的MOS晶体管)。该多个像素晶体管可以包括三个晶体管，诸如，转移晶体管、重置晶体管和放大晶体管，并且，通过进一步地添加选择晶体管，也可以包括四个晶体管。每个像素2(单位像素)的等效电路与通常采用的等效电路相同，因此此处将不再赘述。

[0064] 同样，像素2可以具有像素共享结构。该像素共享结构包括多个光电二极管、多个转移晶体管、一个待共享的浮置扩散、待共享的其它像素晶体管中的一个像素晶体管。光电二极管是光电转换元件。

[0065] 外围电路包括垂直驱动电路4、列信号处理电路5、水平驱动电路6、输出电路7和控

制电路8。

[0066] 控制电路8接收数据以执行针对输入时钟、操作模式等的命令，并且输出数据，诸如，固态成像装置1的内部信息。更具体地，控制电路8生成垂直同步信号和水平同步信号，并且还基于主时钟生成时钟信号和控制垂直驱动电路4、列信号处理电路5和水平驱动电路6的操作的控制信号。进一步地，控制电路8向垂直驱动电路4、列信号处理电路5和水平驱动电路6输入这些信号。

[0067] 垂直驱动电路4包括，例如，移位寄存器，并且选择像素驱动线，为选择的像素驱动线提供脉冲以驱动像素2，并且以行为单位驱动像素2。更具体地，垂直驱动电路4以行为单位在垂直方向上顺序地选择性地扫描像素区域3中的各个像素2，并且，基于根据各个像素2中的光电转换元件中的光接收量所生成的信号电荷，经由垂直信号线9，为列信号处理电路5提供像素信号。

[0068] 列信号处理电路5针对，例如，每列像素2而布置，并且以像素列为单位执行信号处理，诸如，针对从一行的像素2中输出的信号，执行消除噪声。更具体地，列信号处理电路5执行信号处理，诸如，CDS(相关双采样)、信号放大、A/D(模数转换)等，以便消除像素2独有的固定模式噪声。水平选择开关(未图示)在连接至水平信号线10的途中，设置在列信号处理电路5的输出级处。

[0069] 水平驱动电路6包括，例如，移位寄存器，并且顺序地输出水平扫描脉冲，从而按顺序选择列信号处理电路5中的每个列信号处理电路，并且使列信号处理电路5中的每个列信号处理电路向水平信号线10输出像素信号。

[0070] 输出电路7经由水平信号线10对从列信号处理电路5中的每个列信号处理电路顺序地提供的信号执行信号处理，并且输出信号。输出电路7可以仅仅执行，例如，缓冲，或者可以执行黑色电平调整、列变化校正和各种数字信号处理等。

[0071] 设置输入和输出端子12，以与部件或者装置交换信号。

[0072] <像素的示例性配置>

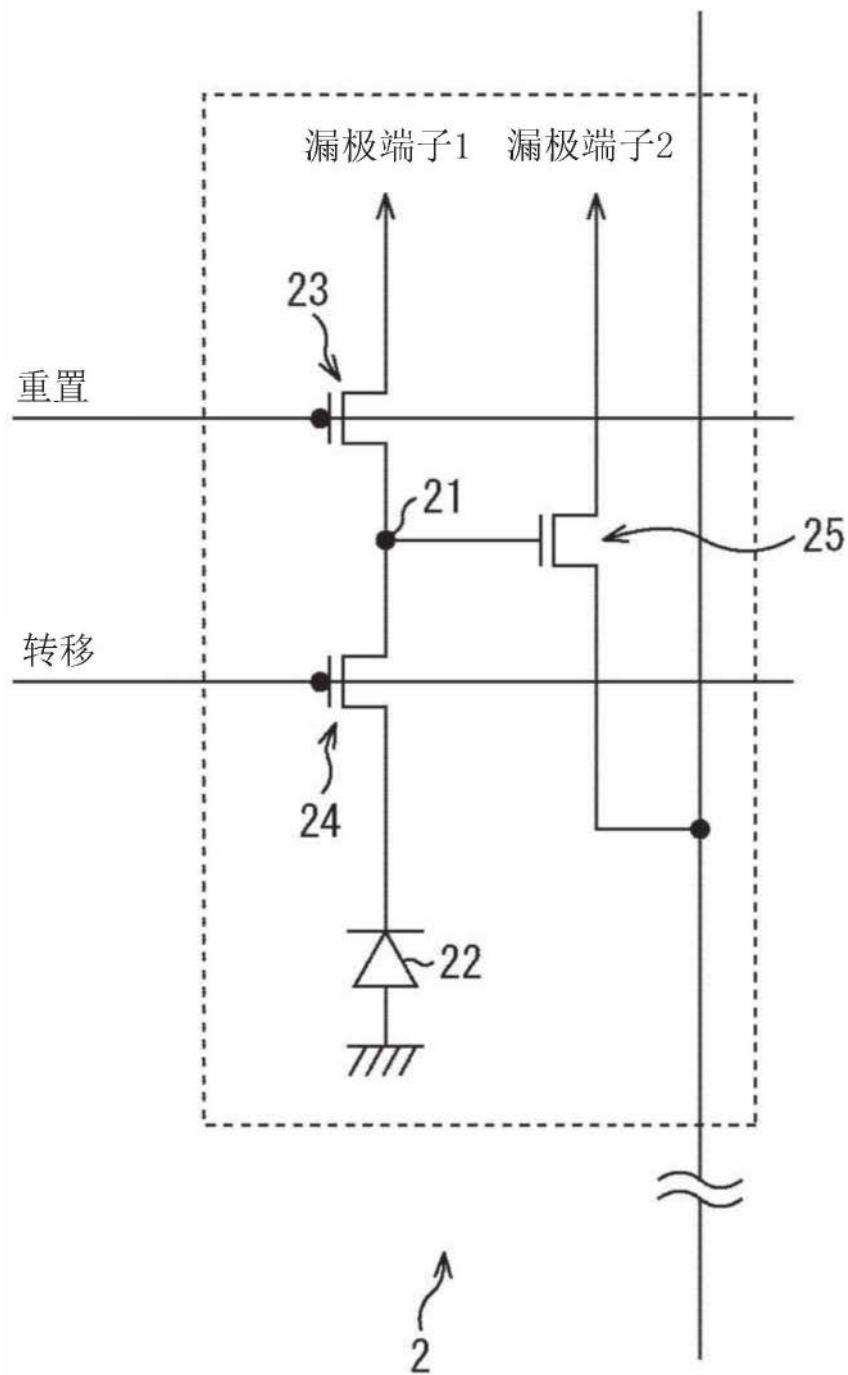

[0073] 图2是图示了全局快门式CMOS(互补金属氧化物半导体)传感器中的像素的示例性配置的图。在图2中的示例中，图示了包括三个晶体管(以下称为Tr.)的示例性配置(以下也称为3个Tr.类型)。

[0074] 图2中的像素2包括一个待共享的浮置扩散(以下称为FD)21、光电二极管22、和在单位像素内部的三个共享或者像素晶体管。三个共享Tr.分别是重置Tr.23、转移Tr.24和放大Tr.25。

[0075] 光电二极管22具有连接至负侧电源(例如，地面)的阳极电极，并且根据光量，将接收到的光光电转化为光电荷(在这种情况下是光电子)。光电二极管22具有经由转移Tr.24电连接至放大Tr.25的栅极电极的阴极电极。电连接至放大Tr.25和转移Tr.24的栅极电极的节点是FD 21。

[0076] 转移Tr.24连接在光电二极管22的阴极电极与FD 21之间。经由未图示的传输线，通过转移Tr.24的栅极电极，接收具有有效高电平(例如，VDD电平)(以下称为高有效)的转换脉冲 $\varphi_{TRF}$ 。通过接收转换脉冲 $\varphi_{TRF}$ ，转换Tr.24变为导通状态，并且将在光电二极管22处已经光电转换的光电荷传输至FD 21。

[0077] 重置Tr.23具有分别连接至像素电源(VDD)的漏极电极和连接至FD 21的源极电

极。在将信号电荷从光电二极管22转移至FD 21之前,经由重置线(未图示),通过重置Tr.23的栅极电极,接收高有效重置脉冲 $\varphi RST$ 。通过接收重置脉冲 $\varphi RST$ ,将重置Tr.23置于导通状态,并且将FD 21的电荷放电至像素电源VDD,从而重置FD 21。

[0078] 放大Tr.25具有连接至FD 21的栅极电极、连接至像素电源VDD的漏极电极、和连接至垂直信号线的源极电极。同样,放大Tr.25输出已经通过重置Tr.23重置的FD 21的电位,作为重置信号(重置电平)Vreset。进一步地,放大Tr.25进一步输出在通过转移晶体管24转移信号电荷之后的FD 21的电位,作为光累积信号(信号电平)Vsig。

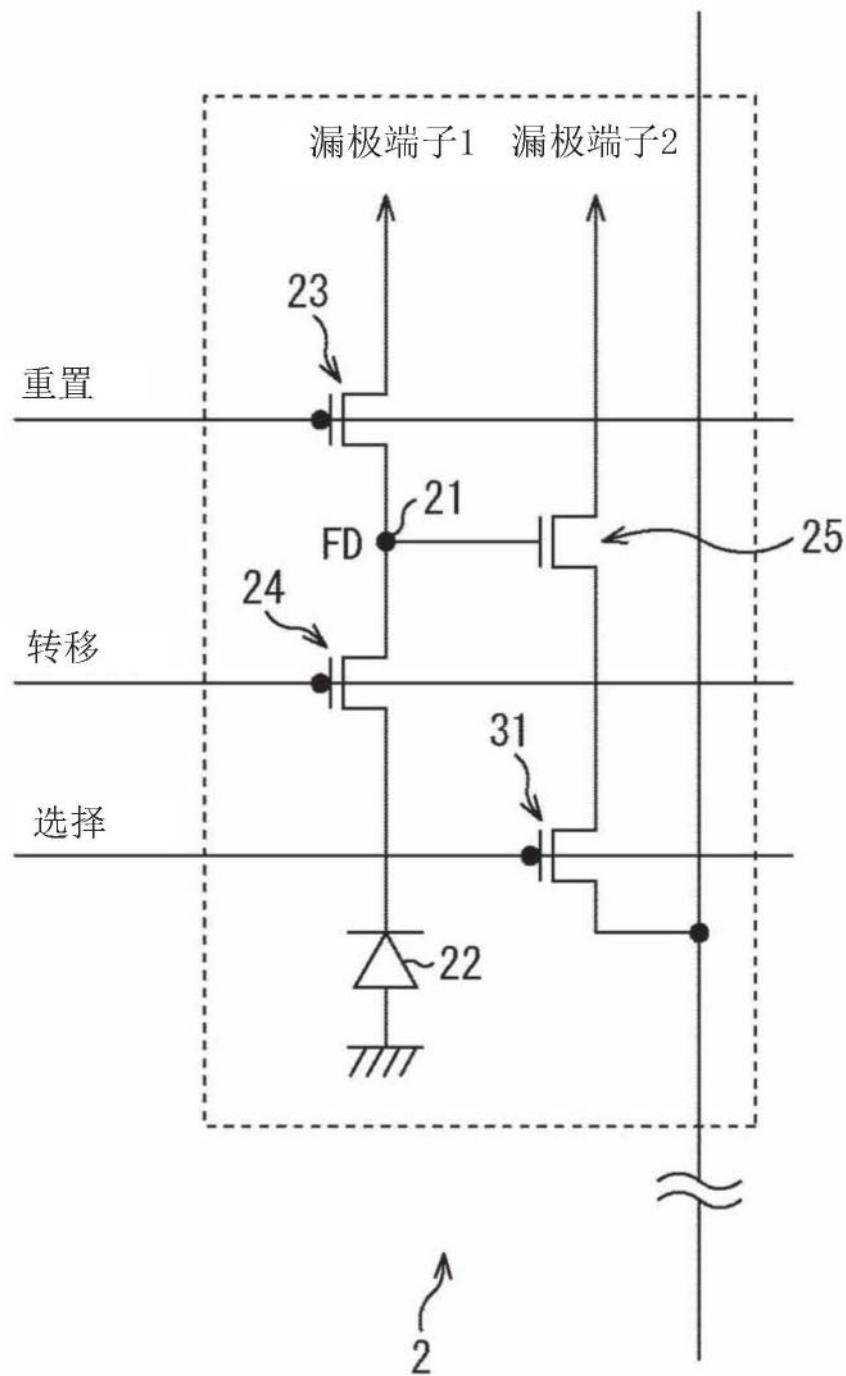

[0079] 图3是图示了全局快门式CMOS(互补金属氧化物半导体)传感器中的像素的不同配置的图。在图3中的示例中,图示了四个Tr.的示例性配置(以下称为4个晶体管式)。

[0080] 图3中的像素2与图2中的像素2的相似之处在于像素2都包括FD 21、光电晶体管22、重置Tr.23、转换Tr.24和放大晶体管25。图3中的像素2与添加有选择晶体管31的图2中的像素2不同。

[0081] 例如,选择Tr.31具有分别连接至放大Tr.25的源极电极的漏极电极、和连接至垂直信号线的源极电极。经由未图示的选择线,通过选择Tr.31的栅极电极,接收高有效选择脉冲 $\varphi SEL$ 。通过接收选择脉冲 $\varphi SEL$ ,选择Tr.31进入导通状态,并且将单位像素置于选择状态,从而中继从放大Tr.25输出到垂直信号线的信号。

[0082] 同时,选择Tr.31也可以连接在像素电源VDD与放大Tr.25的漏极之间。

[0083] <像素共享的示例性结构>

[0084] 图4是图示了由两个像素、四个像素和八个像素共享一套Tr.的结构的图。该套Tr.包括上面参照图2所描述的重置Tr.23和放大Tr.25。或者参照图3所描述的重置Tr.23、放大Tr.25和选择Tr.31。在这两种情况下,每个光电二极管需要一个转移Tr.,并且该转移Tr.直接连接至每个光电二极管。

[0085] 更具体地,在2个像素共享的情况下,将一对转移Tr.41和光电二极管42经由FD 21添加至图3中的像素2的配置。换言之,在这种情况下,一套Tr.配置为由两个像素(光电二极管22和光电二极管42)共享。

[0086] 在4个像素共享的情况下,将两对转移Tr.51-1、51-2和光电二极管52-1、52-2经由FD 21进一步添加至上述2个像素共享结构。换言之,在这种情况下,一套Tr.配置为由四个像素(光电二极管22、光电二极管42、光电二极管52-1和52-2)共享。

[0087] 在8个像素共享的情况下,将四对转移Tr.61-1至61-4和光电二极管62-1至62-4经由FD 21进一步添加至上述4个像素共享结构。换言之,在这种情况下,一套Tr.配置为由八个像素(光电二极管22、光电二极管42、光电二极管52-1、52-2、和光电二极管62-1至62-4)共享。

[0088] 第一实施例

[0089] <根据本技术的固态成像装置的示例性配置>

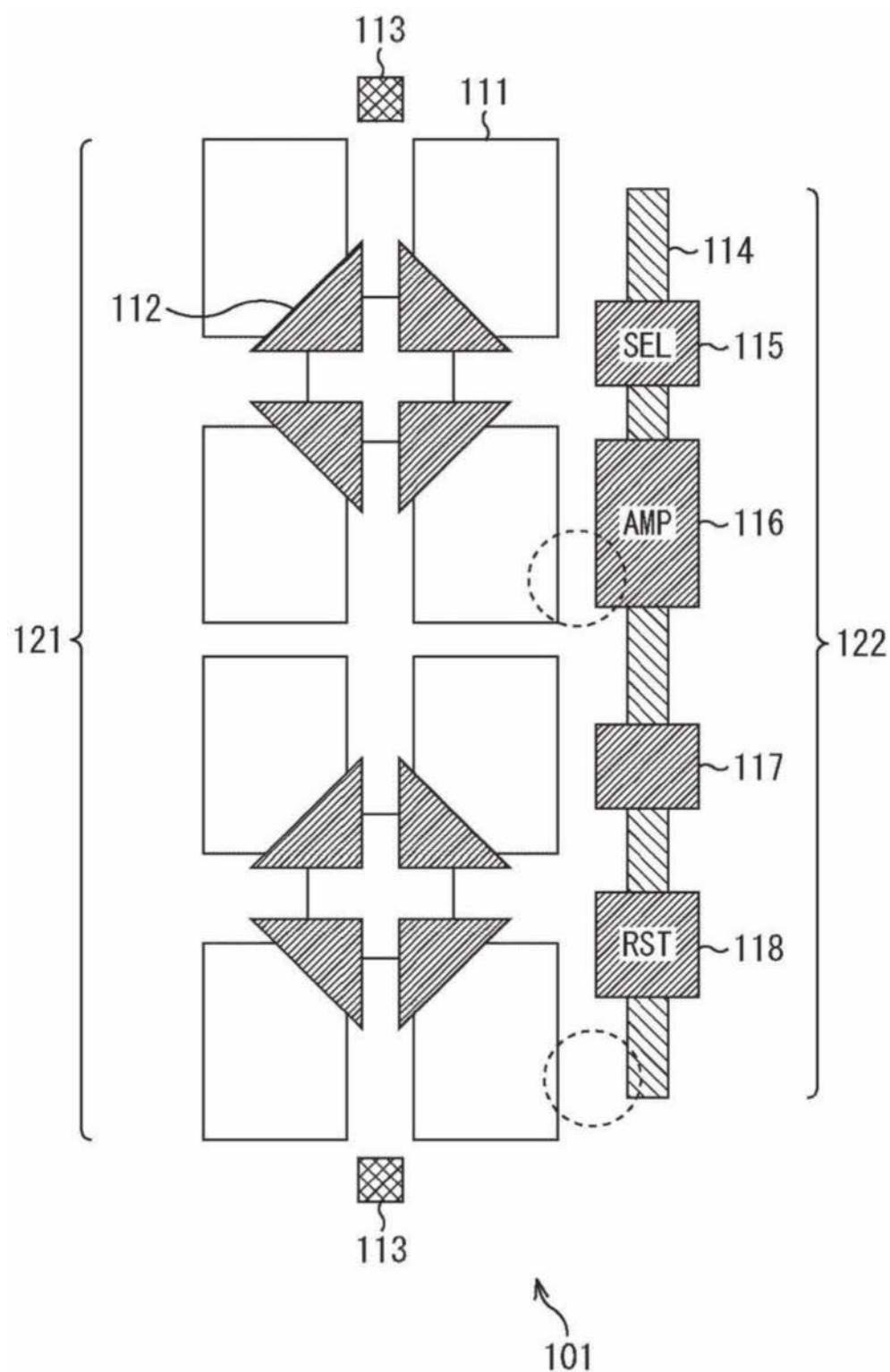

[0090] 图5是图示了采用了本技术的固态成像装置的示例性配置的图。在图5中的示例中,图示了包括4个Tr.类型、8个像素共享(24个像素)的背照式CMOS传感器的固态成像装置的情况。

[0091] 通常,4个Tr.类型具有一个如下区域:三个晶体管,包括上述的重置Tr. (RST)、放大Tr. (AMP) 和选择Tr. (SEL),布置在布置有光电二极管的光电二极管区域旁边。进一步地,

假设由于转移Tr.直接连接至光电二极管,所以转移Tr.布置在光电二极管区域中。

[0092] 在图5中的固态成像装置101中,作为像素共享单元的光电二极管111的 $2 \times 4$ 个像素和转移Tr.112的 $2 \times 4$ 个像素作为PD组121布置在图左侧的光电二极管区域中。

[0093] 在PD组121中,布置有二极管111的 $2 \times 4$ 个像素和转移Tr.112的 $2 \times 4$ 个像素,使得每4个像素在该图的垂直方向上分两个梯阶排列,从而形成垂直长矩形。

[0094] 另一方面,在固态成像装置101中,均直接连接至源极漏极114的选择Tr.115、放大Tr.116、虚设Tr.117和重置Tr.118作为一个Tr.组122布置在该图右侧的除光电二极管之外的区域中。

[0095] 换言之,像素Tr.,包括选择Tr.115、放大Tr.116、虚设Tr.117和重置Tr.118,作为一个Tr.组122布置在包括光电二极管111的 $2 \times 4$ 个像素的一个PD组121的长边的一侧。

[0096] 利用这种布置,可以加长放大Tr.116的L-长度(至少比其它Tr.长),从而使RN(随机噪声)性能得到改善。注意,虽然从RN角度看L-长度方向通常比放大Tr.长,但是放大Tr.的长边不一定等于L-长度,并且,在本实施例中,L-长度也是长边。换言之,L-长度代表链接源极-漏极的方向的长度。

[0097] 同时,不仅放大Tr.116,选择Tr.117也可以使L-长度加长。在加长选择Tr.的L-长度的情况下,可以减少短沟道效应,并且可以获得鲁邦的随机噪声容限。

[0098] 进一步地,Tr.组122中的各个像素Tr.布置为相对于PD组121的各个光电二极管111位置对称(即,相对于光电二级管光学对称)。

[0099] 更具体地,如虚线圆所示,放大Tr.116定位在上侧4个像素的右下方的光电二极管111旁边,但是在下侧4个像素的右下方的光电二极管111旁边无Tr..因此,尽管具有相同颜色(例如,绿色),但是由于多晶硅密度差异,光学性质可能会改变。

[0100] 考虑到这一点,在固态成像装置101中,设置有虚设Tr.117,该虚设Tr.117是重置Tr.118的虚设,并且,在Tr.组122中设置有两个重置Tr..更具体地,选择Tr.115和放大Tr.116设置在上侧4个像素的转移Tr.112附近,并且虚设Tr.117和重置Tr.118设置在下侧4个像素上的转移Tr.112附近。注意,和Tr.不同,不一定需要驱动虚设Tr.117。换言之,可以驱动虚设Tr.117,或者只是设置虚设Tr.117但不驱动虚设Tr.117。

[0101] 由此,因为通过在该图下侧的虚设Tr.117和重置Tr.118在Tr.组122中可以获得与选择Tr.115和放大Tr.116侧大体相等的布局,所以可以改善对称性。利用该结构,可以减少由Tr.之间的多晶硅密度差异造成的影响,并且可以改善在固态成像装置101中的PRNU(光子响应非均匀性:灵敏非均匀性)。

[0102] 注意,虚设Tr.117不局限于重置Tr.118的虚设,并且可以是其它Tr.的虚设。

[0103] 进一步地,在固态成像装置101中,阱接触113布置在PD组121与其它PD组121(未图示但布置在该图的上下两侧)之间。利用这种布置,可以有效地确保附加Tr.的区域。注意,PD组121的布置间隔以下称为PD组121的间距。

[0104] 进一步地,由于阱接触113影响各种像素特征(尤其是暗电流),所以可以通过在PD组121与其它PD组121(布置在图的上下两侧)之间布置阱接触,来抑制像素间的差异。换言之,因为通过如上所述地布置阱接触113而将阱接触定位为与所有PD具有相等的间隔,所以像素间的差异可以较小。

[0105] 进一步地,如接下来的图6所示,在Tr.的多晶硅对称性高的情况下,可能不需要设

置附加虚设Tr.来应对PRNU。

[0106] <Tr.布置的其它示例>

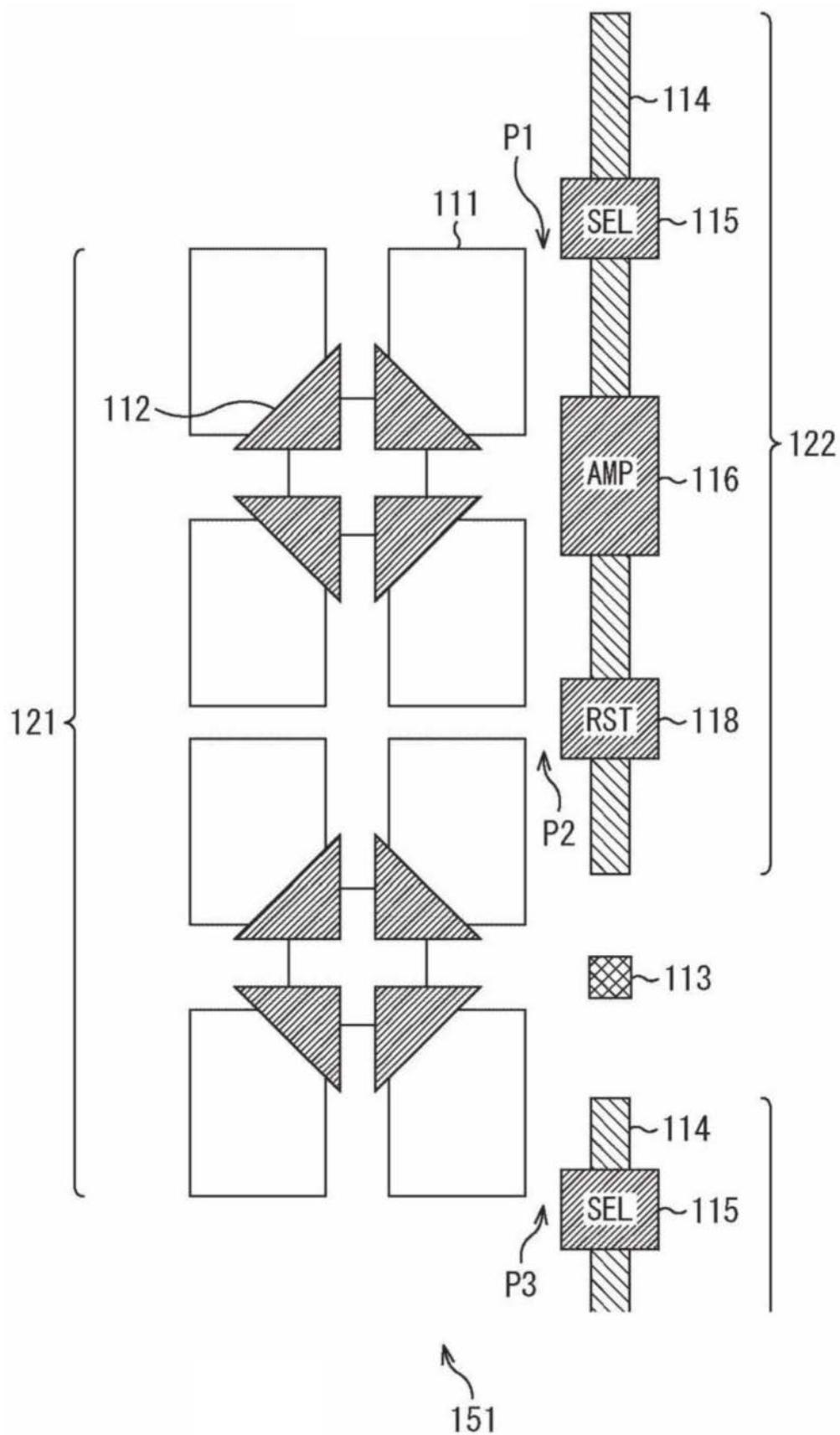

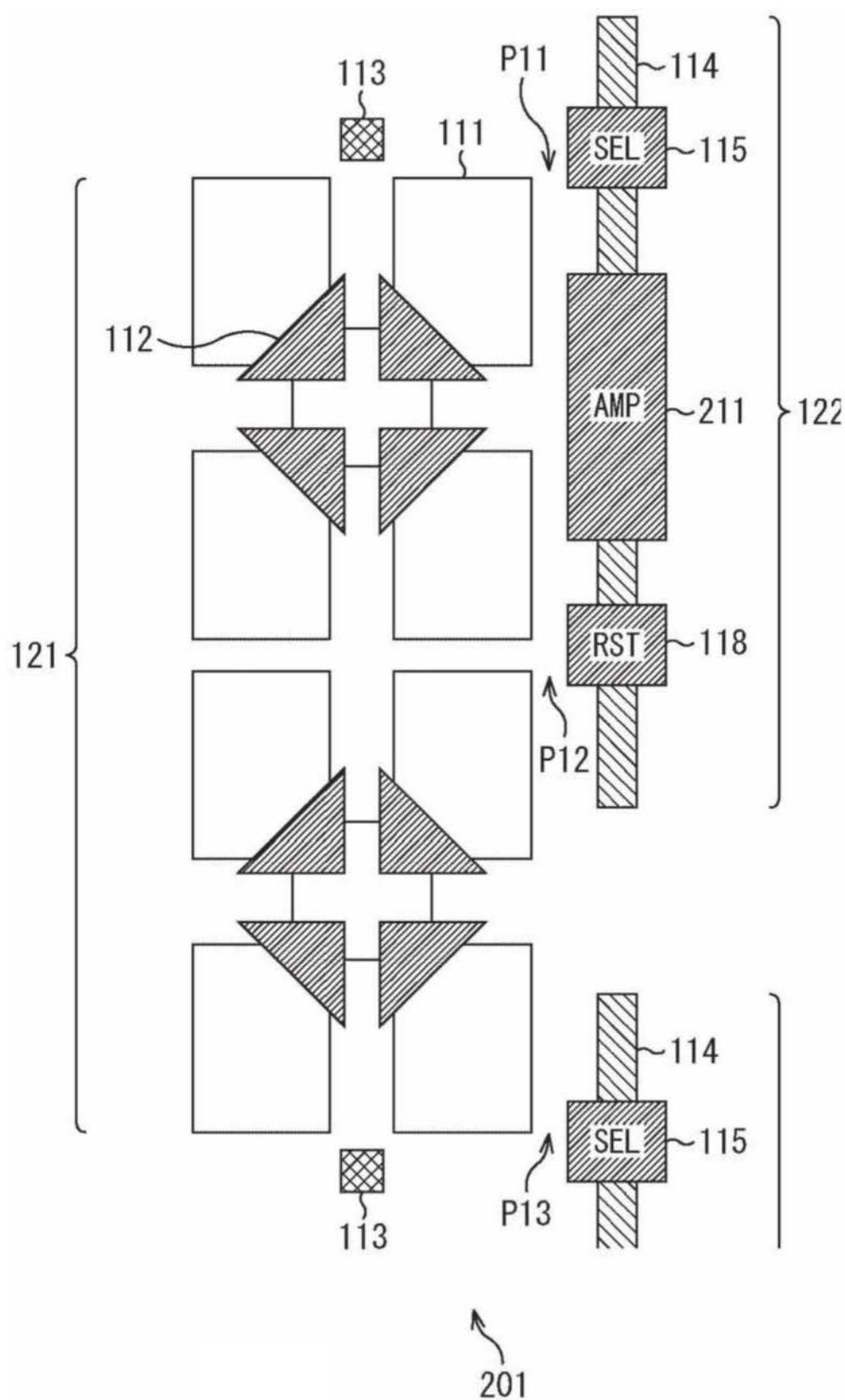

[0107] 图6是图示了采用了本技术的固态成像装置中的光电二极管和Tr.的示例性配置的图。

[0108] 在图6中的固态成像装置151中,按照与图5中的固态成像装置101相同的方式,将Tr.122布置在包括光电二极管111的 $2 \times 4$ 个像素的一个PD组121的长边的一侧。因此,如图所示,可以将现有的Tr.的L-长度加长放大Tr.116的L-长度,从而使RN(随机噪声)性能得到改善。

[0109] 另一方面,在图6中的固态成像装置151与图5中的固态成像装置101的不同之处在于Tr.组122不包括虚设Tr.117并且Tr.组122相对于PD组121的布置位置不同。

[0110] 更具体地,在Tr.组122中,放大Tr.116布置在该图上侧的转移Tr.112的4个像素旁边,并且,选择Tr.115和重置Tr.118布置在该图上侧的光电二极管111的4个像素的未设置有转移Tr.112的一侧的角部处,如箭头P1和P2所示。此外,如箭头p3所示,与布置在PD组121下方的另一PD组121对应的Tr.组122中的选择Tr.155也布置在该图下侧的光电二极管111的四个像素的未设置有转移Tr.112的一侧的角部处。

[0111] 进一步地,利用这种布置,Tr.组122布置为:相对于PD组121位置,整个移位至该图的上侧。在图5的示例中,PD组121的位置和Tr.组122的位置对准。与此相反,在图6的示例中,Tr.组122相对于PD组121的矩形形状的共享单元而向上移位一个光电二极管111的长边的长度。注意,移位的量不限于一个光电二极管111的长边的长度。以下同样适用。

[0112] 进一步地,阱接触113布置在该图下侧的转移Tr.112的4个像素旁边,以便改善在图6中的固态成像装置151中的光电二极管111的上4个像素和下4个像素之间的对称性。注意,放大Tr.116和阱接触113不一定正好分别定位于转移Tr.112的4个像素旁边,并且在放大Tr.116和阱接触113正好定位于转移Tr.112旁边附近的情况下,可以预期对称性改善的效果。

[0113] 如上所述,在图6中的固态成像装置151中,因为仅通过在Tr.组122中布置重置Tr.、放大Tr.和选择Tr.各一个来实现相对于PD组121中的光电二极管111的对称性,所以,在未设置虚设Tr.的情况下,也可以改善PRNU。

[0114] 同时,由于在图6中的固态成像装置151中的PD组121之间未设置阱接触113,所以,与图5中的固态成像装置101不同,由像素间的差异造成的影响可能仍然存在。在这种情况下,可以按照与图5中的示例相同的方式在PD组121之间布置阱接触113。

[0115] 而且,如图7所示,可以根据可以借此改善PRNU和RN的布局来布置Tr.组122中的各个Tr.的位置。

[0116] 图7中的固态成像装置201与图6中的固态成像装置151的不同之处在于用在Tr.组122中的具有加长至最大限度的L-长度的放大Tr.211代替了放大Tr.116。

[0117] 换言之,在图7中的固态成像装置201中,在Tr.组122中的放大Tr.211的L-长度比图6中的放大Tr.116的L-长度长。

[0118] 由于这一点,在图7中的固态成像装置201中,按照与图5中的固态成像装置101相同的方式,沿着包括光电二极管111的 $2 \times 8$ 个像素的PD组121的长边,布置Tr.122。因此,因为如图所示可以将现有Tr.的L-长度加长Tr.211的L-长度,所以可以改善RN(随机噪声)性

能。

[0119] 更具体地,在Tr.组122中,放大Tr.211布置在该图上侧的转移Tr.112的4个像素旁边,并且,进一步如箭头p11和p12所示,选择Tr.115和重置Tr.118布置在该图上侧的光电二极管111的4个像素的未布置有转移Tr.的一侧的角部处。此外,如箭头p13所示,与布置在图示的PD组121下方的另一PD组121(未图示)对应的Tr.组122的选择Tr.115还布置在该图下侧的光电二极管111的4个像素的未布置有转移Tr.的一侧的角部处。

[0120] 注意,在这种情况下,Tr.组122也相对于PD组121的位置而在该图中向上整个移位。

[0121] 如上所述,由于将放大Tr.的L-长度加长至最大限度而未在图7的固态成像装置201中设置虚设Tr.,所以可以改善RN容限。而且,由于选择Tr.115和重置Tr.118布置为相对于光电二极管对称,所以可以改善PRNU。

[0122] 进一步地,在图7的固态成像装置中,阱接触113布置在PD组121与另一PD组121(未图示但是按照与图5中的固态成像装置101中相同的方式布置在该图下侧)之间。

[0123] 因此,在图7的固态成像装置201中,按照与图5中的固态成像装置201相似的方式,可以抑制像素之间的差异。同时,在可以减小在PD与PD之间的元件隔离宽度并且阱接触113不可以布置在PD与PD之间的情况下,可以按照与图6中的示例相同的方式来布置Tr.组122。

[0124] 进一步地,作为具有最高对称性的布局,Tr.的多晶硅相对于PD组121的光电二极管111的布置大体均匀地布置,如图8所示,从而实现改善PRNU。

[0125] 更具体地,在图8的固态成像装置251中,Tr.组122的选择Tr.115布置在阱接触113旁边,该阱接触113布置在该图中的PD组121的上侧。进一步地,放大Tr.116布置在该图上侧的PD组121中的转移Tr.112的4个像素旁边,并且重置Tr.118布置在光电二极管111的4个像素与PD组121中的光电二极管111的4个像素之间。

[0126] 此外,虚设Tr.117布置在该图下侧的PD组121中的转移Tr.112的4个像素旁边。

[0127] 如上所述,在图8的固态成像装置251中,Tr.的多晶硅相对于PD组121中的光电二极管的布置更均匀地布置。在这种情况下,与在图5中的固态成像装置101相比,不能加长放大Tr.116的L-长度。因此,不能改善RN性能,但是可以最大程度地改善PRNU。进一步地,由于按照与图5中的固态成像装置101相同的方式将阱接触113布置在PD组与PD组之间,所以可以使在像素之间的像素特征的差异最小化。注意,不一定需要设置虚设Tr.117。更具体地,由于在转移Tr.112的外围中的多晶硅的密度已经较高,所以转移Tr.112旁边的多晶硅可能不会影响到PRNU。在这种情况下,不具有虚设Tr.117的布局也可以是另外一种选择。

[0128] 第二实施例

[0129] <根据本技术的固态成像装置的示例性配置>

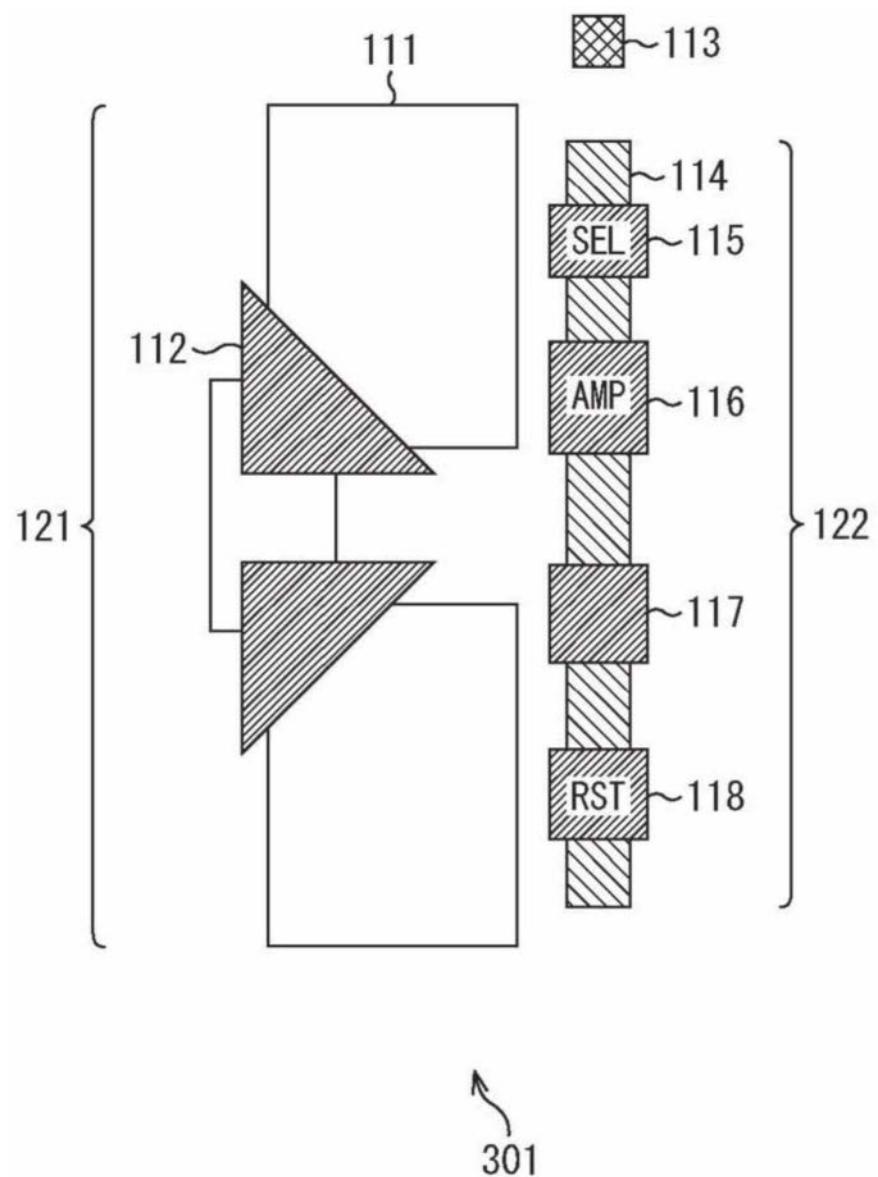

[0130] 图9是图示了采用了本技术的固态成像装置的另一示例性配置的图。在图9中的示例中,图示了包括4个Tr.类型、2个像素共享( $1 \times 2$ 个像素)的背照式CMOS传感器的固态成像装置的情况。注意,在图9中的示例是将图5中描述的布局应用于2个像素共享的情况。

[0131] 在图9的固态成像装置301中,布置有采用像素共享结构的光电二极管111的 $1 \times 2$ 个像素和与其对应的转移Tr.112的 $1 \times 2$ 个像素,以便在该图左侧的光电二极管区域中形成垂直长矩形作为PD组121。

[0132] 进一步地,像素Tr.,包括选择Tr.115、放大Tr.116、虚设Tr.117和重置Tr.118,作

为Tr.组122布置在PD组121中的长边的一侧。Tr.组122的各个像素Tr.布置为相对于PD组121的各个光电二极管111对称。

[0133] 更具体地,在图9的Tr.组122中,选择Tr.115布置在PD组121的上光电二极管111的中心附近,并且,重置Tr.118布置在PD组121的下光电二极管111的中心附近,以便与选择Tr.115对称。

[0134] 按照相同的方式,在图9的Tr.组122中,放大Tr.116布置在PD组121中的上转移Tr.112附近,并且,虚设Tr.117布置在PD组121的下转移Tr.112附近,以便与放大Tr.116对称。

[0135] 如上所述,在2个像素共享的情况下,可以获得与上面参照图5所述的8个像素共享相同的效果。更具体地,因为可以通过将放大Tr.作为Tr.组122布置在PD组121的长边的一侧来加长放大Tr.的L-长度,所以可以改善RN(随机噪声)性能。进一步地,由于Tr.的多晶硅相对于光电二极管的对称性高,所以可以改善PRNU。

[0136] 同时,在图9中的固态成像装置301的情况下,在Tr.组122和定位于Tr.组122上方的另一Tr.组122之间布置阱接触113,但也可以如在图8所示的示例中一样,在PD与PD之间布置阱接触113。

[0137] 第三实施例

[0138] <根据本技术的固态成像装置的示例性配置>

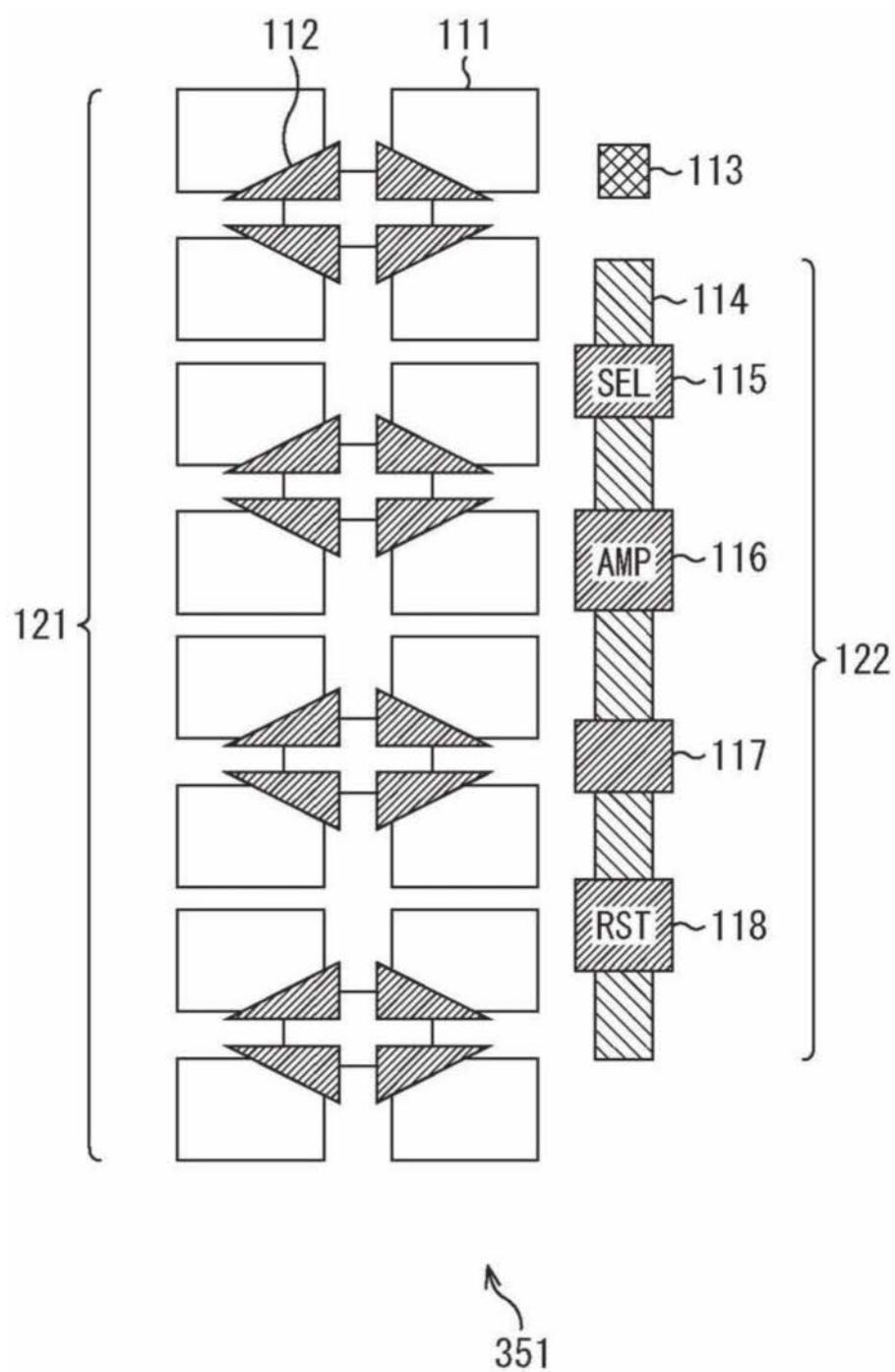

[0139] 图10是图示了采用了本技术的固态成像装置的另一示例性配置的图。在图10中的示例中,图示了包括4个Tr.类型、16个像素共享(28个像素)的背照式CMOS传感器的固态成像装置的情况。注意,在图10中的示例是将图5中描述的布局应用于16个像素共享的情况。

[0140] 在图10的固态成像装置351中,采用像素共享结构的光电二极管111的 $2 \times 8$ 个像素和与其对应的转移Tr.112的 $2 \times 8$ 个像素作为一个PD组121布置在该图左侧的光电二极管区域中。

[0141] 在PD组121组中,布置有光电二极管111的 $2 \times 8$ 个像素和转移Tr.112的 $2 \times 8$ 个像素以便形成垂直长矩形,并且每4个像素在该图的垂直方向上分四个梯阶排列。

[0142] 进一步地,像素Tr.,包括选择Tr.115、放大Tr.116、虚设Tr.117和重置Tr.118,作为一个Tr.组122布置在PD组121的长边的一侧(该图中的右侧)。进一步地,阱接触113布置在该图中的Tr.组122的上侧。阱接触113和Tr.组122的各个像素Tr.布置为相对于PD组121的各个光电二极管111对称。

[0143] 更具体地,在图10中的示例中,阱接触113正好布置在从该图顶部算起的第一梯阶中的转移Tr.112的4个像素的旁边附近。在Tr.组122中,选择Tr.115布置在与从该图顶部算起的第二梯阶中的光电二极管111的4个像素的转移Tr.112相对的位置附近。

[0144] 在Tr.组122中,放大Tr.116布置在从该图顶部算起的第二梯阶中的光电二极管111的4个像素的转移Tr.112的位置附近。在Tr.组122中,虚设Tr.117布置在PD组121中的从该图顶部算起的第三梯阶中的光电二极管111的4个像素的转移Tr.112的位置附近。重置Tr.118布置在PD组121的从该图顶部算起的第四梯阶中的光电二极管111的转移Tr.112相对的位置附近。

[0145] 如上所述,在16个像素共享的情况下,也可以获得与上面参照图5所述的8个像素共享相同的效果。更具体地,在图10的固态成像装置351中,因为按照与图5中的固态成像装

置101相同的方式将Tr.组122布置在包括光电二极管111的 $2 \times 8$ 个像素的一个PD组121的长边的一侧,所以如图所示可以将现有Tr.的L-长度加长放大Tr.116的L-长度。利用这样的配置,可以改善RN性能。进一步地,由于Tr.的多晶硅相对于光电二极管的对称性高,所以可以改善PRNU。

[0146] 然而,在图10中的固态成像装置351的情况下,阱接触113布置在Tr.组122和定位于Tr.组122上方的另一Tr.组122之间,并且阱接触113不设置在PD组121之间。因此,由像素之间的差异造成的影响可能仍然存在。在这种情况下,如在图5所示的示例中一样,阱接触113可以布置在PD与PD之间。在将阱接触113布置在各个梯阶的4个像素之间的情况下,可以减少像素之间的特征差异。

[0147] 如上所述,本技术可应用于矩形形状的共享单元(诸如,4个Tr.类型的2个像素共享、8个像素共享、和16个像素共享)的情况。换言之,待共享的像素的数量不受限制,并且,固态成像装置的布置不限于上述布置示例,只要一个共享单元中的光电二极管的布置呈矩形形状即可。

[0148] 此外,关于Tr.的布置,上面在第一实施例中所示的4个Tr.式、8个像素共享( $2 \times 4$ 个像素)的各种布置可以适用于2个像素共享和16个像素共享。

[0149] 第四实施例

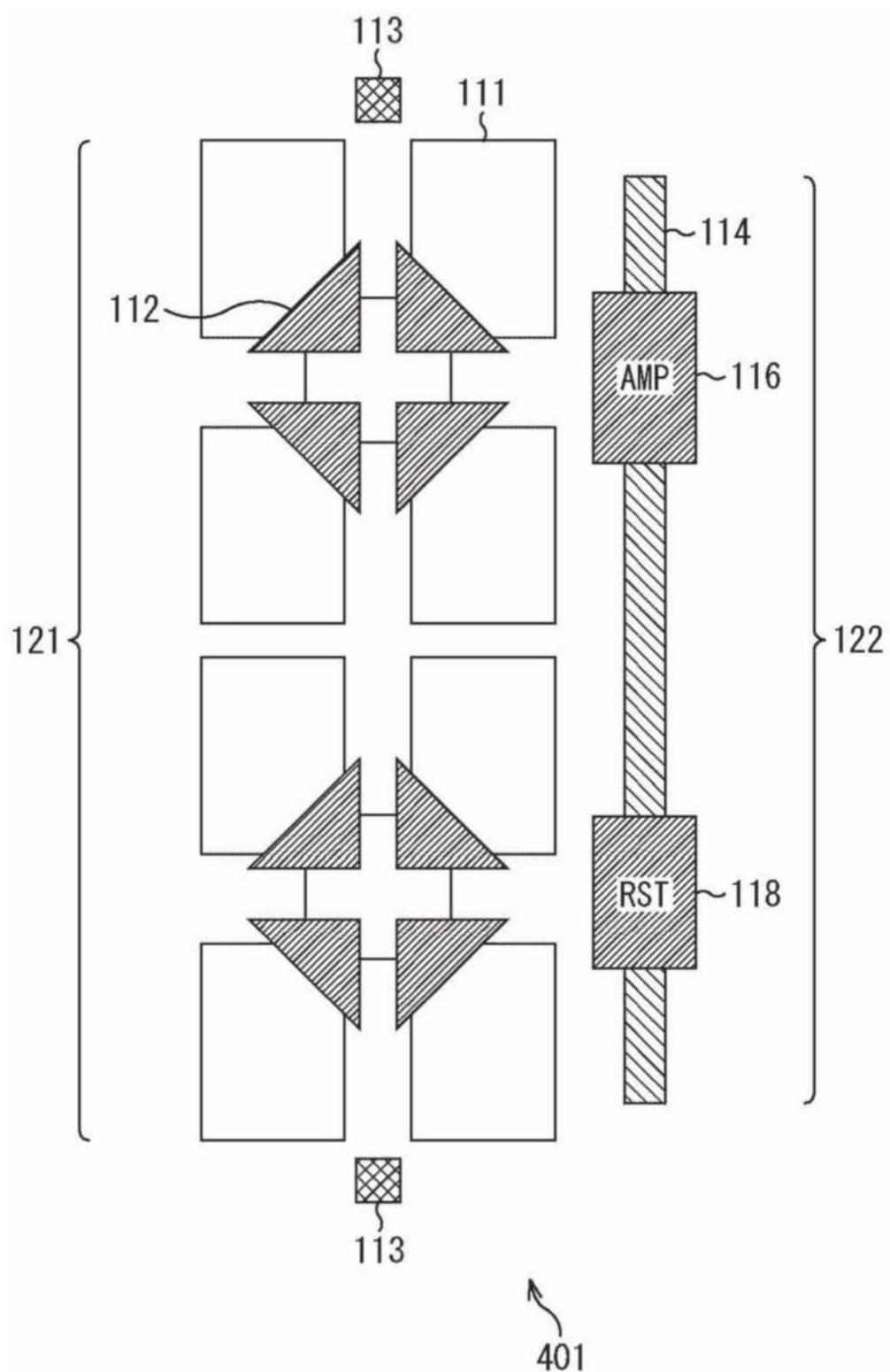

[0150] <根据本技术的固态成像装置的示例性配置>

[0151] 图11是图示了采用了本技术的固态成像装置的示例性配置的图。在图11中的示例中,图示了包括3个Tr.类型、8个像素共享( $2 \times 4$ 个像素)的背照式CMOS传感器的固态成像装置的情况。

[0152] 通常,在3个Tr.式中,上述的重置Tr.(RST)和放大Tr.(AMP)这两个晶体管包括在布置有光电二极管的光电二极管区域旁边,并且未设置选择Tr.(SEL)。进一步地,假设因为转移Tr.直接连接至光电二极管,所以转移Tr.设置在光电二极管区域中。

[0153] 在图11中的固态成像装置401与图5中的固态成像装置101的不同之处在于在一个Tr.组122中不包括选择Tr.115和虚设Tr.117。从布置在矩形形状共享单元内的角度来看(PD组正好布置在Tr.组旁边),图11中的固态成像装置401与图5中的固态成像装置101相同。

[0154] 更具体地,在Tr.组122中,放大Tr.116布置在该图上侧的转移Tr.112的4个像素旁边,并且重置Tr.118布置在该图下侧的转移Tr.112的4个像素旁边。在图11的示例中,放大Tr.116和重置Tr.118形成为大小大体相同。

[0155] 同时,在图12的固态成像装置451中,例如,在图11中的Tr.组122的布置位置向上移位了大约在该图中的一个光电二极管111的长边的长度。更具体地,在Tr.组122中,放大Tr.116布置在光电二极管111的4个像素旁边,而不是布置在该图上侧的转移Tr.112的一侧,并且重置Tr.118布置在光电二极管111的4个像素旁边,而不是布置该图下侧的转移Tr.112的一侧。在图12的示例中,放大Tr.116和重置Tr.118也形成为大小大体相同。

[0156] 换言之,在图11的固态成像装置401和图12的固态成像装置451中,因为Tr.组122沿着PD组121的长边布置,所以如图所示可以将现有Tr.的L-长度加长放大Tr.116的L-长度。利用这样的配置,可以改善RN性能。进一步地,在图11的固态成像装置401和图12的固态成像装置451中,因为Tr.的多晶硅相对于光电二极管对称,所以可以改善PRNU。

[0157] 如上所述,关于3个Tr.类型,本技术也可适用于共享单元呈矩形形状的所有情况。换言之,待共享的像素的数量不受限制,并且,固态成像装置的布置不限于上述布置示例,只要一个共享单元中的光电二极管的布置呈矩形形状即可。

[0158] 同时,在上面的描述中,已经描述了一个像素共享的短边布置在该图的上侧并且一个像素共享单元的长边沿着该图的右侧布置的示例(垂直类型实例)。然而,通过使上述示例旋转90度,即使是在对固态成像装置进行布局使得一个像素共享单元的长边布置在该图的上侧并且一个像素共享单元的短边布置在该图的左侧的情况下,结果是一样的。

[0159] 如上所述,根据本技术,因为可以加长Tr. (尤其是放大Tr.) 的L-长度,所以可以改善RN(随机噪声)容限或性能。

[0160] 更具体地,在将AMP和SEL布置在组1中并且将两个Tr.布置在组2的情况下,组1需要3个源极漏极,并且组2需要3个源极漏极,即,总共需要六个源极漏极。此时,由于光刻线宽度受到限制,并且处理多晶硅和接触孔、确保隔离击穿电压等受到限制,加长Tr.的L-长度也受到限制。具体地,在微型化的情况下,这种状态的影响相当严重,并且,由于AMP的L-长度较短,所以RN容限可能会恶化。

[0161] 与此相反,根据本技术,因为可以加长放大Tr.的L-长度,所以可以改善RN性能。注意,放大Tr.的L-长度是上述示例中的PD组的间距的0.6倍至1.4倍。进一步地,根据本技术,可以加长选择Tr.的L-长度。因此,在加长选择Tr.的L-长度的情况下,可以避免短沟道效应,并且可以获得鲁棒的随机噪声容限。

[0162] 可以获得上述效果,并且,上述效果在像素大小缩小至大约1.0mm或者更小的情况下尤其有利。

[0163] 此外,根据本技术,因为进行布置以使Tr.的多晶硅具有对称性,所以可以改善PRNU。

[0164] 同时,虽然上文已经描述了将本技术应用于CMOS固态成像装置的配置,但是可以将本技术应用于固态成像装置,诸如,CCD(电荷耦合器件)固态成像装置。

[0165] 注意,固态成像装置既可以是背照式的,也可以是前照式的。

[0166] 进一步地,固态成像装置既可以是全局快门式的,也可以不是全局快门式的。固态成像装置不受限于全局快门式的。

[0167] 注意,本技术的应用不受限于固态成像装置,并且本技术可应用于成像装置。此处,成像装置指的是诸如数码相机和数码摄像机等照相机系统、以及设置有成像功能的电子设备,诸如,手机。注意,成像装置可以具有安装在电子设备上的模块式配置,即,照相模块。

[0168] 第五实施例

[0169] <电子设备的示例性配置>

[0170] 此处,根据参照图13的本技术的第二实施例,将对电子设备的示例性配置进行说明。

[0171] 图13图示的电子设备500包括固态成像装置(装置芯片)501、光学透镜502、快门装置503、驱动电路504和信号处理电路505。对于固态成像装置501,提供了根据本技术的上述第一至第四实施例的固态成像装置。因此,可以提供具有高性能的并且RN性能和PRNU得到改善的电子设备500。

[0172] 光学透镜502在固态成像装置501的成像表面上形成来自物体的图像光(入射光)。由此,在预定期间内,信号电荷累积在固态成像装置501内部。快门装置503控制固态成像装置501的照射时间和遮蔽时间。

[0173] 驱动电路504提供控制固态成像装置501的信号转移操作和快门装置503的快门操作的驱动信号。固态成像装置501根据驱动电路504提供的驱动信号(定时信号)传送信号。信号处理电路505对从固态成像装置501输出的信号执行各种信号处理。与信号处理一起应用的视频信号储存在诸如存储器等存储介质中,或者输出至显示器。

[0174] 同时,在本说明书中,虽然并非总是以时间序列执行,但是用于描述一系列上述处理的步骤显然可以包括按照所描述的顺序以时间序列执行的处理,但是也可以包括并行地或者单独地执行的处理。

[0175] 同样,根据本公开的实施例可以不限于上述实施例,并且在不脱离本公开的主旨的范围内,可以进行各种改变。

[0176] 进一步地,上述流程图中描述的各个步骤可以由一种装置执行,也可以由多种装置按照共享的方式执行。

[0177] 进一步地,在一个步骤包括多个处理的情况下,这一个步骤中包括的该多个处理可以由一种装置执行,也可以由多种装置按照共享的方式执行。

[0178] 此外,上述配置作为一个装置(或者处理段)可以进行划分,并且可以配置成多个装置(或者处理段)。相反,上述配置作为多个装置(或者处理段)可以整体配置为一个装置(或者处理段)。进一步地,各个装置(或者各个处理段)可以添加除了上述配置之外的配置。此外,只要配置和操作与整个系统大体相同,装置(或者处理段)的部分配置可以包括在其它装置(或者其它处理段)中。换言之,本技术不限于上述实施例,并且在不脱离本公开的主旨的范围内,可以进行各种改变。

[0179] 虽然已经参照附图详细描述了本公开的优先实施例,但是本公开不限于此。应当理解,本公开的本技术领域的技术人员显然可以在随附权利要求书中叙述的技术构思的范围内设想各种修改和变更,并且这种修改和变更显然属于本公开的技术范围。

[0180] 另外,本公开可以具有以下配置。

[0181] (1)

[0182] 一种成像设备,该成像设备包括:共享像素结构,该共享像素结构包括:多个光电二极管,其中,多个光电二极管中的每个光电二极管都位于矩形区域内;

[0183] 多个共享晶体管,其中,多个共享晶体管中的每个晶体管都与包含该多个光电二极管的矩形区域的一侧相邻。

[0184] (2)

[0185] 上述(1)的成像装置,其中,矩形区域具有两条短边和两条长边,其中,共享晶体管中的每个共享晶体管与包含该多个光电二极管的矩形区域的长边中的一条长边相邻。

[0186] (3)

[0187] 上述(2)的成像装置,其中,共享像素结构的多个共享晶体管中的共享晶体管沿着与矩形区域的长边中的一条长边平行的线布置。

[0188] (4)

[0189] (1)至(3)中任何一项的成像装置,其中,共享像素结构的多个共享晶体管中的共

享晶体管在矩形区域外部。

[0190] (5)

[0191] (1) 至 (4) 中任何一项的成像装置,其中,多个共享晶体管中的共享晶体管包括放大晶体管、选择晶体管和重置晶体管中的至少一种。

[0192] (6)

[0193] (2) 或者 (3) 的成像装置,其中,多个共享晶体管中的共享晶体管包括至少一个放大晶体管和至少一个其它晶体管,以及其中,放大晶体管的沿着放大晶体管的与矩形区域的长边平行的尺寸的长度比至少一个其它晶体管的沿着其它晶体管的与矩形区域的长边平行的长度长。

[0194] (7)

[0195] (2) 和 (3) 的成像装置,其中,多个光电二极管是光电转换元件组,该光电转换元件组包括位于矩形区域内的共享单元,以及其中,多个共享晶体管是布置为相对于光电转换元件组大体对称的像素晶体管组。

[0196] (8)

[0197] 上述(7)的成像装置,该成像装置还包括:阱接触,其中,阱接触设置在光电转化元件组和紧挨着光电转换元件组定位的另一光电转换元件组之间。

[0198] (9)

[0199] (1) 至 (8) 中任何一项的成像装置,其中,多个共享晶体管包括虚设晶体管。

[0200] (10)

[0201] (2) 或者 (3) 的成像装置,其中,多个共享晶体管包括至少一个选择晶体管和至少一个其它晶体管,以及其中,选择晶体管的沿着选择晶体管的与矩形区域的长边平行的尺寸的长度比至少一个其它晶体管的沿着其它晶体管的与矩形区域的长边平行的长度长。

[0202] (11)

[0203] 一种电子设备,该电子设备包括:具有共享像素结构的成像设备,该共享像素结构包括:多个光电二极管,其中,多个光电二极管中的每个二极管都位于矩形区域内;

[0204] 多个共享晶体管,其中,多个共享晶体管中的每个晶体管都与包含多个光电二极管的矩形区域的一侧相邻。

[0205] (12)

[0206] (12) 上述(11)的电子设备,其中,矩形区域具有两条短边和两条长边,以及其中,共享晶体管中的每个共享晶体管与包括多个光电二极管的矩形区域的长边中的一条长边相邻。

[0207] (13)

[0208] 上述(12)的电子设备,其中,共享像素结构的多个共享晶体管中的共享晶体管沿着与矩形区域的长边中的一条长边平行的线布置。

[0209] (14)

[0210] (11) 至 (13) 中任何一个电子设备,其中,共享像素结构的多个共享晶体管中的共享晶体管在矩形区域的外部。

[0211] (15)

[0212] (11) 至 (14) 中任何一项的电子设备,其中,多个共享晶体管中的共享晶体管包括

放大晶体管、选择晶体管和像素晶体管中的至少一种。

[0213] (16)

[0214] (12)或者(13)的电子设备,其中,多个共享晶体管中的共享晶体管包括至少一个放大晶体管和至少一个其它晶体管,以及其中,放大晶体管的沿着放大晶体管的与矩形区域的长边平行的尺寸的长度比至少一个其它晶体管的沿着其它晶体管的与矩形区域的长边平行的长度长。

[0215] (17)

[0216] (12)或(13)的电子设备,其中,多个光电二极管是光电转换元件组,该光电转换元件组包括位于所述矩形区域内的共享单元,以及其中,多个共享晶体管是布置为相对于光电转换元件组大体对称的像素晶体管组。

[0217] (18)

[0218] 上述(17)的电子设备,该电子设备进一步包括:阱接触,其中,阱接触设置在光电转换元件组和紧挨着光电转换元件组定位的另一光电转换元件组之间。

[0219] (19)

[0220] (11)至(18)中任何一项的电子设备,其中,多个共享晶体管包括虚设晶体管。

[0221] (20)

[0222] (12)或(13)中的电子设备,其中,多个共享晶体管包括至少一个选择晶体管和至少一个其它晶体管,以及其中,选择晶体管的沿着放大晶体管的与矩形区域的长边平行的尺寸的长度比至少一个其它晶体管的沿着其它晶体管的与矩形区域的长边平行的长度长。

[0223] [附图标记列表]

[0224] 1 固态成像装置

[0225] 2 像素

[0226] 3 像素区域

[0227] 101 固态成像装置

[0228] 111 光电二极管

[0229] 112转移Tr.

[0230] 113 阵接触

[0231] 114 源极漏极

[0232] 115选择Tr.

[0233] 116放大Tr.

[0234] 117虚设Tr.

[0235] 118重置Tr.

[0236] 121PD组

[0237] 122Tr.组

[0238] 151、201固态成像装置

[0239] 211放大Tr.

[0240] 251、301、351、401、451固态成像装置

[0241] 500 电子设备

[0242] 501 固态成像装置

- [0243] 502 光学透镜

- [0244] 503 快门装置

- [0245] 504 驱动电路

- [0246] 505 信号处理电路。

图1

## 垂直信号线

图2

## 垂直信号线

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13