(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6495272号

(P6495272)

(45) 発行日 平成31年4月3日(2019.4.3)

(24) 登録日 平成31年3月15日(2019.3.15)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 29/78  | (2006.01)    |

| HO 1 L 29/739 | (2006.01)    |

| HO 1 L 21/336 | (2006.01)    |

|               | HO 1 L 29/78 |

請求項の数 14 (全 15 頁)

|               |                               |           |                                                                                           |

|---------------|-------------------------------|-----------|-------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2016-528598 (P2016-528598)  | (73) 特許権者 | 507044103<br>エコ・セミコンダクターズ・リミテッド<br>イギリス国 エルイー2 2エルディー、<br>レスター、グリーブ・ロード、ウィルミン<br>トン・コート 2 |

| (86) (22) 出願日 | 平成26年7月2日(2014.7.2)           | (74) 代理人  | 100073184<br>弁理士 柳田 征史                                                                    |

| (65) 公表番号     | 特表2016-527722 (P2016-527722A) | (74) 代理人  | 100090468<br>弁理士 佐久間 剛                                                                    |

| (43) 公表日      | 平成28年9月8日(2016.9.8)           | (72) 発明者  | マダシル、サンカラ<br>英国 エルイー2 21ディー レスター<br>シャー レスター グリーブ ロード ウ<br>ィルミントン コート 2                   |

| (86) 國際出願番号   | PCT/GB2014/052013             | 審査官       | 杉山 芳弘                                                                                     |

| (87) 國際公開番号   | W02015/011440                 |           |                                                                                           |

| (87) 國際公開日    | 平成27年1月29日(2015.1.29)         |           |                                                                                           |

| 審査請求日         | 平成29年6月29日(2017.6.29)         |           |                                                                                           |

| (31) 優先権主張番号  | 1313126.3                     |           |                                                                                           |

| (32) 優先日      | 平成25年7月23日(2013.7.23)         |           |                                                                                           |

| (33) 優先権主張国   | 英國(GB)                        |           |                                                                                           |

| (31) 優先権主張番号  | 1314474.6                     |           |                                                                                           |

| (32) 優先日      | 平成25年8月13日(2013.8.13)         |           |                                                                                           |

| (33) 優先権主張国   | 英國(GB)                        |           |                                                                                           |

最終頁に続く

(54) 【発明の名称】 MOS-バイポーラ素子

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体素子であって、

第1導電型及び第2導電型の少なくとも1つのカソード領域が配された第1導電型のベース領域、

第2導電型の第1ウエル領域、

第1導電型の第2ウエル領域、

第2導電型のドリフト領域、

第1導電型のアノード領域、及び

アノードコンタクト、

を含む複数のセルであって、該複数のセルが導電コンタクトにより相互に接続されているもの、を有し、

前記セルのそれぞれが前記第1ウエル領域内に配され、前記第1ウエル領域が前記第2ウエル領域内に配されている、

半導体素子において、

前記素子が、縦方向で前記第2ウエル領域及び前記ドリフト領域と交差し、横方向で前記ベース領域及び前記第1および第2ウエル領域と交差する、細長トレンチであって、前記第2ウエル領域の全厚の一部に亘って伸びている、細長トレンチを有し、

絶縁膜が前記トレンチの内表面を実質的に覆うように設けられ、

第1ゲートが前記トレンチを実質的に埋めるように前記絶縁膜上に形成され、

前記素子が、前記素子の動作中に、前記ベース領域と前記第1ウエル領域の間の接合における空乏領域が前記第1ウエル領域と前記第2ウエル領域の間の接合まで延びることができ、よって前記第1ウエル領域の電位を前記アノードコンタクトの電位のいかなる上昇からも実質的に絶縁するように構成され、

前記複数のセルの少なくとも一部のセルが作動し、前記複数のそれ以外のセルがダミーセルとして不作動であるように構成されている、

ことを特徴とする半導体素子。

【請求項2】

請求項1に記載の半導体素子を作製する方法において、

第2導電型の半導体層内に前記第2ウエル領域を、残余半導体層が前記ドリフト領域を形成するように、形成する工程、

10

前記第2ウエル領域内に前記第1ウエル領域を形成する工程、

前記第1ウエル領域内に前記ベース領域を形成する工程、及び

前記カソード領域を形成する工程、

を含み、

前記方法がさらに、細長トレンチを、前記トレンチが縦方向で前記第2ウエル領域及び前記ドリフト領域と交差し、横方向で前記ベース領域及び前記第1ウエル領域と交差するように、形成する工程を含み、

前記方法がさらに、半導体基板上に請求項1に記載の半導体素子を複数作製する工程であって、該半導体素子の一部は作動するように、それ以外の半導体素子はダミーセルとして作動しないように構成する工程を含む、

ことを特徴とする方法。

20

【請求項3】

前記トレンチの各々が前記カソード領域の各々の形成に先立って形成されることを特徴とする請求項2に記載の方法。

【請求項4】

半導体基板上に、複数の、請求項1に記載の半導体素子を形成する工程であって、その際、前記素子は1つ以上の実質的に平行な列をなして配置されるものである、工程、及び

1つまたは複数の前記半導体素子列に実質的に直交して通る、実質的に平行な列をなす、複数本の細長トレンチを、前記トレンチのそれぞれが縦方向で前記第2ウエル領域及び前記ドリフト領域と交差し、横方向で少なくとも1つの半導体素子の前記ベース領域及び前記第1ウエル領域と交差するように、形成する工程、

を含むことを特徴とする請求項2に記載の方法。

30

【請求項5】

少なくとも1本のトレンチが、横方向で、前記半導体素子のそれぞれの前記第1ウエル領域及び前記第2ウエル領域と交差することを特徴とする請求項2に記載の方法。

【請求項6】

前記少なくとも1本のトレンチが前記第2ウエル領域の全厚を貫通しないことを特徴とする請求項5に記載の方法。

【請求項7】

前記少なくとも1本のトレンチが横方向で前記第2ウエル領域の全厚を貫通して前記ドリフト領域に延び込むことを特徴とする請求項5に記載の方法。

40

【請求項8】

少なくとも1本のトレンチの前記内表面上に絶縁層を形成する工程及び前記トレンチのそれを実質的に埋めるように構成されたゲートを形成する工程をさらに含むことを特徴とする請求項2に記載の方法。

【請求項9】

少なくとも1つの前記素子列の前記素子のそれぞれが作動するように構成されることを特徴とする請求項4に記載の方法。

【請求項10】

50

一つおきの前記素子列の前記素子のそれぞれが作動するように構成され、残余素子列の前記素子がダミーセルと指定されることを特徴とする請求項4に記載の方法。

【請求項11】

半導体構造において、実質的に平行な素子列をなして配置された、複数の、請求項1に記載の半導体素子を含み、前記半導体素子列に実質的に直交する、実質的に平行な列をなして配置された複数本のトレンチを有し、前記トレンチのそれぞれが、前記素子列のそれぞれの前記素子の、縦方向で前記第2ウエル領域及び前記ドリフト領域と交差し、横方向で前記ベース領域、前記第1ウエル領域及び前記第2領域と交差し、前記トレンチの少なくとも1本の前記内表面を実質的に覆うように絶縁膜が設けられ、前記少なくとも1本のトレンチを実質的に埋めるようにゲートが前記絶縁膜上に形成されており、前記素子の少なくとも一部が作動し、それ以外の前記素子がダミーセルとして作動しないように構成されていること、特徴とする半導体構造。

10

【請求項12】

一つおきの前記素子列の前記素子のそれぞれが作動するように構成され、残余素子列の前記素子がダミーセルと指定されることを特徴とする請求項11に記載の半導体構造。

【請求項13】

複数の前記セル及び/または前記素子が接続領域によって相互に接続されてクラスターをなしていることを特徴とする請求項11に記載の半導体構造。

【請求項14】

前記接続領域が1本以上のトレンチを含むことを特徴とする請求項13に記載の半導体構造。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明はMOS-バイポーラ素子に関し、さらに詳しくは、クラスター化絶縁ゲートバイポーラトランジスタ(CIGBT)及びその作製のためのプロセスに関する。

【背景技術】

【0002】

従来、小電力用途及び中電力用途にはパワー金属酸化物電界効果トランジスタ(MOSFET)が用いられてきた。しかし、絶縁ゲートバイポーラトランジスタ(IGBT)が、そのより低いオン状態電力損失及びより大きい電流密度により、一層優れたスイッチング性能を可能にすることがわかつてきた。IGBTの電力定格は徐々に大きくなっていて、高電圧直流(HDVC)インバータシステム及びトラクション伝導装置制御のような中電力用途においてサイリスタを置き換えると予想される。

30

【0003】

MOSゲート型サイリスタ(MGT)素子は、より小さい順方向電圧降下及び改善された電流密度を示すから、トランジスタ型素子に対する有望な代替と見なされてきた。特許文献1に説明されるCIGBTは、全ての動作条件下で高アノード電圧からカソードセルを保護する独特的のセルフクランピング機能をもつ、MOSゲート型サイリスタ素子である。このセルフクランピング機能は、高ゲートバイアス時の電流飽和も可能にし、低スイッチング損失も提供し、その低オン状態電圧及び高電圧遮断能力はIGBTをIGBTへの代替として極めて好適にする。

40

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開第01/18876号

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の課題は、CIGBT技術を用いる、カソードセル構造及びその作製方法を提供

50

することにある。

【課題を解決するための手段】

【0006】

本発明にしたがえば、

第1及び第2の導電型の内の少なくとも1つのカソード領域がその中に配されていて、導電コンタクトによって相互に接続されている、第1の導電型のベース領域、

第2導電型の第1ウエル領域、

第1導電型の第2ウエル領域、

第2導電型のドリフト領域、

第1導電型のアノード領域、及び

アノードコンタクト、

を含む少なくとも1つのセルを有し、

それぞれのセルが第1ウエル領域内に配され、第1ウエル領域が第2ウエル領域内に配されている、

半導体素子が提供され、

素子は、縦方向で第2ウエル領域及びドリフト領域と交差し、横方向でベース領域及び第1ウエル領域と交差する、細長トレンチを有し、

絶縁膜がトレンチの内表面を実質的に覆うように設けられ、

ゲートがトレンチを実質的に埋めるように絶縁膜上に設けられ、

素子は、素子の動作中に、ベース領域と第1ウエル領域の間の接合における空乏領域が第1ウエル領域と第2ウエル領域の間の接合まで延びることができ、よって第1ウエル領域の電位をアノードコンタクトの電位のいかなる上昇からも実質的に絶縁するように構成される。

【0007】

本発明の第1の実施形態例において、トレンチは横方向で第1ウエル及び第2ウエルと交差するように構成され、この場合、トレンチは、必要に応じて、第2ウエル領域の全厚を貫通してドリフト領域に延び込むことができるか、またはできない。したがって、トレンチは第2ウエル領域に必ずしも延び込めるとは限らないが、延び込む場合には、第2ウエル内で終端することができ、あるいは第2ウエルの全厚を貫通してドリフト領域に延び込むことができる。これは、例えば、所要の素子特性及びプロセス上の制約に依存する。

【0008】

本発明にしたがえば、上で定めた半導体素子を作製する、

第2導電型の半導体層内に第2ウエル領域を、残余半導体層がドリフト領域を形成するように、形成する工程、

第2ウエル領域内に第1ウエル領域を形成する工程、

第1ウエル領域内にベース領域を形成する工程、及び

カソード領域を形成する工程、

を含む方法も提供し、方法はさらに、

細長トレンチを、縦方向で第2ウエル領域及びドリフト領域と交差し、横方向でベース領域及び第1ウエル領域と交差するように、形成する工程、

を含む。

【0009】

本発明の一実施形態例において、方法はさらに、

複数の、請求項1に記載の半導体素子を一枚の半導体基板上に形成する工程、素子は1つ以上の実質的に平行な列をなして配置される、及び

それぞれのトレンチが縦方向で第2ウエル領域及びドリフト領域と交差し、横方向で少なくとも1つの半導体素子のベース領域及び第1ウエル領域と交差するように、半導体素子の1つ以上の列に実質的に直交して通る、実質的に平行な列をなす、複数本の細長トレンチを形成する工程、

を含む。

10

20

30

40

50

**【0010】**

少なくとも1本のトレンチは横方向でそれぞれの半導体素子の第1ウエル領域及び第2ウエル領域と交差するように構成することができるが、それらのトレンチは第2のウエル領域の全厚を貫通しないことが好ましい。

**【0011】**

方法はさらに、それぞれのトレンチの内表面上に絶縁層を形成する工程及びそれぞれのトレンチを実質的に埋めるように構成されたゲートを形成する工程を含むことができる。

**【0012】**

本発明の一実施形態例において、それぞれの素子または少なくとも1つの素子列は作動するように構成することができる。

10

**【0013】**

しかし、本発明の別の例においては、一部の素子だけが作動するように構成することができ、残余不作動素子はダミーセルと指定される。例えば、一つおきの素子列のそれぞれの素子は作動するように構成することができ、残余素子列の素子はダミーセルと指定される。

**【0014】**

本発明の範囲は、実質的に平行な素子列をなして配置された、上に定められたような複数の半導体素子を有し、半導体素子列に実質的に直交する、実質的に平行な列をなして配置された複数本のトレンチを含み、それぞれのトレンチが、それぞれの素子列の素子の、縦方向で第2ウエル領域及びドリフト領域と交差し、横方向で少なくとも1つの半導体素子のベース領域、第1ウエル領域及び第2ウエル領域と交差するように構成されて、絶縁膜がトレンチの内の少なくとも1本の内表面を実質的に覆うように設けられ、ゲートが少なくとも1本のそのようなトレンチを実質的に埋めるように絶縁膜上に形成されている、半導体構造に及ぶ。

20

**【図面の簡単な説明】****【0015】**

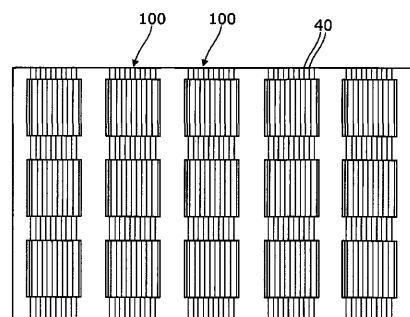

【図1a】図1aは、本発明の一実施形態例にしたがう、カソード構造の簡略な部分前断面図である。

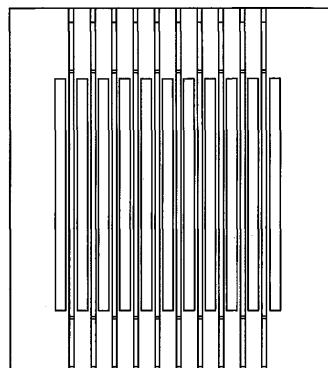

【図1b】図1bは本発明の一実施形態例にしたがう、ダミートレンチを有するカソード構造の簡略な部分側断面図である。

30

【図1c】図1cは複数のカソードセルをもつ構造の簡略な平面図である。

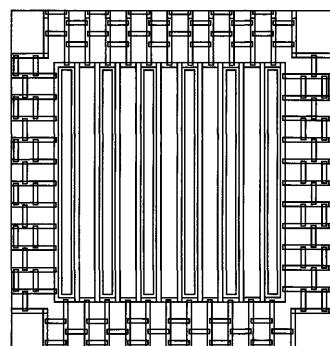

【図2a】図2aは、本発明の一実施形態例にしたがう、カソード配置形状の簡略な平面図である。

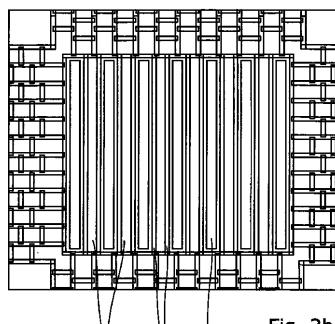

【図2b】図2bは、本発明の別の実施形態例にしたがう、カソード配置形状の簡略な平面図である。

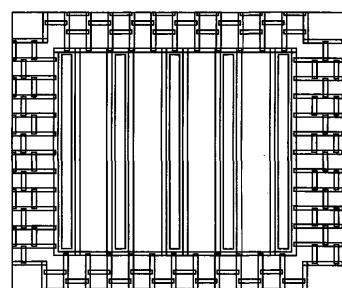

【図2c】図2cは、本発明のまた別の実施形態例にしたがう、カソード配置形状の簡略な平面図である。

【図2d】図2dは、本発明のまた別の実施形態例にしたがう、カソード配置形状の簡略な平面図である。

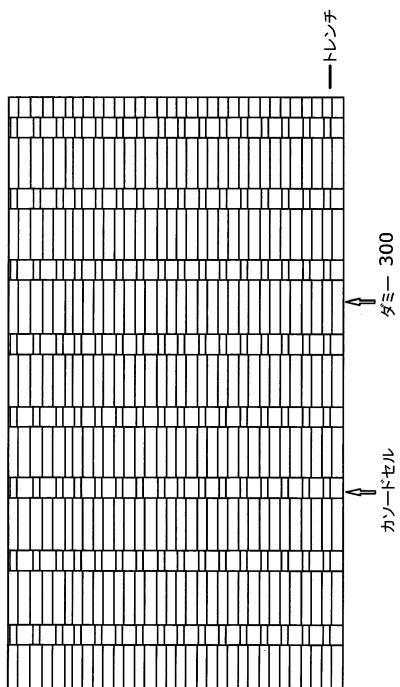

【図2e】図2eは、本発明のまた別の実施形態例にしたがう、カソード配置形状の簡略な平面図である。

40

【図2f】図2fは複数のカソードセルをもつ構造の、单一基板上に複数のカソードセルをどのようにしてまとめて構築できるかを説明する、平面図である。

【図2g】図2gは、明確にするため、接続トレンチが省略されている、図2aの配置形状の平面図である。

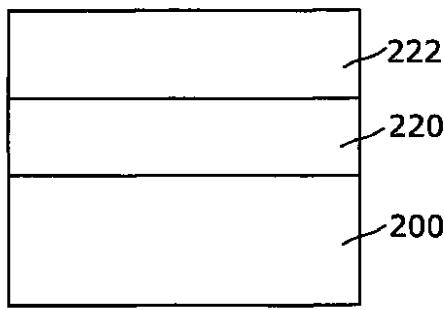

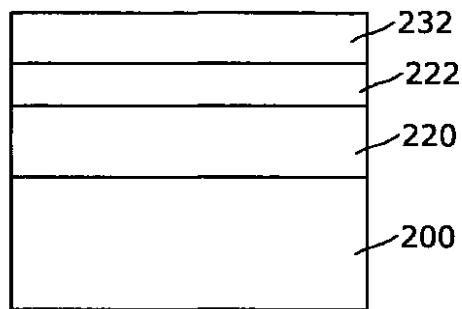

【図3a】図3aは、本発明の一実施形態例にしたがう、素子の作製プロセスの様々な段階の一つを説明する簡略な断面図である。

【図3b】図3bは、本発明の一実施形態例にしたがう、素子の作製プロセスの様々な段階の一つを説明する簡略な断面図である。

【図3c】図3cは、本発明の一実施形態例にしたがう、素子の作製プロセスの様々な段階の一つを説明する簡略な断面図である。

50

階の一つを説明する簡略な断面図である。

【図3d】図3dは、本発明の一実施形態例にしたがう、素子の作製プロセスの様々な段階の一つを説明する簡略な断面図である。

【図3e】図3eは、本発明の一実施形態例にしたがう、素子の作製プロセスの様々な段階の一つを説明する簡略な断面図である。

【図3f】図3fは、トレンチの構成を説明するための、本発明の一実施形態例にしたがう素子の単セルの簡略な平面図である。

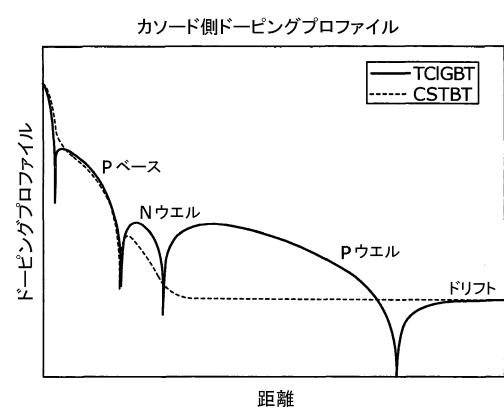

【図4】図4は本発明の一実施形態例にしたがう素子の相対ドーピングプロファイルを示す。

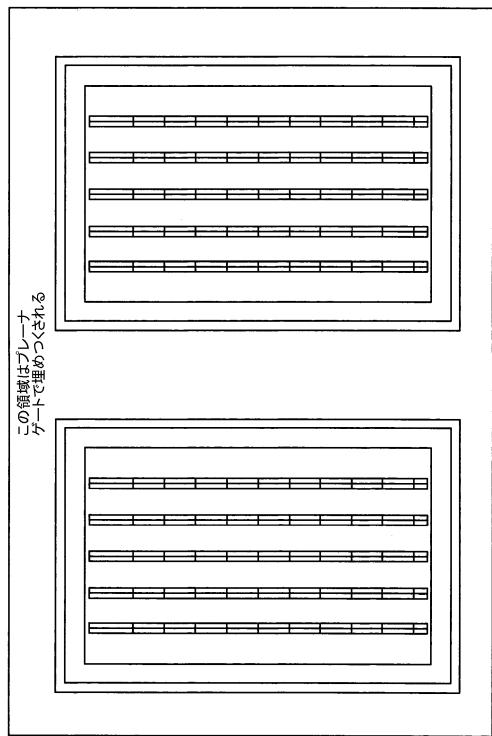

【図5】図5は、クラスターを接続するためのプレーナゲートの使用を示す、本発明の一実施形態例にしたがう構造を示す。

【発明を実施するための形態】

【0016】

本発明の一実施形態例を、単なる例として、添付図面を参照してここで説明する。

【0017】

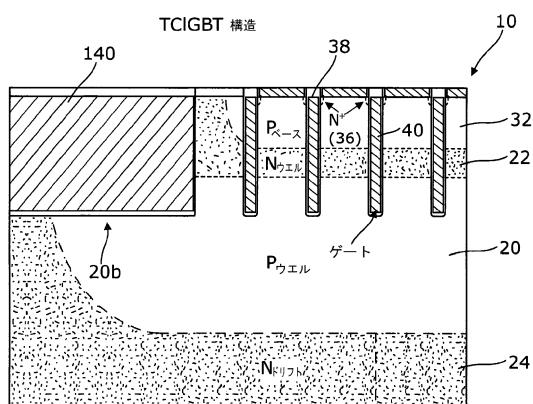

図面の図1aを参照する。図1aでは、本発明の一実施形態例にしたがって作製されたセルの内部構造を説明するために、コンタクト層、アノード領域及びアノードコンタクトが、またカソード領域も、省略されている。したがって、図1aは、一般には単結晶シリコンの、半導体材料の基体の一部10を示す。素子は、上表面にカソードセルのパターンを設けるためにそれを通して拡散がなされるN型シリコンから作製された、NPT(非パンチスルー)素子である。PT(パンチスルー)技術及び/またはフィールドストップ(FS)技術も本発明の範囲内にある。

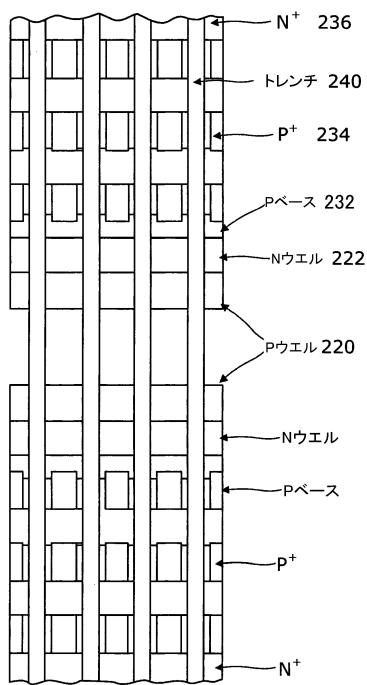

【0018】

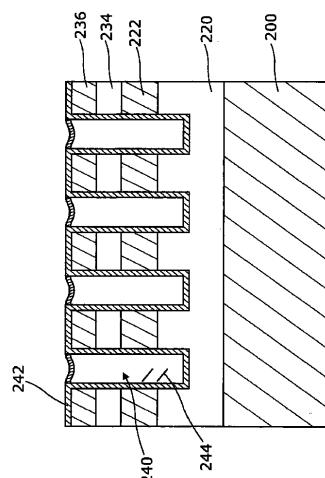

素子構造は、Pウエル20が拡散でつくり込まれるNドリフト領域24を有する。素子は、Pウエル内に垂直方向にも水平方向にも広がり、したがって、使用において、主電流経路内に広がるであろう、P領域20bを残すように、Pウエル20内に拡散でつくり込まれるNウエル22をさらに有する。領域20bはMOSFETゲート140が上に重なるチャネルを与える。図1a, 1b及び1cにおいて、ゲート酸化物は黒地で示される。

【0019】

Nウエル22内に、カソードセルのクラスターが、トレンチで分離されて、設けられる。それぞれのセルは構造が同じであり、よってそれらの内の1つだけが詳細に説明される。すなわち、それぞれのセルはNウエル22内に拡散でつくり込まれた浅いPベース32を有する。

【0020】

本発明の一実施形態にしたがう素子に対する相対ドーピングプロファイルが図面の図4に示される。

【0021】

拡散は全て、例えば複数の通常のリソグラフィ工程を用い、上表面を通してなされる。これらの拡散を達成するために用いられる特定のプロセスは本発明に必須ではなく、拡散領域を得るためにいざれか既知のプロセスを用いることができ、したがって、そのプロセスのいかなる詳細もこれ以上説明されることはない。しかし、これらの領域に選択的にまたはそうではないに關わる、エピタキシーのような、成長プロセスでこの素子構造を形成することが可能であり、このプロセスが、特に炭化シリコン素子のような広バンドギャップ素子に、ただし排他的ではないに、適用可能であることは、当業者によって認められるであろう。

【0022】

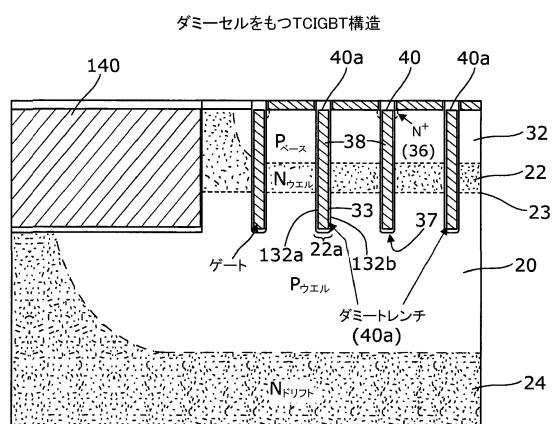

図面の図1bを次に参照すれば、先述したように、Nウエルはカソードセルのクラスターを收め、それぞれのセルは同じ対称構造を有する。セルは、それぞれのセルのゲート構造によって交差される単Pベース領域32に形成される。ゲート構造は、表面26からエッチングで掘り込まれ、表面からPウエル領域20に延び込む、トレンチ40を有する。

10

20

30

40

50

別の実施形態において、トレンチ 4 0 は N ウエル領域にしか延び込まないか、あるいは P ウエルの厚さを貫通してドレンイン領域 2 0 に延び込む。多結晶シリコンゲート 3 8 がトレンチ内に配され、ゲート酸化物 3 3 によって隣接するシリコン材料から絶縁される。

#### 【 0 0 2 3 】

本発明の一実施形態例において、トレンチゲートの形成後、P<sup>+</sup>領域 3 4 が選択拡散によって P ベース 3 2 につくり込まれ、次いで、N<sup>+</sup>カソード領域 3 6 が拡散で P<sup>+</sup>領域 3 4 につくり込まれる。カソード領域は P<sup>+</sup>ベース領域 3 4 と非整流性接合を形成する。別の実施形態例において、P<sup>+</sup>領域 3 4 及びカソード領域 3 6 はトレンチ 4 0 の形成前に形成され、よって、P<sup>+</sup>領域 3 4 及びカソード領域 3 6 を、また P ベース領域 3 2 及び N ウエル 2 2 も、貫通するようにトレンチを形成することができる。

10

#### 【 0 0 2 4 】

したがって、いずれの場合にも、表面に隣接して、N<sup>+</sup>領域 3 6 がベース材料 3 2 内に形成される。領域 1 3 2 a 及び 1 3 2 b はそれぞれ、各々が P ウエル 2 0 の領域 1 2 2 にソース 3 6 及びドレンインを有する、MOSFET のチャネルをゲートによって与える。ゲートは P ウエルに被着されたカソード / ソースコンタクト金属膜 (140 : 図 1 a) からの電気伝導を制御する。図 1 b において、カソードコンタクトはそれぞれのソース領域 3 6 まで広がる金属膜によって与えられ、表面 2 6 においてコンタクトは N<sup>+</sup>領域 3 6 と P ベース 3 4 の間の PN 接合をまたぐことに気付くであろう。

#### 【 0 0 2 5 】

P<sup>+</sup>アノード領域 1 4 がドリフト領域 2 4 の下表面上に形成され、アノードコンタクト 1 6 がアノード領域 1 4 につくられる。

20

#### 【 0 0 2 6 】

いくつかの場合、カソードセルの N ウエルと隣接セルの N ウエルの間の離隔を大きくするため、構造内にいわゆる「ダミーセル」を設けることが必要になり得る。これは図 1 b に示されるように単に 1 つのセルを含めることにより、ただしそのセルをフローティングのままにするかまたは接地し、したがって不作動にすることによって達成され得る。ダミーセルにおいて、n<sup>+</sup>領域はない。それゆえ、ダミーセルをカソードに接続してもしなくても差し支えない。これらのダミーセルはクラスター内に離ればなれに分散させることができる。さらに、作動セル内のいくつかのトレンチ 4 0 a は「ダミートレンチ」と指定することができる。これは図 1 b の構成において、単にダミートレンチとして指定されたトレンチに対するカソードコンタクト 3 7 を省略して、それらを休止状態または不作動のままにすることによって達成される。構造内のダミーセルの数及び作動セル内のダミートレンチの数は、設計、用いられる製造プロセス及び所要の素子特性に依存する。しかし、カソードセル構造におけるダミーセルの使用により、オン状態損失とターンオフ損失の間のトレードオフを改善され得ることが示されている。上述したように、ダミーセルはフローティングのままにするかまたは接地することができる。ダミーセル及びダミートレンチはまとめて接地するかまたはフローティングのままにしておくことができる。ダミートレンチもフローティングのままにしておくことができる。

30

#### 【 0 0 2 7 】

上述した素子に用いるための可能な多くの様々なトレンチ構成が思い描かれる。図面の図 2 a、2 b、2 c、2 d 及び 2 e をここで参照すれば、4 つの異なる可能なストライプ型カソード配置形状が示されている。図 2 a は、全カソードが「活」コンポーネントであるように、100% がコンタクトであり、軸に沿ってダミーコンポーネントが全く設けられていない、ストライプ型構造を示す。これは、(他のカソードクラスターへの)接続トレンチが省略されている、図面の図 2 g に一層明確に示される。図 2 b は活性セル毎に 1 つのダミーセルがある場合を示し、トレンチ 4 0 間の黒地領域 3 0 0 がダミー領域である。図示される構成において、ダミーは Y 軸に沿って配置される。図 2 c は単位トレンチ毎に 2 つのダミーがある場合を示し、図 2 d は単位トレンチ毎に 3 つのダミーがある場合を示す。

40

#### 【 0 0 2 8 】

50

図2eはダミー300がトレンチ40に直交して配置されている場合を示す。

【0029】

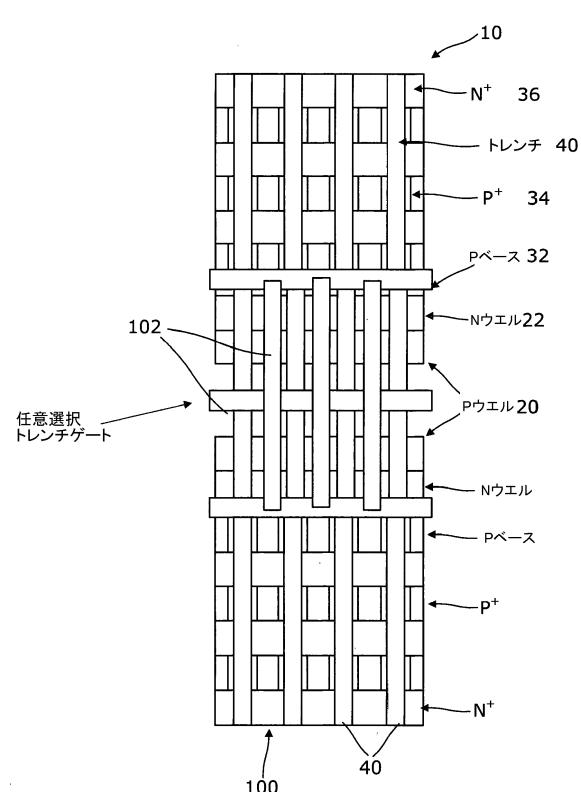

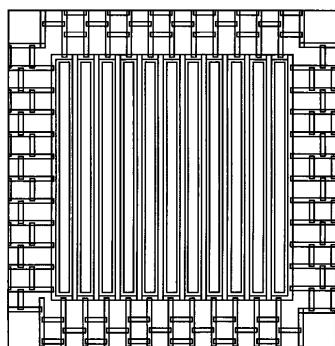

カソードクラスターはまとめて構築することができる。例えば、図面の図1c及び2fを参照すれば、カソードセルのブロック100間に複数本の平行「ストライプ」またはトレンチ40があるストライプ型構成が示され、それぞれのセルにはゲートコンタクト(図示せず)のセットが与えられ、それぞれのセルはゲートコンタクトにより、トレンチ102を介して、電源に接続される。これらの接続トレンチが図示される様で、すなわち縦方向及び/または横方向にデバイスにかかるように、構成される必要はないことは了解されるであろう-多数の別の構成、例えばジグザグパターンが思い浮かび、本発明はこの点に関して全く限定されない。用いられる特定の装置の負荷条件に依存して、多くのトレンチゲートをクラスター間に分散させることができる。しかし、図2bにでは「活」ブロック間に広いスペースがあり、図2c及び2dでもスペースはやはり広い。これらのスペースに「ダミー」トレンチは必ずしも必要ではない。しかし、エッチング及びリソグラフィの容易さを含む、作製上の制約により、設計毎にリソグラフィまたはエッチングのマスクを変えなければならなくなることを避けるためには、これが望ましいことであり得る。全ての構成において、図1bに示されるように、同じトレンチが、縦方向でそれぞれの素子のドリフト領域及びPウエル領域と交差し、また横方向でベース領域、Nウエル領域及びPウエル領域とも交差することがわかる。

【0030】

図面の図5に示されるように、クラスターセルを接続するためにプレーナゲートが用いられることは了解されるであろう。

【0031】

図1bをさらに参照すれば、ゲートに閾電圧より大きい正バイアスを印加すると、カソードMOSFETがオンになり、Nドリフト領域24に電子が供給される。アノード電圧がバイポーラ立ち上がり電圧より大きいと、正孔がアノードから注入される。しかし、正孔が直接にカソード領域に流れ込む経路はない。この結果、Pウエル領域20の電位が高くなる。N領域22の濃度は素子の総合性能に重要な役割を果たし、電荷蓄積IGBT(CS-IGBT)の場合のように、正孔に対する障壁を形成するに必要な臨界値より大きい。制御ゲートがオンであれば、Nウエル22はNウエル領域に形成された蓄積領域及びPベース領域32内の反転チャネルを介してカソード電位に結合される。PウエルとNウエルの接合の電位差が内蔵電位より大きくなると、サイリスタが動作し始める事になる。

【0032】

サイリスタがオンになると、Nウエル22/Pウエル20の電位はアノード電圧のさらなる上昇とともに高くなる。この電位上昇によりPベース32/Nウエル22空乏領域が拡大する。Nウエル22の濃度はPベース32の濃度より低いから、空乏領域は主にNウエル領域内に広がる。(ドーピング濃度、Nウエル深さ、Pベース深さ及びMOSチャネル飽和特性によって決定される)ある電圧において、空乏領域はPウエル/Nウエル接合23に接触し、この点において素子はクランプされる。このセルフクランピング機能が、以降のアノード電位のいかなる上昇もPウエル20/Nドリフト領域24だけにかけて降下することを保証する。

【0033】

素子のターンオフ性能はIGBTのターンオフ性能と同様である。制御ゲートがオフになると、セルフクランピングがおこるまで、Pベース32/Nウエル22にかかる電位が上昇する。クランプされてしまうと、Pウエル20の幅が広いという性質がPベース領域32, 34への正孔の有効な収集を可能にする。

【0034】

クラスター化絶縁ゲートバイポーラトランジスタの、Pウエル及びドリフト領域と縦方向に交差し、ベース、Nウエル及びPウエル領域と横方向に交差するように単一の細長トレンチが用いられる、他の構造が思い描かれる事は了解されるであろう。本発明はこの

10

20

30

40

50

点に関して限定されるつもりはない。

【0035】

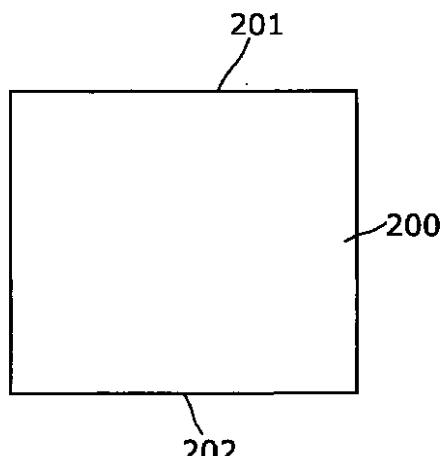

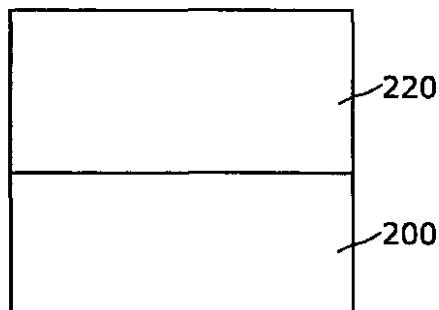

図面の図3aから3hを参照してここで作製プロセスの一例を説明する。すなわち、図3aを参照すれば、プロセスは上表面201及び、上表面201と表裏をなす、下表面202を有するn型半導体200の作製をもって始まる。次に、図3bに示されるように、n型半導体200の上表面201を通して、例えば、フォトリソグラフィ及びイオン注入により、Pウエル層220が形成される。図面の図3cを参照すれば、Pウエル層220内に、同じく構造の上表面201を通して、例えば、フォトリソグラフィ及びイオン注入により、Nウエル層222が形成される。図3dには、Nウエル層222内に、同じく上表面を通して、同じく、例えば、フォトリソグラフィ及びイオン注入を用いて、形成されたPベース層232が見られる。

【0036】

次に図面の図3eを参照すれば、例えば、ドライエッティングにより、ゲートとしてはたらくことになるトレンチ240が選択的に形成される。これらのトレンチ240は横方向にPベース層232、Nウエル層222及びPウエル層220と交差するように形成されるが、トレンチはNウエル領域222内で終端することができ、あるいはPウエル領域220を貫通してドリフト領域に延び込むことができる。トレンチは、図3fの簡略な平面図に示されるように、縦方向に、基板200、Pウエル層220及びNウエル層222とも交差する。一実施形態例において、トレンチゲートの形成後にP<sup>+</sup>層234及びカソード層236が形成されるが、これらの層はトレンチの形成に先立って形成され得る。

【0037】

図3eに戻って参考すれば、トレンチ240の内表面がゲート酸化物（絶縁膜242）で覆われ、トレンチを埋めるようにゲート電極244がゲート酸化膜242上に形成される。ゲート電極244は、例えば、化学的気相成長法（CVD）のような、当業者に既知のいずれか適するプロセスにより、ドープト多結晶シリコンで形成することができる。トレンチ開口を覆って絶縁膜（図示せず）が選択的に形成され、次いで基板の上表面を覆ってカソード電極（図示せず）が形成される。

【0038】

最後に、n型基板200の下表面202上にN<sup>+</sup>バッファ層（図示せず）が、必要であれば、形成され、Pアノード層が形成される。しかし、NPT技術においてバッファ層は必要ではないことが了解されるであろう。

【0039】

素子のそれぞれの領域及び層が形成される様に本発明が限定されるとは決して意図されていないことは了解されるであろう。多くの適する堆積方法、エッティング方法及び注入方法の内のいずれか1つは当業者には明らかであろうし、それらは全て本発明の範囲内に入るとされる。

【符号の説明】

【0040】

|       |                       |

|-------|-----------------------|

| 2 0   | Pウエル                  |

| 2 0 b | P領域                   |

| 2 2   | Nウエル                  |

| 2 3   | Pウエル/Nウエル接合           |

| 2 4   | Nドリフト領域               |

| 2 6   | 表面                    |

| 3 2   | Pベース                  |

| 3 3   | ゲート酸化物                |

| 3 4   | P <sup>+</sup> 領域     |

| 3 6   | N <sup>+</sup> カソード領域 |

| 3 7   | カソードコンタクト             |

| 3 8   | 多結晶シリコンゲート            |

10

20

30

40

50

|                     |                  |

|---------------------|------------------|

| 4 0 , 4 0 a , 1 0 2 | トレンチ             |

| 1 0 0               | カソードセルブロック       |

| 1 3 2 a , 1 3 2 b   | チャネル領域           |

| 1 4 0               | M O S F E T ゲート  |

| 2 0 0               | n型半導体基板          |

| 2 2 0               | P ウエル層           |

| 2 2 2               | N ウエル層           |

| 2 3 2               | P ベース層           |

| 2 3 4               | P <sup>+</sup> 層 |

| 2 3 6               | カソード層            |

| 2 4 0               | トレンチ             |

| 2 4 2               | ゲート酸化膜           |

| 2 4 4               | ゲート電極            |

| 3 0 0               | ダミー領域            |

10

【図 1 a】

【図 1 b】

【図 1 c】

【図 2 a】

Fig. 2a

【図 2 c】

Fig. 2c

【図 2 b】

300 40 37 Fig. 2b

【図 2 d】

Fig. 2d

【図 2 e】

【図 2 f】

Fig. 2f

【図 2 g】

Fig. 2g

【図 3 a】

Fig. 3a

【図 3 b】

Fig. 3b

【図 3 c】

Fig. 3c

【図3d】

Fig. 3d

### 【図3e】

Fig. 3e

【図3f】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 米国特許出願公開第2009/0008674(US, A1)

特開2001-044415(JP, A)

特表2003-509849(JP, A)

特開2012-227335(JP, A)

特開2004-200540(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/749

H01L 29/739

H01L 29/78

H01L 21/336