(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6378515号

(P6378515)

(45) 発行日 平成30年8月22日(2018.8.22)

(24) 登録日 平成30年8月3日(2018.8.3)

(51) Int.Cl.

F 1

**G06F** 9/30 (2018.01)

**G06F** 9/302 (2006.01)

**G06F** 9/38 (2006.01)

**G06F** 9/34 (2006.01)

G06F 9/30 370

G06F 9/302 E

G06F 9/38 350F

G06F 9/38 370X

G06F 9/34 330

請求項の数 10 (全 28 頁) 最終頁に続く

(21) 出願番号

特願2014-63125(P2014-63125)

(22) 出願日

平成26年3月26日(2014.3.26)

(65) 公開番号

特開2015-185076(P2015-185076A)

(43) 公開日

平成27年10月22日(2015.10.22)

審査請求日

平成29年2月24日(2017.2.24)

(73) 特許権者 591128453

株式会社メガチップス

大阪府大阪市淀川区宮原一丁目1番1号

(74) 代理人 100143498

弁理士 中西 健

(74) 代理人 100125704

弁理士 坂根 剛

(74) 代理人 100104444

弁理士 上羽 秀敏

(74) 代理人 100112715

弁理士 松山 隆夫

(74) 代理人 100120662

弁理士 川上 桂子

最終頁に続く

(54) 【発明の名称】 V L I Wプロセッサ

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のレジスタを含むレジスタファイル部と、

第1スロットと、Nビット分(N:自然数)のデータを格納することができるストート

レジスタと、を含む命令実行部と、

を備え、

前記第1スロットは、

前記レジスタファイル部からの出力データを入力するためのN×2ビット(N:自然数)

)の入力ポートと、

前記レジスタファイル部にデータを出力するためのNビットの第1出力ポートと、

前記ストートレジスタにデータを出力するためのNビットの第2出力ポートと、

Nビットデータに対して演算処理を行うことで、2×Nビットデータの出力データを取

得する第1スロット用第1拡張演算ユニットと、

を含み、

前記第1スロット用第1拡張演算ユニットにより取得された2×Nビットデータの前記

出力データのうちのNビット分のデータを、第1データとして、前記第1出力ポートから

前記レジスタファイル部に出力し、

前記第1スロット用第1拡張演算ユニットにより取得された2×Nビットデータの前記

出力データのうちの前記第1データを除くNビット分のデータを、第2データとして、前

記ストートレジスタに出力し、

10

20

前記命令実行部は、

前記レジスタファイル部からの出力データを入力するための  $N \times 2$  ビット (  $N$  : 自然数 ) の入力ポートと、

前記レジスタファイル部にデータを出力するための  $N$  ビットの出力ポートと、

$N$  ビットデータに対して処理の演算を行う第 2 スロット用第 1 演算ユニットと、

を含む第 2 スロットをさらに備え、

前記第 1 スロットは、

前記第 1 スロットから前記レジスタファイル部に出力され、前記レジスタファイル部により保持されている前記第 1 データを入力し、

前記ステートレジスタは、

10

前記第 1 スロットから出力された前記第 2 データを、前記第 2 スロットに出力し、

前記第 2 スロットは、

前記レジスタファイル部から出力されるデータ、および、前記ステートレジスタから出力されるデータのいずれか一方のデータを選択し、選択したデータを前記第 2 スロット用第 1 演算ユニットに入力させる第 2 スロット用選択部をさらに含み、

前記第 1 スロットは、 $N$  ビットデータに対して処理の演算を行う第 1 スロット用第 1 演算ユニットをさらに含み、

前記第 1 スロット用第 1 拡張演算ユニットは、2 つの  $N$  ビットデータに対して、乗算処理を行う第 1 スロット用乗算ユニットであり、

前記第 1 データは、前記第 1 スロット用乗算ユニットが乗算処理により取得した  $2 \times N$  ビットデータのうちの下位  $N$  ビットのデータであり、

20

前記第 2 データは、前記第 1 スロット用乗算ユニットが乗算処理により取得した  $2 \times N$  ビットデータのうちの上位  $N$  ビットのデータであり、

前記第 1 スロット用第 1 演算ユニットは、2 つの  $N$  ビットデータに対して、加減算処理を行う第 1 スロット用加減算ユニットであり、

前記第 2 スロット用第 1 演算ユニットは、2 つの  $N$  ビットデータに対して、加減算処理を行う第 2 スロット用加減算ユニットである、

V L I W プロセッサ。

## 【請求項 2】

複数のレジスタを含むレジスタファイル部と、

30

第 1 スロットと、 $N$  ビット分 (  $N$  : 自然数 ) のデータを格納することができるステートレジスタと、を含む命令実行部と、

を備え、

前記第 1 スロットは、

前記レジスタファイル部からの出力データを入力するための  $N \times 2$  ビット (  $N$  : 自然数 ) の入力ポートと、

前記レジスタファイル部にデータを出力するための  $N$  ビットの第 1 出力ポートと、

前記ステートレジスタにデータを出力するための  $N$  ビットの第 2 出力ポートと、

$N$  ビットデータに対して演算処理を行うことで、 $2 \times N$  ビットデータの出力データを取得する第 1 スロット用第 1 拡張演算ユニットと、

を含み、

40

前記第 1 スロット用第 1 拡張演算ユニットにより取得された  $2 \times N$  ビットデータの前記出力データのうちの  $N$  ビット分のデータを、第 1 データとして、前記第 1 出力ポートから前記レジスタファイル部に出力し、

前記第 1 スロット用第 1 拡張演算ユニットにより取得された  $2 \times N$  ビットデータの前記出力データのうちの前記第 1 データを除く  $N$  ビット分のデータを、第 2 データとして、前記ステートレジスタに出力し、

前記命令実行部は、

前記レジスタファイル部からの出力データを入力するための  $N \times 2$  ビット (  $N$  : 自然数 ) の入力ポートと、

50

前記レジスタファイル部にデータを出力するためのNビットの出力ポートと、所定のメモリからデータを取得するロード処理、および、前記所定のメモリにデータを格納するストア処理の少なくとも一方の処理を行うロード／ストアユニットと、を含む第3スロットをさらに含む、

V L I Wプロセッサ。

**【請求項3】**

前記第1スロットは、

前記第1スロットから前記ステートレジスタに出力され、前記ステートレジスタにより保持されている前記第2データを入力するNビットの入力ポートをさらに含む、

請求項1または2に記載のV L I Wプロセッサ。

10

**【請求項4】**

前記第2スロットは、Nビットデータを読み出す読み出し部をさらに含み、

前記第2スロットの前記読み出し部は、前記ステートレジスタから出力されるデータを読み出し、読み出したデータを、前記レジスタファイル部に出力する、

請求項1に記載のV L I Wプロセッサ。

**【請求項5】**

前記ステートレジスタは、保持しているNビットデータを、前記第1スロットに出力し、

前記第1スロットは、

Nビットデータに対して演算処理を行うことで、 $2 \times N$ ビットデータの出力データを取得する第1スロット用第2拡張演算ユニットと、

Nビットデータに対して処理の演算を行う第1スロット用第1演算ユニットと、

前記レジスタファイル部から出力されるデータ、および、前記ステートレジスタから出力されるデータのいずれか一方のデータを選択し、選択したデータを前記第1スロット用第2拡張演算ユニットに入力させる第1スロット用選択部と、

をさらに含む、

請求項1から3のいずれかに記載のV L I Wプロセッサ。

20

**【請求項6】**

前記第1スロット用第2拡張演算ユニットは、2つのNビットデータに対して、シフト演算を行い、 $2 \times N$ ビットデータの出力データを取得する第1スロット用シフト演算ユニットである、

30

請求項5に記載のV L I Wプロセッサ。

**【請求項7】**

前記第1スロット用シフト演算ユニットは、

シフト演算の処理対象のデータの上位Nビットデータを、前記第1スロット用選択部から出力されるデータとして、シフト演算を行う、

請求項6に記載のV L I Wプロセッサ。

**【請求項8】**

前記レジスタファイル部は、

前記第1スロット用加減算ユニットの加減算処理により取得されるキャリーフラグを格納する領域を有しており、

40

前記第2スロット用加減算ユニットは、前記レジスタファイル部に格納されている前記キャリーフラグを用いて、2つのNビットデータに対して、加減算処理を行う、

請求項1に記載のV L I Wプロセッサ。

**【請求項9】**

前記第2スロット用加減算ユニットは、

加減算処理の処理対象の一方のNビットデータを、前記第2スロット用選択部から出力されるデータとして、加減算処理を行う、

請求項1に記載のV L I Wプロセッサ。

**【請求項10】**

50

前記第1データは、前記第1スロット用第1拡張演算ユニットにより取得された $2 \times N$ ビットデータの前記出力データのうちの下位Nビット分のデータであり、

前記第2データは、前記第1スロット用第1拡張演算ユニットにより取得された $2 \times N$ ビットデータの前記出力データのうちの上位Nビット分のデータである、

請求項1から9のいずれかに記載のVLIWプロセッサ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、VLIW(Very long instruction word)アーキテクチャを採用するプロセッサ( VLIWプロセッサ )に関する。 10

【背景技術】

【0002】

画像データのような大容量データに対して効率良く演算処理を行うために、多様なプロセッサ技術が開発されている。

【0003】

例えば、特許文献1には、グラフィックス処理用の画像処理プロセッサであって、ロード/ストアユニットと、複数の演算ユニットと、複数の演算ユニットの間ににおいて、ある演算ユニットの演算結果を、他の演算ユニットに入力させるための切り替えチャネルとを備える画像処理プロセッサの開示がある。 20

【0004】

ところで、従来のプロセッサにおいて、画像処理や画像認識処理を実行する場合、主として、8ビットあるいは16ビット単位での演算が実行されていた。近年、画像処理や画像認識処理の高度化・複雑化に伴い、画像処理や画像認識処理を実行するためのプロセッサでは、32ビット単位の演算を実行する割合が大幅に増えてきている。 20

【0005】

これに伴い、8ビットあるいは16ビット単位での演算だけでなく、32ビット単位の演算にも対応可能なプロセッサ( VLIWプロセッサ )が求められている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003-216943号公報 30

【発明の概要】

【発明が解決しようとする課題】

【0007】

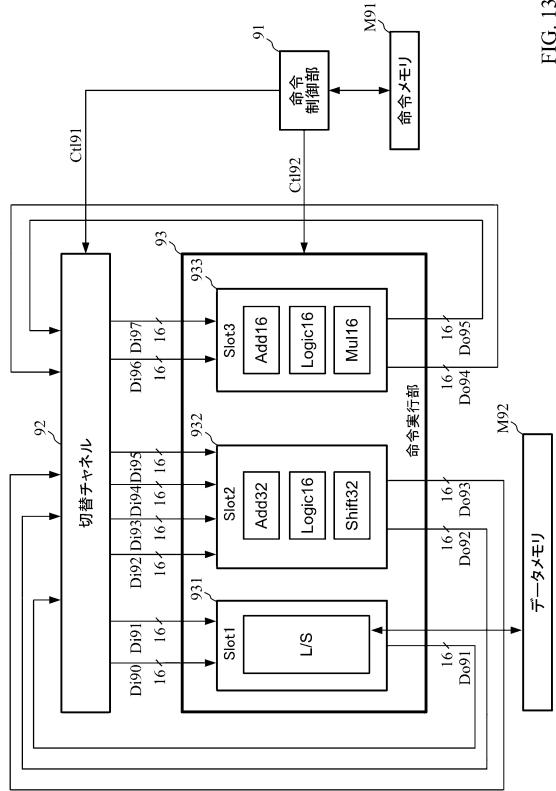

例えば、特許文献1の技術を用いて、16ビット単位での演算だけでなく、32ビット単位の演算にも対応可能なプロセッサを構成する場合、図13に示すような構成が考えられる。

【0008】

図13は、従来技術を用いて構成した32ビット単位の演算にも対応可能なプロセッサ900の概略構成図である。 40

【0009】

図13に示すように、プロセッサ900は、命令制御部91と、切替チャネル92と、命令実行部93と、命令メモリM91と、データメモリM92とを備える。

【0010】

命令制御部91は、命令メモリM91から命令を読み出し(命令フェッチ処理を行い)、読み出した命令をデコードする(命令デコード処理を行う)。そして、命令制御部91は、命令デコード処理の結果に基づいて、切替チャネル92および命令実行部93に対する制御を行う。

【0011】

命令実行部93は、1サイクル(1クロックサイクル)で複数の命令を同時実行するた 50

めに、1サイクルで同時に演算可能な複数の命令スロットを備える。命令実行部93は、図13に示すように、3つのスロット、すなわち、第1スロット931、第2スロット932、および、第3スロット933を有している。

**【0012】**

第1スロット931は、データメモリM92に対してデータのロード／ストアを行うロード／ストアユニットを有している。

**【0013】**

第2スロット932は、32ビット演算を行う加算ユニット（図13に「Add32」で示したユニット）と、16ビット演算を行う論理演算ユニット（図13に「Logic16」で示したユニット）と、32ビット演算を行うシフト演算ユニット（図13に「Shift32」で示したユニット）とを有している。

10

**【0014】**

第3スロット933は、16ビット演算を行う加算ユニット（図13に「Add16」で示したユニット）と、16ビット演算を行う論理演算ユニット（図13に「Logic16」で示したユニット）と、16ビット演算を行う乗算ユニット（図13に「Mul16」で示したユニット）とを有している。

**【0015】**

命令メモリM91は、プロセッサ900で、演算を実行するための命令等を記憶する記憶装置である。

**【0016】**

データメモリM92は、プロセッサ900で、演算を実行するためのデータ等を記憶することができる記憶装置である。

20

**【0017】**

図13から分かるように、プロセッサ900では、第2スロット932に、32ビット演算を行うユニットを設けたので、切替チャネル92から、第2スロット932に、32ビットのデータを2つ分送信する必要がある。例えば、加算ユニットAdd16にて、32ビットデータの加算演算を行う場合、2つの32ビットデータが必要となる。このため、プロセッサ900では、図13に示すように、切替チャネル92と第2スロット932との間に16ビットデータの転送用バスが4つ（データバスDi92～Di95）必要となる。つまり、プロセッサ900において、切替チャネル92と第2スロット932との間に、64ビット分のデータバスが必要となる。

30

**【0018】**

また、第2スロット932で32ビット演算が実行された場合、その出力結果は、32ビットデータとなるため、当該出力結果を、第2スロット932から切替チャネル92に送信するために、32ビット分のデータバスが必要となる。図13では、16ビットのデータ転送用のデータバスDo92、Do93により、第2スロット932から切替チャネル92に送信するために、32ビット分のデータバスを確保している。

**【0019】**

また、プロセッサ900では、第3スロット933に、出力結果が32ビットとなる16ビットデータの乗算を行う乗算ユニットMul16を設けたので、当該出力結果を、第3スロット933から切替チャネル92に送信するために、32ビット分のデータバスが必要となる。図13では、16ビットのデータ転送用のデータバスDo94、Do95により、第3スロット933から切替チャネル92に送信するために、32ビット分のデータバスを確保している。

40

**【0020】**

このように、従来技術を用いて、32ビット単位の演算にも対応可能なプロセッサ900を構成した場合、切替チャネル92と命令実行部93との間に設置しなければならない入出力ポート数が多くなり、回路規模の増大を招く。また、切替チャネル92を、例えば、汎用レジスタファイルに置換する構成も考えられるが、この場合であっても、汎用レジスタファイルと命令実行部93との間に設置しなければならない入出力ポート数が多くな

50

り、回路規模の増大を招く。

【0021】

そこで、本発明は、上記問題点に鑑み、回路規模の増大を抑えつつ、画像処理、画像認識処理等で多用される命令フローのようにビット拡張された演算を含む場合であっても、効率良く処理を実行することができるVLIWプロセッサを実現することを目的とする。

【課題を解決するための手段】

【0022】

上記課題を解決するために、第1の発明は、レジスタファイル部と、命令実行部と、を備えるVLIWプロセッサである。

【0023】

命令実行部は、第1スロットと、Nビット分（N：自然数）のデータを格納することができるステートレジスタと、を含む。

【0024】

第1スロットは、レジスタファイル部からの出力データを入力するためのN×2ビット（N：自然数）の入力ポートと、レジスタファイル部にデータを出力するためのNビットの第1出力ポートと、ステートレジスタにデータを出力するためのNビットの第2出力ポートと、を含む。また、第1スロットは、Nビットデータに対して演算処理を行うことでの、2×Nビットデータの出力データを取得する第1スロット用第1拡張演算ユニットを含む。

【0025】

そして、第1スロットは、第1スロット用第1拡張演算ユニットにより取得された2×Nビットデータの出力データのうちのNビット分のデータを、第1データとして、第1出力ポートからレジスタファイル部に出力し、第1スロット用第1拡張演算ユニットにより取得された2×Nビットデータの出力データのうちの第1データを除くNビット分のデータを、第2データとして、前記ステートレジスタに出力する。

【0026】

このVLIWプロセッサでは、第1スロットが、第1スロット用第1拡張演算ユニットにより取得された2×Nビットデータを、Nビットずつに分けた2つのデータとして、レジスタファイル部およびステートレジスタに出力する。つまり、このVLIWプロセッサでは、処理対象が2×Nビットデータとなる2×Nビット演算を実行する場合であっても、当該2×NビットデータのうちのNビットデータが、ステートレジスタにより、保持され、例えば、次のサイクル（クロックサイクル）において、所定の演算ユニットにより利用することができる。

【0027】

また、このVLIWプロセッサでは、第1スロットにおいて、レジスタファイル部からの入力ポートは、N×2ビット（N×2ビット分の入力ポート）であり、レジスタファイル部への出力ポートは、Nビット（Nビット分の出力ポート）であるため、VLIWプロセッサが、Nビット演算のみを実行する場合に比べて、入出力ポート数を増やす必要がない。

【0028】

このように、VLIWプロセッサでは、上記の通り、レジスタファイル部の入出力ポート数を増加させることなく、2×Nビットの演算をサポートすることが可能となる。

【0029】

したがって、VLIWプロセッサでは、回路規模の増大を抑えつつ、画像処理、画像認識処理等で多用される命令フローのようにビット拡張された演算（N×2ビット演算）を含む場合であっても、効率良く処理を実行することができる。

【0030】

第2の発明は、第1の発明であって、第1スロットは、第1スロットからステートレジスタに出力され、ステートレジスタにより保持されている第2データを入力する。

【0031】

10

20

30

40

50

これにより、このV L I Wプロセッサでは、例えば、1つ前のサイクルにおいて、第1スロットから出力されたNビットデータを、現在のサイクルにおいて、ステートレジスタから第1スロットに入力させ、第1スロットでの演算に用いることができる。

【0032】

第3の発明は、第1の発明であって、命令実行部は、第2スロットをさらに備える。

【0033】

第2スロットは、レジスタファイル部からの出力データを入力するための $N \times 2$ ビット( N : 自然数 )の入力ポートと、レジスタファイル部にデータを出力するための N ビットの出力ポートと、 N ビットデータに対して処理の演算を行う第2スロット用第1演算ユニットと、

10

を含む。

【0034】

そして、第1スロットは、第1スロットから前記レジスタファイル部に出力され、レジスタファイル部により保持されている前記第1データを入力する。

【0035】

ステートレジスタは、第1スロットから出力された第2データを、第2スロットに出力する。

【0036】

これにより、このV L I Wプロセッサでは、例えば、1つ前のサイクルにおいて、第1スロットから出力されたNビットデータを、現在のサイクルにおいて、ステートレジスタから第2スロットに入力させ、第2スロットでの演算に用いることができる。

20

【0037】

第4の発明は、第3の発明であって、第2スロットは、 N ビットデータを読み出す読み出し部をさらに含む。

【0038】

第2スロットの読み出し部は、ステートレジスタから出力されるデータを読み出し、読み出したデータを、レジスタファイル部に出力する。

【0039】

このV L I Wプロセッサでは、第2スロットの読み出し部により、ステートレジスタに保持されているNビットデータを読み出し、所定のタイミングで、レジスタファイル部に出力することができるため、 $2 \times N$ ビットデータを扱う演算が存在していても効率良くレジスタファイル部に所定のデータを出力し、レジスタファイル部において、必要なデータを保持させることができる。

30

【0040】

第5の発明は、第3または第4の発明であって、第2スロットは、レジスタファイル部から出力されるデータ、および、ステートレジスタから出力されるデータのいずれか一方のデータを選択し、選択したデータを第2スロット用第1演算ユニットに入力させる第2スロット用選択部をさらに含む。

【0041】

これにより、このV L I Wプロセッサでは、第2スロット用第1演算ユニットに、レジスタファイル部から出力されるデータ、および、ステートレジスタから出力されるデータのいずれか一方を選択して入力させることができるので、必要なデータを、第2スロット用第1演算ユニットに、入力することができる。例えば、第2スロット用第1演算ユニットが加減算処理を行う演算ユニットである場合、当該演算ユニットを N ビットデータの加減算処理に用いる場合、第1選択部により、レジスタファイル部から出力される 2 つの N ビットデータが入力されるようにすることができる。一方、上記演算ユニットを  $2 \times N$  ビットデータの加減算処理の上位 N ビット分の加減算処理に用いる場合、ステートレジスタに  $2 \times N$  ビットデータのうちの上位 N ビット分のデータ( 例えば、第1スロットの加算演算ユニットで取得された N ビット分のデータ ) を保持し、第2スロット用選択部により、ステートレジスタの出力が上記演算ユニットに入力されるようにし、さらに、当該上位 N

40

50

ビット分のデータと加算する  $2 \times N$  ビットデータの上位  $N$  ビットデータをレジスタファイル部から入力されるようにすればよい。これにより、当該演算ユニットにおいて、 $2 \times N$  ビットデータの加減算処理の上位  $N$  ビットデータの加減算処理を実行することができる。

**【0042】**

第6の発明は、第5の発明であって、第1スロットは、 $N$  ビットデータに対して処理の演算を行う第1スロット用第1演算ユニットをさらに含む。

**【0043】**

第1スロット用第1拡張演算ユニットは、2つの $N$  ビットデータに対して、乗算処理を行う第1スロット用乗算ユニットである。

**【0044】**

第1データは、第1スロット用乗算ユニットが乗算処理により取得した  $2 \times N$  ビットデータのうちの下位  $N$  ビットのデータである。

10

**【0045】**

第2データは、第1スロット用乗算ユニットが乗算処理により取得した  $2 \times N$  ビットデータのうちの上位  $N$  ビットのデータである。

**【0046】**

第1スロット用第1演算ユニットは、2つの $N$  ビットデータに対して、加減算処理を行う第1スロット用加減算ユニットである。

20

**【0047】**

第2スロット用第1演算ユニットは、2つの $N$  ビットデータに対して、加減算処理を行う第2スロット用加減算ユニットである。

**【0048】**

これにより、第1スロットに、 $N$  ビットの乗算を行うユニット（乗算ユニット）と、 $N$  ビットの加減算処理を行うユニット（下位  $N$  ビットデータの加算ユニット）を割り当て、第2スロットに、 $N$  ビットの加減算処理を行うユニット（上位  $N$  ビットデータの加算ユニット）を割り当てることができる。

**【0049】**

第7の発明は、第3から第6のいずれかの発明であって、ステートレジスタは、保持している $N$  ビットデータを、第1スロットに出力する。

30

**【0050】**

第1スロットは、第1スロット用第2拡張演算ユニットと、第1スロット用第1演算ユニットと、第1スロット用選択部と、をさらに含む。

**【0051】**

第1スロット用第2拡張演算ユニットは、 $N$  ビットデータに対して演算処理を行うことで、 $2 \times N$  ビットデータの出力データを取得する。

**【0052】**

第1スロット用第1演算ユニットは、 $N$  ビットデータに対して処理の演算を行う。

**【0053】**

第1スロット用選択部は、レジスタファイル部から出力されるデータ、および、ステートレジスタから出力されるデータのいずれか一方のデータを選択し、選択したデータを第1スロット用第2拡張演算ユニットに入力させる。

40

**【0054】**

これにより、このVLIWプロセッサでは、例えば、1つ前のサイクルにおいて、第1スロットから出力された $N$  ビットデータを、現在のサイクルにおいて、ステートレジスタから第1スロットの第1スロット用第2拡張演算ユニットに入力させ、当該演算ユニットでの演算に用いることができる。

**【0055】**

第8の発明は、第7の発明であって、第1スロット用第2拡張演算ユニットは、2つの $N$  ビットデータに対して、シフト演算を行い、 $2 \times N$  ビットデータの出力データを取得する第1スロット用シフト演算ユニットである。

50

**【 0 0 5 6 】**

これにより、このV L I Wプロセッサでは、第1スロット用シフト演算ユニットにより、例えば、ステートレジスタから出力されたNビットデータと、レジスタファイル部から出力されたNビットデータとを用いて、シフト演算処理を実行することができる。

**【 0 0 5 7 】**

第9の発明は、第8の発明であって、第1スロット用シフト演算ユニットは、シフト演算の処理対象のデータの上位Nビットデータを、第1スロット用選択部から出力されるデータとして、シフト演算を行う。

**【 0 0 5 8 】**

これにより、このV L I Wプロセッサでは、第1スロット用シフト演算ユニットにより、例えば、ステートレジスタから出力されたNビットデータを上位Nビットデータとし、レジスタファイル部から出力されたNビットデータを下位Nビットデータとして、シフト演算処理を実行することができる。 10

**【 0 0 5 9 】**

第10の発明は、第6の発明であって、レジスタファイル部は、第1スロット用加減算ユニットの加減算処理により取得されるキャリーフラグを格納する領域を有している。

**【 0 0 6 0 】**

第2スロット用加減算ユニットは、レジスタファイル部に格納されているキャリーフラグを用いて、2つのNビットデータに対して、加減算処理を行う。 20

**【 0 0 6 1 】**

これにより、このV L I Wプロセッサでは、例えば、第1スロットの演算ユニットでの加減算処理により生成されたキャリーフラグであって、レジスタファイル部に格納されたキャリーフラグを用いて、第2スロット用加減算ユニットが、2つのNビットデータに対する加減算処理を実行することができる。

**【 0 0 6 2 】**

第11の発明は、第6の発明であって、第2スロット用加減算ユニットは、加減算処理の処理対象の一方のNビットデータを、第2スロット用選択部から出力されるデータとして、加減算処理を行う。

**【 0 0 6 3 】**

これにより、第2スロットにおいても、ステートレジスタに保持されているデータを利用することが可能となり、Nビットデータの演算処理（例えば、Nビットデータの加減算処理）および $2 \times N$ ビットの演算処理（拡張演算処理（例えば、 $2 \times N$ ビットデータの加減算処理））を効率良く実行することが可能となる。 30

**【 0 0 6 4 】**

第12の発明は、第1から第11のいずれかの発明であって、命令実行部は、第3スロットをさらに備える。

**【 0 0 6 5 】**

第3スロットは、レジスタファイル部からの出力データを入力するための $N \times 2$ ビット（N：自然数）の入力ポートと、レジスタファイル部にデータを出力するためのNビットの出力ポートと、所定のメモリからデータを取得するロード処理、および、前記所定のメモリにデータを格納するストア処理の少なくとも一方の処理を行うロード／ストアユニットと、を含む。 40

**【 0 0 6 6 】**

これにより、ロード／ストアユニットを含む第3スロットを備えるV L I Wプロセッサを実現することができる。

**【 0 0 6 7 】**

第13の発明は、第1から第12のいずれかの発明であって、第1データは、第1スロット用第1拡張演算ユニットにより取得された $2 \times N$ ビットデータの出力データのうちの下位Nビット分のデータである。

**【 0 0 6 8 】**

10

20

30

40

50

第2データは、第1スロット用第1拡張演算ユニットにより取得された $2 \times N$ ビットデータの出力データのうちの上位Nビット分のデータである。

#### 【0069】

これにより、このVLIWプロセッサでは、第1データ（レジスタファイル部に出力するデータ）を下位Nビットデータとし、第2データ（ステートレジスタに出力するデータ）を上位Nビットデータとして、効率良く演算処理を実行することができる。

#### 【発明の効果】

#### 【0070】

本発明によれば、回路規模の増大を抑えつつ、画像処理、画像認識処理等で多用される命令フローのようにビット拡張された演算を含む場合であっても、効率良く処理を実行することができるVLIWプロセッサを実現することができる。10

#### 【図面の簡単な説明】

#### 【0071】

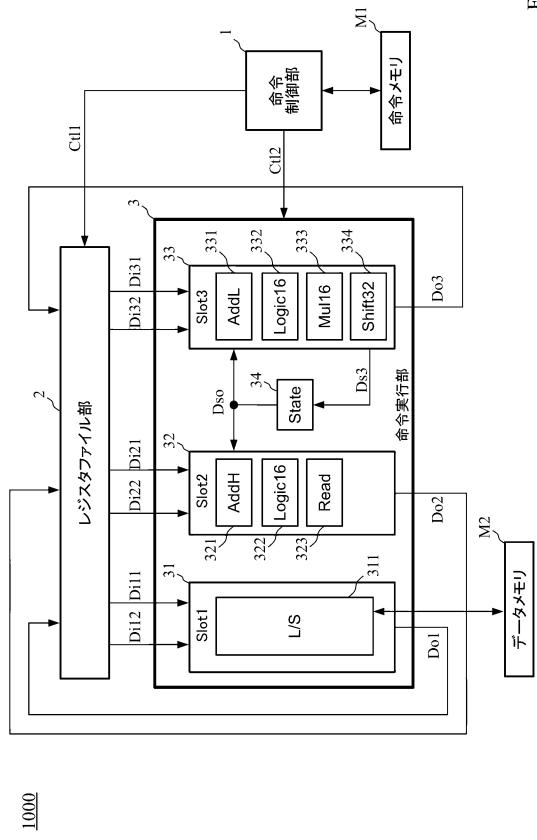

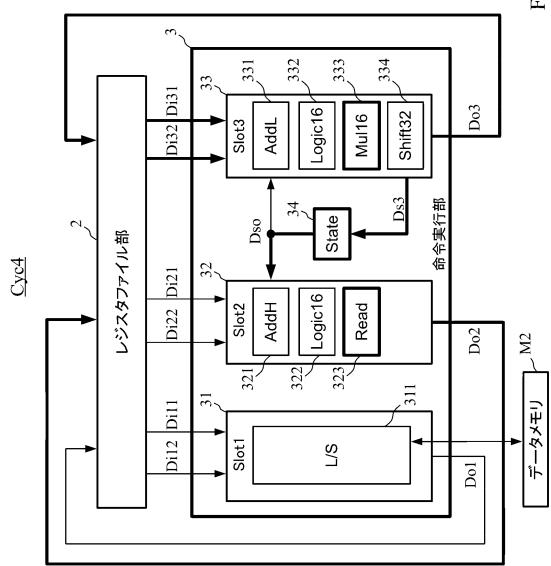

【図1】第1実施形態に係るVLIWプロセッサ1000の概略構成図。

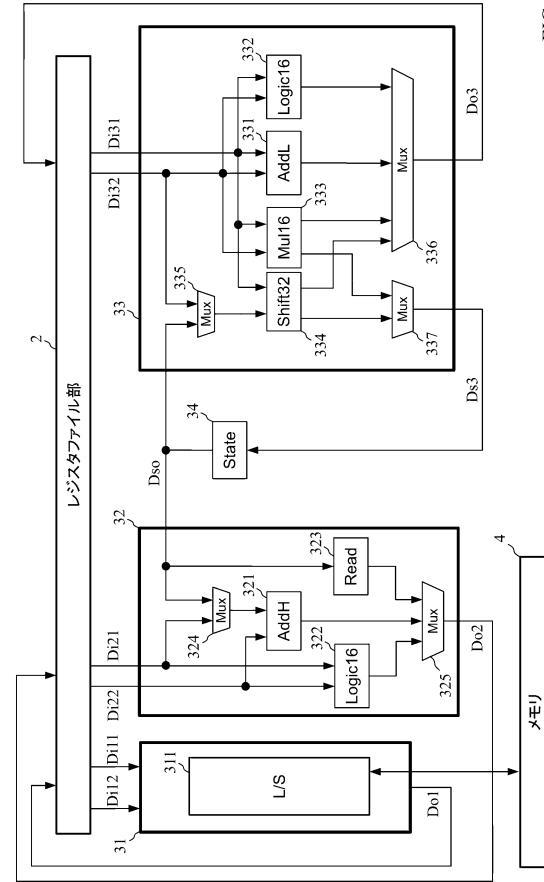

【図2】命令実行部3の構成例（一例）の概略図。

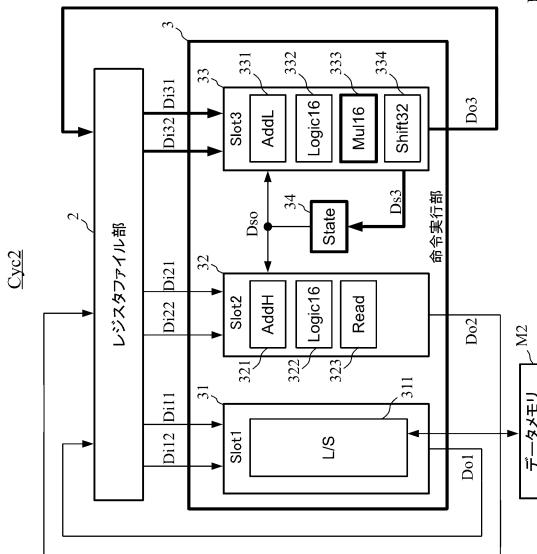

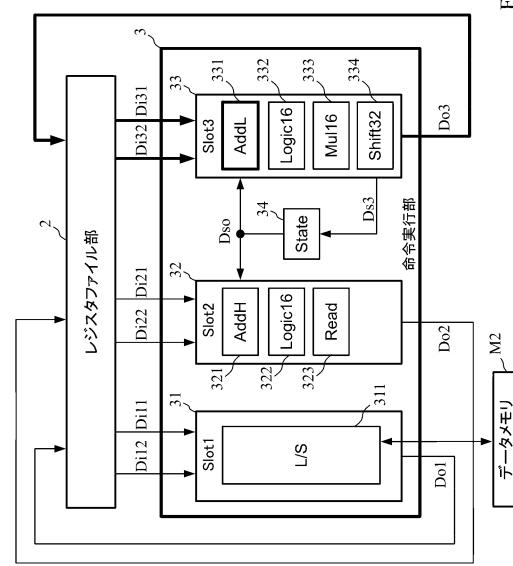

【図3】MulShift処理における各スロットに割り当てられる演算処理を示した図、および、サイクル2においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。10

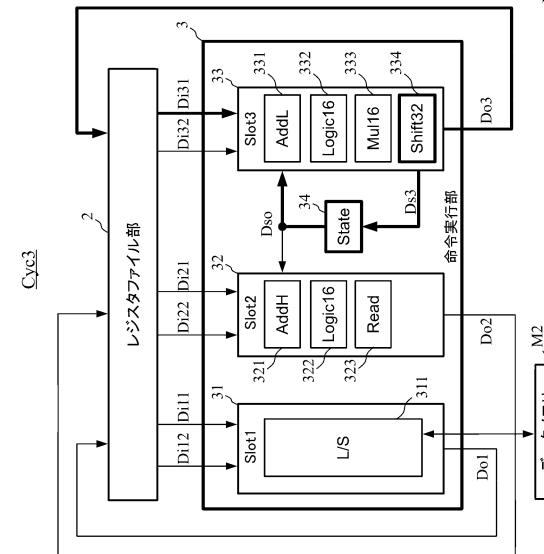

【図4】MulShift処理における各スロットに割り当てられる演算処理を示した図、および、サイクル3においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。20

【図5】MulShift処理における各スロットに割り当てられる演算処理を示した図、および、サイクル4においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。

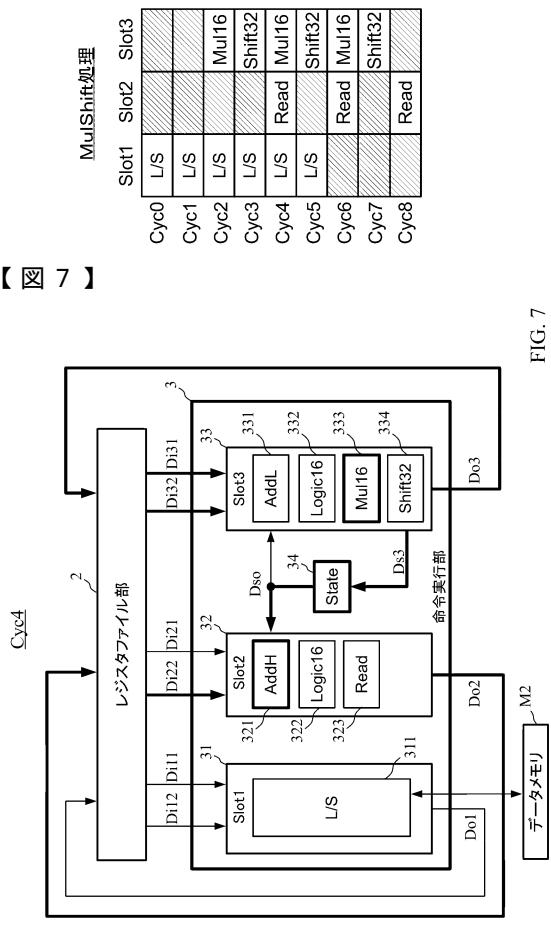

【図6】MulAdd処理における各スロットに割り当てられる演算処理を示した図、および、サイクル3においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。

【図7】MulAdd処理における各スロットに割り当てられる演算処理を示した図、および、サイクル4においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。30

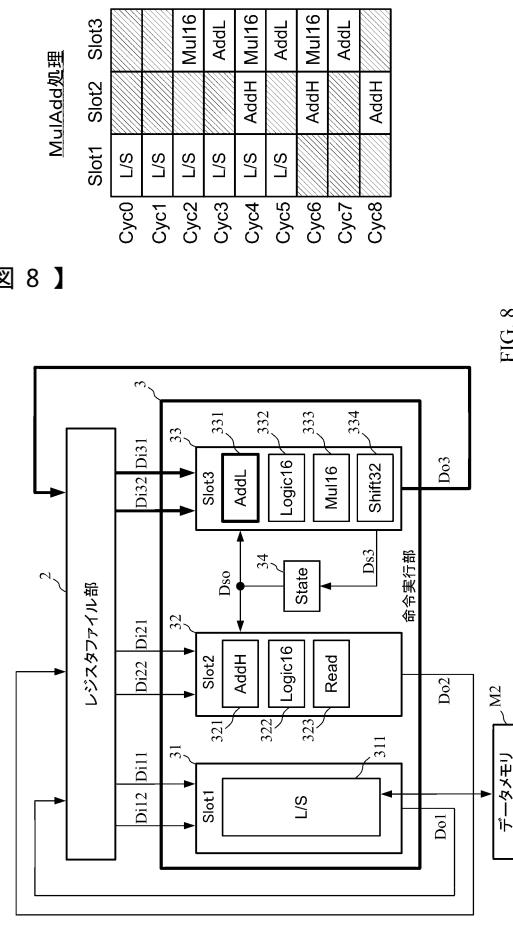

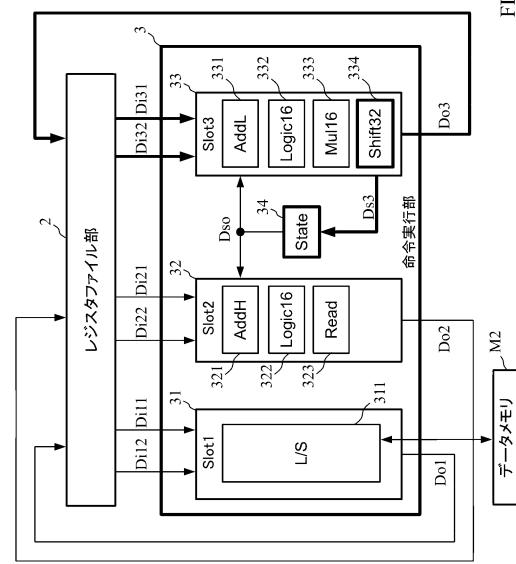

【図8】MulShiftAdd処理における各スロットに割り当てられる演算処理を示した図、および、サイクル4においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。

【図9】MulShiftAdd処理における各スロットに割り当てられる演算処理を示した図、および、サイクル5においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。

【図10】ShiftAdd処理における各スロットに割り当てられる演算処理を示した図、および、サイクル2においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。

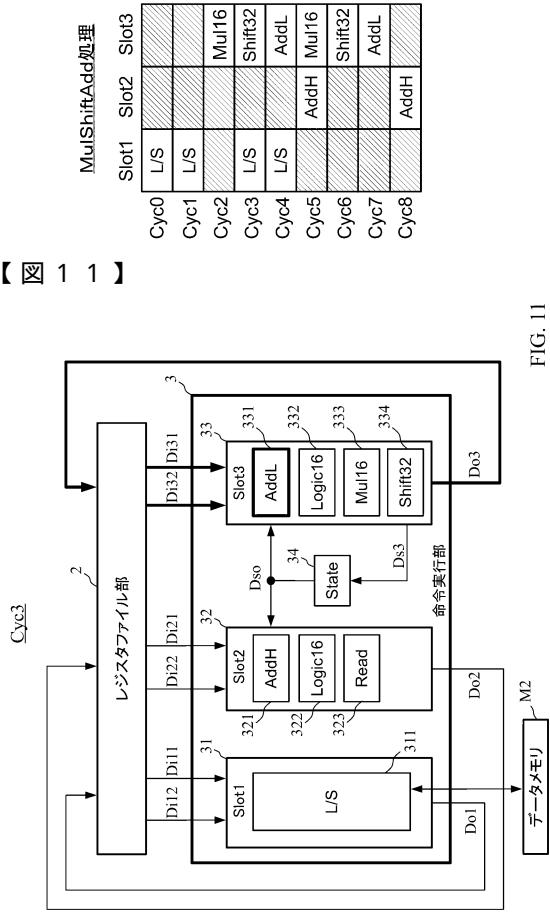

【図11】ShiftAdd処理における各スロットに割り当てられる演算処理を示した図、および、サイクル3においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。40

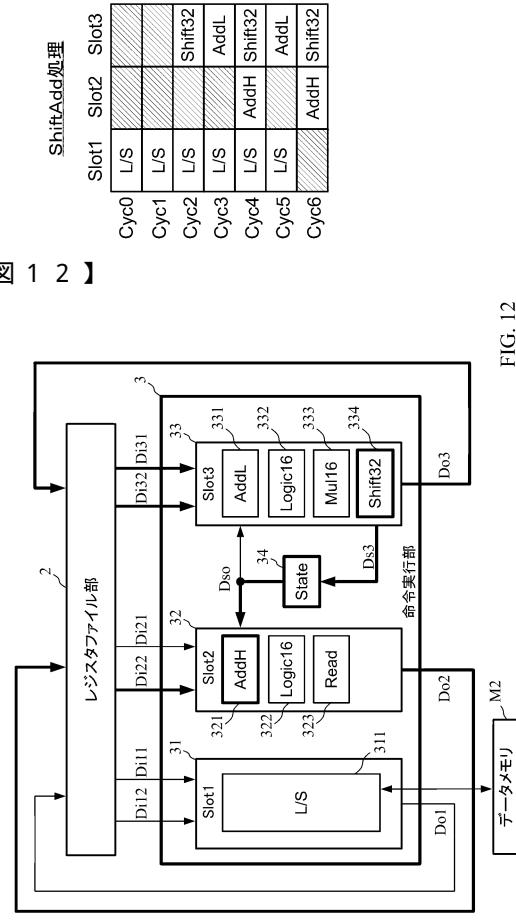

【図12】ShiftAdd処理における各スロットに割り当てられる演算処理を示した図、および、サイクル4においてアクティブになっているVLIWプロセッサ1000の部分を明示した図。

【図13】従来技術を用いて構成した32ビット単位の演算にも対応可能なプロセッサ900の概略構成図。

#### 【発明を実施するための形態】

#### 【0072】

[第1実施形態]

第1実施形態について、図面を参照しながら、以下、説明する。

**【0073】**

<1.1: VLIWプロセッサの構成>

図1は、第1実施形態に係るVLIWプロセッサ1000の概略構成図である。

**【0074】**

VLIWプロセッサ1000は、Nビット(N:自然数)単位の演算、および、 $2 \times N$ ビット単位の演算を行うVLIWプロセッサである。

**【0075】**

なお、以下では、説明便宜のため、 $N = 16$ 、つまり、VLIWプロセッサ1000が、16ビット単位の演算および32ビット単位の演算を行うVLIWプロセッサである場合について、説明する。

10

**【0076】**

VLIWプロセッサ1000は、図1に示すように、命令制御部1と、レジスタファイル部2と、命令実行部3と、命令メモリM1と、データメモリM2とを備える。

**【0077】**

命令制御部1は、命令メモリM1から命令を読み出し(命令フェッチ処理を行い)、読み出した命令をデコードする(命令デコード処理を行う)。そして、命令制御部1は、命令デコード処理の結果に基づいて、レジスタファイル部2を制御するための制御信号Ct11を生成し、生成した制御信号Ct11をレジスタファイル部2に出力する。

20

**【0078】**

また、命令制御部1は、命令デコード処理の結果に基づいて、命令実行部3を制御するための制御信号Ct12を生成し、生成した制御信号Ct12を命令実行部3に出力する。

。

**【0079】**

レジスタファイル部2は、複数のレジスタを有しており、命令制御部1からの制御信号Ct11に基づいて、所定のレジスタのデータを命令実行部3の所定のスロットに出力する。また、レジスタファイル部2は、制御信号Ct11に基づいて、命令実行部3から出力されるデータを、所定のレジスタに入力されるように制御する。

**【0080】**

命令実行部3は、1サイクル(1クロックサイクル)で複数の命令を実行するために、1サイクルで同時に演算可能な複数の命令スロットを備える。以下では、説明便宜のため、命令スロット数が「3」である場合について説明する。

30

**【0081】**

命令実行部3は、図1に示すように、3つのスロット、すなわち、第1スロット31、第2スロット32、および、第3スロット33を有している。また、命令実行部3は、ステートレジスタ34を備える。

**【0082】**

第1スロット31は、データメモリM2に対して16ビットのデータのロード/ストアを行うロード/ストアユニット311を備える。

**【0083】**

第2スロット32は、16ビットデータの加算処理を行う加算ユニット321と、16ビットデータに対して論理演算を行う論理演算ユニット322と、ステートレジスタ34から16ビットデータを読み出すステート読み出しユニット323と、を備える。なお、「加算処理」は、減算処理を含んでもよい。つまり、「加算処理」は、加減算処理であつてもよい(以下、同様)。

40

**【0084】**

第3スロット33は、16ビットデータの加算処理を行う加算ユニット331と、16ビットデータに対して論理演算を行う論理演算ユニット332と、16ビットデータの乗算を行う乗算ユニット333と、32ビットデータに対してビットシフト処理を行うシフト演算ユニット334と、を備える。

50

**【0085】**

ステートレジスタ34は、第3スロット33から出力される16ビットデータを入力し、入力された16ビットデータを記憶保持する。ステートレジスタ34は、保持している16ビットデータを第2スロット32および第3スロット33に出力する。

**【0086】**

ここで、命令実行部3の構成例（一例）について、図2を用いて説明する。

**【0087】**

図2は、命令実行部3の構成例（一例）の概略図である。

**【0088】**

図2に示すように、命令実行部3の第2スロット32は、加算ユニット321と、論理演算ユニット322と、ステート読み出しユニット323と、第1切替部324と、第2切替部325と、を備える。10

**【0089】**

第1切替部324は、レジスタファイル部2から出力される16ビットデータD<sub>i21</sub>と、ステートレジスタ34から出力される16ビットデータD<sub>s0</sub>とを入力とする。第1切替部324は、命令制御部1の指令（制御信号C<sub>t12</sub>）に従い、16ビットデータD<sub>i21</sub>および16ビットデータD<sub>s0</sub>のいずれか一方のデータを加算ユニット321に出力する。

**【0090】**

加算ユニット321は、レジスタファイル部2から出力される16ビットデータD<sub>i22</sub>と、第1切替部324から出力される16ビットデータとを入力とし、入力された2つの16ビットデータに対して加算処理を行う。そして、加算ユニット321は、加算処理後のデータを第2切替部325に出力する。20

**【0091】**

また、加算ユニット321は、32ビット加算処理の上位16ビットの加算処理を実行する場合、16ビットデータD<sub>i22</sub>と第1切替部324から出力される16ビットデータと、例えば、第3スロットの加算ユニット331が生成しレジスタファイル部2のキャリーレジスタ（不図示）に格納されているキャリーフラグ（キャリービット（1ビットデータ））とを入力とし、入力された3つのデータに対して加算処理を行う。そして、加算ユニット321は、加算処理後のデータを第2切替部325に出力する。30

**【0092】**

論理演算ユニット322は、レジスタファイル部2から出力される2つの16ビットデータD<sub>i21</sub>、D<sub>i22</sub>を入力とし、入力された2つの16ビットデータに対して所定の論理演算処理を行う。そして、論理演算ユニット322は、論理演算処理後のデータを第2切替部325に出力する。

**【0093】**

ステート読み出しユニット323は、ステートレジスタ34で保持されている16ビットデータを読み出す。そして、ステート読み出しユニット323は、ステートレジスタ34から読み出したデータを第2切替部325に出力する。

**【0094】**

第2切替部325は、加算ユニット321からの出力、論理演算ユニット322からの出力、および、ステート読み出しユニット323からの出力を入力とする。そして、第2切替部325は、命令制御部1の指令（制御信号C<sub>t12</sub>）に従い、加算ユニット321からの出力、論理演算ユニット322からの出力、および、ステート読み出しユニット323からの出力のいずれかをデータD<sub>o2</sub>として、レジスタファイル部2に出力する。なお、第2切替部325は、加算ユニット321からの出力を選択して、レジスタファイル部2に出力する場合、加算演算のキャリーフラグをデータD<sub>o2</sub>に含めて、レジスタファイル部2に出力するようにしてもよいし、また、別のパスを用いて、加算演算のキャリーフラグを、レジスタファイル部2に出力するようにしてもよい。

**【0095】**

50

図2に示すように、命令実行部3の第3スロット33は、加算ユニット331と、論理演算ユニット332と、乗算ユニット333と、シフト演算ユニット334と、第3切替部335と、第4切替部336と、第5切替部337とを備える。

#### 【0096】

第3切替部335は、レジスタファイル部2から出力される16ビットデータDi32と、ステートレジスタ34から出力される16ビットデータDs0とを入力とする。第3切替部335は、命令制御部1の指令(制御信号Ct12)に従い、16ビットデータDi32および16ビットデータDs0のいずれか一方のデータをシフト演算ユニット334に出力する。

#### 【0097】

加算ユニット331は、レジスタファイル部2から出力される2つの16ビットデータDi31とDi32とを入力とし、入力された2つの16ビットデータに対して加算処理を行う。そして、加算ユニット331は、加算処理後のデータを第4切替部336に出力する。

#### 【0098】

また、加算ユニット331は、32ビット加算処理の下位16ビットの加算処理を実行する場合、16ビットデータDi31と16ビットデータDi32との加算処理により取得されるキャリーフラグ(キャリーピット(1ビットデータ))を、レジスタファイル部2に出力し、例えば、レジスタファイル部2のキャリーレジスタに格納する(出力バスについて不図示)。

#### 【0099】

論理演算ユニット332は、レジスタファイル部2から出力される2つの16ビットデータDi31と、Di32とを入力とし、入力された2つの16ビットデータに対して所定の論理演算処理を行う。そして、論理演算ユニット332は、論理演算処理後のデータを第4切替部336に出力する。

#### 【0100】

乗算ユニット333は、レジスタファイル部2から出力される2つの16ビットデータDi31、Di32を入力とし、入力された2つの16ビットデータに対して乗算処理を行う。そして、乗算ユニット333は、乗算処理後の32ビットデータのうち、下位16ビットデータを第4切替部336に出力し、上位16ビットのデータを第5切替部337に出力する。

#### 【0101】

シフト演算ユニット334は、レジスタファイル部2から出力される16ビットデータDi31と、第3切替部335から出力される16ビットデータとを入力とし、入力された2つの16ビットデータに対してシフト演算処理(32ビットシフト演算処理)を行う。そして、シフト演算ユニット334は、シフト演算処理後の32ビットデータのうち、下位16ビットデータを第4切替部336に出力し、上位16ビットのデータを第5切替部337に出力する。

#### 【0102】

第4切替部336は、加算ユニット331からの出力、論理演算ユニット332からの出力、乗算ユニット333から出力される乗算結果データの下位16ビットデータ、および、シフト演算ユニット334から出力されるシフト演算結果データの下位16ビットデータを入力とする。そして、第4切替部336は、命令制御部1の指令(制御信号Ct12)に従い、上記4つのユニットからの出力のいずれかを選択して、データDo3として、レジスタファイル部2に出力する。

#### 【0103】

なお、第4切替部336は、加算ユニット331の加算処理で取得されたキャリーフラグをデータDo3に含めて、出力するようにしてもよいし、また、別のバスを用いて、当該キャリーフラグを、レジスタファイル部2に出力するようにしてもよい。

#### 【0104】

10

20

30

40

50

第5切替部337は、乗算ユニット333から出力される乗算結果データの上位16ビットデータ、および、シフト演算ユニット334から出力されるシフト演算結果データの上位16ビットデータを入力とする。そして、第5切替部337は、命令制御部1の指令(制御信号Ct12)に従い、上記2つのユニットからの出力のいずれかを選択して、データDs3として、ステートレジスタ34に出力する。

#### 【0105】

ステートレジスタ34は、第3スロット33の第5切替部337から出力される16ビットデータを入力し、入力された16ビットデータを記憶保持する。ステートレジスタ34は、保持している16ビットデータを第2スロット32のステート読み出しユニット323および第1切替部324と、第3スロット33の第3切替部335に出力する。 10

#### 【0106】

命令メモリM1は、VLIWプロセッサ1000で、演算を実行するための命令等を記憶することができる記憶装置である。命令メモリM1は、命令制御部1によりアクセス可能なメモリである。

#### 【0107】

データメモリM2は、VLIWプロセッサ1000で、演算を実行するためのデータ等を記憶することができる記憶装置である。データメモリM2は、命令実行部3の第1スロット31のロード/ストアユニット311によりアクセス可能なメモリである。

#### 【0108】

なお、命令メモリM1およびデータメモリM2は、1つのメモリ(記憶装置)に実現されるものであってもよい。 20

#### 【0109】

<1.2: VLIWプロセッサの動作>

以上のように構成されたVLIWプロセッサ1000の動作について、以下、図面を参照しながら、説明する。

#### 【0110】

以下では、

(1)乗算処理を実行し、乗算結果に対してシフト演算処理を実行する場合(MulShift処理)、

(2)乗算処理を実行し、乗算結果に対して、加算処理を実行する場合(MulAdd処理)、 30

(3)乗算処理を実行し、乗算結果に対して、シフト演算処理を実行し、シフト演算結果に対して加算処理を実行する場合(MulShiftAdd処理)、および、

(4)シフト演算処理を実行し、シフト演算結果に対して、加算処理を実行する場合(ShiftAdd処理)、

について、説明する。

#### 【0111】

(1.2.1:MulShift処理)

VLIWプロセッサ1000において、2つの16ビットデータに対して乗算処理を実行し、その乗算結果である32ビットデータを、32ビットシフトする場合(この場合の処理を「MulShift処理」という。)について、説明する。 40

#### 【0112】

図3の左図は、VLIWプロセッサ1000がMulShift処理を実行する場合において、各スロット(第1スロット31、第2スロット32および第3スロット33)に割り当てられる演算処理を、サイクル毎に示した図である。また、図3の右図は、サイクル2(Cyc2)においてアクティブになっている部分を明示した図である。なお、アクティブになっている部分は、太線で示している(以下、同様)。

#### 【0113】

図4、図5も、図3と同様の図である。

#### 【0114】

10

20

30

40

50

図4の右図は、サイクル3(Cyc3)においてアクティブになっている部分を明示した図である。

【0115】

図5の右図は、サイクル4(Cyc4)においてアクティブになっている部分を明示した図である。

【0116】

MulShif t処理は、例えば、2つの16ビットデータを乗算し、固定小数点位置を合わせる処理に相当する。

【0117】

(Cyc0) :

10

サイクル0(Cyc0)において、命令制御部1は、命令実行部3に対して、制御信号Ct12により、ロード／ストア命令を発行し、第1スロット31のロード／ストアユニット311は、当該ロード／ストア命令に基づいて、第3スロット33の乗算ユニット333による乗算処理(Mul116)に必要な2つの16ビットデータ(ソースオペランド)のうちの1つを、データメモリM2から読み出す。そして、第1スロット31は、読み出した16ビットデータをレジスタファイル部2に出力する。

【0118】

レジスタファイル部2は、第1スロット31から読み出された16ビットデータを所定のレジスタに格納する。

【0119】

20

(Cyc1) :

サイクル1(Cyc1)において、命令制御部1は、命令実行部3に対して、制御信号Ct12により、ロード／ストア命令を発行し、第1スロット31のロード／ストアユニット311は、当該ロード／ストア命令に基づいて、第3スロット33の乗算ユニット333による乗算処理(Mul116)に必要な2つの16ビットデータ(ソースオペランド)のうちのもう1つのデータを、データメモリM2から読み出す。そして、第1スロット31は、読み出した16ビットデータをレジスタファイル部2に出力する。

【0120】

レジスタファイル部2は、第1スロット31から読み出された16ビットデータを所定のレジスタに格納する。

30

【0121】

(Cyc2) :

サイクル2(Cyc2)において、命令制御部1は、命令実行部3に対して、制御信号Ct12により、乗算命令を発行し、第3スロット33の乗算ユニット333が実行可能な状態となる。また、レジスタファイル部2は、命令制御部1からの制御信号Ct12に基づいて、サイクル0、1で、所定のレジスタに格納された乗算処理対象の2つの16ビットデータを、データバスDi31、Di32を介して、第3スロット33に出力する。

【0122】

第3スロット33の乗算ユニット333は、データバスDi31、Di32を介して、入力された2つの16ビットデータに対して乗算処理を実行する。そして、乗算ユニット333は、乗算結果の32ビットデータのうち上位16ビットのデータを16ビットデータDs3として、第5切替部337を介して、ステートレジスタ34に出力する。そして、ステートレジスタ34は、第3スロット33から出力された16ビットデータDs3を格納する。

40

【0123】

また、乗算ユニット333は、乗算結果の32ビットデータのうち下位16ビットのデータを16ビットデータDo3として、第4切替部336を介して、レジスタファイル部2に出力する。レジスタファイル部2は、受信した当該16ビットデータDo3を所定のレジスタに格納する。

【0124】

50

( C y c 3 ) :

サイクル 3 ( C y c 3 )において、命令制御部 1 は、命令実行部 3 に対して、制御信号 C t 1 2 により、シフト演算命令を発行し、第 3 スロット 3 3 のシフト演算ユニット 3 3 4 が実行可能な状態となる。また、レジスタファイル部 2 は、命令制御部 1 からの制御信号 C t 1 2 に基づいて、サイクル 2 で、所定のレジスタに格納されたシフト演算対象の 1 6 ビットデータ（乗算結果の下位 1 6 ビットデータ）を、データバス D i 3 1 を介して、第 3 スロット 3 3 に出力する。

【 0 1 2 5 】

シフト演算ユニット 3 3 4 は、レジスタファイル部 2 から、データバス D i 3 1 を介して入力された 1 6 ビットデータと、ステートレジスタ 3 4 から出力された 1 6 ビットデータ（乗算結果の上位 1 6 ビットデータ）とを取得する。なお、このとき、第 3 切替部 3 3 5 は、命令制御部 1 からの指令により、ステートレジスタ 3 4 からの出力を選択して、シフト演算ユニット 3 3 4 に出力するように制御されている。

【 0 1 2 6 】

シフト演算ユニット 3 3 4 は、上記のようにして入力された、2つの 1 6 ビットデータからなる 3 2 ビットデータに対して、シフト演算処理を実行する。そして、シフト演算ユニット 3 3 4 は、シフト演算処理結果の 3 2 ビットデータのうち上位 1 6 ビットのデータを 1 6 ビットデータ D s 3 として、第 5 切替部 3 3 7 を介して、ステートレジスタ 3 4 に出力する。そして、ステートレジスタ 3 4 は、第 3 スロット 3 3 から出力された 1 6 ビットデータ D s 3 を格納する。

【 0 1 2 7 】

また、シフト演算ユニット 3 3 4 は、シフト演算処理結果の 3 2 ビットデータのうち下位 1 6 ビットのデータを 1 6 ビットデータ D o 3 として、第 4 切替部 3 3 6 を介して、レジスタファイル部 2 に出力する。レジスタファイル部 2 は、受信した当該 1 6 ビットデータ D o 3 を所定のレジスタに格納する。

【 0 1 2 8 】

( C y c 4 ) :

サイクル 4 ( C y c 4 )において、命令制御部 1 は、命令実行部 3 に対して、制御信号 C t 1 2 により、読み出し命令を発行し、第 2 スロット 3 2 のステート読み出しユニット 3 2 3 が実行可能な状態となる。ステート読み出しユニット 3 2 3 は、サイクル 3 でのシフト演算結果の上位 1 6 ビットデータを、第 2 切替部 3 2 5 を介して、1 6 ビットデータ D o 2 として、レジスタファイル部 2 に出力する。なお、このとき、第 2 切替部 3 2 5 は、制御信号 C t 1 2 により、ステート読み出しユニット 3 2 3 からの出力を選択し、出力するように制御されている。

【 0 1 2 9 】

レジスタファイル部 2 は、受信した上記の 1 6 ビットデータ D o 2 を所定のレジスタに格納する。

【 0 1 3 0 】

また、別のデータに対する乗算処理（第 3 スロットの乗算ユニット 3 3 3 による乗算処理）が、上記と同様にして、実行される。なお、この乗算処理の処理対象となる 2 つの 1 6 ビットデータは、図 5 の右図に示すように、サイクル 2、3 において、第 1 スロット 3 1 のロード／ストアユニット 3 1 1 により、データメモリ M 2 から読み出され、レジスタファイル部 2 の所定のレジスタに格納されている。

【 0 1 3 1 】

以上により、V L I W プロセッサ 1 0 0 0 において、2つの 1 6 ビットデータに対して乗算処理を実行し、その乗算結果である 3 2 ビットデータを、3 2 ビットシフトする処理 ( M u l S h i f t 処理) を実行することができる。

【 0 1 3 2 】

( 1 . 2 . 2 : M u l A d d 処理 )

次に、V L I W プロセッサ 1 0 0 0 において、2つの 1 6 ビットデータに対して乗算処理

10

20

30

40

50

理を実行し、その乗算結果である 32 ビットデータを、他の 32 ビットデータと加算する場合（この場合の処理を「MulAdd 处理」という。）について、図6、図7を用いて説明する。このMulAdd 处理の一例として、2つの16ビットデータの乗算結果の累積加算処理がある。このような処理は、画像処理や画像認識処理等において多用される。

#### 【0133】

図6の左図は、VLIW プロセッサ1000がMulAdd 处理を実行する場合において、各スロット（第1スロット31、第2スロット32および第3スロット33）に割り当てられる演算処理を、サイクル毎に示した図である。また、図6の右図は、サイクル3（Cycle 3）においてアクティブになっている部分を明示した図である。

#### 【0134】

図7は、図6と同様の図である。

#### 【0135】

図7の右図は、サイクル4（Cycle 4）においてアクティブになっている部分を明示した図である。

#### 【0136】

（Cycle 0～2）：

サイクル0～2（Cycle 0～2）の処理は、「1.2.1：MulShift 处理」におけるサイクル0～2の処理と同様であるので、詳細な説明を省略する。

#### 【0137】

（Cycle 3）：

サイクル3（Cycle 3）において、命令制御部1は、命令実行部3に対して、制御信号 Ct12 により、加算命令（AddL 命令）を発行し、第3スロット33 の加算ユニット331 が実行可能な状態となる。また、レジスタファイル部2は、命令制御部1からの制御信号 Ct12 に基づいて、サイクル2で、所定のレジスタに格納した乗算結果の下位16ビットデータを、データパス Di31 を介して、第3スロット33 に出力する。また、レジスタファイル部2は、命令制御部1からの制御信号 Ct12 に基づいて、加算される32ビットデータ（例えば、累積加算値（32ビットデータ））の下位16ビットデータを、データパス Di32 を介して、第3スロット33 に出力する。

#### 【0138】

第3スロット33 の加算ユニット331 は、データパス Di31 、Di32 を介して、入力された2つの16ビットデータに対して加算処理を実行する。そして、加算ユニット331 は、加算結果の16ビットデータを、16ビットデータ Do3 として、レジスタファイル部2 に出力する。レジスタファイル部2 は、受信した当該16ビットデータ Do3 を所定のレジスタに格納する。なお、加算ユニット331 での加算処理により取得されたキャリービットも、レジスタファイル部2 に出力され、所定のレジスタ（例えば、キャリーレジスタ）に格納される。なお、キャリービットのデータパスについては、図示を省略している。

#### 【0139】

（Cycle 4）：

サイクル4（Cycle 4）において、命令制御部1は、命令実行部3に対して、制御信号 Ct12 により、加算命令（AddH 命令）を発行し、第2スロット32 の加算ユニット321 が実行可能な状態となる。また、レジスタファイル部2は、命令制御部1からの制御信号 Ct12 に基づいて、加算される32ビットデータ（例えば、累積加算値（32ビットデータ））の上位16ビットデータを、データパス Di22 を介して、第2スロット32 に出力する。

#### 【0140】

また、ステートレジスタ34 は、サイクル2で格納した乗算結果（乗算ユニット333 による乗算結果の上位16ビットデータ）を、第1切替部324 を介して、加算ユニット321 に出力する。このとき、第1切替部324 は、制御信号 Ct12 により、ステートレジスタ34 の出力が、加算ユニット321 に出力されるように制御されている。

10

20

30

40

50

## 【0141】

第2スロット32の加算ユニット321は、データバスD<sub>i</sub>22を介して、入力された16ビットデータと、第1切替部324から出力される16ビットデータ（乗算ユニット333による乗算結果の上位16ビットデータ）と、加算ユニット331での加算処理により取得されたキャリービット（キャリービットの入力バスについては不図示）とに対して、加算処理を実行する。そして、加算ユニット321は、加算結果の16ビットデータを、第2切替部325を介して、16ビットデータD<sub>o</sub>2として、レジスタファイル部2に出力する。なお、このとき、第2切替部325は、制御信号C<sub>t</sub>12により、加算ユニット321の出力が、レジスタファイル部2に出力されるように制御されている。

## 【0142】

10

レジスタファイル部2は、受信した当該16ビットデータD<sub>o</sub>2を所定のレジスタに格納する。なお、加算ユニット321での加算処理により取得されたキャリービットも、レジスタファイル部2に出力され、所定のレジスタ（例えば、キャリーレジスタ）に格納される。なお、キャリービットのデータバスについては、図示を省略している。

## 【0143】

また、サイクル4において、命令制御部1は、命令実行部3に対して、制御信号C<sub>t</sub>12により、乗算命令を発行し、第3スロット33の乗算ユニット333が実行可能な状態となる。そして、サイクル2の第3スロット33の乗算ユニット333の処理と同様の処理が実行される。つまり、別のデータに対する乗算処理（第3スロットの乗算ユニット333による乗算処理）が、上記と同様にして、実行される。なお、この乗算処理の処理対象は、サイクル2、3において、第1スロット31のロード／ストアユニット311により、データメモリM2から読み出され、レジスタファイル部2の所定のレジスタに格納されている。

20

## 【0144】

以上により、VLIWプロセッサ1000において、2つの16ビットデータに対して乗算処理を実行し、その乗算結果である32ビットデータを、他の32ビットデータと加算する処理（MulAdd処理）を実行することができる。

## 【0145】

（1.2.3：MulShiftAdd処理）

30

次に、VLIWプロセッサ1000において、2つの16ビットデータに対して乗算処理を実行し、その乗算結果である32ビットデータに対してシフト演算を行い、そのシフト演算結果を、他の32ビットデータと加算する場合（この場合の処理を「MulShiftAdd処理」という。）について、図8、図9を用いて説明する。このMulShiftAdd処理の一例として、2つの16ビットデータの乗算結果データに対して固定小数点位置を合わせた後、累積加算する処理がある。このような処理は、画像処理や画像認識処理等において多用される。

## 【0146】

図8の左図は、VLIWプロセッサ1000がMulShiftAdd処理を実行する場合において、各スロット（第1スロット31、第2スロット32および第3スロット33）に割り当てられる演算処理を、サイクル毎に示した図である。また、図8の右図は、サイクル4（Cyc4）においてアクティブになっている部分を明示した図である。

40

## 【0147】

図9は、図8と同様の図である。

## 【0148】

図9の右図は、サイクル5（Cyc5）においてアクティブになっている部分を明示した図である。

## 【0149】

（Cyc0～3）：

サイクル0～3（Cyc0～3）の処理は、「1.2.1：MulShift処理」におけるサイクル0～3の処理と同様であるので、詳細な説明を省略する。

50

## 【0150】

(Cyc4) :

サイクル4(Cyc4)において、命令制御部1は、命令実行部3に対して、制御信号Ct12により、加算命令(AddL命令)を発行し、第3スロット33の加算ユニット331が実行可能な状態となる。また、レジスタファイル部2は、命令制御部1からの制御信号Ct12に基づいて、サイクル3で、所定のレジスタに格納したシフト演算処理結果の下位16ビットデータを、データバスDi31を介して、第3スロット33に出力する。また、レジスタファイル部2は、命令制御部1からの制御信号Ct12に基づいて、加算される32ビットデータ(例えば、累積加算値(32ビットデータ))の下位16ビットデータを、データバスDi32を介して、第3スロット33に出力する。

10

## 【0151】

第3スロット33の加算ユニット331は、データバスDi31、Di32を介して、入力された2つの16ビットデータに対して加算処理を実行する。そして、加算ユニット331は、加算結果の16ビットデータを、16ビットデータDo3として、レジスタファイル部2に出力する。レジスタファイル部2は、受信した当該16ビットデータDo3を所定のレジスタに格納する。なお、加算ユニット331での加算処理により取得されたキャリービットも、レジスタファイル部2に出力され、所定のレジスタ(例えば、キャリーレジスタ)に格納される。なお、キャリービットのデータパスについては、図示を省略している。

20

## 【0152】

(Cyc5) :

サイクル5(Cyc5)において、命令制御部1は、命令実行部3に対して、制御信号Ct12により、加算命令(AddH命令)を発行し、第2スロット32の加算ユニット321が実行可能な状態となる。また、レジスタファイル部2は、命令制御部1からの制御信号Ct12に基づいて、加算される32ビットデータ(例えば、累積加算値(32ビットデータ))の上位16ビットデータを、データバスDi22を介して、第2スロット32に出力する。

## 【0153】

また、ステートレジスタ34は、サイクル3で格納したシフト演算処理結果(シフト演算ユニット334によるシフト演算処理結果の上位16ビットデータ)を、第1切替部324を介して、加算ユニット321に出力する。このとき、第1切替部324は、制御信号Ct12により、ステートレジスタ34の出力が、加算ユニット321に出力されるように制御されている。

30

## 【0154】

第2スロット32の加算ユニット321は、データバスDi22を介して、入力された16ビットデータと、第1切替部324から出力される16ビットデータ(シフト演算ユニット334によるシフト演算処理結果の上位16ビットデータ)と、加算ユニット331での加算処理により取得されたキャリービット(キャリービットの入力バスについては不図示)とに対して、加算処理を実行する。そして、加算ユニット321は、加算結果の16ビットデータを、第2切替部325を介して、16ビットデータDo2として、レジスタファイル部2に出力する。なお、このとき、第2切替部325は、制御信号Ct12により、加算ユニット321の出力が、レジスタファイル部2に出力されるように制御されている。

40

## 【0155】

レジスタファイル部2は、受信した当該16ビットデータDo2を所定のレジスタに格納する。なお、加算ユニット321での加算処理により取得されたキャリービットも、レジスタファイル部2に出力され、所定のレジスタ(例えば、キャリーレジスタ)に格納される。なお、キャリービットのデータパスについては、図示を省略している。

## 【0156】

また、サイクル5において、命令制御部1は、命令実行部3に対して、制御信号Ct1

50

2により、乗算命令を発行し、第3スロット33の乗算ユニット333が実行可能な状態となる。そして、サイクル2の第3スロット33の乗算ユニット333の処理と同様の処理が実行される。つまり、別のデータに対する乗算処理（第3スロットの乗算ユニット33による乗算処理）が、上記と同様にして、実行される。なお、この乗算処理の処理対象は、サイクル3、4において、第1スロット31のロード／ストアユニット311により、データメモリM2から読み出され、レジスタファイル部2の所定のレジスタに格納されている。

#### 【0157】

以上により、VLIWプロセッサ1000において、2つの16ビットデータに対して乗算処理を実行し、その乗算結果である32ビットデータに対してシフト演算を行い、そのシフト演算結果を、他の32ビットデータと加算する処理（MulShiftAdd処理）を実行することができる。10

#### 【0158】

（1.2.4：ShiftAdd処理）

次に、VLIWプロセッサ1000において、32ビットデータに対してシフト演算処理を実行し、そのシフト演算処理結果である32ビットデータと、他の32ビットデータと加算する場合（この場合の処理を「ShiftAdd処理」という。）について、図10～12を用いて説明する。このShiftAdd処理の一例として、固定小数点位置を合わせた累積加算処理がある。このような処理は、画像処理や画像認識処理等において多用される。20

#### 【0159】

図10の左図は、VLIWプロセッサ1000がShiftAdd処理を実行する場合において、各スロット（第1スロット31、第2スロット32および第3スロット33）に割り当てられる演算処理を、サイクル毎に示した図である。また、図10の右図は、サイクル2（Cyc2）においてアクティブになっている部分を明示した図である。

#### 【0160】

図11、図12は、図10と同様の図である。

#### 【0161】

図11の右図は、サイクル3（Cyc3）においてアクティブになっている部分を明示した図である。30

#### 【0162】

図12の右図は、サイクル4（Cyc4）においてアクティブになっている部分を明示した図である。

#### 【0163】

（Cyc0～1）：

サイクル0～1（Cyc0～1）の処理は、「1.2.1：MulShift処理」におけるサイクル0～1の処理と同様であるので、詳細な説明を省略する。

#### 【0164】

（Cyc2）：

サイクル2（Cyc2）において、命令制御部1は、命令実行部3に対して、制御信号Ctl2により、シフト演算命令（Shift32命令）を発行し、第3スロット33のシフト演算ユニット334が実行可能な状態となる。また、レジスタファイル部2は、命令制御部1からの制御信号Ctl2に基づいて、サイクル0、1で、所定のレジスタに格納したシフト演算処理対象の32ビットデータの下位16ビットデータを、データバスDi31を介して、当該データの上位16ビットデータを、データバスDi32を介して、第3スロット33に出力する。40

#### 【0165】

第3スロット33のシフト演算ユニット334は、データバスDi31を介して入力された16ビットデータと、データバスDi32および第3切替部335を介して入力された16ビットデータの2つの16ビットデータに対してシフト演算処理を実行する。そし50

て、シフト演算ユニット334は、シフト演算処理結果の32ビットデータの上位16ビットデータを、第5切替部337を介して、16ビットデータDs3として、ステートレジスタ34に出力する。

#### 【0166】

ステートレジスタ34は、受信した16ビットデータDs3を格納する。

#### 【0167】

また、シフト演算ユニット334は、シフト演算処理結果の32ビットデータの下位16ビットデータを、16ビットデータDo3として、第4切替部336を介して、レジスタファイル部2に出力する。レジスタファイル部2は、受信した当該16ビットデータDo3を所定のレジスタに格納する。

10

#### 【0168】

(Cyc3) :

サイクル3(Cyc3)において、命令制御部1は、命令実行部3に対して、制御信号Ct12により、加算命令(AddL命令)を発行し、第3スロット33の加算ユニット331が実行可能な状態となる。また、レジスタファイル部2は、命令制御部1からの制御信号Ct12に基づいて、サイクル2で、所定のレジスタに格納したシフト演算処理結果の下位16ビットデータを、データパスDi31を介して、第3スロット33に出力する。また、レジスタファイル部2は、命令制御部1からの制御信号Ct12に基づいて、加算される32ビットデータ(例えば、累積加算値(32ビットデータ))の下位16ビットデータを、データパスDi32を介して、第3スロット33に出力する。

20

#### 【0169】

第3スロット33の加算ユニット331は、データパスDi31、Di32を介して、入力された2つの16ビットデータに対して加算処理を実行する。そして、加算ユニット331は、加算結果の16ビットデータを、16ビットデータDo3として、レジスタファイル部2に出力する。レジスタファイル部2は、受信した当該16ビットデータDo3を所定のレジスタに格納する。なお、加算ユニット331での加算処理により取得されたキャリービットも、レジスタファイル部2に出力され、所定のレジスタ(例えば、キャリーレジスタ)に格納される。なお、キャリービットのデータパスについては、図示を省略している。

#### 【0170】

30

(Cyc4) :

サイクル4(Cyc4)において、命令制御部1は、命令実行部3に対して、制御信号Ct12により、加算命令(AddH命令)を発行し、第2スロット32の加算ユニット321が実行可能な状態となる。また、レジスタファイル部2は、命令制御部1からの制御信号Ct12に基づいて、加算される32ビットデータ(例えば、累積加算値(32ビットデータ))の上位16ビットデータを、データパスDi22を介して、第2スロット32に出力する。

#### 【0171】

また、ステートレジスタ34は、サイクル2で格納したシフト演算処理結果(シフト演算ユニット334によるシフト演算処理結果の上位16ビットデータ)を、第1切替部324を介して、加算ユニット321に出力する。このとき、第1切替部324は、制御信号Ct12により、ステートレジスタ34の出力が、加算ユニット321に出力されるように制御されている。

40

#### 【0172】

第2スロット32の加算ユニット321は、データパスDi22を介して、入力された16ビットデータと、第1切替部324から出力される16ビットデータ(シフト演算ユニット334によるシフト演算処理結果の上位16ビットデータ)とに対して、加算処理を実行する。そして、加算ユニット321は、加算結果の16ビットデータを、第2切替部325を介して、16ビットデータDo2として、レジスタファイル部2に出力する。なお、このとき、第2切替部325は、制御信号Ct12により、加算ユニット321の

50

出力が、レジスタファイル部2に出力されるように制御されている。

**【0173】**

レジスタファイル部2は、受信した当該16ビットデータD<sub>0</sub>2を所定のレジスタに格納する。なお、加算ユニット321での加算処理により取得されたキャリービットも、レジスタファイル部2に出力され、所定のレジスタ（例えば、キャリーレジスタ）に格納される。なお、キャリービットのデータバスについては、図示を省略している。

**【0174】**

また、サイクル4において、命令制御部1は、命令実行部3に対して、制御信号C<sub>t</sub>12により、シフト演算命令（Shift32命令）を発行し、第3スロット33のシフト演算ユニット334が実行可能な状態となる。そして、サイクル2の第3スロット33のシフト演算ユニット334の処理と同様の処理が実行される。つまり、別のデータに対するシフト演算処理が、上記と同様にして、実行される。なお、このシフト演算処理の処理対象は、サイクル2、3において、第1スロット31のロード／ストアユニット311により、データメモリM2から読み出され、レジスタファイル部2の所定のレジスタに格納されている。

**【0175】**

以上により、VLIWプロセッサ1000において、32ビットデータに対してシフト演算処理を実行し、そのシフト演算処理結果である32ビットデータと、他の32ビットデータと加算する処理（ShiftAdd処理）を実行することができる。

**【0176】**

以上のように、VLIWプロセッサ1000では、処理対象が32ビットデータとなる32ビット演算を実行する場合であっても、当該32ビットデータの上位16ビットデータが、ステートレジスタ34により、保持され、次のサイクルにおいて、所定の演算ユニットにより利用することができる。

**【0177】**

また、上記の通り、VLIWプロセッサ1000では、ステートレジスタ34が、第3スロット33から出力される32ビットデータの上位16ビットデータを格納保持し、格納したデータを第2スロット32または第3スロット33に出力することができる。したがって、VLIWプロセッサ1000では、第3スロット33から32ビットデータをレジスタファイル部2に出力する必要がなく、また、レジスタファイル部2から第3スロット33に32ビットデータを出力する必要もない。つまり、VLIWプロセッサ1000では、レジスタファイル部2と命令実行部3との間において、16ビットデータのみが入出力されることが保証されるので、レジスタファイル部2と命令実行部3との間の入出力ポートを、16ビット演算のみを実行する場合に比べて、増やす必要がない。

**【0178】**

すなわち、VLIWプロセッサ1000では、上記の通り、レジスタファイル部2の入出力ポート数を増加させることなく、Nビット演算（N：自然数）を各スロットに割り当てながら、2×Nビットの演算をサポートすることが可能となる。

**【0179】**

このように、VLIWプロセッサ1000では、回路規模の増大を抑えつつ、画像処理、画像認識処理等で多用される命令フローのようにビット拡張された演算（上記では、32ビット演算）を含む場合であっても、効率良く処理を実行することができる。\_\_\_\_\_

**[他の実施形態]**

上記実施形態において、第3スロット33から出力される32ビットデータの上位16ビットデータをステートレジスタ34に出力し、下位16ビットデータをレジスタファイル部2に出力する場合について説明したが、これに限定されることはない。VLIWプロセッサ1000において、例えば、第3スロット33から出力される32ビットデータの下位16ビットデータをステートレジスタ34に出力し、上位16ビットデータをレジスタファイル部2に出力するようにしてもよい。

**【0180】**

10

20

30

40

50

また、上記実施形態では、第2スロット32の加算ユニット321と、第3スロット33の加算ユニット331とは、32ビット加算処理に使用される場合について説明したが、これに限定されることはない。例えば、第2スロット32の加算ユニット321および第3スロット33の加算ユニット331を、それぞれ、16ビットデータの加算処理を実行する演算処理ユニットとして機能させてもよい。これにより、VLIWプロセッサ1000において、16ビットデータの加算処理を、同一サイクルにおいて、第2スロット32と、第3スロット33とに割り当てることも可能となる。

#### 【0181】

上記実施形態では、VLIWプロセッサ1000において、命令実行部3のスロット数が「3」の場合について説明したが、これに限定されることはなく、命令実行部3は、他の数のスロットを有するものであってもよい。10

#### 【0182】

また、上記実施形態の一部または全部を組み合わせるようにしてもよい。

#### 【0183】

また、上記実施形態における処理方法の実行順序は、必ずしも、上記実施形態の記載に制限されるものではなく、発明の要旨を逸脱しない範囲で、実行順序を入れ替えることができるものである。

#### 【0184】

なお、本発明の具体的な構成は、前述の実施形態に限られるものではなく、発明の要旨を逸脱しない範囲で種々の変更および修正が可能である。20

#### 【符号の説明】

#### 【0185】

1000 VLIWプロセッサ

1 命令制御部

2 レジスタファイル部

3 命令実行部

31 第1スロット

32 第2スロット

33 第3スロット

311 ロード/ストアユニット

321、331 加算ユニット

322、332 論理演算ユニット

323 ステート読み出しユニット

333 乗算ユニット

334 シフト演算ユニット

324 第1切替部

325 第2切替部

335 第3切替部

336 第4切替部

34 ステートレジスタ

30

40

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

| MulShift処理 |         |         |

|------------|---------|---------|

| Slot1      | Slot2   | Slot3   |

| Cyc0 L/S   |         |         |

| Cyc1 L/S   |         |         |

| Cyc2 L/S   | Mul16   |         |

| Cyc3 L/S   | Shift32 |         |

| Cyc4 L/S   | Read    | Mul16   |

| Cyc5 L/S   | Shift32 | Shift32 |

| Cyc6 L/S   | Read    | Mul16   |

| Cyc7 L/S   | Shift32 | Shift32 |

| Cyc8 L/S   | Read    |         |

| MulShift処理 |         |         |

|------------|---------|---------|

| Slot1      | Slot2   | Slot3   |

| Cyc0 L/S   |         |         |

| Cyc1 L/S   |         |         |

| Cyc2 L/S   | Mul16   |         |

| Cyc3 L/S   | Shift32 |         |

| Cyc4 L/S   | Read    | Mul16   |

| Cyc5 L/S   | Shift32 | Shift32 |

| Cyc6 L/S   | Read    | Mul16   |

| Cyc7 L/S   | Shift32 | Shift32 |

| Cyc8 L/S   | Read    |         |

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

【図 12】

FIG. 12

|      | Slot1 | Slot2   | Slot3   |

|------|-------|---------|---------|

| Cyc0 | L/S   |         |         |

| Cyc1 | L/S   |         |         |

| Cyc2 | L/S   | Shift32 |         |

| Cyc3 | L/S   | AddL    |         |

| Cyc4 | L/S   | AddH    | Shift32 |

| Cyc5 | L/S   | AddL    | AddL    |

| Cyc6 | L/S   | AddH    | Shift32 |

|      | Slot1 | Slot2   | Slot3   |

|------|-------|---------|---------|

| Cyc0 | L/S   |         |         |

| Cyc1 | L/S   |         |         |

| Cyc2 | L/S   | Shift32 |         |

| Cyc3 | L/S   | AddL    |         |

| Cyc4 | L/S   | AddH    | Shift32 |

| Cyc5 | L/S   | AddL    | AddH    |

| Cyc6 | L/S   | AddH    | Shift32 |

【図 1 3】

FIG. 13

---

フロントページの続き

(51)Int.Cl. F I

G 06 F 9/38 350B

(72)発明者 野本 祥平

大阪府大阪市淀川区宮原一丁目1番1号 株式会社メガチップス内

(72)発明者 水野 雄介

大阪府大阪市淀川区宮原一丁目1番1号 株式会社メガチップス内

審査官 小林 哲雄

(56)参考文献 特開2006-338684 (JP, A)

特開平09-212361 (JP, A)

特開平06-083582 (JP, A)

米国特許第05901301 (US, A)

特開2008-310693 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 30

G 06 F 9 / 302

G 06 F 9 / 34

G 06 F 9 / 38