## (12) 发明专利

(10) 授权公告号 CN 110709966 B

(45) 授权公告日 2023.09.19

(21) 申请号 201880015666.0

(72) 发明人 S·梅耶 H·林克

(22) 申请日 2018.01.19

M·米特斯塔德

(65) 同一申请的已公布的文献号

(74) 专利代理机构 北京纪凯知识产权代理有限公司 11245

申请公布号 CN 110709966 A

专利代理人 李英

(43) 申请公布日 2020.01.17

(51) Int.CI.

(30) 优先权数据

H01L 21/311 (2006.01)

62/448,138 2017.01.19 US

H01L 21/469 (2006.01)

15/714,169 2017.09.25 US

(85) PCT国际申请进入国家阶段日

(56) 对比文件

2019.09.03

US 2009127594 A1, 2009.05.21

(86) PCT国际申请的申请数据

US 4804438 A, 1989.02.14

PCT/US2018/014522 2018.01.19

US 2009188696 A1, 2009.07.30

(87) PCT国际申请的公布数据

JP H1187401 A, 1999.03.30

W02018/136795 EN 2018.07.26

JP 2002124487 A, 2002.04.26

(73) 专利权人 德克萨斯仪器股份有限公司

US 2001022398 A1, 2001.09.20

地址 美国德克萨斯州

US 6265779 B1, 2001.07.24

审查员 赵萌

权利要求书1页 说明书13页 附图26页

## (54) 发明名称

使用保护盖层蚀刻含铂薄膜

## (57) 摘要

一种微电子器件(200)是通过在该微电子器件(200)的衬底(202)上形成含铂层(220)来形成的。盖层(232)在含铂层(220)上形成，使得盖层(232)和含铂层(220)之间的界面不含氧化铂。盖层(232)在蚀刻含铂层(220)的蚀刻溶液中也是可蚀刻的。可替代地，含铂层(200)上的氧化铂可以在形成盖层(232)之前被去除。含铂层(220)可以用于形成硅化铂(226)。可以通过在含铂层(220)的顶部表面上的一部分上形成硬掩模或掩模氧化铂(264)以阻挡湿蚀刻剂来图案化含铂层(220)。

1. 一种形成微电子器件的方法,其包括:

提供衬底;

在所述衬底上方形成含铂层;

在所述含铂层上形成盖层,在所述盖层和所述含铂层之间的界面不含氧化铂,其中所述盖层主要是铝或主要是铜;以及

通过湿蚀刻工艺去除所述盖层和所述含铂层的至少一部分,所述湿蚀刻工艺的相同湿蚀刻剂去除所述盖层和所述含铂层的所述至少一部分,其中在所述相同湿蚀刻剂中,所述盖层的蚀刻速率是所述含铂层的蚀刻速率的至少两倍。

2. 根据权利要求1所述的方法,其中所述含铂层主要包括铂。

3. 根据权利要求1所述的方法,其中所述盖层具有的组成和所述微电子器件的互连线中的层的组成相同。

4. 根据权利要求1所述的方法,其中所述湿蚀刻工艺使用王水。

5. 根据权利要求1所述的方法,其中在所述含铂层被暴露于氧化环境之前形成所述盖层。

6. 根据权利要求1所述的方法,其中在从所述含铂层的顶部表面去除氧化铂之后形成所述盖层。

7. 根据权利要求6所述的方法,其中使用溅射蚀刻工艺执行去除所述氧化铂。

8. 根据权利要求6所述的方法,其中通过加热所述含铂层来执行去除所述氧化铂。

9. 根据权利要求1所述的方法,还包括:

在形成所述盖层之前在所述含铂层的一部分上方形成硬掩模,其中所述盖层在所述硬掩模上方形成。

10. 根据权利要求9所述的方法,其中所述硬掩模包括介电材料。

11. 根据权利要求9所述的方法,其中所述硬掩模是导电的。

12. 根据权利要求11所述的方法,还包括:

在使用所述湿蚀刻工艺去除所述盖层和所述含铂层的所述至少一部分之后,对所述含铂层的剩余部分上的所述硬掩模进行图案化。

13. 根据权利要求1所述的方法,还包括:

去除所述含铂层的对应部分上方的所述盖层的一部分;以及

在使用所述湿蚀刻工艺去除所述盖层和所述含铂层的所述至少一部分之前,在通过去除所述盖层的所述一部分暴露出的地方的对应含铂层上形成掩模氧化铂,其中所述掩模氧化铂阻挡去除所述掩模氧化铂下面的所述含铂层。

14. 根据权利要求1所述的方法,其中所述含铂层接触所述衬底的硅;并且所述方法还包括在去除所述盖层和所述含铂层的所述至少一部分之前,加热所述含铂层以形成硅化铂。

15. 根据权利要求1所述的方法,其中所述含铂层的一部分提供局部互连。

16. 根据权利要求15所述的方法,其中所述局部互连进行与硅化铂的电连接。

17. 根据权利要求1所述的方法,其中所述含铂层的一部分提供键合焊盘。

## 使用保护盖层蚀刻含铂薄膜

### 技术领域

[0001] 本发明一般涉及微电子器件，并且更具体地涉及在微电子器件中的金属层。

### 背景技术

[0002] 可能需要在微电子器件中形成含铂金属的图案化层。蚀刻含铂金属是困难的。湿蚀刻需要非常强的酸，例如王水，并且在蚀刻区域中产生含铂残留物。此外，湿蚀刻趋于不均匀，需要显著的过蚀刻，这在图案化层的横向尺寸上引入不希望的变化。干蚀刻可以通过溅射蚀刻（也称为离子研磨）来完成，但是在微电子器件上导致不期望的再沉积的含铂材料，这可能降低微电子器件的可靠性。此外，溅射蚀刻可能导致在溅射蚀刻室的内表面上沉积不需要的含铂残留物，这可能导致随后处理的晶圆上的污染。溅射蚀刻对含铂金属下面的层中的材料的选择性差。

### 发明内容

[0003] 通过在微电子器件的衬底上形成含铂层来形成微电子器件。在含铂层上形成盖层，使得盖层和含铂层之间的界面不含氧化铂。盖层在用于蚀刻含铂层的蚀刻溶液中是可蚀刻的。在一个方面，在含铂层暴露于氧化环境之前，可以在含铂层上形成盖层。在另一方面，可以在形成盖层之前去除含铂层上的氧化铂。随后通过湿蚀刻工艺去除盖层和含铂层。

[0004] 在一个方面，可以在形成盖层之前在含铂层的一部分上方形成硬掩模。在形成盖层之前，从氧化铂中的由硬掩模暴露的地方除去氧化铂。随后使用蚀刻溶液的湿蚀刻工艺去除盖层并去除由硬掩模暴露的含铂层，从而留下图案化区域中的含铂层。

[0005] 在另一方面，可以从含铂层的一部分上去除盖层，从而暴露图案化区域中的含铂层。然后可以在暴露的含铂层上形成掩模氧化铂。随后使用蚀刻溶液的湿蚀刻工艺去除剩余的盖层并去除盖层下面的含铂层，从而留下图案化区域中的掩模氧化铂下面的含铂层。

### 附图说明

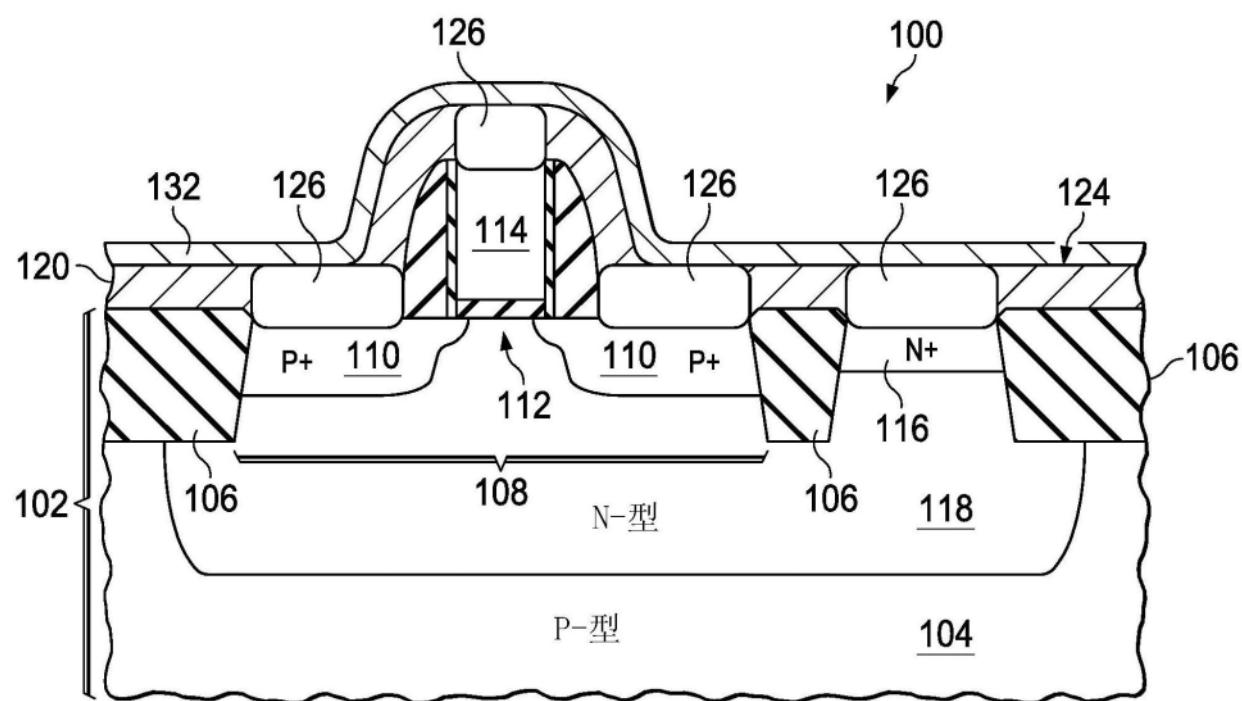

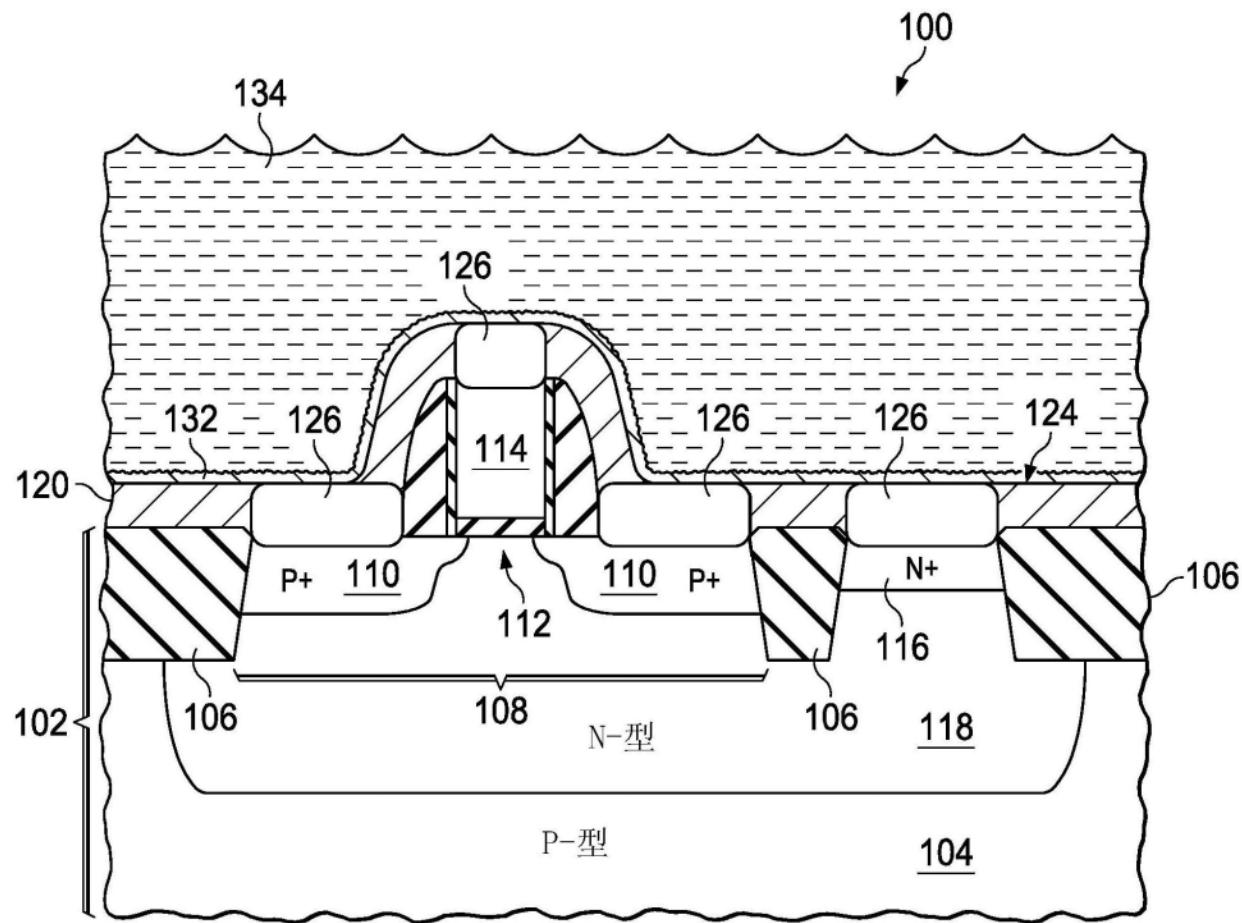

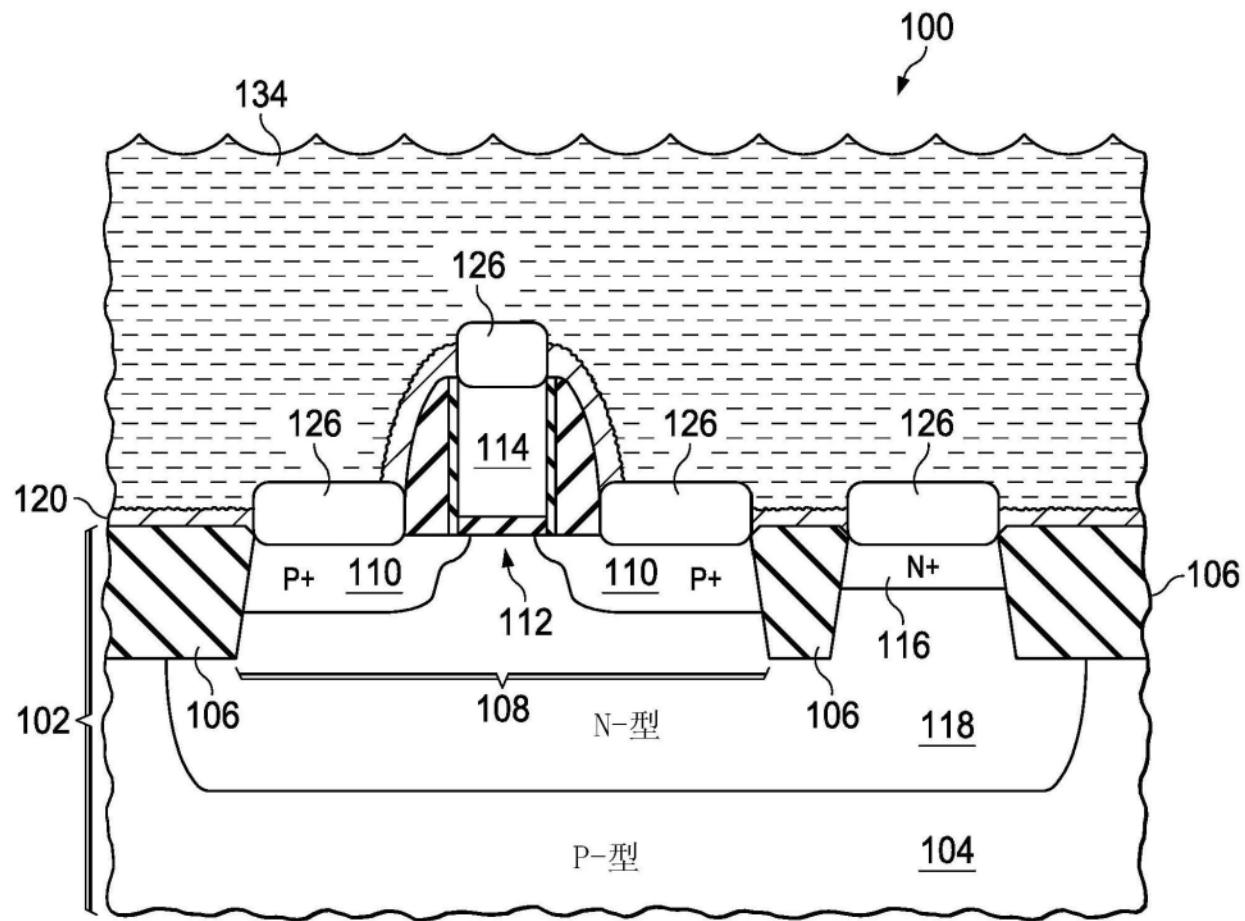

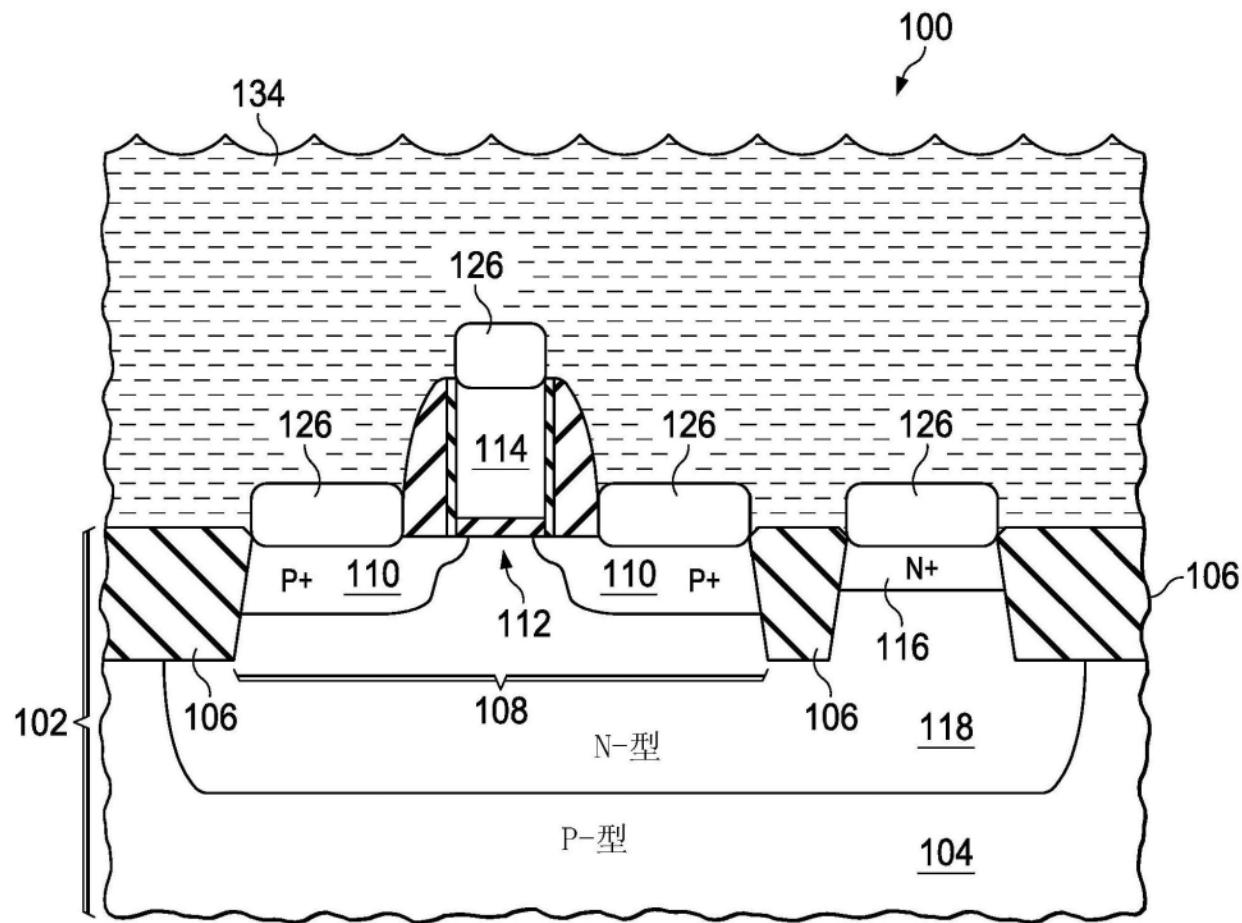

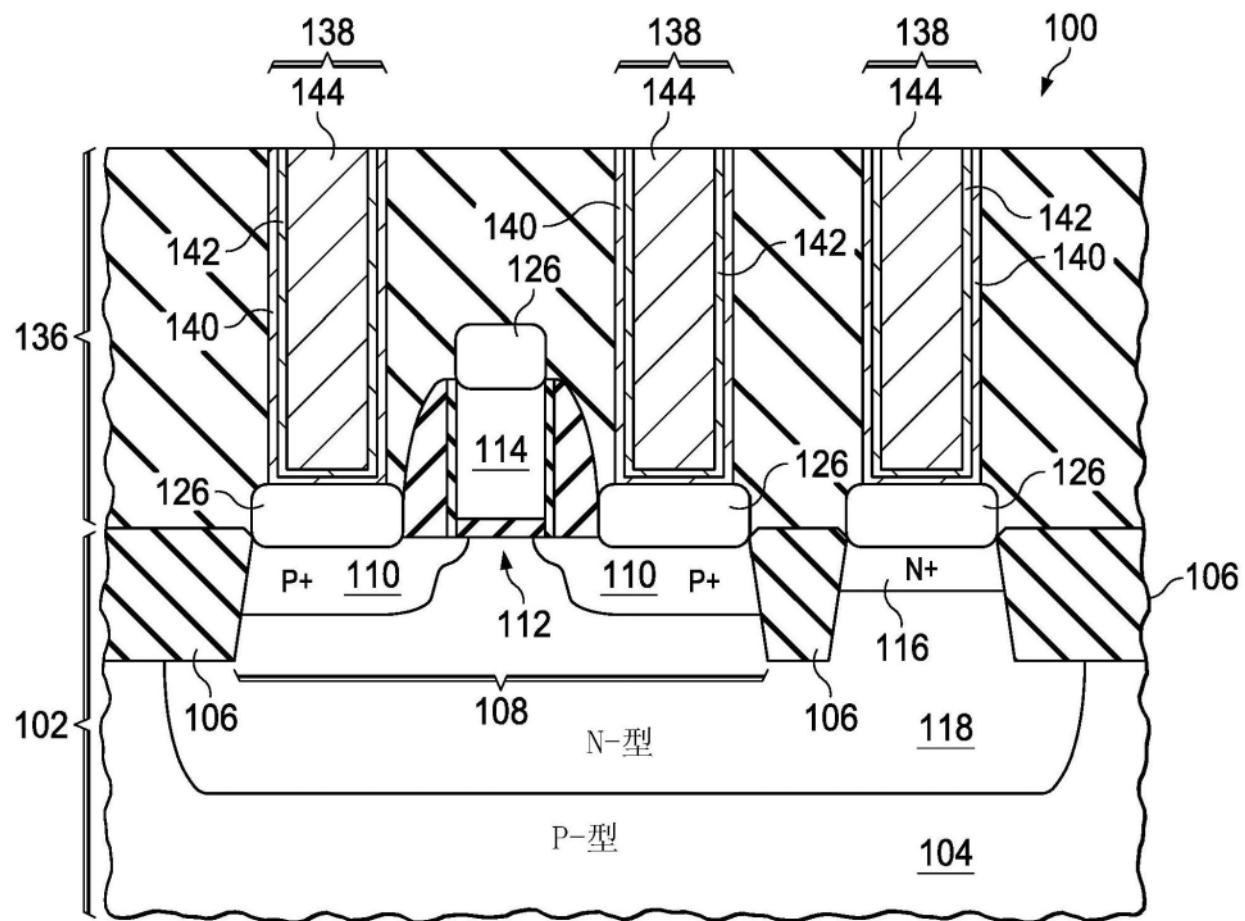

[0006] 图1A至图1H是在一个示例形成方法的连续阶段中描绘的具有含铂层的微电子器件的横截面。

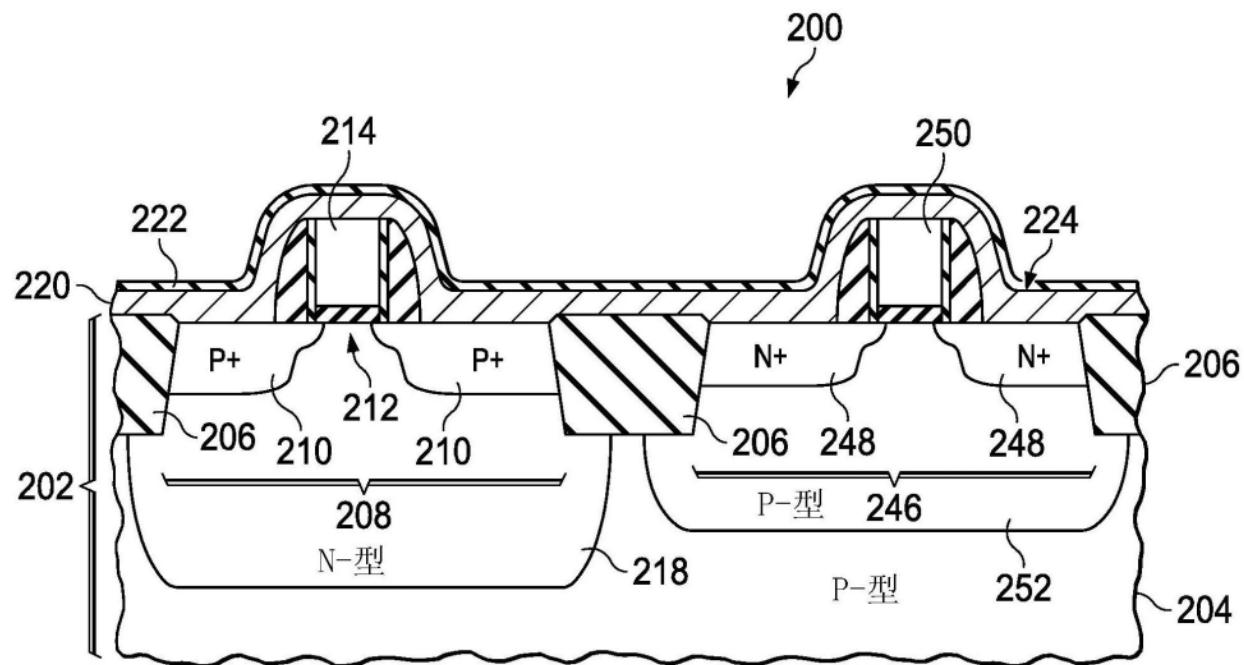

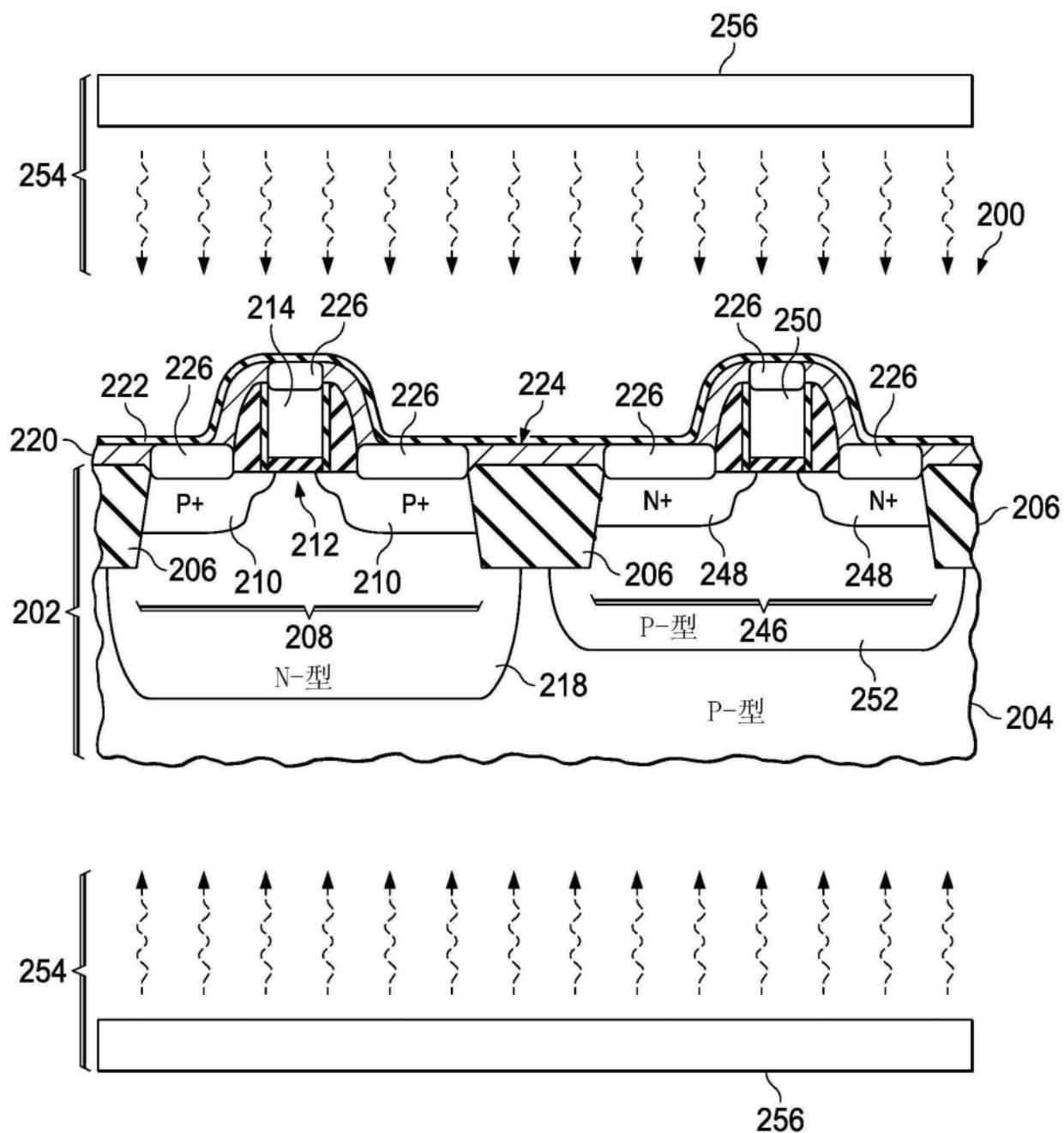

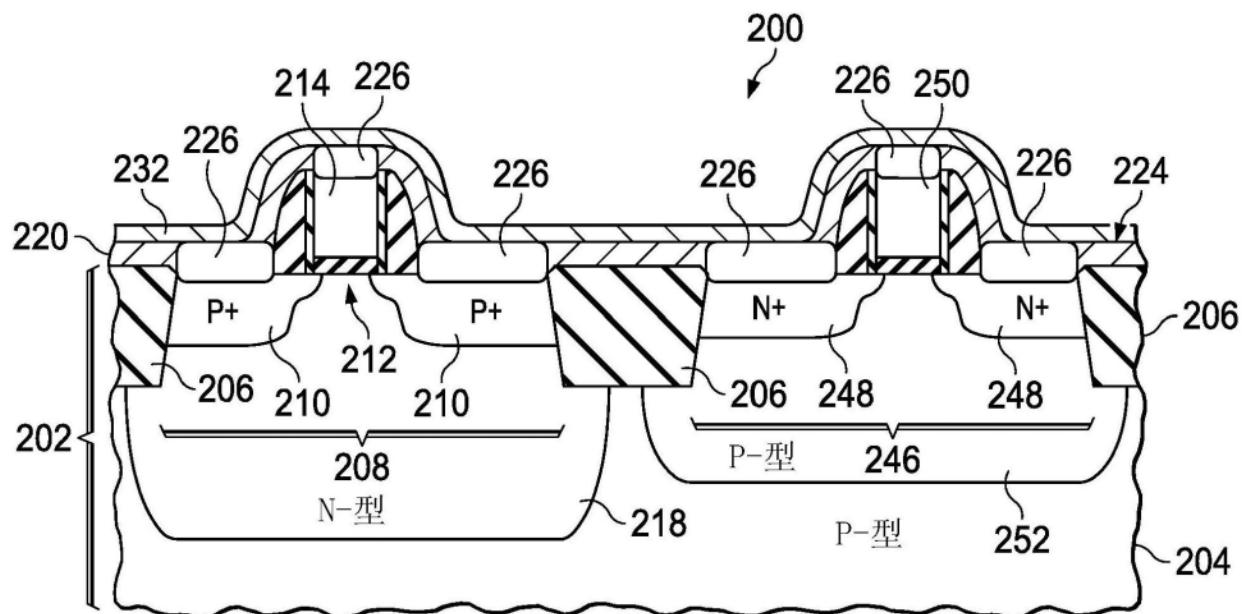

[0007] 图2A至图2H是在另一示例形成方法的连续阶段中描绘的具有含铂层的微电子器件的横截面。

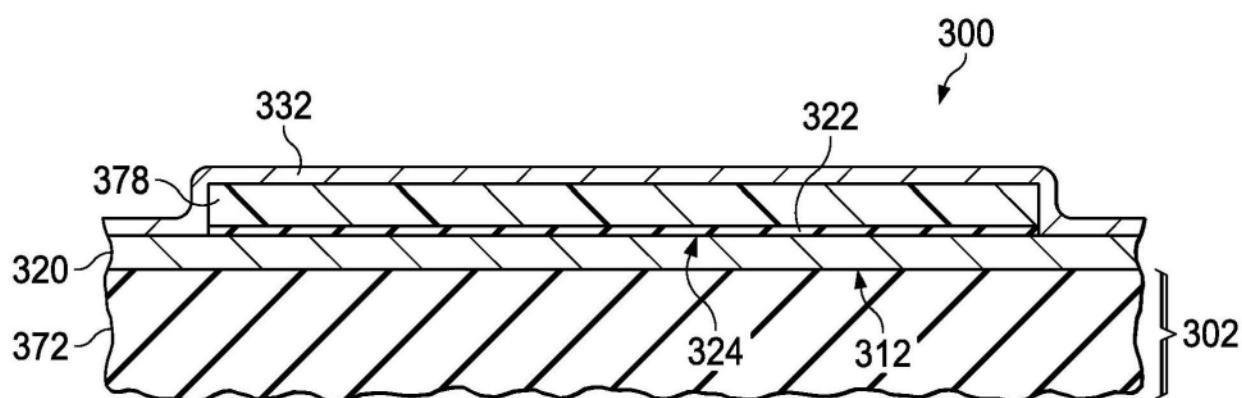

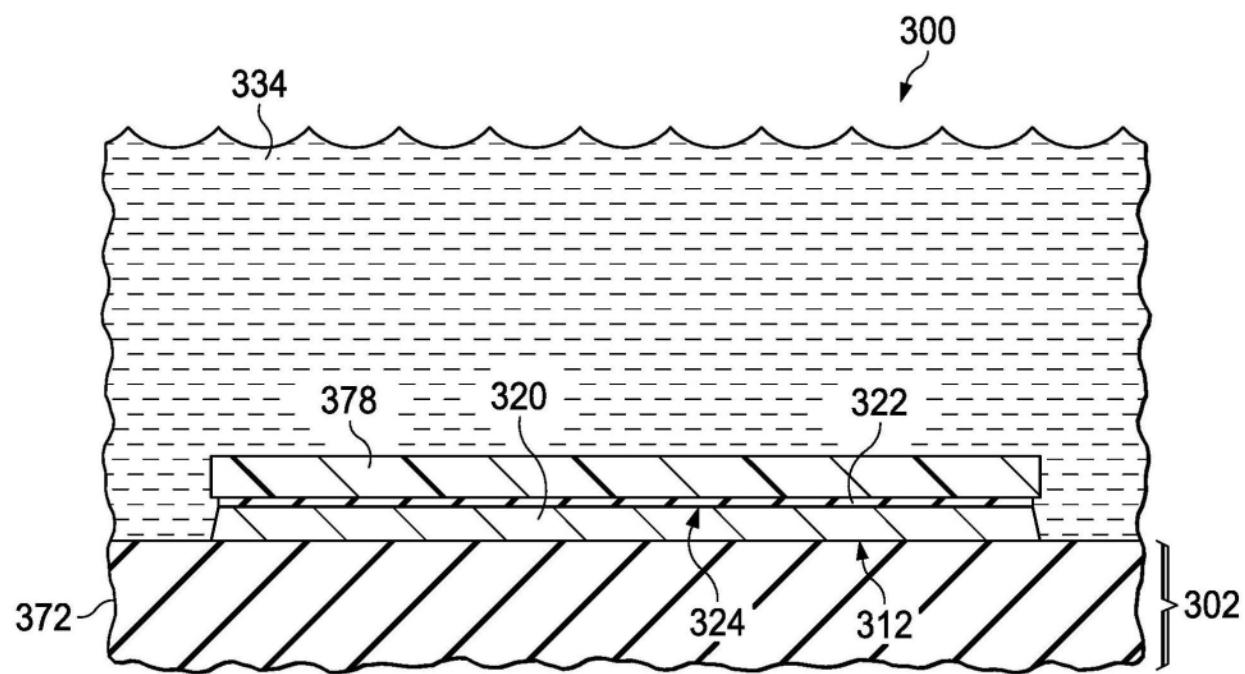

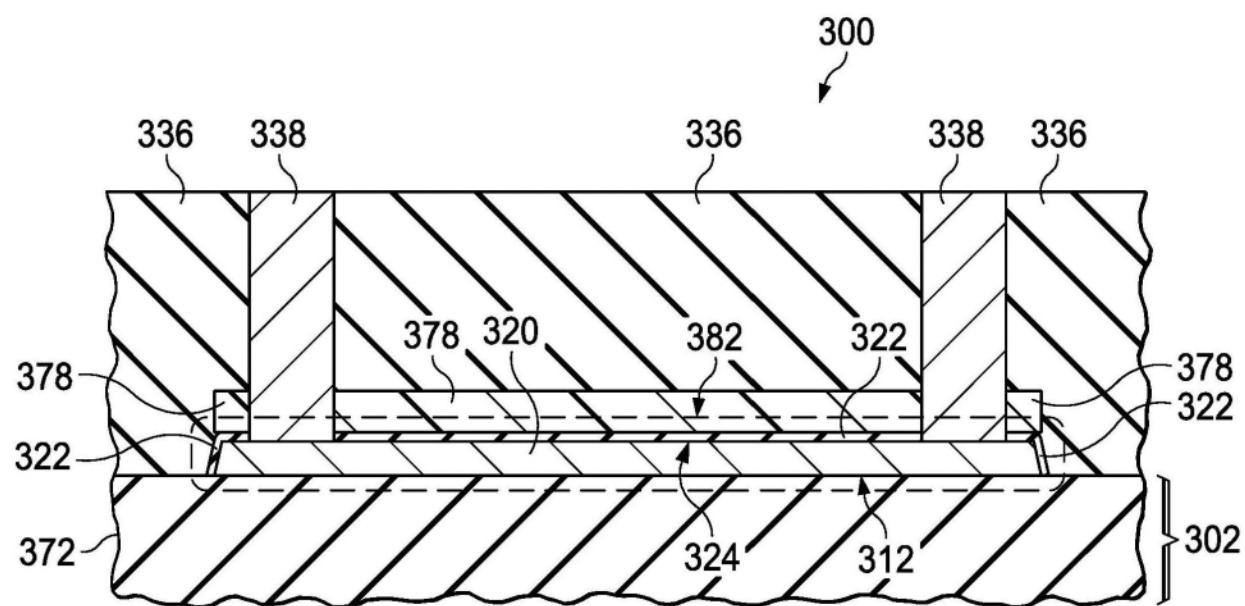

[0008] 图3A至图3F是在又一个示例形成方法的连续阶段中描绘的具有含铂层的微电子器件的横截面。

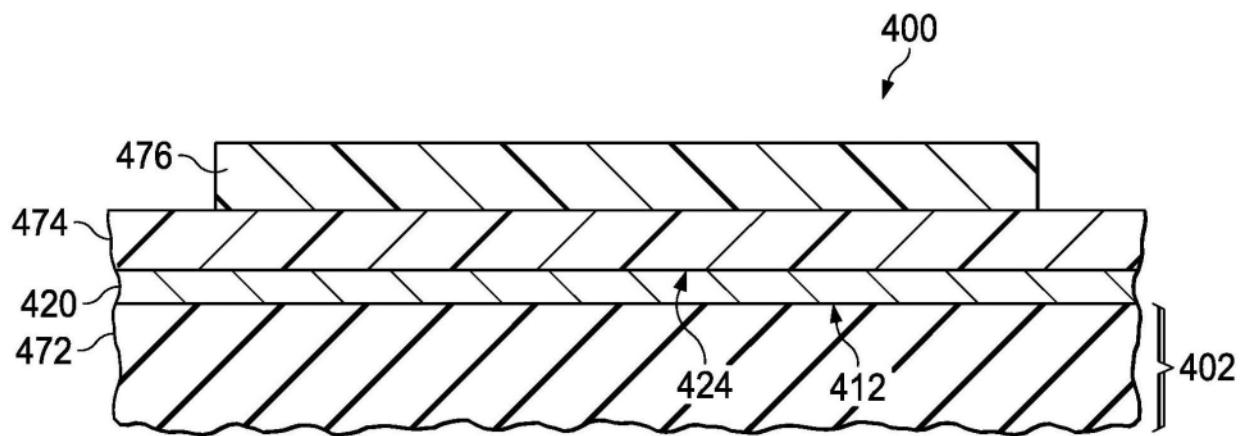

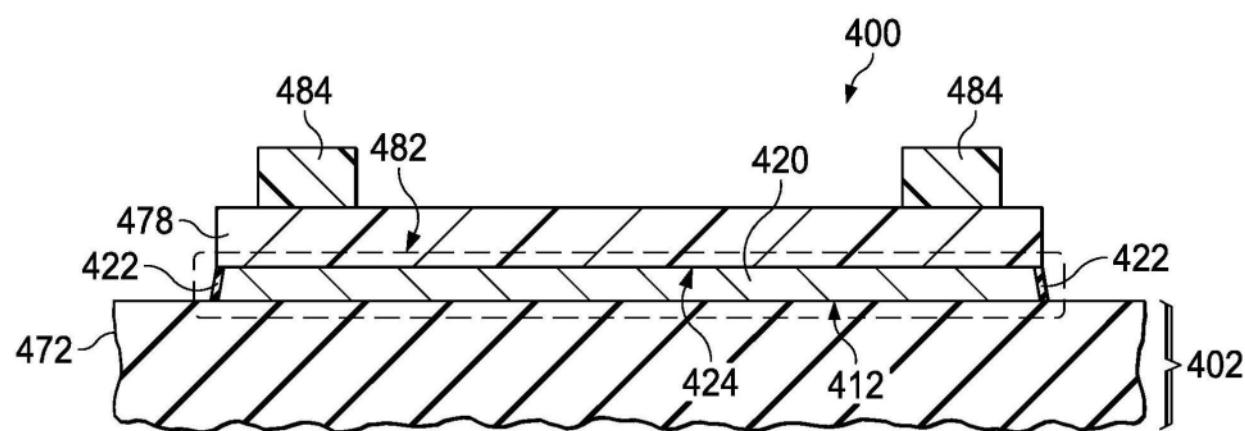

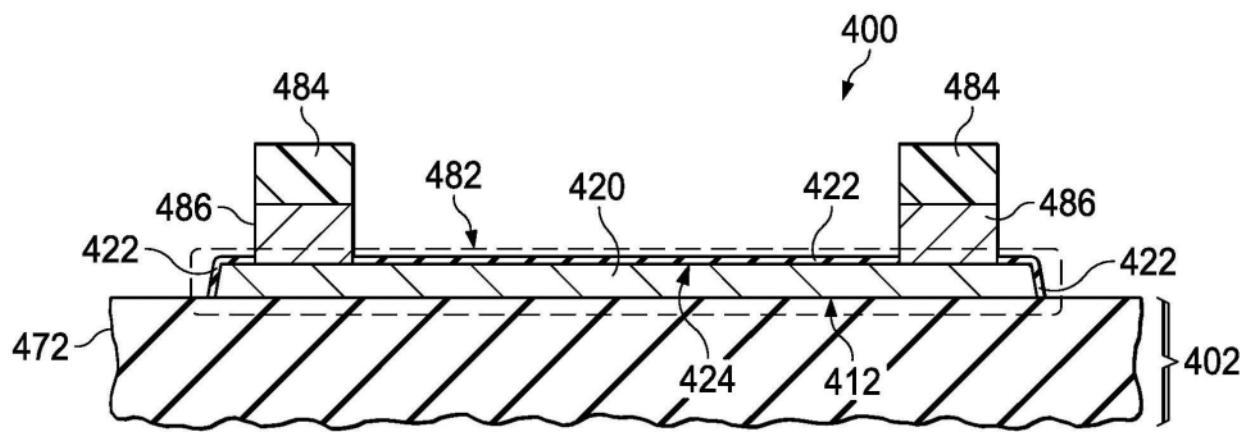

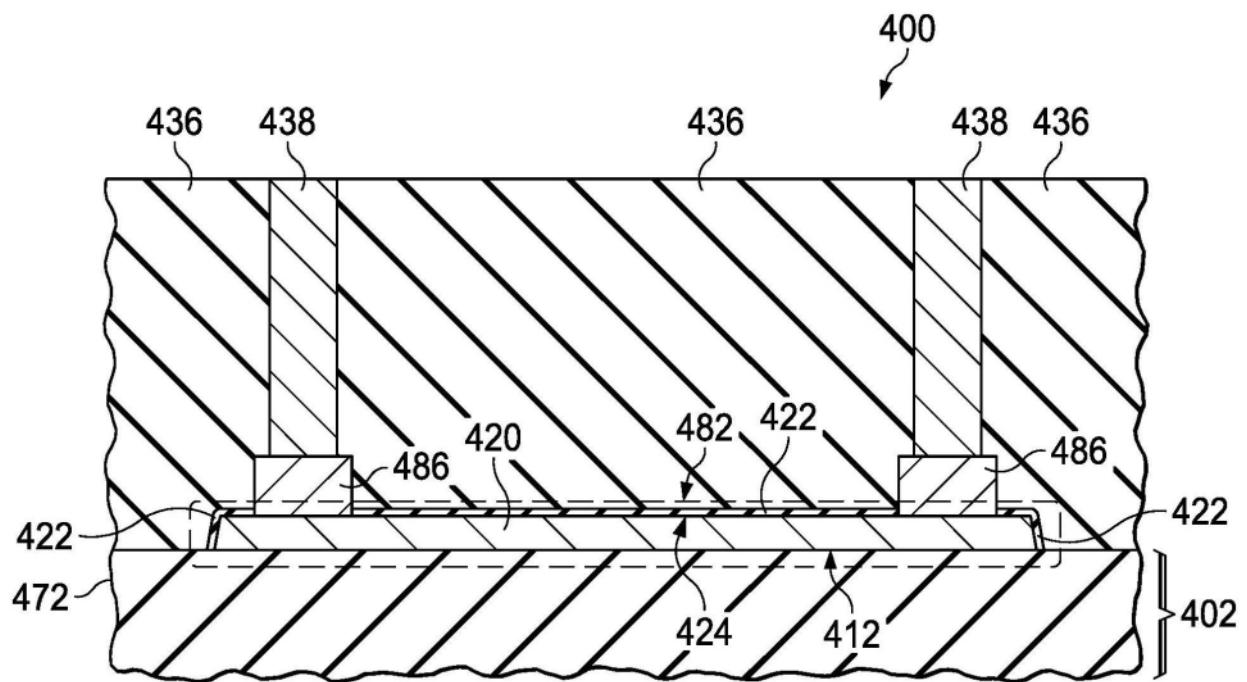

[0009] 图4A至图4H是在另一示例形成方法的连续阶段中描绘的具有含铂层的微电子器件的横截面。

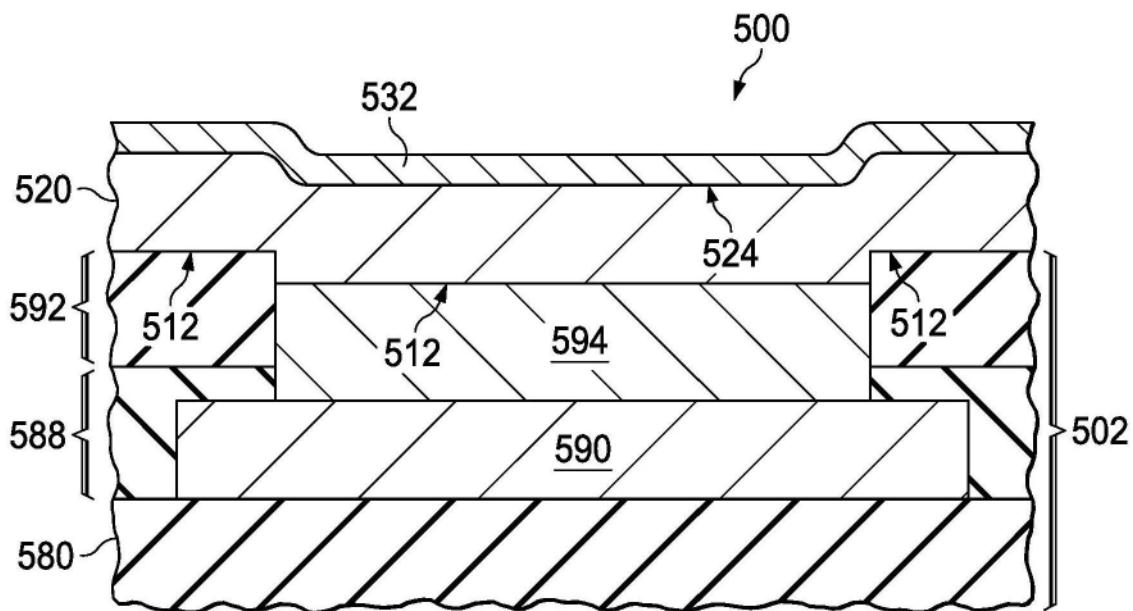

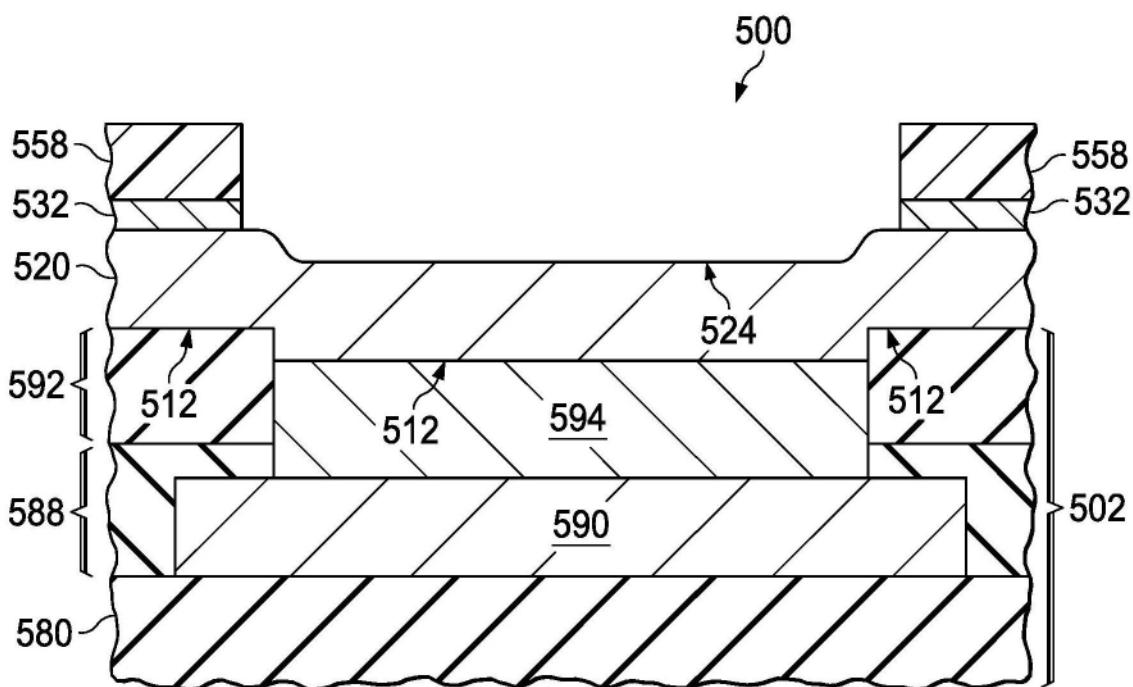

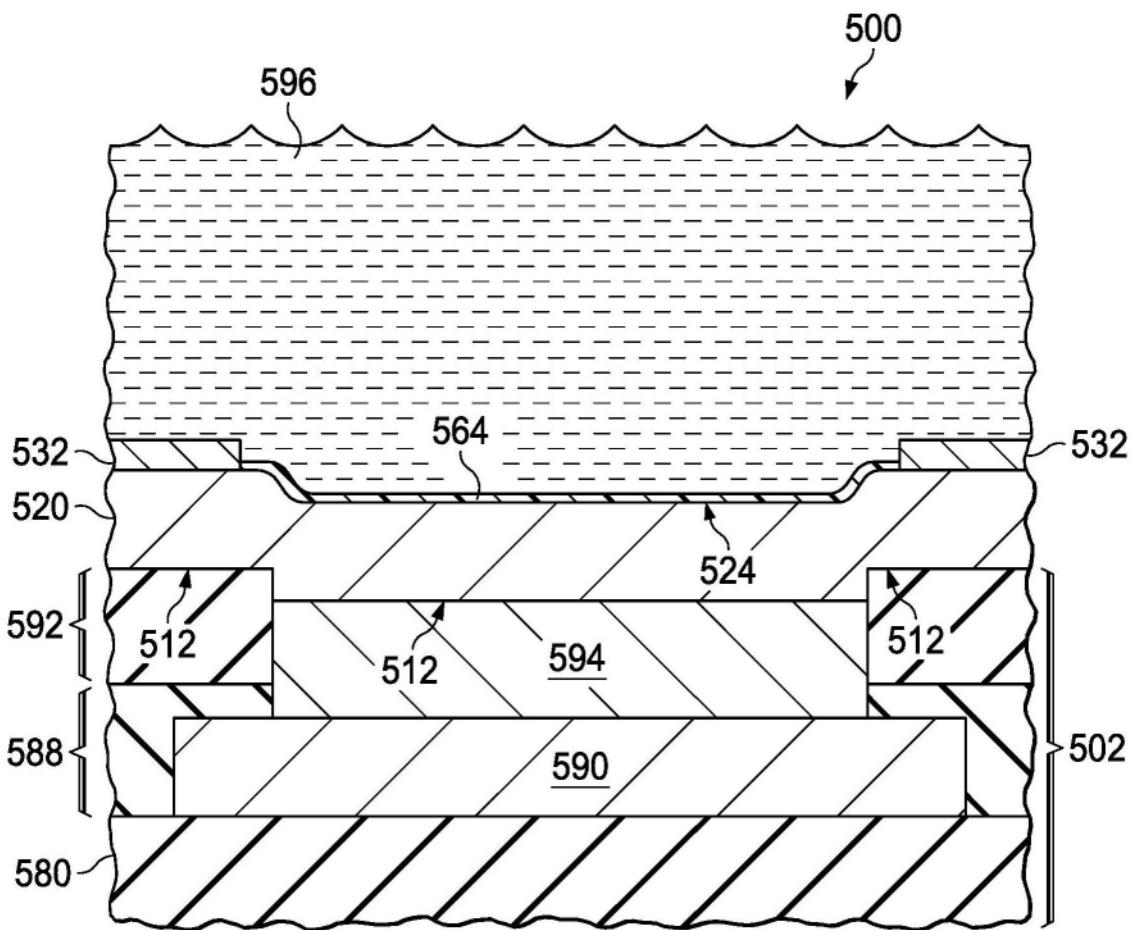

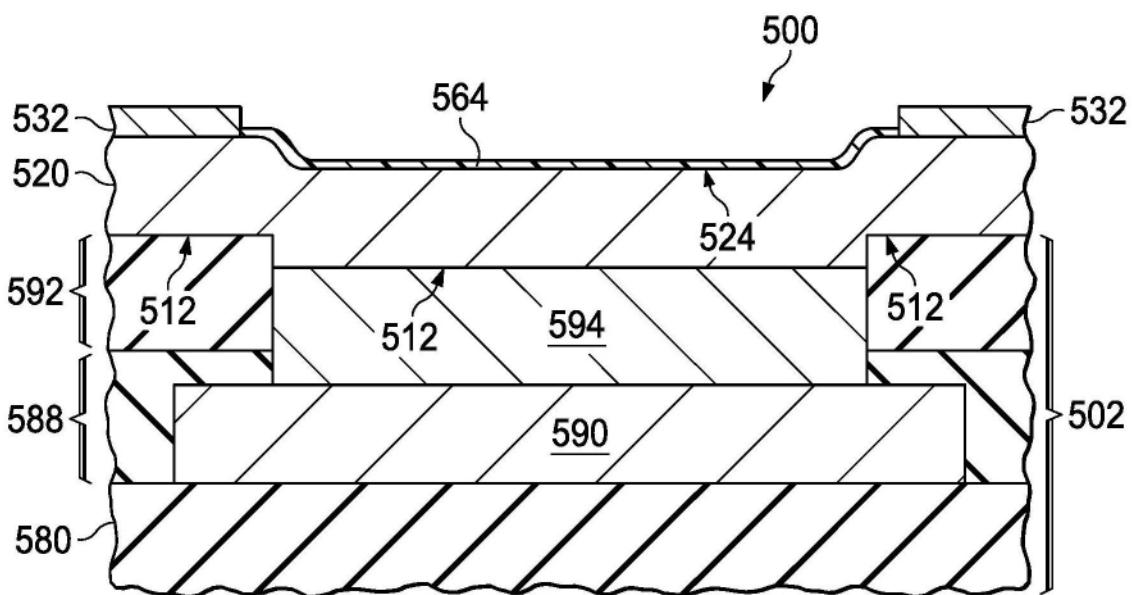

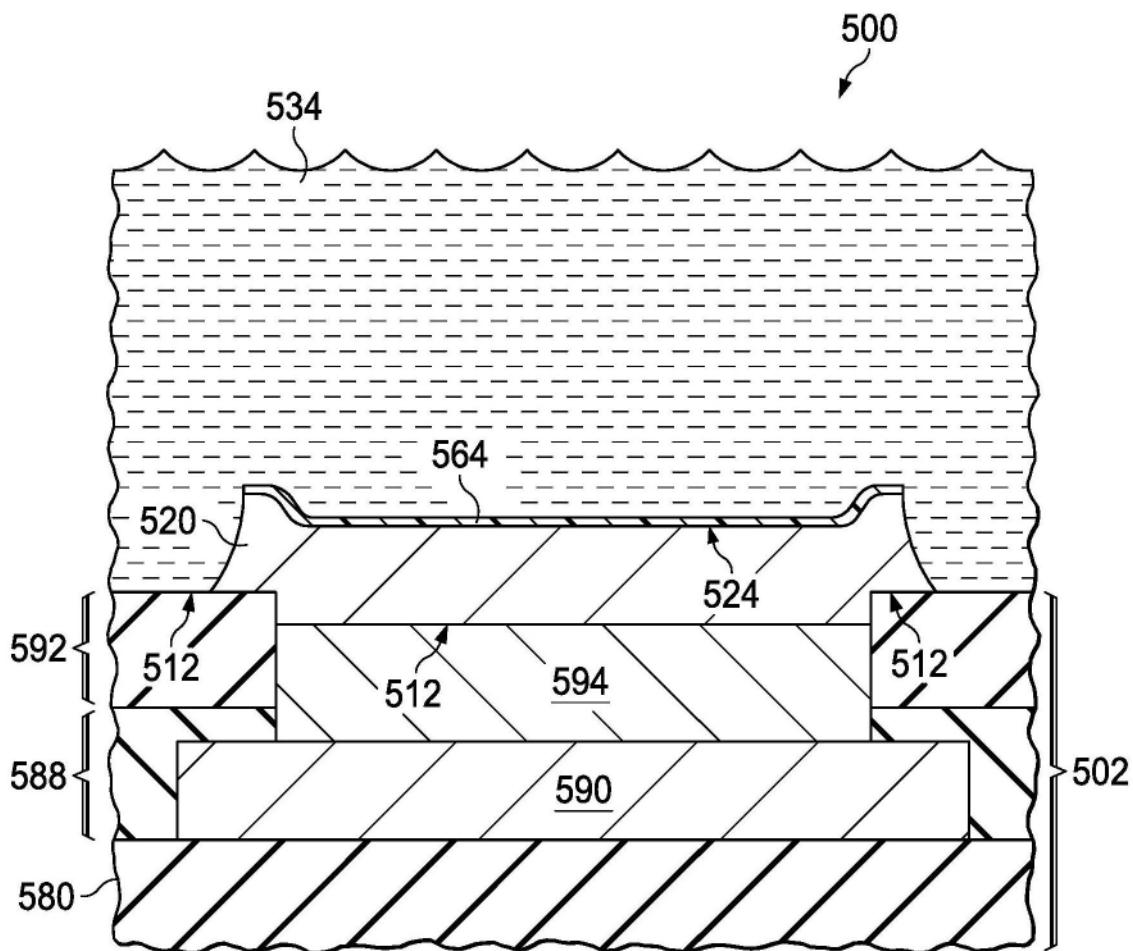

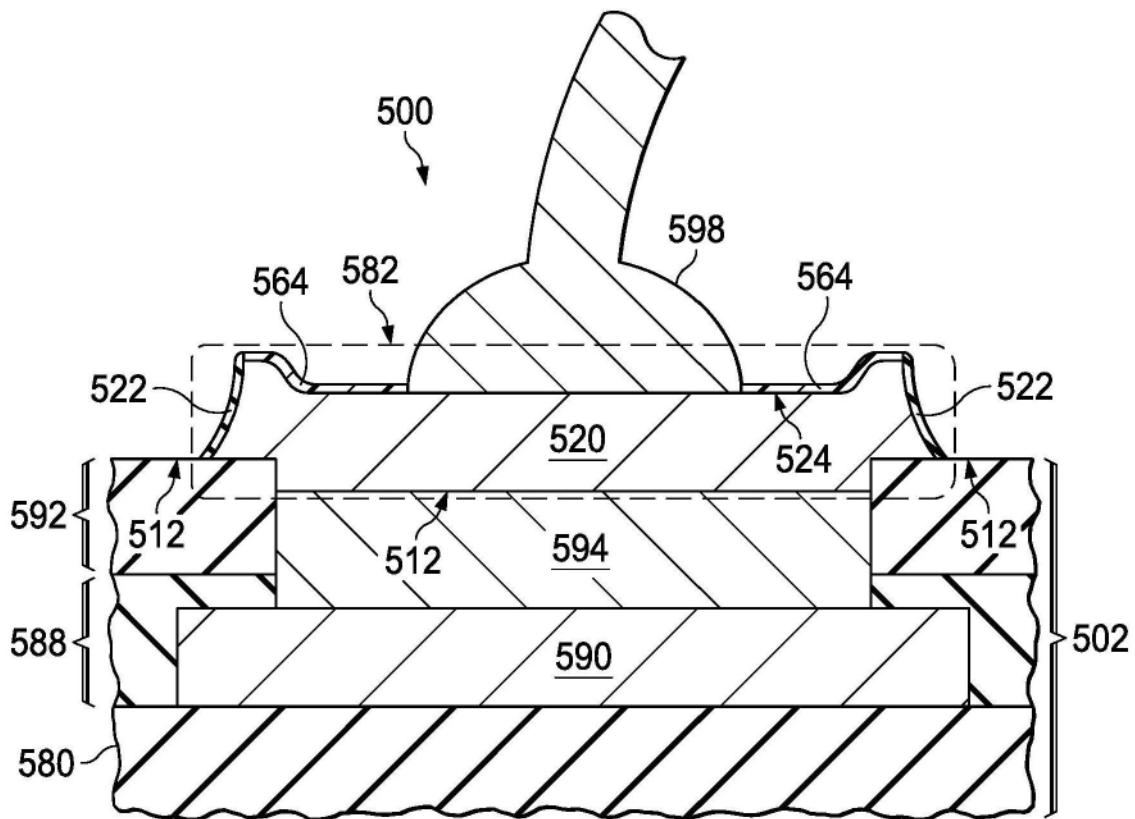

[0010] 图5A至图5F是在另一示例形成方法的连续阶段中描绘的在键合焊盘中具有含铂层的微电子器件的横截面。

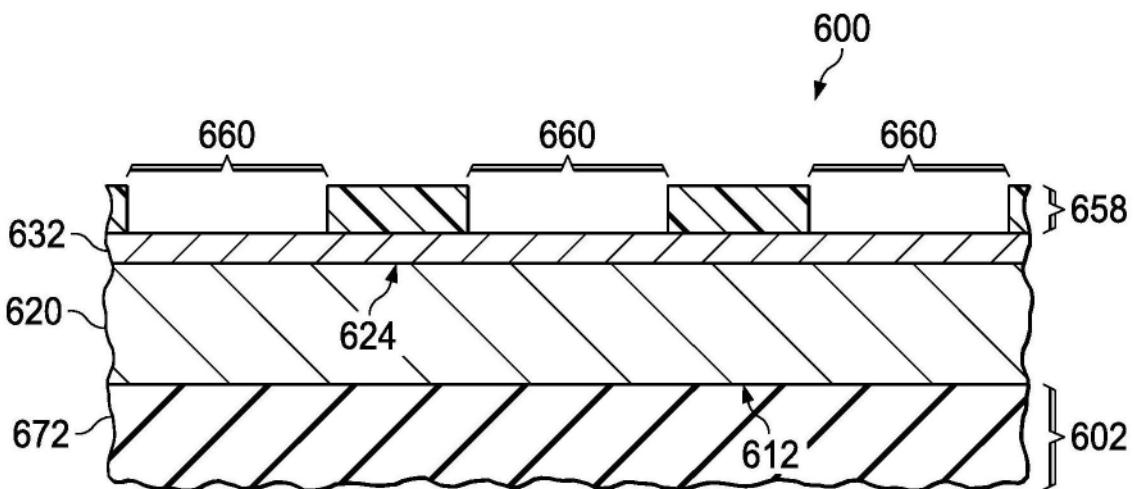

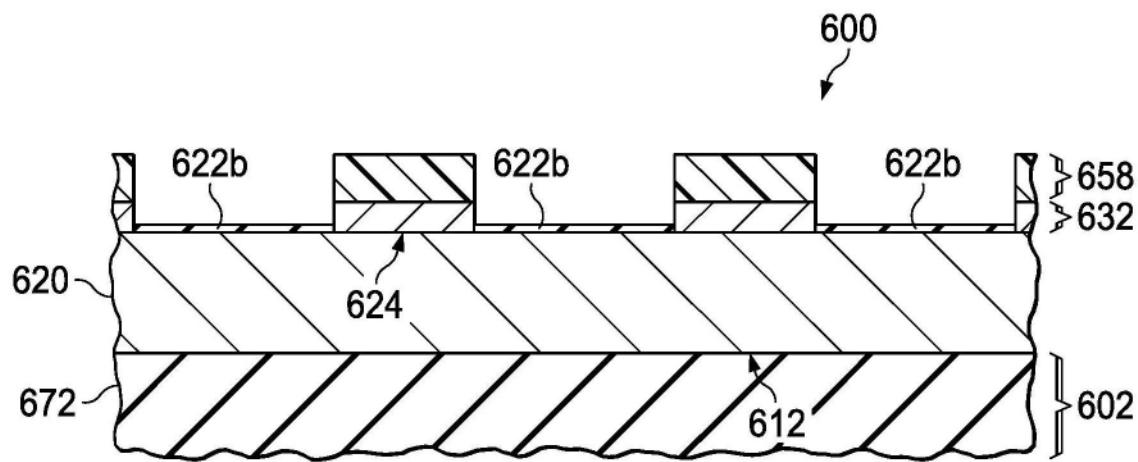

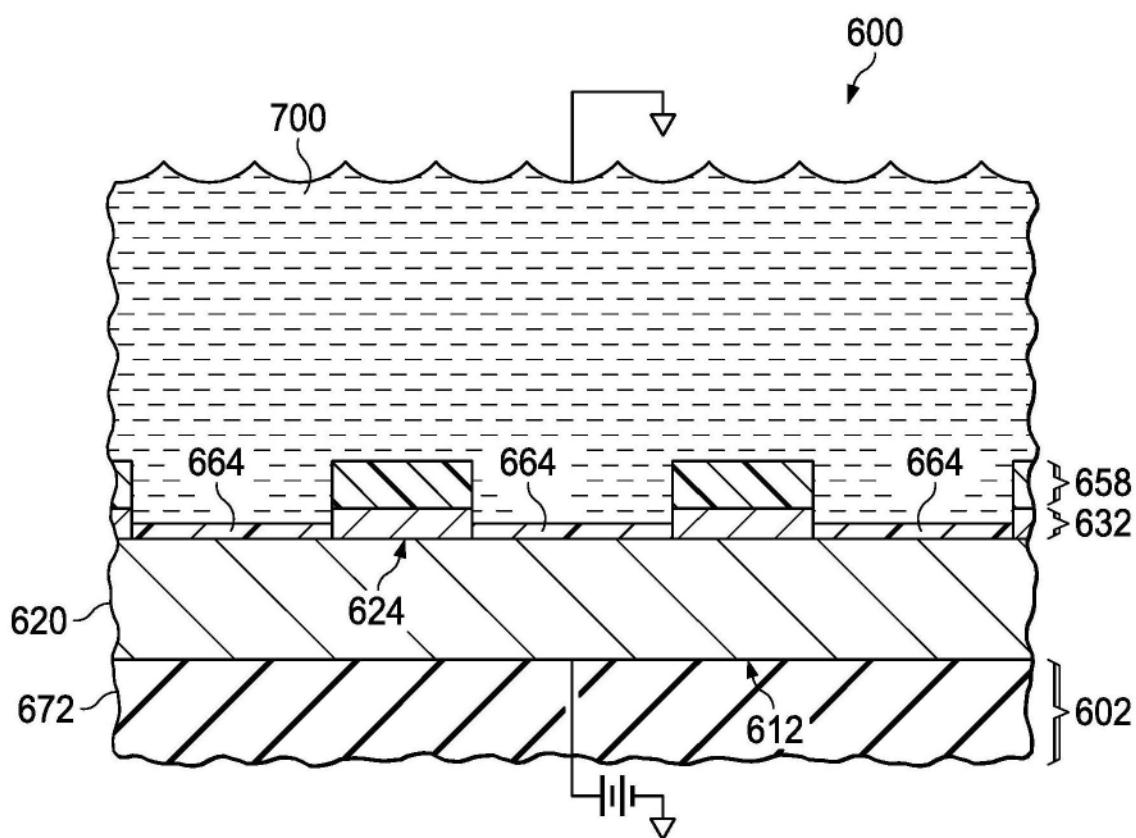

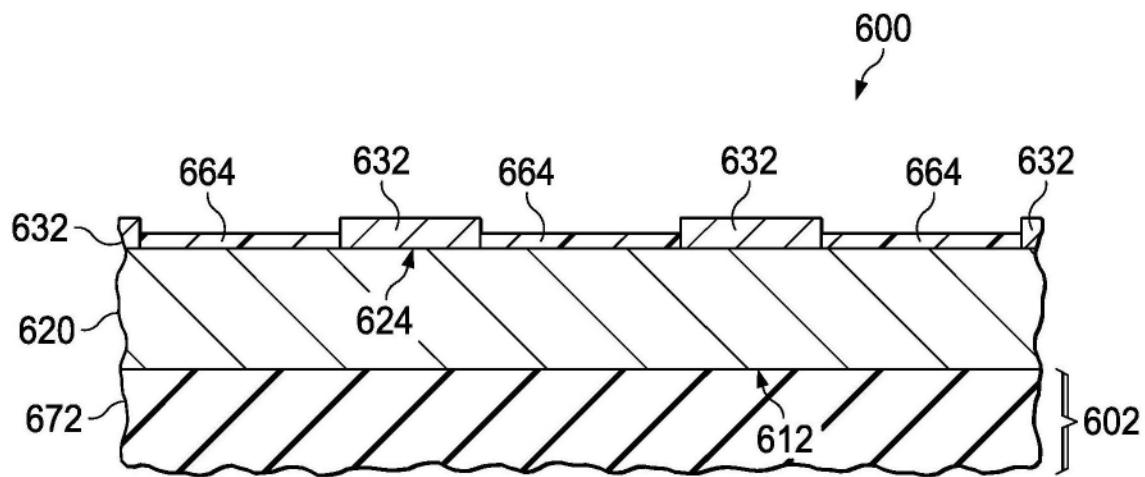

[0011] 图6A至图6I是在又一个示例形成方法的连续阶段中描绘的具有图案化的含铂层

的微电子器件的横截面。

### 具体实施方式

[0012] 附图未按比例绘制。示例实施例不受所示出的动作或事件的排序的限制,因为一些动作或事件可以以不同的顺序发生和/或与其他动作或事件同时发生。此外,并非所有示出的动作或事件都是实施方法所需的。

[0013] 一种包括具有含铂层的组件的微电子器件,其可以通过包括在微电子器件的即时顶部表面上形成含铂层的方法来形成。出于本公开的目的,术语微电子器件的“即时(instant)顶部表面”应理解为指的是在所公开的特定步骤中存在的微电子器件的顶部表面。在微电子器件的形成中,即时顶部表面的身份可以从一个步骤到另一个步骤而改变。在一个步骤中,即时顶部表面可以指暴露的半导体材料和暴露的场氧化物。在另一步骤中,即时顶部表面可以指互连区域中的介电层。在进一步的步骤中,即时顶部表面可以指互连区域上方的保护性外涂(PO)层。

[0014] 在该方法的一个实施方案中,含铂层可以基本上由铂组成。在另一个实施方案中,含铂层可主要包括铂,以及某个其他金属,例如铱、铑、镍、钯或其组合。

[0015] 在含铂层上形成盖层。形成盖层使得盖层和含铂层之间的界面不含氧化铂。出于本公开的目的,术语“氧化铂”被理解为是指任何化学计量或非化学计量的铂的氧化物,包括但不限于PtO<sub>2</sub>、Pt<sub>3</sub>O<sub>4</sub>、PtO和PtO<sub>3</sub>。出于本公开的目的,术语“原生氧化铂”被理解为是指由于在半导体制造设施中在晶圆通常遇到的温度下(例如,从20°C到50°C)暴露于空气而在含铂层上形成的氧化铂。由于含铂层在接近室温下暴露于水中,也可能形成原生氧化铂。原生氧化铂在通常用于在半导体制造工艺中蚀刻铂和含铂材料的湿蚀刻剂中具有低蚀刻速率。此外,原生氧化铂通常不完全阻挡湿蚀刻剂,因此含铂层顶部表面上的原生氧化铂通常导致含铂层的不均匀蚀刻,并且还可能导致在微电子器件上有含铂残留物。

[0016] 在该方法的一个实施方式中,在含铂层上形成原生氧化铂之前,可以在含铂层上形成盖层,例如通过在含铂层暴露于氧化环境(例如空气)之前形成盖层。在另一方面,可以在含铂层上形成盖层之前去除含铂层上的原生氧化铂。

[0017] 盖层具有这样的组成,即在湿蚀刻溶液中去除盖层,该溶液也去除含铂层。在该方法的一个实施方式中,盖层可主要包括铝。在一个示例中,含铝盖层可仅包括铝。在另一个示例中,含铝盖层可以包括用于微电子器件中的蚀刻铝互连的金属,因此可以包括若干原子百分比的硅、铜、钛等。这种用于盖层的组成可以有利地在形成蚀刻铝互连的制造设备中实施。在该方法的另一种实施方式中,盖层可以主要包括铜,或者可以基本上由铜组成。这种用于盖层的组成可以有利地在形成镶嵌铜互连的制造设备中实施,其中溅射的铜膜用于铜电镀工艺的种子层。

[0018] 随后通过湿蚀刻工艺去除盖层和含铂层。湿蚀刻工艺可以使用一份硝酸(HNO<sub>3</sub>)和三至四份盐酸(HCl)的未稀释混合物,通常称为王水。湿蚀刻工艺可以使用由水稀释的硝酸和盐酸的混合物。湿蚀刻工艺可以使用硝酸、盐酸和磷酸(H<sub>3</sub>PO<sub>4</sub>)的混合物。或者,湿蚀刻工艺可以使用过氧化氢和盐酸的混合物。用于湿蚀刻工艺的蚀刻溶液的其他配方在本公开的范围内。由于在盖层和含铂层之间的界面处不存在原生氧化铂,湿蚀刻工艺可以去除盖层并贯穿微电子器件均匀地进入含铂层。在湿蚀刻工艺中,盖层和含铂层的均匀蚀刻速率可

以实现较少的过蚀刻。与在湿蚀刻工艺期间在含铂层上存在原生氧化铂的制造工艺相比，界面处不存在原生氧化铂还可有利地减少微电子器件上的含铂残留物。

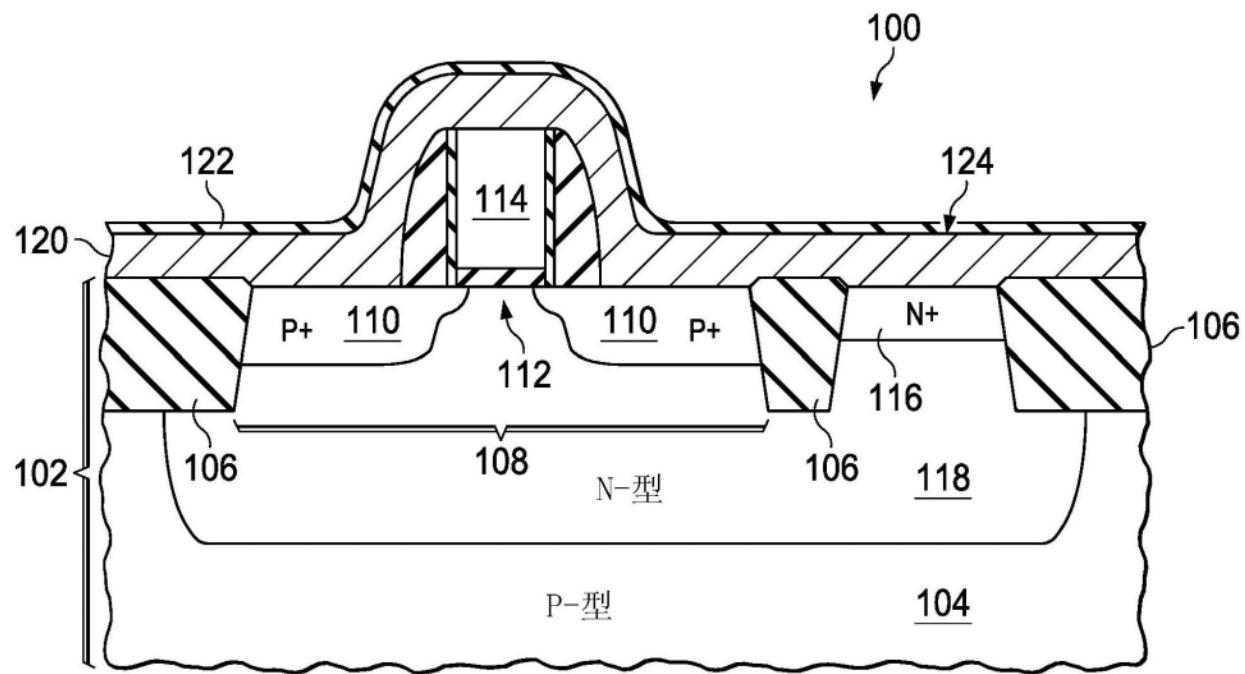

[0019] 图1A至图1H是在一个示例形成方法的连续阶段中描绘的具有含铂层的微电子器件的横截面。参考图1A，微电子器件100具有衬底102，衬底102包括半导体材料104和场氧化物106。场氧化物106可以具有浅沟槽隔离(STI)结构，如图1A所示，或者可以具有硅局部氧化(LOCOS)结构。该示例的微电子器件100包括组件108，在图1A中描绘为p沟道金属氧化物半导体(PMOS)晶体管108。组件108可以具有延伸到衬底102的顶部表面112的半导体材料104的区域；在图1中，两个区域110被描绘为PMOS晶体管108的p型源极和漏极区域110。在该示例中，PMOS晶体管108具有栅极114，栅极114包括延伸到微电子器件100的即时顶部表面的多晶硅。微电子器件100可以包括延伸到衬底的顶部表面112的半导体材料104的附加区域，例如n型阱接触区域116，其提供与在PMOS晶体管108下面延伸的n型阱118的电连接。延伸到衬底102的顶部表面112或延伸到微电子器件100的即时顶部表面的半导体材料的其他区域，例如n沟道金属氧化物半导体(NMOS)晶体管的源极区和漏极区，双极结型晶体管的集电极区、基极区和发射极区以及衬底接触区域都在本示例的范围内。

[0020] 含铂层120形成在微电子器件100的即时顶部表面上，在衬底102的顶部表面112处接触衬底102的暴露的半导体材料，包括PMOS晶体管108的源极区和漏极区110以及阱接触区116。含铂层120还可以接触PMOS晶体管108的栅极114中的多晶硅，如图1A所示。在该实例的一个版本中，含铂层120可以基本上由铂组成。在另一版本中，含铂层120可主要包括铂，具有10%或更少的镍或其他金属。例如，含铂层120可以具有20纳米至200纳米的厚度。含铂层120可以例如使用溅射工艺、蒸发工艺或金属有机化学气相沉积(MOCVD)工艺形成。用于形成含铂层120的其他工艺在该实例的范围内。含铂层120具有与衬底102的顶部表面112相对定位的顶部表面124。

[0021] 在形成含铂层120之后，含铂层120可暴露于氧化环境(例如空气)，例如，通过从形成含铂层120的设备中移除衬底102。暴露于氧化环境可导致在含铂层120的顶部表面124上形成原生氧化铂122。在该示例中，顶部表面124是与含铂层120和衬底102的顶部表面112之间的边界相对定位的含铂层120的表面。原生氧化铂122可以是例如一到两个单层厚。

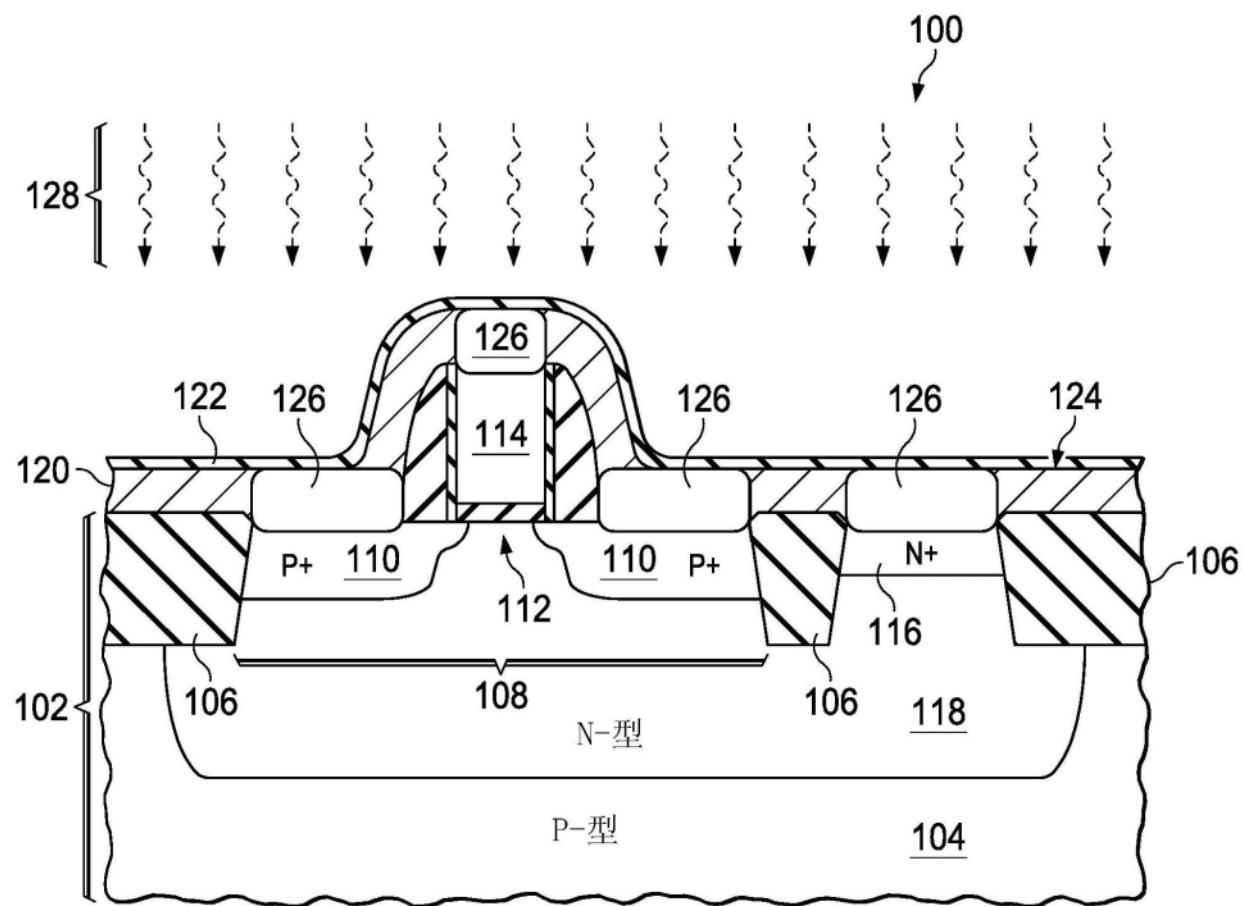

[0022] 参考图1B，衬底102和含铂层120被加热，使得含铂层120中的铂与在衬底102的顶部表面112处暴露的半导体材料中的硅反应，以形成跨越含铂层120和衬底102的顶部表面112之间边界的硅化铂126。

[0023] 在该示例中，硅化铂126形成在PMOS晶体管108的源极区和漏极区110，以及阱接触区116上，并且可选地在PMOS晶体管108的栅极114上，以及在微电子器件100的其他暴露的半导体区上。例如，可以通过辐射加热工艺128加热衬底102和含铂层120，如图1B所示，在快速热处理工具中，或通过熔炉工艺。在形成硅化铂126的工艺期间，原生氧化铂122的厚度可以增加，厚度可以减小，或者可以不显著改变厚度，这取决于在衬底102和含铂层120被加热时的环境条件。由于硅原子的氧化，可以在硅化铂126上方形成薄的二氧化硅层。

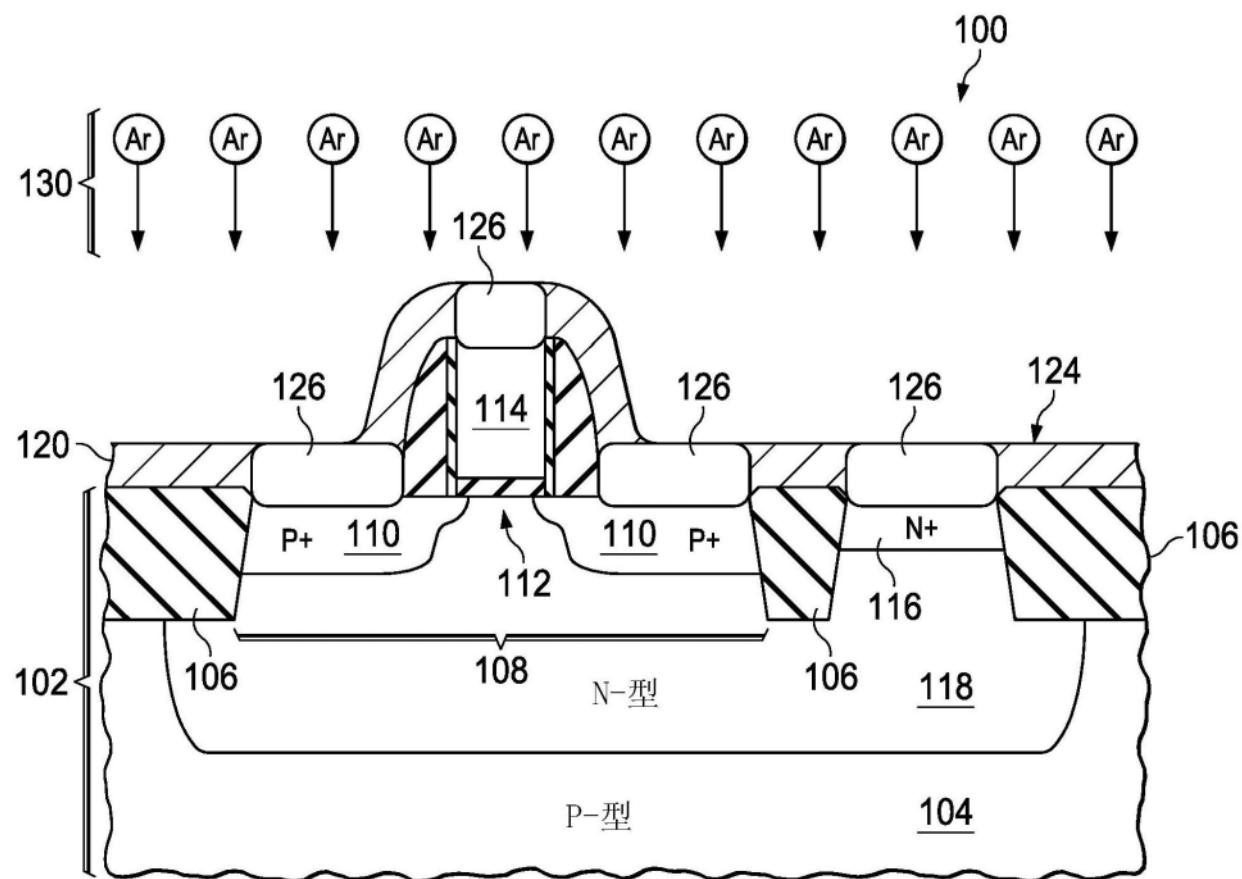

[0024] 参考图1C，微电子器件100暴露于使用离子130(例如图1C中示意性描绘的氩离子)的溅射蚀刻工艺。离子130去除图1B的原生氧化铂122，留下含铂层120的顶部表面124不含氧化铂。例如，溅射蚀刻工艺可以持续3秒至10秒，以令人满意地从含铂层120的顶部表面124去除原生氧化铂122。在硅化铂126上方的薄的二氧化硅层被去除之前终止溅射蚀刻工

艺。

[0025] 参考图1D, 盖层132形成在含铂层120的顶部表面124上, 使得盖层132和含铂层120之间的界面不含氧化铂。例如, 这可以通过在图1B的原生氧化铂122被去除之后形成盖层132而不将含铂层120的顶部表面124暴露于氧化环境来实现。在该示例的一个版本中, 可以在单个工艺工具中去除原生氧化铂122并且可以形成覆盖层132, 其中微电子器件100在整个过程中保持在非氧化环境中。

[0026] 盖层132可在随后用于去除至少一部分含铂层120的相同湿蚀刻剂中蚀刻。盖层132在湿蚀刻剂中的蚀刻速率是含铂层120在湿蚀刻剂中的蚀刻速率的至少两倍。在该示例的一个版本中, 盖层132可以主要包括铝, 并且可以例如通过溅射形成。例如, 盖层132可以具有与微电子器件100的蚀刻铝互连线中的铝层类似的组成, 其中盖层132包括至少90%的铝并且具有百分之几的硅、钛、铜或诸如此类。在该示例的另一版本中, 盖层132可以基本上由铝组成, 并且可以例如通过蒸发或溅射形成。在该示例的又一版本中, 盖层132可以主要包括铜, 并且可以例如通过溅射或蒸发形成。例如, 盖层132可以具有与微电子器件100的镶嵌铜互连线中的铜种子层类似的组成。

[0027] 盖层132的厚度足以提供贯穿微电子器件100的含铂层120的均匀去除。在该示例的一个方面, 这可以通过足以完全覆盖含铂层120的顶部表面124的厚度来实现。在另一方面, 这可以通过足以防止氧化剂扩散(例如防止氧气( $O_2$ )和水蒸气( $H_2O$ )通过盖层132扩散到含铂层120的顶部表面124)的厚度来实现。在另一方面, 这可以通过足以在盖层132中保持未氧化金属层, 直到通过湿蚀刻剂除去含铂层120的厚度来实现。在其中盖层132主要包括铝的该示例的一个版本中, 盖层132可以是至少10纳米厚。在其中盖层132主要包括铜的该示例的一个版本中, 盖层132可以是至少6纳米厚。

[0028] 盖层132的厚度范围可以进一步受到其他考虑因素的影响。在该示例的一个方面, 盖层132可以足够厚以提供用于形成盖层132的所需工艺宽容度, 其可以通过50纳米至100纳米的厚度获得, 这取决于用于形成盖层132的工艺。在另一方面, 盖层132可以足够厚以在微电子器件100的非平面表面上提供所需的覆盖, 例如在PMOS晶体管108的栅极114的侧面上, 其可以通过100纳米至150纳米的厚度获得, 这取决于用于形成盖层132的工艺。盖层132的厚度大于150纳米在本示例的范围内。

[0029] 此时可以存储或以其他方式处理微电子器件100, 而不在含铂层120的顶部表面124处形成氧化铂。这可以有利地实现用于通过允许变化用于后续工艺步骤的等待时间来形成微电子器件100的工艺顺序的灵活性, 因此降低了操作正在形成微电子器件100的制造设备的总成本。

[0030] 参考图1E, 使用湿蚀刻剂134的湿蚀刻工艺去除了盖层132。在该示例的一个版本中, 湿蚀刻剂134可以是一份硝酸和三至四份盐酸的未稀释混合物, 其可以提供期望的快速蚀刻速率。在另一版本中, 湿蚀刻剂134可以是用水稀释的硝酸和盐酸的混合物, 其可以提供较低的蚀刻速率, 从而实现更严格的工艺控制。在又一版本中, 湿蚀刻剂134可以是硝酸, 盐酸和磷酸的混合物。在另一个版本中, 湿蚀刻剂134可以是过氧化氢和盐酸的混合物。湿蚀刻剂134的其他配方在该示例的范围内。图1E描绘了通过去除盖层132的中途的湿蚀刻工艺。继续湿蚀刻工艺直到去除含铂层120。

[0031] 参考图1F, 继续湿蚀刻工艺, 使得图1E的剩余盖层132可以被完全去除并且湿蚀刻

工艺去除含铂层120。图1F描绘了通过去除含铂层120的中途的湿蚀刻工艺。湿蚀刻工艺可以平滑且均匀地通过盖层132进入含铂层120，因为盖层132下面的含铂层120的图1E的顶部表面124不含氧化铂，如参考

[0032] 图1C和图1D所公开的。湿蚀刻剂134可以以比盖层132低得多的速率去除含铂层120，例如，速率是其1/10至1/100。湿蚀刻工艺不去除硅化铂126，因为硅化铂126上的薄二氧化硅层阻挡了湿蚀刻剂134。

[0033] 参考图1G，继续湿蚀刻工艺，使得图1F的剩余含铂层120被完全去除。湿蚀刻剂134可以去除一部分硅化铂126；湿蚀刻工艺终止并且微电子器件100被冲洗，在适当位置留下足够量的（例如10纳米至100纳米）硅化铂126，用于微电子器件100的适当功能。与在含铂层120的顶部表面上存在氧化铂的工艺顺序相比，均匀地去除含铂层120可以有利地实现从包含微电子器件100的晶圆的所有区域去除含铂层120所需的较低的过蚀刻时间。因为在过蚀刻期间可以去除一部分的硅化铂126，所以减少的过蚀刻时间可以在包含微电子器件100的晶圆上提供更一致的硅化铂126厚度。

[0034] 参考图1H中，衬底102的顶部表面112可以有利地不含含铂残留物，因为图1E的盖层132下面的含铂层120的图1E的顶部表面124不含氧化铂；氧化铂的存在可能导致形成含铂残留物。

[0035] 可以在微电子器件100的即时顶部表面上形成金属前介电（PMD）层136。PMD层136可以包括介电材料的一个或更多个子层，例如氮化硅PMD衬垫（liner），通过高密度等离子体或使用正硅酸乙酯（TEOS）和臭氧的化学气相沉积（CVD）工艺形成的一层基于二氧化硅的材料，诸如磷硅酸盐玻璃（PSG）或硼磷硅酸盐玻璃（BPSG）的一层基于二氧化硅的材料，以及氮化硅、氮氧化硅、碳化硅或碳化硅氮化物的盖层。

[0036] 可以通过PMD层136形成触点138，以与硅化铂126形成电连接。可以通过蚀刻穿过PMD层136的接触孔，并通过溅射或电离金属等离子体（IMP）工艺在PMD层136上并延伸到接触孔中形成钛衬垫140来形成触点138。可以通过反应溅射或原子层沉积（ALD）在钛衬垫上形成氮化钛衬垫142。然后可以通过MOCVD工艺在氮化钛衬垫上形成钨层144，填充接触孔。通过钨CMP工艺从PMD层136的顶部表面上去除钨144、氮化钛衬垫142和钛衬垫140，在接触孔中留下钨144、氮化钛衬垫142和钛衬垫140以提供触点138。

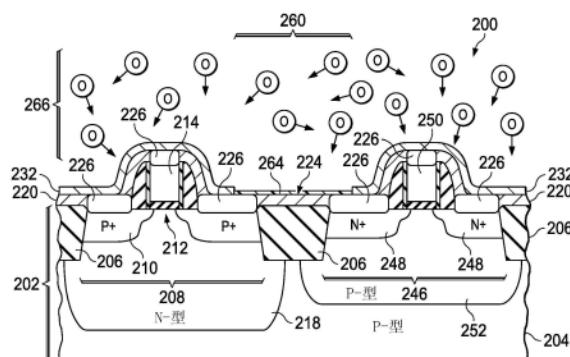

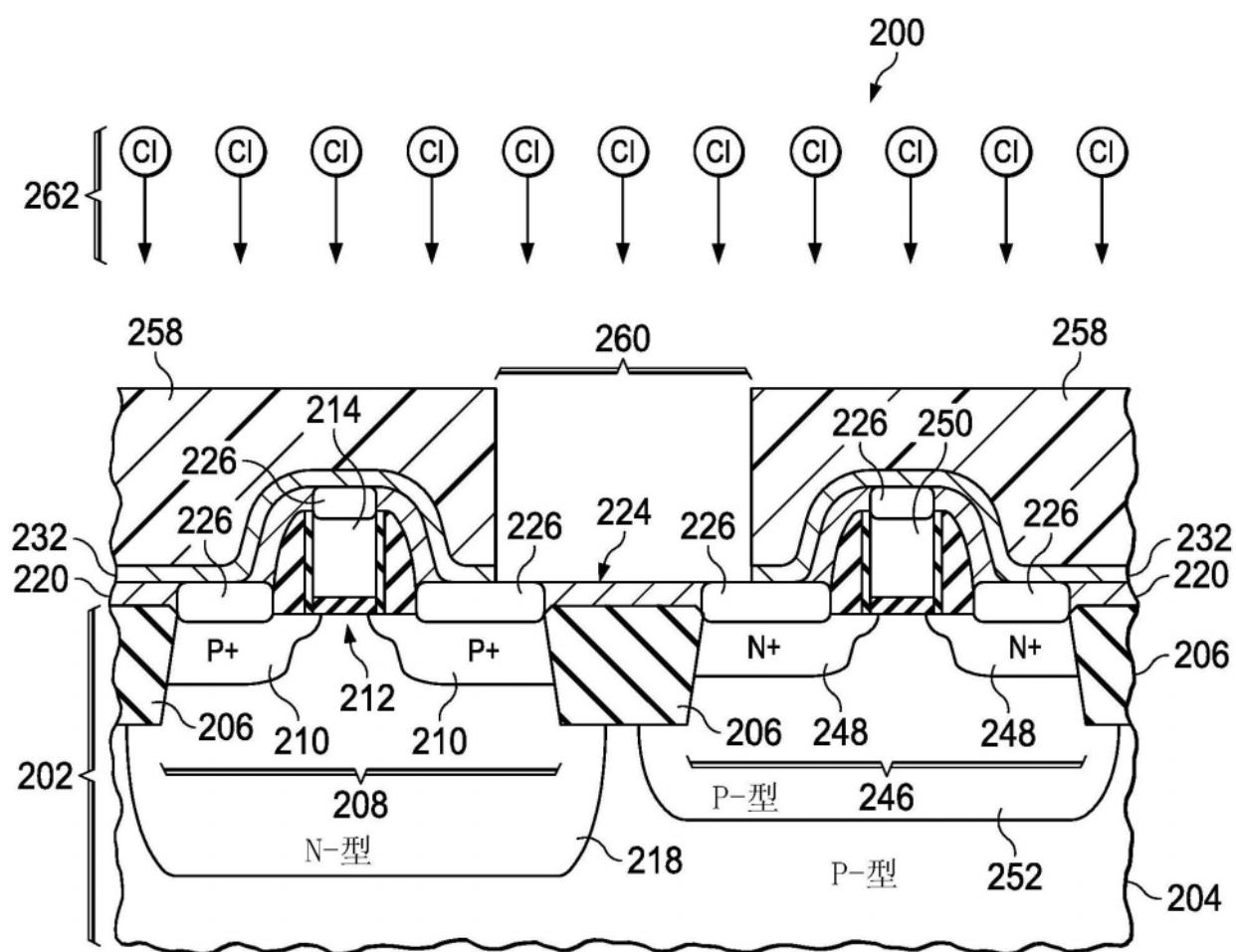

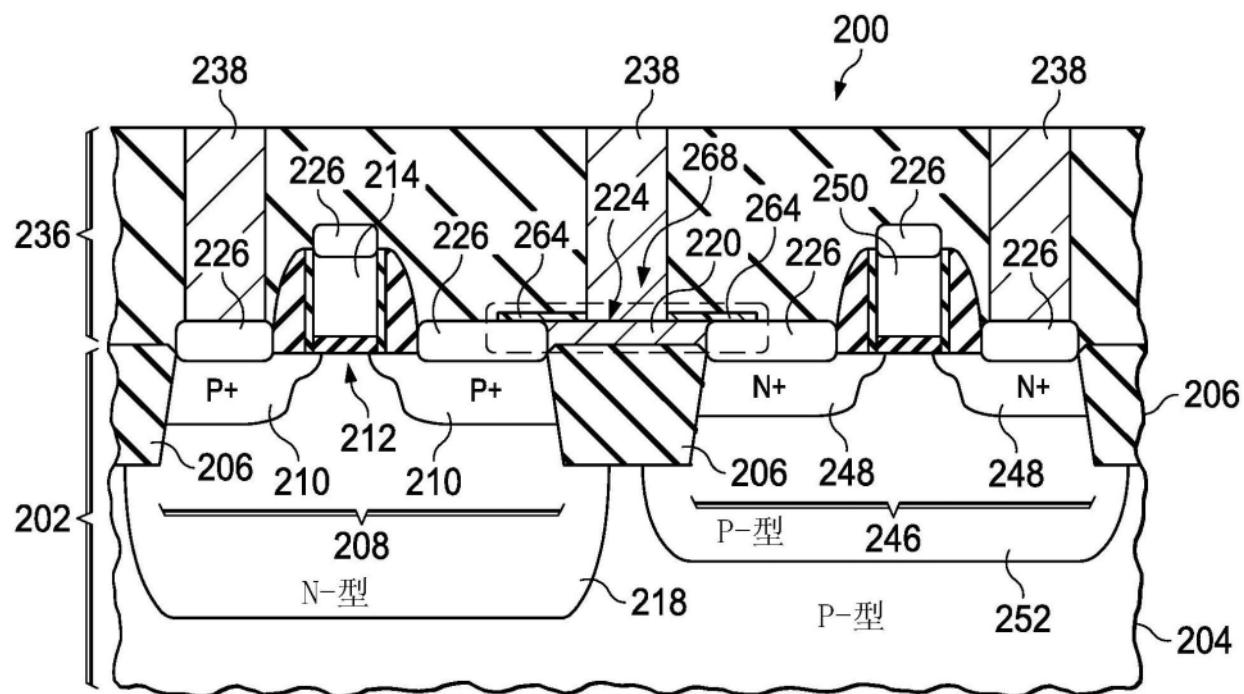

[0037] 图2A至图2H是在另一示例形成方法的连续阶段中描绘的具有含铂层的微电子器件的横截面。参考图2A，微电子器件200具有衬底202，衬底202包括半导体材料204和场氧化物206。该示例的微电子器件200包括第一组件208，在图2A中描述为PMOS晶体管208，其中p型源极区和漏极区域210延伸到衬底202的顶部表面212，并且栅极214包括多晶硅。该示例的微电子器件200还包括第二组件246，图2A中描述为NMOS晶体管246，具有延伸到衬底202的顶部表面212的n型源极区和漏极区248，以及包括多晶硅的栅极250。衬底202可以包括在PMOS晶体管208下面的n型阱218，以及在NMOS晶体管246下面的p型阱252。延伸到衬底202的顶部表面212或延伸到微电子器件200的即时顶部表面的半导体材料的其他区域，双极结型晶体管的阱接触区、集电极区、基极区和发射极区以及衬底接触区都在本例的范围内。

[0038] 含铂层220形成在微电子器件200的即时顶部表面上，在顶部表面212处接触衬底202的暴露的半导体材料，包括PMOS晶体管208的源极区和漏极区210以及NMOS晶体管246的源极区和漏极区248。如图2A所示，含铂层220还可以接触PMOS晶体管208的栅极214中的多

晶硅和NMOS晶体管246的栅极250中的多晶硅。含铂层220可以基本上由铂组成,或者可以主要包括铂,以及少于10%的另一种金属或多种金属。含铂层220的厚度可以为例如,20纳米至200纳米。原生氧化铂222存在于含铂层220的顶部表面224上。

[0039] 参考图2B,衬底202和含铂层220被加热,使得含铂层220中的铂与在衬底202的顶部表面212处暴露的半导体材料中的硅反应,以形成跨越含铂层220和衬底202的顶部表面212之间边界的硅化铂226。在该示例中,在PMOS晶体管208的源极区和漏极区210以及NMOS晶体管246的源极区和漏极区248上形成硅化铂226,可选地在PMOS晶体管208的栅极214上和NMOS晶体管246的栅极250上形成硅化铂226。可以加热衬底202和含铂层220,例如,如图2C所示由炉壁256通过熔炉工艺254,或通过快速热处理工具中的辐射加热工艺,或通过另一加热工艺。

[0040] 参考图2C,图2B中的原生氧化铂222被去除,例如通过参考图1C所公开的溅射蚀刻工艺。或者,可以通过另一种工艺去除原生氧化铂222,例如在真空中加热含铂层220。盖层232形成在含铂层220的顶部表面224上,使得盖层232和含铂层220之间的界面不含氧化铂。在该示例中,这可以通过在去除原生氧化铂222之后形成盖层232而不将含铂层220的顶部表面224暴露于氧化环境来实现。盖层232可在随后用于去除至少一部分含铂层220的相同湿蚀刻剂中蚀刻。盖层232可具有如参考图1D所公开的组成和厚度,并且可以通过参考图1D公开的任何工艺形成。

[0041] 参考图2D,在盖层232上方形成蚀刻掩模258。蚀刻掩模258暴露出区域260,用于PMOS晶体管208的源极区和漏极区210中的一个与NMOS晶体管246的源极区和漏极区248中的一个之间的局部互连。蚀刻掩模258可以进一步暴露额外的区域以用于额外的局部互连。蚀刻掩模258可以包括通过光刻工艺形成的光刻胶,并且可以可选地包括抗反射层,例如底部抗反射涂层(BARC)。或者,蚀刻掩模258可以包括硬掩模材料,例如二氧化硅、氮化硅、无定形碳等。

[0042] 在由蚀刻掩模258暴露的区域中去除盖层232,暴露含铂层220的顶部表面224。在其中盖层232包括铝的该示例的一个版本中,可以通过使用氯离子262的反应离子蚀刻(RIE)工艺去除盖层232,如图2D所示。在其中盖层232包括铝的该示例的一个版本中,可以通过湿蚀刻去除盖层232。用于去除由蚀刻掩模258暴露的区域中的盖层232的其他工艺在该示例的范围内。

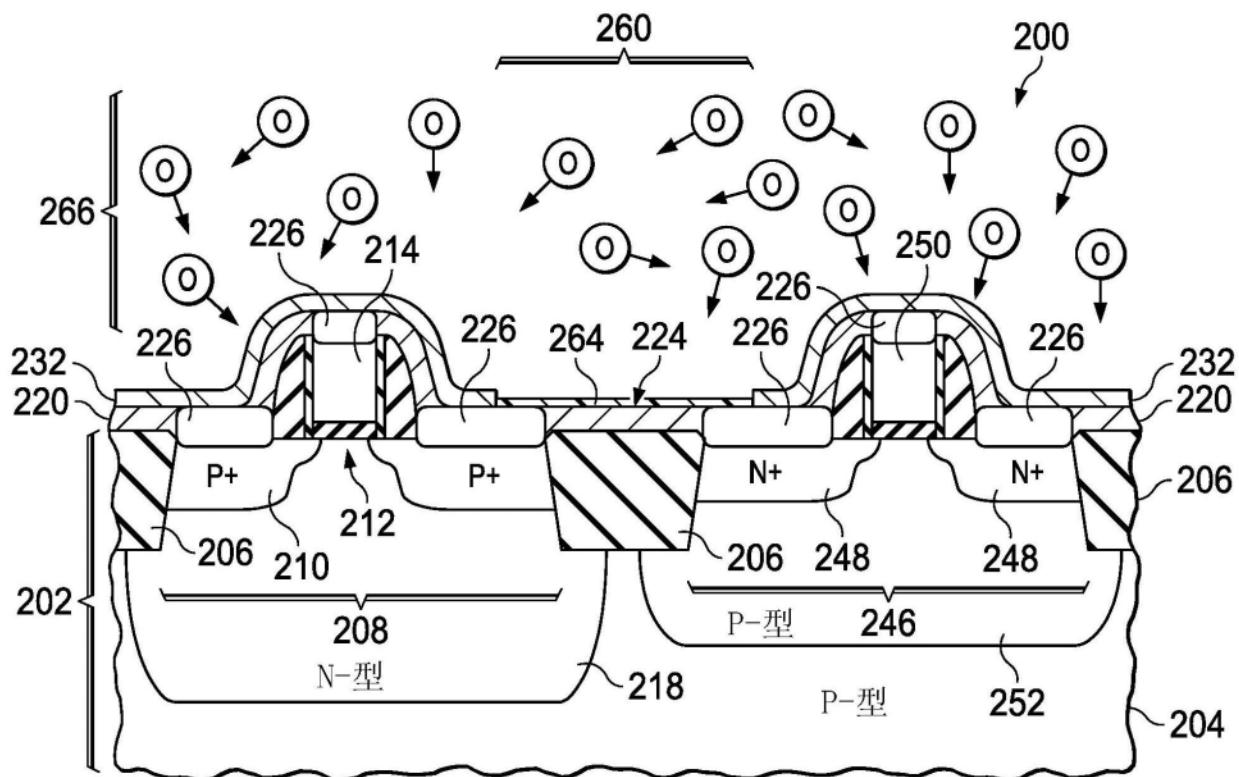

[0043] 随后例如通过使用氧自由基的等离子体工艺(例如灰化工艺)去除蚀刻掩模258。或者,可以通过湿法清洁工艺和氧等离子体工艺的组合来去除蚀刻掩模258。去除蚀刻掩模258可导致在已经去除盖层232的区域中的含铂层220的顶部表面224上形成氧化铂层。

[0044] 参考图2E,掩模氧化铂264形成在被盖层232暴露的含铂层220的顶部表面224上。出于本公开的目的,术语“掩模氧化铂”是指有意形成的氧化铂,其足够连续且足够厚以阻挡随后用于蚀刻含铂层220的湿蚀刻剂。掩模氧化铂264的一部分或全部可通过用于去除图2D的蚀刻掩模258的工艺形成。如果需要额外的掩模氧化铂264,则微电子器件200可以被暴露于氧化环境266,例如氧等离子体,如图2E中示意性所示,在去除蚀刻掩模258之后,在升高的温度下的氧,由紫外光、一氧化碳(CO)活化的臭氧等。掩模氧化铂264可以延伸到由盖层232暴露的硅化铂226上,如图2E中所示。

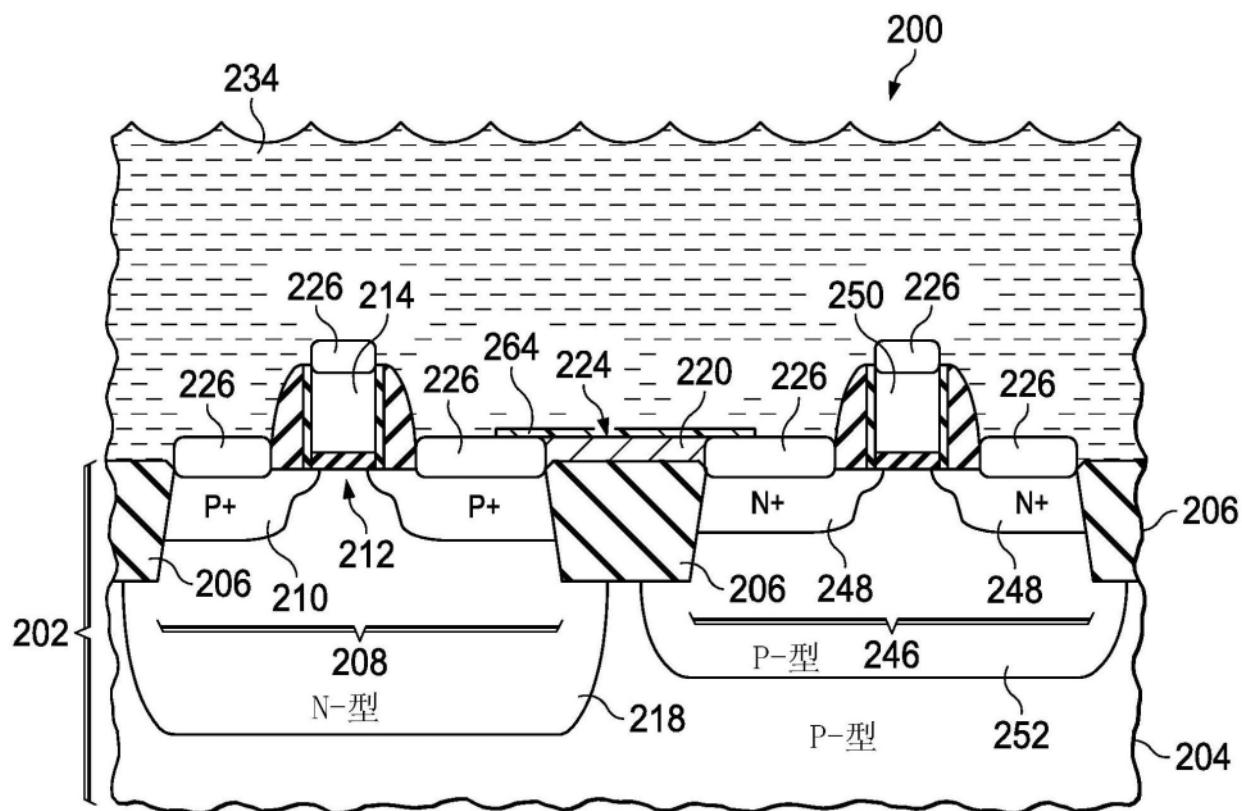

[0045] 参考图2F,使用湿蚀刻剂234的湿蚀刻工艺去除图2E的盖层232,并且去除由掩模

氧化铂264暴露的含铂层220,如参考图1E到图1G所述。湿蚀刻剂234可以具有参考图1E公开的任何组成。图2F描绘在完成湿蚀刻工艺时的微电子器件200。掩模氧化铂264防止湿蚀刻剂234去除掩模氧化铂264下面的含铂层220,因为掩模氧化铂264在湿蚀刻剂234中具有非常低的蚀刻速率。

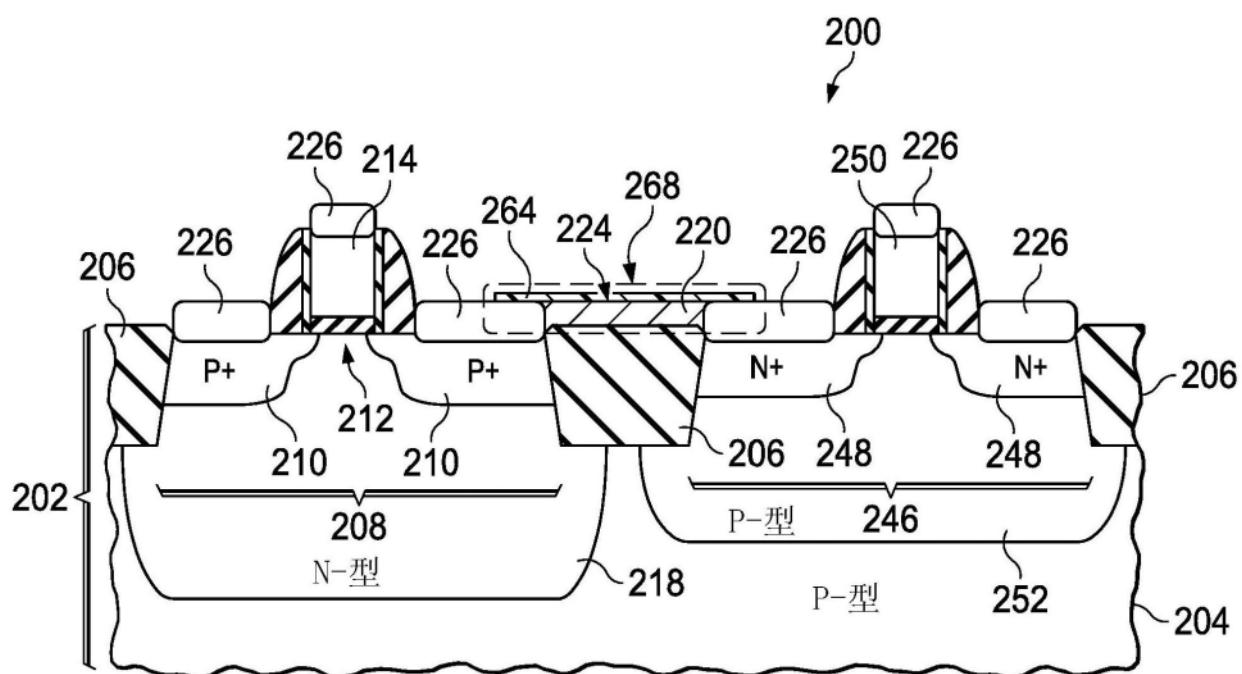

[0046] 图2G描绘图2F的湿蚀刻工艺完成之后的微电子器件200。剩余的含铂层220提供局部互连268,其电连接PMOS晶体管208的源极区和漏极区210中的一个上的硅化铂226和NMOS晶体管246的源极区和漏极区中的一个上的硅化铂226。从用于形成硅化铂226的含铂层220形成局部互连268可以在局部互连268和硅化铂226之间提供低接触电阻,因此有利地提供低电阻,用于PMOS晶体管208的源极区和漏极区210中的一个与NMOS晶体管246的源极区和漏极区248中的一个之间的电连接。

[0047] 参考图2H,PMD层236可以形成在微电子器件200的即时顶部表面上。可以通过PMD层236形成触点238,以与硅化铂226形成电连接。PMD层236和触点238可以具有与参考图1H所公开的结构类似的结构。硅化铂226可以不含含铂残留物,这可以有利地提供在触点238和硅化铂226之间的一致电阻。在该示例中,触点238中的一个或更多个可以形成在局部互连268上,如图2H所示。在形成触点238期间,通过形成接触孔的工艺,以及通过在接触孔中沉积接触金属之前的随后溅射蚀刻工艺来去除局部互连268上的掩模氧化铂264,以在触点238和局部互连268之间提供低电阻。

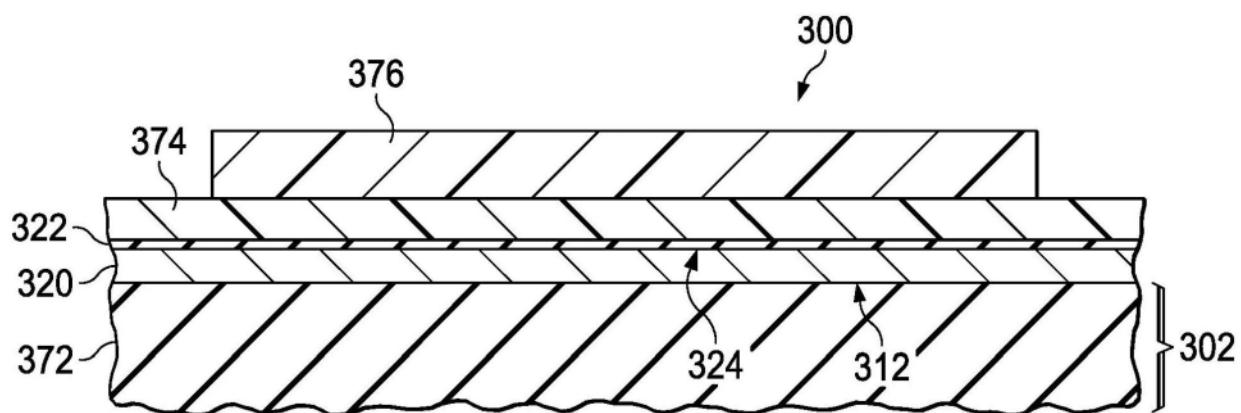

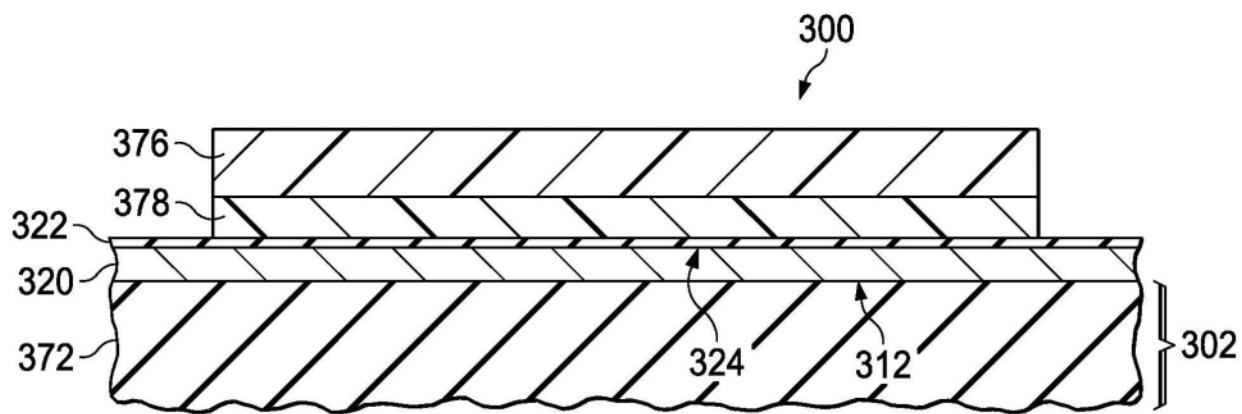

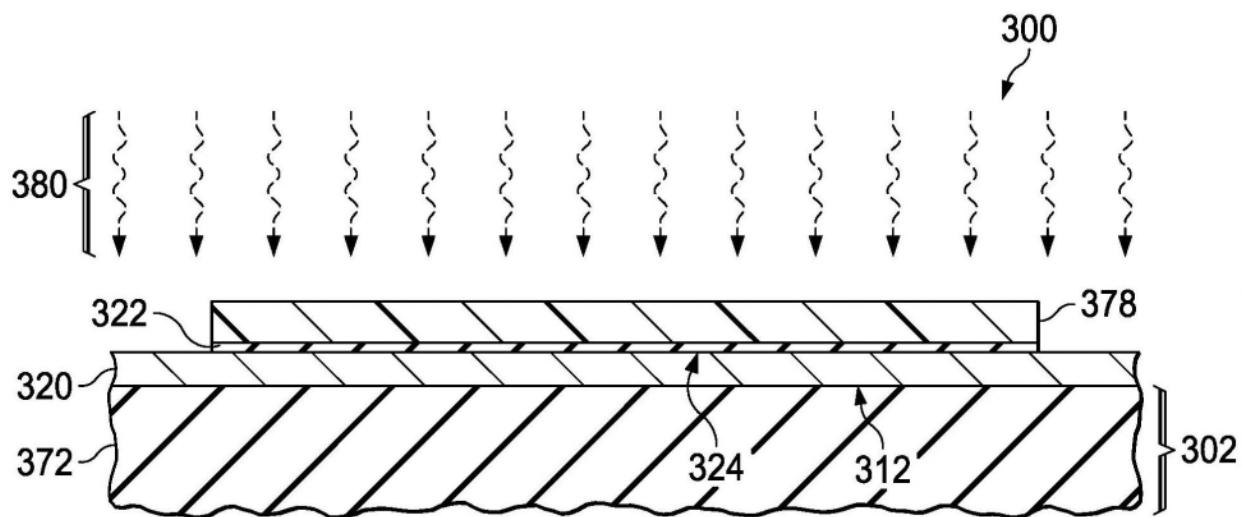

[0048] 图3A至图3F是在又一个示例形成方法的连续阶段中描绘的具有含铂层的微电子器件的横截面。参考图3A,微电子器件300具有衬底302,衬底302可以包括延伸到衬底302的顶部表面312的介电材料372。介电材料372可以包括例如场氧化物,PMD层,在相同金属化级中的互连线之间的金属间介电(IMD)层,或在金属化级之间的层内介电(ILD)层。微电子器件300的延伸到衬底302的顶部表面312的其他介电层在该示例的范围内。含铂层320形成在衬底302的顶部表面312上方。可选的粘合层,导电或不导电,未在图3A中示出,其在含铂层320形成之前在衬底302的顶部表面312上形成,也在本示例的范围内。

[0049] 在该示例的一个版本中,含铂层320可以基本上由铂组成。在另一版本中,含铂层320可包括至少50%的铂,其余部分包括镍、铑、铼、钯、铱等。例如,含铂层320可以具有20纳米至2微米的厚度。含铂层320可以例如使用溅射工艺,蒸发工艺或MOCVD工艺形成。用于形成含铂层320的其他工艺在该示例的范围内。

[0050] 在含铂层320的顶部表面324上形成硬掩模层374。在该示例的一个版本中,在形成硬掩模层374之前在含铂层320的顶部表面324上可能存在原生氧化铂322,如图3A所示。例如,可以通过在形成硬掩模层374之前将含铂层320的顶部表面324暴露于空气来形成原生氧化铂322。在该示例的另一版本中,含铂层320的顶部表面324可以不含氧化铂,例如通过在相同的处理工具中形成硬掩模层374和含铂层320,而不将含铂层320的顶部表面324暴露于氧化环境。在该示例中,硬掩模层374可以包括一层或多层介电材料,例如二氧化硅、氮氧化硅、氮化硅、氧化铝等。硬掩模层374在用于去除含铂层320的湿蚀刻剂中具有蚀刻速率,该蚀刻速率显著低于在相同湿蚀刻剂中的含铂层320的蚀刻速率。在该示例中,硬掩模层374的厚度足以通过后续工艺步骤保持完整,后续工艺步骤包括在一些区域中去除原生氧化铂322,以及在相同区域中去除含铂层320。硬掩模层374的厚度可以由用于形成微电子器件300的后续制造步骤的实际考虑来限制,例如随后形成的介电材料和金属层的平面性,

以及穿过硬掩模层374的蚀刻通孔。例如在该示例的一个版本中，其中含铂层320在场氧化物上或在第一或第二金属化层中的介电层上形成，硬掩模层374的厚度可以是10纳米至200纳米。在该示例的一个版本中，其中含铂层320形成在靠近顶部金属化级的介电层上，硬掩模层374的厚度可以是10纳米至1000纳米。

[0051] 可以在硬掩模层374上形成蚀刻掩模376以覆盖用于含铂组件的区域。蚀刻掩模376可以包括通过光刻工艺形成的光刻胶。蚀刻掩模376可以包括抗反射层，例如BARC。蚀刻掩模376在用于含铂组件的区域外的区域中暴露硬掩模层374。

[0052] 参考图3B，在由蚀刻掩模376暴露的地方去除图3A的硬掩模层374以形成硬掩模378。可以例如通过RIE工艺或其他等离子体蚀刻工艺去除硬掩模层374。或者，可通过湿蚀刻工艺任选地移除硬掩模层374。可以在由硬掩模层374暴露的地方去除原生氧化铂322，但是当暴露于诸如空气的氧化环境时，原生氧化铂322可以再次快速形成。

[0053] 随后去除蚀刻掩模376，使硬掩模378留在适当位置，覆盖含铂组件的区域。可以去除蚀刻掩模376，例如通过灰化工艺，然后进行湿法清洁工艺。

[0054] 在该示例的替代版本中，硬掩模378可以通过添加工艺形成，即，通过仅在含铂层320上方的需要的地方形成硬掩模材料。添加工艺的示例可以包括喷墨工艺、丝网印刷、静电沉积和直接激光转印。

[0055] 参考图3C，含铂层320在非氧化环境中加热，例如真空或氮气、氩气、氦气等的低压环境。含铂层320可以例如通过如图3C所示的辐射加热工艺380，或通过炉子工艺加热。将含铂层320加热至足够的温度达足够的时间以除去由硬掩模378暴露的地方的原生氧化铂322。例如，可将含铂层320加热至300℃至350℃达30分钟至120分钟。

[0056] 参考图3D，盖层332形成在硬掩模378上方和在由硬掩模378暴露处的含铂层320的顶部表面324上，使得盖层332和含铂层320之间的界面不含氧化铂。例如，可以在如参考图3C所公开的用于加热含铂层320的相同工具中形成盖层332，而不将含铂层320的顶部表面324暴露于氧化环境中。盖层332可具有如参考图1D所公开的组成和厚度，其可以通过参考图1D公开的任何过程形成。

[0057] 参考图3E，使用湿蚀刻剂334的湿蚀刻工艺去除图3D的盖层332和含铂层320，此处由硬掩模378暴露，如参考图1E到图1G所述。湿蚀刻剂334可具有参考图1E公开的任何组成。图3E描绘在完成湿蚀刻工艺时的微电子器件300。硬掩模378和原生氧化铂322(如果存在的)防止湿蚀刻剂334去除硬掩模378下方的含铂层320，因为硬掩模378在湿蚀刻剂334中具有足够低的蚀刻速率。在含铂层320上形成盖层332，其间没有氧化铂，如参考图3D所述，这可以使湿蚀刻工艺能够完全去除在由硬掩模378暴露的地方的含铂层320，而不需要长时间的过蚀刻，因此有利地减少了在硬掩模378的边缘下面的含铂层320的底切，并且有利地提供剩余含铂层320的一致的横向尺寸。

[0058] 参考图3F，在图3E的湿蚀刻工艺完成之后，在剩余含铂层320的暴露的横向表面上可以形成另外的原生氧化铂322。剩余含铂层320提供含铂组件382，其可以包括例如电阻器、互连、传感器元件、热电偶元件或加热器元件。

[0059] 在该示例的一个版本中，硬掩模378可以留在适当位置，如图3F所示。在另一版本中，可以在图3E的湿蚀刻工艺完成之后去除硬掩模378。

[0060] 可以在微电子器件300的即时顶部表面上形成介电层336，其可以是PMD层、IMD层

或ILD层。垂直连接338(其可以是触点或通孔)可以穿过介电层336以及穿过硬掩模378(如果存在的话)形成,以与含铂组件382形成电连接。在形成垂直连接338期间,含铂层320的顶部表面324上的原生氧化铂322被容易地去除以实现垂直连接338和含铂组件382之间的低电阻。

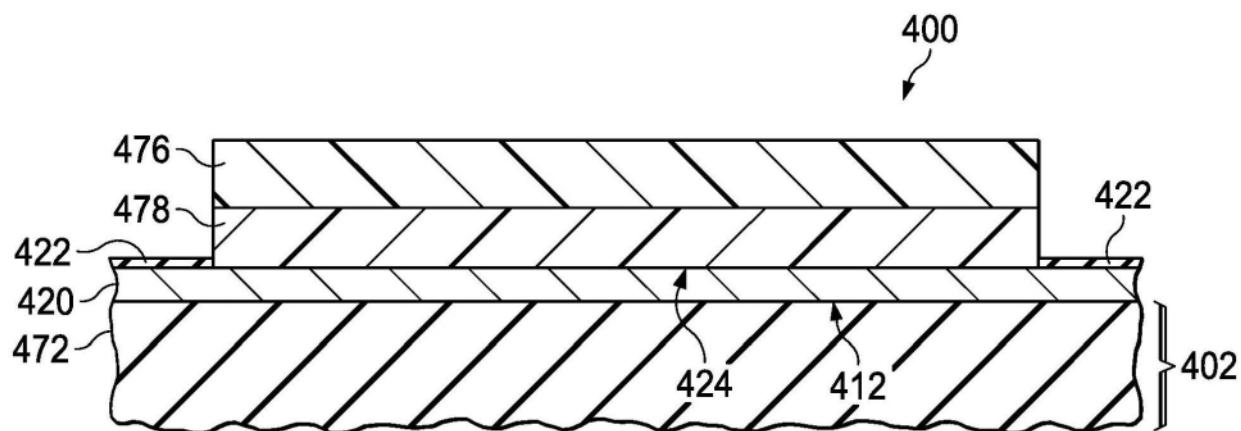

[0061] 图4A至图4H是在另一示例形成方法的连续阶段中描绘的具有含铂层的微电子器件的横截面。参考图4A,微电子器件400具有衬底402,在该示例中,衬底402包括延伸到衬底402的顶部表面412的介电材料472。含铂层420形成在衬底402的顶部表面412上。含铂层420可具有与图3A的含铂层320类似的组成和结构。

[0062] 硬掩模层474形成在含铂层420的顶部表面424上。在该示例中,硬掩模层474是导电的,并且形成在含铂层420的顶部表面424上,使得在硬掩模层474和含铂层420之间没有氧化铂。硬掩模层474与含铂层420电连接,例如接触电阻率小于 $10^{-8}\text{ohm}\cdot\text{cm}^2$ 。在该示例的一个版本中,这可以通过在相同的处理工具中形成硬掩模层474和含铂层420,而不将含铂层420的顶部表面424暴露于氧化环境来实现。在该示例的另一版本中,可以在形成硬掩模层474之前去除含铂层420的顶部表面424上的氧化铂。硬掩模层474可以包括一层或更多层导电材料,该导电材料在用于去除含铂层420的湿蚀刻剂中具有的蚀刻速率显著低于含铂层420在相同湿蚀刻剂中的蚀刻速率。硬掩模层474可以包括例如钛、氮化钛、钨、钛钨、钽、氮化钽或铬。在该示例中,硬掩模层474的厚度足以通过后续工艺步骤保持完整,后续工艺步骤包括在一些区域中从含铂层420去除氧化铂,以及在相同的区域中去除含铂层420,并且足以作为随后形成的触点或通孔提供着陆焊盘。硬掩模层474的厚度可能受到用于形成微电子器件400的后续制造步骤的实际考虑的限制,例如随后形成的介电材料和金属层的平面性。举例来说,硬掩模层474的厚度可以是30纳米至200纳米。

[0063] 在硬掩模层474上形成蚀刻掩模476以覆盖用于含铂组件的区域。蚀刻掩模476可以通过与参考图3A的蚀刻掩模376所公开的工艺类似的工艺形成。

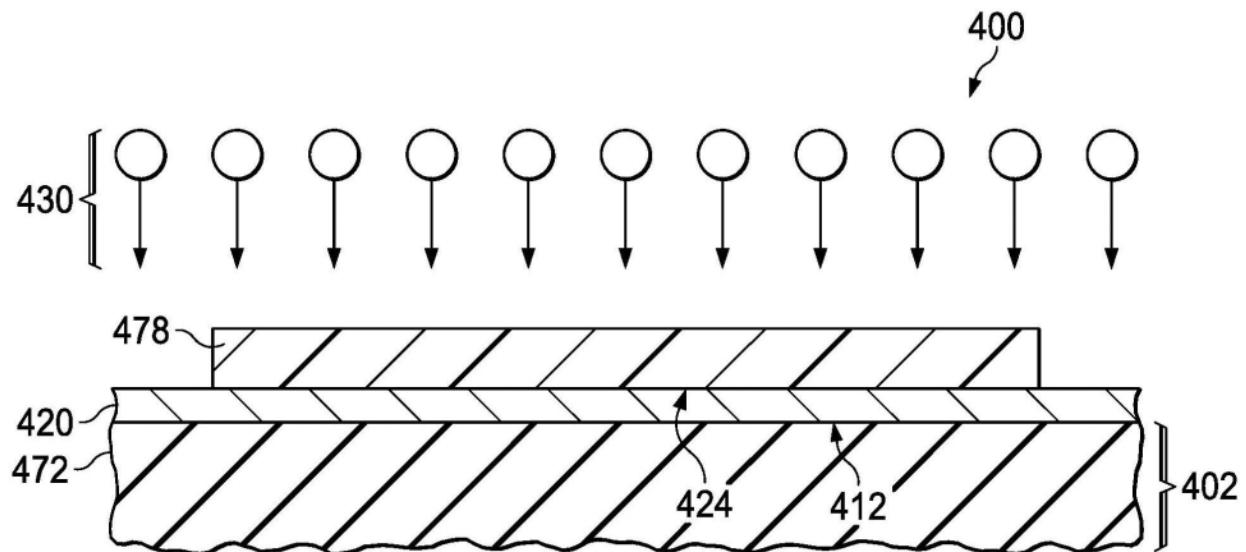

[0064] 参考图4B,在由蚀刻掩模476暴露的地方去除图4A的硬掩模层474以形成硬掩模478。可以例如通过使用卤素自由基的RIE工艺或其他等离子体蚀刻工艺去除硬掩模层474。或者,可以使用包括硝酸、磷酸、氢氟酸、过氧化氢或其任何组合的蚀刻剂的混合物通过湿蚀刻工艺可选地去除硬掩模层474。原生氧化铂422可以在由硬掩模478暴露的地方的含铂层420的顶部表面424上形成。随后去除蚀刻掩模476,在适当位置留下硬掩模478覆盖用于含铂组件的区域。

[0065] 参考图4C,在从由硬掩模478暴露的地方的含铂层420的顶部表面424移除图4B的原生氧化铂422。可以使用惰性气体离子430(例如氦或氩)通过溅射蚀刻去除原生氧化铂422,如图4C所示。或者,可以通过另一种方法除去原生氧化铂422,例如在非氧化环境中加热含铂层420,或者通过使用高能卤素离子的等离子体工艺,其通过组合使用物理和化学机制去除原生氧化铂422。去除原生氧化铂422的其他方法也在本实施例的范围内。

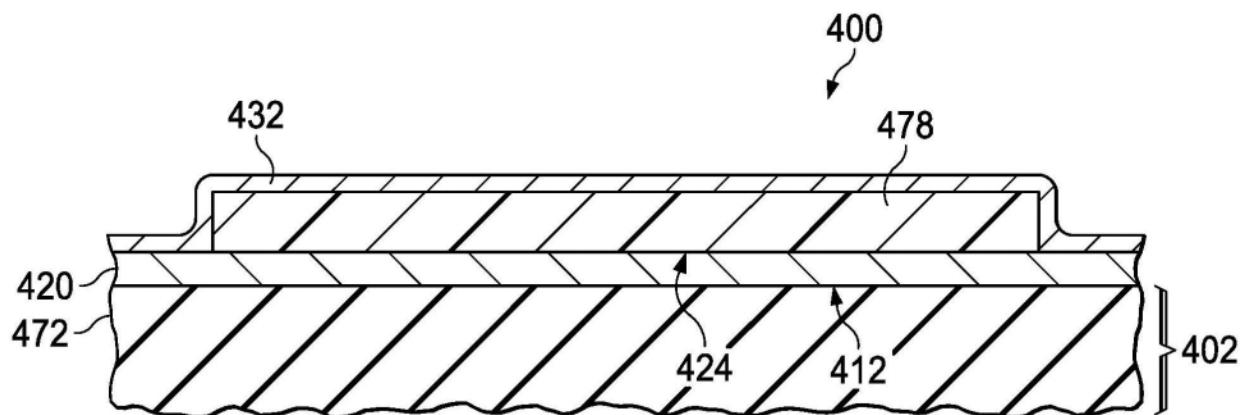

[0066] 参考图4D,在硬掩模478上方并且在由硬掩模478暴露的地方的含铂层420的顶部表面424上形成盖层432,使得盖层432和含铂层420之间的界面不含氧化铂。例如,盖层432可以形成在如参考图4C所公开的用于去除含铂层420的相同工具中,而不将含铂层420的顶部表面424暴露于氧化环境。盖层432可具有如参考图1D所公开的组成和厚度,并且可以通过参考图1D公开的任何工艺形成。

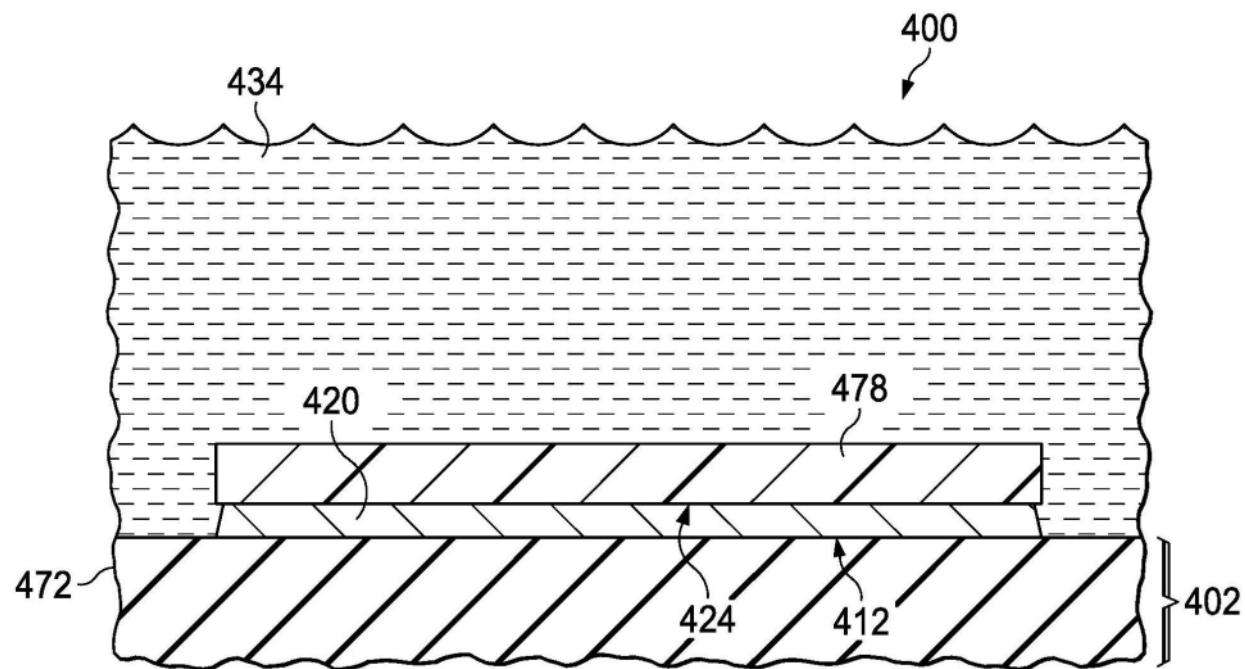

[0067] 参考图4E, 使用湿蚀刻剂434的湿蚀刻工艺去除图4D的盖层432和由硬掩模478暴露的含铂层420, 如参考图1E到图1G所描述的。湿蚀刻剂434可以具有参考图1E公开的任何组成。图4E描绘了在完成湿蚀刻工艺时的微电子器件400。硬掩模478防止湿蚀刻剂434去除硬掩模478下方的含铂层420, 因为硬掩模478在湿蚀刻剂434中具有足够低的蚀刻速率。在含铂层420上形成盖层432, 其间没有氧化铂, 如参考图4D所述, 可以使湿蚀刻工艺能够完全去除由硬掩模478暴露的地方的含铂层420, 而不需要长时间的过蚀刻, 因此有利地减少了在硬掩模478的边缘下面的含铂层420的底切, 并且有利地提供剩余含铂层420的一致的横向尺寸。

[0068] 参考图4F, 剩余含铂层420提供含铂组件482, 其可包括例如电阻器、互连、传感器元件、热电偶元件或加热器元件。在硬掩模478上方形成着陆焊盘掩模484, 以覆盖用于含铂组件482上的着陆焊盘的区域。着陆焊盘掩模484可以包括光刻胶, 并且可以可选地包括BARC层。新的原生氧化铂422可以在含铂组件482的暴露表面上形成, 如图4F所示。

[0069] 参考图4G, 在由着陆焊盘掩模484暴露的地方去除图4F的硬掩模478, 以形成硬掩模478的剩余部分的着陆焊盘486。可以例如通过参考去除图4A的硬掩模层474所公开的、参考图4B讨论的任何工艺去除硬掩模478。可以在通过对硬掩模478而暴露的含铂组件482的表面上形成另外的原生氧化铂422, 如图4G所描绘的。随后去除着陆焊盘掩模484, 例如通过灰化工艺, 然后进行湿法清洁工艺。

[0070] 参考图4H, 可以在微电子器件400的即时顶部表面上形成介电层436, 其可以是PMD层, IMD层或ILD层。形成通过介电层436的垂直连接438, 其可以是接触或通孔, 以与着陆焊盘486形成电连接。在着陆焊盘486和含铂组件482之间不存在氧化铂可有利地导致着陆焊盘486和含铂组件482之间的低电阻。

[0071] 图5A至图5F是在另一示例形成方法的连续阶段中描绘的在键合焊盘中具有含铂层的微电子器件的横截面。参考图5A, 微电子器件500具有衬底502, 在该示例中, 衬底502包括ILD层580, 在ILD层580上方的IMD层588, 在ILD层580上方并且由IMD层588横向围绕的互连590, 在IMD层588上方的P0层592, 以及在互连590上的键合焊盘下层594。P0层592暴露用于键合焊盘的区域中的键合焊盘下层594的至少一部分。P0层592可以包括二氧化硅、氮氧化硅、氮化硅等。键合焊盘下层594可包括一层或更多层镍、钯或适于支撑键合焊盘的其他金属。键合焊盘下层594可以例如使用化学镀形成。

[0072] 在衬底502的顶部表面512上形成含铂层520, 与键合焊盘下层594接触。可选的粘合金属层, 未在图5A中示出, 在形成含铂层520之前, 其可以在衬底502的顶部表面512上形成, 在该示例的范围内。在该示例中, 含铂层520将提供用于引线键合的键合焊盘, 因此可主要包括铂或可基本上由铂组成。含铂层520可以具有例如1微米至5微米的厚度。

[0073] 盖层532形成在含铂层520的顶部表面524上, 使得盖层532和含铂层520之间的界面不含氧化铂。在该示例的一个版本中, 盖层532可以与含铂层520原位形成, 即, 与含铂层520在相同的处理工具中形成。在另一个版本中, 可以在形成盖层532之前从含铂层520的顶部表面524去除氧化铂。

[0074] 参考图5B, 在盖层532上形成蚀刻掩模558。蚀刻掩模558在用于键合焊盘的区域中暴露盖层532。在由蚀刻掩模558暴露的地方去除盖层532。可以通过等离子体蚀刻, 通过湿蚀刻或通过另一工艺来移除盖层532。随后可以在进行氧化铂形成步骤之前去除蚀刻掩模

558,或者可以将蚀刻掩模558留在适当位置并在完成氧化铂形成步骤之后去除。

[0075] 参考图5C,掩模氧化铂564形成在由盖层532暴露的地方的含铂层520的顶部表面524上。在该示例中,掩模氧化铂564可以由氧化湿试剂596形成,如图5C所示。氧化湿试剂596可包括例如过氧化氢、硝酸等。用于形成掩模氧化铂564的其他工艺在该示例的范围内。

[0076] 参考图5D中,将微电子器件500从与图5C的氧化湿试剂596的接触中移除。掩模氧化铂564在用于键合焊盘的区域上方延伸。

[0077] 参考图5E,使用湿蚀刻剂534的湿蚀刻工艺去除图5D的盖层532和由掩模氧化铂564暴露的含铂层520,如参考图1E到图1G所描述的。湿蚀刻剂534可以具有参考图1E公开的任何组成。图5E描绘了在完成湿蚀刻工艺时的微电子器件500。掩模氧化铂564防止湿蚀刻剂534去除掩模氧化铂564下面的含铂层520。在含铂层520上形成盖层532,其间没有氧化铂,如参考

[0078] 图5D所述,这可以提供低过蚀刻并因此具有低底切和一致的横向尺寸的优点,如参考本文的其他示例所讨论的。

[0079] 参考图5F,剩余含铂层520提供键合焊盘582,其通过键合焊盘下层594与互连590电连接。在键合焊盘582的暴露横向表面上可形成原生氧化铂522。

[0080] 键合连接598,在图5F中被描述为引线键合598,可以随后通过键合操作在键合焊盘582上形成。使用超声波键合工艺,已经在适当位置具有掩模氧化铂564的铂焊盘上进行了利用金属和铂引线的引线键合。引线键合的过程突破掩模氧化铂564,导致引线键合598直接接触含铂层520。或者,键合连接598可以包括具有铟和其他金属的凸块键合,电镀到键合焊盘582上。形成凸块键合的工艺包括其中熔化凸块键合的回流操作,导致凸块键合金属直接接触含铂层520。与铝或另一种更具反应性的金属相比,形成含铂金属的键合焊盘582可以为微电子器件500提供所需的可靠性。

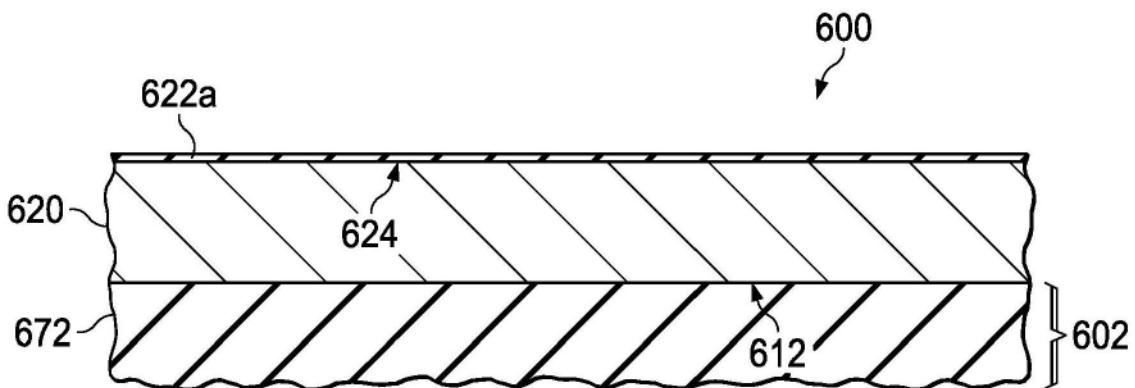

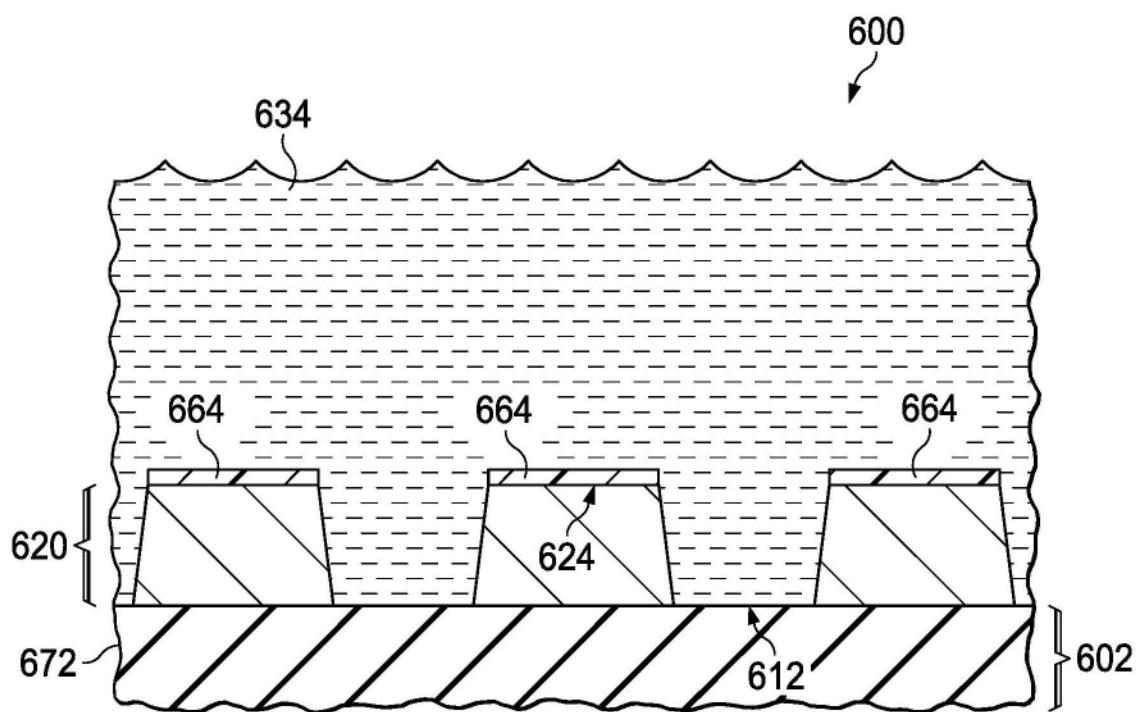

[0081] 图6A至图6I是在进一步示例形成方法的连续阶段中描绘的具有图案化的含铂层的微电子器件的横截面。参考图6A,微电子器件600具有衬底602,在该示例中,衬底602包括延伸到衬底602的顶部表面612的介电材料672。在衬底602的顶部表面612上形成含铂层620。含铂层620可以具有与参考图3A公开的含铂层620类似的组成和结构。在该示例的一个版本中,在含铂层620的顶部表面624上可以存在原生氧化铂622a,如图6A所示。

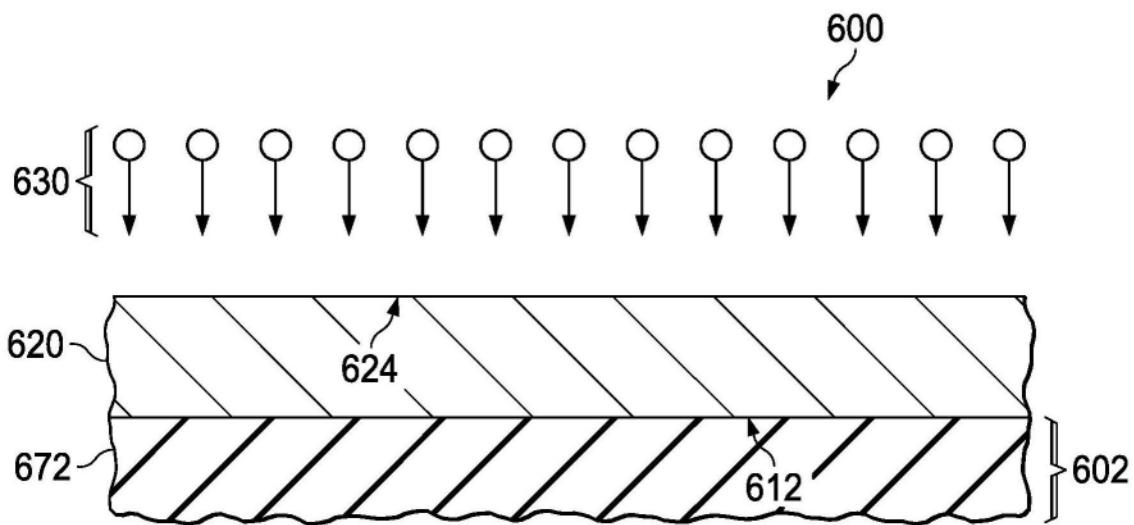

[0082] 参考图6B,从含铂层620的顶部表面624去除图6A的原生氧化铂622a。在该示例的一个版本中,可以通过溅射蚀刻工艺的离子630去除原生氧化铂622a,如图6B所示。在另一个版本中,可以加热含铂层620去除原生氧化铂622a。去除原生氧化铂622a的其他方法也在本示例的范围内。

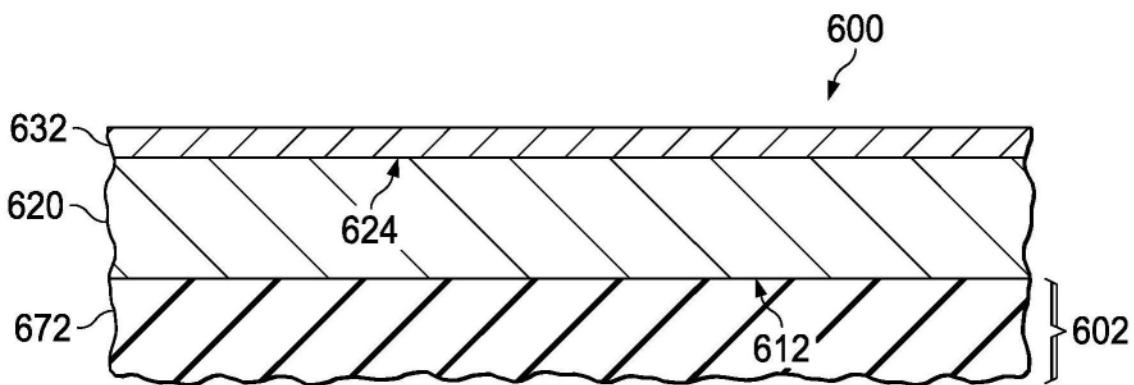

[0083] 参考图6C,在含铂层620的顶部表面624上形成盖层632,使得盖层632和含铂层620之间的界面不含氧化铂。在该示例中,这可以通过在去除图6A的原生氧化铂622a之后形成覆盖层632而不将含铂层620的顶部表面624暴露于氧化环境来实现。在该示例的替代版本中,盖层632可以形成在含铂层620上,而不允许首先形成原生氧化铂622a。盖层632可在随后用于去除至少一部分含铂层620的相同湿蚀刻剂中蚀刻。盖层632可具有如参考图1D所公开的组成和厚度,并且可以通过参考图1D公开的任何工艺形成。

[0084] 参考图6D,在盖层632上形成蚀刻掩模658。蚀刻掩模658暴露用于含铂结构的区域660。在该示例的一个版本中,蚀刻掩模658可以包括通过光刻工艺形成的抗蚀剂,例如光刻

工艺或电子束光刻工艺。在另一个版本中，蚀刻掩模658可以包括通过添加工艺形成的有机聚合物材料。在另一个版本中，蚀刻掩模658可以包括通过掩模和蚀刻工艺或者通过添加工艺形成的无机材料。

[0085] 参考图6E，在由蚀刻掩模658暴露的地方去除盖层632。可以通过等离子体蚀刻工艺，通过湿蚀刻工艺或其他方法去除盖层632。可以在通过去除盖层632暴露的含铂层620的顶部表面624上形成新一层的原生氧化铂622b。

[0086] 参考图6F，在由盖层632暴露的地方的含铂层620的顶部表面624上形成掩模氧化铂664。掩模氧化铂664可以代替或添加到图6E的原生氧化铂622b。掩模氧化铂664可以通过使用氧化电解质700的电化学工艺形成，其中含铂层620相对于氧化电解质700被偏置到正电位，如图6F中示意性地所示。氧化电解质700可包括例如硫酸( $H_2SO_4$ )的水溶液，或氢氧化钠(NaOH)的水溶液。氧化电解质700可以具有其他配方。或者，掩模氧化铂664可以通过其他方法形成，例如本文公开的任何示例。在形成掩模氧化铂664期间，蚀刻掩模658可以可选地被保留在适当位置，以保护盖层632的顶部表面。随后去除蚀刻掩模658。

[0087] 图6G描绘了在去除图6F的蚀刻掩模658之后的微电子器件600。掩模氧化铂664覆盖用于含铂结构的区域中的含铂层620。掩模氧化铂664足够厚以防止在随后的湿蚀刻工艺期间去除用于含铂结构的区域中的含铂层620。

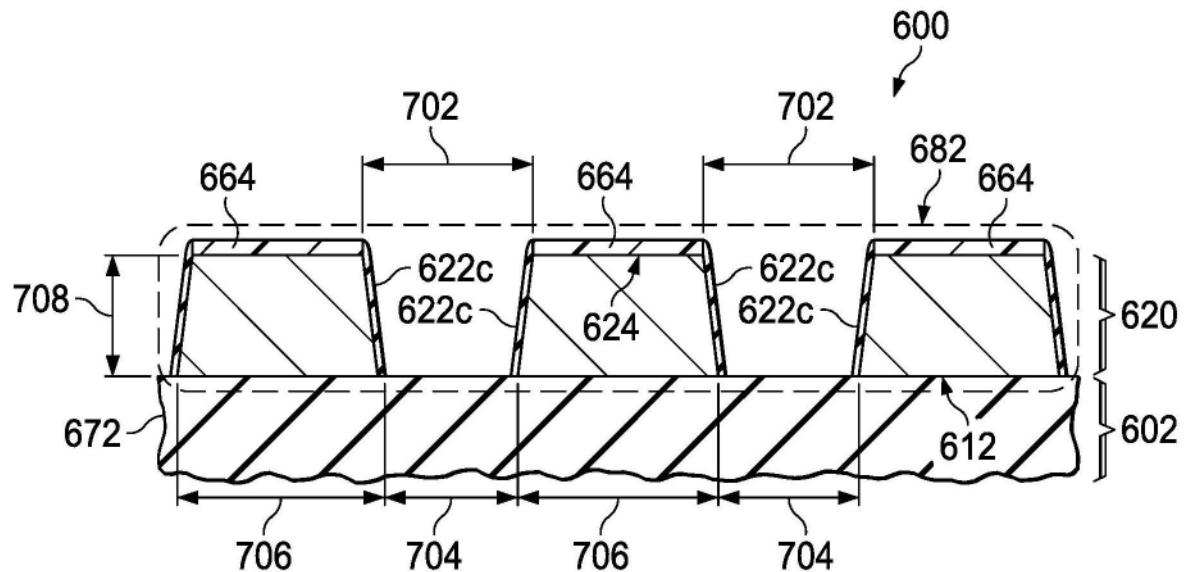

[0088] 参考图6H，使用湿蚀刻剂634的湿蚀刻工艺去除图6G的盖层632和由掩模氧化铂664暴露的含铂层620，如图1E到图1G所示。湿蚀刻剂634可具有参考图1E公开的任何组成。图6H描绘了在完成湿蚀刻工艺时的微电子器件600。掩模氧化铂664防止湿蚀刻剂634去除掩模氧化铂664下面的含铂层620。在含铂层620上形成盖层632，其间没有氧化铂，如参考图6A至图6C所述，这可以使湿蚀刻工艺能够完全去除由掩模氧化铂664暴露的地方的含铂层620，而不需要长时间的过蚀刻，因此有利地提供剩余含铂层620的一致的横向尺寸。

[0089] 图6I描绘从暴露于图6H的湿蚀刻剂634中移除之后的微电子器件600。另外的原生氧化铂622c可以在含铂层620的所有暴露表面上形成。含铂层620提供含铂结构682，其可以是电阻器、传感器、电感器、电容器、互连等的一部分。

[0090] 通过如参考图6H所述的湿蚀刻工艺形成含铂结构682可以在含铂结构682中的含铂层620的区段中产生特征。第一特征是含铂层620的相邻区段之间的第一间距702，如从一个区段的顶部表面624到相邻区段的顶部表面624测量的，可以大于沿着衬底602的顶部表面612测量的相同的两个相邻区段之间的第二间隔704。第一特征是通过图6H的湿蚀刻剂634进行蚀刻的各向同性的结果。

[0091] 第二特征是沿着衬底602的顶部表面612测量的区段的宽度706可以是相同区段的厚度708的1/2。在含铂层620中具有第二特征可以有利地为含铂结构682并因此为微电子器件600提供较低的区域。通过在没有氧化铂的含铂层620上形成图6C的盖层632，能够实现第二特征，这进而使得能够以最小的过蚀刻完全去除第二间隔704中的含铂层620。

[0092] 第三特征是与含铂层620的一区段相邻的第二间隔704可以是相同区段的厚度708的1/2。在含铂层620中具有第三特征可以进一步为含铂结构682并因此为微电子器件600提供较低的区域。通过在没有氧化铂的含铂层620上形成图6C的盖层632，同样能够实现第三特征。

[0093] 第四特征是在含铂层620上不存在再沉积的溅射残留物。再沉积的溅射残留物(其

可以包括聚合物材料和可能的含铂材料)是通过离子研磨工艺形成的结构的典型,并且不是由本文示例中公开的湿蚀刻工艺形成的。使含铂层620不含再沉积的含铂残留物可减少污染和相关缺陷,因此有利地为含有含铂结构682的微电子器件600的电路提供更一致的性能和可靠性。

[0094] 第五特征是在与含铂层620的区段相邻的衬底602的顶部表面612上不存在含铂残留物。在衬底602的顶部表面612上的含铂残留物是通过湿蚀刻工艺形成的典型的含铂结构,其中在湿蚀刻步骤期间,在铂的顶部表面上具有氧化铂。含铂残留物是由于氧化铂在湿蚀刻步骤中使用的湿蚀刻剂中具有非常低的蚀刻速率导致的。通过在含铂层620上形成图6C的盖层632,而其间没有氧化铂,能够实现第五特征。使衬底602的顶部表面612没有含铂残留物可以有利地提高微电子器件600的可靠性。形成具有如本文示例中所述的含铂结构的微电子器件可以提高微电子器件的产率,其可有利地为所产生的微电子器件提供较低的制造成本。

[0095] 在所描述的实施例中修改是可能的,并且在权利要求的范围内,其他实施例也是可能的。

图1A

图1B

图1C

图1D

图1E

图1F

图1G

图1H

图2A

图2B

图2C

图2D

图2E

图2F

图2G

图2H

图3A

图3B

图3C

图3D

图3E

图3F

图4A

图4B

图4C

图4D

图4E

图4F

图4G

图4H

图5A

图5B

图5C

图5D

图5E

图5F

图6A

图6B

图6C

图6D

图6E

图6F

图6G

图6H

图61