US011438504B2

# (12) United States Patent

Hasegawa et al.

## (54) IMAGING ELEMENT, IMAGING APPARATUS, OPERATION METHOD OF IMAGING ELEMENT, AND PROGRAM

(71) Applicant: **FUJIFILM CORPORATION**, Tokyo

(JP)

(72) Inventors: Ryo Hasegawa, Saitama (JP);

Tomoyuki Kawai, Saitama (JP); Hitoshi Sakurabu, Saitama (JP); Makoto Kobayashi, Saitama (JP)

(73) Assignee: **FUJIFILM CORPORATION**, Tokyo

(JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 17/348,779

(22) Filed: Jun. 16, 2021

(65) Prior Publication Data

US 2021/0314486 A1 Oct. 7, 2021

#### Related U.S. Application Data

(63) Continuation of application No. PCT/JP2019/049219, filed on Dec. 16, 2019.

## (30) Foreign Application Priority Data

Dec. 26, 2018 (JP) ...... JP2018-243663

(51) Int. Cl. *H04N 5/232* (2006.01) *G02B 7/14* (2021.01)

(Continued)

# (10) Patent No.: US 11,438,504 B2

(45) **Date of Patent:**

Sep. 6, 2022

#### 58) Field of Classification Search

CPC .... H04N 5/23232; H04N 5/2353; G02B 7/14; G02B 17/14

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

JP 2001-333429 A 11/2001 JP 2009-296353 A 12/2009 (Continued)

#### OTHER PUBLICATIONS

International Search Report issued in International Application No. PCT/JP2019/049219 dated Mar. 3, 2020.

(Continued)

Primary Examiner — Ahmed A Berhan (74) Attorney, Agent, or Firm — Solaris Intellectual Property Group, PLLC

#### (57) ABSTRACT

An imaging element incorporates a memory and a processor. The memory stores image data obtained by imaging a subject at a first frame rate. The processor is configured to derive a degree of difference between first image data obtained as the image data by performing imaging and second image data that is obtained as the image data earlier than the first image data and stored in the storage portion, and perform processing of deciding at least one of the first image data or the second image data as the output image data in a case where the derived degree of difference is greater than or equal to a threshold value. The processor is configured to output the decided output image data at a second frame rate.

# 21 Claims, 43 Drawing Sheets

# US 11,438,504 B2

Page 2

(51) **Int. Cl.** *H04N 5/235* (2006.01) *G03B 17/14* (2021.01) *G02B 7/10* (2021.01)

# (56) References Cited

# FOREIGN PATENT DOCUMENTS

| JР | 2010-88050 A  | 4/2010  |

|----|---------------|---------|

| JP | 2017-108368 A | 6/2017  |

| JP | 2017-188760 A | 10/2017 |

# OTHER PUBLICATIONS

Written Opinion of the ISA issued in International Application No. PCT/JP2019/049219 dated Mar. 3, 2020. International Preliminary Report on Patentability issued in International Application No. PCT/JP2019/049219 dated Sep. 8, 2020.

<sup>\*</sup> cited by examiner

12(212,312,412,512,612)

FIG. 4

CPU

46A

SECOND DISPLAY

90

90

90

HYBRID FINDER

FIG. 5

FIG. 8

FIG. 10

FIG. 12

FIG. 13

CONTROLLER OUTPUT 62D **(** FIG. 14 **OUTPUT IMAGE DATA DECISION PORTION (**©) IMAGE PROCESSING CIRCUIT PROCESSING CIRCUIT

FIG. 18

FIG. 19

FIG. 22

FIG. 24

FIG. 26

FIG. 28

FIG. 29

FIG. 30 STANDARD FRAME RATE SETTING PROCESSING ST440 IS STANDARD FR SETTING N INSTRUCTION SIGNAL RECEIVED? ST442 SET STANDARD FRAME RATE ST444 N IS FINISH CONDITION SATISFIED? **END**

FIG. 31 LOW FRAME RATE SETTING PROCESSING ST450 IS LOW FR SETTING INSTRUCTION N SIGNAL RECEIVED? ST452 SET LOW FRAME RATE ST454 N IS FINISH CONDITION SATISFIED? **END**

FIG. 32

**OUTPUT IMAGE DATA DECISION PORTION OUTPUT IMAGE DATA** FIG. 33

FIG. 34A

Sep. 6, 2022

FIG. 34

FIG. 36 **IMAGING PROCESSING ∕ST10** N IS EXPOSURE START TIMING REACHED? ST20 N IS PAST FRAME IMAGE DATA PRESENT? ST200 GENERATE THINNED IMAGE DATA ∠ST300 DETECT MAIN SUBJECT IMAGE DATA ST322 CALCULATE AREA OF BINARIZED DIFFERENCE REGIONS ST324 AREA OF BINARIZED DIFFERENCE N REGIONS ≥ PREDETERMINED AREA? ST500 TEMPORARILY DECIDE MOST RECENT FRAME IMAGE DATA AS OUTPUT **IMAGE DATA** ST502 IS CLOSED-EYE IMAGE DATA INCLUDED? ST504 ST506 N **OUTPUT OUTPUT CONFIRMATION OUTPUT SECOND DUMMY DATA IMAGE DATA ST30** IS FINISH CONDITION SATISFIED? **END**

FIG. 37

Sep. 6, 2022

FIG. 38

FIG. 40

# IMAGING ELEMENT, IMAGING APPARATUS, OPERATION METHOD OF IMAGING ELEMENT. AND PROGRAM

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation application of International Application No. PCT/JP2019/049219, filed Dec. 16, 2019, the disclosure of which is incorporated herein by reference in its entirety. Further, this application claims priority from Japanese Patent Application No. 2018-243663, filed Dec. 26, 2018, the disclosure of which is incorporated herein by reference in its entirety.

#### BACKGROUND

#### 1. Technical Field

The technology of the present disclosure relates to an <sup>20</sup> imaging element, an imaging apparatus, an operation method of an imaging element, and a program.

#### 2. Related Art

JP2017-108368A discloses a technology for obtaining difference data between a first frame and a second frame, outputting the difference data in a case where a difference is not detected, and displaying an image corresponding to imaging data of a third frame on a display apparatus in a case <sup>30</sup> where the difference is detected.

JP2009-296353A discloses an imaging element module comprising a memory that stores captured image data as a digital signal, and a compressor that compresses the captured image data read out from the memory and outputs the 35 captured image data to an outside. In the imaging element module disclosed in JP2009-296353A, difference data between previous captured image data and current captured image data is compressed data.

#### **SUMMARY**

One embodiment according to the technology of the present disclosure provides an imaging element, an imaging apparatus, an operation method of an imaging element, and 45 a program capable of reducing power consumption required for outputting image data, compared to a case of outputting every image data obtained by imaging.

An imaging element according to a first aspect of the technology of the present disclosure is an imaging element 50 comprising a storage portion that stores image data obtained by imaging a subject at a first frame rate and is incorporated in the imaging element, a processing portion that performs processing using the image data and is incorporated in the imaging element, and an output portion that outputs output 55 image data based on the image data at a second frame rate based on a processing result and is incorporated in the imaging element, in which the processing portion derives a degree of difference between first image data obtained as the image data by performing imaging and second image data 60 that is obtained as the image data earlier than the first image data and stored in the storage portion, and performs processing of deciding at least one of the first image data or the second image data as the output image data in a case where the derived degree of difference is greater than or equal to a 65 threshold value, and the output portion outputs the output image data decided by the processing portion. Accordingly,

2

power consumption required for outputting image data can be reduced, compared to a case of outputting every image data obtained by imaging.

In the imaging element according to a second aspect of the technology of the present disclosure, the processing portion performs thinning processing on the first image data and the second image data, and derives a degree of difference between the first image data after the thinning processing and the second image data after the thinning processing. Accordingly, the power consumption required for outputting the image data can be reduced, compared to a case of not performing the thinning processing on the first image data and the second image data.

In the imaging element according to a third aspect of the technology of the present disclosure, the processing portion detects main subject image data indicating an image of a main subject from one of the first image data and the second image data, and detects, from the other of the first image data and the second image data, specific image data indicating an image specified from a position corresponding to a position of the image of the main subject within an image indicated by the first image data, and the degree of difference is a degree of difference between the main subject image data detected by the processing portion and the specific image 25 data detected by the processing portion. Accordingly, a load exerted on the processing portion can be reduced, compared to a case of deriving a degree of difference between the entire first image data and the entire second image data.

In the imaging element according to a fourth aspect of the technology of the present disclosure, the processing portion, in a case where a state where the degree of difference is less than the threshold value continues for a predetermined time period, decreases at least the first frame rate out of the first frame rate and the second frame rate. Accordingly, power consumption of the imaging element can be reduced, compared to a case of performing imaging without decreasing the first frame rate during a period in which the subject is not having a noticeable motion.

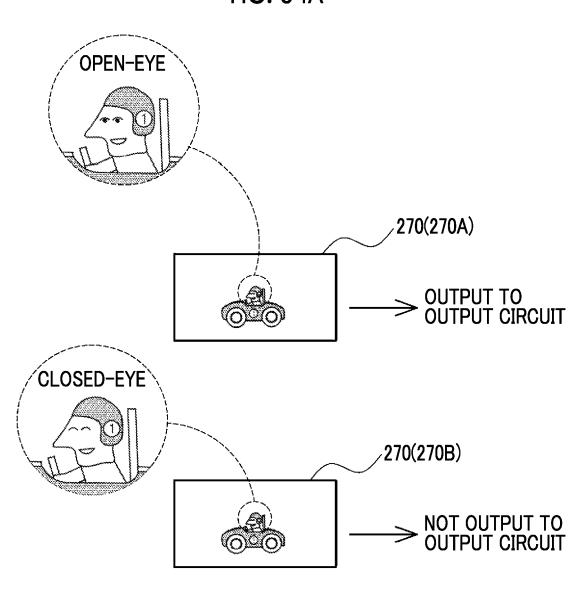

In the imaging element according to a fifth aspect of the technology of the present disclosure, the processing portion detects, from the image data, closed-eye image data indicating an image of an eye in a state where an eyelid is closed, and the output portion, in a case where the closed-eye image data is detected, does not output the image data from which the closed-eye image data is detected. The power consumption required for outputting the image data can be reduced, compared to a case of outputting the output image data including the closed-eye image data.

In the imaging element according to a sixth aspect of the technology of the present disclosure, the output portion, in a case where the degree of difference is greater than or equal to the threshold value, decides at least one of the first image data or the second image data as the output image data on a condition that the closed-eye image data is not detected by the processing portion. Accordingly, the output image data that is expected to be highly necessary for a user can be provided to the user.

In the imaging element according to a seventh aspect of the technology of the present disclosure, the processing portion derives an evaluation value indicating a degree of focusing for the image data, and the output portion, in a case where the derived evaluation value is less than a predetermined evaluation value, does not output the image data of a derivation target for the evaluation value less than the predetermined evaluation value. Accordingly, the power consumption required for outputting the image data can be reduced, compared to a case of outputting the output image

data corresponding to the evaluation value less than the predetermined evaluation value.

In the imaging element according to an eighth aspect of the technology of the present disclosure, the processing portion, in a case where the degree of difference is greater 5 than or equal to the threshold value, decides at least one of the first image data or the second image data as the output image data on a condition that the evaluation value is greater than or equal to the predetermined evaluation value. Accordingly, the output image data that is expected to be highly 10 necessary for the user can be provided to the user.

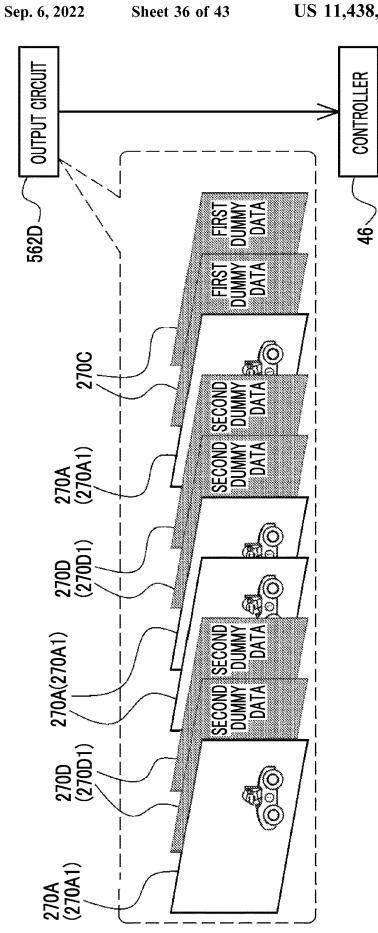

In the imaging element according to a ninth aspect of the technology of the present disclosure, the output portion outputs first dummy data in a case where the degree of difference is less than the threshold value. Accordingly, a 15 toggle rate of data can be decreased, compared to an output of the output image data in a case where the degree of difference is less than the threshold value.

In the imaging element according to a tenth aspect of the technology of the present disclosure, the output portion, 20 even in a case where the degree of difference is greater than or equal to the threshold value, does not output the output image data and outputs second dummy data in a case where the output image data is image data satisfying a specific condition. Accordingly, the toggle rate of data can be 25 decreased, compared to a constant output of every output image data in a case where the degree of difference is greater than or equal to the threshold value.

In the imaging element according to an eleventh aspect of the technology of the present disclosure, at least a photo-solution conversion element and the storage portion are formed in one chip. Accordingly, portability of the imaging element can be increased, compared to a case where the photoelectric conversion element and the storage portion are not formed in one chip.

In the imaging apparatus according to a twelfth aspect of the technology of the present disclosure, the imaging element is a laminated imaging element in which the photoelectric conversion element is laminated with the storage portion. Accordingly, a transfer speed of data from the 40 photoelectric conversion element to the storage portion can be increased, compared to a non-laminated imaging element in which the photoelectric conversion element is not laminated with the storage portion.

An imaging apparatus according to a thirteenth aspect of 45 the technology of the present disclosure comprises the imaging element according to any one of the first to twelfth aspects, and a display control portion that performs a control for displaying an image based on the output image data output by the output portion on a display portion. Accordingly, the power consumption can be reduced, compared to a case of displaying images indicated by every image data obtained by imaging the subject.

An imaging apparatus according to a fourteenth aspect of the technology of the present disclosure comprises the 55 imaging element according to any one of the first to twelfth aspects, and a storage control portion that performs a control for storing the output image data output by the output portion in a storage device. Accordingly, the power consumption can be reduced, compared to a case of storing 60 every image data obtained by imaging the subject in the storage device.

An operation method of an imaging element according to a fifteenth aspect of the technology of the present disclosure is an operation method of an imaging element including a 65 storage portion that stores image data obtained by imaging a subject at a first frame rate, a processing portion that 4

performs processing using the image data, and an output portion that outputs output image data based on the image data at a second frame rate based on a processing result of the processing portion, the storage portion, the processing portion, and the output portion being incorporated in the imaging element, the operation method comprising, by the processing portion, deriving a degree of difference between first image data obtained as the image data by performing imaging and second image data that is obtained as the image data earlier than the first image data and stored in the storage portion, and performing processing of deciding at least one of the first image data or the second image data as the output image data in a case where the derived degree of difference is greater than or equal to a threshold value, and by the output portion, outputting the output image data decided by the processing portion. Accordingly, the power consumption required for outputting the image data can be reduced, compared to a case of outputting every image data obtained by imaging.

A program according to a sixteenth aspect of the technology of the present disclosure is a program causing a computer to function as a processing portion and an output portion included in an imaging element including a storage portion that stores image data obtained by imaging a subject at a first frame rate, a processing portion that performs processing using the image data, and an output portion that outputs output image data based on the image data at a second frame rate based on a processing result of the processing portion, the storage portion, the processing portion, and the output portion being incorporated in the imaging element, in which the processing portion derives a degree of difference between first image data obtained as the image data by performing imaging and second image data that is obtained as the image data earlier than the first image data and stored in the storage portion, and performs processing of deciding at least one of the first image data or the second image data as the output image data in a case where the derived degree of difference is greater than or equal to a threshold value, and the output portion outputs the output image data decided by the processing portion. Accordingly, the power consumption required for outputting the image data can be reduced, compared to a case of outputting every image data obtained by imaging.

An imaging element according to a seventeenth aspect of the technology of the present disclosure is an imaging element comprising a memory that stores image data obtained by imaging a subject at a first frame rate and is incorporated in the imaging element, and a processor that is incorporated in the imaging element and configured to perform processing using the image data and output output image data based on the image data at a second frame rate depending on a processing result of the processing portion, in which the processor is configured to derive a degree of difference between first image data obtained as the image data by performing imaging and second image data that is obtained as the image data earlier than the first image data and stored in the memory, perform processing of deciding at least one of the first image data or the second image data as the output image data in a case where the derived degree of difference is greater than or equal to a threshold value, and output the decided output image data.

### BRIEF DESCRIPTION OF THE DRAWINGS

Exemplary embodiments of the technology of the disclosure will be described in detail based on the following figures, wherein:

- FIG. 1 is a schematic perspective view illustrating an example of an imaging apparatus according to first to sixth embodiments:

- FIG. 2 is a schematic rear view illustrating an example of the imaging apparatus according to the first to sixth embodiments:

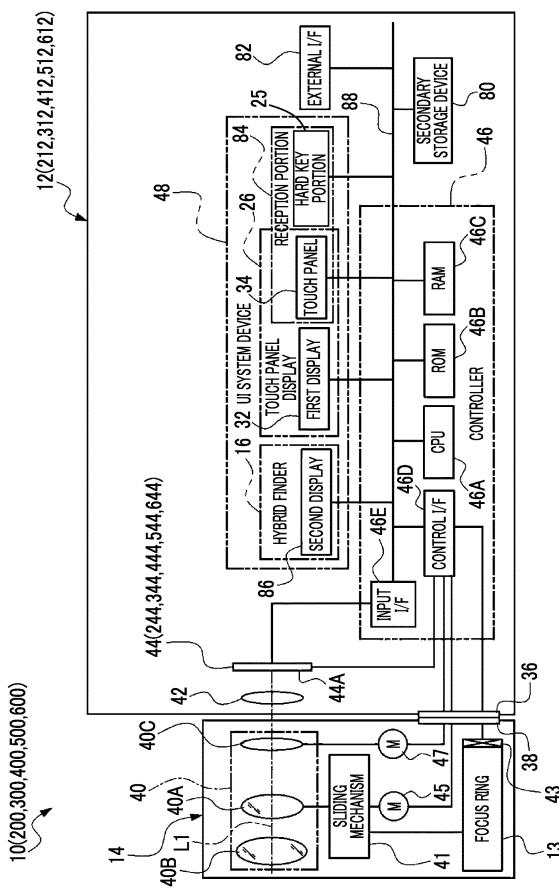

- FIG. 3 is a block diagram illustrating an example of a hardware configuration of an electric system of the imaging apparatus according to the first to sixth embodiments;

- FIG. 4 is a schematic configuration diagram illustrating an example of a configuration of a hybrid finder included in the imaging apparatus according to the first to sixth embodiments:

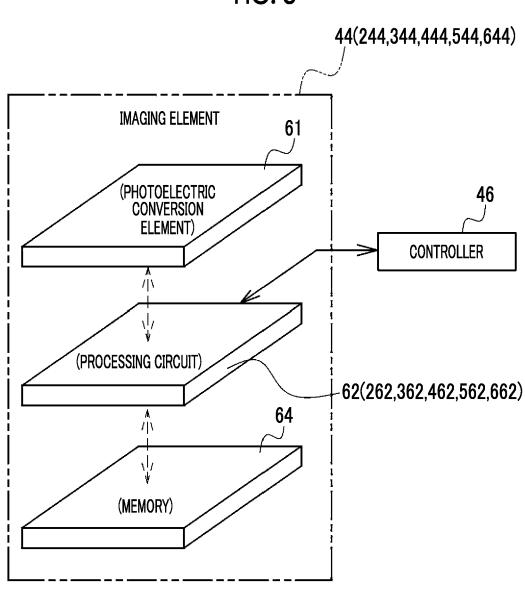

- FIG. **5** is a schematic configuration diagram illustrating an example of a laminated structure of an imaging element included in the imaging apparatus according to the first to sixth embodiments;

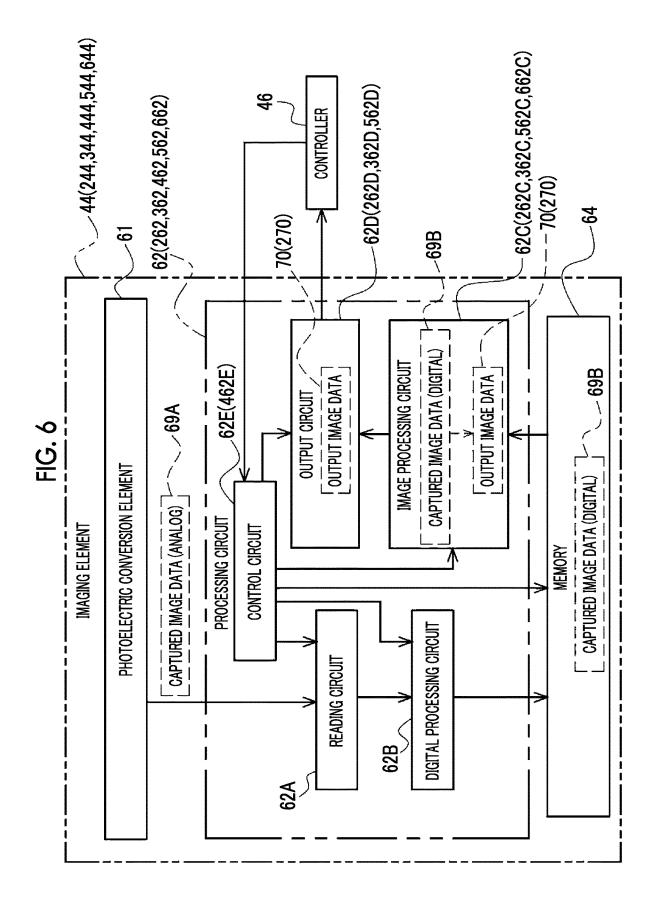

- FIG. **6** is a block diagram illustrating an example of a configuration of the imaging element according to the first to 20 sixth embodiments;

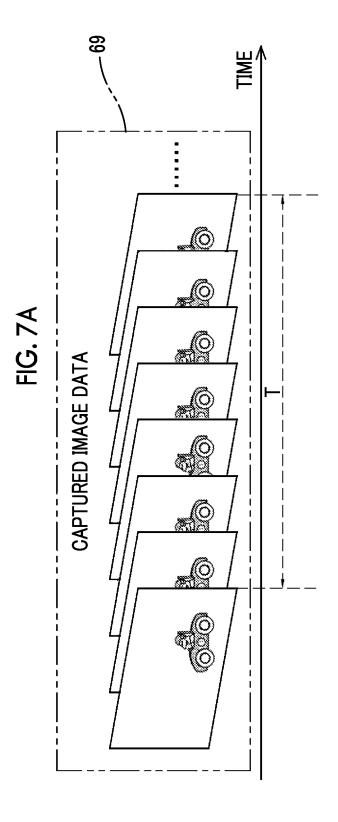

- FIG. 7A is a conceptual diagram for describing an imaging frame rate of the imaging apparatus according to the first to sixth embodiments;

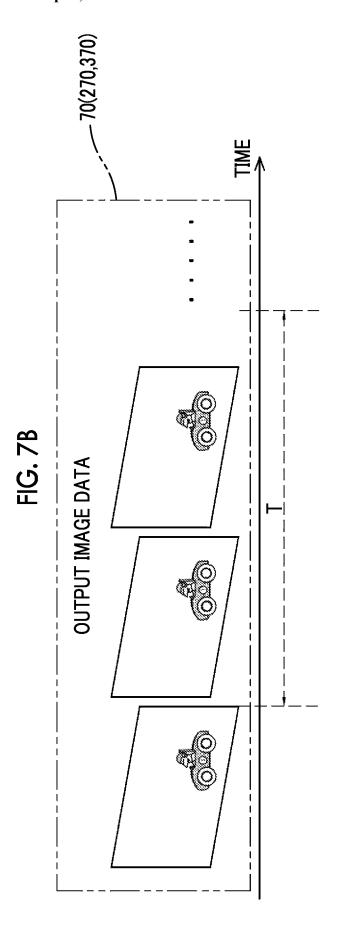

- FIG. 7B is a conceptual diagram for describing an output 25 frame rate of the imaging apparatus according to the first to sixth embodiments;

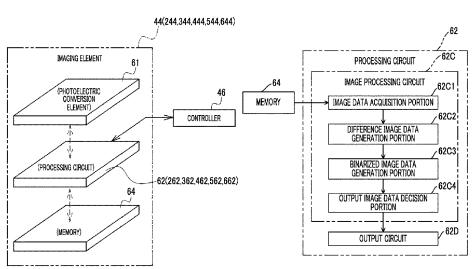

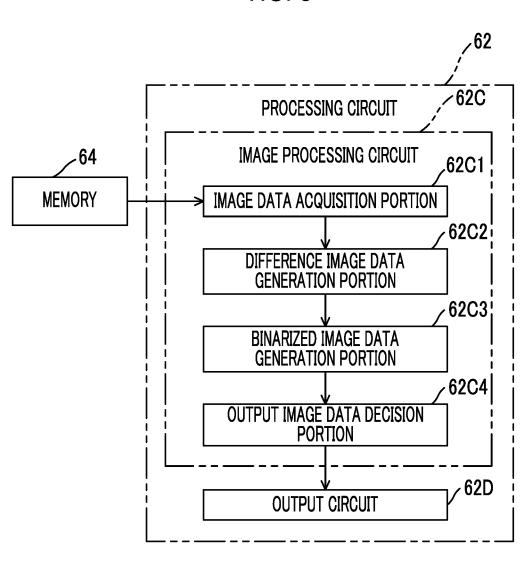

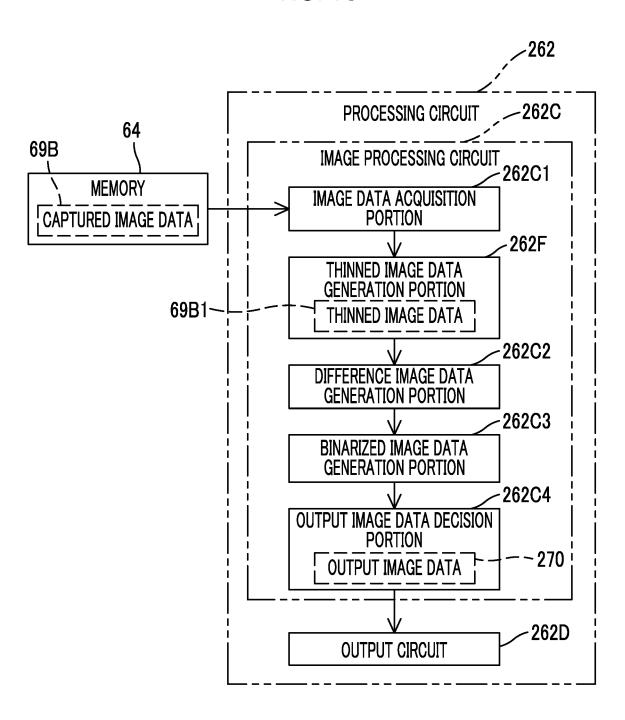

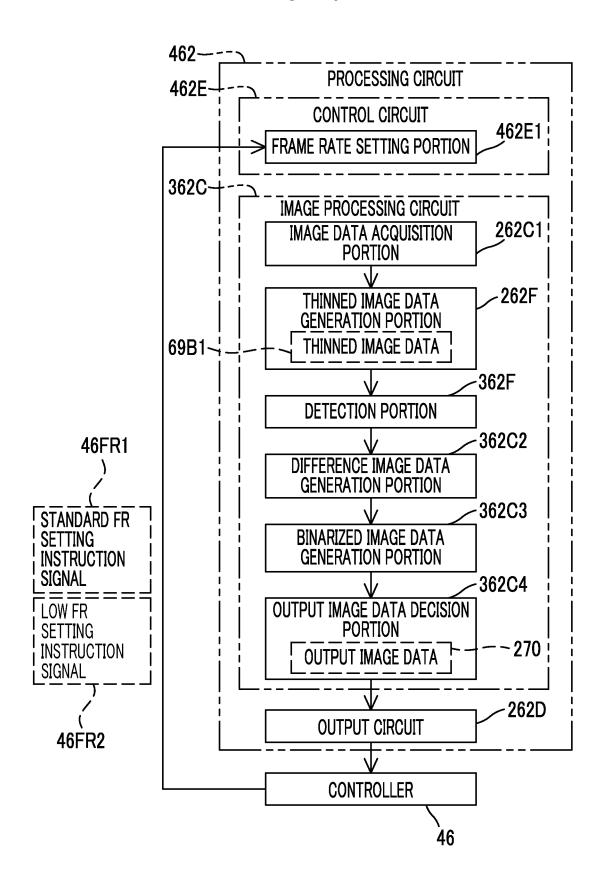

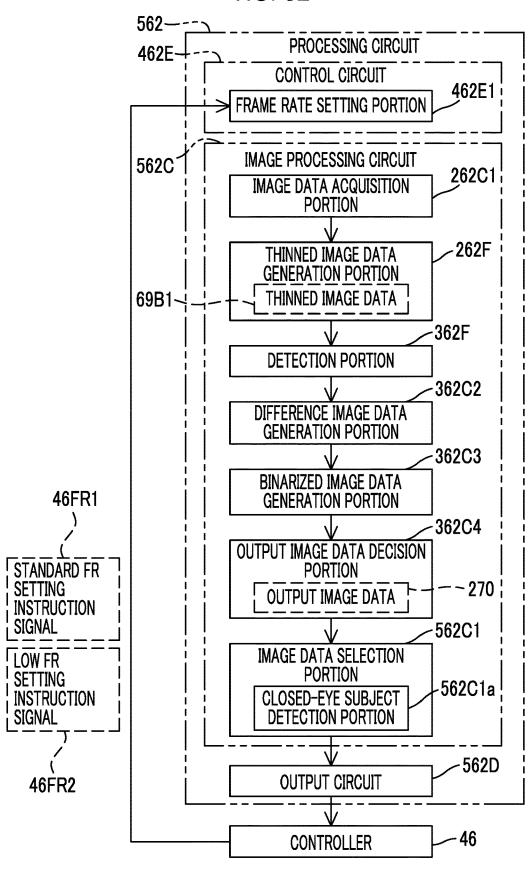

- FIG. 8 is a block diagram illustrating an example of a configuration of a processing circuit included in the imaging element of the imaging apparatus according to the first embodiment;

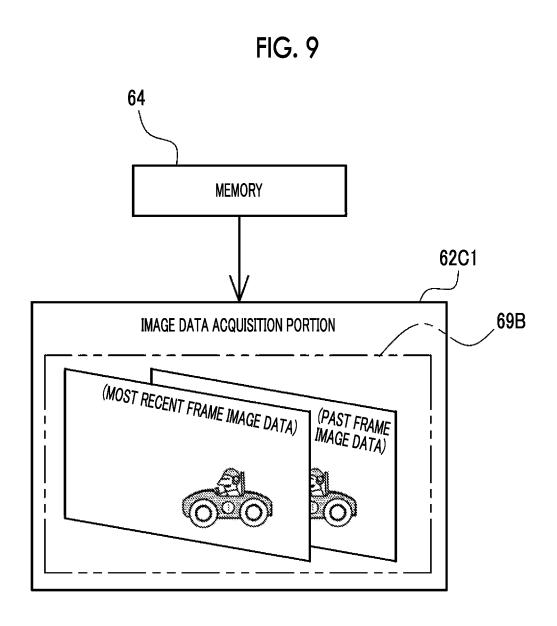

- FIG. 9 is a conceptual diagram for describing an image data acquisition portion illustrated in FIG. 8;

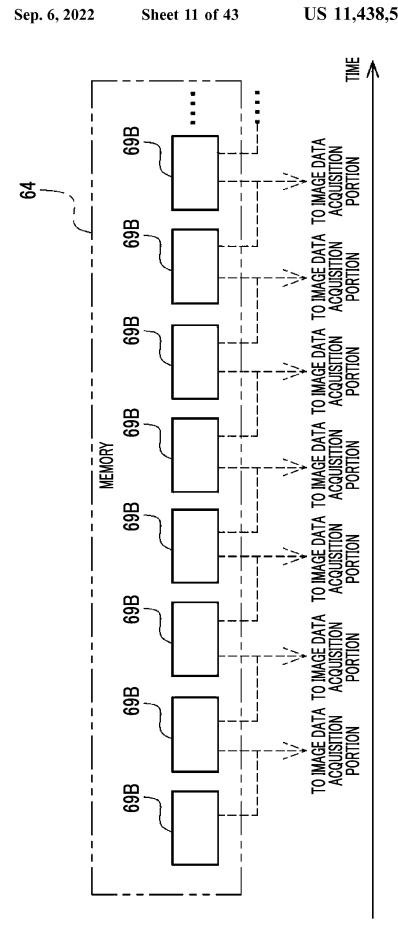

- FIG. 10 is a conceptual diagram illustrating an example of an aspect of output of captured image data output to the image data acquisition portion from a memory illustrated in FIG. 8,

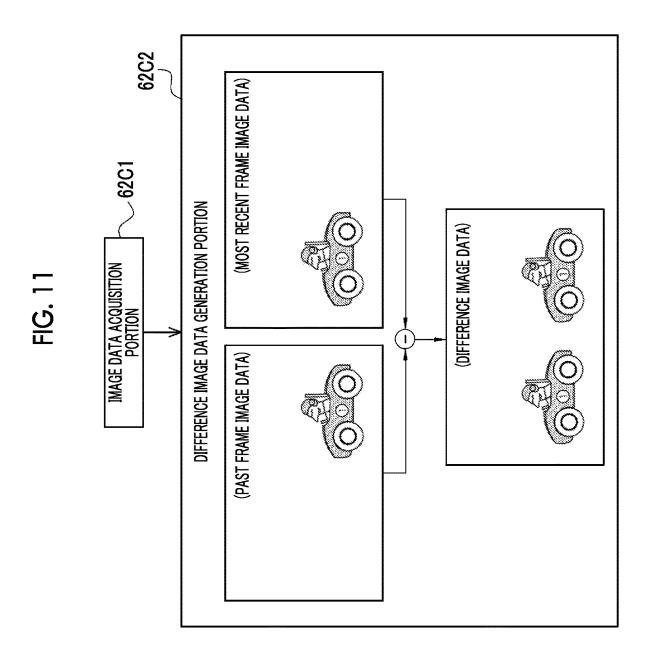

- FIG. 11 is a conceptual diagram for describing a difference image data generation portion illustrated in FIG. 8;

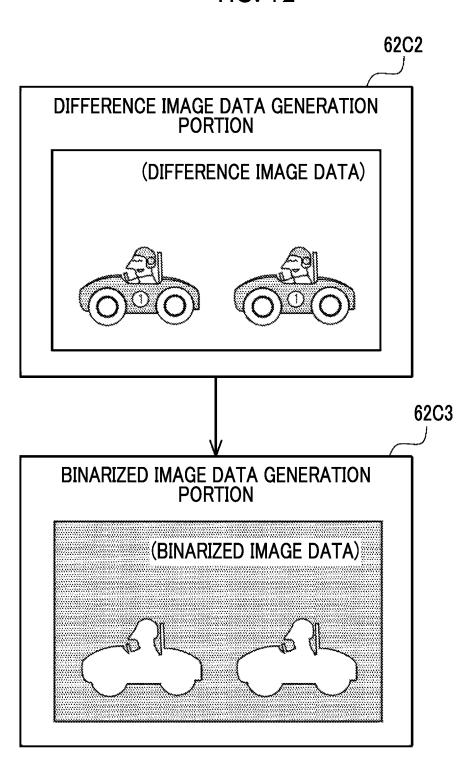

- FIG. 12 is a conceptual diagram for describing the difference image data generation portion and a binarized image data generation portion illustrated in FIG. 8;

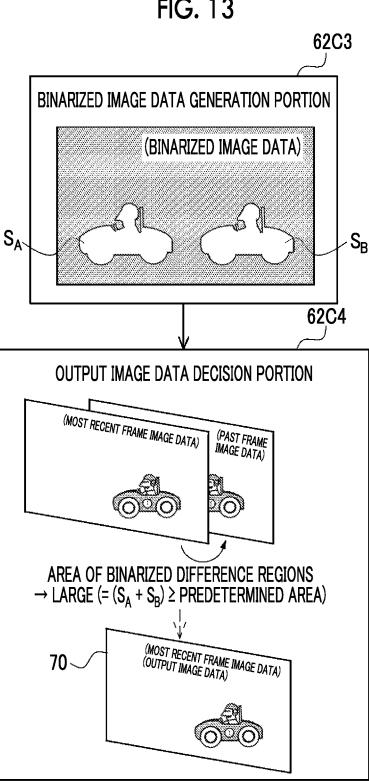

- FIG. 13 is a conceptual diagram for describing the binarized image data generation portion and an output image 45 data decision portion illustrated in FIG. 8;

- FIG. 14 is a conceptual diagram for describing the output image data decision portion illustrated in FIG. 8 and FIG. 13 in detail;

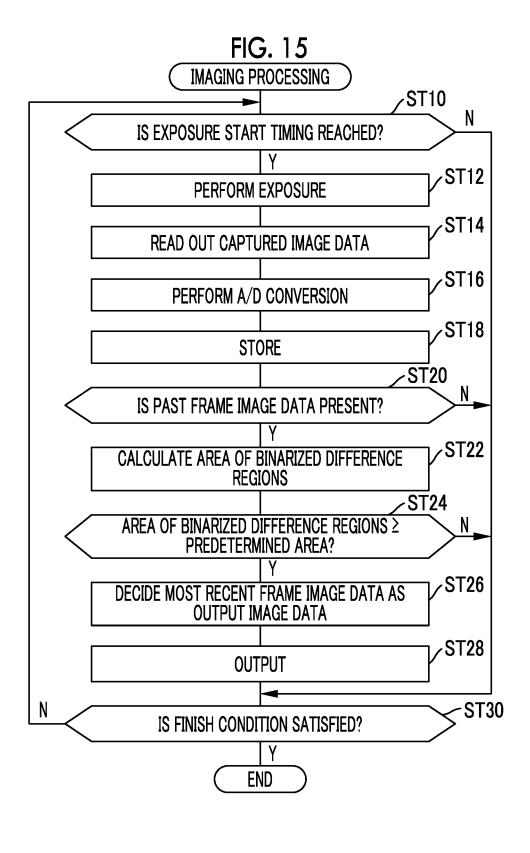

- FIG. 15 is a flowchart illustrating an example of a flow of 50 imaging processing according to the first embodiment;

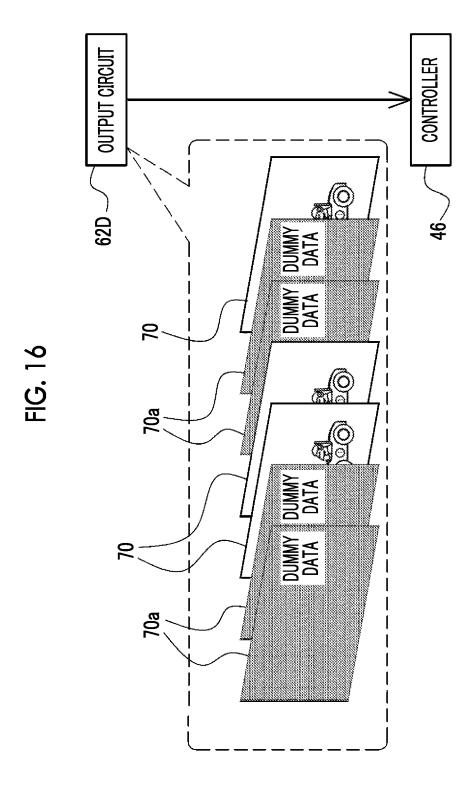

- FIG. 16 is a conceptual diagram illustrating a modification example of image data output by an output circuit included in the processing circuit of the imaging apparatus according to the first embodiment;

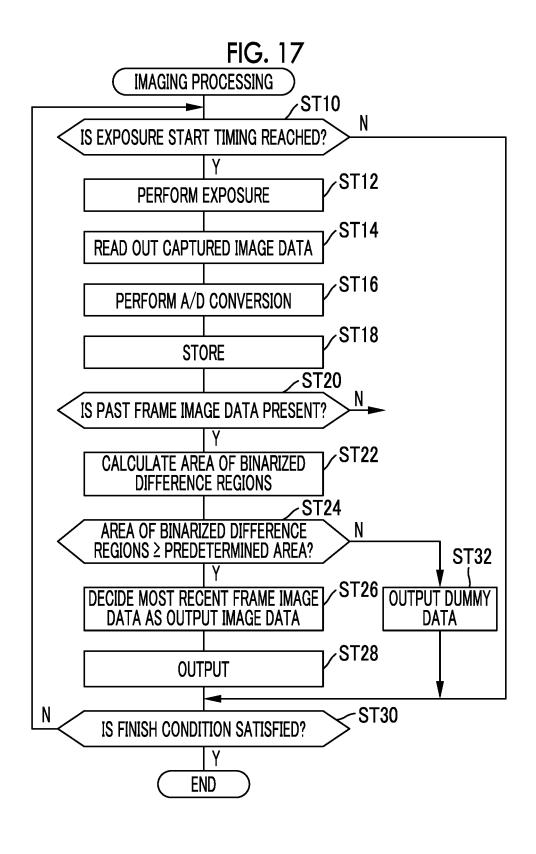

- FIG. 17 is a flowchart illustrating a modification example of the flow of imaging processing according to the first embodiment;

- FIG. **18** is a block diagram illustrating an example of a configuration of a processing circuit included in the imaging 60 element of the imaging apparatus according to the second embodiment:

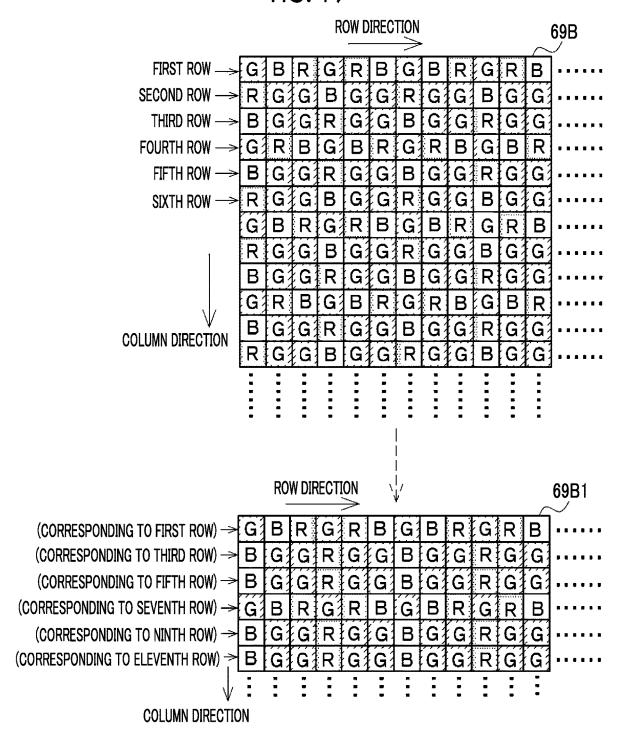

- FIG. 19 is a conceptual diagram illustrating an example of a data structure of each of the captured image data obtained by imaging performed by the imaging element included in 65 the imaging apparatus according to the second embodiment and thinned image data;

6

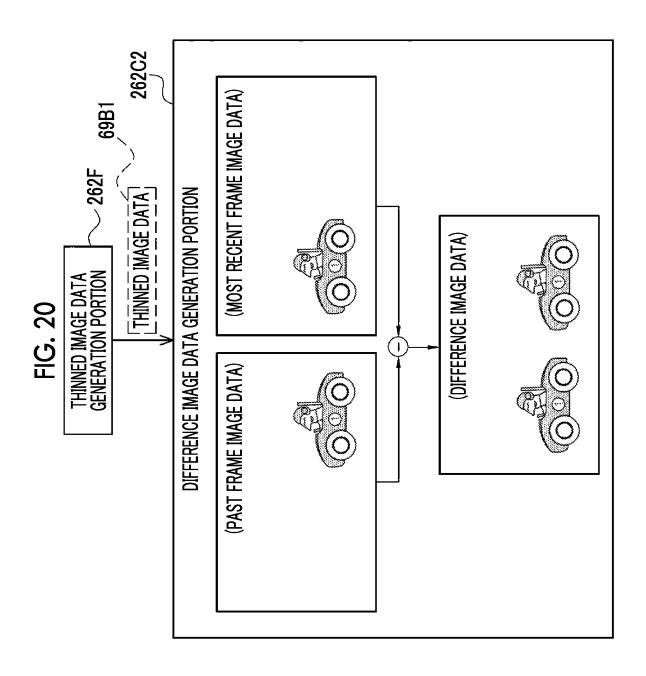

- FIG. 20 is a conceptual diagram for describing a thinned image data generation portion and a difference image data generation portion illustrated in FIG. 18;

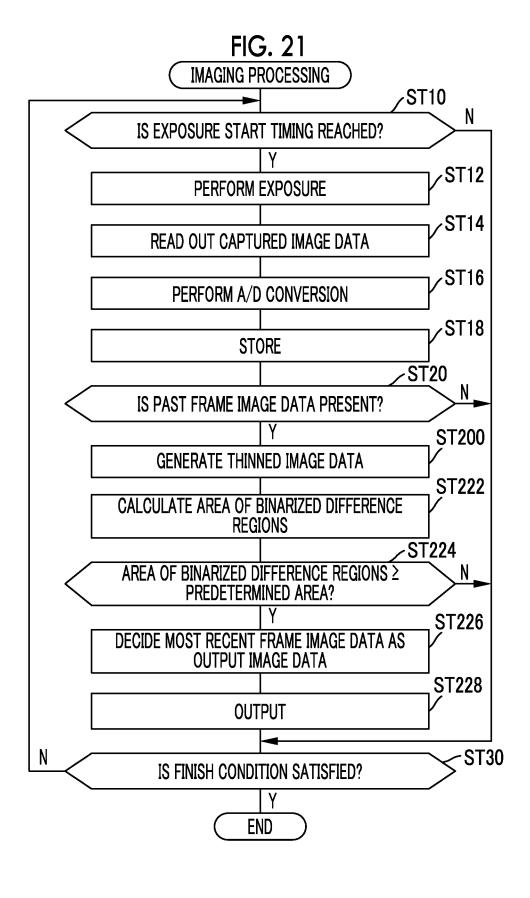

- FIG. 21 is a flowchart illustrating an example of a flow of imaging processing according to the second embodiment;

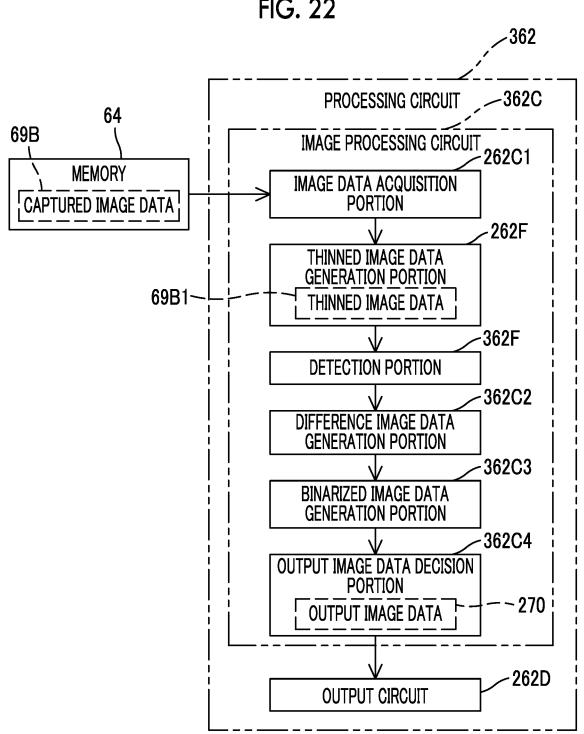

- FIG. 22 is a block diagram illustrating an example of a configuration of a processing circuit included in the imaging element of the imaging apparatus according to the third embodiment;

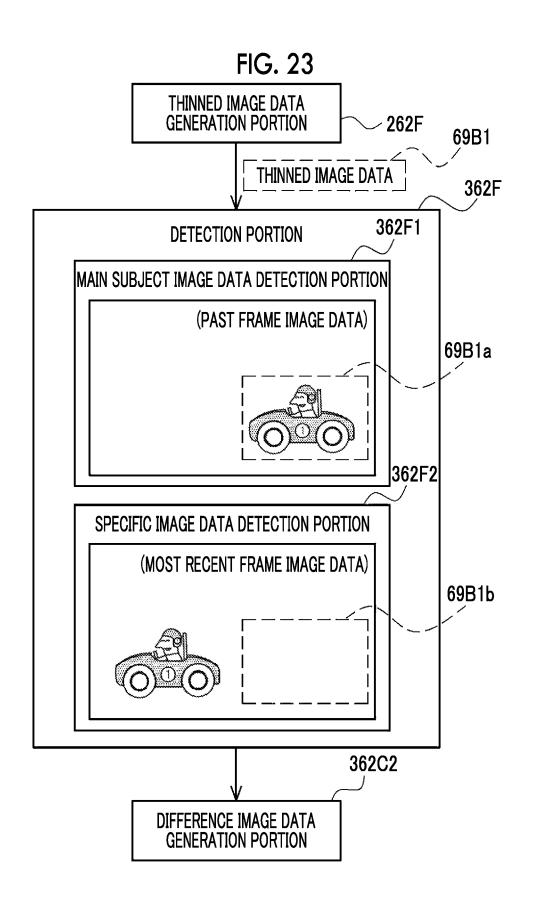

- FIG. 23 is a conceptual diagram for describing the thinned image data generation portion, a detection portion, and a difference image data generation portion illustrated in FIG. 22:

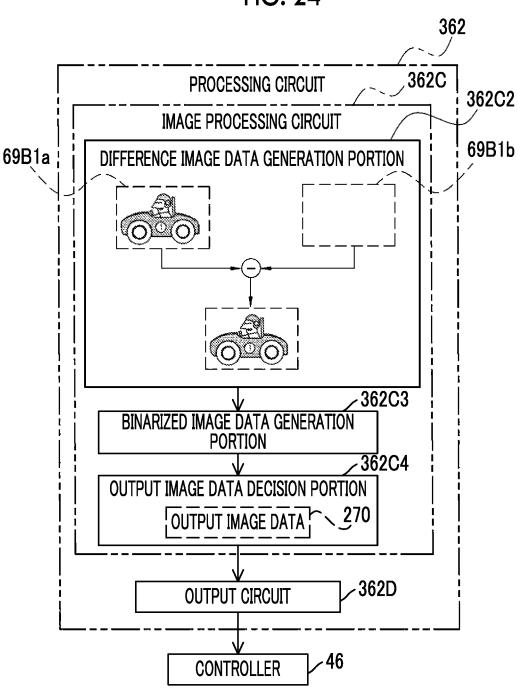

- FIG. 24 is a conceptual diagram for describing an image processing circuit and an output circuit illustrated in FIG. 22 and a controller:

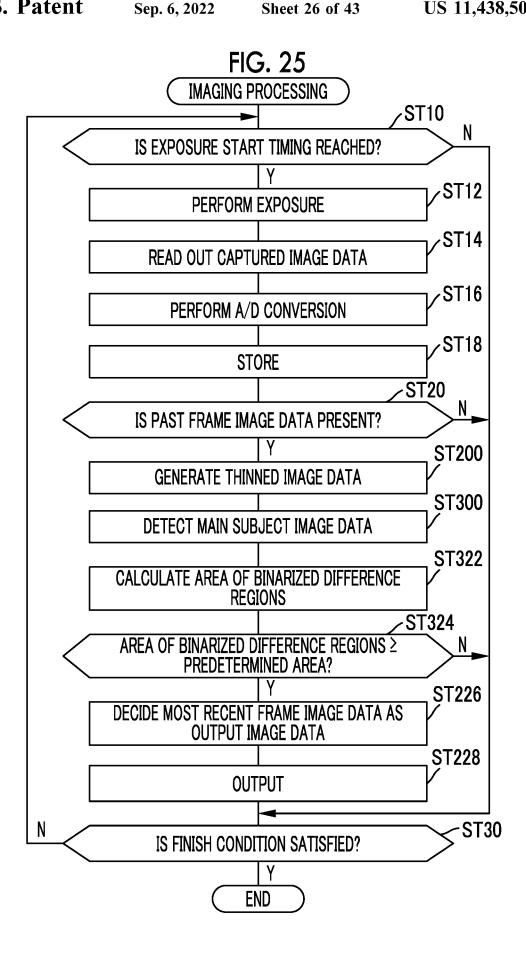

- FIG. **25** is a flowchart illustrating an example of a flow of imaging processing according to the third embodiment;

- FIG. **26** is a block diagram illustrating an example of a configuration of a processing circuit included in the imaging element of the imaging apparatus according to the fourth embodiment;

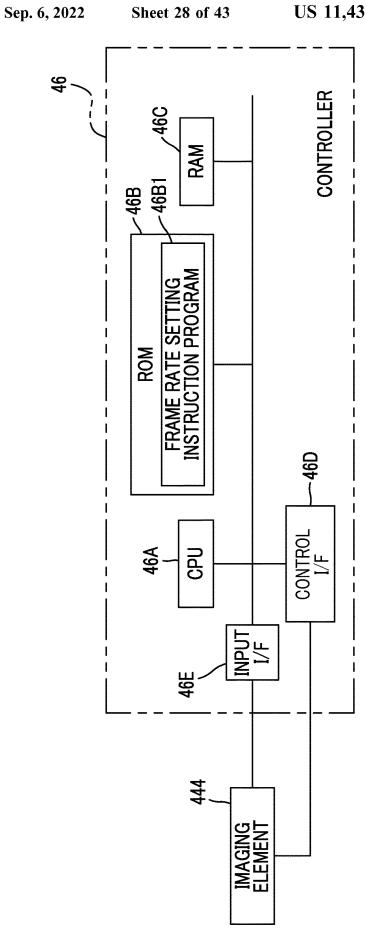

- FIG. 27 is a block diagram illustrating an example of a configuration of the controller included in the imaging apparatus according to the fourth embodiment;

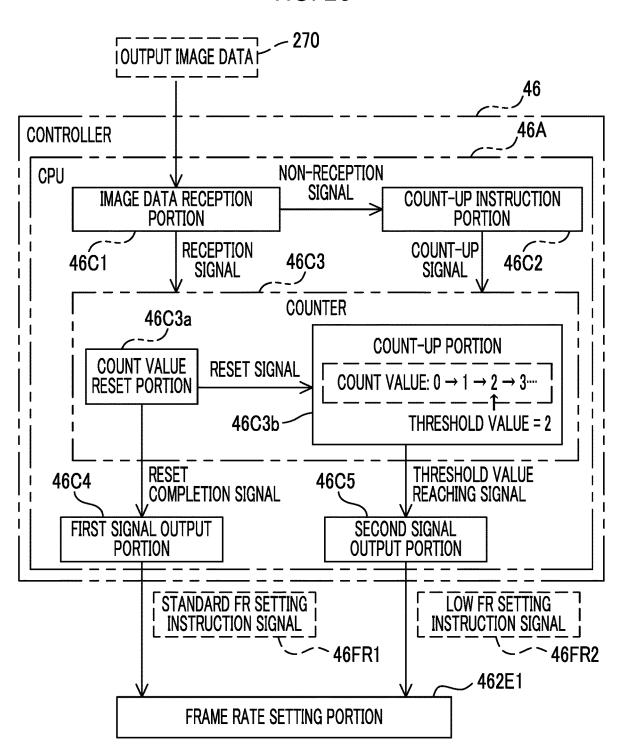

- FIG. 28 is a functional block diagram illustrating an example of a function of a CPU of the controller included in the imaging apparatus according to the fourth embodiment;

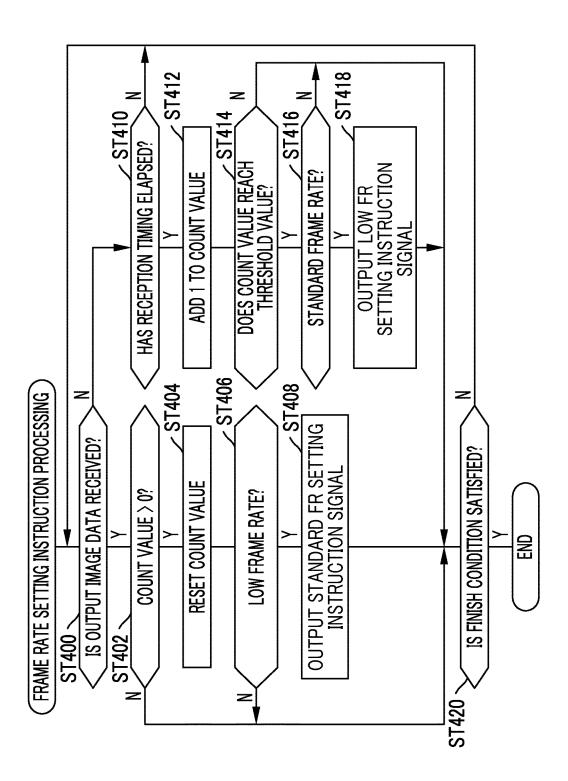

- FIG. 29 is a flowchart illustrating an example of a flow of frame rate setting instruction processing according to the fourth embodiment;

- FIG. 30 is a flowchart illustrating an example of a flow of standard frame rate setting processing according to the fourth embodiment;

- FIG. 31 is a flowchart illustrating an example of a flow of low frame rate setting processing according to the fourth embodiment;

- FIG. 32 is a block diagram illustrating an example of a configuration of a processing circuit included in the imaging element of the imaging apparatus according to the fifth embodiment;

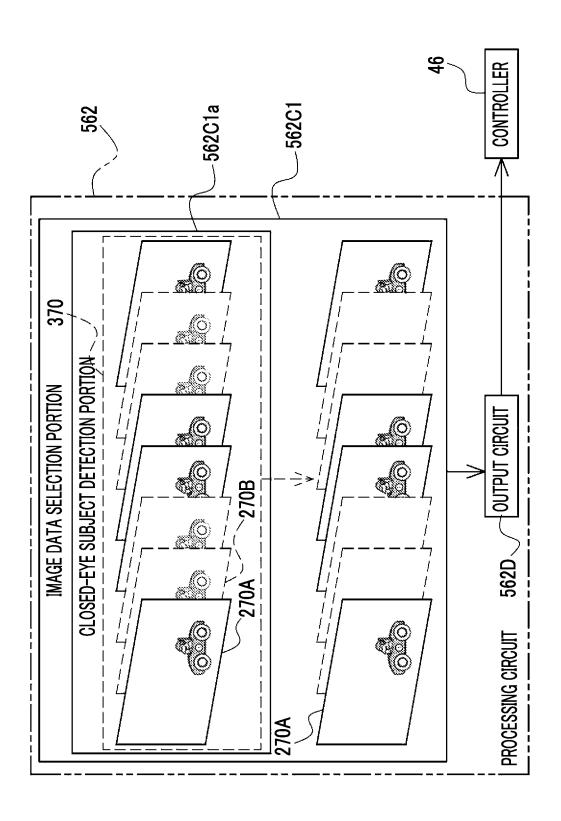

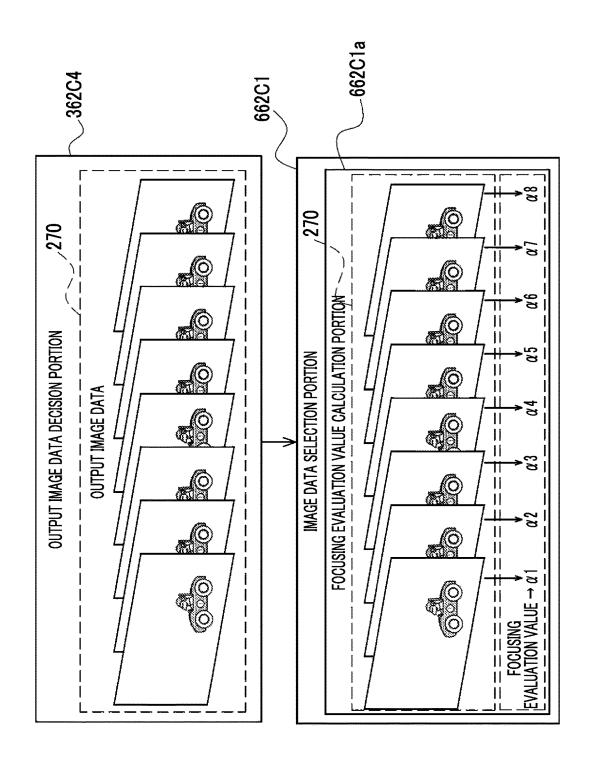

- FIG. 33 is a conceptual diagram for describing an output image data decision portion and an image data selection portion illustrated in FIG. 32;

- FIG. 34A is a conceptual diagram for describing the image data selection portion illustrated in FIG. 33;

- FIG. 34B is a conceptual diagram for describing the image data selection portion illustrated in FIG. 33 in detail;

- FIG. 35 is a conceptual diagram illustrating an example of image data output by an output circuit included in the processing circuit of the imaging apparatus according to the fifth embodiment;

- FIG. **36** is a flowchart illustrating an example of a flow of imaging processing according to the fifth embodiment;

- FIG. 37 is a block diagram illustrating an example of a configuration of a processing circuit included in the imaging element of the imaging apparatus according to the sixth embodiment;

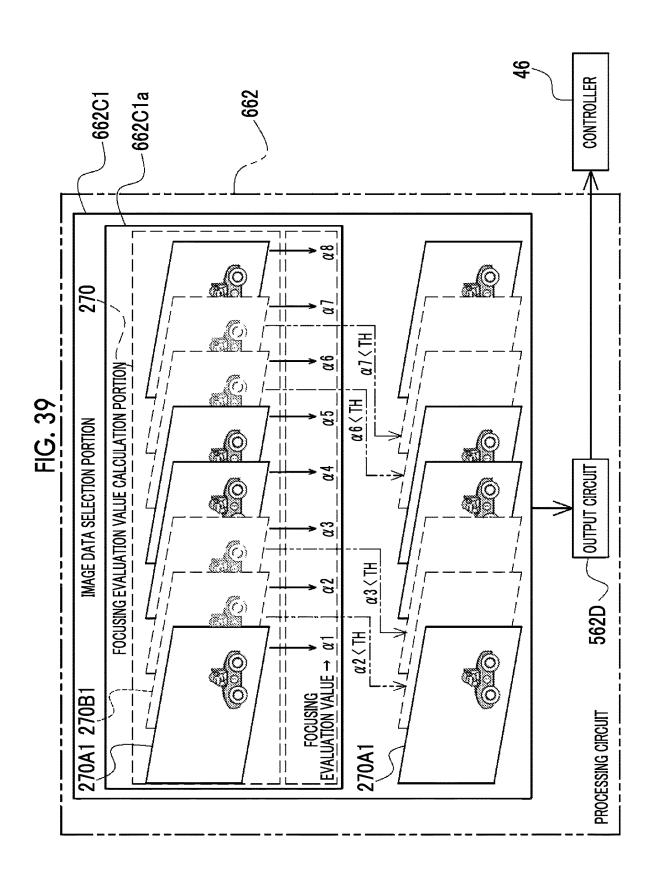

- FIG. 38 is a conceptual diagram for describing the output image data decision portion and an image data selection portion illustrated in FIG. 37;

- FIG. 39 is a conceptual diagram for describing the image data selection portion illustrated in FIG. 38 in detail;

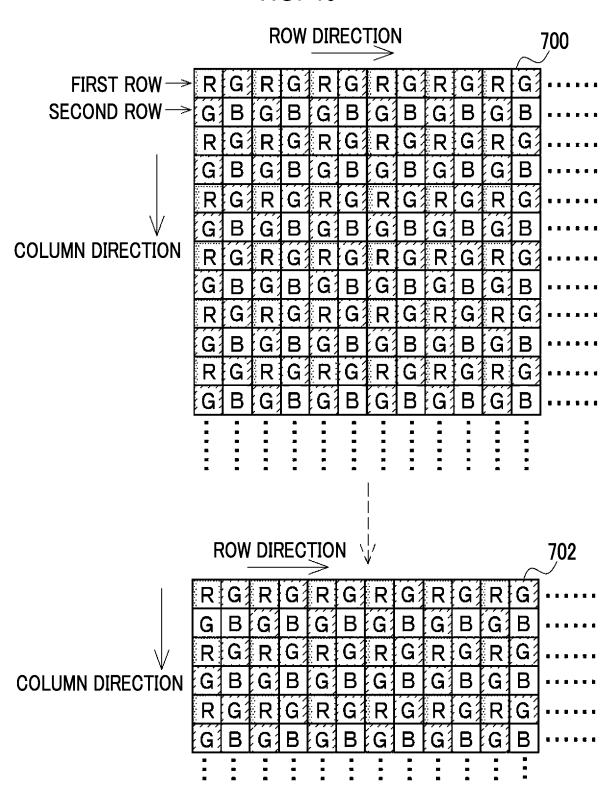

- FIG. 40 is a conceptual diagram illustrating an example of a data structure of each of captured image data and thinned image data corresponding to Bayer arrangement;

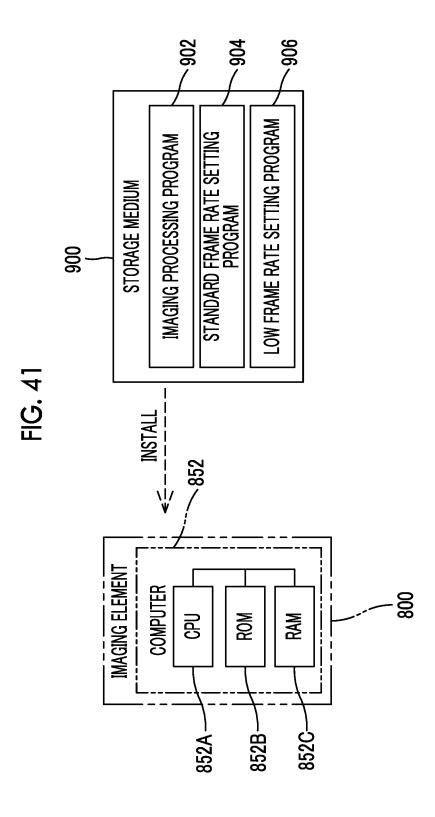

FIG. 41 is a conceptual diagram illustrating an example of an aspect in which a program is installed on a computer within the imaging element from a storage medium storing the program; and

FIG. **42** is a block diagram illustrating an example of a <sup>5</sup> schematic configuration of a smart device incorporating the imaging element according to the embodiments.

#### **DETAILED DESCRIPTION**

Hereinafter, an example of embodiments of an imaging apparatus according to the embodiments of the technology of the present disclosure will be described in accordance with the appended drawings.

First, meanings of terms used in the following description 15 will be described.

In the following description, the abbreviation CPU stands for "Central Processing Unit". In addition, in the following description, the abbreviation RAM stands for "Random Access Memory". In addition, in the following description, 20 the abbreviation ROM stands for "Read Only Memory". In addition, in the following description, the abbreviation DRAM stands for "Dynamic Random Access Memory". In addition, in the following description, the abbreviation SRAM stands for "Static Random Access Memory".

In the following description, the abbreviation LSI stands for "Large-Scale Integration". In addition, in the following description, the abbreviation ASIC stands for "Application Specific Integrated Circuit". In addition, in the following description, the abbreviation PLD stands for "Programmable <sup>30</sup> Logic Device". In addition, in the following description, the abbreviation FPGA stands for "Field-Programmable Gate Array".

In the following description, the abbreviation SSD stands for "Solid State Drive". In addition, in the following description, the abbreviation DVD-ROM stands for "Digital Versatile Disc Read Only Memory". In addition, in the following description, the abbreviation USB stands for "Universal Serial Bus". In addition, in the following description, the abbreviation HDD stands for "Hard Disk Drive". In addition, in the following description, the abbreviation EEPROM stands for "Electrically Erasable and Programmable Read Only Memory".

In the following description, the abbreviation CCD stands for "Charge Coupled Device". In addition, in the following description, the abbreviation CMOS stands for "Complementary Metal Oxide Semiconductor". In addition, in the following description, the abbreviation EL stands for "Electro-Luminescence". In addition, in the following description, the abbreviation A/D stands for "Analog/Digital". In saddition, in the following description, the abbreviation FIFO stands for "First in First out". In addition, in the following description, the abbreviation AF stands for "Auto-Focus". In addition, in the following description, the abbreviation AF stands for "Auto-Focus". In addition, in the following 55 description, the abbreviation AE stands for "Automatic Exposure".

# First Embodiment

As illustrated in FIG. 1 as an example, an imaging apparatus 10 is an interchangeable lens camera. The imaging apparatus 10 is a digital camera that includes an imaging apparatus main body 12 and an interchangeable lens 14, and that does not include a reflex mirror.

A hybrid finder (registered trademark) 16 is disposed in the imaging apparatus main body 12. For example, the 8

hybrid finder 16 here refers to a finder in which an optical view finder (hereinafter, referred to as the OVF) and an electronic view finder (hereinafter, referred to as the EVF) are selectively used. The abbreviation OVF stands for "optical viewfinder". In addition, the abbreviation EVF stands for "electronic viewfinder".

An imaging element 44 is disposed in a front view center portion of the imaging apparatus main body 12. For example, the imaging element 44 is a CMOS image sensor. As will be described in detail later, the imaging element 44 is an example of a "laminated imaging element" according to the embodiments of the technology of the present disclosure. While the CMOS image sensor is illustrated here as the imaging element 44, the technology of the present disclosure is not limited thereto. For example, the technology of the present disclosure is also established in a case where the imaging element 44 is a CCD image sensor.

The interchangeable lens 14 is interchangeably mounted on the imaging apparatus main body 12. An imaging lens 40 is disposed in a lens barrel of the interchangeable lens 14. In a case where the interchangeable lens 14 is mounted on the imaging apparatus main body 12, an optical axis L1 of the imaging lens 40 is positioned in a center portion of a light receiving surface 44A of the imaging element 44, and an image of subject light showing a subject is formed on the light receiving surface 44A through the imaging lens 40.

A focus ring 13 that is used in a case where the imaging apparatus 10 is in a manual focus mode is disposed in the interchangeable lens 14. The imaging lens 40 includes a focus lens 40A. The focus lens 40A moves in an optical axis direction in accordance with a manual rotation operation of the focus ring 13, and the image of the subject light is formed on the light receiving surface 44A at a focal position corresponding to a subject distance. The "focal position" here refers to a position of the focus lens 40A on the optical axis L1 in a focused state.

A finder switching lever 18 is disposed on a front surface of the imaging apparatus main body 12. An optical image visually recognizable by the OVF and a live view image that is an electronic image visually recognizable by the EVF are switched by rotationally moving the finder switching lever 18 in a direction of arrow SW. The "live view image" here refers to a motion picture image for displaying obtained by imaging the subject by the imaging element 44. The live view image is generally referred to as a live preview image.

A release button 20 and a dial 22 are disposed on an upper surface of the imaging apparatus main body 12. The dial 22 is operated in a case of setting an operation mode of an imaging system, an operation mode of a playback system, and the like.

The release button 20 functions as an imaging preparation instruction portion and an imaging instruction portion, and a push operation of two stages of an imaging preparation instruction state and an imaging instruction state can be detected. For example, the imaging preparation instruction state refers to a state where a push is performed to an intermediate position (half push position) from a standby position, and the imaging instruction state refers to a state where a push is performed to a final push position (full push position) exceeding the intermediate position. Hereinafter, the "state where a push is performed to the half push position from the standby position" will be referred to as a "half push state", and the "state where a push is performed to the full push position from the standby position" will be referred to as a "full push state".

In the imaging apparatus 10, an imaging mode and a playback mode are selectively set as an operation mode in

accordance with an instruction of a user. The imaging mode is broadly divided into a display motion picture capturing mode and a recording imaging mode.

The display motion picture capturing mode is an operation mode in which the live view image of a plurality of 5 consecutive frames obtained by consecutive imaging is displayed on a first display 32 and/or a second display 86 (refer to FIG. 3) described later.

The recording imaging mode is broadly divided into a still picture image capturing mode and a motion picture image 10 capturing mode. The still picture image capturing mode is an operation mode in which a still picture image obtained by imaging the subject by the imaging apparatus 10 is recorded, and the motion picture image capturing mode is an operation mode in which a motion picture image obtained by imaging 15 the subject by the imaging apparatus 10 is recorded.

The recording imaging mode is an operation mode in which the live view image is displayed on the first display 32 and/or the second display 86 described later, and in which recording image data is recorded on a secondary storage 20 device 80 (refer to FIG. 3) described later and/or a memory card or the like. The recording image data is broadly divided into still picture image data and motion picture image data. The still picture image data is image data obtained in the still picture image capturing mode, and the motion picture image 25 data is image data obtained in the motion picture image capturing mode.

In a case where the imaging mode is set, first, the imaging apparatus 10 is set to the display motion picture capturing mode. In the display motion picture capturing mode, in a 30 case where the push operation is performed on the release button 20, the imaging apparatus 10 transitions to the recording imaging mode from the display motion picture capturing mode.

In the imaging mode, a manual focus mode and an auto 35 focus mode are selectively set in accordance with an instruction of the user. In the auto focus mode, an imaging condition is adjusted by setting the release button **20** to the half push state. Then, in a case where the full push state is subsequently set, exposure is performed. That is, by setting 40 the release button **20** to the half push state, an AE function is operated, and an exposure state is set. Then, an AF function is operated, and a focusing control is performed. In a case where the release button **20** is set to the full push state, imaging is performed.

As illustrated in FIG. 2 as an example, a touch panel display 26, an instruction key 28, and a finder eyepiece portion 30 are disposed on a rear surface of the imaging apparatus main body 12.

The touch panel display 26 comprises the first display 32 50 and a touch panel 34 (refer to FIG. 3). A liquid crystal display or an organic EL display is illustrated as the first display 32.

The first display 32 displays images, text information, and the like. The first display 32 is used for displaying the live 55 view image which is obtained by consecutive imaging in a case where the imaging apparatus 10 is in the imaging mode. In addition, the first display 32 is used for displaying the still picture image obtained by imaging in a case where a still picture image capturing instruction is provided. Furthermore, the first display 32 is used for displaying a playback image and displaying a menu screen and the like in a case where the imaging apparatus 10 is in the playback mode.

The touch panel 34 is a transmissive touch panel and is overlaid on a surface of a display region of the first display 32. The touch panel 34 senses a contact by an instruction object such as a finger or a stylus pen and outputs a sensing

10

result to a predetermined output destination such as the CPU **46**A (refer to FIG. **3**) described later.

The instruction key 28 receives various instructions such as selection of one or a plurality of menus, confirmation of a selected content, deletion of the selected content, zooming, and frame advance.

As illustrated in FIG. 3 as an example, the imaging apparatus 10 comprises mounts 36 and 38. The mount 36 is disposed in the imaging apparatus main body 12. The mount 38 is disposed in the interchangeable lens 14 at a position corresponding to a position of the mount 36. The interchangeable lens 14 is interchangeably mounted on the imaging apparatus main body 12 by joining the mount 38 to the mount 36.

As illustrated in FIG. 3 as an example, the interchangeable lens 14 includes an imaging lens 40. The imaging lens 40 comprises an objective lens 40B and a stop 40C in addition to the focus lens 40A. The focus lens 40A, the objective lens 40B, and the stop 40C are arranged in an order of the objective lens 40B, the focus lens 40A, and the stop 40C along the optical axis L1 from a subject side to an imaging apparatus main body 12 side.

The imaging lens 40 includes a sliding mechanism 41 and motors 45 and 47. The motor 47 is connected to the stop 40C. The stop 40C adjusts exposure by operating in response to motive power provided from the motor 47.

The sliding mechanism 41 moves the focus lens 40A along the optical axis L1 by receiving motive power. The motor 45 and the focus ring 13 are connected to the sliding mechanism 41. Motive power from the motor 45 or motive power obtained by operating the focus ring 13 is provided to the sliding mechanism 41. That is, the sliding mechanism 41 moves the focus lens 40A along the optical axis L1 in accordance with the motive power from the motor 45 or the motive power obtained by operating the focus ring 13.

The motors 45 and 47 are connected to the imaging apparatus main body 12 through the mounts 36 and 38, and driving of the motors 45 and 47 is controlled in accordance with a command from the imaging apparatus main body 12. In the present embodiment, stepping motors are applied as an example of the motors 45 and 47. Accordingly, the motors 45 and 47 operate in synchronization with pulse electric power in accordance with the command from the imaging apparatus main body 12. While an example of disposing the motors 45 and 47 in the imaging lens 40 is illustrated in the example illustrated in FIG. 3, the technology of the present disclosure is not limited thereto. At least one of the motors 45 and 47 may be disposed in the imaging apparatus main body 12.

A rotary encoder 43 is disposed in the imaging apparatus main body 12. The rotary encoder 43 is connected to the imaging apparatus main body 12 through the mounts 36 and 38. The rotary encoder 43 detects a position of the focus ring 13 and outputs a detection result to the imaging apparatus main body 12.

The imaging apparatus main body 12 comprises a mechanical shutter 42. The mechanical shutter 42 operates by receiving motive power from a driving source (not illustrated) such as a motor under control of the CPU 46A described later. In a case where the interchangeable lens 14 is mounted on the imaging apparatus main body 12 through the mounts 36 and 38, the subject light is transmitted through the imaging lens 40, and the image of the subject light is formed on the light receiving surface 44A through the mechanical shutter 42.

The imaging apparatus main body 12 comprises a controller 46 and a UI system device 48. The controller 46

controls the entire imaging apparatus 10. The UI system device 48 is a device that presents information to the user or receives an instruction from the user. The UI system device 48 is connected to the controller 46 through a busline 88. The controller 46 acquires various types of information from 5 the UI system device 48 and controls the UI system device 48.

The controller 46 comprises a CPU 46A, a ROM 46B, a RAM 46C, a control I/F 46D, and an input I/F 46E. The CPU 46A, the ROM 46B, the RAM 46C, the control I/F 46D, and the input I/F 46E are connected to each other through the busline 88.

The ROM **46**B stores various programs. The CPU **46**A reads out the various programs from the ROM **46**B and loads the read various programs into the RAM **46**C. The CPU **46**A controls the entire imaging apparatus **10** in accordance with the various programs loaded in the RAM **46**C.

The control I/F 46D is a device including an FPGA and is connected to the imaging element 44. The CPU 46A controls 20 the imaging element 44 through the control I/F 46D. In addition, the control I/F 46D is connected to the motors 45 and 47 through the mounts 36 and 38, and the CPU 46A controls the motors 45 and 47 through the control I/F 46D. Furthermore, the control I/F 46D is connected to the rotary 25 encoder 43 through the mounts 36 and 38, and the CPU 46A specifies the position of the focus ring 13 based on the detection result input from the rotary encoder 43.

The secondary storage device **80** and an external I/F **82** are connected to the busline **88**. The secondary storage <sup>30</sup> device **80** is a non-volatile memory such as a flash memory, an SSD, an HDD, or an EEPROM. The CPU **46**A reads out and writes various types of information in the secondary storage device **80**.

The external I/F **82** is a device including an FPGA. An 35 external apparatus (not illustrated) such as a USB memory and a memory card is connected to the external I/F **82**. The external I/F **82** exchanges various types of information between the CPU **46**A and the external apparatus.

The CPU 46A stores output image data 70 (refer to FIG. 40 6) described later in the secondary storage device 80 and/or the external apparatus. The CPU 46A is an example of a "storage control portion" according to the embodiments of the technology of the present disclosure. In addition, the secondary storage device 80 and the external apparatus are 45 an example of a "storage device" according to the embodiments of the technology of the present disclosure.

The UI system device 48 comprises the hybrid finder 16, the touch panel display 26, and a reception portion 84. The first display 32 and the touch panel 34 are connected to the 50 busline 88. Accordingly, the CPU 46A displays various types of information on the first display 32 and operates in accordance with various instructions received by the touch panel 34.

The reception portion **84** comprises the touch panel **34** 55 and a hard key portion **25**. The hard key portion **25** includes a plurality of hard keys and includes a release button **20**, a dial **22**, and an instruction key **28**. The hard key portion **25** is connected to the busline **88**, and the CPU **46**A operates in accordance with various instructions received by the hard 60 key portion **25**.

The hybrid finder 16 comprises the second display 86. The CPU 46A displays various types of information on the second display 86.

As illustrated in FIG. 4 as an example, the hybrid finder 65 16 includes an OVF 90 and an EVF 92. The OVF 90 is a reverse Galilean finder and includes an eyepiece lens 94, a

12

prism 96, and an objective lens 98. The EVF 92 includes the second display 86, the prism 96, and the eyepiece lens 94.

A liquid crystal shutter 100 is arranged closer to the subject side than the objective lens 98 along an optical axis L2 of the objective lens 98. The liquid crystal shutter 100 blocks light such that the optical image is not incident on the objective lens 98 in a case of using the EVF 92.

The prism 96 reflects and guides the electronic image or various types of information displayed on the second display 86 to the eyepiece lens 94 and combines the optical image with the electronic image and/or the various types of information displayed on the second display 86. A live view image is illustrated as an example of the electronic image displayed on the second display 86.

In a case of an OVF mode, the CPU 46A enables the optical image to be visually recognized from the eyepiece lens 94 by controlling the liquid crystal shutter 100 to a non-light blocking state. In addition, in a case of an EVF mode, the CPU 46A enables only the electronic image displayed on the second display 86 to be visually recognized from the eyepiece lens 94 by controlling the liquid crystal shutter 100 to a light blocking state.

Hereinafter, for convenience of description, the first display 32 (refer to FIG. 3) and the second display 86 will be referred to as the "display" without a reference sign unless otherwise necessary to distinguish therebetween. The display is an example of a "display portion" according to the embodiments of the technology of the present disclosure. In addition, the CPU 46A is an example of a "display control portion" according to the embodiments of the technology of the present disclosure.

As illustrated in FIG. 5 as an example, the imaging element 44 incorporates a photoelectric conversion element 61, a processing circuit 62, and a memory 64. In the imaging element 44, the photoelectric conversion element 61 is laminated with the processing circuit **62** and the memory **64**. The imaging element 44 is an imaging element in which the photoelectric conversion element 61, the processing circuit 62, and the memory 64 are formed in one chip. That is, the photoelectric conversion element 61, the processing circuit 62, and the memory 64 are formed in one package. Specifically, the photoelectric conversion element 61 and the processing circuit 62 are electrically connected to each other by a bump (not illustrated) of copper or the like having conductivity. The processing circuit 62 and the memory 64 are also electrically connected to each other by a bump (not illustrated) of copper or the like having conductivity. The memory 64 is an example of a "storage portion" according to the embodiments of the technology of the present disclosure.

The processing circuit 62 is, for example, an LSI, and the memory 64 is, for example, a DRAM. However, the technology of the present disclosure is not limited thereto, and an SRAM may be employed as the memory 64 instead of the DRAM.

The processing circuit 62 is implemented by an ASIC and an FPGA and exchanges various types of information with the controller 46. While an example of implementing the processing circuit 62 by the ASIC and the FPGA is illustrated here, the technology of the present disclosure is not limited thereto. For example, the processing circuit 62 may be implemented by only an ASIC, a PLD, or an FPGA or may be implemented by a combination of the ASIC and the PLD or a combination of the PLD and the FPGA among the ASIC, the PLD, and the FPGA. In addition, a computer including a CPU, a ROM, and a RAM may be employed. The number of CPUs may be singular or plural. In addition,

the processing circuit **62** may be implemented by a combination of a hardware configuration and a software configuration

The photoelectric conversion element **61** includes a plurality of photodiodes arranged in a matrix form. Photodiodes of "4896×3265" pixels are illustrated as an example of the plurality of photodiodes.

The photoelectric conversion element 61 comprises color filters, and the color filters include a G filter corresponding to green (G) that most contributes to obtaining a brightness 10 signal, an R filter corresponding to red (R), and a B filter corresponding to blue (B). In the present embodiment, the G filter, the R filter, and the B filter are arranged with a predetermined periodicity in each of a row direction (horizontal direction) and a column direction (vertical direction) 15 for the plurality of photodiodes of the photoelectric conversion element 61. Thus, the imaging apparatus 10 can perform processing in accordance with a repeating pattern in a case of performing demosaicing and the like on R, G, and B signals. The demosaicing refers to processing of calculating 20 every color information for each pixel from a mosaic image corresponding to color filter arrangement of a single plate color imaging element. For example, in a case of an imaging element consisting of color filters of three colors of R, G, and B, the demosaicing means processing of calculating 25 color information about all of R, G, and B for each pixel from a mosaic image consisting of R, G, and B.

The imaging element **44** has a so-called electronic shutter function and controls an electric charge accumulation time period of each photodiode in the photoelectric conversion 30 element **61** by performing the electronic shutter function under control of the controller **46**. The electric charge accumulation time period refers to a so-called shutter speed.

In the imaging apparatus 10, the imaging for the still picture image and the imaging for the motion picture image 35 are performed using a rolling shutter method. The imaging for the still picture image is implemented by performing the electronic shutter function and operating the mechanical shutter 42 (refer to FIG. 3). The imaging for the live view image is implemented by performing the electronic shutter 40 function without operating the mechanical shutter 42. While the rolling shutter method is illustrated here, the technology of the present disclosure is not limited thereto. A global shutter method may be applied instead of the rolling shutter method.

As illustrated in FIG. 6 as an example, the processing circuit 62 includes a reading circuit 62A, a digital processing circuit 62B, an image processing circuit 62C, an output circuit 62D, and a control circuit 62E. The reading circuit 62A, the digital processing circuit 62B, the image processing circuit 62C, and the control circuit 62E are implemented by ASICs, and the output circuit 62D is implemented by an FPGA. The image processing circuit 62C is an example of a "processing portion" according to the embodiments of the technology of the present disclosure, and the output circuit 55 62D is an example of an "output portion" according to the embodiments of the technology of the present disclosure.

The control circuit **62**E is connected to the controller **46**. Specifically, the control circuit **62**E is connected to the control I/F **46**D (refer to FIG. **3**) of the controller **46** and 60 controls the entire imaging element **44** in accordance with an instruction of the CPU **46**A (refer to FIG. **3**).

The reading circuit **62**A is connected to the photoelectric conversion element **61**, the digital processing circuit **62**B, and the control circuit **62**E. The memory **64** is connected to 65 the digital processing circuit **62**B, the image processing circuit **62**C, and the control circuit **62**E. The image process-

14

ing circuit 62C is connected to the output circuit 62D, the control circuit 62E, and the memory 64.

The output circuit **62**D is connected to the control circuit **62**E and the controller **46**. Specifically, the output circuit **62**D is connected to the input I/F **46**E (refer to FIG. **3**) of the controller **46**.

The reading circuit 62A reads out analog captured image data 69A that is signal electric charges accumulated in the photoelectric conversion element 61, from the photoelectric conversion element 61 under control of the control circuit 62E. Specifically, the reading circuit 62A reads out the captured image data 69A for each frame in accordance with a vertical synchronization signal input from the control circuit 62E. In addition, the reading circuit 62A reads out the captured image data 69A for each row in accordance with a horizontal synchronization signal input from the control circuit 62E within a reading period of one frame.

The digital processing circuit 62B digitizes the analog captured image data 69A by performing signal processing of correlative double sampling processing and then, A/D conversion on the analog captured image data 69A read out by the reading circuit 62A. The digital processing circuit 62B stores captured image data 69B obtained by digitizing the captured image data 69A in the memory 64. Hereinafter, the captured image data 69A and 69B will be referred to as "captured image data 69" unless otherwise necessary to distinguish therebetween.

The memory 64 is a memory that can store the captured image data 69B of a plurality of frames. The memory 64 has a storage region (not illustrated) in units of pixels. The captured image data 69B is stored in a corresponding storage region of the memory 64 in units of pixels by the digital processing circuit 62B.

The image processing circuit 62C performs processing using the captured image data 69B. Specifically, the image processing circuit 62C acquires the captured image data 69B from the memory 64 and performs various types of signal processing on the acquired captured image data 69B. The "various types of signal processing" here include not only well-known signal processing such as tone correction, white balance adjustment, sharpness adjustment, gamma correction, and gradation correction but also signal processing according to the embodiments of the technology of the present disclosure. As will be described in detail later, for example, the signal processing according to the embodiments of the technology of the present disclosure refers to signal processing performed by an image data acquisition portion 62C1, a difference image data generation portion 62C2, a binarized image data generation portion 62C3, and an output image data decision portion 62C4 illustrated in FIG. 8.

The image processing circuit 62C generates the output image data 70 by performing the various types of signal processing on the captured image data 69A and outputs the generated output image data 70 to the output circuit 62D.

The output circuit 62D outputs the output image data 70 based on the captured image data 69B, depending on a result of the various types of signal processing performed by the image processing circuit 62C. Specifically, the output circuit 62D outputs the output image data 70 input from the image processing circuit 62C to the controller 46.

In the imaging element 44, the subject is imaged at an imaging frame rate, and the output image data 70 is output to the controller 46 at an output frame rate. The imaging frame rate is an example of a "first frame rate" according to the embodiments of the technology of the present disclosure, and the output frame rate is an example of a "second frame

rate" according to the embodiments of the technology of the present disclosure. The "imaging" here refers to processing from a start of exposure of one frame in the photoelectric conversion element 61 to storage of the captured image data **69**B of one frame in the memory **64**.

The imaging frame rate is a frame rate required for imaging performed in cooperation among the photoelectric conversion element 61, the reading circuit 62A, the digital processing circuit 62B, the control circuit 62E, and the memory **64**. Meanwhile, the output frame rate is a frame rate that is the same as a frame rate used in a device in a rear stage of the imaging element 44.

The imaging frame rate and the output frame rate may have a relationship of "imaging frame rate≤output frame rate". For example, the imaging frame rate may be a frame 15 rate at which imaging of eight frames is performed within a period T as illustrated in FIG. 7A, and the output frame rate may be a frame rate at which three frames are output within the period T as illustrated in FIG. 7B.

In the present embodiment, 240 frames per second (fps) 20 is employed as the imaging frame rate, and 60 fps is employed as the output frame rate. However, the technology of the present disclosure is not limited thereto. For example, 300 fps may be employed as the imaging frame rate, and 120 fps may be employed as the output frame rate. Alternatively, 25 the imaging frame rate and the output frame rate may be the

As illustrated in FIG. 8 as an example, the image processing circuit 62C includes the image data acquisition portion 62C1, the difference image data generation portion 30 62C2, the binarized image data generation portion 62C3, and the output image data decision portion 62C4. The image data acquisition portion 62C1 is connected to the memory 64. The difference image data generation portion 62C2 is connected to the image data acquisition portion 62C1. The 35 binarized image data generation portion 62C3 is connected to the difference image data generation portion 62C2. The output image data decision portion 62C4 is connected to the binarized image data generation portion 62C3. The output circuit 62D is connected to the output image data decision 40 portion 62C4.

As illustrated in FIG. 9 as an example, the image data acquisition portion 62C1 acquires the captured image data 69B from the memory 64. In the example illustrated in FIG. 9, an aspect of acquiring most recent frame image data and 45 past frame image data as the captured image data 69B by the image data acquisition portion 62C1 is illustrated.

The memory 64 inputs and outputs the captured image data 69B using a FIFO method. The image data acquisition portion 62C1 sequentially acquires the captured image data 50 69B output from the memory 64. The image data acquisition portion 62C1 temporarily holds a pair of pieces of the captured image data 69B sequentially acquired from the memory 64. Out of the pair of pieces of captured image data 69B held by the image data acquisition portion 62C1, the 55 most recent captured image data 69B acquired from the memory 64 is the most recent frame image data. In addition, out of the pair of pieces of captured image data 69B held by the image data acquisition portion 62C1, the captured image data 69B acquired from the memory 64 earlier than the most 60 dance with Expression (2) and Expression (3) below. recent frame image data by one frame is the past frame image data.

That is, as illustrated in FIG. 10 as an example, the captured image data 69B is input and output in the memory 64 using the FIFO method, and each time the captured image 65 data 69B is stored in the memory 64, the image data acquisition portion 62C1 acquires the captured image data

16

69B output from the memory 64. The image data acquisition portion 62C1 temporarily holds the pair of pieces of captured image data 69B of which timings of acquisition from the memory **64** are adjacent.

In a case where new captured image data 69B is acquired from the memory 64, the image data acquisition portion 62C1 outputs the past frame image data. In addition, in a case where new captured image data 69B is acquired from the memory 64, the image data acquisition portion 62C1 holds the most recent frame image data as the past frame image data and holds the newly acquired captured image data 69B as the most recent frame image data. Each time the captured image data 69B is acquired from the memory 64 by the image data acquisition portion 62C1, the pair of pieces of captured image data 69B held by the image data acquisition portion 62C1 are updated.

As illustrated in FIG. 11 as an example, the captured image data 69B output from the image data acquisition portion 62C1 is input into the difference image data generation portion 62C2. The difference image data generation portion 62C2 acquires the captured image data 69B from the image data acquisition portion 62C1 and holds the captured image data 69B as the most recent frame image data and the past frame image data in the same manner as the image data acquisition portion 62C1. Furthermore, in a case where new captured image data 69B is acquired from the image data acquisition portion 62C1, the difference image data generation portion 62C2 updates the most recent frame image data and the past frame image data of a holding target in the same manner as the image data acquisition portion 62C1 and outputs the captured image data 69B held as the past frame image data to the binarized image data generation portion 62C3 (refer to FIG. 8 and FIG. 12).

The difference image data generation portion 62C2 calculates an absolute value (hereinafter, referred to as a "difference absolute value") of a difference between the currently held pair of pieces of captured image data 69B, that is, the most recent frame image data and the past frame image data, and generates difference image data based on the difference absolute value. Here, in a case where the past frame image data is denoted by  $I_{past}(x, y)$ , and the most recent frame image data is denoted by  $I_{curr}(x, y)$ , difference image data  $I_{diff}(x, y)$  is calculated in accordance with Expression (1) below.

$$I_{diff}(x,y) = |I_{curr}(x,y) - I_{past}(x,y)| \tag{1}$$

In a case where the difference image data  $I_{diff}(x, y)$  is calculated, the difference image data generation portion **62**C2 outputs the calculated difference image data  $I_{diff}(x, y)$ to the binarized image data generation portion 62C3 (refer to FIG. 12).

As illustrated in FIG. 12 as an example, the binarized image data generation portion 62C3 acquires the difference image data from the difference image data generation portion 62C2 and generates binarized image data from the acquired difference image data. The binarized image data generation portion 62C3 binarizes the difference image data  $I_{diff}(x, y)$ . For example, the difference image data  $I_{diff}(x, y)$ is converted into binarized image data  $I_{bin}(x, y)$  in accor-

$$I_{bin}(x,y)=1$$

( $I_{diff}(x,y)$ >threshold value  $T1$ ) (2)

$$I_{bin}(x,y) = 0 (I_{diff}(x,y) \le \text{threshold value } T1)$$

(3)

The captured image data 69B output from the difference image data generation portion 62C2 is input into the binarized image data generation portion 62C3. The binarized

image data generation portion 62C3 acquires the captured image data 69B from the difference image data generation portion 62C2 and holds the captured image data 69B as the most recent frame image data and the past frame image data in the same manner as the image data acquisition portion 62C1. Furthermore, in a case where new captured image data 69B is acquired from the difference image data generation portion 62C3, the binarized image data generation portion 62C3 updates the most recent frame image data and the past frame image data of the holding target in the same manner as the image data acquisition portion 62C1 and outputs the captured image data 69B held as the past frame image data to the output image data decision portion 62C4 (refer to FIG. 8).

In the example illustrated in FIG. 13, binarized difference regions  $S_A$  and  $S_B$  of " $I_{bin}(x, y)=1$ " are included in the binarized image data. The output image data decision portion 62C4 calculates a total area ( $=\Sigma I_{bin}(x, y)$ ) of the binarized difference region  $S_A$  and the binarized difference 20 region  $S_B$  and determines whether or not the calculated total area is greater than or equal to a predetermined area. In a case where the calculated total area is greater than or equal to the predetermined area, the output image data decision portion 62C4 decides the most recent frame image data as 25 the output image data 70 out of the most recent frame image data and the past frame image data that are used for generating the binarized image data including the binarized difference region  $S_A$  and the binarized difference region  $S_B$ .

For example, the "predetermined area" is an area obtained 30 from a result of a computer simulation and/or a sensory test using an actual apparatus, as an area of the binarized difference regions in a case where it is possible to visually recognize that the subject has a motion during imaging of two frames. In the first embodiment, an area of 20 percent 35 62C1. of an area of the entire image indicated by the binarized image data is employed as the "predetermined area". The "predetermined area" may be a fixed value or a variable value that can be changed in accordance with an instruction received by the reception portion 84 (refer to FIG. 3). The 40 "predetermined area" is an example of a "threshold value" according to the embodiments of the technology of the present disclosure. The total area of the binarized difference region  $S_A$  and the binarized difference region  $S_B$  is an example of a "degree of difference" according to the 45 embodiments of the technology of the present disclosure. Hereinafter, for convenience of description, the total area of the binarized difference region S<sub>4</sub> and the binarized difference region  $S_B$  will be simply referred to as the "area of the binarized difference regions".

As illustrated in FIG. 14 as an example, each time the captured image data 69B is input from the binarized image data generation portion 62C3, the output image data decision portion 62C4 compares the total area of the binarized difference regions of the binarized image data corresponding 55 to the input captured image data 69B with the predetermined area. The output image data decision portion 62C4 determines whether or not to output the input captured image data 69B to the output circuit 62D based on a comparison result. The output image data decision portion 62C4 sequentially 60 outputs the output image data 70 decided as the captured image data 69B to be output to the output circuit 62D.

The output circuit 62D outputs image data at the output frame rate based on a processing result of the image processing circuit 62C. Specifically, the output circuit 62D 65 outputs the output image data 70 based on the captured image data 69B at the output frame rate depending on the

18

processing result obtained by processing the captured image data **69**B by the image processing circuit **62**C.

Next, an action of the imaging apparatus 10 will be described.

First, a flow of imaging processing executed by the processing circuit 62 of the imaging element 44 will be described with reference to FIG. 15.

In the imaging processing illustrated in FIG. 15, first, in step ST10, the reading circuit 62A determines whether or not a timing (hereinafter, referred to as an "exposure start timing") at which the photoelectric conversion element 61 starts the exposure is reached. The exposure start timing is a timing that is periodically defined by the imaging frame rate. In step ST10, in a case where the exposure start timing is not reached, a negative determination is made, and the imaging processing transitions to step ST30. In step ST10, in a case where the exposure start timing is reached, a positive determination is made, and the imaging processing transitions to step ST12.

In step ST12, the reading circuit 62A causes the photoelectric conversion element 61 to perform the exposure of one frame.

In subsequent step ST14, the reading circuit 62A reads out the captured image data 69A of one frame from the photoelectric conversion element 61.

In subsequent step ST16, the digital processing circuit 62B digitizes the captured image data 69A by performing signal processing of the correlative double sampling processing and then, the A/D conversion on the captured image data 69A read out in step ST14.

In subsequent step ST18, the digital processing circuit 62B stores captured image data 69B obtained by digitization in the memory 64. The captured image data 69B stored in the memory 64 is acquired by the image data acquisition portion 62C1

In subsequent step ST20, the image data acquisition portion 62C1 determines whether or not the past frame image data is included. That is, the image data acquisition portion 62C1 determines whether or not the pair of pieces of captured image data 69B including the most recent frame image data and the past frame image data are held. In step ST20, in a case where the past frame image data is not included, a negative determination is made, and the imaging processing transitions to step ST30. In step ST20, in a case where the past frame image data is included, a positive determination is made, and the imaging processing transitions to step ST22.

In step ST22, first, the difference image data generation portion 62C2 calculates the difference absolute value of the most recent frame image data and the past frame image data acquired by the image data acquisition portion 62C1 and generates the difference image data from the calculated difference absolute value. Next, the binarized image data generation portion 62C3 generates the binarized image data by binarizing the difference image data. The output image data decision portion 62C4 calculates the binarized difference regions from the binarized image data value generated by the binarized image data generation portion 62C3.

In subsequent step ST24, the output image data decision portion 62C4 determines whether or not the area of the binarized difference regions is greater than or equal to the predetermined area. In step ST24, in a case where the area of the binarized difference regions is not greater than or equal to the predetermined area, a negative determination is made, and the imaging processing transitions to step ST30. In step ST24, in a case where the area of the binarized difference regions is greater than or equal to the predeter-

mined area, a positive determination is made, and the imaging processing transitions to step ST26.

In step ST26, the output image data decision portion 62C4 decides the most recent frame image data as the output image data 70 out of the most recent frame image data and 5 the past frame image data which are used for generating the binarized image data including the binarized difference regions.

In subsequent step ST28, the output circuit 62D outputs the output image data 70 decided in step ST26 to the 10 controller 46.

The controller 46 displays the output image data 70 input from the output circuit 62D on the display as the live view image or the still picture image or stores the output image data 70 in the secondary storage device 80 and/or the 15 memory card (not illustrated).

In step ST30, the control circuit 62E determines whether or not a condition (hereinafter, referred to as an "imaging processing finish condition") under which the imaging processing is finished is satisfied. For example, a condition that 20 an instruction to finish the imaging processing is received by the reception portion 84 is illustrated as the imaging processing finish condition. In step ST30, in a case where the imaging processing finish condition is not satisfied, a negative determination is made, and the imaging processing 25 transitions to step ST10. In step ST30, in a case where the imaging processing finish condition is satisfied, the imaging processing is finished.

As described above, the imaging element 44 comprises the memory 64, the image processing circuit 62C, and the 30 memory 64. The memory 64 stores the captured image data 69B obtained by imaging the subject at the imaging frame rate. In the image processing circuit 62C, a degree of difference between the most recent frame image data and the past frame image data which are the pair of pieces of 35 captured image data 69B is calculated.

In the first embodiment, the degree of difference refers to the area of the binarized difference regions. An increase in area of the binarized difference regions means an increase in motion of the subject. Thus, it is expected that the captured 40 image data 69 obtained by imaging at this point is image data worth displaying or storing for the user. Conversely, a decrease in area of the binarized difference regions means a decrease in motion of the subject. Thus, it is expected that the captured image data 69 obtained by imaging at this point 45 is image data not worth displaying or storing for the user.

Therefore, in the image processing circuit **62**C, in a case where the area of the binarized difference regions is greater than or equal to the predetermined area, the most recent frame image data used for calculating the degree of difference is decided as the output image data **70**. The output image data **70** is output to the controller **46** by the output circuit **62**D. Accordingly, the power consumption required for outputting the image data can be reduced, compared to a case of outputting every image data obtained by imaging. 55

In addition, the imaging element 44 is an imaging element in which the photoelectric conversion element 61, the processing circuit 62, and the memory 64 are formed in one chip. Accordingly, portability of the imaging element 44 is increased, compared to an imaging element in which the 60 photoelectric conversion element 61, the processing circuit 62, and the memory 64 are not formed in one chip. In addition, a degree of design freedom can be increased, compared to a case of the imaging element in which the photoelectric conversion element 61, the processing circuit 65, and the memory 64 are not formed in one chip. Furthermore, it is possible to contribute to size reduction of the

20

imaging apparatus main body 12, compared to a case of the imaging element in which the photoelectric conversion element 61, the processing circuit 62, and the memory 64 are not formed in one chip.

In addition, as illustrated in FIG. 5, the laminated imaging element in which the photoelectric conversion element 61 is laminated with the memory 64 is employed as the imaging element 44. Accordingly, a transfer speed of the captured image data 69 from the photoelectric conversion element 61 to the memory 64 can be increased, compared to a case of not laminating the photoelectric conversion element 61 and the memory 64. Improving the transfer speed contributes to high-speed processing in the entire processing circuit 62. In addition, the degree of design freedom can be increased, compared to a case of not laminating the photoelectric conversion element 61 and the memory 64. Furthermore, it is possible to contribute to size reduction of the imaging apparatus main body 12, compared to a case of not laminating the photoelectric conversion element 61 and the memory 64.

In addition, in the imaging apparatus 10, the live view image or the like based on the output image data 70 is displayed on the second display 86. Accordingly, the user can visually recognize an image indicated by the output image data 70. In addition, the power consumption can be reduced, compared to a case of displaying every captured image data 69B obtained by imaging the subject on the display. In addition, the user can visually recognize only an image that is expected to be highly necessary for the user.

Furthermore, in the imaging apparatus 10, the output image data 70 is stored in the secondary storage device 80 and/or the memory card or the like. Accordingly, a storage capacity of the secondary storage device 80 and/or the memory card can be prolonged, compared to a case of storing every captured image data 69B obtained by imaging the subject in the secondary storage device 80 or the like.

While an example of a form in which the most recent frame image data not decided as the output image data 70 in step ST26 is not output to the controller 46 by the output circuit 62D is illustratively described in the first embodiment, the technology of the present disclosure is not limited thereto. For example, in a case where the area of the binarized difference regions is less than the predetermined area, as illustrated in FIG. 16, dummy data 70a may be output instead of the most recent frame image data out of the most recent frame image data and the past frame image data which are used for generating the binarized image data including the binarized difference regions. That is, the output circuit 62D may output the dummy data 70a to the controller 46 instead of the most recent frame image data not decided as the output image data 70 in step ST26 of the imaging processing. For example, image data having the same pixel value for all pixels is illustrated as the dummy data 70a. For example, the image data having the same pixel value for all pixels refers to image data in which pixel values for all pixels are "0".

In a case where the output circuit 62D outputs the dummy data 70a, imaging processing illustrated in FIG. 17 as an example is executed by the processing circuit 62. In the example illustrated in FIG. 17, in a case where a negative determination is made in step ST24 of the imaging processing, the imaging processing transitions to step ST32. In step ST32, the output circuit 62D outputs the dummy data 70a to the controller 46. Then, the imaging processing transitions to step ST30.

In a case where the area of the binarized difference regions is less than the predetermined area, the dummy data

70a is output to the controller 46 by the output circuit 62D. In a case where the area of the binarized difference regions is less than the predetermined area, it is expected that the captured image data 69 obtained by imaging at this point is image data not worth displaying or storing for the user. In 5 this case, by outputting the dummy data 70a to the controller 46, a degree of change in data between the imaging element 44 and the controller 46, that is, a toggle rate of data, can be decreased, compared to a case of simply not outputting the image data. Consequently, the power consumption required for outputting the image data can be reduced, compared to an output of any captured image data 69 to the controller 46 in a case where the area of the binarized difference regions is less than the predetermined area. The dummy data 70a is an example of "first dummy data" according to the embodi- 15 ments of the technology of the present disclosure.

In addition, while the area of the binarized difference regions in the first embodiment is illustrated as an example of the "degree of difference" according to the embodiments of the technology of the present disclosure, the technology of the present disclosure is not limited thereto. For example, an absolute value of a simple difference between the most recent frame image data and the past frame image data may be applied instead of the area of the binarized difference regions.