(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4931329号

(P4931329)

(45) 発行日 平成24年5月16日(2012.5.16)

(24) 登録日 平成24年2月24日(2012.2.24)

(51) Int.CI.

H01G 4/30 (2006.01)

F 1

H01G 4/30 301B

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2003-335812 (P2003-335812)

(22) 出願日 平成15年9月26日 (2003.9.26)

(65) 公開番号 特開2004-140351 (P2004-140351A)

(43) 公開日 平成16年5月13日 (2004.5.13)

審査請求日 平成18年9月12日 (2006.9.12)

審判番号 不服2010-4126 (P2010-4126/J1)

審判請求日 平成22年2月25日 (2010.2.25)

(31) 優先権主張番号 特願2002-284379 (P2002-284379)

(32) 優先日 平成14年9月27日 (2002.9.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000006633

京セラ株式会社

京都府京都市伏見区竹田鳥羽殿町6番地

(72) 発明者 西村 道明

鹿児島県国分市山下町1番4号 京セラ

株式会社総合研究所内

(72) 発明者 佐藤 恒

鹿児島県国分市山下町1番1号 京セラ

株式会社鹿児島国分工場内

(72) 発明者 竹下 良博

鹿児島県国分市山下町1番4号 京セラ

株式会社総合研究所内

最終頁に続く

(54) 【発明の名称】コンデンサ、配線基板、デカップリング回路及び高周波回路

## (57) 【特許請求の範囲】

## 【請求項 1】

誘電体層の一方主面に第1導体層が、前記誘電体層の他方主面に第2導体層が配設されるとともに、前記誘電体層の厚み方向に、前記第2導体層と第1非導体形成領域によって隔てられ、且つ前記第1導体層に接続される複数の第1貫通導体と、前記第1導体層と第2非導体形成領域によって隔てられ、且つ前記第2導体層に接続される複数の第2貫通導体とが形成されてなるコンデンサにおいて、

2つの前記第1貫通導体及び2つの前記第2貫通導体が格子状に配置されて格子の縦横の方向に隣接する前記第1貫通導体の前記第1非導体形成領域と前記第2貫通導体の前記第2非導体形成領域とが積層方向に重なり合った貫通導体群を複数形成しているとともに、複数の前記貫通導体群が互いに一様な距離をもって配置され、前記第1導体層及び前記第2導体層の周縁部と前記貫通導体群との間に、前記格子の縦横の方向に隣接する前記第1貫通導体と前記第2貫通導体との中心間の間隔以上の幅で、前記第1導体層及び前記第2導体層が存在していることを特徴とするコンデンサ。

## 【請求項 2】

前記貫通導体群が、前記第1貫通導体及び前記第2貫通導体並びに前記第1導体層及び前記第2導体層を流れる電流によって誘起される磁界を互いに相殺するように配置されていることを特徴とする請求項1記載のコンデンサ。

## 【請求項 3】

前記貫通導体群内において、前記第1貫通導体及び前記第2貫通導体が、実質的に正方

形の各頂点に位置する分布状態をもって互いに隣り合うように配置されていることを特徴とする請求項 1 又は 2 記載のコンデンサ。

【請求項 4】

請求項 1 乃至 3 のうちいずれかに記載のコンデンサを備えたことを特徴とする配線基板。

【請求項 5】

請求項 1 乃至 3 のうちいずれかに記載のコンデンサを備えたことを特徴とするデカップリング回路。

【請求項 6】

請求項 1 乃至 3 のうちいずれかに記載のコンデンサを備えたことを特徴とする高周波回路。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンデンサ、配線基板、デカップリング回路及び高周波回路に関するもので、特に、高周波領域において有利に適用され得るコンデンサ、ならびに、このコンデンサを用いて構成される、配線基板、デカップリング回路及び高周波回路に関するものである。

【背景技術】

【0002】

20

代表的なコンデンサとして、積層コンデンサを例にとって説明する。

【0003】

積層コンデンサを用いた等価回路では、コンデンサの静電容量を  $C$ 、等価直列インダクタンス (E S L) を  $L$  としたとき、共振周波数 ( $f_0$ ) は、 $f_0 = 1 / [2 \times (L \times C)]^{1/2}$  の関係で表され、共振周波数 ( $f_0$ ) より高い周波数領域では、コンデンサの機能が消失してしまうことが知られている。すなわち、一定値以上の静電容量 ( $C$ ) を維持するためには、できるだけ E S L ( $L$ ) を低くする必要がある。つまり、E S L が低ければ、共振周波数 ( $f_0$ ) は高くなり、より高周波領域で使用できることになる。このことから、積層コンデンサをマイクロ波領域で使うためには、より低 E S L 化が図られたものが必要となる。

30

【0004】

また、ワークステーションやパーソナルコンピュータ等のマイクロプロセッsingユニット (M P U) の M P U チップに電源を供給するために用いられ、通常デカップリングコンデンサとして配線基板上に接続されている積層コンデンサも、近年の M P U の高速、高周波化に伴って、低 E S L 化が求められている。

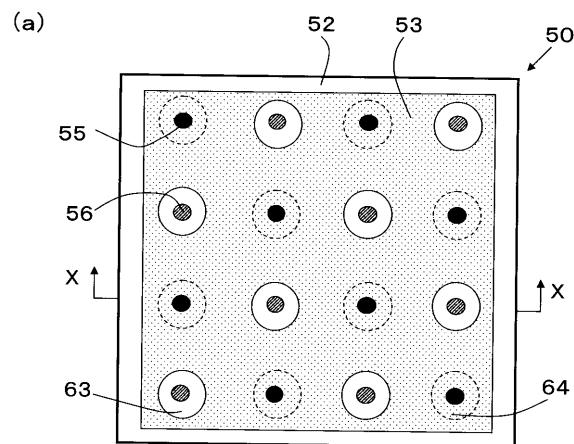

【0005】

ここで、従来の積層コンデンサについて、図 6 (a)  (b)  をもとに説明する。(a) は第 1 及び第 2 導体層の重なり状態を示す概略図、(b) は (a) の X - X 線断面図である。

【0006】

40

図に示す従来の積層コンデンサ 50 は、誘電体層 52 の一方正面に第 1 導体層 53 が、他方正面に第 2 導体層 54 が夫々形成され、これらの誘電体層 52 が複数積層されており、また、これらの誘電体層 52 の厚み方向には第 1 及び第 2 導体層 53、54 同士を夫々接続する第 1 及び第 2 貫通導体 55、56 が形成され、

積層体 51 が構成されている。そして、ここでは、第 1 及び第 2 貫通導体 55、56 が、積層体 51 の一方の最表面に露出し、夫々第 1 及び第 2 接続端子 57、58 に接続され、積層コンデンサ 50 が構成されている。さらに、第 1 及び第 2 導体層 53、54 内に、第 2 及び第 1 貫通導体 56、55 とは夫々接続しない第 1 及び第 2 非導体形成領域 63、64 が形成されている。

【0007】

50

そして、第1及び第2貫通導体55、56は、第1及び第2導体層53、54の全域にわたって、交互に格子状に分散して配置されている。

【0008】

上記積層コンデンサ50によれば、静電容量は、第1及び第2導体層53、54の内、主に第1及び第2貫通導体55、56に囲まれた部分に発生していた。

【0009】

また、上記積層コンデンサ50の製造方法は、未焼成状態の積層体1に、脱バインダ処理、焼成を行い、積層体1を得た後、第1及び第2接続端子7、8を形成していた（特許文献1乃至4参照）。

【特許文献1】特開平7-201651号公報（3-5頁、図1-5）

10

【特許文献2】特開平11-204372号公報（4-6頁、図1-4）

【特許文献3】特開2001-148324号公報（4-7頁、図1-6）

【特許文献4】特開2001-148325号公報（5-7頁、図1-9）

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかしながら、上記積層コンデンサ50によれば、低ESL化を図るために、第1及び第2貫通導体55、56の数を増加するとともに、これらの中心間の距離を小さくする方法が考えられるが、第1及び第2貫通導体55、56の数を増加した場合、第1及び第2導体層53、54内の非導体形成領域63、64の面積が増大するため、積層コンデンサ50の静電容量が低下するという問題点があった。一方、上記中心間の距離を小さくした場合、未焼成状態の積層体1のハンドリングや、焼成時の誘電体層2と第1及び第2貫通導体55、56の収縮率の差、ICパッケージなどへの実装時の誘電体層2と第1及び第2貫通導体55、56との熱膨張係数の差などにより、第1及び第2貫通導体55、56にまたがるように、クラックが発生するという問題点があった。

20

【0011】

また、上記積層コンデンサ50によれば、第1導体層53と第2非導体形成領域64、あるいは第2導体層54と第1非導体形成領域63が重なる部分は、静電容量が発生しないため、積層コンデンサ50の高容量化には限界があった。

【0012】

30

本発明は、上述の問題点に鑑みて案出されたものであり、その目的は、低ESL且つ高容量を実現し、且つクラックの発生を抑制できるコンデンサを提供することである。

【0013】

本発明の他の目的は、上述したようなコンデンサを用いて構成される、配線基板、デカップリング回路及び高周波回路を提供することである。

【課題を解決するための手段】

【0014】

本発明のコンデンサは、誘電体層の一方主面に第1導体層が、前記誘電体層の他方主面に第2導体層が配設されるとともに、前記誘電体層の厚み方向に、前記第2導体層と第1非導体形成領域によって隔てられ、且つ前記第1導体層に接続される複数の第1貫通導体と、前記第1導体層と第2非導体形成領域によって隔てられ、且つ前記第2導体層に接続される複数の第2貫通導体とが形成されてなるコンデンサにおいて、

40

2つの前記第1貫通導体及び2つの前記第2貫通導体が格子状に配置されて格子の縦横の方向に隣接する前記第1貫通導体の前記第1非導体形成領域と前記第2貫通導体の前記第2非導体形成領域とが積層方向に重なり合った貫通導体群を複数形成しているとともに、複数の前記貫通導体群が互いに一様な距離をもって配置され、前記第1導体層及び前記第2導体層の周縁部と前記貫通導体群との間に、前記格子の縦横の方向に隣接する前記第1貫通導体と前記第2貫通導体との中心間の間隔以上の幅で、前記第1導体層及び前記第2導体層が存在していることを特徴とするものである。

【0018】

50

また、前記貫通導体群が、前記第1及び第2貫通導体及び前記第1及び第2導体層を流れる電流によって誘起される磁界を互いに相殺するように配置される。

【0020】

また、前記貫通導体群内において、前記第1及び第2の貫通導体が、実質的に正方形の各頂点に位置する分布状態をもって互いに隣り合うように配置される。

【0021】

また、本発明は上述のコンデンサを備えた配線基板にも適用できる。

【0022】

さらに、本発明に係るコンデンサは、MPUに備えるMPUチップのための電源回路に接続されるデカッピングコンデンサとしても有利に用いられる。

10

【0023】

また、本発明は、上述のコンデンサを備えた高周波回路にも適用できる。

【発明の効果】

【0024】

以上の通り、本発明のコンデンサによれば、2つの第1貫通導体及び2つの第2貫通導体が格子状に配置されて格子の縦横の方向に隣接する第1貫通導体の第1非導体形成領域と第2貫通導体の第2非導体形成領域とが積層方向に重なり合った貫通導体群の複数が、互いに一様な距離をもって配置されているため、貫通導体群内のみに流れる電流は、流れる距離が短くなることから、電流によって誘起される磁束に起因する自己インダクタンス成分が低くなる。このため、コンデンサ全体の等価直列インダクタンス(ESL)を低くできる。また、ESLを低くするために、第1及び第2貫通導体の数を増加する必要がないため、コンデンサの高容量化を実現できる。さらに、貫通導体群間に、貫通導体の無い領域が存在するため、複数の貫通導体群にまたがるように応力が発生することを防止でき、コンデンサのクラックの発生を抑制できる。

20

【0025】

また、貫通導体群を構成し、且つ隣接しあう第1貫通導体と第2貫通導体との間に容量の発生する領域が存在しないため、第1貫通導体から他方、例えば第2貫通導体へ流れる電流は、ほとんど無くなる。このことにより、電流によって誘起される磁束に起因する自己インダクタンス成分が極めて低くなり、コンデンサ全体のESLをさらに低くすることができる。また、第1導体層と第2非導体形成領域、あるいは第2導体層と第1非導体形成領域が重なる部分の面積が減少するため、コンデンサのさらなる高容量化を実現できる。

30

【0026】

さらに、第1導体層及び第2導体層の周縁部と貫通導体群の間に、第1貫通導体と第2貫通導体との中心間の間隔P以上の幅で、第1貫通導体、第2貫通導体及び非導体形成領域の無い、静電容量領域が形成されているため、静電容量領域の第1導体層及び第2導体層に流れる電流の量が多くなり、このことによってもコンデンサ全体のESLをさらに効果的に低くすることができる。また、貫通導体群の周囲に静電容量が発生するため、加わる電界を大きくすることができ、このことによってもコンデンサの高容量化を実現できる。

40

【0027】

またさらに、貫通導体群が、貫通導体及び導体層を流れる電流によって誘起される磁界を互いに相殺するように配置されるため、コンデンサ全体のESLをさらに効果的に低くすることができる。

【0028】

さらにまた、貫通導体群が、一様な距離をもって互いに隣り合うように配置されるため、貫通導体群間で部分的にESLが高くなることがなく、コンデンサ全体のESLをさらに効果的に低くすることができる。

【0029】

そして、貫通導体群内において、第1及び第2の貫通導体が、実質的に正方形の各頂点

50

に位置する分布状態をもって互いに隣り合うように配置されるため、貫通導体群内で部分的に E S L が高くなることがなく、コンデンサ全体の E S L をさらに効果的に低くすることができる。

【 0 0 3 0 】

また、本発明は、上述のコンデンサを備えた配線基板、M P U に備えるM P U チップのための電源回路に接続されるデカップリングコンデンサとしても有利に用いられる。

【 0 0 3 1 】

また、本発明は、上述のコンデンサを備えた高周波回路にも適用できる。

【発明を実施するための最良の形態】

【 0 0 3 2 】

以下、本発明のコンデンサ、配線基板、デカップリング回路及び高周波回路を図面に基づいて詳説する。

【 0 0 3 3 】

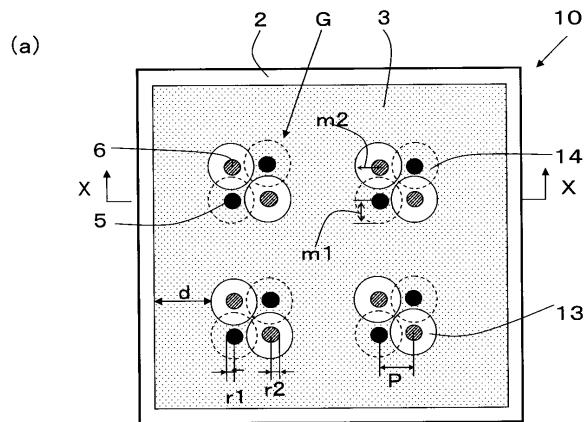

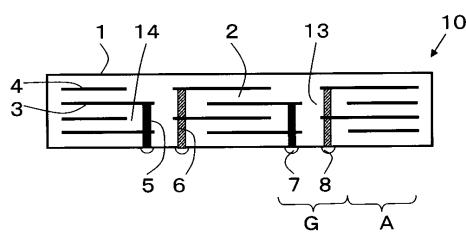

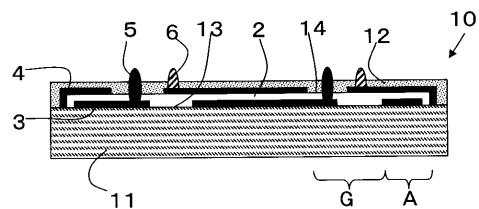

図 1 は本発明のコンデンサの一例である積層コンデンサを示す図であり、( a ) は第 1 及び第 2 導体層の重なり状態を示す概略図、( b ) は( a ) の X - X 線断面図である。

【 0 0 3 4 】

図において、1 0 は積層コンデンサ、2 は誘電体層、3 、4 は第 1 及び第 2 導体層(内部電極層)、5 、6 は第 1 及び第 2 貫通導体(ビアホール導体)、7 、8 は第 1 及び第 2 接続端子である。

【 0 0 3 5 】

図に示すように、積層コンデンサ 1 0 は、誘電体層 2 の一方主面に第 1 導体層 3 が、他方主面に第 2 導体層 4 が夫々形成され、これらの誘電体層 2 が複数積層されており、また、これらの誘電体層 2 の厚み方向には第 1 及び第 2 導体層 3 、4 同士を夫々接続する複数の第 1 及び第 2 貫通導体 5 、6 が形成され、積層体 1 が構成されている。そして、ここでは、複数の第 1 及び第 2 貫通導体 5 、6 が、積層体 1 の一方の最表面に露出し、第 1 及び第 2 接続端子 7 、8 に接続され、積層コンデンサ 1 0 が構成されている。さらに、第 1 及び第 2 導体層 3 、4 内に、第 2 及び第 1 貫通導体 6 、5 とは夫々接続しない第 1 及び第 2 非導体形成領域 1 3 、1 4 が形成されている。

【 0 0 3 6 】

そして、第 1 及び第 2 貫通導体 5 、6 は、例えば 2 つの第 1 貫通導体 5 と 2 つの第 2 貫通導体 6 が互いに格子状となるようにして貫通導体群 G を構成し、この貫通導体群 G が第 1 導体層 3 及び第 2 導体層 4 に分散して配置されている。例えば、図 1 では、4 つの貫通導体群 G で構成され、平面視、矩形状の各頂点となる位置に配置されている。

【 0 0 3 7 】

誘電体層 2 は、チタン酸バリウムを主成分とする非還元性誘電体材料、及びガラス成分を含む誘電体材料からなり、この誘電体層 2 が図上、上方向に積層して積層体 1 が構成される。なお、誘電体層 2 の形状、厚み、積層数は容量値によって任意に変更することができる。第 1 及び第 2 導体層 3 、4 は、N i 、C u 、あるいはこれらの合金を主成分とする材料から構成され、その厚みは 1 ~ 2  $\mu$  m としている。

【 0 0 3 8 】

第 1 及び第 2 接続端子 7 、8 は、半田バンプ、半田ボールなどが用いられる。

【 0 0 3 9 】

本発明の特徴的なことは、少なくとも一対の第 1 貫通導体 5 及び第 2 貫通導体 6 (図 1 では 2 対の第 1 貫通導体 5 及び第 2 貫通導体 6 ) とが近接してなる貫通導体群 G が、一様な距離をもって配置されていることである。

【 0 0 4 0 】

また、貫通導体群 G を構成し、且つ隣接しあう第 1 貫通導体 5 と第 2 貫通導体 6 との間に容量の発生する領域が存在しない。具体的には、近接してなる第 1 貫通導体 5 の中心と第 2 貫通導体 6 の中心との間隔を P 、非導体形成領域 1 3 、1 4 の半径を m 1 、m 2 としたときに、 $P = m 1 + m 2$  の関係を満足する。ここで、等価直列抵抗( E S R ) の増大を

10

20

30

40

50

防ぐためには、第1及び第2の貫通導体3、4の半径を夫々  $r_1$ 、 $r_2$ としたときに、 $r_1 + m_2 \leq P$ 、あるいは  $r_2 + m_1 \leq P$  の関係を満足することが望ましい。また、高容量を実現するためには、 $P > 1.4m_1$ 、且つ  $P > 1.4m_2$  の関係にあることが望ましい。

【0041】

さらに、第1導体層3及び第2導体層4の周縁部と貫通導体群Gの間に、間隔P以上の幅dで、第1貫通導体5、第2貫通導体6及び非導体形成領域13、14の無い、静電容量領域Aが形成されている。好ましくは  $d \leq 1.5P$ 、さらに好ましくは  $d \leq 2P$  の関係にあることが望ましい。

【0042】

またさらに、貫通導体群Gが、貫通導体5、6及び導体層3、4を流れる電流によって誘起される磁界を互いに相殺するように配置されている。

【0043】

さらにまた、貫通導体群Gが、一様な距離をもって互いに隣り合うように配置されている。

【0044】

そして、貫通導体群G内において、第1及び第2の貫通導体5、6が、実質的に正方形の各頂点に位置する分布状態をもって互いに隣り合うように配置されている。

【0045】

次に、本発明の積層コンデンサ10の製造方法について説明する。なお、図面において、各符号は焼成の前後で区別しないことにする。

【0046】

まず、誘電体層となるセラミックグリーンシート2に、第1及び第2導体層となる導体膜3、4を導電性ペーストの印刷・乾燥により形成する。このとき、第1及び第2非導体形成領域13、14も形成される。なお、誘電体層2として、他のペロブスカイト構造を持つセラミック材料や、有機強誘電体材料を用いても良い。

【0047】

次に、導体膜3、4が形成されたグリーンシート2を交互に所要枚数を積み重ね、積層体1が抽出される大型積層体を形成する。

【0048】

次に、レーザの照射や、マイクロドリル又はパンチングを用いた打ち抜き法などにより、大型積層体の主面に導体膜3、4、セラミックグリーンシート2を貫く貫通孔を形成する。

【0049】

次に、この貫通孔に導体層3、4に用いる導電性ペーストと同様の導電性ペーストを充填することにより、第1及び第2貫通導体となる導体部5、6が形成される。

【0050】

なお、誘電体層となるセラミックグリーンシート2に、マイクロドリル又はパンチングを用いた打ち抜き法などにより、あらかじめ貫通孔をあけておき、スクリーン印刷法により、セラミックグリーンシート2上に導体層3、4となる導体膜を印刷すると同時に、貫通孔に導電性ペーストを充填することにより、導体部5、6を形成後、積層するようにしても良い。

【0051】

次に、大型積層体を押し切り刃加工、ダイシング方式などにより切断し、未焼成状態の積層体1を得る。

【0052】

次に、この未焼成状態の積層体1は、脱バインダ処理後、焼成を行い、内部に第1及び第2導体層3、4、第1及び第2貫通導体5、6が形成されるとともに、一方主面に第1及び第2貫通導体5、6が露出した積層体1が得られる。

【0053】

このとき、積層体1の一方主面に露出した第1及び第2貫通導体5、6は、表面が酸化

10

20

30

40

50

されているため、表面研磨により、酸化被膜を除去する。

【0054】

次に、第1及び第2貫通導体5、6の露出部に、Niメッキ、Snメッキを形成する。

【0055】

次に、半田ペーストをスクリーン印刷する方法や、フラックスを塗布後半田ボールを搭載する方法により、第1及び第2接続端子7、8となる半田を形成した後、リフロー処理を施すことにより、第1及び第2接続端子7、8が形成される。

【0056】

このようにして、図1に示すような積層コンデンサ10が得られる。

【0057】

特に、複数の第1貫通導体5及び第2貫通導体6が一ヵ所に集中することができないため、誘電体の強度が維持・向上し、焼成時において、第1貫通導体5、第2貫通導体6でのクラックの発生を未然に防止できる。

【0058】

なお、本発明は以上の実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲で種々の変更・改良を加えることは何ら差し支えない。

【0059】

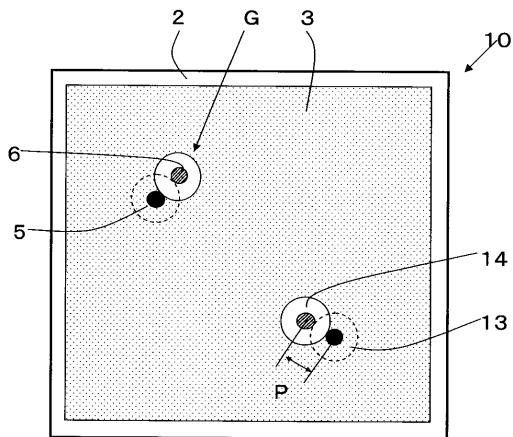

図2は、本発明の積層コンデンサ10の他の実施の形態の概略図である。図2では、貫通導体群Gは、一対の第1及び第2貫通導体5、6が近接するように並んで構成されている。しかも、貫通導体群Gを構成する第1及び第2貫通導体5、6の配列方向が、各貫通導体群Gで異なっているため、複数の貫通導体群Gにまたがるように応力が発生することによるコンデンサ全体のクラックを、より効果的に抑制できる。

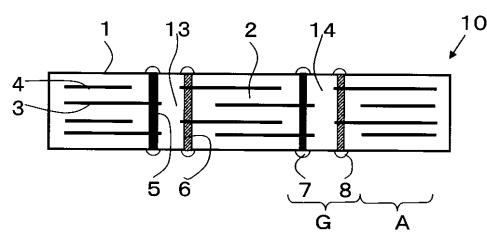

【0060】

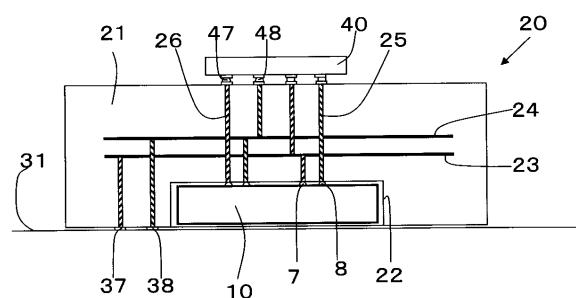

図3は、本発明の積層コンデンサ10のさらに他の実施の形態を示す断面図である。図のように、第1及び第2貫通導体5、6が積層体1の両主面に露出しても良い。このことにより、ICパッケージとIC素子との間や、ICパッケージ内部に、本積層コンデンサ10を介在させて実装することができる。

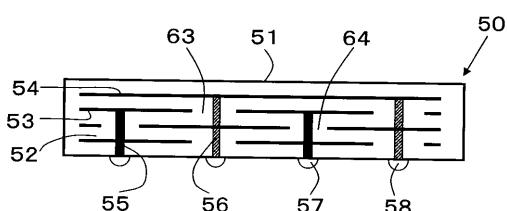

【0061】

図4は、本発明の積層コンデンサ10のさらに他の実施の形態を示す断面図である。図のように、絶縁基板11の表面に、第1導体層3、誘電体層2、第2導体層4、保護層12が順次被着形成されるとともに、誘電体層2の厚み方向に、第2導体層4とは非導体形成領域13によって隔てられ第1導体層3に接続される第1貫通導体5と、第1導体層3とは非導体形成領域14によって隔てられ第2導体層4に接続される第2貫通導体6とが形成され、且つ第1貫通導体5及び第2貫通導体6とが、誘電体層2の最表面に露出してなる。このように、本発明の積層コンデンサを薄膜コンデンサに適用することにより、微細加工が可能であるため、さらなる低ESL化を実現できる。

【0062】

また、第1及び第2貫通導体の半径r1、r2、第1及び第2非導体形成領域の半径m1、m2は夫々等しくても良く、異なっても良い。

【0063】

さらに、積層コンデンサ10が安定して実装されるために、積層体1の一方主面の接続端子7、8が形成されていない領域に、ダミーの端子を形成しても良い。

【0064】

また、第1及び第2貫通導体5、6の断面形状、または第1及び第2非導体形成領域13、14の形状は、略円形の他、橢円形、多角形など、任意の形状にすることができる。

【0065】

図5は、本発明の積層コンデンサ10をデカップリングコンデンサとして用いた、MPU20の構造例を示す断面図である。

【0066】

図に示すように、MPU20は、下面側にキャビティ22が設けられた多層構造の配線

10

20

30

40

50

基板 2 1 を備えている。配線基板 2 1 の上面には、MPU チップ 4 0 が表面実装されている。また、配線基板 2 1 のキャビティ 2 2 内には、デカップリングコンデンサとして機能する、本発明の積層コンデンサ 1 0 が収容されている。さらに、配線基板 2 1 は、マザーボード 3 1 上に表面実装されている。

【 0 0 6 7 】

配線基板 2 1 の内部には、電源側導体層 2 3 及びグランド側導体層 2 4 が形成されている。

【 0 0 6 8 】

電源側導体層 2 3 は、電源側貫通導体 2 5 を介して、積層コンデンサ 1 0 の第 1 接続端子 7 に電気的に接続されるとともに、MPU チップ 4 0 の特定の端子 4 7 に電気的に接続され、さらにマザーボード 3 1 の電源側導体ランド 3 7 に電気的に接続されている。 10

【 0 0 6 9 】

グランド側導体層 2 4 は、グランド側貫通導体 2 6 を介して、積層コンデンサ 1 0 の第 2 接続端子 8 に電気的に接続されるとともに、MPU チップ 4 0 の特定の端子 4 8 に電気的に接続され、さらにマザーボード 3 1 のグランド側導体ランド 3 8 に電気的に接続されている。 20

【 0 0 7 0 】

このように、本発明の積層コンデンサ 1 0 は、ESL が低いので、MPU 2 0 におけるデカップリングコンデンサに用いた場合も、高速動作に十分対応することができる。さらに、積層コンデンサ 1 0 を備えた配線基板にも適用できる。 20

【 0 0 7 1 】

また、本発明の積層コンデンサ 1 0 は、低 ESL 化が可能となることから、共振周波数 ( $f_0$ ) は高くなり、より高周波で使用できることになる。このことから、電子回路の高周波化に十分対応することができ、たとえば、高周波回路におけるバイパスコンデンサやデカップリングコンデンサとして有利に用いることができる。 30

【 0 0 7 2 】

本発明者らは、図1に示す本発明の積層コンデンサ 1 0 と、図 6 に示す従来の積層コンデンサ 5 0 を作成し、静電容量 C 及び等価直列インダクタンス L を測定した。ここで、積層コンデンサ 1 0 、 5 0 の両方とも、寸法は  $3.2\text{ mm} \times 3.2\text{ mm} \times 0.85\text{ mm}$  、積層数は 120 層、第 1 及び第 2 貫通導体 5 、 6 の数は両方合わせて 36 個、第 1 及び第 2 貫通導体 3 、 4 の半径は  $r_1 = r_2 = 0.07\text{ mm}$  、第 1 及び第 2 非導体形成領域 1 3 、 1 4 の半径は  $m_1 = m_2 = 0.17\text{ mm}$  とした。また、近接してなる第 1 及び第 2 貫通導体 3 、 4 の中心間の距離 P は、積層コンデンサ 1 0 が  $0.25\text{ mm}$  、積層コンデンサ 5 0 が  $0.40\text{ mm}$  とした。測定の結果、図5に示す従来の積層コンデンサ 5 0 は  $C = 7.8\text{ }\mu\text{F}$  、  $L = 20\text{ pH}$  となったのに対し、図1に示す本発明の積層コンデンサ 1 0 は  $C = 10\text{ }\mu\text{F}$  、  $L = 7\text{ pH}$  となった。 30

【 0 0 7 3 】

また、図1の積層コンデンサ 1 0 において、貫通導体群 G と第 1 及び第 2 導体層 5 、 6 の外周との最短距離 d を 0 にした場合、  $d = P$  にした場合に比べて ESL が約 15 % 増大した。 40

【 0 0 7 4 】

さらに、図1の積層コンデンサ 1 0 は、未焼成状態の積層体 1 のハンドリング、焼成時、IC パッケージへの実装時のいずれにおいても、クラックが発生しなかった。

【 0 0 7 5 】

これらの結果から、本発明の積層コンデンサ 1 0 は、少なくとも一対の第 1 及び第 2 貫通導体 5 、 6 とが近接してなる貫通導体群 G が、一様な距離をもって配置されているとともに、  $P = m_1 + m_2$  の関係にあり、且つ  $d = P$  の範囲にあるため、低 ESL 且つ高容量を実現でき、且つクラックの発生を抑制できることがわかった。

【 0 0 7 6 】

なお、上述の実施例の他に、貫通導体群 G が、一様な距離をもって互いに隣り合うよう

に配置された一例として、図7(a)、(b)に示すように配置することができる。

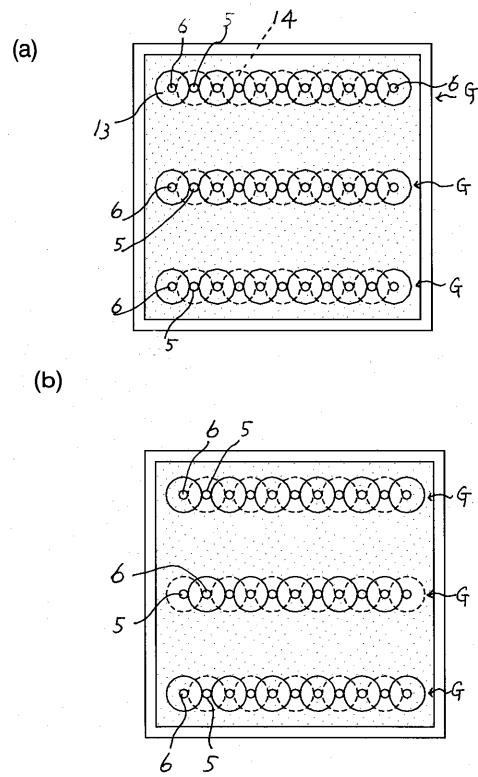

【0077】

すなわち、第1の貫通導体5と第2の貫通導体6とを直線的に配置し、貫通導体群Gとして、この直線的に配列された貫通導体群Gを一様な距離をもって、互いに平行となるように配置してもよい。ここで、図7(a)と図7(b)との違いは、図7(a)では、例えば、第2の貫通導体6が各列状に配列された貫通導体群Gで、最も左側、3番・・に配列されているのに対して、図7(b)では、第2の貫通導体6が図面の上から1番目と3番目の貫通導体群Gで、最も左側、3番・・に配列され、上から2番目の貫通導体群Gでは、第1の貫通導体5が、最も左側、3番・・に配列されている。

【0078】

本発明のコンデンサによれば、2つの第1貫通導体及び2つの第2貫通導体が格子状に配置されて格子の縦横の方向に隣接する第1貫通導体の第1非導体形成領域と第2貫通導体の第2非導体形成領域とが積層方向に重なり合った貫通導体群の複数が、互いに一様な距離をもって配置されているため、貫通導体群内のみに流れる電流は、流れる距離が短くなることから、電流によって誘起される磁束に起因する自己インダクタンス成分が低くなる。このため、コンデンサ全体の等価直列インダクタンス(ESL)を低くできる。また、ESLを低くするために、第1及び第2貫通導体の数を増加する必要がないため、コンデンサの高容量化を実現できる。さらに、貫通導体群間に、貫通導体の無い領域が存在するため、複数の貫通導体群にまたがるように応力が発生することを防止でき、コンデンサのクラックの発生を抑制できる。

【0079】

また、貫通導体群を構成し、且つ隣接しあう第1貫通導体と第2貫通導体との間に容量の発生する領域が存在しないため、第1貫通導体から他方、例えば第2貫通導体へ流れる電流は、ほとんど無くなる。このことにより、電流によって誘起される磁束に起因する自己インダクタンス成分が極めて低くなり、コンデンサ全体のESLをさらに低くすることができる。また、第1導体層と第2非導体形成領域、あるいは第2導体層と第1非導体形成領域が重なる部分の面積が減少するため、コンデンサのさらなる高容量化を実現できる。

【0080】

さらに、第1導体層及び第2導体層の周縁部と貫通導体群の間に、第1貫通導体と第2貫通導体との中心間の間隔P以上の幅で、第1貫通導体、第2貫通導体及び非導体形成領域の無い、静電容量領域が形成されているため、静電容量領域の第1導体層及び第2導体層に流れる電流の量が多くなり、このことによってもコンデンサ全体のESLをさらに効果的に低くすることができる。また、貫通導体群の周囲に静電容量が発生するため、加わる電界を大きくすることができ、このことによってもコンデンサの高容量化を実現できる。

【0081】

またさらに、貫通導体群が、貫通導体及び導体層を流れる電流によって誘起される磁界を互いに相殺するように配置されるため、コンデンサ全体のESLをさらに効果的に低くすることができる。

【0082】

さらにまた、貫通導体群が、一様な距離をもって互いに隣り合うように配置されるため、貫通導体群間で部分的にESLが高くなることがなく、コンデンサ全体のESLをさらに効果的に低くすることができる。

【0083】

そして、貫通導体群内において、第1及び第2の貫通導体が、実質的に正方形の各頂点に位置する分布状態をもって互いに隣り合うように配置されるため、貫通導体群内で部分的にESLが高くなることがなく、コンデンサ全体のESLをさらに効果的に低くすることができる。

【図面の簡単な説明】

10

20

30

40

50

## 【0084】

【図1】本発明のコンデンサを示す図であり、(a)は第1、第2の導体層の重なり状態を示す概略図、(b)は図1(a)のX-X線断面図である。

【図2】本発明のコンデンサの他の実施の形態を示す概略図である。

【図3】本発明のコンデンサのさらに他の実施の形態を示す断面図である。

【図4】本発明のコンデンサのさらに他の実施の形態を示す断面図である。

【図5】本発明のコンデンサをデカップリングコンデンサとして用いた、MPUの構造例を示す断面図である。

【図6】従来のコンデンサを示す図であり、(a)は第1、第2の導体層の重なり状態を示す概略図、(b)は図6(a)のX-X線断面図である。

【図7】(a)(b)本発明のコンデンサのさらに別の実施の形態を示す概略図である。

## 【符号の説明】

## 【0085】

|         |                  |    |

|---------|------------------|----|

| 1 0     | コンデンサ            |    |

| 1       | 積層体              |    |

| 2       | 誘電体層             |    |

| 3       | 第1の導体層(内部電極層)    |    |

| 4       | 第2の導体層(内部電極層)    |    |

| 5       | 第1の貫通導体(ビアホール導体) |    |

| 6       | 第2の貫通導体(ビアホール導体) | 20 |

| 1 3     | 第1の非導体形成領域       |    |

| 1 4     | 第2の非導体形成領域       |    |

| A       | 静電容量領域           |    |

| G       | 貫通導体群            |    |

| 2 0     | MPU              |    |

| 2 1     | 配線基板             |    |

| 2 2     | キャビティ            |    |

| 2 3     | 電源側導体層           |    |

| 2 4     | グランド側導体層         |    |

| 4 0     | MPUチップ           | 30 |

| 3 7、3 8 | MPUチップの端子        |    |

| 3 1     | マザーボード           |    |

【図1】

【図2】

(b)

【図3】

【図4】

【図5】

【図6】

(b)

【図7】

---

フロントページの続き

合議体

審判長 鈴木 匡明

審判官 小野田 誠

審判官 酒井 英夫

(56)参考文献 特開2001-189234 (JP, A)

特開平9-191184 (JP, A)

特開平8-330183 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01G4/00