(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-22708

(P2014-22708A)

(43) 公開日 平成26年2月3日(2014.2.3)

(51) Int.Cl.

**H01L 29/739 (2006.01)**

**H01L 29/78 (2006.01)**

**H01L 29/12 (2006.01)**

F 1

H01L 29/78 655D

H01L 29/78 652T

H01L 29/78 655B

H01L 29/78 655C

テーマコード (参考)

審査請求 未請求 請求項の数 5 書面 (全 28 頁)

(21) 出願番号

特願2012-171456 (P2012-171456)

(22) 出願日

平成24年7月17日 (2012.7.17)

(71) 出願人 509260466

菅原 良孝

茨城県日立市みかの原町2丁目19番10号

(72) 発明者 509260466

菅原 良孝

茨城県日立市みかの原町2丁目19番10号

(54) 【発明の名称】半導体装置とその動作方法

(57) 【要約】 (修正有)

【課題】逆導通IGBTのターンオフ時のスナップバック現象を抑制するとともに、スナップバック現象による半導体本体の損傷も抑制し、信頼性が高い高耐圧の半導体装置とその動作方法を提供する。

【解決手段】逆導通IGBTをワイドギャップ半導体で形成し、コレクタ短絡部103間の距離Wpを、Si半導体で形成した同耐圧・同一構成の逆導通IGBTの短絡部間距離Wp(Si)を上限とし、A×Wp(Si)を下限とする範囲に設定する。ここで、係数Aは、前記ワイドギャップ半導体のpn接合のビルトイン電圧Vbi(WB)とワイドギャップ半導体装置の特性オン抵抗Rons(WB)との積を、前記Si半導体装置のpn接合のビルトイン電圧Vbi(Si)とSi半導体装置の特性オン抵抗Rons(Si)との積で割算した値とする。

【選択図】図2

**【特許請求の範囲】**

**【請求項 1】**

第1導電型の第1半導体層と、

前記半導体層の裏面に設けられた第2導電型の第1半導体層と、前記第2導電型の第1半導体層を貫通する複数の第1導電型の第1半導体領域とを備え、

前記第1導電型の第1半導体層のおもて面には、選択的に設けられた複数の第2導電型の第1半導体領域と、

前記第2導電型の第1半導体領域の各々のおもて面に選択的に設けられた第1導電型の第2半導体領域と、

前記各々の第2導電型の第1半導体領域と前記第1導電型の第2半導体領域とに接する第1の主電極と、

前記各々の第2導電型の第1半導体領域の、前記各々の第1導電型の第2半導体領域と前記第1導電型の第1半導体層とに挟まれた部分の表面に、絶縁膜を介して設けられた制御電極と、

前記第2導電型の第1半導体層と前記複数の第1導電型の第1半導体領域との裏面に接する第2の主電極とを備えた半導体装置において、

各半導体層と各半導体領域がワイドギャップ半導体から構成されており

前記複数の第1導電型の第1半導体領域間の距離 $W_p$ ( $W_B$ )を、

$S_i$ 半導体で構成した同耐圧でほぼ同一構成の前記半導体装置の前記距離 $W_p$ ( $S_i$ )を上限とし、

前記ワイドギャップ半導体の $p_n$ 接合のビルトイン電圧 $V_{bi}$ ( $W_B$ )とワイドギャップ半導体装置の特性オン抵抗 $R_{onS}$ ( $W_B$ )との積を、前記 $S_i$ 半導体装置の $p_n$ 接合のビルトイン電圧 $V_{bi}$ ( $S_i$ )と $S_i$ 半導体装置の特性オン抵抗 $R_{onS}$ ( $S_i$ )との積で割算した値に前記短絡部間距離 $W_p$ ( $S_i$ )を乗じた値を下限とする範囲より選択したことを特徴とする半導体装置。

**【請求項 2】**

請求項1の半導体装置において、

前記第1導電型の第1半導体層と、前記第2導電型の第1半導体層および前記複数の第1導電型の第1半導体領域(短絡部)との間に第1導電型の第2半導体層を設けたことを特徴とする半導体装置。

**【請求項 3】**

請求項1および2の半導体装置において、前記複数の第1導電型の第1半導体領域間の距離 $W_p$ ( $W_B$ )のうち、少なくとも一つの距離 $W_p$ ( $W_B$ )を前記範囲の上限以下で下限よりも十分大きな値とし、それ以外の $W_p$ ( $W_B$ )を前記範囲の下限に近い値としたことを特徴とする半導体装置。

**【請求項 4】**

請求項1～3の半導体装置において、セル内に複数の前記第1導電型の第1半導体領域を有し、その幅 $W_n$ ( $W_B$ )と前記第1導電型の第1半導体領域間の距離 $W_p$ ( $W_B$ )との比率 $W_n$ ( $W_B$ ) /  $W_p$ ( $W_B$ )を0.2～5.0にしたことを特徴とする半導体装置。

**【請求項 5】**

少なくとも初動時には、前記第1の主電極と前記第2の主電極間に順方向電圧を印加し且つ前記制御電極にも低い電圧を印加して順方向バイアス状態し、前記複数の第1導電型の第1半導体領域を介して多数キャリアによる順方向電流を流し、この電流により半導体装置を40以上に昇温させた後に、前記第2導電型の第1半導体層から前記第1導電型の第1半導体層に少数キャリアが注入されるように前記第1の主電極と前記第2の主電極間の電圧および前記制御電極の電圧、もしくはいづれか一方の電圧をより高い電圧に制御することを特徴とする請求項1～4の半導体装置の動作方法。

**【発明の詳細な説明】**

**【技術分野】**

10

20

30

40

50

## 【0001】

本発明は、半導体装置に係わり、特に高性能の逆導通IGBTとその動作方法に関する。

## 【背景技術】

## 【0002】

現在、高耐圧の大電力および中電力用途ではもっぱらシリコン(Si)を材料としたSi-IGBTが主要半導体装置として種々の応用分野で多用されており、6kV級まで製品が供給されている。近年これらのSi-IGBTのターンオフ速度を短くし損失を低減するために様々な工夫がこらされている。その代表的な例として、図5に示す従来例1や図6に示す従来例2のSi逆導通IGBTが開発され、各々非特許文献1や2に開示されている。10

## 【0003】

従来例1の短絡コレクタSi-IGBTではn<sup>-</sup>ドリフト層がpコレクタ層に設けたn<sup>+</sup>短絡部によりコレクタ電極に短絡されており、ターンオフ時にn<sup>-</sup>ドリフト層内に残存するキャリアをこのn<sup>+</sup>短絡部を介して排除することによりターンオフ時間を短くし損失の低減を図っている。

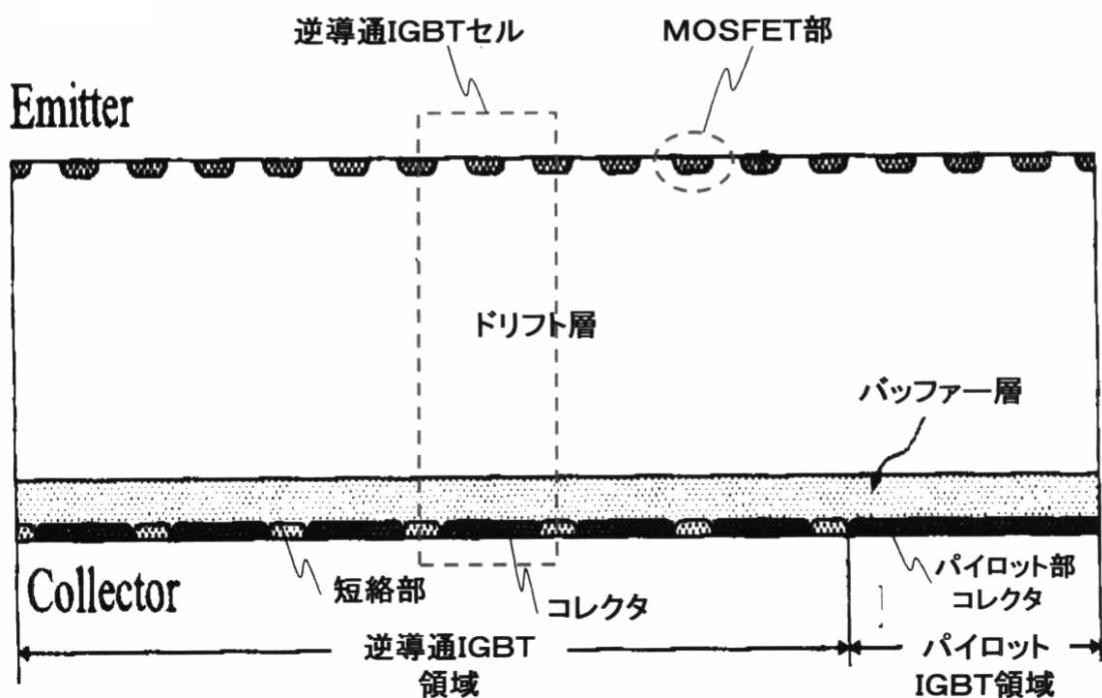

従来例2のSi逆導通IGBTは、逆導通Si-IGBT領域とパイロットIGBT領域とから構成されている。Si逆導通IGBT領域には従来例1と同様にnドリフト層がpコレクタ層に設けたn<sup>+</sup>短絡部によりコレクタ電極に短絡されており、ターンオフ時にnドリフト層内に残存するキャリアをこのn<sup>+</sup>短絡部を介して排除することによりターンオフ時間を短くし損失の低減を図っている。また、パイロットIGBT領域のコレクタの幅は逆導通IGBT領域のコレクタの幅よりも大幅に大きくなり、パイロットIGBT領域が逆導通IGBT領域に先駆けてオンするようにしている。20

なお、これらの開示されているIGBTはnドリフト層がn<sup>+</sup>短絡部によりコレクタ電極に短絡されているので、逆電圧に対する阻止能力がないために、近年逆導通IGBTと総称されている。それ故、以下ではいづれも逆導通IGBTと呼ぶ。

## 【先行技術文献】

## 【特許文献】

## 【非特許文献】

## 【0004】

【非特許文献1】ハジメ・アキヤマ(Hajime AKIYAMA)、他5名、イヘクト オブ ショーティコレクタ オン キャラクタリストイクス オブ IGBTs (EFFECTS OF SHORTED COLLECTOR ON CHARACTERISTICS OF IGBTs)、プロシードィングス オブ ザ セカンド インターナショナル シンポジューム オン パワー セミコンダクタ デバイシズ アンド ICs (Proceedings of The 2nd International Symposium on Power Semiconductor Devices & ICs), 1990年4月、p.131-13630

【非特許文献2】リウタウラス ストラスター(Litauras Storasta), 他2名、ア コンパリソング オブ チャージ ダイナミックス イン ザ レヴァースコンダクティング RCIGBT アンド バイモード インシュレイテド ゲイトトランジスタ BiGT) (A Comparison of charge dynamics in the Reverse-Conducting RCIGBT and Bi-mode Insulated Gate Transistor BiGT)、プロシードィングス オブ ザ トエンティセカンド インターナショナル シンポジューム オン パワー セミコンダクタ デバイシズ アンド ICs (Proceedings of The 22nd International Symposium on Power Semiconductor Devices & ICs), 2010年6月、p.391-3944050

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

ところで、開示されている従来例1および2のSi逆導通IGBTの出力特性、すなわちコレクターエミッタ間電圧（以下、V<sub>ce</sub>と記す）とコレクターエミッタ間電流（以下、I<sub>ce</sub>と記す）の間のI<sub>ce</sub>-V<sub>ce</sub>特性には、オン直前のコレクターエミッタ間電圧がオン直後のコレクターエミッタ間電圧（以下、V<sub>on0</sub>と記す）よりも大きいというスナップバック現象が発生する。オン直前のコレクターエミッタ間電圧を、従来例1ではknee point voltageと呼び、従来例2ではスナップバック前ピーク電圧と呼んでいるが、以下ではスナップバック電圧と呼び、V<sub>sb</sub>と記述する。また、このV<sub>sb</sub>におけるコレクターエミッタ間電流をスナップバック電流と呼びI<sub>sb</sub>と記述する。

10

**【0006】**

ところで、これらの逆導通IGBTはオン直前から直後に推移するまでの時間すなわちターンオン時間が短いので、スナップバック現象が存在するとターンオン時に急峻な電圧変化（以下dV/dtと表記）や急峻な電流変化（以下dI/dtと表記）を生じる。この結果、回路内に存在する寄生容量により急峻な跳ね上がり電圧（C·dv/dt）が、また寄生リアクトルにより急峻な跳ね上がり電流（L·dI/dt）が生じ、これに起因して大きな過度現象が誘発される。このため、この逆導通IGBTを用いた回路に大きな擾乱を招いてしまい誤動作を起したり、場合によっては素子や回路の破壊に至る。これは極めて深刻な第1の課題である。

20

**【0007】**

また、従来例2のSi逆導通IGBTでは、多数の逆導通IGBTセルから構成される逆導通IGBT領域に隣接してパイロットIGBT領域を設けている。パイロットIGBT領域のpコレクタ幅は逆導通IGBT領域のIGBTセルのpコレクタ幅よりも大幅に大きくすることによりpコレクタ上のバッファー層の横方向抵抗を大きくしており、従つてまず小さいI<sub>ce</sub>でパイロットIGBT領域をオンさせるようにしている。これにより、パイロットIGBT領域のスナップバック現象を抑制している。この結果、まずスナップバック現象が抑制されたパイロットIGBT領域が小さなI<sub>ce</sub>でオンしてより大きなオン電流が流れ、このオン電流が拡がって最隣接の逆導通IGBTセルに流れ込む。最隣接の逆導通IGBTセルのpコレクタは幅が小さいためpコレクタ上のバッファー層の横方向抵抗が小さいが、パイロットIGBTのオン電流の一部が大きな拡がり電流となって流れ込むために、最隣接の逆導通IGBTセルのpコレクタ接合が容易にビルトイン電圧に達してオンする。この結果、オン電流が更に増大し、この最近接の逆導通IGBTセルに隣接する逆導通IGBTセルが同様にオンする。このような動作を繰り返して、パイロットIGBT領域に近接する逆導通IGBTセルから順次オンしてゆき、逆導通Si-IGBT全体がオンするに至る。

30

**【0008】**

しかし、この引例2の場合は全体のIGBTチップ面積に占めるパイロットIGBT領域の面積がかなり大きくなってしまう。例えば、引例2の場合、データから読み取ると、逆導通IGBTセルのpコレクタ幅が180μmであるのに対し、パイロットIGBTのpコレクタ幅を約4倍以上の720μm以上にすることにより、V<sub>sb</sub>をビルトイン電圧である0.7V以下にしている。この結果、スナップバック現象は解消されるが逆導通IGBT領域の面積が少なくなるので、ターンオフ時に残存するキャリアを排除するという本来の逆導通IGBTの機能が大幅に損ねられてしまう。これは歩留まりなどの経済性の点から素子のチップサイズが通常12mm×12mm以下程度に設定されている現状では大きな問題であり、解決すべき第2の課題である。

40

**【0009】**

高耐圧の逆導通IGBTの場合は、耐圧が高くなるほどチップ表面の電界を緩和するのにより大きな占有面積が必要となるため活性面積がより少なくなるので、この第2の課題はより深刻になる。

50

## 【0010】

またスナップバック現象に基づく回路動作の擾乱を介して逆導通IGBTが誤動作や部分破壊を起こすといった間接的な半導体装置の信頼性の問題は、上記のように明らかにされている。しかし、スナップバック現象により直接的に半導体本体に及ぼされる損傷に関連する信頼性の問題は明らかにされておらず、引例でも言及されていない。これは重要な第3の課題である。

## 【0011】

本発明は、前記の従来技術の課題を解消し、V<sub>SB</sub>やI<sub>SB</sub>を小さくできスナップバック現象を抑制できる高性能逆導通IGBTを提供することを目的にする。また、この発明は、パイロットIGBT領域を設けた逆導通IGBTにおいて、パイロットIGBT領域の専有面積を小さくでき、且つターンオフ時の残存キャリアの排除機能があまり抑制されない高性能逆導通IGBTを提供することを目的にする。更に、この発明はスナップバック現象が直接的な原因となって生じる半導体本体の劣化に起因して信頼性が損ねられるのを抑制し、高い信頼性を達成できる高性能逆導通IGBTと逆導通IGBTの動作方法を提供することを目的にする。

10

## 【課題を解決するための手段】

以下では、理解を容易にするために、各半導体層や半導体領域が機能的にどの層に相当するかを括弧内に付記して説明する。

## 【0012】

上記した課題を解決し本発明の目的を達成するため、この発明にかかる半導体装置は、第1導電型の第1半導体層(ドリフト層)と、

20

前記半導体層(ドリフト層)の裏面に設けられた第2導電型の第1半導体層(コレクタ層)と、前記第2導電型の第1半導体層(コレクタ層)を貫通する複数の第1導電型の第1半導体領域(短絡部)とを備え、

前記第1導電型の第1半導体層(ドリフト層)のおもて面には、選択的に設けられた複数の第2導電型の第1半導体領域(pボディ層)と、

前記第2導電型の第1半導体領域(pボディ層)の各々のおもて面に選択的に設けられた第1導電型の第2半導体領域(エミッタ層)と、

30

前記各々の第2導電型の第1半導体領域(pボディ層)と前記第1導電型の第2半導体領域(エミッタ層)とに接する第1の主電極(エミッタ電極)と、

前記各々の第2導電型の第1半導体領域(pボディ層)の、前記各々の第1導電型の第2半導体領域(エミッタ層)と前記第1導電型の第1半導体層(ドリフト層)とに挟まれた部分の表面に、絶縁膜を介して設けられた制御電極と、

前記第2導電型の第1半導体層(コレクタ層)と前記複数の第1導電型の第1半導体領域(短絡部)との裏面に接する第2の主電極(コレクタ電極)とを備えた半導体装置において、

各半導体層と各半導体領域がワイドギャップ半導体から構成されており

40

前記複数の第1導電型の第1半導体領域(短絡部)間の距離W<sub>P</sub>(W<sub>B</sub>)を、S<sub>i</sub>半導体で構成した同耐圧でほぼ同一構成の前記半導体装置の前記距離W<sub>P</sub>(S<sub>i</sub>)を上限とし、

前記ワイドギャップ半導体のp-n接合のビルトイン電圧V<sub>bi</sub>(W<sub>B</sub>)とワイドギャップ半導体装置の特性オン抵抗R<sub>onS</sub>(W<sub>B</sub>)との積を、前記S<sub>i</sub>半導体装置のp-n接合のビルトイン電圧V<sub>bi</sub>(S<sub>i</sub>)とS<sub>i</sub>半導体装置の特性オン抵抗R<sub>onS</sub>(S<sub>i</sub>)との積で割算した値に前記短絡部間距離W<sub>P</sub>(S<sub>i</sub>)を乗じた値を下限とする範囲より選択したことを特徴とする。

## 【0013】

また、この発明にかかる半導体装置は、上述した発明において、前記第1導電型の第1半導体層(ドリフト層)と、前記第2導電型の第1半導体層(コレクタ層)および前記複数の第1導電型の第1半導体領域(短絡部)との間に第1導電型の第2半導体層(バッファー層)を設けたことを特徴とする。

50

## 【0014】

また、この発明にかかる半導体装置は、上述した発明において、

前記複数の第1導電型の第1半導体領域(短絡部)間の距離W<sub>p</sub>(WB)のうち、少なくとも一つの距離W<sub>p</sub>(WB)を前記範囲の上限以下で下限よりも十分大きな値とし、それ以外のW<sub>p</sub>(WB)を前記範囲の下限に近い値としたことを特徴とする。

## 【0015】

また、この発明にかかる半導体装置は、上述した発明において、

セル内に1個以上の前記第1導電型の第1半導体領域(短絡部)を有し、その幅W<sub>n</sub>(WB)と前記第1導電型の第1半導体領域(短絡部)間の距離W<sub>p</sub>(WB)との比率W<sub>n</sub>(WB)/W<sub>p</sub>(WB)を0.3~5.0にしたことを特徴とする。

10

## 【0016】

また、この発明にかかる半導体装置の動作方法は、上述した発明において前記第1の主電極(エミッタ電極)と前記第2の主電極(コレクタ電極)間に順方向電圧を印加し且つ前記制御電極にも低い電圧を印加して順方向バイアス状態し、前記複数の第1導電型の第1半導体領域(短絡部)を介して多数キャリアによる順方向電流を流し、この電流により半導体装置を40以上に昇温させた後に、前記第2導電型の第1半導体層(コレクタ層)から前記第1導電型の第1半導体層(ドリフト層)に少数キャリアが注入されるように前記第1の主電極(エミッタ電極)と前記第2の主電極(コレクタ電極)間の電圧および前記制御電極の電圧、もしくはいづれか一方の電圧をより高い電圧に制御することを特徴とする。

20

## 【0017】

この発明によれば、各半導体層と各半導体領域をワイドギャップ半導体で構成し、前記短絡部間の距離W<sub>p</sub>(WB)を(1)式に示すように、その上限をS<sub>i</sub>半導体で構成した同耐圧で同一構成の半導体装置の短絡部間距離W<sub>p</sub>(Si)とし、その下限を新しく発見した下限、すなわちA×W<sub>p</sub>(Si)とするようにし、これらの上限と下限の間の値になるように設定する。

$$W_p(Si) > W_p(WB) \geq AW_p(Si) \quad (1)$$

## 【0018】

30

ここで新しく発見した係数Aは(2)式に示すが、前記ワイドギャップ半導体のp-n接合のビルトイン電圧V<sub>bi</sub>(WB)とワイドギャップ半導体装置の特性オン抵抗R<sub>onS</sub>(WB)との積を、前記S<sub>i</sub>半導体装置のp-n接合のビルトイン電圧とS<sub>i</sub>半導体装置の特性オン抵抗との積で割算したものである。

$$A = \frac{V_{bi}(WB) \cdot R_{onS}(WB)}{V_{bi}(Si) \cdot R_{onS}(Si)} \quad (2)$$

この係数Aは1よりも大幅に小さい値である。

## 【0019】

40

なお、ここで「S<sub>i</sub>半導体で構成した同耐圧で同一構成の半導体装置」とは、「ワイドギャップ半導体逆導通IGBTと断面形状は同じであり且つn<sup>+</sup>短絡部の不純物濃度と幅も同じであるが、同耐圧を実現するためにS<sub>i</sub>材料特有の物性を考慮して、必要な各半導体層や各半導体領域の不純物濃度や厚さおよび幅を採用しているS<sub>i</sub>逆導通IGBT構造の半導体装置」を意味する。

## 【0020】

このように逆導通ワイドギャップ半導体IGBTの短絡部間の距離W<sub>p</sub>(WB)を設定することにより、引例と同耐圧で同一構成のS<sub>i</sub>逆導通IGBTに比べてW<sub>p</sub>を小さくしているにもかかわらずスナップバック現象を抑制でき、且つ高速化とスイッチング損失の大幅低減による高性能化も達成でき、第1の課題を解決できるものである。

50

## 【0021】

以下に、その理由を新しく発見した係数Aの導出とあわせて、図1を参照しながら説明する。

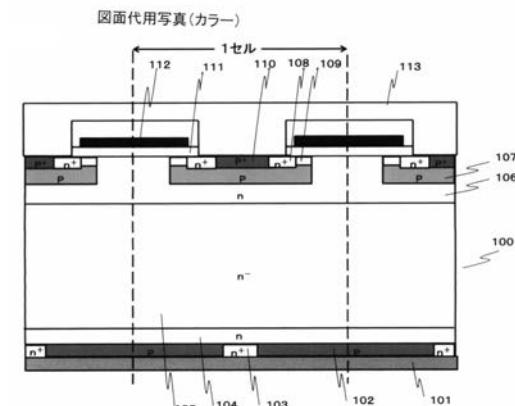

図1はn型Si逆導通IGBTの断面図の一部を示す。以下のように構成されている。

逆導通IGBTのコレクタ電極1に接する裏面には、pコレクタ領域2とn+短絡部3とが交互に設けられ、これらの領域2と3のおもて面には、n(第2導電型)バッファーレイ4が設けられている。nバッファーレイ4の表面には、n-ドリフト層(第1半導体層)5が、またその表面には、n型半導体層(電流密度増大層:CEL、第2半導体層)6を設けている。nCEL6の表面層には、pボディ領域(第1半導体領域)7が選択的に複数設けられ、その表面層には、n+エミッタ領域(第2半導体領域)8およびp-低濃度チャネル領域9やp+コンタクト領域10が選択的に設けられている。p-低濃度チャネル領域9の表面には、ゲート絶縁膜11を介してゲート電極(制御電極)12が設けられている。エミッタ電極(入力電極)13は、n+エミッタ領域8に接するとともにp+コンタクト層10を介してpボディ領域7にも接する。また、エミッタ電極13はゲート電極12から絶縁されている。

10

## 【0022】

まず、この逆導通IGBTを用いてスナップバック現象の発生メカニズムを説明する。

逆導通Si-IGBTのMOSゲート電極12にしきい値以上のゲート電圧を印加しコレクタ電極1とエミッタ電極13の間の順方向電圧Vceを印加し上昇してゆくと、まずMOSFET部が動作し、エミッタ電極13からn+エミッタ領域8、p-低濃度チャネル領域9、nCEL層6、n-ドリフト層5、nバッファーレイ4、n+短絡部3を順次介してコレクタ電極に電子電流が流れる。図中にはこの電子電流の流路を図式的にa、b、cの点線で示してある。この電流の一部cはコレクタ接合上のバッファーレイ4を横方向に流れn+短絡部3を介してコレクタ電極1に流れるが、この横方向の電子電流によりpコレクタ接合中央部14とコレクタ電極1の間に電位差を生じ、この電位差がコレクタ接合のビルトイン電圧Vbi(Si)の場合は約0.7Vを超えるとpコレクタ2からnバッファーレイ4ついでnドリフト層5に正孔の注入が生じ実線の矢印で示した正孔電流dが流れ、IGBT部がオンする。この際、pコレクタ層2の幅が小さい場合は横方向抵抗が小さいので、横方向電流による電位差をビルトイン電圧Vbi以上にするためには大きな電流が必要となり、この結果n-ドリフト層での電圧降下とMOSFET部での電圧降下が大きくなりVsbが大きくなってしまう。しかし、一旦IGBT部がオンするとpコレクタ2から注入された正孔によりn-ドリフト層5に伝導度変調が生じn-ドリフト層の内部抵抗が激減するので、オン後のVceは大幅に低くなる。このためスナップバック現象が生じてしまうのである。

20

20

## 【0023】

次に新しく発見した係数Aをどのようにして導き出したのか説明する。

まず、上記のスナップバック現象の発生のメカニズムの考察から、Si逆導通IGBTのコレクタから正孔の注入が生じる時のVbi(Si)は下式2項目のように表せ、4項目のように変換できる。

30

30

$$V_{bi}(Si) = \frac{1}{2} I_{sb}(Si) R_b(Si) = \frac{1}{4} j_{sb}(Si) \cdot \rho_b(Si) \cdot W_p(Si)$$

40

ここで、Rb(Si)とrb(Si)は各々Si逆導通IGBTのバッファーレイ層の抵抗と抵抗率を、jsb(Si)はスナップバック電流密度を示す。

これよりWp(Si)は近似的に(2)式で示すことができる。

$$\therefore W_p(Si) = \frac{4 V_{bi}(Si)}{I_{sb}(Si) \rho_b(Si)} \quad (3)$$

同様に、同じ構成のワイドギャップ半導体逆導通IGBTにおいてコレクタからの正孔の注入が生じる条件は

50

$$W_p(WB) \geq \frac{4 V_{bi}(WB)}{J_{sb}(WB)\rho_b(WB)} \quad (4)$$

ここで、 $\rho_b(WB)$  はワイドギャップ半導体逆導通 IGBT のバッファー層の抵抗率を、 $J_{sb}(WB)$  はスナップバック電流密度を示す。

#### 【0024】

ところで、高耐圧 IGBT で定状オン損失とターンオフ損失をバランスよく低減し適正化するには、コレクタからの正孔の適正な注入を行う必要がある。この適正な正孔注入を行うための n バッファー層 4 の  $\rho_b$  は半導体材料にあまり依存しないでほぼ一義的に定めることができるので、ほぼ  $\rho_b(Si) = \rho_b(WB)$  となる。従って、(3) と (4) 式から (5) 式を導くことができる。

$$W_p(WB) \geq \frac{V_{bi}(WB) \cdot J_{sb}(Si)}{V_{bi}(Si) \cdot J_{sb}(WB)} W_p(Si) \quad (5)$$

#### 【0025】

ところで、高耐圧 IGBT の場合はオンする前はドレイン層が伝導度変調されていないので、MOSFET 部のチャネル抵抗での電圧ドロップ  $V_{ch}$  やコレクタのビイルトイン電圧  $V_{bi}$  に比べてドレイン層の電圧ドロップ  $V_{drift}$  がはるかに大きい。従って、

$$V_{ce} = V_{ch} + V_{drift} + V_{bi} = I_{ce} R_{on,drift}$$

逆導通 IGBT のオン直前の  $V_{ce}$  が  $V_{sb}$  であり、 $I_{ce}$  が  $I_{sb}$  であるので、

$$V_{sb} = I_{sb} R_{on,drift} = J_{sb} R_{on} S_{drift} \quad (6)$$

(5) 式に (6) 式より求めた  $J_{sb}$  を代入すると、

$$W_p(WB) \geq \frac{V_{bi}(WB) \cdot R_{on} S(WB) \cdot V_{sb}(Si)}{V_{bi}(Si) \cdot R_{on} S(Si) \cdot V_{sb}(WB)} W_p(Si) \quad (30)$$

従って、同耐圧のワイドギャップ半導体逆導通 IGBT と Si 逆導通 IGBT とで  $V_{sb}$  を同じにするための短絡部間距離  $W_p(WB)$  と  $W_p(Si)$  との間の関係は、 $V_{sb}(WB) = V_{sb}(Si)$  とすることにより (7) 式となる。

$$W_p(WB) \geq \frac{V_{bi}(WB) \cdot R_{on} S(WB)}{V_{bi}(Si) \cdot R_{on} S(Si)} W_p(Si) \quad (7)$$

このようにして、(2) 式の係数 A を導くことができる。

#### 【0026】

次に  $W_p(WB)$  を (1) 式に示すように設定することにより第 1 の課題を解決できる理由を説明する。

(7) 式より、Si 逆導通 IGBT に比べてワイドギャップ半導体逆導通 IGBT は短絡部間距離  $W_p(WB)$  を大幅に低減できることが判る。例えば、ワイドギャップ半導体の一種である炭化ケイ素（以下、SiC と記す）半導体で構成した SiC 逆導通 IGBT の場合は、 $R_{on} S(SiC)$  が  $R_{on} S(Si)$  の約 1 / 1000、 $V_{bi}(SiC)$  が  $V_{bi}(Si)$  の約 4 倍なので、(7) 式より  $W_p(SiC)$  が  $W_p(Si)$  の約 1 / 250 となる。従って、 $W_p(SiC)$  を  $W_p(Si)$  の約 1 / 250 まで大幅に低減しても、ほぼ同じ  $V_{sb}$  にできる。典型的な高耐圧 Si 逆導通 IGBT のケースについて試算してみると、 $W_p(Si)$  は (3) 式から 175 μm と算出でき、従って SiC 逆導通

10

20

30

40

50

I G B T の V<sub>s</sub> b を同耐圧の S i 逆導通 I G B T よりも抑制できる範囲は(1)式から、次のようになる。

$$175 \mu m > W_p(SiC) > 0.7 \mu m$$

この結果、同耐圧で同じチップサイズの場合、SiC逆導通I G B TのV<sub>s</sub> bをSi逆導通I G B TのV<sub>s</sub> bと同じにする時、W<sub>p</sub>(SiC)を175 μmまで大幅に増大できる余地が生じることになる。従って、W<sub>p</sub>(SiC)をW<sub>p</sub>(Si)以上にならない範囲で大幅に増大してI<sub>s</sub> bを小さくすることによりV<sub>s</sub> bを大幅に小さくできる。これはスナップバック現象を大幅に抑制できることを意味するものである。

#### 【0027】

また、同耐圧で同じチップサイズの場合、W<sub>p</sub>(WB)を上記の範囲内でW<sub>p</sub>(Si)よりも小さく設定することにより上記のようにスナップバック現象を抑制する一方、その小さくした分の一部で短絡領域のみの面積を増やしたり、セル数を増やしたりすることができ、いづれの場合もn<sup>+</sup>短絡部のトータル面積を大幅に増加できる。この結果、逆導通I G B Tのターンオフ時の残存キャリアの排除機能を大幅に増大できるので、ターンオフ時間を低減させ逆導通I G B Tを高速化することができるとともにスイッチング損失も低減でき、ワイドギャップ半導体逆導通I G B Tをより高性能化できる。

#### 【0028】

このように、スナップバック現象を大幅に抑制でき且つ逆導通I G B Tをより高性能化できるので、第1の課題を解決できる。

なお当然ながら、ワイドギャップ半導体で構成していることに起因して同耐圧のままで損失を低減できるという公知の効果も享受できるものである。

#### 【0029】

またこの発明によれば、上記構成により、前記複数の第1導電型の第1半導体領域(短絡部)間の距離W<sub>p</sub>のうち、少なくとも一つの距離W<sub>p</sub>を上限に近い値、すなわち前記範囲の上限以下で下限の数倍以上のかなり大きな値とし、それ以外のW<sub>p</sub>を前記範囲の下限に近い値としている。この短絡部間距離が上限に近い部分はパイロットI G B T部として十分機能させることができる。従って、Si逆導通I G B Tに比べてワイドギャップ半導体逆導通I G B TはパイロットI G B T部の専有面積をはるかに小さく抑えることができる。このため、同耐圧で同じチップサイズの場合、パイロットI G B T部以外の逆導通I G B T領域の面積を増やすことができ、その結果パイロットI G B T部を導入してスナップバック現象を抑制したにもかかわらず、ターンオフ時に残存するキャリアを排除するという逆導通I G B T本来の機能の低下を防止でき、逆に増大も可能であり第2の課題を解決できる。これは歩留まりなどの経済性の点からワイドギャップ半導体素子のチップサイズが10mm×10mm以下、一般的には5mm×5mm程度以下に制約されている現状では、逆導通I G B Tの本来の機能を発揮させる上で極めて効果が大きいものである。

#### 【0030】

当然ながら、同構造のSi逆導通I G B TのパイロットI G B T部のW<sub>p</sub>を超えない範囲内で、本発明になる逆導通I G B TのパイロットI G B T部のW<sub>p</sub>を大きくした場合は更にスナップバック現象を抑制できる。

#### 【0031】

また、この発明によれば、第1導電型の第1半導体領域(短絡部)の幅W<sub>n</sub>と前記第1導電型の第1半導体領域(短絡部)間の距離W<sub>p</sub>の比率を特定の範囲に限定にしており、これによりスナップバック現象が直接的な原因となって生じる半導体本体の劣化を抑制し、高性能逆導通I G B Tの高い信頼性を実現でき、第3の課題を達成できる。

#### 【0032】

一般に、ワイドギャップ半導体材料にはSiよりも各種の欠陥が多量に発生する。これらの欠陥のうちの積層欠陥は、注入された少数キャリアが結晶の格子点に衝突すると衝突エネルギーで格子点の原子が動かされるので積層欠陥が拡大してしまうというワイドギャップ半導体特有の性質がある。この積層欠陥は少数キャリアをトラップして再結合させ通電にあまり寄与することなく消滅させてしまうので、積層欠陥の拡大はI G B T半導体装

10

20

30

40

50

置の内部抵抗の増大を招く。従って、IGBTのようなバイポーラタイプのワイドギャップ半導体装置の場合は、装置を稼働し通電している間に注入される少数キャリアにより積層欠陥が拡大し内部抵抗が増大してゆくので、オン電圧増大すなわちオン電圧劣化をもたらし信頼性が大きく損ねられてしまう。しかし、このワイドギャップ半導体の積層欠陥が少数キャリアをトラップして再結合させ消滅させてしまうという現象は、温度を約40以上に上げると徐々に抑制され、200以上ではほぼ完全に消失することが発明者らにより見出されており、Silicon Carbide and Related Materials 2007の論文集(K.Nakayama他7名、Behavior of Stacking Faults in TEDREC Phenomena for 4.5kV SiC GT、Silicon Carbide and Related Materials 2007、2007年10月、p.1175-1178)に開示されている。10

以下では、この種のオン電圧増大を、オン電流増大に伴うオン電圧の増大と区別するためにオン電圧劣化と記述する。

#### 【0033】

ワイドギャップ半導体逆導通IGBTにスナップバック現象が存在すると、オンする直前のVs<sub>b</sub>ではコレクタから少数キャリアの注入を生じるのに必要な電圧降下すなわちV<sub>b*i*</sub>を実現するために比較的大きなI<sub>s*b*</sub>を流す必要がある。オンする直前のVs<sub>b</sub>まではもっぱら多数キャリアによるI<sub>s*b*</sub>が流れしており積層欠陥を拡大しないが、一旦オンするとこのI<sub>s*b*</sub>に対応する多量の少数キャリア電流がコレクタから一挙にバッファー層やドリフト層に流れ込む。これによりワイドギャップ半導体逆導通IGBTに存在する積層欠陥が一挙に拡大してしまい、オン電圧劣化の急速な進展を招き、半導体本体が劣化しついには損傷や破壊に至ってしまう。このスナップバック現象が存在するワイドギャップ半導体逆導通IGBTがオンする際のオン電圧の急速な劣化を、以後急速オン電圧劣化と記載する。20

#### 【0034】

しかし、この発明によれば、n<sup>+</sup>短絡部の幅W<sub>n</sub>を増大し n<sup>+</sup>短絡部のトータル面積を増大することにより、上記のスナップバック現象が直接的な原因となって生じる半導体本体が劣化するという急速オン電圧劣化を抑制でき高い信頼性を実現できる。

すなわち、スナップバック現象が存在する逆導通IGBTがオンする前にn<sup>+</sup>短絡部を介してI<sub>s*b*</sub>が流れるが、この電流は多数キャリ電流であり積層欠陥の拡大を招かない。そこで、n<sup>+</sup>短絡部の幅W<sub>n</sub>を増大し n<sup>+</sup>短絡部の面積を増大することにより積極的に多数キャリアで構成されるI<sub>s*b*</sub>の増大を図り、これにより逆導通IGBTの素子温度を、積層欠陥が少数キャリアをトラップして再結合させ消滅させてしまう現象が抑制される温度まで、逆導通IGBTがオンする前に上昇させ、オン時点での急速オン電圧劣化を抑制することができる。30

#### 【0035】

同耐圧で同じチップサイズの場合、セルの第1導電型の第1半導体領域(n<sup>+</sup>短絡部)の幅W<sub>n</sub>の増大によるn<sup>+</sup>短絡部のトータル面積を増大は、セルの前記第1導電型の第1半導体領域(n<sup>+</sup>短絡部)間の距離W<sub>p</sub>の減小ひいてはコレクタ面積の減少を招く。これは前者の場合はスナップバック現象の増大を招き後者の場合はオン後のオン電圧の増大即ち電力損失の増大を招く。すなわち、セルの幅を一定にした場合、W<sub>n</sub>/W<sub>p</sub>の比率が小さいとオン電圧劣化を抑制できるレベルまでの温度上昇が容易でなく、大きすぎるとスナップバック現象の増大やオン電圧の増大による電力損失の増大を招く。従って、W<sub>n</sub>/W<sub>p</sub>の比率を適正な範囲に設定する必要がある。一方、高耐圧素子ほどドリフト領域の不純物濃度は低く且つその厚さは厚く設定されるので、ドリフト領域の内部抵抗が大きく素子温度をより少ないI<sub>s*b*</sub>で上昇できる。従って、W<sub>n</sub>/W<sub>p</sub>の適正範囲は耐圧によって異なる。発明者は種々の検討の結果、3kV以上の高耐圧逆導通IGBTにおいては、W<sub>n</sub>/W<sub>p</sub>の適正範囲はSiC半導体の場合、0.2~5.0の範囲にするのが良く、より好ましくは0.3~3.0の範囲にするのが良いことを見出した。40

50

これにより第3の課題を解決し、高性能逆導通IGBTの高い信頼性を実現できる。

#### 【0036】

また、この発明の動作方法によれば、ワイドギャップ半導体逆導通IGBTの急速オン電圧劣化に加えて初動時のオン電圧劣化も抑制でき高い信頼性を実現できる。

#### 【0037】

ワイドギャップ半導体逆導通IGBTには上記のように積層欠陥に起因し通常のオン電圧劣化が発生するとともに、スナップバック現象に起因し急速オン電圧劣化が発生する。

従って、この発明の動作方法により、少なくともワイドギャップ半導体逆導通IGBTがオンする前に所定の低いゲート電圧でMOSFET部をオンさせて前記短絡部を介して多数キャリアによる順方向電流を流し、この積層欠陥の増大を招かない多数キャリア電流により半導体装置を所定温度まで昇温させ、その後にゲート電圧を高くしてコレクタ層から少数キャリアを注入させ、逆導通IGBTをオンさせる。

これにより、すでに存在する積層欠陥の拡大のみならず、スナップバック現象によりコレクタ層からバッファー層やドリフト層に大量の少数キャリアが短時間に急激に注入されることによる積層欠陥の急速拡大も、温度上昇により積層欠陥の少数キャリアトラップ現象を抑制できるので通常のオン電圧劣化のみならず急速オン電圧劣化も抑制できる。

ワイドギャップ半導体逆導通IGBTは一旦オンすると自己発熱で温度が上昇してゆくので、通常のオン電圧劣化や急速オン電圧劣化の影響は抑制される。しかし、初動時にはワイドギャップ半導体逆導通IGBTの温度は周囲温度と同程度に低くなっている。この状態でオンさせると既に存在する積層欠陥が更に拡大しオン電圧劣化を促進し信頼性が損なわれる。

従って、少なくともワイドギャップ半導体逆導通IGBTの初動時には、この発明の動作方法により、逆導通IGBTをオンさせる前に積層欠陥の少数キャリアトラップ現象を抑制できる所定温度まで昇温させものである。これにより、初動時にもオン電圧の劣化の影響を大幅に抑制でき信頼性を向上できる。

現象は大幅に抑制されるためオン電圧の増大のような劣化を大幅に抑制でき信頼性を向上できる。

#### 【0038】

逆導通IGBTの積層欠陥の量や大きさに依存して適切な昇温温度が異なるが、少なくとも初動時には40以上に昇温するのが好ましく、より好ましくは50以上である。また、動作開始後に40以上を維持できない場合でも、動作開始後の各オン時に本発明の動作方法を適用すると初動時と同様に甚大なオン電圧劣化の悪影響を抑制できる。

このように、この動作方法により第3の課題をより効果的に解決し、高性能逆導通IGBTの高い信頼性を実現できる。

#### 【発明の効果】

#### 【0039】

以上のように、本発明により、逆導通IGBTの短絡部の面積をあまり狭めることなくスナップバック現象を抑制でき、ターンオフ時の残存キャリアの排除もより効果的にできる。この結果、スナップバック現象に起因する回路動作の擾乱や破壊を低減できとともに、ターンオフ時間をより短くしてスイッチング損失をより低減できる。また、より小さいチップ面積にしてもスナップバック現象を抑制ができるので低コスト化が図れる。また、オン電圧劣化の影響を抑制し信頼性の向上が図れる。

#### 【図面の簡単な説明】

#### 【0040】

【図1】発見した係数Aの導出法説明図

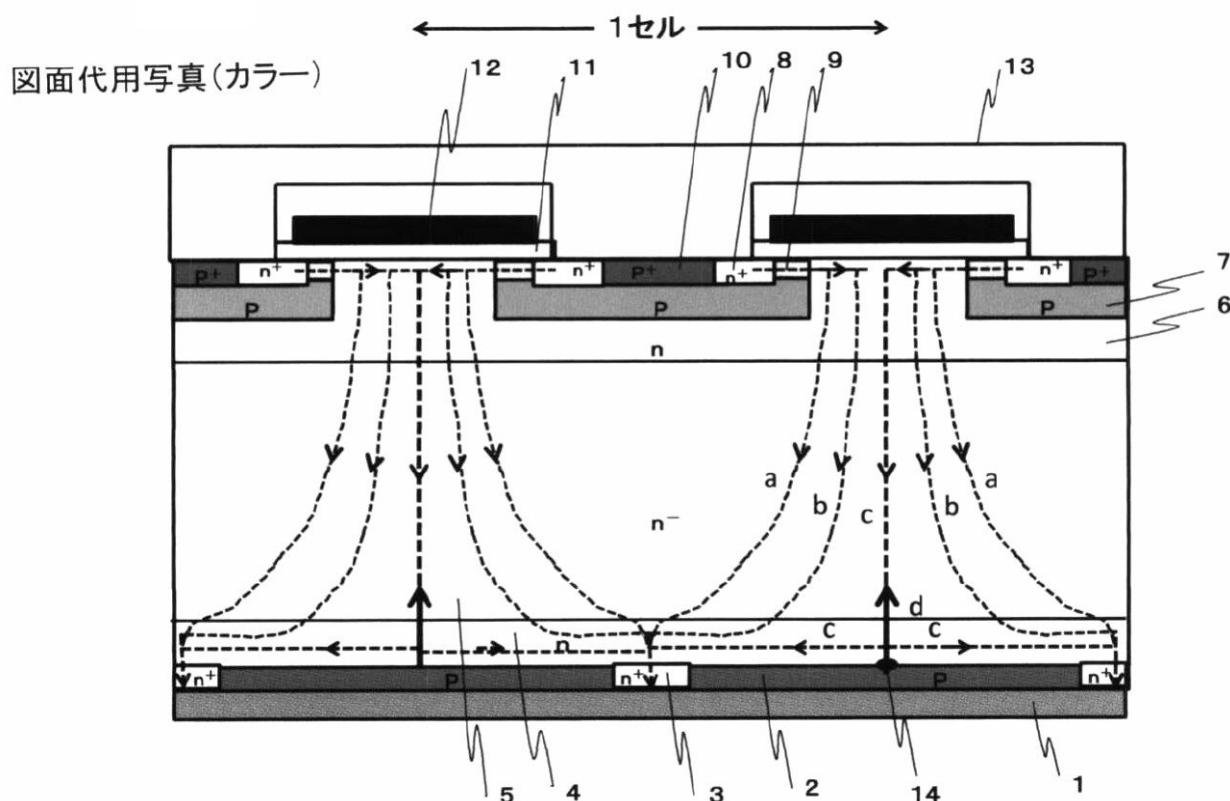

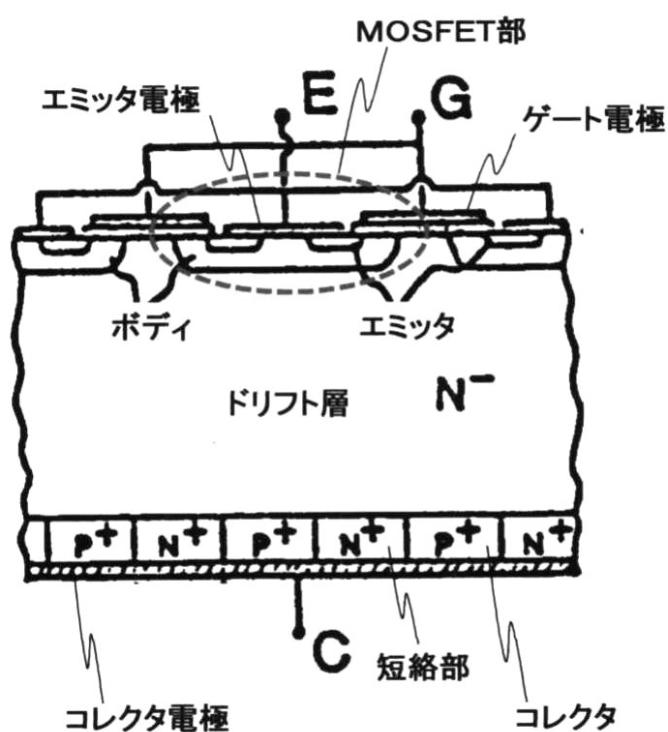

【図2】実施の形態1にかかる半導体装置の模式的断面図

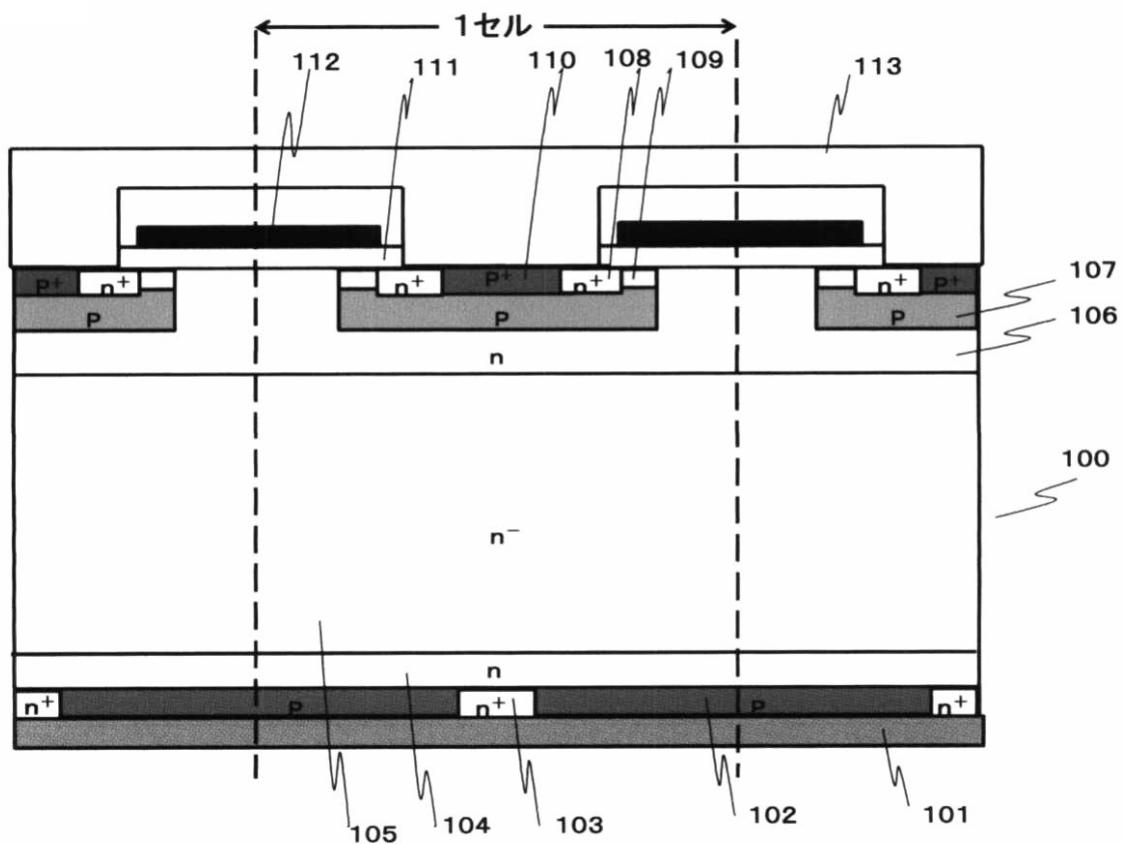

【図3】実施の形態2にかかる半導体装置の模式的断面図

【図4】実施の形態3にかかる半導体装置の模式的断面図

【図5】実施の形態4にかかる半導体装置の模式的断面図

【図6】実施の形態5にかかる半導体装置の模式的断面図

10

20

30

40

50

【図7】従来例1の高耐圧Si逆導通IGBT装置の断面図。

【図8】従来例2の高耐圧Si逆導通IGBT装置の断面図。

【発明を実施するための形態】

#### 【0041】

以下に添付図面を参照して、この発明にかかる半導体装置の好適な実施の形態を詳細に説明する。本明細書および添付図面においては、nまたはpを冠記した層や領域では、それぞれ電子または正孔が多数キャリアであることを意味する。また、nまたはpに付す+および-は、それぞれそれが付されていない層や領域よりも高不純物濃度および低不純物濃度であることを意味する。図面中の層や領域を示す番号と矢印は同じ層や領域の場合、各々代表して1個のみに記し他は省略してある。

10

#### 【0042】

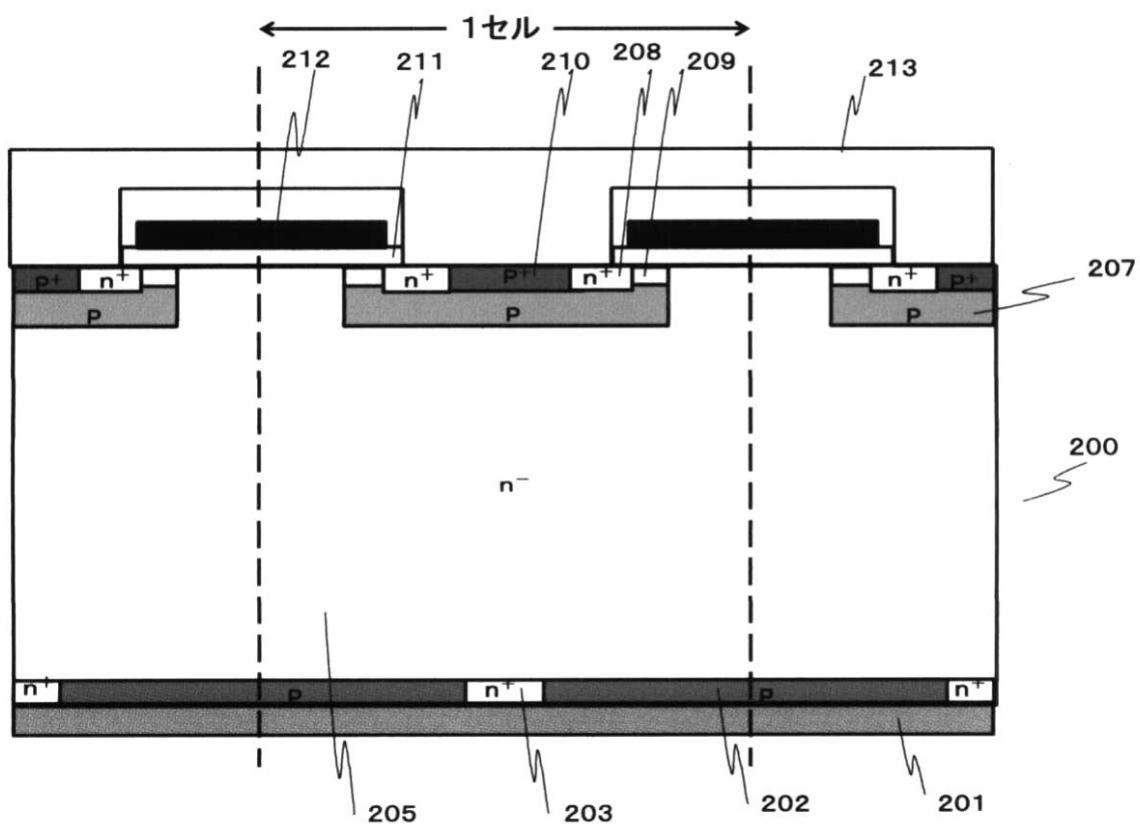

(実施の形態1)

図2は、実施の形態1にかかる半導体装置を模式的に示す断面図である。図2に示す実施の形態1にかかる半導体装置は、炭化珪素(SiC)半導体を用いて作製された例えば設計耐圧15kV級のプレーナゲート構造の逆導通IGBT100である。図2には、逆導通IGBT100の活性領域の一部のみを示す。SiC逆導通IGBT100は、例えば活性領域を囲むように耐圧構造部(不図示)を備えている。活性領域とは、半導体装置のオン時に電流が流れる領域であり、耐圧構造部とは、半導体装置を構成するpn接合表面の電界強度を緩和し、所望の耐圧を実現する構造部である。

20

SiC逆導通IGBT100のチップサイズは8mm×8mmであり、活性領域は6mm×6mmであり、活性領域を囲んでいる耐圧構造部の幅は1mmである。活性領域中の逆導通IGBTセルはストライプ状であり、セルの幅は16ミクロンメートルである。

#### 【0043】

図2に示すように、SiC逆導通IGBT100において、コレクタ電極101に接する裏面にはpコレクタ層とこの層を貫通する複数のn<sup>+</sup>短絡部が設けられ、pコレクタ領域102とn<sup>+</sup>短絡部領域103とが交互に形成されている。これらの領域102と103のおもて面には、n(第2導電型)バッファー層104が設けられている。nバッファー層104は、SiCエピタキシャル層である。pコレクタ領域102の不純物濃度および厚さは、例えば、それぞれ $3.5 \times 10^{17} \text{ cm}^{-3}$ および1.5μmであってもよい。n<sup>+</sup>短絡部103の不純物濃度および厚さは、例えば、それぞれ $1 \times 10^{19} \text{ cm}^{-3}$ および1.5μmであってもよい。また、nバッファー層104の不純物濃度および厚さは、例えば、それぞれ $1.5 \times 10^{16} \text{ cm}^{-3}$ および10μmであってもよい。セルの中のn<sup>+</sup>短絡部103はセルの中心付近に設けられてもよく、その幅は4μmであってもよい。n<sup>+</sup>短絡部間の距離、これはpコレクタ領域の幅に該当するが、この幅は12μmであってもよい。

30

#### 【0044】

nバッファー層104の表面には、n<sup>-</sup>ドリフト層(第1半導体層)105が設けられている。n<sup>-</sup>ドリフト層105は、SiCエピタキシャル層である。n<sup>-</sup>ドリフト層105の不純物濃度は、nバッファー層102の不純物濃度よりも低い。具体的には、n<sup>-</sup>ドリフト層105の不純物濃度および厚さは、例えば、それぞれ $2 \times 10^{14} \text{ cm}^{-3}$ および150μmであってもよい。概略的にこの程度の不純物濃度の場合、n<sup>-</sup>ドリフト層105の厚さ10μm当たり例えば耐圧1kVは容易に実現することができる。このため、n<sup>-</sup>ドリフト層105の厚さを150μmとすることで、耐圧15kVが期待できる

40

#### 【0045】

n<sup>-</sup>ドリフト層105の表面には、n型半導体層106を設けている。この層106はpコレクタ領域102から注入された正孔をn<sup>-</sup>ドリフト層105表面付近に蓄積させIGBTのオン電圧を低減させる効果を持つ層であり、以下ではn電荷蓄積層と記述する。このn電荷蓄積層は例えば窒素(N)を不純物としてエピタキシャル成長させたSiCエピタキシャル層であるが、窒素イオンをイオン注入することによって形成された半導体層であってもよい。また、n電荷蓄積層106は、活性領域のみに設けられていてもよく、

50

例えば活性領域の n<sup>-</sup> ドリフト層 105 にイオン注入によって形成した半導体層であってもよい。

#### 【0046】

n 電荷蓄積層の不純物濃度は、n<sup>-</sup> ドリフト層 105 の不純物濃度よりも高く、後述する p ボディ領域（p ベース領域）107 の不純物濃度よりも低い。但し、n 電荷蓄積層 106 は、逆導通 IGBT 100 の耐圧よりも小さい印加電圧で空乏化する不純物濃度および厚さを有することが肝要である。具体的には、n 電荷蓄積層 106 の不純物濃度は、 $3 \times 10^{15} \text{ cm}^{-3}$  以上  $5 \times 10^{17} \text{ cm}^{-3}$  以下であってもよい。また n 電荷蓄積層 106 の n<sup>-</sup> ドリフト層 105 と p ボディ領域（p ベース領域）間の厚さは、例えば 0.3  $\mu\text{m}$  以上 1.6  $\mu\text{m}$  以下であってもよい。10

#### 【0047】

n 電荷蓄積層 106 の表面層には、p ボディ領域（第 1 半導体領域）107 が選択的に複数設けられている。p ボディ領域 107 の不純物濃度は、n<sup>-</sup> ドリフト層 105、n 電荷蓄積層 106 の不純物濃度よりも高い。具体的には、p ボディ領域 107 の不純物濃度および厚さは、例えば、それぞれ  $1 \times 10^{18} \text{ cm}^{-3}$  および 0.3  $\mu\text{m}$  であってもよい。隣り合う p ボディ領域 107 に挟まれた n 電荷蓄積層 106 の、p ボディ領域 107 が並列する方向（以下、水平方向とする）の幅は、例えば 6  $\mu\text{m}$  であってもよい。

#### 【0048】

p ボディ領域 107 は、例えばアルミニウムのイオン注入によって形成された拡散層である。本実施例では n 電荷蓄積層 106 の不純物濃度を  $5 \times 10^{16} \text{ cm}^{-3}$ 、厚さを 0.7  $\mu\text{m}$  とした。20

#### 【0049】

なお、SiC 半導体は深さ方向に直行する方向の不純物拡散がシリコン半導体に比べて少ないので、図 2 において半導体層を矩形状に図示する（以下、図 3～5 に示す逆導通 IGBT においても同様に、半導体層を矩形状に図示する）。

#### 【0050】

p ボディ領域 107 の表面層には、n<sup>+</sup> エミッタ領域（第 2 半導体領域）108 および p<sup>-</sup> 低濃度チャネル領域 109 や p<sup>+</sup> コンタク領域 110 が選択的に設けられている。n<sup>+</sup> エミッタ領域 108 および p<sup>-</sup> 低濃度チャネル領域 109 や p<sup>+</sup> コンタク領域 110 は、例えばイオン注入によって形成された半導体層である。p<sup>-</sup> 低濃度チャネル領域 109 は、p ボディ領域 108 の一方の端部に設けられ n 電荷蓄積層 106 に接する。n<sup>+</sup> エミッタ領域 8 は、p<sup>-</sup> 低濃度チャネル領域 109 の n 電荷蓄積層 106 に接する端部に対して反対側の端部に接する。30

#### 【0051】

n<sup>+</sup> エミッタ領域 108 の、p<sup>-</sup> 低濃度チャネル領域 109 に接していない側の端部は、p<sup>+</sup> コンタク領域 110 に接している。各 p ボディ領域 107 に設けられた p<sup>-</sup> 低濃度チャネル領域 109 および n<sup>+</sup> エミッタ領域 108 は、隣り合う他の p ボディ領域 107 の p<sup>-</sup> 低濃度チャネル領域 109 および n<sup>+</sup> エミッタ領域 108 と対称に配置されている。40

#### 【0052】

p<sup>-</sup> 低濃度チャネル領域 109 の不純物濃度は、p ボディ領域 107 の不純物濃度よりも低い。具体的には、p<sup>-</sup> 低濃度チャネル領域 109 の不純物濃度および厚さは、例えば、それぞれ  $3 \times 10^{16} \text{ cm}^{-3}$  および 0.3  $\mu\text{m}$  であってもよい。またチャネルの長さは 0.75  $\mu\text{m}$  であってもよい。

n<sup>+</sup> エミッタ領域 108 の不純物濃度は、n<sup>-</sup> ドリフト層 105、n 電荷蓄積層 106 の不純物濃度よりも高い。具体的には、n<sup>+</sup> エミッタ領域 8 の不純物濃度および厚さは、例えば、それぞれ  $5 \times 10^{19} \text{ cm}^{-3}$  および 0.3  $\mu\text{m}$  であってもよい。p<sup>+</sup> コンタク領域 10 の不純物濃度および厚さは、例えば  $1 \times 10^{19} \text{ cm}^{-3}$  および 0.3  $\mu\text{m}$  であってもよい。

#### 【0053】

10

20

30

40

50

$p^-$  低濃度チャネル領域 109 および  $n^+$  エミッタ領域 110 は、 $p$  ボディ領域 108 の表面層にそれぞれイオン注入によって形成される。 $p^-$  低濃度チャネル領域 109 および  $n^+$  エミッタ領域 108 は  $p$  ボディ領域 107 の表面層に例えば 0.3 μm の深さで設けられるので、 $p$  ボディ領域 107 の、 $n$  電荷蓄積層 106 と  $p^-$  低濃度チャネル領域 109 および  $n^+$  エミッタ領域 108 とに挟まれた部分の厚さは例えば 0.3 μm となる。

#### 【0054】

$p^-$  低濃度チャネル領域 109 の水平方向の幅は、例えば 0.75 μm であってもよい。 $n^+$  エミッタ領域 108 の水平方向の幅は、例えば 3 μm であってもよい。

#### 【0055】

$p^-$  低濃度チャネル領域 109 の表面には、ゲート絶縁膜 111 を介してゲート電極（制御電極）112 が設けられている。ゲート絶縁膜 111 の厚さは約 500 オングストロームであってもよい。エミッタ電極（入力電極）113 は、 $n^+$  エミッタ領域 108 に接するとともに  $p^+$  コンタクト層 110 を介して  $p$  ボディ領域 107 にも接する。また、エミッタ電極 113 はゲート電極 112 から絶縁されている。

#### 【0056】

つぎに、図 2 に示す SiC 逆導通 IGBT 100 の製造方法について説明する。まず、300 μm 厚のオフアングル  $n^+$  SiC 基板に厚さ 170 μm の  $n$  ドリフト層 105 を、ついで 11.5 μm 厚の  $n$  バッファー層 104 をエピタキシャル成長で順次形成する。更に 1.5 μm 厚の  $p$  コレクタ層をアルミニニュームのイオン注入により形成し、ついで選択的に窒素のイオン注入により 1.5 μm 厚の  $n$  短絡部領域 103 と  $p$  コレクタ領域 102 を形成する。以下では本明細書全体に渡って、 $n$  短絡部領域および  $p$  コレクタ領域を単に  $n$  短絡部および  $p$  コレクタと記述する。

その後、 $n^+$  SiC 基板の研磨時に  $p$  コレクタ 102 と短絡部 103 を保護する保護用被覆膜を  $p$  コレクタ 102 上と短絡部 103 上に形成する。次に研磨により  $n^+$  SiC 基板を完全に除去し、 $n$  ドリフト層 105 も約 20 μm 研磨し 150 μm の厚さにする。

#### 【0057】

つぎに、例えば窒素を不純物としてドープしてエピタキシャル成長を行い、 $n^-$  ドリフト層 105 の表面に nCEL 106 を成長させる。nCEL 106 は、少なくとも活性領域にのみ設けられていればよいので、例えばイオン注入によって、活性領域の  $n^-$  ドリフト層 105 の表面層のみに nCEL を形成してもよい。

#### 【0058】

イオン注入によって nCEL 106 を形成する場合、まず、 $n^-$  ドリフト層 105 の表面に、nCEL 106 の形成領域が露出する開口部を有するレジストマスクを形成する。そして、このレジストマスクをマスクとして、レジストマスクの開口部に露出する  $n^-$  ドリフト層 105 に例えば窒素イオンをイオン注入する。さらに、熱アニール処理を行う。これにより、活性領域全体にわたって  $n^-$  ドリフト層 105 の表面層に  $n$  電荷蓄積層 106 が形成される。その後、 $n$  電荷蓄積層 106 の形成に用いたレジストマスクを除去する。

$n$  電荷蓄積層 106 をエピタキシャル成長で形成する場合は、例えば窒素を不純物としてドープしてエピタキシャル成長をさせる。

#### 【0059】

つぎに、 $n$  電荷蓄積層 106 の表面に、 $p$  ボディ領域 107 の形成領域が露出する開口部を有するレジストマスクを形成する。そして、このレジストマスクをマスクとして、レジストマスクの開口部に露出する  $n$  電荷蓄積層 106 に  $p$  型不純物イオンをイオン注入する。このとき、後の工程において  $p$  ボディ領域 107 の表面層に  $p$  ボディ領域 107 よりも不純物濃度が低い  $p^-$  低濃度チャネル領域 109 を形成するために、 $p$  ボディ領域 107 の、浅い部分の不純物濃度が深い部分の不純物濃度よりも低くなるようにイオン注入を行うのが好ましい。

#### 【0060】

つぎに、熱アニール処理を行う。これにより、 $n$  電荷蓄積層 106 の表面層に選択的に

10

20

30

40

50

p ボディ領域 107 が形成される。つぎに、p ボディ領域 107 の形成に用いたレジストマスクを除去する。つぎに、p ボディ領域 107 の表面に p<sup>+</sup> コンタクト層形成領域 110 が露出する開口部を有するレジストマスクを形成する。そして、このレジストマスクをマスクとして、レジストマスクの開口部に露出する p ボディ領域 107 に p 型不純物イオンをイオン注入する。

更に、p<sup>-</sup> 低濃度チャネル領域 109 の形成領域が露出する開口部を有するレジストマスクを形成する。そして、このレジストマスクをマスクとして、レジストマスクの開口部に露出する p ボディ領域 107 に不純物イオンをイオン注入する。

#### 【0061】

p<sup>-</sup> 低濃度チャネル領域 109 を形成するためのイオン注入では、p ボディ領域 107 の表面層の不純物濃度が p<sup>-</sup> 低濃度チャネル領域 109 の所望の不純物濃度よりも低い場合には、p<sup>-</sup> 低濃度チャネル領域 109 が所望の不純物濃度となるように p 型不純物濃度をイオン注入する。一方、p ボディ領域 107 の表面層の不純物濃度が p<sup>-</sup> 低濃度チャネル領域 109 の所望の不純物濃度よりも高い場合には、p<sup>-</sup> 低濃度チャネル領域 109 が所望の不純物濃度となるように n 型不純物濃度をイオン注入する。

#### 【0062】

つぎに、熱アニール処理を行う。p ボディ領域 107 の表面層に選択的に p<sup>-</sup> 低濃度チャネル領域 109 が形成される。つぎに、p<sup>-</sup> 低濃度チャネル領域 109 の形成に用いたレジストマスクを除去する。つぎに、p<sup>-</sup> 低濃度チャネル領域 109 の表面に、n<sup>+</sup> エミッタ領域 8 の形成領域が露出する開口部を有するレジストマスクを形成する。そして、このレジストマスクをマスクとして、レジストマスクの開口部に露出する p ボディ領域 107 に n 型不純物イオンをイオン注入する。

#### 【0063】

つぎに、熱アニール処理を行う。これにより、p ボディ領域 107 の表面層に選択的に n<sup>+</sup> エミッタ領域 108 が形成される。つぎに、n<sup>+</sup> エミッタ領域 108 の形成に用いたレジストマスクを除去する。つぎに、p<sup>-</sup> 低濃度チャネル領域 109 の表面に、ゲート絶縁膜 111 を介して多結晶シリコンのゲート電極 112 を形成する。つぎに、おもて面に層間絶縁膜 113 を形成し、層間絶縁膜 113 でゲート電極 112 を覆う。

#### 【0064】

つぎに、フォトリソグラフィによって層間絶縁膜 113 およびゲート絶縁膜 111 を選択的に除去し、n<sup>+</sup> エミッタ領域 108 および p<sup>+</sup> コンタクト層形成領域 110 とエミッタ電極 114 とを接続するためのコンタクトホールを形成する。つぎに、おもて面およびコンタクトホール内にエミッタ電極 114 を形成し、エミッタ電極 114 と、n<sup>+</sup> エミッタ領域 108 および p<sup>+</sup> コンタクト領域 110 とを接続する。つぎに、半導体基板のおもて面に保護膜（不図示）などを形成する。その後、半導体基板の裏面に、p コレクタ 102 と n 短絡部 103 に接するコレクタ電極 111 を形成し、図 1 に示す逆導通 IGBT 100 が完成する。

#### 【0065】

次に、前記の製造方法で作製する IGBT 100 の特性について説明する。

前記の IGBT 100 は T0 型の高耐圧パッケージのリードフレームにダイボンディングし、更にエミッタ電極 114 上に結線用の A1 ワイヤを複数本ワイヤボンディングし、ついで保護用の高耐熱レジン（ナノテクレジン）でチップと A1 ワイヤを完全に被覆して半導体装置にしたのち動作試験に供する。

ゲート電圧を印加しない状態でエミッタ電極 114 とコレクタ電極 101 間に順方向電圧を印加すると、リーク電流が流れるが良好な順阻止特性を示し、室温での耐圧すなわちなだれ降伏を示す電圧は約 16.4 kV である。また、なだれ降伏前のリーク電流は室温で  $3.5 \times 10^{-3} \text{ A/cm}^2$  以下、250°の高温でも  $5 \times 10^{-2} \text{ A/cm}^2$  以下と良好である。

#### 【0066】

ゲート電極 112 に閾値電圧以上のゲート電圧を印加し、ついでコレクタ電極 - エミッタ

10

20

30

40

50

々電極間に順方向電圧を印加し増加してゆくと約2.7Vのビルトイン電圧付近でオン電流が流れ始め、スナップバック現象は観察されない。これは本発明の効果である。コレクターエミッタ間電圧(以下Vce)が5VでのJceは105A/cm<sup>2</sup>と良好である。

#### 【0067】

(7)式より導出したSiC逆導通IGBTのWp(SiC)の下限値はWp(Si)の約1/250である。n<sup>+</sup>短絡部間距離Wpはpコレクタの幅そのものであり、本実施例では前記のように例えば12μmであってもよい。従って、同耐圧・同構成でのスナップバック現象を解消できるSi逆導通IGBTの場合は、n<sup>+</sup>短絡部間距離Wp(Si)は3000μmである。ここで同構成とは、前記したように図2と同じ構造であるが、Si材料の物性を考慮して同耐圧を実現するために必要な各半導体層や各半導体領域の不純物濃度や厚さ及び幅等を採用している逆導通IGBT構造を意味する。両者のWnは4μmであり活性領域の面積を同程度の約6mm×6mmにすると、Si逆導通IGBTの場合は2個のpコレクタと3個のn<sup>+</sup>短絡部しか設けることができない。このため、スナップバック現象は解消できても逆導通IGBTの狙いとするターンオフ速度の改善はWnの占有面積があまりにも少ないため微々たるものであろうと推測される。実際には上記のスナップバック現象を解消した15kV級SiC逆導通IGBTと同耐圧・同構成設計の逆導通Si-IGBTはシミュレーション検討ではIGBT動作が達成できていない。そこで、耐圧を6kVに低減した同構成のSi逆導通IGBTを検討したところ、上記の逆導通SiC-IGBTと同じくWn(Si)を4μmおよびWp(Si)を12μmにした場合、Vsbが0.7kV以上ありオン動作を繰り返す過程で破壊する可能性が大である。

10

20

30

#### 【0068】

本実施の形態になる半導体装置の場合は、直流電源電圧6kV、電流密度50A/cm通電時のターンオフ時間を1.1μsに短縮できている。同耐圧で同構成の上記の6kV Si逆導通IGBTの場合はターンオフ時間は6.5μsである。一般に耐圧を高くするとターンオフ時間は更に長くなる傾向にあるので、本実施の形態の効果が明らかである。すなわち、本実施の形態のSiC逆導通IGBTはn<sup>+</sup>短絡部の幅は同じであるが、n<sup>+</sup>短絡部間距離Wpがはるかに小さいので、その分セル数を増やすことができトータルのn<sup>+</sup>短絡部103の占有面積を増加できるため、逆導通IGBT本来のターンオフ時のキャリアの排除機能を増加できるものである。

30

#### 【0069】

また、n<sup>+</sup>短絡幅Wnが4μm、n<sup>+</sup>短絡部間距離Wpが3000μmとSi逆導通IGBTと同じであり、それ以外の構造が本実施例と同じSiC逆導通IGBTのターンオフ時間は4.2μsである。更に、Wpを1μmにしターンオフ時のキャリアの排除機能の大幅増加を図ったSiC逆導通IGBTはターンオフ時間を約0.35μsに短縮できたが、顕著なスナップバック現象が発生した。

40

#### 【0070】

本実施の形態になるSiC逆導通IGBTを、Jce100A/cm<sup>2</sup>で500時間の通電試験実施後のオン電圧の増大は、ほとんどの素子がSi逆導通IGBTと同等の0.1V以下にとどまり顕著な信頼性への悪影響は見いだされない。

40

#### 【0071】

一方、n<sup>+</sup>短絡部間距離Wpを極端に小さくしてスナップバック現象を意図的に発生させたSiC逆導通IGBTの場合は、同様の通電試験で2V以上のオン電圧劣化を示すIGBTが発生する。また、この構造のSiC逆導通IGBTはJce60A/cm<sup>2</sup>でパルス幅500μsとする20時間のオン・オフ繰り返し試験後に、オン電圧の急速オン電圧劣化が観察され7V以上のオン電圧劣化を示すIGBTも発生する。

50

#### 【0072】

これらのSiC逆導通IGBTは前記の本発明による動作方法の適用により、IGBT動作時のオン電圧の増大を0.2V以下に抑制でき信頼性への悪影響を解消できるとともに、上記のオン・オフ繰り返し試験でも、急速オン電圧劣化を解消できる。すなわち、ま

50

ずコレクタ電極とエミッタ電極間に所定の  $V_{ce}$  電圧を印加し且つゲート電極に IGBT 動作が始まらないゲート電圧、例えば 5 V 程度を印加し動作させる。これにより、 $n^+$  短絡部 103 を介して MOSFET 電流を流し、この電流で素子の温度を上昇させる。素子の温度が 50 以上になった時点でのゲート電圧を 20 V 程度に昇圧し IGBT 動作をさせる。このような本発明になる動作方法の適用により、オン電圧の増大をもたらした積層欠陥による少数キャリアをトラップし消滅させる現象が大幅に抑制されることによるものである。

#### 【0073】

なお、上記本発明になる動作方法を適用しない場合、すなわち、所定の  $V_{ce}$  電圧と 20 V のゲート電圧を印加してオンさせる動作を SiC 逆導通 IGBT が周囲温度程度に冷える時間間隔をおいて何回か繰り返す場合は、そのたびにオン電圧の増大が更に進行し、オン時に破壊に至る素子が発生する可能性が増大する。10

#### 【0074】

以上に説明したように、実施の形態 1 にかかる半導体装置によれば、スナップバック現象を大幅に抑制でき且つ更なる高速・低損失化により高性能化できるとともに、オン電圧劣化が抑制でき信頼性も高い逆導通 IGBT 100 を実現できる。また、 $n^+$  短絡部間距離  $W_p$  を極端に小さくしてスナップバック現象を意図的に発生させた SiC 逆導通 IGBT に本発明になる動作方法を適用することにより、オン電圧劣化を抑制でき信頼性も高い逆導通 IGBT の動作方法を実現できる。

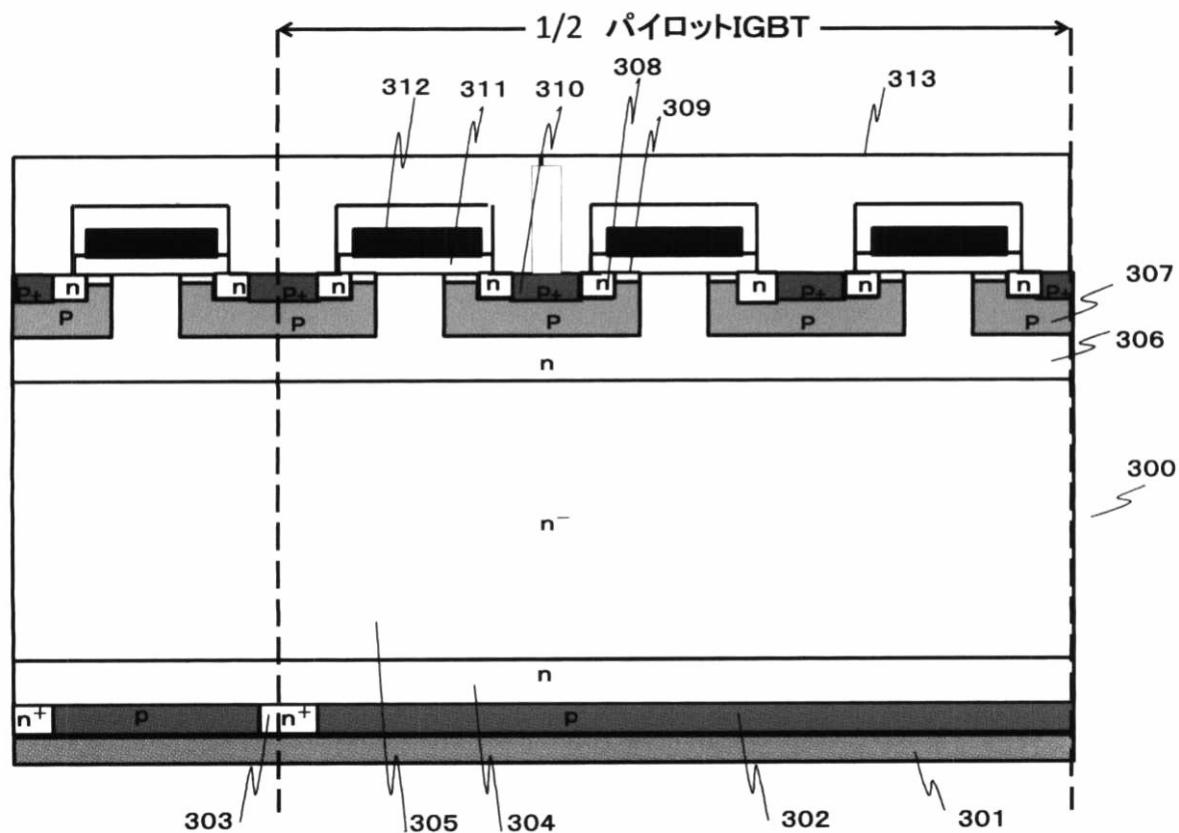

#### 【0075】

##### (実施の形態 2)

図 3 は、実施の形態 2 にかかる半導体装置を模式的に示す断面図である。上記の実施の形態 1 の半導体装置に比べて、 $n$  ドリフト層を 175 μm と厚くし  $n$  バッファー層を設けていない点と  $n$  電荷蓄積層を設けていない点を除けば、その他は同じ構造である。また、製作プロセスも  $n$  ドリフト層を 195 μm と厚くエピタキシャル成長させている点と  $n$  バッファー層および  $n$  電荷蓄積層の形成プロセスが削除されている点を除けばほぼ同じである。20

#### 【0076】

次に、本実施の形態 2 にかかる SiC 逆導通 IGBT の特性を説明する。

ゲート電圧を印加しない状態でエミッタ電極 214 とコレクタ電極 201 間に順方向電圧を印加すると、リーク電流が流れるが良好な順阻止特性を示し、室温での耐圧すなわちなだれ降伏を示す電圧は 17.8 kV 付近である。また、なだれ降伏前のリーク電流は室温で  $1.5 \times 10^{-3} \text{ A/cm}^2$  以下、250 の高温でも  $3 \times 10^{-2} \text{ A/cm}^2$  以下と良好である。30

ゲート電極 212 に閾値電圧以上のゲート電圧を印加し、ついでコレクターエミッタ間に順方向電圧を印加すると約 2.7 V のビルトイン電圧以上でオン電流が流れ、スナップバック現象は観察されない。コレクターエミッタ間電圧（以下  $V_{ce}$ ）が 5 V での  $J_{ce}$  は約 80 A/cm<sup>2</sup> と良好である。

#### 【0077】

本実施の形態になる半導体装置の場合は、同耐圧で同構成のスナップバック現象を解消できる上記の短絡部間距離  $W_p$  が 3000 μm の Si 逆導通 IGBT に比べて、 $n^+$  短絡部幅は 4 μm と同じであるが  $n^+$  短絡部間距離  $W_p$  が 12 μm でありはるかに小さい。従って、 $W_p$  が短い分セル数を増やすことができトータルの  $n^+$  短絡部 203 の面積を増加できるため、逆導通 IGBT 本来のターンオフ時のキャリアの排除機能を増加できる。この結果、直流電源電圧 6 kV、電流密度 50 A/cm 通電時のターンオフ時間を 1.2 μs に短縮できている。一方、同構成の 6 kV 耐圧の Si 逆導通 IGBT は耐圧が低いにもかかわらずターンオフ時間は 8.1 μs である。また、 $n^+$  短絡幅  $W_n$  と  $n^+$  短絡部間距離  $W_p$  が Si 逆導通 IGBT と同じであり、それ以外の構造が本実施例と同じ SiC 逆導通 IGBT の場合は、ターンオフ時間は 3.9 μs である。40

#### 【0078】

10

20

30

40

50

また、 $J_{ce} = 100 \text{ A/cm}^2$  での 500 時間の通電試験後でも、オン電圧の増大は 0.1 V 以下にとどまり SiC 逆導通 IGBT と同等であり顕著な信頼性への悪影響は見いだされない。一方、 $n^+$  短絡部間距離  $W_p$  を極端に小さくしてスナップバック現象を意図的に発生させた SiC 逆導通 IGBT の場合は、同様の通電試験を実施すると 4 V 以上のオン電圧劣化をしめす IGBT が発生する。

以上に説明したように、実施の形態 2 にかかる半導体装置によれば、スナップバック現象を大幅に抑制でき且つ更なる高速・低損失化により高性能化できるとともに、オン電圧劣化が抑制でき信頼性も高い SiC 逆導通 IGBT 200 を実現できる。

#### 【0079】

(実施の形態 3)

10

図 4 は、実施の形態 3 にかかる半導体装置を模式的に示す断面図である。設計耐圧 30 kV の SiC 逆導通 IGBT であり、スナップバック現象を抑制するためにパイロット IGBT 領域を設けており、図 4 には、その 1/2 と逆導通 IGBT 1 セル分とが示されている。

#### 【0080】

SiC 逆導通 IGBT セルの中の  $n^+$  短絡部 303 は p ボディ 307 に対向してその中心付近に設けられてもよく、その幅は  $4 \mu\text{m}$  であってもよい。 $n^+$  短絡部間の距離、これは p コレクタの幅に該当するが、この幅は  $12 \mu\text{m}$  であってもよい。一方、パイロット IGBT 領域の p コレクタの幅は  $108 \mu\text{m}$  であってもよい。

本 SiC 逆導通 IGBT 300 は上記のパイロット IGBT 領域を設けた点と、 $n^-$  ドリフト層 305 と p コレクタ層 302 および n バッファー層 304 の濃度と厚さが異なる点を除けば、その他の構造は実施の形態 1 とほぼ同じである。

#### 【0081】

本実施の形態における  $n^-$  ドリフト層 305 は不純物濃度が  $9 \times 10^{13} \text{ cm}^{-3}$ 、厚さが  $300 \mu\text{m}$  であってもよい。また、p コレクタ 302 の不純物濃度および厚さは、例えば、それぞれ  $6 \times 10^{17} \text{ cm}^{-3}$  および  $1.5 \mu\text{m}$  であってもよい。n バッファー層 304 の不純物濃度および厚さは、例えば、それぞれ  $3.0 \times 10^{16} \text{ cm}^{-3}$  および  $17 \mu\text{m}$  であってもよい。

#### 【0082】

本 SiC 逆導通 IGBT 300 の製造プロセスは以下の点を除けば実施の形態 1 とほぼ同じである。

30

$300 \mu\text{m}$  厚のオフアングル  $n^+$  SiC 基板に厚さ  $320 \mu\text{m}$  の  $n^-$  ドリフト層 305 を、ついで  $17 \mu\text{m}$  厚の n バッファー層 304 をエピタキシャル成長で順次形成する。更に  $1.5 \mu\text{m}$  厚の p コレクタ層をエピタキシャル成長する。ついで  $1.5 \mu\text{m}$  厚の n 短絡部 303 を公知のホトリソ技術を用いて選択的に窒素のイオン注入することにより順次形成する。

その後、 $n^+$  SiC 基板の研磨時に p コレクタ 302 と短絡部 303 を保護する保護用被覆膜を p コレクタ 302 上と短絡部 303 上に形成する。次に研磨により  $n^+$  SiC 基板を完全に除去し、n ドリフト層 303 も約  $20 \mu\text{m}$  研磨し  $300 \mu\text{m}$  の厚さにする。

#### 【0083】

次に、本実施の形態 3 にかかる SiC 逆導通 IGBT 300 の特性を説明する。

ゲート電圧を印加しない状態でエミッタ電極 314 とコレクタ電極 301 間に順方向電圧を印加すると、リーク電流が流れるが良好な順阻止特性を示し、室温での耐圧すなわちなだれ降伏を示す電圧は  $31.2 \text{ kV}$  付近であった。また、なだれ降伏前のリーク電流は室温で  $6.5 \times 10^{-3} \text{ A/cm}^2$  以下、 $250^\circ\text{C}$  の高温でも  $5 \times 10^{-2} \text{ A/cm}^2$  以下と良好であった。

#### 【0084】

ゲート電極 312 に閾値電圧以上のゲート電圧を印加し、ついでコレクターエミッタ間に順方向電圧を印加すると約  $2.7 \text{ V}$  のビルトイン電圧以上でオン電流が流れ、スナップバック現象は観察されなかった。コレクタ - エミッタ間電圧（以下  $V_{ce}$ ）が  $5 \text{ V}$  での  $J$

40

50

c e は  $63 \text{ A/cm}^2$  と良好であった。

#### 【0085】

本実施の形態になる半導体装置の場合は、同耐圧で同構成のスナップバック現象を解消した Si 逆導通 IGBT に比べて、 $n^+$  短絡部幅は同じであるが、逆導通 IGBT セルおよびパイロット IGBT 領域の  $n^+$  短絡部間距離  $W_p$  がいづれもはるかに小さいので、その分セル数を増やすことができる。このため  $n^+$  短絡部 303 の面積を増加できるため、逆導通 IGBT 本来のターンオフ時のキャリアの排除機能を増加できる。この結果、直流電源電圧 10 kV、電流密度  $50 \text{ A/cm}$  通電時のターンオフ時間を  $1.8 \mu\text{s}$  にできている。一方、同構成の 30 kV 級の Si 逆導通 IGBT は製作困難であり、シミュレーションにより検討では、ターンオフ時間は約  $20 \mu\text{s}$  以上と推測される。

10

#### 【0086】

また、 $J_{ce} 50 \text{ A/cm}^2$  でのパルス幅  $500 \mu\text{s}$  20 時間のオン・オフ繰り返し試験実施後でも急速オン電圧劣化は観察されない。これは本実施の形態によりスナップバック現象が解消できることによる効果である。なお、 $J_{ce} 50 \text{ A/cm}^2$  での 500 時間の通電試験後でもオン電圧の増大はほとんどの素子で  $0.1 \text{ V}$  以下にとどまり、オン電圧劣化は観察されない。

#### 【0087】

以上に説明したように、実施の形態 3 にかかる半導体装置によれば、スナップバック現象を大幅に抑制でき且つ更なる高速・低損失化により高性能化できるとともに、オン電圧劣化が抑制でき信頼性も高い超高耐圧 SiC 逆導通 IGBT を実現できる。

20

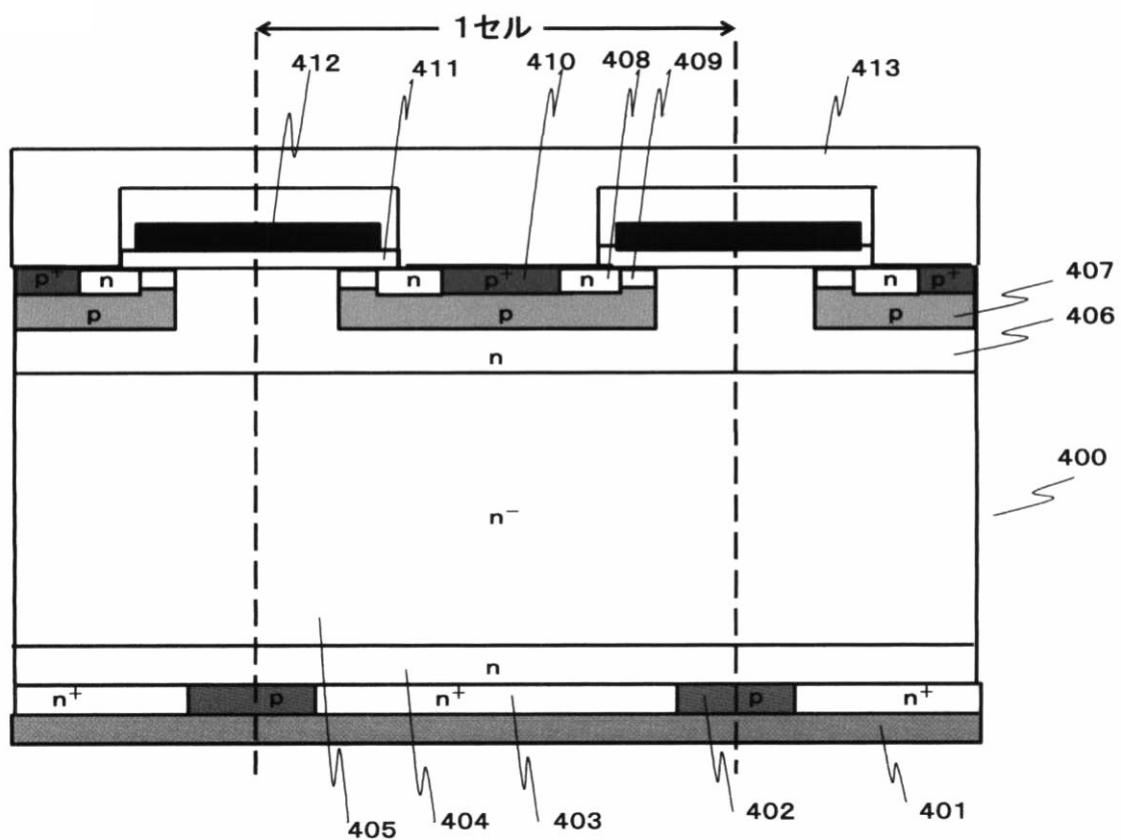

#### 【0088】

##### (実施の形態 4)

図 5 は、実施の形態 4 にかかる半導体装置を模式的に示す断面図である。上記の実施の形態 1 の半導体装置に比べて、 $n^+$  短絡部 403 の幅  $W_n$  を  $12 \mu\text{m}$ 、短絡部間の距離すなわち p コレクタ 402 の幅  $W_p$  を  $4 \mu\text{m}$  としている点を除けば、その他は同じ構造である。これにより、実施の形態 4 にかかる SiC 逆導通 IGBT は、前記の実施形態 1 に比べて更により高い信頼性を実現するものである。

#### 【0089】

すなわち、本 SiC 逆導通 IGBT では  $n^+$  短絡部の幅  $W_n$  と p コレクタの幅  $W_p$  の比率  $W_n / W_p$  を大きくし 3 にしている。セルの幅は  $12 \mu\text{m}$  と同じなので、実施の形態 1 に比べて、 $n^+$  短絡部の幅  $W_n$  の増大により  $n^+$  短絡部の面積が増大するとともに、 $W_n$  の増大分だけ  $W_p$  が低減されることにより p コレクタ接合がビルトインする電流  $I_{sb}$  が増大される。この SiC 逆導通 IGBT がオンする前に流れる  $I_{sb}$  電流は多数キャリ電流であり積層欠陥の拡大を招かないので、本実施の形態では積極的に増大するものである。 $I_{sb}$  の増大により、特にドリフト層 405 での電力損失に伴う発熱が増大しこれにより、SiC 逆導通 IGBT がオンする前にその素子温度を、積層欠陥が少数キャリアをトラップして再結合させ消滅してしまう現象が抑制される温度まで上昇させ、オン時点でのオン電圧劣化の抑制をはかっている。

30

#### 【0090】

セルの幅を一定にした場合、 $W_n / W_p$  の比率が小さすぎるとオン電圧劣化を抑制できるレベルまでの温度上昇が困難であり、大きすぎるとスナップバック現象の増大やオン電圧の増大による電力損失の増大を招く。従って、 $W_n / W_p$  の比率は適正な範囲に設定する必要がある。一方、高耐圧素子ほどドリフト領域の不純物濃度は低く且つその厚さは厚く設定されるので、ドリフト領域の内部抵抗が大きく素子温度をより少ない  $I_{sb}$  で上昇できる。従って、 $W_n / W_p$  の適正範囲は耐圧によっても異なる。発明者は種々の検討の結果、5 kV 以上の高耐圧 SiC 逆導通 IGBT においては、 $W_n / W_p$  の適正範囲は、 $0.2 \sim 5.0$  の範囲にするのが良く、より好ましくは  $0.3 \sim 3.0$  の範囲にするのが良いことを見出した。

#### 【0091】

以下に、本実施の形態 4 にかかる SiC 逆導通 IGBT の特性を説明する。

40

50

ゲート電圧を印加しない状態でエミッタ電極 413 とコレクタ電極 401 間に順方向電圧を印加すると、リーク電流が流れるが良好な順阻止特性を示し、室温での耐圧すなわちなだれ降伏を示す電圧は 17.3 kV 付近である。また、なだれ降伏前のリーク電流は室温で  $2.3 \times 10^{-3} \text{ A/cm}^2$  以下、250 の高温でも  $2.8 \times 10^{-2} \text{ A/cm}^2$  以下と良好である。

ゲート電極 412 に閾値電圧以上のゲート電圧を印加し、ついでコレクターエミッタ間に順方向電圧を印加すると約 2.7 V のビルトイン電圧以上でオン電流が流れ、スナップバック現象は観察されない。コレクターエミッタ間電圧  $V_{ce}$  が 5 V での  $J_{ce}$  は約 60 A / cm<sup>2</sup> と良好である。

#### 【0092】

10

また、ターンオフ時間が 0.7 μs であり、実施の形態 1 に比べて短縮できている。これは、同耐圧でチップサイズとセル幅が同じ逆導通 IGBT で、Wn / Wp の比率を大きくしたために n<sup>+</sup> 短絡部のトータル面積が大きくなり、従ってターンオフ時の残存キャリアの排出能力が大きくなりターンオフ時間を短くできることによるものである。これにより電力損失も低減でき、より高性能化できている。

#### 【0093】

また、Jce 60 A / cm<sup>2</sup> でパルス幅 500 μs とする 20 時間のオン・オフ繰り返し試験後で、オン電圧の急速劣化は観察されない。これは本実施の形態においてスナップバック現象が解消できることによる効果である。更に、本実施の形態になるほとんどの素子のオン電圧の変化は 0.1 V 以下にとどまり、低耐圧の市販の SiC 逆導通 IGBT と同等であり顕著な信頼性への悪影響は見いだされない。

20

#### 【0094】

また、上記のオン・オフ繰り返し動作試験を 500 時間の長時間実施した場合、試験終了後に SiC 逆導通 IGBT の温度が室温程度（30 以下）に低減した状態で測定すると、オン電圧が劣化している素子が発生する。従って、室温程度の温度でこの素子を動作させる場合は素子損傷などの懸念が生じる。

但し、一旦動作を開始し動作試験実施中には素子温度が自己発熱で 100 以上に高くなっているので、前記の積層欠陥のトラップ現象が抑制されるためこのようなオン電圧が劣化している素子でも著しく電力損失が増える等の実害は生じない。

#### 【0095】

30

上記からも判るように、本実施の形態の効果を確認するうえでは耐久オン・オフ繰り返し動作試験がより好ましい。この試験は、20 時間オン・オフ繰り返し動作後に素子温度を室温程度まで冷却し、再度 20 時間オン・オフ繰り返し動作させ再度室温程度まで冷却するといった動作を繰り返す試験である。

実施の形態 1 において n<sup>+</sup> 短絡部 203 の幅 Wn を 2 μm、短絡部間の距離すなわち p コレクタ 202 の幅 Wp を 14 μm とした Wn / Wp が約 0.14 の SiC 逆導通 IGBT にこの耐久オン・オフ繰り返し動作試験を試みると、20 回程度の繰り返し時にオン電圧が 15 V 以上に増大し容易に破損してしまう。

一方、本実施の形態 4 の SiC 逆導通 IGBT の場合は 100 回以上繰り返しても破壊する素子は発生することはなく、より高い信頼性を実現できている。これは上記の Wn / Wp を大きくしたことによる本実施の形態の効果である。

#### 【0096】

40

以上に説明したように、実施の形態 4 にかかる半導体装置によれば、Wn / Wp を大きくし適正化することにより、高速・低損失化による高性能化が実現できるとともに、オンする直前の温度を上昇させてきオン電圧劣化を抑制でき信頼性も高い SiC 逆導通 IGBT を実現できる。

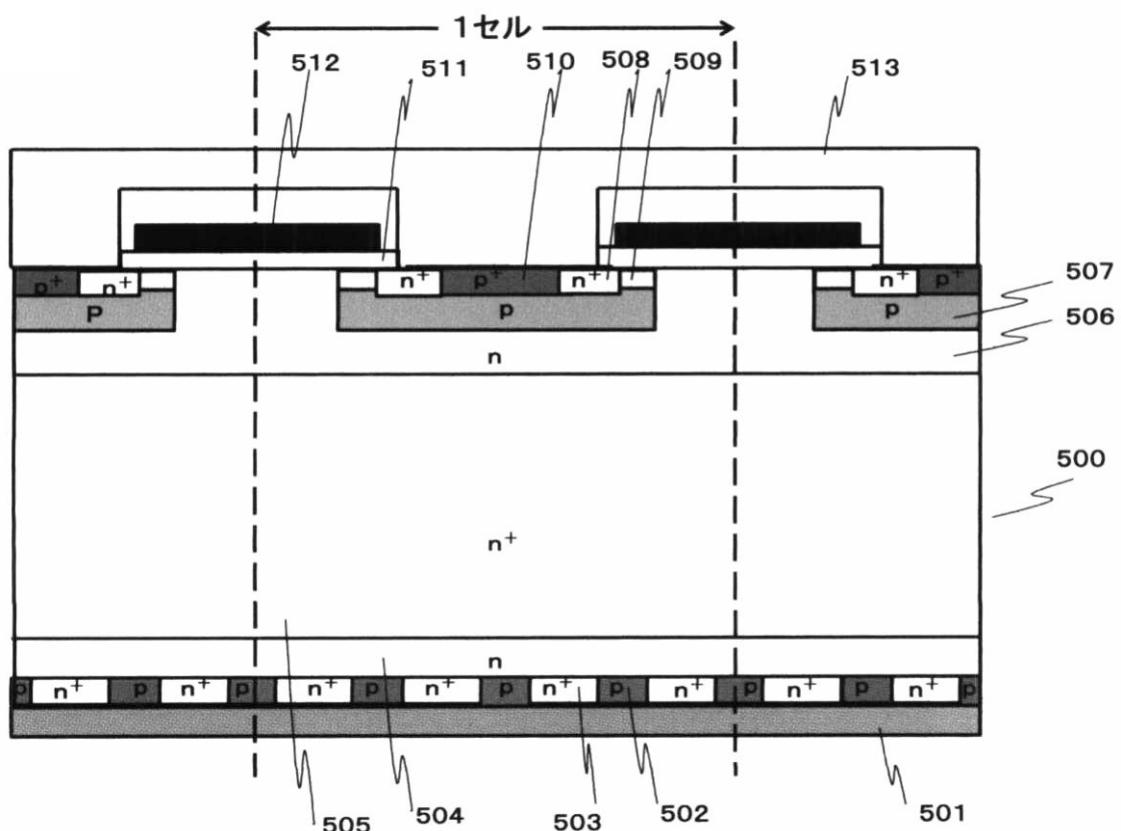

#### 【0097】

##### (実施の形態 5)

図 6 は、実施の形態 5 にかかる半導体装置を模式的に示す断面図である。上記の実施の形態 4 の半導体装置に比べて、n<sup>+</sup> 短絡部 503 の幅 Wn を 2.5 μm、短絡部間の距離

50

すなわち p コレクタ 502 の幅 Wp を  $1.5 \mu m$  とし、セル内に 4 組の n<sup>+</sup> 短絡部と p コレクタを設けた点を除けば、その他は同じ構造である。

#### 【0098】

本 SiC 逆導通 IGBT では実施の形態 4 と同様に、実施形態 1 に比べて  $Wn / Wp$  を大きくして 1 とすることにより高性能化とオン電圧劣化抑制による高信頼性化を図っている。その一方、実施の形態 4 に比べてセル内の p コレクタ 502 の幅 Wp を細断することにより  $2 \mu m$  と小さくしているため Isb を大きくでき、オン直前の素子温度の上昇がより高くなるようにしている。しかしほセル内の Wp のトータル幅は  $8 \mu m$  であり実施形態 4 に比べて 2 倍に大きくしており、これによりオン後の Jce を増大させる一方、オン電圧の低減による電力損失の低減を図っている。

10

#### 【0099】

以下に、本実施の形態 5 にかかる SiC 逆導通 IGBT の特性を説明する。

ゲート電圧を印加しない状態でエミッタ電極 513 とコレクタ電極 501 間に順方向電圧を印加すると、リーク電流が流れるが良好な順阻止特性を示し、室温での耐圧すなわちなだれ降伏を示す電圧は  $17.1 kV$  付近である。また、なだれ降伏前のリーク電流は室温で  $2.5 \times 10^{-3} A / cm^2$  以下、 $250^\circ C$  の高温でも  $3.1 \times 10^{-2} A / cm^2$  以下と良好である。

Vce が  $5 V$ 、ゲート電極 512 の電圧が  $20 V$  での Jce は約  $85 A / cm^2$  と良好であり実施の形態 4 に比べて大幅に増加できる。これは一定オン電流でのオン電圧を低減できることもあり電力損失の低減ができる。これらは本実施の形態 5 の効果である。また、ターンオフ時間は  $0.9 \mu s$  である。

20

#### 【0100】

本実施の形態 5 の SiC 逆導通 IGBT は、耐久オン・オフ繰り返し動作試験において、200 回以上繰り返しても破壊する素子は発生しない。これは実施の形態 4 に比べて Wp の幅が低減したので SiC 逆導通 IGBT がオンする前に流れる Isb 電流が増大できたために、逆導通 IGBT がオンする前にその温度を実施の形態 4 よりも高い温度に上昇させることができ、積層欠陥が少数キャリアをトラップして再結合させ消滅させてしまう現象がより大幅に抑制されオン電圧劣化の大幅な抑制を達成できることによる。

#### 【0101】

以上のように、本実施の形態 5 の SiC 逆導通 IGBT により、より高い性能とより高い信頼性を実現できる。

30

#### 【0102】

以上、第 1 から第 5 の実施の形態に基づき本発明を説明したが、本発明はこれらに限定されるものではなく各種の変形応用が容易に出来ることは当業者には自明である。例えば、構造諸元の数値を変更し  $3 kV$  といった低い耐圧や  $50 kV$  といった更に高い耐圧のワイドギャップ半導体逆導通 IGBT に展開できることは当然である。セル形状も言及したストライプ形状以外にメッシュ形状等の種々の形状が採用できることは当然である。また、セルの幅や n 短絡部の幅や p コレクタの幅および両者の面積比も言及した値以外に逆導通 IGBT の仕様によって種々の値を採用できることも当然のことである。主に、n 短絡部をセルの中心付近の p ボディ下に対向して設けたセル構造について言及したが、n 短絡部をセルの片側端部もしくは両端部に設けたセル構造等に応用展開できることも当然である。また、n 型逆導通 SiC - IGBT に言及したが、極性の異なる p 型逆導通 SiC - IGBT にも同様に展開できることは自明である。更に、逆導通 SiC - IGBT について言及したが、GaN やダイヤモンドといった他のワイドギャップ半導体を用いた逆導通 IGBT にも応用展開できるものである。

40

#### 【産業上の利用可能性】

#### 【0103】

本発明は配電系統に直結する高耐圧インバータ等に利用でき、この場合はトランスの大幅な小型化やトランス自体の除去することもでき、システムの大幅な小型軽量化や省エネルギー化・省資源化が可能になる。また、現在の配電系統にとどまらず、次世代の系統網

50

であるスマートグリッドへの利用が可能である。更に、大型ファンやポンプ、圧延機といった産業用機器の制御装置にも利用できる。

【符号の説明】

【0 1 0 4】

- |                           |                          |

|---------------------------|--------------------------|

| 1、101, 201, 301、401、501   | : コレクタ電極                 |

| 2、102, 202, 302、402、502   | : pコレクタ                  |

| 3、103, 203, 303、403、503   | : n <sup>+</sup> 短絡部     |

| 4、104, 304、404、504        | : nバッファー層                |

| 5、105, 205, 305、405、505   | : n <sup>-</sup> ドリフト層   |

| 6、106, 306、406、506        | : n電荷蓄積層                 |

| 7、107, 207, 307、407、507   | : pボディ領域                 |

| 8、108, 208, 308、408、508   | : n <sup>+</sup> エミッタ領域  |

| 9、109, 209, 309、409、509   | : p <sup>-</sup> チャネル領域  |

| 10、110, 210, 310、410、510  | : p <sup>+</sup> コンタクト領域 |

| 11, 111, 211, 311、411、511 | : ゲート酸化膜                 |

| 12, 112, 212, 312、412、512 | : ゲート電極                  |

| 13, 113, 213, 313、413、513 | : エミッタ電極                 |

| 14                        | : pコレクタ接合中央部             |

10

【図1】

【図2】

図面代用写真(カラー)

【図3】

図面代用写真(カラー)

【図4】

図面代用写真(カラー)

【図5】

図面代用写真(カラー)

【図6】

図面代用写真(カラー)

【図7】

図面代用写真(カラー)

【図8】

図面代用写真(カラー)