(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-519052

(P2007-519052A)

(43) 公表日 平成19年7月12日(2007.7.12)

| (51) Int.C1.               | F 1       | テーマコード (参考) |

|----------------------------|-----------|-------------|

| <b>G06F 9/38</b> (2006.01) | G06F 9/38 | 310J 5B013  |

| <b>G06F 9/30</b> (2006.01) | G06F 9/38 | 370B 5B033  |

|                            | G06F 9/30 | 350F        |

|                            | G06F 9/30 | 330A        |

審査請求 未請求 予備審査請求 未請求 (全 17 頁)

|               |                              |          |                                                                                           |

|---------------|------------------------------|----------|-------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2006-516736 (P2006-516736) | (71) 出願人 | 590000248<br>コーニングレッカ フィリップス エレクトロニクス エヌ ヴィ<br>オランダ国 5621 ベーアー アインドーフェン フルーネヴァウツウェッハ<br>1 |

| (86) (22) 出願日 | 平成16年6月22日 (2004.6.22)       | (74) 代理人 | 100070150<br>弁理士 伊東 忠彦                                                                    |

| (85) 翻訳文提出日   | 平成18年2月21日 (2006.2.21)       | (74) 代理人 | 100075812<br>弁理士 吉武 賢次                                                                    |

| (86) 國際出願番号   | PCT/IB2004/050964            | (74) 代理人 | 100088889<br>弁理士 橋谷 英俊                                                                    |

| (87) 國際公開番号   | W02004/114128                | (74) 代理人 | 100082991<br>弁理士 佐藤 泰和                                                                    |

| (87) 國際公開日    | 平成16年12月29日 (2004.12.29)     |          |                                                                                           |

| (31) 優先権主張番号  | 03101877.3                   |          |                                                                                           |

| (32) 優先日      | 平成15年6月25日 (2003.6.25)       |          |                                                                                           |

| (33) 優先権主張国   | 歐州特許庁 (EP)                   |          |                                                                                           |

最終頁に続く

(54) 【発明の名称】 命令制御式データ処理装置

## (57) 【要約】

データ処理装置は、複数の機能ユニットを有し、連続した命令サイクルで命令を発行する。第1タイプの命令は、それぞれ一時に1つの機能ユニットに向けたものである。第2タイプの命令により、機能ユニットの組合せが同じ命令実行サイクルで応答するようになり、1つの機能ユニットからの結果が、同じ命令の実行の一環として別の機能ユニットによって使用される。好ましくは、この装置は、実行されるプログラム・セグメントが第2タイプの命令を含むかどうかに応じた、いくつかの異なる命令サイクル速度での選択的演算をサポートする。最も速い命令サイクル速度では、異なる機能ユニットによる演算が命令実行サイクル内に収まらないので、第2タイプの命令の実行は許容されない。可能であれば、この装置は、遅いクロック速度に切り換わることによって電力消費を節減し、その場合、第2タイプの命令が実行されて、発行されるべき命令の数を低減することにより電力消費をさらに節減する。

**【特許請求の範囲】****【請求項 1】**

命令セットから命令を発行するための発行スロットを有し、前記命令のそれぞれを連続した命令サイクルで発行する命令発行ユニットと、

読み取りポートおよび書き込みポートをもつレジスタ・ファイルと、

それぞれ前記発行スロットに結合された制御入力、前記読み取りポートに結合されたオペランド入力、および前記書き込みポートに結合された結果出力を有し、それぞれが他の機能ユニットが応答しない前記命令セットの該当のサブセットからの命令に応答する、機能ユニットのグループであって、前記命令セットがさらに、前記機能ユニットのうちの第1および第2機能ユニットが応答する組合せ命令を含む機能ユニットのグループと、

前記発行スロットに結合され、前記命令セットからの前記組合せ命令に応答して、前記機能ユニットのうちの前記第1機能ユニットの結果出力を、前記機能ユニットのうちの前記第2機能ユニットの前記オペランド入力に送る制御ユニットとを含む、命令制御式データ処理装置。

**【請求項 2】**

VLIWプロセッサとして構成され、前記発行スロットが、前記組合せ命令をその命令の1つとして含むVLIW命令語を発行するための前記命令発行ユニットの複数の発行スロットの1つであり、前記レジスタ・ファイルが、複数組の読み取りおよび書き込みポートを有する命令制御式データ処理装置であって、それぞれ前記発行スロットの1つおよび前記複数組の読み取りおよび書き込みポートに結合された、前記VLIW命令語からの該当の命令を実行するための、機能ユニットまたは機能ユニット・グループを含み、前記機能ユニットのうちの前記第1および第2機能ユニットが、前記組合せ命令と同じ命令語中で発行された命令の実行と並列に、前記発行スロット内に発行された前記組合せ命令に応答する、請求項1に記載の命令制御式データ処理装置。

**【請求項 3】**

前記機能ユニットのうちの前記第1および第2機能ユニットが、同じ命令実行サイクル内で前記組合せ命令に応答する、請求項1に記載の命令制御式データ処理装置。

**【請求項 4】**

前記命令サイクルをクロック制御するためのクロック回路を含み、前記クロック回路が、命令実行サイクル内で前記組合せ命令を実行する際でも前記機能ユニットのうちの前記第1機能ユニットに適用されるオペランドに応答して前記命令実行サイクル内で前記機能ユニットのうちの前記第2機能ユニットからの結果を生成するのに伴う待ち時間に対応できるのに十分なほど遅い第1のクロック速度と、前記命令サイクル内で前記待ち時間に対応できるには速すぎるが前記サブセットからの命令の待ち時間には対応できる第2のクロック速度とを含む複数の選択可能なクロック速度を有する、請求項3に記載の命令制御式データ処理装置。

**【請求項 5】**

前記命令発行ユニットがさらなる発行スロットを有し、前記レジスタ・ファイルがさらなる読み取りポートを有する命令制御式データ処理装置であって、前記さらなる発行スロットに結合された制御入力を有するさらなる機能ユニットと、前記さらなる読み取りポートに結合されたオペランド入力を含み、前記制御ユニットが、前記さらなる機能ユニットの結果出力を、前記組合せ命令の制御下で前記レジスタ・ファイルをバイパスし、前記組合せ命令の制御下で前記機能ユニットのうちの前記第2機能ユニットのさらなるオペランド入力に送るように構成される、請求項1に記載の命令制御式データ処理装置。

**【請求項 6】**

同じ命令サイクル内で発行される、前記さらなる機能ユニット用のコマンドと、前記機能ユニット・グループ用の前記組合せ命令とを含むVLIW命令を含むプログラムが組み込まれる、請求項5に記載の命令制御式データ処理装置。

**【請求項 7】**

前記制御ユニットが、前記機能ユニットのうちの前記第1機能ユニットが前記組合せ命

10

20

20

30

40

50

令に応答する命令実行サイクルに続く命令実行サイクルで、前記機能ユニットのうちの前記第2機能ユニットに、前記組合せ命令に応答させるように構成される、請求項1に記載の命令制御式データ処理装置。

**【請求項8】**

前記機能ユニットのうちの前記第1機能ユニットの結果が、中間でラッチされずに、前記機能ユニットのうちの前記第1機能ユニットから、前記機能ユニットのうちの前記第2機能ユニットの前記オペランド入力に送られる、請求項7に記載の命令制御式データ処理装置。

**【請求項9】**

機能ユニット・グループを用意すること、

連続した命令を前記グループに発行すること、

前記命令のうちの第1タイプの命令を、それぞれ個々の前記機能ユニットで実行すること、

第2タイプの命令を、連続した前記機能ユニットの第1および第2機能ユニットで実行すること、および

前記第2タイプの前記命令に応答して、前記機能ユニットのうちの第1機能ユニットの結果を、前記機能ユニットのうちの第2機能ユニットのオペランドに送ることを含む、処理タスクを実行する方法。

**【請求項10】**

前記機能ユニットのうちの前記第1および前記第2機能ユニットが、同じ命令実行サイクル内で前記第2タイプの前記命令に応答する方法であって、

第1の速度が、前記機能ユニットのうちの少なくとも2つのカスケードによる組合せ命令の実行が前記第1の速度における命令サイクル内に収まるほど遅く、第2の速度が、前記機能ユニットのうちの1つの機能ユニットによる命令の実行しか前記第2の速度における前記命令実行サイクル内に収まらないほど速く、前記組合せ命令の実行が、前記第2の速度における1命令実行サイクル内に収まらないように、少なくとも前記第1および前記第2の速度から命令サイクル速度を選択すること、および

前記処理タスクを実行するために使用される前記命令を、前記タスクが前記第1の速度で実行されるときは、前記組合せ命令が使用され、前記タスクが前記第2の速度で実行されるときは、前記組合せ命令が、対応する効果を有する前記第1タイプの命令によって置き換えられるように、前記選択された命令サイクル速度に適合させることを含む、請求項9に記載の方法。

**【請求項11】**

それぞれのさらなる機能ユニット用の複数の命令を含む、V L I W命令語の一部である、前記連続した命令を発行すること、

前記第2タイプの前記命令を含む前記命令語中に、前記さらなる機能ユニットのうちのある特定の機能ユニット用のさらなる命令を含むこと、および

前記第2タイプの前記命令に応答して、前記さらなる機能ユニットのうちの前記特定の機能ユニットからの前記さらなる命令のさらなる結果を、前記機能ユニットのうちの前記第2機能ユニットのさらなるオペランド入力に送ることを含む、請求項9に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、命令制御式データ処理装置に関する。

**【背景技術】**

**【0002】**

P C T特許出願公開第W O 0 0 / 6 0 4 5 7号は、V L I W処理装置を開示している。V L I W処理装置は、それぞれ他の機能ユニットと並列に命令を実行可能な複数の機能ユニットを含んでいる。V L I W処理装置は、一般にそれぞれの機能ユニットによって並列に実行するための複数の命令を含む、V L I W命令語を処理する。V L I Wプロセッサは

10

20

30

40

50

、プログラムされた処理タスクの高速な実行を可能にする利点があるが、この利点を得るには、メモリ使用量が多く電力消費が大きいという犠牲を伴う。W000/60457は、VLW処理装置のためのプログラムに必要な命令メモリ・サイズを低減することを目的としている。この目的のために、処理装置は、メモリ内の命令に応答してVLW命令を作る。したがって、メモリからの元の命令は、VLW命令語中の複数の命令に変換されて、異なる機能ユニットで並列に実行される。

#### 【0003】

電力消費が大きいのは、とりわけ、多数の命令を並列に発行する必要があり、また命令が発行されるごとにレジスタ・ファイルにアクセスする必要があることに起因する。これらの問題は、W000/60457によって対処されていない。

10

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0004】

本発明の一目的は、とりわけ、命令制御式処理装置における電力消費を低減することである。

#### 【0005】

本発明の一目的は、とりわけ、特にVLW処理装置における電力消費を低減することである。

#### 【課題を解決するための手段】

#### 【0006】

本発明による装置が請求項1に記載されている。この装置は、発行スロットおよびレジスタ・ファイルのポートに並列に接続され、発行スロットから発行された命令を少なくとも1つのポートからのオペランドを用いて実行し、結果を少なくとも1つのポートに書き込むことを交互に行うための、1つの機能ユニット・グループを含む。この装置は、それら交互の命令に加えて組合せ命令を提供し、その場合、組合せ命令に応答してそのグループの2つ以上の機能ユニットが応答し、組合せ命令に応答して機能ユニットの第1ユニットからの結果が機能ユニットの第2ユニットのオペランド入力に送られる。機能ユニットの第2ユニットの結果が使用されて、組合せ命令の結果が生成される。組合せ命令を使用することにより、所与のタスク用のプログラムを実行中に機能ユニット・グループに発行する必要のある命令数を、低減することができ、これにより消費電力が低減できる。W000/60457とは対照的に、組合せ命令は、個々に発行される必要のある複数の命令に分割されず、1つの発行スロット中に発行される。したがって、この装置は、もちろん同じVLW命令語中で組合せ命令と並列に他の命令を発行することができるけれども、異なる機能ユニットに対して並列に命令を発行する必要性を部分的に回避することにより、VLW処理の理念に部分的に反する。

20

#### 【0007】

一実施形態では、処理装置は、命令サイクルに合わせて選択可能なクロック速度を有する。速いクロック速度を必要としない処理タスクの実行中に使用されるクロック速度を下げるにより、電力消費が低減される。処理タスクを高速で実行する必要があるときは、個々の機能ユニットがすべて1命令サイクル内で命令をちょうど実行できる最大速度まで、クロック速度が上げられる。本発明の一態様によれば、この装置は、2つ以上の機能ユニットが同じ命令サイクル内で組合せ命令に応答し、連続して働き、またクロック速度を、組合せ命令の連続実行が1命令サイクル内に収まらなくなる程、速い速度に上げることができるように構築される。クロック速度がそのようなレベルまで上がると、たとえば、組合せ命令を含まないプログラムのみを実行するか、またはそれぞれ同じタスクを完了するための組合せ命令を使用するプログラムのバージョンとそれを使用しないプログラムのバージョンとを二者択一的に切り換えることにより、あるいは組合せ命令を異なる機能ユニットによって連続したサイクル内で実行される命令に変換することにより、組合せ命令の使用が回避される。

30

#### 【0008】

40

50

このようにして、電力消費をより節減することができる。というのは、装置が低クロック速度で実行される場合、命令を組み合わせて、発行スロットが1命令サイクル内のみアクティブであればよい組合せ命令にすることにより、処理タスクを実行するために発行する必要のある命令の合計数を減らすことができるからである。組合せ命令が通常の命令よりも多くの命令サイクルを使い果たさない場合、組合せ命令の使用により、プログラムの実行に必要とされる時間が低減され、指定された期間内に実行される必要のある処理タスクについて、クロック速度をさらに一層下げることが可能になる。

#### 【0009】

もう1つの実施形態では、処理装置が、並列実行のために、命令語からの命令を並列に発行できる複数の機能ユニットを含むV L I Wプロセッサである。この実施形態では、組合せ命令を受け取る機能ユニット・グループと並列に命令を受け取るさらなる機能ユニットの結果出力から、組合せ命令に応答しました機能ユニットの第1ユニットの結果を受け取る機能ユニットの第2ユニットのオペランド入力への、バイパス結合が提供される。好ましくは、バイパス接続は、複数命令サイクルにわたって機能ユニットにより実行される実行ステージをパイプライン処理するためのラッチを含まない。したがって、1つのグループ用の組合せ命令を、その組合せ命令の実行中に使用されるオペランドを引き渡すある機能ユニット用の別の命令と一緒に含む、V L I W命令語を使用することができる。その結果、十分に遅いクロック速度では、十分な速度をなお維持しながら、発行する必要のある命令数が少なくて済む。

#### 【0010】

さらに他の一実施形態では、組合せ命令の実行が、1命令サイクルを超えて延長してもよい。したがって、組合せ命令を、連続実行が1命令サイクル内に収まらないクロック速度で実行することもできる。一実施形態では、機能ユニットがどちらも組合せ命令に応答するとき、1つの機能ユニットから別の機能ユニットに送られる結果をラッチするために、中間レジスタが提供される。しかし、これには、レジスタによる追加の電力消費が必要とされ、実行が分割される。もう1つの実施形態では、機能ユニット間でレジスタが使用されず、ウェーブ・パイプラインを使用して、1命令サイクルより長い期間の一部分中で1つの機能ユニットから別の機能ユニットに結果が渡される。

#### 【0011】

本発明の上記その他の目的および有利な諸態様は、添付の図面を用いて説明される。

30

#### 【発明を実施するための最良の形態】

#### 【0012】

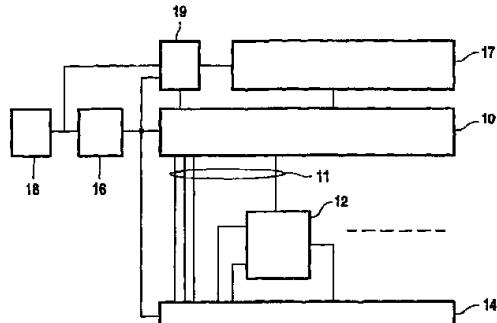

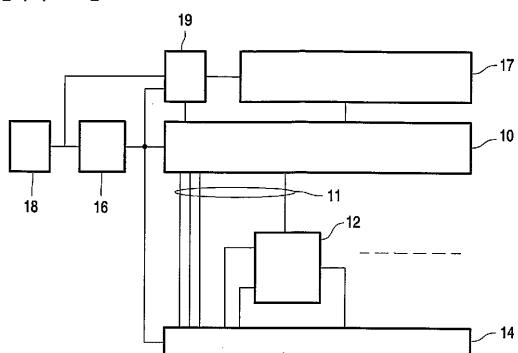

図1に、命令メモリ17、発行スロット11を有する命令発行ユニット10、機能ユニット・グループ12、レジスタ・ファイル14、クロック回路16、クロック速度選択回路18、およびプログラム・カウンタ19を含む処理装置を示す。プログラム・カウンタ19は、命令メモリ17のアドレス入力に結合された出力を有する。命令メモリ17は、命令発行ユニット10に結合された出力を有する。命令発行ユニット10の発行スロット11は、機能ユニット・グループ12に結合されたオペレーションコードと、レジスタ・ファイル14に結合された第1オペランド・レジスタ・アドレスおよび第2オペランド・レジスタ・アドレスおよび結果レジスタ・アドレスとのための出力を含む。機能ユニット・グループ12は、レジスタ・ファイル14の出力に結合されたオペランド入力と、レジスタ・ファイル14の入力に結合された結果出力を有する。

40

#### 【0013】

機能ユニット・グループ12のみが示されているが、複数のグループが並列に存在してもよいことを理解されたい。この場合、命令発行ユニットは、機能ユニット・グループごとに、該当するグループのオペレーションコード入力に結合された出力と、レジスタ・ファイル14に結合されたレジスタ・アドレス出力を有する発行スロットとを含む。また、この場合、レジスタ・ファイル14は、機能ユニット・グループごとに、個別の結果入力ならびに個別のオペランド出力を有する。

#### 【0014】

50

クロック速度選択回路 18 は、クロック回路 16 およびプログラム・カウンタ 19 の制御入力に結合された出力を有する。クロック回路 16 は、命令発行ユニット 10 およびレジスタ・ファイル 14 に結合されたクロック出力を有する。命令発行ユニット 10 は、プログラム・カウンタ 19 に結合されている。動作においては、クロック回路 16 からのクロック信号が、連続した命令サイクルを規定する。通常、それぞれの命令が、各命令サイクルで実行される。各命令サイクルでは、命令発行ユニット 10 が、命令の一部であるコマンドのオペレーションコードを機能ユニット・グループ 12 に発行する。同様に、命令発行ユニット 10 は、各命令サイクル内で命令用のオペランド・レジスタ・アドレスをレジスタ・ファイル 14 に発行し、各命令サイクル内で命令用の結果レジスタ・アドレスをレジスタ・ファイル 14 に発行する。パイプライン処理のため、同じ命令サイクル内で発行されるオペレーションコード、オペランド・レジスタ・アドレス、および結果レジスタ・アドレスは、異なる命令に属することができる。

【 0 0 1 5 】

1 命令サイクル内では、機能ユニット・グループ 12 が、レジスタ・ファイル 14 から受け取った 1 つまたは複数のオペランドを使用して、命令発行ユニット 10 からのオペレーションコードによって識別されるコマンドを実行する。

【 0 0 1 6 】

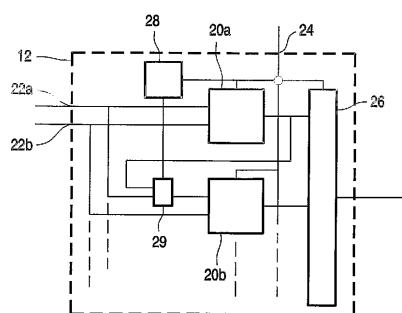

図 2 に、機能ユニット・グループ 12 をより詳細に示す。グループ 12 は、複数の機能ユニット 20 a、b（わかりやすいように 2 つだけ示されているが、もっと多く存在してもよい）を含む。グループ 12 のオペランド入力 22 a、b が、機能ユニット 20 a、b のオペランド入力に結合されている。機能ユニット 20 a、b の結果出力が、出力マルチプレクサ 26 を介してグループ 12 の結果出力に結合されている。オペレーションコード入力 24 が、機能ユニット 20 a、b のオペレーションコード入力および出力マルチプレクサ 26 に結合されている（好ましくは、オペレーションコード 24 が、機能ユニット 20 a、b および出力マルチプレクサ 26 にプリデコーダを介して結合されるが、これはわかりやすくするために示されていない）。

【 0 0 1 7 】

グループ 12 は、制御ユニット 28 および入力マルチプレクサ 29 も含んでいる。入力マルチプレクサ 29 は、そのグループのオペランド入力 22 a に結合されている第 1 の入力と、第 2 機能ユニット 20 b のオペランド入力に結合されている出力とを有する。入力マルチプレクサ 29 の第 2 の入力が、第 1 機能ユニット 20 a の結果出力に結合されている。制御ユニット 28 が、オペレーションコード入力 24 に結合されており、入力マルチプレクサ 29 の選択入力に結合されている出力を有する。

【 0 0 1 8 】

動作においては、受け取られた第 1 タイプのオペレーションコードがそれぞれ、オペレーションコードを実行する機能ユニット 20 a、b のどちらか 1 つを識別する。この第 1 タイプのオペレーションコードの場合、制御ユニット 28 が、入力マルチプレクサ 29 にオペランド入力 22 b からのオペランドを渡させる。識別された機能ユニット 20 a、b が、そのオペランド入力に適用されるオペランドを用いて、オペレーションコードによって識別される処理演算（たとえば ADD、または乗算）を実行する。識別された機能ユニット 20 a、b が、結果を出力する。出力マルチプレクサ 26 は、識別された機能ユニット 20 a、b からの結果を、機能ユニット・グループ 12 の結果出力に渡す。

【 0 0 1 9 】

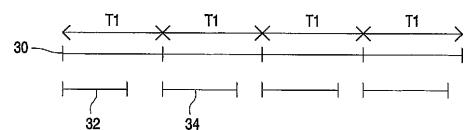

図 3 a に、機能ユニット 20 a、b による演算実行のタイミングの諸側面を示す。最上部において、トレース 30 は、連続した命令サイクルを示す。各命令サイクルは、持続時間 T1 だけ続く。最上行の下には、機能ユニット 20 a、b が実行中に結果を生成するのに必要とされる最小期間 32、34 が示されている。期間 32、34 は、オペレーションコードによって選択される演算の種類と、演算を実行する機能ユニット 20 a、b と、演算において使用されるオペランド・データとに依存し得る。ただし、結果は常に、命令サイクルの終了の前に利用可能になる、すなわちこれらの期間の持続時間は T1 よりも短く

なる。図3aは、1つの機能ユニットでの実行に必要な期間だけを示していることに留意されたい。実際には、演算はパイプライン処理されてもよく、したがって、各命令の処理は、命令フェッチ段階、オペランド・フェッチ段階、実行段階、および結果書込段階を伴っており、中間結果をラッピングした後に、必要であれば、連続した命令サイクルで前記種々の段階が実行される。期間32、34は、実行段階にのみ関係している。

#### 【0020】

オペレーションコードは、機能ユニット20a、bのカスケード演算をもたらす第2タイプのオペレーションコードも含んでいる。第2タイプのオペレーションコードがオペランド入力24に適用されたとき、制御ユニットは、入力マルチプレクサ29に機能ユニットの第1ユニット20aからの結果を機能ユニットの第2ユニット20bのオペランド入力に渡させる。出力マルチプレクサ26は、機能ユニットの第2ユニット20bからの結果を機能ユニット・グループ12の結果出力に渡す。

10

#### 【0021】

第2タイプのオペレーションコードの例として、2乗とオペランドの和の計算用のオペレーションコードがある。

結果 =  $A * A + B$

この例では、グループ12の第1機能ユニット20aは乗算器であり、グループ12の第2機能ユニット20bは加算器である。この演算は、AおよびBをオペランドとして含むレジスタのレジスタ・アドレスを有する。このオペレーションコードに応答して、グループ12の第1機能ユニット20aは、積 $A * A$ を生成する。同じオペレーションコードに応答して、制御ユニット28は、マルチプレクサ29に、積 $A * A$ をオペランドとして、グループ12の第2機能ユニット20bに渡せる。さらに同じオペレーションコードに応答して、グループ12の第2機能ユニット20bは、受け取った積 $A * A$ とオペランドBの合計である $A * A + B$ を生成する。このオペレーションコードは単なる例に過ぎないことを理解されたい。他の演算(たとえば、 $A * A - B$ 、 $A / (A + B)$ など、 $A * B + A$ )用のオペレーションコードが提供されてもよく、このようなオペレーションコードが1つでも複数でもサポートされ得る。

20

#### 【0022】

コマンド内に3つ以上のオペランド・レジスタ・アドレスを含めることにより、または同じレジスタ内に2つ以上のオペランドを含めることにより、より多くのオペランドが利用可能な場合、より複雑な演算を実行することができる。たとえば、オペランドがそれぞれ複素数の実部および虚部を表す、数の対( $\text{Re } A, \text{Im } A$ )および( $\text{Re } B, \text{Im } B$ )を含む場合、組合せ演算は、乗算器機能ユニットに、それぞれ実部( $\text{Re } A * \text{Re } B$ )の積および虚部( $\text{Im } A * \text{Im } B$ )の積を生成するよう指令し、加算器にその積を合計するよう指令する。この場合、グループ12は好ましくは、少なくとも2つの乗算器および1つの加算器を機能ユニットとして含み、また、加算器がオペランドを、オペランド入力22a、bから受け取るか、それとも乗算器から受け取るかを選択する制御ユニット28の制御下にあるマルチプレクサも含む。

30

#### 【0023】

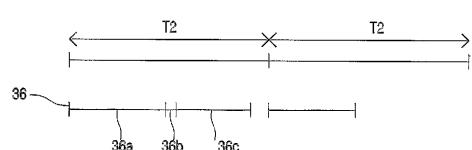

図3bは、第2タイプのオペレーションコードによって選択される演算の実行の実行段階におけるタイミングの諸侧面を示している。この場合、命令サイクルの持続時間がT2である。この演算の結果が利用可能になるまでに必要な期間36の持続時間は、機能ユニットの第1ユニット20aによって必要とされる第1の期間36aの持続時間と、機能ユニットの第1ユニット20aの結果を機能ユニットの第2ユニット20bのオペランド入力に渡す必要のある第2の期間36bの持続時間と、機能ユニットの第2ユニット20bによって必要とされる第3の期間36cの持続時間との和である(より正確には、第2の期間36bの持続時間の代わりに、機能ユニットの第1ユニット20aの出力からの結果を機能ユニットの第2ユニット20bのオペランド入力に渡すのに必要とされる期間の持続時間から、外部のオペランドをこのオペランド入力に渡すのに必要とされる期間の持続時間を引いた差を考慮すべきである。この差は負になることもある)。

40

50

## 【0024】

第2タイプの演算の結果が利用可能になるまでの期間36の全持続時間は、その演算の構成要素である諸演算のために機能ユニット20a、bによって必要とされる期間36a、36cの持続時間よりも長い。それでもやはり、この総持続時間は、1命令サイクルの持続時間T2内に収まるべきである。

## 【0025】

クロック速度選択回路18は、クロック速度、すなわち命令サイクルの持続時間T1またはT2を選択するための信号を、クロック回路16に供給する。好ましくは、クロック速度は、必要な期間内に必要なタスクを実行する能力を損なわずに、できるだけ低く（命令サイクル持続時間ができるだけ長く）設定される。クロック速度を下げるにより、この装置の電力消費が低減される。

10

## 【0026】

選択可能なクロック速度には、第2タイプの命令の持続実行が命令サイクル（持続時間T2）内に収まる遅いクロック速度と、第2タイプの命令の持続実行が命令サイクル（持続時間T1）内に収まらない速いクロック速度が含まれる。クロック速度が遅いクロック速度に設定された場合、タスクは、第2タイプのオペレーションコードをもつ命令を使用して実行される。クロック速度が速いクロック速度に設定された場合、タスクは、たとえば第2タイプのオペレーションコードをもつ各命令を第1タイプのオペレーションコードをもつ2つ以上の命令で置き換えることによって、第2タイプのオペレーションコードをもつ命令を使用せずに実行される。遅いクロック速度で第2タイプのオペレーションコードをもつ命令を使用することにより、タスクを実行するのに必要とされる命令サイクル数が低減される。それによって、実行速度が速くなる。

20

## 【0027】

タスクを実行する際に用いられる命令を適用するためのどんな方法も使用することができる。一実施形態では、命令メモリ17が、同じタスクを実行するための少なくとも2つのプログラムの命令を記憶し、その際に、あるものは第1タイプのオペレーションコードをもつ命令を使用するが、別のものはそのような命令を使用しない。この実施形態では、クロック速度選択回路18は、クロック速度に加えて、たとえばタスクの実行開始時にプログラム・カウンタ19の初期値を設定することにより、該当するプログラムも選択する。

30

## 【0028】

ただし、タスクの実行中、第2タイプのオペレーションコードの使用を回避するために、他の多くの方法を使用することができる。たとえば、設定されているクロック速度に応じて、第2タイプのオペレーションコードをもつプログラム、またはそのタイプのオペレーションコードをもたないプログラムのどちらかにジャンプする命令を実行することができる。同様に、適切な命令を選択するために、選択されたクロック速度に応じて、命令アドレスの物理メモリ・アドレスへの変換を行うことができる。これらの場合には、タスクを実行するプログラム全体の二者択一のバージョン（第2タイプのオペレーションコードがあるものおよびないもの）を提供する必要はない。代わりに、そのような命令を含むプログラムのセクションについてのみ、二者択一のバージョンを提供することができる（この場合、第2タイプのオペレーションコードをもつ命令は、頻繁に実行されるセクションにのみ含まれることが好ましい）。速いクロック速度が選択されている場合、二者択一の命令として、発行ユニットを、第2タイプのオペレーションコードをもつ命令をそのタイプのオペレーションコードをもたない複数の命令に、その場で変換するように構成することもできる。

40

## 【0029】

第2タイプのオペレーションコードは、頻繁に実行される命令をサポートすることが好ましい。

## 【0030】

本発明は、クロック速度選択回路18をもつ一実施形態によって説明されているが、ク

50

ロック速度を、他の方法で、たとえばプログラム・カウンタ値の一部の制御下で、命令がそこから実行されているプログラムのセグメントに応じてクロック速度が設定されるよう、選択することもできることが理解されよう。あるいは、クロック速度を、プログラムからの命令の制御下で、選択することもできることが理解されよう。

【0031】

図2は、いくつかの機能ユニット20a、bが、第2タイプの同じオペレーションコードに応答する一実施形態を示す。さらに、制御ユニット28がこのオペレーションコードに応答し、出力マルチプレクサ26が、応答する機能ユニット20a、bのどれか1つのみからの結果を出力する。ただし、オペレーションコードに対応してどの機能ユニットをアクティブにすべきかを検出し、それらの機能ユニット20a、bをアクティブにする(プリ)デコーダ(図示せず)を使用できることが理解されよう。この場合、(プリ)デコーダは、オペレーションコードが第1タイプである場合、機能ユニット20a、bを命令サイクルあたり1つアクティブにし、オペレーションコードが第2タイプである場合、機能ユニットの組合せをアクティブにする。図に示すように、第2タイプのオペレーションコードに応答してアクティブにされた各機能ユニット20a、bは、第1タイプのオペレーションコードに対して個別に応答することもできる。したがって、命令ユニット20a、bは、効率的に再利用される。ただし、一代替実施形態では、カスケード接続された、第2タイプのオペレーションコードを実行するために使用される機能ユニット20a、bの一部分が、第1タイプのどんなオペレーションコードにも個別に応答しないタイプであってよい。したがって、機能ユニット・グループ12に、あるオーバヘッドを導入する必要がある。

【0032】

入力マルチプレクサ29は1つだけが例として示され、機能ユニット20a、bは2つだけ示されているが、実際には、機能ユニット20a、bの出力間、またはグループ12における追加の機能ユニット(図示せず)間に、より複雑な接続網を備えることができることが理解されよう。

【0033】

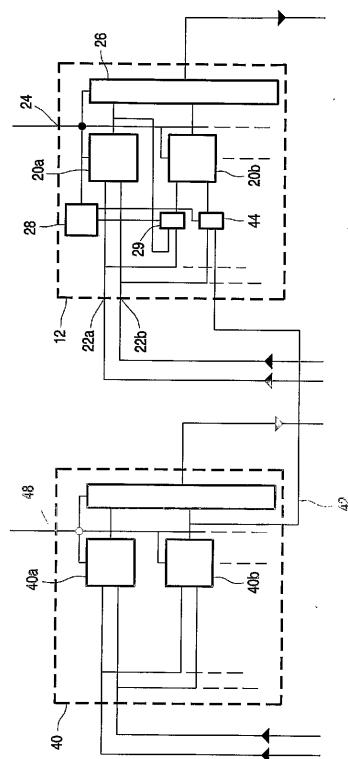

図4は、本発明のさらなる一態様を実装した、図1に示す処理装置で使用される機能ユニットの2つのグループ12、40を示す。各グループ12、40は、命令発行ユニット(図示せず)からの発行スロットにそれぞれ結合され、かつレジスタ・ファイル(図示せず)の読み取りおよび書き込みポートに結合された演算選択入力24、48を有する。したがって、この装置は、異なるグループ12、40について実質的に独立に選択可能な複数のコマンドを含む、VLIWプロセッサ(超長命令語プロセッサ)である。グループ12の第1グループが図2に示すとおりに配置されている。ただし、さらなるマルチプレクサ44が追加されており、その第1の入力に、グループ12の第2のオペランド入力22bが結合されている。さらなるマルチプレクサ44の出力が、第2機能ユニット20bのオペランド入力に結合されている。さらなるマルチプレクサ44は、制御ユニット28に結合された制御入力を有する。

【0034】

機能ユニット40の第2グループは、いくつかの機能ユニット40a、40bを含んでいる。第2グループ40の機能ユニット40bの1つの出力が、バイパス接続42を介して、さらなるマルチプレクサ44の第2の入力に結合されている。

【0035】

動作においては、制御装置28は、組合せ命令のオペレーションコードが機能ユニット・グループ12に発行されるとき、そのことを認識する。その場合、制御ユニット28は、マルチプレクサ29、44に、グループ12の第1機能ユニット20aからおよびさらなるグループ40の機能ユニット40bからのオペランドを、グループ12の第2機能ユニット20bのオペランド入力に渡させる。グループ12の第1および第2の機能ユニット20a、bはどちらも組合せ命令に応答し、第1機能ユニット20aはグループ12のオペランド入力22a、bからオペランドを受け取り、マルチプレクサ26は、第2機能

ユニット 20 b からの結果をグループ 12 用に提供されているレジスタ・ファイルの書き込みポートに渡す。

【 0036 】

命令メモリ 17 に記憶されているプログラムは、グループ 12 用のコマンドとグループ 40 用のコマンドを含む命令を含んでいる。この命令は、第 1 グループ 12 用の組合せ命令を含んでおり、第 2 グループ 40 用のコマンドは、第 2 グループの第 2 機能ユニット 40 b をアクティブにするオペレーションコードを含んでいる。したがって、この命令に応答して、第 1 グループ 12 の第 1 機能ユニット 20 a と第 2 グループ 40 の第 2 機能ユニット 40 b はどちらも結果を生成し、その結果がグループ 12 の第 2 機能ユニット 20 b でオペランドとして使用される。第 2 グループ 40 の第 2 機能ユニット 40 b からの結果は、グループ 12 と 40 の間でバイパス接続 42 を介して渡される。マルチプレクサ 29、44 は、その結果をオペランドとして第 1 グループ 12 の第 2 機能ユニット 20 b に渡す。

【 0037 】

一例として、2 対のオペランドの積が加算される乗算 - 加算演算に、このタイプの命令を使用することができる。

結果 =  $A * B + C * D$

この例では、第 1 グループ 12 の第 1 機能ユニット 20 a が乗算器であり、第 2 グループ 40 の第 2 機能ユニット 40 b が乗算器であり、また第 1 グループ 12 の第 2 機能ユニット 20 b が加算器である。この命令は、第 1 グループ 12 に発行される乗算 - 加算コマンド（組合せコマンド）、および第 2 グループ 40 に発行される乗算コマンドを含んでいる。乗算 - 加算コマンドは、A および B をオペランドとして含むレジスタのレジスタ・アドレスを有し、乗算コマンドは、C および D をオペランドとして含むレジスタのアドレスを有する。この命令に応答して、第 1 グループ 12 の第 1 機能ユニット 20 a および第 2 グループ 40 の第 2 機能ユニット 40 b が、それぞれ積  $A * B$  および  $C * D$  を生成する。同じ乗算 - 加算命令に応答して、制御ユニット 28 は、マルチプレクサ 29、44 に、これらの積をオペランドとして第 1 グループ 12 の第 2 機能ユニット 20 b に渡せる。さらに同じ乗算 - 加算命令に応答して、第 1 グループ 12 の第 2 機能ユニット 20 b が、受け取った積  $A * B$  および  $C * D$  の和  $A * B + C * D$  を生成する。

【 0038 】

このタイプの乗算と加算の組合せは、たとえば複素数の乗算で頻繁に発生する命令組合せであり、したがって、この命令により、このタイプの演算のために発行する必要のある命令数の大幅な節減が実現される。ただし、本発明はこの命令に限定されないことを理解されたい。たとえば、類似の技法を乗算と減算に適用して  $A * B - C * D$  を計算することも、あるいはあるプログラムで発生する演算の他のどんな組合せに適用することもできる。この装置は、ただ 1 つの組合せ命令用のオペレーションコードをサポートすることも、あるいは複数の組合せ命令用のオペレーションコードをサポートすることもできる。

【 0039 】

プログラムを図 4 の実施形態の機能ユニットを用いて実行する場合、命令サイクル速度が速すぎて、連続した第 2 グループ 40 の第 2 機能ユニット 40 b および第 1 グループ 12 の第 2 機能ユニット 20 b の遅延に対応できないときは、そのプログラムを、図 2 のコンテキストで論じたように、組合せ命令を排除するように適合させることができることに留意されたい。この組合せ命令により、第 1 グループ 12 の第 2 機能ユニット 20 b 用のオペランドとして使用するために、（第 2 グループ 40 の第 2 機能ユニット 40 b の代わりに）異なる機能ユニットからの結果を選択することができる。これらの異なる機能ユニットは、1 つのグループ 40 の一部でも、異なる複数のグループの一部でもよい。第 2 グループ 40 は、本発明から逸脱せずに、ただ 1 つの機能ユニット（第 2 機能ユニット 40 b）を含むことができる。

【 0040 】

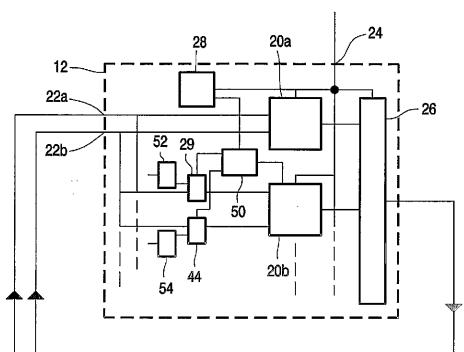

図 5 は、この装置で使用される代替機能ユニット・グループ 12 を示す。これまでに示

10

20

30

40

50

した実施形態においては、組合せ演算が1つの命令サイクル内で実行される。図5の実施形態では、複数の命令サイクルが使用される。機能ユニット・グループ12は、制御ユニット28に結合された入力と、マルチプレクサ29、44および第2機能ユニット20bの制御入力に結合された出力をもつ制御レジスタ50を含んでいる。マルチプレクサ29、44の第1のデータ入力がオペランド入力22a、bに接続されている。結果レジスタ52、54は、マルチプレクサ29、44の第2のデータ入力に結合された出力を備えている。結果レジスタ52、54の入力は、グループ12の1つまたは複数の機能ユニット(たとえば20a)の結果出力に、かつ/または他のグループ(図示せず)の1つまたは複数の機能ユニットの結果出力に結合されている。見やすいように、これらの入力の接続は示されていない。

10

## 【0041】

動作においては、制御ユニット28は、制御レジスタ50に、マルチプレクサ29、44および第1グループ12の第2機能ユニット20bを制御するための情報をロードさせることによって、第1の命令サイクル内で実行すべく発行された組合せ命令に応答する。この情報により、第1の命令サイクルに続く第2の命令サイクルで、マルチプレクサ29、44および第1グループ12の第2機能ユニット20bが制御される。第2の命令サイクルでは、結果レジスタ52、54にラッチされた結果が、オペランドとしてグループ12の第2機能ユニット20bに渡され、この第2機能ユニット20bは、第2の命令サイクルにおける組合せ命令に示されているコマンドのその部分を実行するための制御信号を受け取る。それに応答して、第2の機能ユニット20bは、第2の命令サイクルの終わりに結果を生成する。

20

## 【0042】

このようにして、第2の命令サイクルで、第2機能ユニット20bによる組合せ命令の一部を実行するのと並列して、グループ12で次の命令を実行することができる。たとえば、第1の命令サイクルで  $A * B - C * D$  を計算する第1の命令の実行を開始し、次の命令サイクルで  $A * D + B * C$  を計算する第2の命令を開始することもできる。したがって、2つの数  $A + iC$  および  $B + iD$  の実部と虚部が、2つの命令を用いて計算される。

30

## 【0043】

もちろん、組合せ命令の結果と次の命令の結果の間で矛盾が発生するのを回避すべきである。これは、様々な方法で実現することができる。一実施形態では、次の命令が、第2の命令サイクルにおいて結果を生成しない、命令のサブセットから選択される(たとえば、別の組合せ命令、あるいはNOP命令)。この実施形態では、制御レジスタ50はまた、第2機能ユニット20bからの結果を渡すようにマルチプレクサ26を制御する。もう1つの実施形態では、次の命令に応答する機能ユニットからの結果と並列に、バイパス・レジスタ(図示せず)を使用して第2機能ユニット20bの結果を渡すことができる。

## 【0044】

図5の実施形態では、命令サイクル速度が速すぎて、1つの命令サイクルにおける第1および第2の機能ユニット20a、bの遅延に対応できないときは、プログラムを適合させる必要はないことに留意されたい。

40

## 【0045】

図5は、マルチプレクサ29、44の前に挿入された結果レジスタ52、54を示しているが、ウェーブ・パイプラインが使用される場合、これらのレジスタ52、54を省略することもできる。この場合は、機能ユニット20a、b内の伝播遅延を利用して、第2機能ユニット20bおよび次の命令を実行する機能ユニットの出力に、組合せ命令および次の命令からの結果が同時に存在できるようにする。他の一実施形態では、第1グループ12の第2機能ユニット20bによって使用される結果を生成する特定の機能ユニットの前に、レジスタを設けることができる。これらのレジスタは、これらの機能ユニットのオペランドをラッチすることによって組合せ命令に応答し、これらのオペランドが、第1の命令サイクル内に入力22a、bから直接適用された後、後続の命令サイクル内でもその特定の機能ユニットに供給されるように構成される。

50

## 【0046】

本発明は、同じコマンドに応答する連続した2つの機能ユニットの連続実行を伴う組合せ命令を用いて説明されてきたが、連続した非常に多くの数の機能ユニットを伴う組合せ命令を提供することもできることが理解されよう。

## 【図面の簡単な説明】

## 【0047】

【図1】処理装置を示す図である。

【図2】機能ユニット・グループを示す図である。

【図3】タイミングの諸態様を示す図である。

10

【図4】複数の機能ユニット・グループを示す図である。

【図5】さらなる機能ユニット・グループを示す図である。

## 【図1】

FIG. 1

FIG. 3A

FIG. 3B

## 【図2】

FIG. 2

【図4】

FIG. 4

【図5】

FIG. 5

## 【国際調査報告】

60600620019

## INTERNATIONAL SEARCH REPORT

Int'l. Application No.

PCT/IB2004/050964

|                                     |           |          |          |          |

|-------------------------------------|-----------|----------|----------|----------|

| A. CLASSIFICATION OF SUBJECT MATTER |           |          |          |          |

| IPC 7                               | G06F9/318 | G06F9/38 | G06F1/32 | G06F9/38 |

|                                     | G06F9/30  | G06F9/34 |          | G06F1/32 |

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 G06F

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the International search (name of data base and, where practical, search terms used)

EPO-Internal, INSPEC, IBM-TDB

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                          | Relevant to claim No. |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | US 5 923 871 A (GORSHTEIN ET AL)<br>13 July 1999 (1999-07-13)<br>column 2, line 47 - column 3, line 15<br>column 9, line 10 - line 14<br>column 11, line 57 - column 13, line 37;<br>figure 8                                                                                                                                                                               | 1,2,5-9,<br>11        |

| A        |                                                                                                                                                                                                                                                                                                                                                                             | 3,4,10                |

| A        | JACOBSON Q ET AL: "Instruction<br>pre-processing in trace processors"<br>HIGH-PERFORMANCE COMPUTER ARCHITECTURE,<br>1999. PROCEEDINGS. FIFTH INTERNATIONAL<br>SYMPOSIUM ON ORLANDO, FL, USA 9-13 JAN.<br>1999, LOS ALAMITOS, CA, USA, IEEE COMPUT.<br>SOC, US, 9 January 1999 (1999-01-09),<br>pages 125-129, XP010321129<br>ISBN: 0-7695-0004-8<br>page 127, paragraph 2.3 | 1-11                  |

Further documents are listed in the continuation of box C. Patent family members are listed in annex.

## \* Special categories of cited documents:

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*B\* earlier document but published on or after the International filing date

- \*L\* document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the International filing date but later than the priority date claimed

- \*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*Z\* document member of the same patent family

|                                                                                                                                                                                        |                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the International search                                                                                                                              | Date of mailing of the International search report |

| 1 September 2005                                                                                                                                                                       | 12/09/2005                                         |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epc nl,<br>Fax. (+31-70) 340-3016 | Authorized officer<br>Thibaudeau, J 18. 5. 2006    |

2

| INTERNATIONAL SEARCH REPORT                          |                                                                                                                                                            | Inte<br>and Application No<br>PCT/IB2004/050964 |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                            |                                                 |

| Category *                                           | Citation of document, with indication, where appropriate, of the relevant passages                                                                         | Relevant to claim No.                           |

| A                                                    | US 6 442 701 B1 (HURD LINDA L)<br>27 August 2002 (2002-08-27)<br>column 1, line 66 – column 2, line 26                                                     | 1-11                                            |

| A                                                    | US 5 829 031 A (LYNCH ET AL)<br>27 October 1998 (1998-10-27)<br>column 1, line 59 – column 3, line 16<br>column 7, line 44 – column 8, line 4;<br>figure 2 | 1-11                                            |

3

| INTERNATIONAL SEARCH REPORT<br>Information on patent family members |                  |                         |    | Int'l Application No<br>PCT/IB2004/050964 |  |

|---------------------------------------------------------------------|------------------|-------------------------|----|-------------------------------------------|--|

| Patent document cited in search report                              | Publication date | Patent family member(s) |    | Publication date                          |  |

| US 5923871                                                          | A 13-07-1999     | WO 9806030              | A1 | 12-02-1998                                |  |

| US 6442701                                                          | B1 27-08-2002    | NONE                    |    |                                           |  |

| US 5829031                                                          | A 27-10-1998     | WO 9731311              | A2 | 28-08-1997                                |  |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,M,A,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100096921

弁理士 吉元 弘

(74)代理人 100103263

弁理士 川崎 康

(74)代理人 100118876

弁理士 岡澤 順生

(72)発明者 カルロス、ア・アルバ、ピント

オランダ国5656、アーアー、アンドーフェン、ケアオブ、プロフ・ホルストラーン、6

(72)発明者 バラクリシュナン、スリニバサン

オランダ国5656、アーアー、アンドーフェン、ケアオブ、プロフ・ホルストラーン、6

(72)発明者 ラマナサン、セトウラマン

オランダ国5656、アーアー、アンドーフェン、ケアオブ、プロフ・ホルストラーン、6

Fターム(参考) 5B013 AA11 AA18 DD02 DD04

5B033 AA03 AA05 AA13 AA14 BC01 BE05