(10) **DE 10 2015 109 842 A1 2015.12.24**

(12)

## Offenlegungsschrift

(21) Aktenzeichen: **10 2015 109 842.3**

(22) Anmeldetag: **19.06.2015**

(43) Offenlegungstag: **24.12.2015**

(51) Int Cl.: **H01L 21/8246 (2006.01)**

**H01L 21/8234 (2006.01)**

**H01L 27/112 (2006.01)**

**H01L 27/085 (2006.01)**

(30) Unionspriorität:

**14/309,968**

**20.06.2014 US**

(72) Erfinder:

**Bertrams, Thomas, 01097 Dresden, DE; Feick, Henning, 01099 Dresden, DE; Kaemmer, Kerstin, 01445 Radebeul, DE; Schmeide, Matthias, 01465 Langebrück, DE; Storbeck, Olaf, 01109 Dresden, DE**

(71) Anmelder:

**Infineon Technologies AG, 85579 Neubiberg, DE**

(74) Vertreter:

**Viering, Jentschura & Partner mbB Patent- und Rechtsanwälte, 01099 Dresden, DE**

Prüfungsantrag gemäß § 44 PatG ist gestellt.

**Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen**

(54) Bezeichnung: **Verfahren zum Bearbeiten eines Trägers, Träger und Feldeffekttransistorstruktur mit geteiltem Gate**

(57) Zusammenfassung: Gemäß verschiedenen Ausführungsformen kann ein Verfahren zum Bearbeiten eines Trägers (102) enthalten: Dotieren eines Trägers (102) mit Fluor, so dass eine erste Oberflächenregion des Trägers (102) fluordotiert ist und eine zweite Oberflächenregion des Trägers (102) frei von der Fluordotierung und/oder weniger fluordotiert als die erste Oberflächenregion des Trägers (102) ist; und Oxidieren des Trägers (102) um eine erste Gateoxidschicht (104a) von der ersten Oberflächenregion des Trägers (102) mit einer ersten Dicke und gleichzeitig von der zweiten Oberflächenregion des Trägers (102) mit einer zweiten Dicke, die sich von der ersten Dicke unterscheidet, zu wachsen.

**Beschreibung**

**[0001]** Verschiedene Ausführungsformen betreffen im Allgemeinen ein Verfahren zum Bearbeiten eines Trägers, einen Träger und eine Feldeffekttransistorstruktur mit geteiltem Gate.

**[0002]** Im Allgemeinen kann ein programmierbarer Nur-Lese-Speicher(PROM) oder ein feldprogrammierbarer Nur-Lese-Speicher(FPROM) oder ein einmalig programmierbarer (OTP) nicht flüchtiger Speicher (NVM) in der Halbleitertechnologie durch eine Sicherung oder eine sogenannte Anti-Schmelzsicherung hergestellt werden. PROMs, FPROMs oder OTP NVMs können in einer digitalen elektronischen Vorrichtung zum Speichern permanenter Daten, z.B. in Mikrosteuerungen, drahtlosen Kommunikationsvorrichtungen, Mobiltelefonen, Tablets, Hochfrequenzidentifizierungsetiketten, medizinischen Vorrichtungen und verschiedenen anderen elektronischen Verbrauchsgütern und elektronischen Automobilprodukten verwendet werden. Die Daten können in einen PROM, einen FPROM oder einen OTP NVM nach der Herstellung, z.B. vor Ort oder nach dem Test, mit zum Beispiel einer geeigneten Programmierungsvorrichtung programmiert werden. Ein auf einer Anti-Schmelzsicherung beruhender einmalig programmierbarer (OTP) nicht flüchtiger Speicher (NVM) kann mit einer einzelnen Feldeffekttransistorstruktur (1T) ausgeführt werden, die in einer Standard-Logik CMOS-Technologie hergestellt ist, wobei die einzelne Feldeffekttransistorstruktur eine geteilte Gate-Struktur enthält, die die Anti-Schmelzsicherung (Antifuse) bereitstellt.

**[0003]** Gemäß verschiedenen Ausführungsformen kann ein Verfahren zum Bearbeiten eines Trägers vorgesehen sein, wobei das Verfahren enthält: Dotieren eines Trägers mit Fluor, so dass eine erste Oberflächenregion des Trägers fluordotiert ist und eine zweite Oberflächenregion des Trägers frei von der Fluordotierung ist oder weniger fluordotiert als die erste Oberflächenregion ist; und Oxidieren des Trägers, um eine erste Gateoxidschicht von der ersten Oberflächenregion des Trägers mit einer ersten Dicke und gleichzeitig von der zweiten Oberflächenregion des Trägers mit einer zweiten Dicke, die sich von der ersten Dicke unterscheidet, zu wachsen.

**[0004]** In einer Ausgestaltung kann das Verfahren des Weiteren aufweisen ein teilweises Entfernen des ersten Gateoxids, um die erste Oberflächenregion neben einem verbleibenden Abschnitt des ersten Gateoxids freizulegen. In noch einer Ausgestaltung kann das Verfahren des Weiteren aufweisen ein Wachsen einer Oxidschicht über der freigelegten ersten Oberflächenregion des Trägers und über dem verbleibenden Abschnitt des ersten Gateoxids. In noch einer Ausgestaltung kann ein Wachsen einer Oxidschicht ein Oxidieren des Trägers aufwei-

sen, um ein drittes Gateoxid von der freigelegten ersten Oberflächenregion des Trägers zu wachsen und mit dem Wachsen des übrigen Abschnitts des ersten Gateoxids fortzufahren. In noch einer Ausgestaltung kann ein Wachsen einer Oxidschicht ein Oxidieren des Trägers aufweisen, um mit dem Wachsen des zweiten Gateoxids fortzufahren. In noch einer Ausgestaltung kann ein Wachsen einer Oxidschicht ein Oxidieren des Trägers aufweisen, um ein zusätzliches Gateoxid von einer dritten Oberflächenregion des Trägers zu wachsen. In noch einer Ausgestaltung kann das Verfahren des Weiteren aufweisen ein Bilden einer Source/Drain-Region im Träger neben der ersten Oberflächenregion und Bilden einer elektrisch leitenden Gate-Struktur über der Oxidschicht, um eine Transistorstruktur mit geteiltem Gate vorzusehen. In noch einer Ausgestaltung kann ein Dotieren eines Trägers mit Fluor ein Vorsehen einer Fluordotierungskonzentration in der ersten Oberflächenregion größer als etwa  $10^{14} \text{ cm}^{-3}$  aufweisen.

**[0005]** In verschiedenen Ausführungsbeispielen wird ein Träger bereitgestellt, aufweisend: eine erste Trägerregion, eine zweite Trägerregion und eine dritte Trägerregion, die jeweils nebeneinander liegen; einen ersten Feldeffekttransistor in der ersten Trägerregion, wobei der erste Feldeffekttransistor eine erste Einzelschicht-Gate-Isolation mit einer ersten Dicke aufweist; einen zweiten Feldeffekttransistor in der zweiten Trägerregion, wobei der zweite Feldeffekttransistor eine erste Doppelschicht-Gate-Isolation mit einer zweiten Dicke aufweist; und eine Feldeffekttransistorstruktur mit geteiltem Gate in der dritten Trägerregion; wobei die Feldeffekttransistorstruktur mit geteiltem Gate aufweist: eine erste geteilte Gate-Region und eine zweite geteilte Gate-Region; eine zweite Doppelschicht-Gate-Isolation in der ersten geteilten Gate-Region und eine zweite Einzelschicht-Gate-Isolation in der zweiten geteilten Gate-Region; wobei die zweite Doppelschicht-Gate-Isolation eine dritte Dicke aufweist, die größer als die zweite Dicke ist und die zweite Einzelschicht-Gate-Isolation eine vierte Dicke gleich oder kleiner als die erste Dicke aufweist.

**[0006]** In einer Ausgestaltung kann der Träger zumindest einer von p-Typ dotiert mit Akzeptoren von Gruppe III-Elementen oder n-Typ dotiert mit Donoren von Gruppe V-Elementen sein. In noch einer Ausgestaltung kann die dritte Trägerregion fluordotiert sein und die erste Trägerregion und die zweite Trägerregion können frei von Fluordotierung und/oder weniger fluordotiert als die dritte Oberflächenregion sein. In noch einer Ausgestaltung kann die erste Dicke der ersten Einzelschicht-Gate-Isolation kleiner als etwa 3,5 nm sein. In noch einer Ausgestaltung kann die zweite Dicke der ersten Doppelschicht-Gate-Isolation größer als etwa 3,5 nm sein. In noch einer Ausgestaltung kann das Verhältnis der dritten Dicke der zweiten Doppelschicht-Gate-Isolation zur vierten Dicke der zweiten Einzelschicht-Gate-Isolation größer

als etwa 2 sein. In noch einer Ausgestaltung kann die Feldeffekttransistorstruktur mit geteiltem Gate als eine einmalig programmierbare Vorrichtung konfiguriert sein, wobei die zweite geteilte Gate-Region den Programmierungsbereich vorsieht.

**[0007]** In verschiedenen Ausführungsbeispielen wird eine Feldeffekttransistorstruktur mit geteiltem Gate bereitgestellt, aufweisend: einen Kanal, der eine erste Body-Region und eine zweite Body-Region aufweist, eine erste geteilte Gate-Isolationsschichtstruktur, die über einer ersten Body-Region des Kanals angeordnet ist und eine erste Dicke hat, eine zweite geteilte Gate-Isolationsschichtstruktur, die über einer zweiten Body-Region des Kanals angeordnet ist und eine zweite Dicke hat, wobei die zweite Dicke kleiner als die erste Dicke ist; ein Gate, das einen ersten Gate-Abschnitt aufweist, der über der ersten geteilten Gate-Isolationsschichtstruktur angeordnet ist, und einen zweiten Gate-Abschnitt, der über der zweiten geteilten Gate-Isolationsschichtstruktur angeordnet ist; wobei eine elektrische Leitfähigkeit des zweiten Gate-Abschnitts größer ist als die elektrische Leitfähigkeit des ersten Gate-Abschnitts.

**[0008]** In einer Ausgestaltung kann der erste Gate-Abschnitt ein Halbleitermaterial mit einer ersten Dotierungskonzentration aufweisen und der zweite Gate-Abschnitt kann ein Halbleitermaterial mit einer zweiten Dotierungskonzentration aufweisen, wobei die zweite Dotierungskonzentration größer ist als die erste Dotierungskonzentration. In noch einer Ausgestaltung kann die erste geteilte Gate-Isolationsschichtstruktur eine Doppelschicht-Gate-Isolation aufweisen, wobei die erste Dicke im Bereich von etwa 4 nm bis etwa 10 nm liegt und die zweite geteilte Gate-Isolationsschichtstruktur kann eine Einzelschicht-Gate-Isolation aufweisen, wobei die zweite Dicke im Bereich von etwa 1 nm bis etwa 3 nm liegt. In noch einer Ausgestaltung kann das Verhältnis der ersten Dicke zur zweiten Dicke größer als etwa 2 ist. In noch einer Ausgestaltung kann die Feldeffekttransistorstruktur mit geteiltem Gate als eine einmalig programmierbare Sicherung konfiguriert sein, wobei die zweite geteilte Gate-Region den Programmierungsbereich bereitstellt.

**[0009]** In den Zeichnungen beziehen sich gleiche Bezugszeichen allgemein in allen verschiedenen Ansichten auf dieselben Teile. Die Zeichnungen sind nicht unbedingt im Maßstab, vielmehr liegt der Schwerpunkt stattdessen allgemein auf einer Veranschaulichung der Prinzipien der Erfindung. In der folgenden Beschreibung sind verschiedene Ausführungsformen der Erfindung unter Bezugnahme auf die folgenden Zeichnungen beschrieben, von welchen:

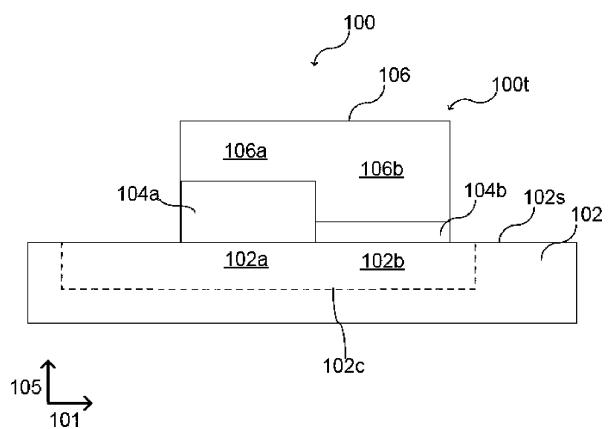

**[0010] Fig. 1** eine schematische Querschnittsansicht einer Feldeffekttransistorstruktur mit geteiltem

Gate auf einem Träger gemäß verschiedenen Ausführungsformen zeigt;

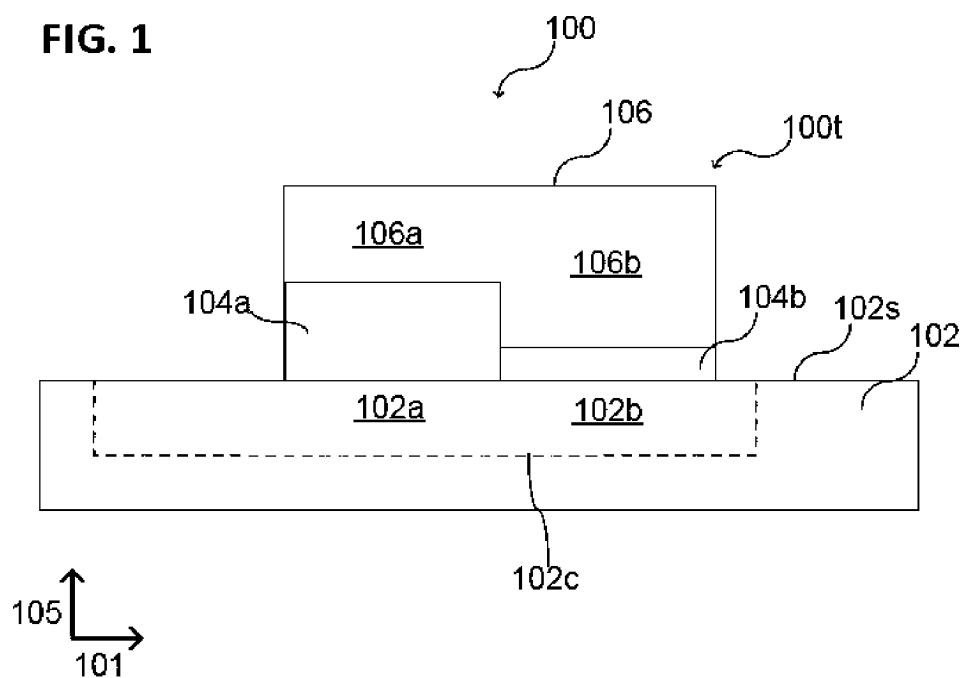

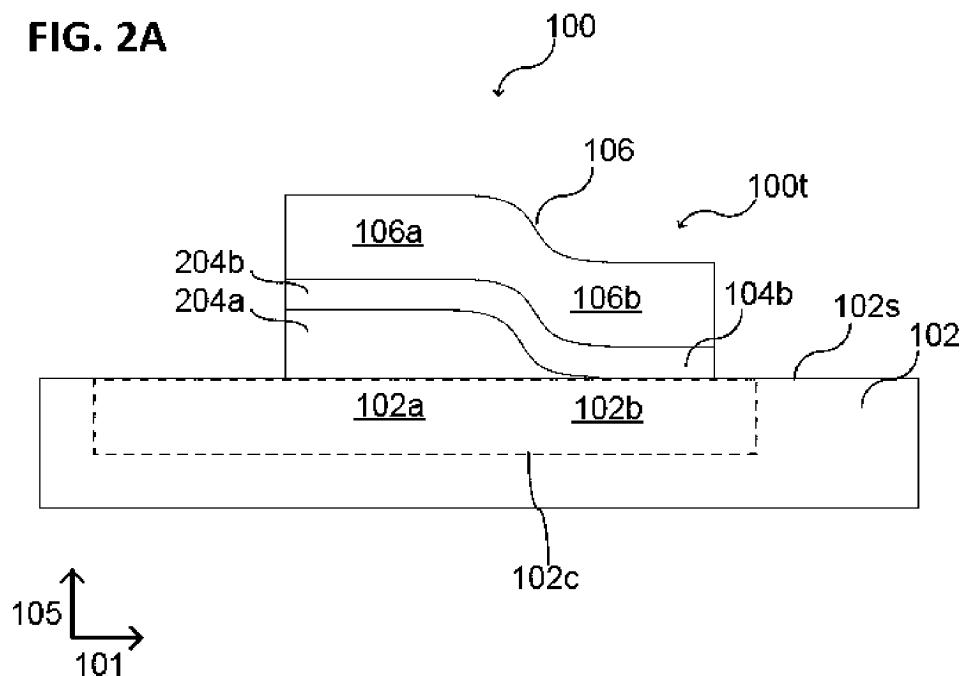

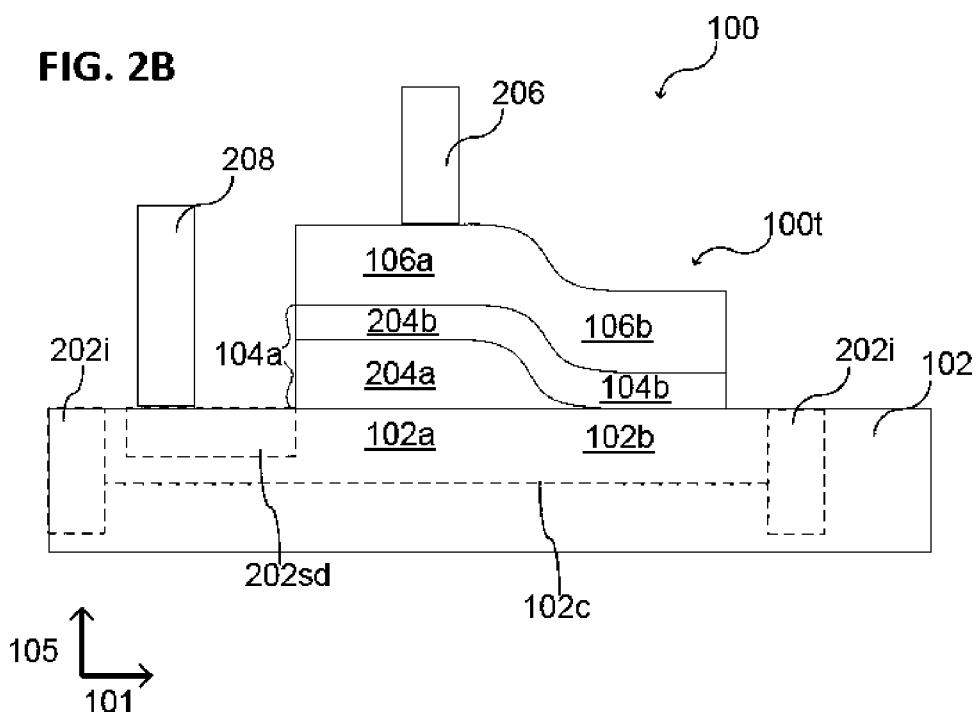

**[0011] Fig. 2A** bis **Fig. 2C** jeweils eine schematische Querschnittsansicht einer Feldeffekttransistorstruktur mit geteiltem Gate auf einem Träger gemäß verschiedenen Ausführungsformen zeigen;

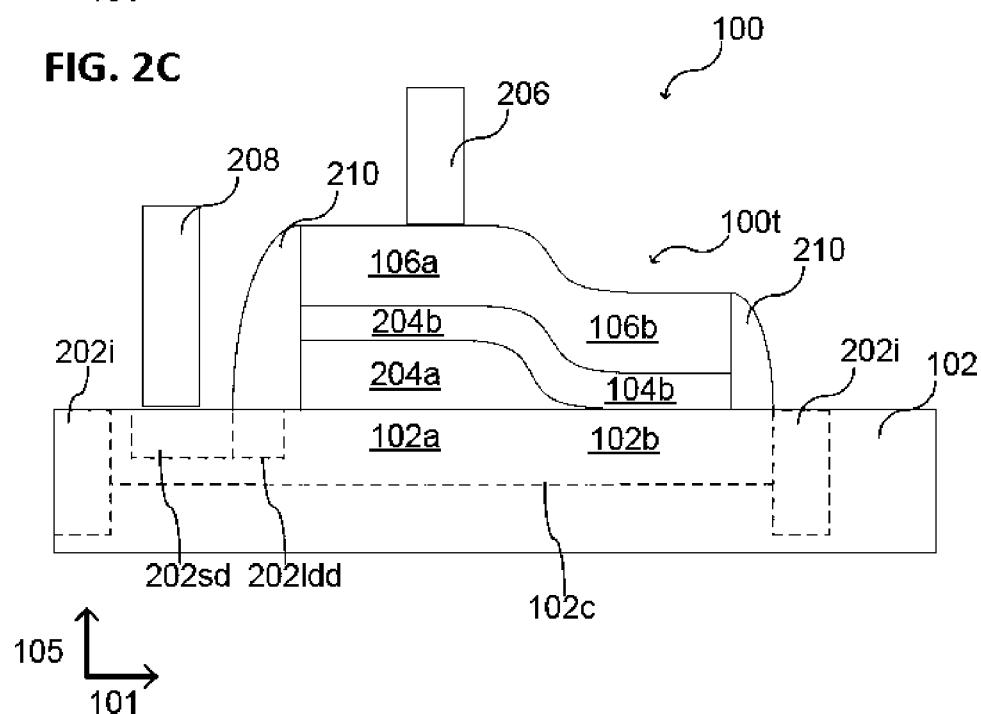

**[0012] Fig. 3** ein schematisches Ablaufdiagramm eines Verfahrens zum Bearbeiten eines Trägers gemäß verschiedenen Ausführungsformen zeigt;

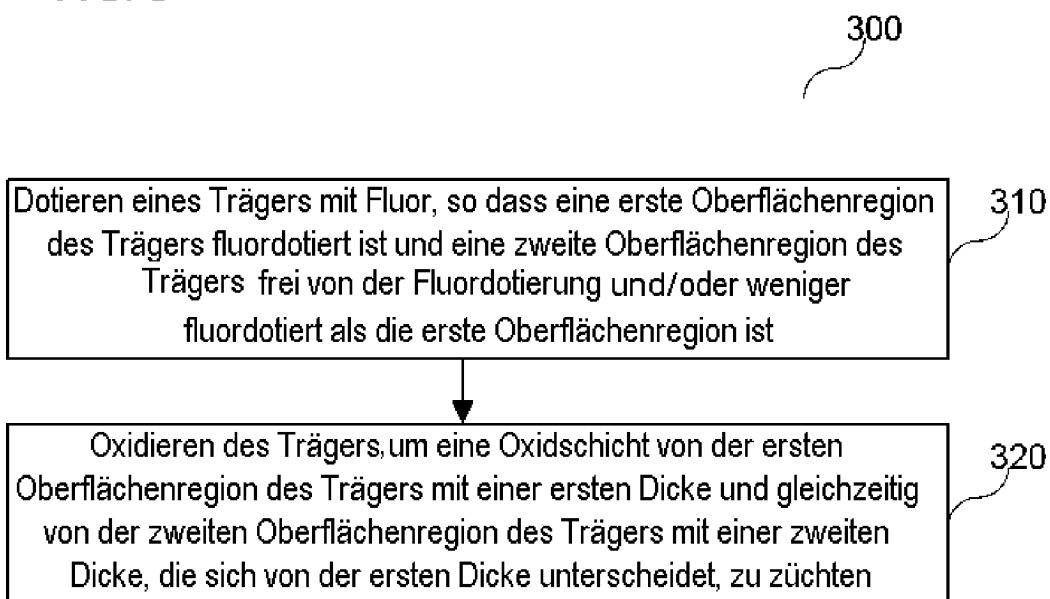

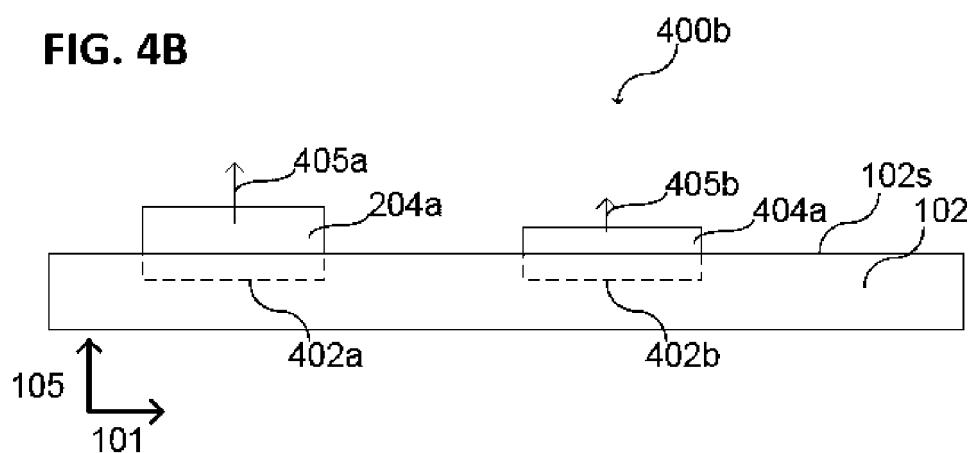

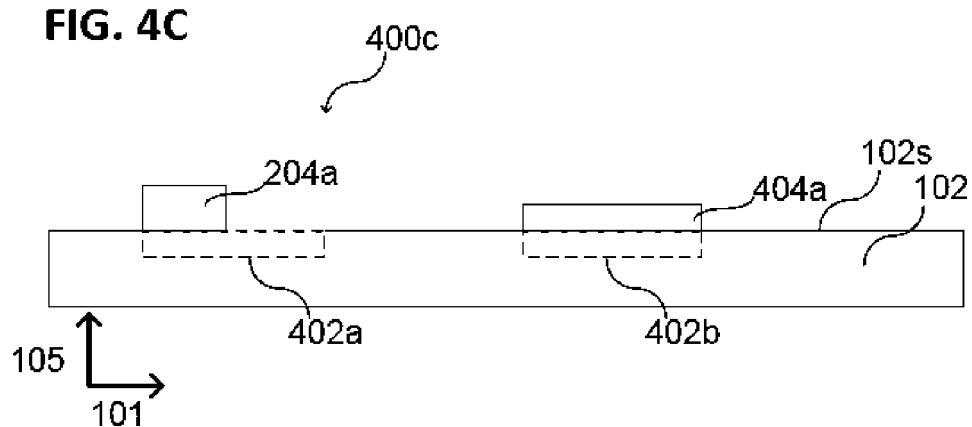

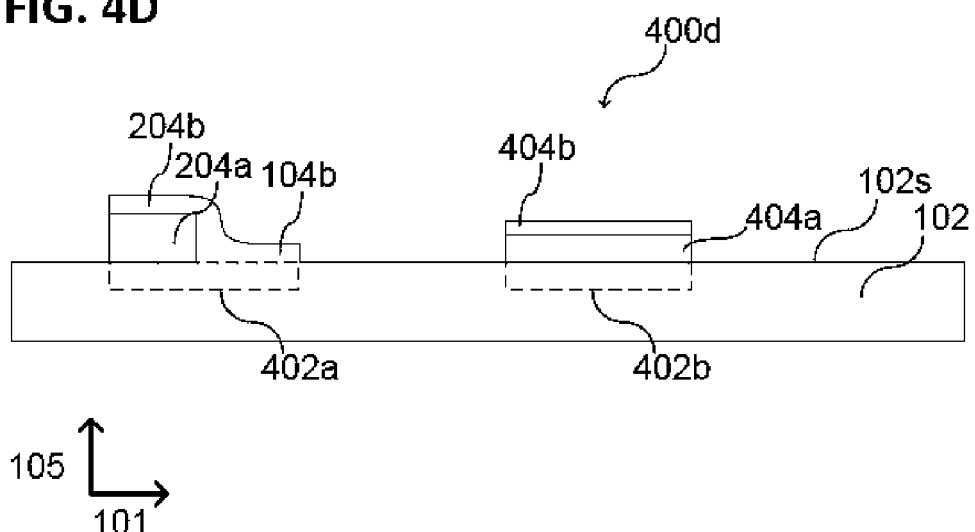

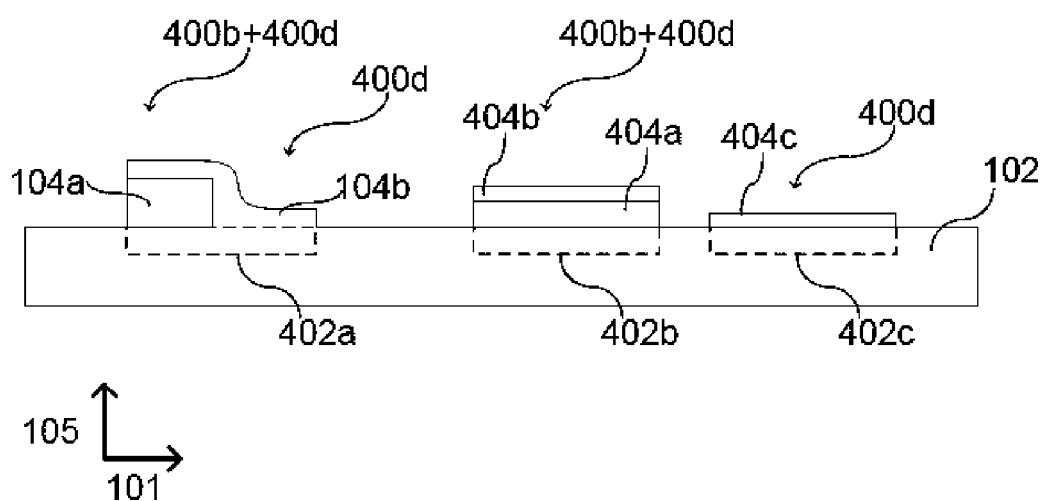

**[0013] Fig. 4A** bis **Fig. 4E** jeweils eine schematische Querschnittsansicht einer Feldeffekttransistorstruktur mit geteiltem Gate auf einem Träger während der Herstellung gemäß verschiedenen Ausführungsformen zeigen;

**[0014] Fig. 5** einen schematischen Querschnitt eines Trägers gemäß verschiedenen Ausführungsformen zeigt;

**[0015] Fig. 6** eine schematische Schnittansicht einer Feldeffekttransistorstruktur mit geteiltem Gate und ein entsprechendes äquivalentes Schaltdiagramm des Bereichs der Feldeffekttransistorstruktur mit geteiltem Gate gemäß verschiedenen Ausführungsformen zeigt;

**[0016] Fig. 7** eine schematische Querschnittsansicht eines Träger mit zwei benachbarten Feldeffekttransistorstrukturen mit geteiltem Gate während der Herstellung, gemäß verschiedenen Ausführungsformen zeigt; und

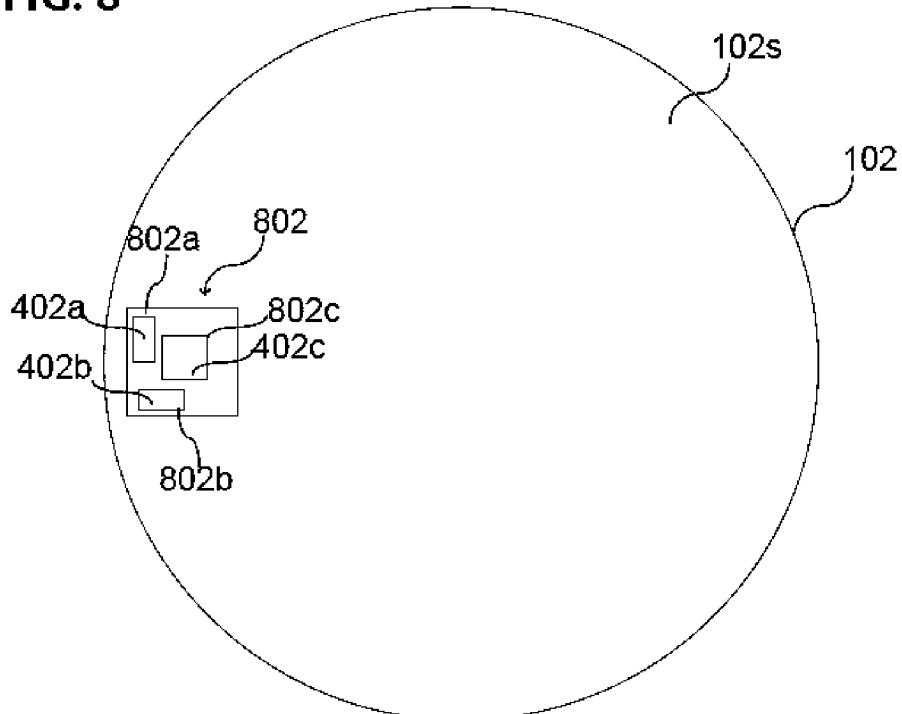

**[0017] Fig. 8** eine schematische Draufsicht eines Trägers gemäß verschiedenen Ausführungsformen zeigt.

**[0018]** Die folgende ausführliche Beschreibung bezieht sich auf die beiliegenden Zeichnungen, die zur Veranschaulichung spezielle Einzelheiten und Ausführungsformen zeigen, in welchen die Erfindung ausgeführt werden kann.

**[0019]** Das Wort "beispielhaft" wird hier in der Bedeutung "als Beispiel, Fallbeispiel oder Veranschaulichung dienend" verwendet. Jede hier als "beispielhaft" beschriebene Ausführungsform oder Gestaltung ist nicht unbedingt gegenüber anderen Ausführungsformen oder Gestaltungen als bevorzugt oder vorteilhaft auszulegen.

**[0020]** Das Wort "über", das in Hinblick auf ein abgeschiedenes Material verwendet wird, das "über" einer Seite oder Oberfläche gebildet wird, kann hier mit der Bedeutung verwendet werden, dass das abgeschiedene Material "direkt auf", z.B. in direktem Kontakt mit, der genannten Seite oder Oberfläche gebildet ist. Das Wort "über", das in Hinblick auf ein ab-

geschiedenes Material verwendet wird, das "über" einer Seite oder Oberfläche gebildet wird, kann hier mit der Bedeutung verwendet werden, dass das abgeschiedene Material "indirekt auf" der genannten Seite oder Oberfläche mit einer oder mehreren zusätzlichen Schichten, die zwischen der genannten Seite oder Oberfläche und dem abgeschiedenen Material angeordnet sind, gebildet wird.

**[0021]** Der Begriff "seitlich", der in Hinblick auf die "seitliche" Ausdehnung einer Struktur (oder eines Trägers) oder "seitlich" neben diesem verwendet wird, kann hier zur Bezeichnung einer Ausdehnung oder eines Positionsverhältnisses entlang einer Oberfläche eines Trägers verwendet werden. Dies bedeutet, dass eine Oberfläche eines Trägers (z.B. eine Oberfläche einer Trägerschicht oder eine Oberfläche eines Wafers) als Referenz dienen kann, die allgemein als die Hauptbearbeitungsfläche eines Wafers (oder die Hauptbearbeitungsfläche einer anderen Art von Träger) bezeichnet wird. Ferner kann der Begriff "Breite", der in Hinblick auf eine "Breite" einer Struktur (oder eines Strukturelements) verwendet wird, hier zur Bezeichnung der seitlichen Ausdehnung einer Struktur verwendet werden. Ferner kann der Begriff "Höhe", der in Hinblick auf eine Höhe einer Struktur (oder eines Strukturelements) verwendet wird, hier zur Bezeichnung einer Ausdehnung einer Struktur entlang einer Richtung senkrecht zur Oberfläche eines Trägers (z.B. senkrecht zur Hauptbearbeitungsfläche eines Trägers) verwendet werden. Der Begriff "Dicke", der in Hinblick auf eine "Dicke" einer Schicht verwendet wird, kann hier zur Bezeichnung der räumlichen Ausdehnung der Schicht senkrecht zur Oberfläche der Auflage verwendet werden, auf der die Schicht abgeschieden wird. Wenn die Oberfläche der Auflage parallel zur Oberfläche des Trägers (z.B. zur Hauptbearbeitungsfläche) ist, kann die "Dicke" der auf der Auflage abgeschiedenen Schicht dieselbe sein wie die Höhe der Schicht.

**[0022]** Im Allgemeinen kann eine elektronische Vorrichtung, abhängig von den gewünschten Funktionen, die von den Transistoren übernommen werden sollen, verschiedene Arten von Transistorstrukturen enthalten, z.B. verschiedene Arten von Feldeffekttransistoren. Die verschiedenen Arten von Feldeffekttransistoren (FETs) auf einem Träger können in derselben Halbleitertechnologie, z.B. in MOS-Technologie (Metall-Oxid-Halbleitertechnologie) oder in CMOS-Technologie (komplementäre Metall-Oxid-Halbleitertechnologie) als MOS-FETs hergestellt werden.

**[0023]** Gemäß verschiedenen Ausführungsformen kann ein Träger eine erste Art von Feldeffekttransistoren und eine zweite Art von Feldeffekttransistoren, die sich von der ersten Art von Feldeffekttransistoren unterscheidet, enthalten, z.B. die zwei Arten von Feldeffekttransistoren können eine unterschiedliche

Dicke der Gate-Isolationsschicht (Gateoxidschicht) aufweisen, die das Gate des jeweiligen Feldeffekttransistors von der Body-Region des Trägers (dem Kanal) unter dem Gate trennt. Ferner kann die erste Art von Feldeffekttransistoren eine erste Gate-Isolationsschicht (z.B. ein Einzelschicht-Gateoxid oder eine erste Gate-Isolationsschichtstruktur), z.B. mit einer Dicke von weniger als etwa 3,5 nm, z.B. mit einer Dicke im Bereich von etwa 1 nm bis etwa 3 nm haben. Die erste Art von Feldeffekttransistoren kann zum Beispiel Niederspannungs-MOSFETs für logische Schaltungen (z.B. für logische Zellen im Kern eines Standard-CMOS-Chips) vorsehen, z.B. mit einer Betriebsspannung (die z.B. am Gate zum Schalten des Feldeffekttransistors angelegt wird) von weniger als etwa 2 V, z.B. von weniger als etwa 1,5 V. Ferner kann die zweite Art von Feldeffekttransistoren eine zweite Gate-Isolationsschicht (z.B. eine Doppelschicht-Gateoxid oder eine zweite Gate-Isolationsschichtstruktur), z.B. mit einer Dicke größer als etwa 3,5 nm, z.B. mit einer Dicke im Bereich von etwa 4 nm bis etwa 10 nm haben. Die zweite Art von Feldeffekttransistoren kann zum Beispiel Hochspannungs-MOSFETs für peripherie Schaltungen (z.B. für Eingabe/Ausgabe (I/O) Zellen eines Standard-CMOS-Chips), z.B. mit einer Betriebsspannung im Bereich von etwa 3 V bis etwa 20 V, z.B. im Bereich von etwa 5 V bis etwa 14 V vorsehen. In dieser Hinsicht können die erste Art von Feldeffekttransistoren und die zweite Art von Feldeffekttransistoren mit Hilfe eines kosten- und zeiteffizienten Integrationsschemas hergestellt werden. Daher können nur zwei verschiedene Wachsprozesse während der Bearbeitung des Trägers angewendet werden, wobei die dünne Gate-Isolationsschicht der ersten Art von Feldeffekttransistoren als ein Einzelschicht-Gateoxid gewachsen werden kann und wobei die dicke Gate-Isolationsschicht der zweiten Art von Feldeffekttransistoren als ein Doppelschicht-Gateoxid mit einer größeren Dicke als das Einzelschicht-Gateoxid gewachsen werden kann.

**[0024]** Gemäß verschiedenen Ausführungsformen kann eine Transistorstruktur mit geteiltem Gate (z.B. eine sogenannte Struktur mit geteiltem Kanal oder eine Zwei-Anschlüsse-Ein-Transistorstruktur mit geteiltem Kanal), wie hier beschrieben, eine erste geteilte Gate-Region und eine zweite geteilte Gate-Region seitlich neben der ersten geteilten Gate-Region enthalten, wobei die erste geteilte Gate-Region eine erste geteilte Gate-Isolationsschicht (oder eine erste geteilte Gate-Isolationsschichtstruktur oder eine erste geteilte Gateoxidschicht) enthält, die einen ersten Abschnitt einer Gate-Struktur über der ersten geteilten Gate-Isolationsschicht von einer ersten Body-Region (ersten Kanalregion) im Träger unter der ersten geteilten Gate-Isolationsschicht trennt und wobei die zweite geteilte Gate-Region eine zweite geteilte Gate-Isolationsschicht (oder eine zweite geteilte Gate-Isolationsschichtstruktur oder eine

zweite geteilte Gateoxidschicht) enthält, die einen zweiten Abschnitt der Gate-Struktur über der zweiten geteilten Gate-Isolationsschicht von einer zweiten Body-Region (zweiten Kanalregion) im Träger unter der zweiten geteilten Gate-Isolationsschicht trennt, wobei sich die Dicke der ersten geteilten Gate-Isolationsschicht von der Dicke der zweiten geteilten Gate-Isolationsschicht unterscheiden kann. Ohne Einschränkung der Allgemeingültigkeit kann die erste geteilte Gate-Isolationsschicht in der ersten geteilten Gate-Region dicker sein als die zweite geteilte Gate-Isolationsschicht in der zweiten geteilten Gate-Region, so dass die erste geteilte Gate-Isolationsschicht hier auch als dicke geteilte Gate-Isolationsschicht bezeichnet werden kann und die zweite geteilte Gate-Isolationsschicht hier auch als dünne geteilte Gate-Isolationsschicht bezeichnet werden kann, um die Begriffe leichter zuzuordnen. Ferner kann, ohne Einschränkung der Allgemeingültigkeit, die Gate-Isolationsschicht der ersten Art von Feldeffekttransistoren dünner sein als die Gate-Isolationsschicht der zweiten Art von Feldeffekttransistoren, so dass die Gate-Isolationsschicht der ersten Art von Feldeffekttransistoren hier auch als dünne Gate-Isolationsschicht bezeichnet werden kann und die Gate-Isolation der zweiten Art von Feldeffekttransistoren hier auch als dicke Gate-Isolationsschicht bezeichnet werden kann, um die Begriffe leichter zuzuordnen.

**[0025]** Die dicke geteilte Gate-Isolationsschicht (die dicke geteilte Gateoxidschicht) kann eine dicke geteilte Gate-Isolation (ein dickes geteiltes Gateoxid) vorsehen. Ferner kann die dicke geteilte Gate-Isolationsschicht eine Doppelschicht sein und daher kann das dicke geteilte Gateoxid einen ersten Abschnitt und einen zweiten Abschnitt über dem ersten Abschnitt enthalten oder mit anderen Worten, das dicke geteilte Gateoxid kann eine sogenannte duale (doppelte) Gateoxid enthalten. Die dünne geteilte Gate-Isolationsschicht (die dünne geteilte Gateoxidschicht) kann eine dünne geteilte Gate-Isolation (ein dünnes geteiltes Gateoxid) vorsehen. Ferner kann die dünne geteilte Gate-Isolationsschicht eine Einzelschicht sein und daher kann das dünne geteilte Gateoxid ein Einzel-Gateoxid enthalten. Die dicke Gate-Isolationsschicht (die dicke Gateoxidschicht) kann eine dicke Gate-Isolation (ein dickes Gateoxid) vorsehen. Ferner kann die dicke Gate-Isolationsschicht eine Doppelschicht sein und daher kann das dicke Gateoxid einen ersten Abschnitt und einen zweiten Abschnitt über dem ersten Abschnitt enthalten oder mit anderen Worten, das dicke Gateoxid kann eine sogenannte duale (doppelte) Gateoxid enthalten. Die dünne Gate-Isolationsschicht kann eine dünne Gate-Isolation (ein dünnes Gateoxid) vorsehen. Ferner kann die dünne Gate-Isolationsschicht eine Einzelschicht sein und daher kann das dünne Gateoxid ein einzelnes Gateoxid enthalten.

**[0026]** Zur Veranschaulichung kann hier gemäß verschiedenen Ausführungsformen ein Verfahren zum Bearbeiten eines Trägers vorgesehen sein, das ein Wachsen von Siliziumoxid von einem Siliziumträger mit unterschiedlichen Wachsgeschwindigkeiten ermöglicht und daher Siliziumoxid in verschiedenen vordefinierten Flächen des Trägers mit unterschiedlichen Dicken durch denselben Wachsprozess gewachsen wird. Somit kann eine dünne Gateoxidschicht in einer ersten Region des Trägers gebildet werden und gleichzeitig kann eine dünne geteilte Gateoxidschicht in einer zweiten Region des Trägers durch denselben Wachsprozess gebildet werden, wobei sich die Dicke der dünnen Gateoxidschicht von der Dicke der dünnen geteilten Gateoxidschicht unterscheiden kann. Ferner kann eine dicke Gateoxidschicht (z.B. ein Doppelschicht-Gateoxid) in einer ersten Region des Trägers gebildet werden und gleichzeitig kann eine dicke geteilte Gateoxidschicht (z.B. ein geteiltes Doppelschicht-Gateoxid) in einer zweiten Region des Trägers durch denselben Wachsprozess gebildet werden (z.B. durch dieselben zwei Oxidationsprozesse des Trägers, die der Reihe nach durchgeführt werden), wobei sich die Dicke der dicken Gateoxidschicht von der Dicke der dicken geteilten Gateoxidschicht unterscheiden kann.

**[0027]** Infolgedessen können gemäß verschiedenen Ausführungsformen durch ausschließliches Ausführen von zwei Wachsprozessen die erste Art von Feldeffekttransistoren mit einer dünnen Gate-Isolationsschicht und die zweite Art von Feldeffekttransistoren mit einer dicken Gate-Isolationsschicht über dem Träger vorgesehen werden und gleichzeitig kann eine Feldeffekttransistorstruktur mit geteiltem Gate mit einer dicken geteilten Gate-Region und einer dünnen geteilten Gate-Region über dem Träger in einer vordefinierten Fläche vorgesehen sein, wobei die Dicke einer dicken geteilten Gate-Isolationsschicht in der ersten geteilten Gate-Region größer ist als die dicke Gate-Isolationsschicht der zweiten Art von Feldeffekttransistoren und wobei die Dicke einer dünnen geteilten Gate-Isolationsschicht in der zweiten geteilten Gate-Region gleich oder geringer als die Dicke der dünnen Gate-Isolationsschicht der ersten Art von FETs ist.

**[0028]** Zur Veranschaulichung kann gemäß verschiedenen Ausführungsformen die Transistorstruktur mit geteiltem Gate als ein auf einer Anti-Schmelzsicherung beruhender OTP NVM konfiguriert oder betrieben werden und die geteilte Gate-Isolationsschicht der Transistorstruktur mit geteiltem Gate kann zur Verbesserung der Zuverlässigkeit des auf einer Anti-Schmelzsicherung beruhenden OTP NVM ausgebildet sein. Mit anderen Worten, die Dicke der dicken geteilten Gate-Isolationsschicht und die Dicke der dünnen geteilten Gate-Isolationsschicht der Transistorstruktur mit geteiltem Gate kann dazu ausgebildet sein, eine zuverlässige Programmierung des

auf einer Anti-Schmelzsicherung beruhenden OTP NVM zu ermöglichen, ohne die Wachsprozesse zum Wachsen der Gateoxide für die erste Art von Feldeffekttransistoren und die zweite Art von Feldeffekttransistoren vom Träger zu ändern und ohne zusätzliche Wachsprozesse zu verwenden. Gemäß verschiedenen Ausführungsformen können nur zwei Wachsprozesse zur Herstellung eines Chips oder eines Nacktchips (bare Die) mit dem auf einer Anti-Schmelzsicherung beruhenden OTP NVM gemeinsam mit der ersten Art von Feldeffekttransistoren und der zweiten Art von Feldeffekttransistoren verwendet werden, wobei die Transistorstruktur mit geteiltem Gate des auf einer Anti-Schmelzsicherung beruhenden OTP NVM zum Modifizieren der Oberflächenregion des Trägers ausgebildet sein kann, in welchem der auf einer Anti-Schmelzsicherung beruhende OTP NVM gebildet werden soll.

**[0029]** Gemäß verschiedenen Ausführungsformen kann das Wachsen der geteilten Gate-Isolationsschichten in einer vordefinierten Oberflächenregion des Trägers modifiziert werden, z.B. kann die Wachsgeschwindigkeit des Gateoxids im Vergleich zu anderen Oberflächenregionen des Trägers erhöht werden, indem die vordefinierte Oberflächenregion des Trägers mit Fluor dotiert wird.

**[0030]** Gemäß verschiedenen Ausführungsformen kann das Wachsen der geteilten Gate-Isolationsschichten in einer vordefinierten Oberflächenregion des Trägers modifiziert werden, z.B. kann die Wachsgeschwindigkeit des Gateoxids, z.B. kann die Wachsgeschwindigkeit des Gateoxids verringert werden, indem die vordefinierte Oberflächenregion des Trägers mit Stickstoff dotiert wird oder indem dem Oxidationsprozess zur Bildung des Gateoxids aus dem Träger Stickstoff hinzugefügt wird. Gemäß verschiedenen Ausführungsformen kann ein Nitrid oder eine Nitridschicht, z.B. Siliziumnitrid oder eine Siliziumnitridschicht, in einem Gateoxid oder einer Gateoxidschichtstruktur enthalten sein. Gemäß verschiedenen Ausführungsformen kann Stickstoff in den Rezepturen zur Bildung eines Gateoxids zur Begrenzung des Wachstums des Gateoxids enthalten sein.

**[0031]** Gemäß verschiedenen Ausführungsformen kann das Wachsen der geteilten Gate-Isolationsschichten der Transistorstruktur mit geteiltem Gate in einer vordefinierten Oberflächenregion des Trägers modifiziert sein, z.B. kann die Wachsgeschwindigkeit des Gateoxids im Vergleich zu anderen Oberflächenregionen des Trägers erhöht und/oder verringert sein, indem die vordefinierte Oberflächenregion des Trägers mit Fluor und/oder Stickstoff dotiert wird und/oder indem dem Oxidationsprozess zur Bildung des Gateoxids vom Träger Stickstoff hinzugefügt wird.

**[0032]** Gemäß verschiedenen Ausführungsformen kann eine Gateoxid (Siliziumoxid) durch thermisches

Oxidieren des Trägers (eines Siliziumwafers oder einer Siliziumträgerschicht oder eines Siliziumnacktchips) durch eine sogenannte thermische Oxidation oder eine schnelle thermische Oxidation gewachsen werden. Gemäß verschiedenen Ausführungsformen kann der erste Wachsprozess (z.B. zur Bildung einer Gate-Isolationsschicht über einem Träger, um einen ersten Abschnitt einer dicken Gate-Isolationsschicht vorzusehen und einen ersten Abschnitt einer dicken geteilten Gate-Isolationsschicht vorzusehen) eine thermische Oxidation des Trägers bei einer Temperatur im Bereich von etwa 500°C bis etwa 1000°C, z.B. im Bereich von etwa 650°C bis etwa 850°C, sein mit einer Ausheilungsdauer im Bereich von etwa mehreren Minuten bis etwa eine Stunde, z.B. im Bereich von etwa 10 min bis etwa 50 min, z.B. im Bereich von etwa 20 min bis etwa 40 min. Ferner kann der erste Wachsprozess in einer Sauerstoffatmosphäre durchgeführt werden. Gemäß verschiedenen Ausführungsformen kann der zweite Wachsprozess (z.B. zur Bildung einer dünnen Gate-Isolationsschicht und einer dünnen geteilten Gate-Isolationsschicht oder zur Bildung einer zusätzlichen Gate-Isolationsschicht über einer bereits gewachsenen Gate-Isolationsschicht, um einen zweiten Abschnitt einer dicken Gate-Isolationsschicht vorzusehen und um einen zweiten Abschnitt einer dicken geteilten Gate-Isolationsschicht vorzusehen) eine thermische Oxidation des Trägers bei einer Temperatur im Bereich von etwa 500°C bis etwa 1000°C, z.B. im Bereich von etwa 650°C bis etwa 850°C, sein, mit einer Ausheilungsdauer im Bereich von etwa mehreren Minuten bis etwa eine Stunde, z.B. im Bereich von etwa 10 min bis etwa 50 min, z.B. im Bereich von etwa 20 min bis etwa 40 min. Ferner kann der zweite Wachsprozess in einer Sauerstoff- oder Sauerstoff/Stickstoff-Atmosphäre ausgeführt werden. Gemäß verschiedenen Ausführungsformen kann der zweite Wachsprozess bei einer höheren Temperatur als der erste Wachsprozess ausgeführt werden. Ferner kann der zweite Wachsprozess mit einer kürzeren Dauer als der erste Wachsprozess ausgeführt werden.

**[0033]** Gemäß verschiedenen Ausführungsformen kann der erste Wachsprozess ein Gateoxid mit einer Dicke im Bereich von etwa 2 nm bis etwa 4 nm vorsehen, das von einer Siliziumfläche gewachsen wird, und ein dickeres Gateoxid, wenn das Gateoxid von einer fluordotierten Siliziumfläche gewachsen wird, z.B. mit einer Dicke im Bereich von etwa 3 nm bis etwa 5 nm. Gemäß verschiedenen Ausführungsformen kann der zweite Wachsprozess ein Gateoxid mit einer Dicke im Bereich von etwa 1 nm bis etwa 3 nm vorsehen, wenn das Gateoxid zum Beispiel von einer Siliziumfläche gewachsen wird, um eine dünne Gateoxidschicht oder eine dünne geteilte Gateoxidschicht vorzusehen, oder wenn das Gateoxid zum Beispiel über einem bereits gewachsenen Gateoxid gewachsen wird, um eine dicke Gateoxidschicht oder eine dicke geteilte Gateoxidschicht als ein Doppelschicht

Gateoxid vorzusehen. Wenn daher gemäß verschiedenen Ausführungsformen ein Doppelschicht Gateoxid durch den ersten Wachsprozess und durch den zweiten Wachsprozess von einer Siliziumfläche gewachsen wird, kann das Doppelschicht Gateoxid eine resultierende endgültige Dicke im Bereich von etwa 3 nm bis etwa 7 nm haben. Wenn ferner ein Doppelschicht Gateoxid durch den ersten Wachsprozess und durch den zweiten Wachsprozess von einer fluordotierten Siliziumfläche gewachsen wird, kann das Doppelschicht Gateoxid eine resultierende endgültige Dicke im Bereich von etwa 4 nm bis etwa 8 nm haben.

**[0034]** Gemäß verschiedenen Ausführungsformen können die Gateoxidschichten oder die Gate-Isolationschichten strukturiert sein, um das jeweilige Gateoxid vorzusehen.

**[0035]** Zur Veranschaulichung kann gemäß verschiedenen Ausführungsformen die Transistorstruktur mit geteiltem Gate dazu ausgebildet sein, die Zuverlässigkeit der Transistorstruktur mit geteiltem Gate zu erhöhen, die als ein auf einer Anti-Schmelzsicherung beruhender OTP NVM verwendet wird. Daher kann gemäß verschiedenen Ausführungsformen das Gate einer Transistorstruktur mit geteiltem Gate modifiziert werden, z.B. kann die elektrische Leitfähigkeit (oder die Dotierungskonzentration) eines Abschnitts des Gates erhöht werden, so dass ein Durchbrennen des auf einer Anti-Schmelzsicherung beruhenden OTP NVM zuverlässiger sein kann. Gemäß verschiedenen Ausführungsformen kann der Abschnitt des Gates, der über dem dünnen geteilten Gateoxid angeordnet ist, das durchgebrannt werden soll, zusätzlich dotiert sein oder kann mit einer größeren elektrischen Leitfähigkeit als der Rest des Gates versehen sein, z.B. als der Abschnitt des Gates, der über dem dicken geteilten Gateoxid angeordnet ist. Gemäß verschiedenen Ausführungsformen kann die Transistorstruktur mit geteiltem Gate auch als OTP-Zelle bezeichnet werden und der Abschnitt der Transistorstruktur mit geteiltem Gate, der das dünne geteilte Gateoxid enthält, kann als Sicherungszelle der OTP-Zelle bezeichnet werden.

**[0036]** Gemäß verschiedenen Ausführungsformen kann eine Feldeffekttransistorstruktur mit geteiltem Gate (geteiltem Kanal) als ein auf einer Anti-Schmelzsicherung beruhender OTP NVM (eine sogenannte Ein-Transistor (1T) Bit-Zelle) gebildet werden, wobei das dünne geteilte Gateoxid durchgebrannt wird, um den Zustand des auf einer Anti-Schmelzsicherung beruhenden OTP NVM zu ändern, indem ein elektrisch leitender Pfad durch das dünne geteilte Gateoxid gebildet wird. Gemäß verschiedenen Ausführungsformen kann ein auf einer Anti-Schmelzsicherung beruhender OTP NVM auch als eine Zwei-Transistor-(2T)Anti-Schmelzsicherung-Bit-Zelle konfiguriert sein, die einen Programmierungstransistor

(z.B. einen ersten MOSFET) und einen Auswahltransistor (z.B. einen zweiten MOSFET) enthält.

**[0037]** Die Feldeffekttransistorstruktur mit geteiltem Gate (geteiltem Kanal), wie hier beschrieben, kann durchbrennen und mit einer Zuverlässigkeit von mehr als 99,9% arbeiten. Daher kann die Feldeffekttransistorstruktur mit geteiltem Gate in einer Automobil-elektronik ohne Fehlerkorrektur verwendet werden. Mit anderen Worten, der Träger mit der Feldeffekttransistorstruktur mit geteiltem Gate könnte keine Region zur Durchführung einer Fehlerfassung und -korrektur benötigen.

**[0038]** Fig. 1 zeigt eine Feldeffekttransistorstruktur mit geteiltem Gate **100** gemäß verschiedenen Ausführungsformen in einer schematischen Querschnittsansicht, wobei zumindest ein (z.B. ein oder mehrere) Feldeffekttransistor **100t** mit geteiltem Gate in einen Träger **102** integriert sein kann. Der Träger **102** kann zumindest eines der folgenden enthalten: einen Siliziumwafer oder einen Teil eines Siliziumwafers, z.B. einen Nacktchip oder einen Chip oder jeden anderen geeigneten Träger mit einer Siliziumflächenschicht **102**. Gemäß verschiedenen Ausführungsformen kann der Träger p-Typ-dotiert, z.B. bordotiert, oder n-Typ-dotiert, z.B. phosphordotiert sein. Daher kann gemäß verschiedenen Ausführungsformen der Träger **102** die Body-Region **102c** (den Kanal **102c**) der Feldeffekttransistorstruktur mit geteiltem Gate **100** vorsehen. Ferner kann der Träger **102** eine Bearbeitungsfläche **102s** enthalten, auf welcher die Feldeffekttransistorstruktur mit geteiltem Gate **100** gebildet werden kann oder an welcher die Feldeffekttransistorstruktur mit geteiltem Gate **100** in MOS-Technologie integriert werden kann. Gemäß verschiedenen Ausführungsformen kann die Feldeffekttransistorstruktur mit geteiltem Gate **100** eine Gate-Struktur **106** (ein Gate) zum Steuern (z.B. zum Durchbrennen, Schreiben und/oder Lesen) der Feldeffekttransistorstruktur mit geteiltem Gate **100** enthalten.

**[0039]** Gemäß verschiedenen Ausführungsformen kann die Feldeffekttransistorstruktur mit geteiltem Gate **100** eine erste geteilte Gate-Region über einer ersten Body-Region **102a** (über einem ersten Abschnitt des Kanals **102c**) und eine zweite geteilte Gate-Region über einer zweiten Body-Region **102b** (über einem zweiten Abschnitt des Kanals **102c**) enthalten. Die erste geteilte Gate-Region kann ein dickes geteiltes Gateoxid **104a** (z.B. eine Doppelschicht-Gate-Isolation, z.B. ein duales Gateoxid) und einen ersten Gate-Abschnitt **106a** über dem dicken geteilten Gateoxid **104a** enthalten. Die zweite geteilte Gate-Region (die Sicherungszelle) kann ein dünnes geteiltes Gateoxid **104b** (z.B. eine Einzelschicht-Gate-Isolation, z.B. ein Einzel-Gateoxid) und einen zweiten Gate-Abschnitt **106b** über dem dünnen geteilten Gateoxid **104b** enthalten. Daher kann der ers-

te Gate-Abschnitt **106a** die erste Body-Region **102a** (die Leitfähigkeit des Kanals unter dem ersten Gate-Abschnitt **106a**) durch Vorsehen eines elektrischen Feldes durch das dicke geteilte Gateoxid **104a** steuern.

**[0040]** Ferner kann der zweite Gate-Abschnitt **106b** ein Anlegen einer Spannung ermöglichen, um das dünne geteilte Gateoxid **104b** durchzubrechen, so dass der zweite Gate-Abschnitt **106b** mit dem Kanal **102c** (z.B. mit der zweiten Body-Region **102b**) elektrisch leitend verbunden werden kann. Zur Veranschaulichung, die Feldeffekttransistorstruktur mit geteiltem Gate **100** kann in einem ersten Zustand sein (z.B. einen ersten logischen Zustand darstellen, z.B. eine "1"), wenn das dünne geteilte Gateoxid **104b** den zweiten Gate-Abschnitt **106b** elektrisch vom Kanal **102c** isoliert, und die Feldeffekttransistorstruktur mit geteiltem Gate **100** kann in einem zweiten Zustand sein (z.B. einen zweiten logischen Zustand darstellen, z.B. eine "0"), wenn das dünne geteilte Gateoxid **104b** den zweiten Gate-Abschnitt **106b** mit dem Kanal **102c** elektrisch verbindet. Der Zustand ("0" oder "1") der Feldeffekttransistorstruktur mit geteiltem Gate **100** kann durch Anlegen einer Schreibspannung an das dünne geteilte Gateoxid **104b** geändert werden. Der Zustand ("0" oder "1") der Feldeffekttransistorstruktur mit geteiltem Gate **100** kann durch Anlegen einer Auslesespannung zwischen der Gate-Struktur **106** und dem Kanal **102** (oder zwischen der Gate-Struktur **106** und einer Source/Drain-Region im Träger **102** neben der ersten Body-Region **102a**) gelesen werden.

**[0041]** Gemäß verschiedenen Ausführungsformen kann die elektrische Leitfähigkeit des zweiten Gate-Abschnitts **106b** größer sein als die elektrische Leitfähigkeit des ersten Gate-Abschnitts **106a**. Daher kann ein größerer Spannungsanteil über dem dünnen geteilten Gateoxid **104b** fallen, wodurch eine Sicherung der Feldeffekttransistorstruktur mit geteiltem Gate **100** verbessert oder möglich wird, indem das dünne geteilte Gateoxid **104b** durchgebrochen wird, da auch ein größerer Strom durch das dünne geteilte Gateoxid **104b** während des Sicherungsprozesses fließen kann. Zur Veranschaulichung, die Gate-Struktur **106** kann dazu ausgebildet sein, die spezifische elektrische Leitfähigkeit über dem dünnen geteilten Gateoxid **104b** lokal zu ändern, wodurch zum Beispiel ein Ausgleich einer Verarmung in der Gate-Struktur **106** möglich ist, wenn eine hohe Schreibspannung (z.B. größer als zum Beispiel 5 V oder im Bereich von etwa 5 V bis etwa 12 V) an die Gateoxid-Struktur **104a**, **104b** angelegt wird. Infolgedessen kann eine geringere Spannung notwendig sein, um das dünne geteilte Gateoxid **104b** durchzubrechen, und daher kann auch das dicke geteilte Gateoxid **104a** während des Sicherungsprozesses entlastet sein. Da die elektrische Leitfähigkeit des dünnen geteilten Gateoxids **104b** nach dem Sichern größer

sein kann, kann dies auch als Anti-Schmelzsicherung bezeichnet werden.

**[0042]** Gemäß verschiedenen Ausführungsformen kann die Dicke (z.B. die Ausdehnung entlang der Richtung **105**) des dünnen geteilten Gateoxids **104b** im Bereich von etwa 1 nm bis etwa 3 nm sein. Die untere Grenze für die Dicke des dünnen geteilten Gateoxids **104b** kann jedoch zum Beispiel aus physikalischer Gründen einer Tunnelung von Elektronen definiert sein, so dass das dünne geteilte Gateoxid **104b** die Fähigkeit verlieren kann, aus dem ersten Zustand in den zweiten Zustand zu wechseln. Auf dieser Basis kann die Dicke des dicken geteilten Gateoxids **104a** relativ zur Dicke des dünnen geteilten Gateoxids **104b** einen Stromfluss und eine Spannungsverteilung im Feldeffekttransistorstruktur mit geteiltem Gate **100** beeinflussen, was die Zuverlässigkeit der Feldeffekttransistorstruktur mit geteiltem Gate **100** während des Schreibens und Lesens beeinflussen kann. Gemäß verschiedenen Ausführungsformen kann das Verhältnis der Dicke des dicken geteilten Gateoxids **104a** relativ zur Dicke des dünnen geteilten Gateoxids **104b** größer als 2, z.B. größer als 3 sein, z.B. im Bereich von etwa 1,5 bis etwa 5 liegen.

**[0043]** Gemäß verschiedenen Ausführungsformen kann die Breite (z.B. die Ausdehnung entlang der seitlichen Richtung **101**) des Feldeffekttransistors **100t** mit geteiltem Gate im Bereich von etwa mehreren Nanometern bis etwa einem Mikrometer oder mehr als einem Mikrometer liegen, z.B. im Bereich von etwa 10 nm bis etwa 10 µm, z.B. im Bereich von etwa 20 nm bis etwa 1 µm, z.B. im Bereich von etwa 20 nm bis etwa 500 nm.

**[0044]** Da gemäß verschiedenen Ausführungsformen die verfügbaren Gateoxid-Wachsprozess auf die zwei Prozesse beschränkt sein können, die für die erste Art von Transistoren und die zweite Art von Transistoren auf dem Träger **102** verwendet werden (siehe **Fig. 5**), kann das Verhältnis der Dicke des dicken geteilten Gateoxids **104a** relativ zur Dicke des dünnen geteilten Gateoxids **104b** erhöht werden, um eine zuverlässigere Feldeffekttransistorstruktur mit geteiltem Gate **100** vorzusehen, indem das Wachsen des Gateoxids von der Body-Region **102c** lokal beeinflusst wird (siehe zum Beispiel **Fig. 3** und **Fig. 4D**).

**[0045]** In der Folge sind verschiedene Modifizierungen und/oder Konfigurationen der Feldeffekttransistorstruktur mit geteiltem Gate **100** und Einzelheiten, die sich auf die geteilten Gateoxide **104a**, **104b**, die Gate-Struktur **106** und den Träger **102** beziehen, beschrieben, wobei die Merkmale und/oder Funktionalitäten, die in Bezug auf **Fig. 1** beschrieben sind, analog enthalten sein können. Ferner können die in der Folge beschriebenen Merkmale und/oder Funktionalitäten in der Feldeffekttransistorstruktur mit geteiltem

Gate **100** enthalten sein oder können mit der Feldeffekttransistorstruktur mit geteiltem Gate **100** kombiniert sein, wie zuvor unter Bezugnahme auf **Fig. 1** beschrieben.

**[0046]** Wie in **Fig. 2A** dargestellt, kann gemäß verschiedenen Ausführungsformen das dicke geteilte Gateoxid **104a** als ein duales Gateoxid vorgesehen sein, wobei zwei Gateoxidschichten **204a**, **204b** als ein Schichtstapel vorgesehen sind. Der erste Abschnitt **204a** des dicken geteilten Gateoxids **104a** kann durch den ersten Wachsprozess vorgesehen sein, wobei Siliziumoxid durch thermische Oxidation von dem (z.B. fluordotierten) Silizium des Trägers **102** gewachsen wird. Ferner kann der zweite Abschnitt **204b** des dicken geteilten Gateoxids **104a** über dem ersten Abschnitt **204a** des dicken geteilten Gateoxids **104a** durch den zweiten Wachsprozess gewachsen werden. Gleichzeitig kann das dünne geteilte Gateoxid **104b** durch den zweiten Wachsprozess vom Träger **102** gewachsen werden.

**[0047]** Gemäß verschiedenen Ausführungsformen kann nach dem Wachsen des ersten Abschnitts **204a** des dicken geteilten Gateoxids **104a** durch den ersten Wachsprozess das Fluor, das in die Oberflächenregion des Trägers **102** dotiert ist, verbraucht sein (z.B. kann das Fluor aufgrund eines vorgesehenen Wärmebudgets tiefer in die Trägerschicht diffundieren), so dass das Wachsen des dünnen geteilten Gateoxids **104b** durch die Fluordotierung des Trägers unbeeinflusst sein kann. Gemäß verschiedenen Ausführungsformen kann eine Fluor-Präimplantation mit einer Dosis gleich oder kleiner als etwa  $10^{15} \text{ cm}^{-2}$  durch den ersten Wachsprozess verbraucht werden, so dass der zweite Wachsprozess im Wesentlichen von der Fluor-Präimplantation unbeeinflusst sein kann. Ferner kann eine Fluor-Präimplantation mit einer Dosis größer als etwa  $10^{15} \text{ cm}^{-2}$  (z.B.  $3 \cdot 10^{15} \text{ cm}^{-2}$ ) nicht vollständig durch den ersten Wachsprozess verbraucht sein, so dass der zweite Wachsprozess auch durch die Fluor-Präimplantation beeinflusst sein kann. Ferner kann der erste Wachsprozess ein Nassofen-Oxidationsprozess sein und der zweite Wachsprozess kann ein Trockenofen-Oxidationsprozess sein.

**[0048]** Gemäß verschiedenen Ausführungsformen kann die Dicke (z.B. die Ausdehnung entlang der Richtung **105**) des ersten Abschnitts **204a** des dicken geteilten Gateoxids **104a** im Bereich von etwa 2 nm bis etwa 6 nm, z.B. im Bereich von etwa 3 nm bis etwa 5 nm liegen. Ferner kann die Dicke (z.B. die Ausdehnung entlang der Richtung **105**) des zweiten Abschnitts **204b** des dicken geteilten Gateoxids **104a** und die Dicke des dünnen geteilten Gateoxids **104b** im Bereich von etwa 1 nm bis etwa 3 nm liegen. Gemäß verschiedenen Ausführungsformen kann das Verhältnis der Dicke des dicken geteilten Gateoxids **104a** relativ zur Dicke des dünnen geteilten Gate-

oxids **104b** durch Fluordotierung der Oberflächenregion des Trägers **102** vor dem Wachsen des ersten Abschnitts **204a** des dicken geteilten Gateoxids **104a** erhöht werden.

**[0049]** Ferner, wie in **Fig. 2B** dargestellt, kann gemäß verschiedenen Ausführungsformen eine Source/Drain-Region **202sd** im Träger **102** vorgesehen sein. Die Source/Drain-Region **202sd** kann den entgegengesetzten Dotierungstyp der Body-Region **102c** oder des Trägers **102** enthalten. Der Träger **102** oder die Body-Region **102c** des Trägers **102** kann zum Beispiel p-Typ dotiert und die Source/Drain-Region **202sd** kann n-Typ dotiert sein. Alternativ kann der Träger **102** oder die Body-Region **102c** des Trägers **102** zum Beispiel n-Typ dotiert sein und die Source/Drain-Region **202sd** kann p-Typ dotiert sein. Ferner kann die Source/Drain-Region **202sd** gemäß verschiedenen Ausführungsformen eine leicht dotierte Drain-Region (LD) enthalten.

**[0050]** Gemäß verschiedenen Ausführungsformen kann die Gate-Struktur **106a**, **106b** Polysilizium, z.B. dotiertes Polysilizium, enthalten. Die Gate-Struktur **106a**, **106b** kann zum Beispiel durch Dotieren des Polysiliziums, das über den geteilten Gateoxiden **104a**, **104b** vorgesehen ist, durch Ionenimplantation gebildet werden. Die Gate-Struktur **106a**, **106b** kann durch denselben Dotierungsprozess dotiert werden, der zum Vorsehen der Source/Drain-Region **202sd** im Träger **102** verwendet wird. Zur Erhöhung der elektrischen Leitfähigkeit des zweiten Gate-Abschnitts **106b** kann der erste Gate-Abschnitt **106a** maskiert sein und ein zusätzlicher Ionenimplantationsprozess kann ausgeführt werden.

**[0051]** Gemäß verschiedenen Ausführungsformen kann die Feldeffekttransistorstruktur mit geteiltem Gate **100** eine dielektrische Struktur **202i** im Träger **102** enthalten. Die dielektrische Struktur **202i** kann den Feldeffekttransistor **100t** mit geteiltem Gate seitlich begrenzen. Zur Veranschaulichung können mehr als ein Feldeffekttransistor **100t** mit geteiltem Gate auf dem Träger **102** vorgesehen sein, wobei entsprechende benachbarte Feldeffekttransistoren **100t** mit geteiltem Gate durch die dielektrische Struktur **202i** elektrisch voneinander getrennt sein können. Gemäß verschiedenen Ausführungsformen kann die dielektrische Struktur **202i** eine Flachgrabenisolation (Shallow Trench Isolation, STI) und/oder eine Tiefgrabenisolation (Deep Trench Isolation, DTI) enthalten, die seitlich die Body-Region **102c** des Feldeffekttransistors **100t** mit geteiltem Gate umgibt.

**[0052]** Ferner kann gemäß verschiedenen Ausführungsformen die Feldeffekttransistorstruktur mit geteiltem Gate **100** Anschlussklemmen **206**, **208** für einen elektrischen Kontakt mit dem Feldeffekttransistor **100t** mit geteiltem Gate enthalten. Wie schematisch in **Fig. 2B** dargestellt, kann eine Source/Drain-

Anschlussklemme (Elektrode oder Kontakt) **208** mit der Source/Drain-Region **202sd** in elektrischem Kontakt stehen und eine Gate-Anschlussklemme (Elektrode oder Kontakt) **206** kann mit der Gate-Struktur **106a**, **106b** des Feldeffekttransistors **100t** mit geteiltem Gate in elektrischem Kontakt stehen.

**[0053]** Gemäß verschiedenen Ausführungsformen können in einem ersten Betriebsmodus die zwei Anschlussklemmen **206**, **208** zum Schreiben von Daten in den Feldeffekttransistor **100t** mit geteiltem Gate verwendet werden, z.B. durch Schmelzen (Durchbrechen) des dünnen geteilten Gateoxids **104b** durch Anlegen einer Schreibspannung an den Anschlussklemmen **206**, **208**. Ferner können in einem zweiten Betriebsmodus die zwei Anschlussklemmen **206**, **208** zum Lesen der Daten aus dem Feldeffekttransistor **100t** mit geteiltem Gate verwendet werden, z.B. durch Anlegen einer Auslesespannung, die geringer als die Schreibspannung ist, an den Anschlussklemmen **206**, **208**. In dieser Hinsicht kann der Strom durch den Feldeffekttransistor **100t** mit geteiltem Gate größer sein, wenn der Feldeffekttransistor **100t** mit geteiltem Gate durchgebrannt wird (wenn z.B. das dünne geteilte Gateoxid **104b** durchbrochen wird, so dass das dünne geteilte Gateoxid **104b** die Body-Region **102c** nicht von der Gate-Struktur **106a**, **106b** elektrisch isolieren kann).

**[0054]** **Fig. 2C** zeigt eine schematische Querschnittsansicht einer Feldeffekttransistorstruktur mit geteiltem Gate **100** gemäß verschiedenen Ausführungsformen, wobei ein Seitenwandabstandhalter **210** am Feldeffekttransistor **100t** mit geteiltem Gate vorgesehen ist. Wie bereits beschrieben, kann die Feldeffekttransistorstruktur mit geteiltem Gate **100** eine Source/Drain-Region **202sd** und eine leicht dotierte Drain-Region **202ldd** seitlich neben der ersten Body-Region **102a** enthalten.

**[0055]** **Fig. 3** zeigt ein schematisches Ablaufdiagramm eines Verfahrens **300** zum Bearbeiten eines Träger **102** gemäß verschiedenen Ausführungsformen, wobei das Verfahren **300** enthalten kann: in **310**, Dotieren eines Trägers **102** mit Fluor, so dass eine erste Oberflächenregion des Trägers **102** fluordotiert ist und eine zweite Oberflächenregion des Trägers **102** frei von Fluordotierung und/oder weniger fluordotiert als die erste Oberflächenregion des Trägers **102** ist; und, in **320**, Oxidieren des Trägers **102**, um ein erstes Gateoxid von der ersten Oberflächenregion des Trägers **102** mit einer ersten Dicke zu wachsen und gleichzeitig ein zweites Gateoxid von der zweiten Oberflächenregion des Trägers **102** mit einer zweiten Dicke zu wachsen, die sich von der ersten Dicke unterscheidet. **Fig. 4A** bis **Fig. 4E** zeigen jeweils den Träger **102** während der Bearbeitung, z.B. während das Verfahren **300** gemäß verschiedenen Ausführungsformen ausgeführt wird.

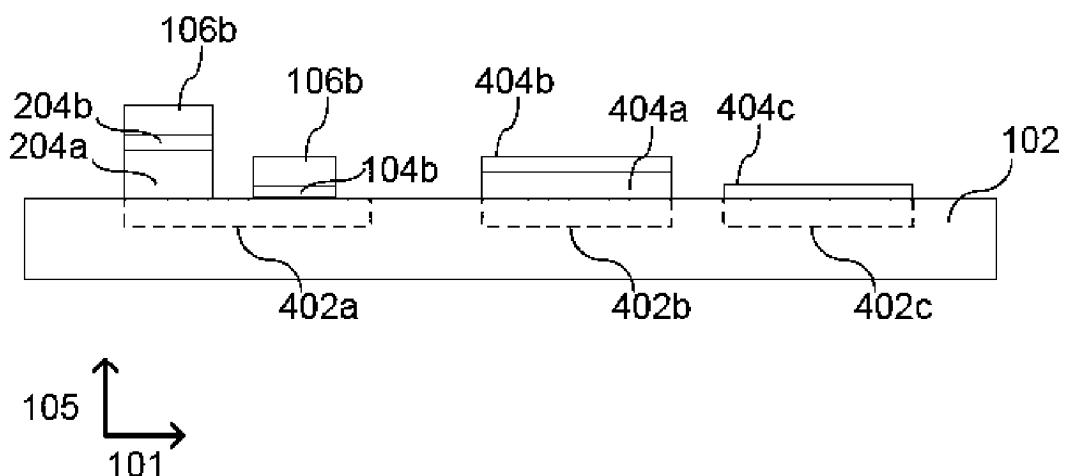

**[0056]** **Fig. 4A** zeigt schematisch den Träger **102** in einer Querschnittsansicht, wobei der Träger **102** gemäß verschiedenen Ausführungsformen teilweise mit Fluor dotiert ist, z.B. durch Ausführen einer Ionimplantation **400a**, um Fluor in eine erste Oberflächenregion **402a** des Trägers **102** zu implantieren. Der Rest des Trägers **102** kann zum Beispiel mit Maskierungsmaterial bedeckt sein, um die Implantation von Fluor außerhalb der ersten Oberflächenregion **402a** des Trägers **102**, z.B. in eine zweite Oberflächenregion **402b** des Trägers **102** oder in eine weitere Oberflächenregion des Trägers **102** zu verhindern (siehe **Fig. 5**).

**[0057]** Gemäß verschiedenen Ausführungsformen kann die Fluordotierung des Trägers **102** ein Vorsehen einer Fluordotierungskonzentration (z.B. eine Spitzendotierungskonzentration) in der ersten Oberflächenregion **402a** größer als etwa  $10^{14} \text{ cm}^{-3}$ , z.B. im Bereich von etwa  $10^{14} \text{ cm}^{-3}$  bis etwa  $10^{19} \text{ cm}^{-3}$ , z.B. im Bereich von etwa  $10^{14} \text{ cm}^{-3}$  bis etwa  $10^{18} \text{ cm}^{-3}$ , z.B. im Bereich von etwa  $10^{17} \text{ cm}^{-3}$  beinhalten. Ferner kann das Fluor mit einer Dosis von etwa  $10^{15} \text{ cm}^{-2}$ , mit einer Implantationsenergie von etwa 15 keV, mit Null-Neigung und Null-Verdrehung implantiert werden. Gemäß verschiedenen Ausführungsformen kann die Fluordotierung des Trägers **102** durch den angewendeten Implantationsprozess und das vorgesehene Wärmebudget beeinflusst sein. Gemäß verschiedenen Ausführungsformen kann das Fluor, das mit einer Dosis von etwa  $10^{15} \text{ cm}^{-2}$  implantiert wird, zu einer Spitzenendkonzentration von Fluor (nach Bildung der Gateoxide) von etwa  $10^{17} \text{ cm}^{-3}$  in eine Tiefe von etwa 2 µm unter der Oberfläche des Trägers **102** führen. In dieser Hinsicht kann die Konzentration von Fluor größer als die Nachweigrenze (z.B.  $10^{12} \text{ cm}^{-3}$ ) einer SIMS-Analyse (sekundäre Ionenmassenspektrometrie) sein.

**[0058]** Gemäß verschiedenen Ausführungsformen kann die Tiefe der fluordotierten ersten Oberflächenregion **402a** des Trägers **102** im Bereich von etwa mehreren Nanometern bis etwa mehreren Mikrometern sein. Gemäß verschiedenen Ausführungsformen kann die erste Oberflächenregion **402a** des Trägers **102** die Region des Wafers definieren, wo die Feldeffekttransistorstruktur mit geteiltem Gate **100** zu bilden ist, da die Fluordotierung die Wachsgeschwindigkeit des ersten Abschnitts **204a** des dicken geteilten Gateoxids **104a** erhöhen kann.

**[0059]** Gemäß verschiedenen Ausführungsformen kann der Träger **102** Fluorunreinheiten außerhalb (neben) der ersten Oberflächenregion **402a** des Trägers **102** enthalten. Die Fluordotierungskonzentration in der ersten Oberflächenregion **402a** kann jedoch größer (z.B. mehr als eine Größenordnung oder mehrere Größenordnungen) sein als im Rest des Trägers **102** außerhalb der ersten Oberflächenregion **402a**.

**[0060]** Wie in **Fig. 4B** dargestellt, kann das erste Gateoxid **204a** von der ersten Oberflächenregion **402a** des Trägers **102** durch Oxidieren des Trägers **102** gewachsen werden, z.B. durch Durchführen des ersten Wachsprozesses **400b**, wie bereits beschrieben. Durch denselben ersten Wachsprozess **400b** kann ein zweites Gateoxid **404a** von der zweiten Oberflächenregion **402b** des Trägers **102** gewachsen werden oder ein zweites Gateoxid **404a** kann außerhalb der ersten Oberflächenregion **402a** des Trägers **102** gewachsen werden. Da eine Wachsgeschwindigkeit **405a** für das erste Gateoxid **204a** größer sein kann als eine Wachsgeschwindigkeit **405b** für das zweite Gateoxid **404a** kann die Dicke des ersten Gateoxids **204a** größer sein als die Dicke des zweiten Gateoxids **404a** obwohl derselbe Wachsprozess **400b** (Oxidationsprozess) angewendet wurde.

**[0061]** Wie in **Fig. 4C** dargestellt, kann gemäß verschiedenen Ausführungsformen das erste Gateoxid **204a** teilweise entfernt (strukturiert) werden, so dass die erste Oberflächenregion **402a** neben dem verbleibenden ersten Gateoxid **204a** teilweise freiliegt.

**[0062]** Nach dem Strukturieren des ersten Gateoxids **204a** kann gemäß verschiedenen Ausführungsformen eine Oxidschicht **204b**, **104b** über der teilweise freigelegten ersten Oberflächenregion **402a** des Trägers **102** und über dem verbleibenden ersten Gateoxid **204a** gebildet werden, wie in **Fig. 4D** dargestellt. Daher kann ein zweiter Wachsprozess **400d** ausgeführt werden, wie bereits beschrieben, der zum Beispiel ein Oxidieren des Trägers **102** enthält, um ein drittes Gateoxid **104b** von der freigelegten ersten Oberflächenregion **402a** des Trägers **102** zu wachsen und das strukturierte erste Gateoxid **204a** weiter zu einem dualen Gateoxid **204a**, **204b** zu wachsen.

**[0063]** Somit kann gemäß verschiedenen Ausführungsformen eine geteilte Gateoxid-Struktur über der ersten Oberflächenregion **402a** des Trägers **102** vorgesehen sein, die Teil einer Feldeffekttransistorstruktur mit geteiltem Gate **100** oder eines Feldeffekttransistors **100t** mit geteiltem Gate, wie hier beschrieben, sein kann. Die geteilte Gateoxid-Struktur kann ein dickes geteiltes Gateoxid **204a**, **204b** (ein Dualschicht-Gateoxid) und ein dünnes geteiltes Gateoxid **104b** (ein Einzelschicht-Gateoxid) enthalten.

**[0064]** Gemäß verschiedenen Ausführungsformen kann der zweite Wachsprozess **400d** ein weiteres Wachsen des zweiten Gateoxids **404a** enthalten, um ein duales Gateoxid **404a**, **404b** in der zweiten Oberflächenregion **402b** vorzusehen. Das duale Gateoxid **404a**, **404b** in der zweiten Oberflächenregion **402b** des Trägers **102** kann die Gateoxid-Struktur der zweiten Art von Feldeffekttransistoren vorsehen, die auf dem Träger **102** vorgesehen ist, wie zuvor beschrieben.

**[0065]** Wie in **Fig. 4E** dargestellt, kann gemäß verschiedenen Ausführungsformen der zweite Wachsprozess **400d** ein Oxidieren des Trägers **102** enthalten, um ein vierter Gateoxid **404c** von einer dritten Oberflächenregion **402c** des Trägers **102** zu wachsen. Das einzelne Gateoxid **404c** in der dritten Oberflächenregion **402c** des Trägers **102** kann die Gateoxid-Struktur der ersten Art von Feldeffekttransistoren vorsehen, die auf dem Träger **102** vorgesehen ist, wie zuvor beschrieben.

**[0066]** Zur Veranschaulichung, durch Durchführen des ersten Wachsprozess **400b** und des zweiten Wachsprozesses **400d** kann eine geteilte Gateoxid-Struktur **104a**, **104b** über der ersten Oberflächenregion **402a** des Trägers **102** vorgesehen sein, wobei die geteilte Gateoxid-Struktur **104a**, **104b** ein dickes (duales) geteiltes Gateoxid **104a** und das dünne (einzelne) geteilte Gateoxid **104b** enthält, und ferner kann ein dickes (duales) Gateoxid **404a**, **404b** für eine zweite Art von Feldeffekttransistoren auf dem Träger **102** vorgesehen sein und ein dünnes (einzelnes) Gateoxid **404c** kann für eine erste Art von Feldeffekttransistoren auf dem Träger **102** vorgesehen sein.

**[0067]** Ferner kann gemäß verschiedenen Ausführungsformen eine Gate-Struktur über der geteilten Gateoxid-Struktur **104a**, **104b**, über dem dicken (dualen) Gateoxid **404a**, **404b** für die zweite Art von FETs und über dem dünnen (einzelnen) Gateoxid **404c** für die erste Art von FETs vorgesehen sein. Dies kann durch Abscheiden einer Polysiliziumschicht, Strukturieren der abgeschiedenen Polysiliziumschicht und Dotieren der Polysiliziumschicht durchgeführt werden. Wie bereits beschrieben, kann eine Source/Drain Struktur für den Feldeffekttransistor **100t** mit geteiltem Gate, die erste Art von Feldeffekttransistoren und die zweite Art von Feldeffekttransistoren vorgesehen sein.

**[0068]** **Fig. 5** zeigt eine Feldeffekttransistorstruktur mit geteiltem Gate **100** in einer schematischen Querschnittsansicht, wobei die Feldeffekttransistorstruktur mit geteiltem Gate **100** als ein auf einer Anti-Schmelzsicherung beruhender OTP NVM konfiguriert sein kann, der einen Programmierungstransistor mit einem dünnen geteilten Gateoxid **104b** und einen Auswahltransistor mit einem dicken geteilten Gateoxid **204a**, **204b** enthält.

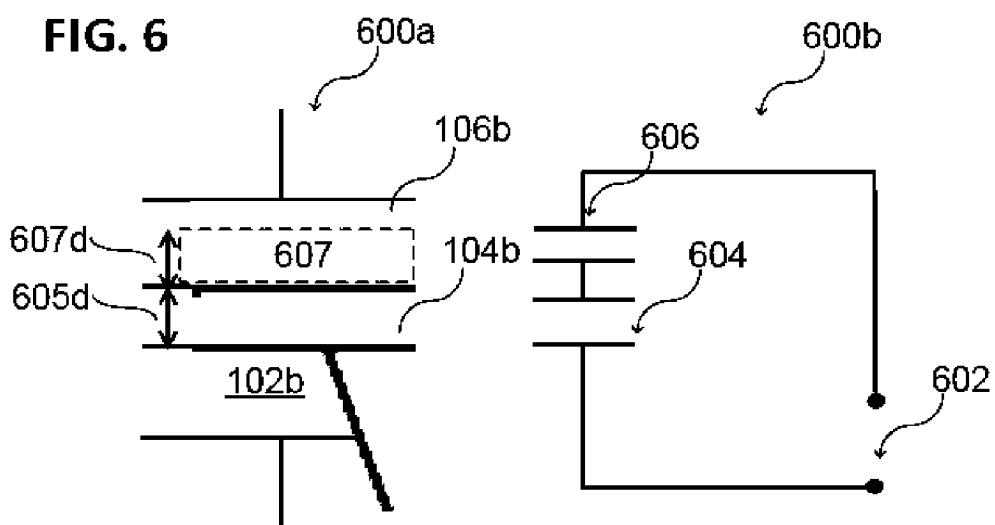

**[0069]** **Fig. 6** zeigt eine schematische Ansicht eines Bereichs **600a** einer Feldeffekttransistorstruktur mit geteiltem Gate **100** und eines entsprechenden äquivalenten Schaltdiagramms **600b** des Bereichs **600a** der Feldeffekttransistorstruktur mit geteiltem Gate **100** gemäß verschiedenen Ausführungsformen. Wie bereits beschrieben, kann die Feldeffekttransistorstruktur mit geteiltem Gate **100** ein dünnes geteiltes Gateoxid **104b** mit einer Dicke **605d** enthalten, das über der zweiten Body-Region **102b** (über der

ersten Oberflächenregion **402a**) des Trägers **102** angeordnet ist, wobei das dünne geteilte Gateoxid **104b** mit dotiertem Polysilizium als Gate **106b** über dem dünnen geteilten Gateoxid **104b** bedeckt ist. Zum Durchbrechen des dünnen geteilten Gateoxids **104b** kann eine (Schreib-)Spannung **602** an dem dünnen geteilten Gateoxid **104b** angelegt werden, wobei aufgrund der Spannung **602** (z.B. größer als 3 V) das dotierte Polysilizium des Gates **106b** teilweise verarmt sein kann. Zur Veranschaulichung, in dem dotierten Polysilizium des Gates **106b** kann eine Verarmungsregion **607** mit einer Dicke **607d** gebildet werden und infolgedessen kann das dünne geteilte Gateoxid **104b** schwieriger durchzubrechen sein, oder mit anderen Worten, das dünne geteilte Gateoxid **104b** kann nicht zuverlässig durchbrechen, wenn die eine (Schreib-)Spannung **602** angelegt wird. Wie in dem äquivalenten Schaltdiagramm **600b** dargestellt, können das dünne geteilte Gateoxid **104b** und die verarmte Region **607** des Gates **106b** als zwei Kapazitäten **604, 606** in Reihe dienen. Im Fall einer wesentlichen Polyverarmung erfolgt ein signifikanter Spannungsabfall der Sicherungsspannung im Poly. Der Spannungsabfall über das dünne geteilte Gateoxid kann für eine ordnungsgemäße (zuverlässige) Sicherung der 1T Bit-Zellen (des auf einer Anti-Schmelzsicherung beruhenden OTP NVM mit geteiltem Kanal) unzureichend sein.

**[0070]** Für eine zuverlässigere Sicherung kann die Polyverarmung (des Gates **106b** in der OTP Sicherungszellfläche) verringert werden, ohne Auswirkung auf andere Teile der Technologie/ des Chips, z.B. ohne die FETs außerhalb der ersten Oberflächenregion **402a** zu beeinflussen.

**[0071]** Gemäß verschiedenen Ausführungsformen kann das Polysilizium (Poly) des Gates **106b** über dem dünnen geteilten Gateoxid **104b** (in der OTP Sicherungszellfläche) dotiert sein, um die Bildung der verarmten Region **607** im Gate **106b** zu verhindern oder deren Dicke zu verringern.

**[0072]** Zur Veranschaulichung, es kann eine zusätzliche lokale Implantation (z.B. ein p-Typ-Dotieren, wenn der Kanal vom n-Typ ist und der Rest des Gates auch p-Typ dotiert ist) in das Poly-Gate **106b** der Sicherungsfäche der OTP-Zelle ausgeführt werden. Die Sicherungszelle kann als Teil des Feldeffekttransistors **100t** mit geteiltem Gate bezeichnet werden, mit dem dünnen geteilten Gateoxid **104b** und der Sicherungsfäche des dünnen geteilten Gateoxids **104b**.

**[0073]** Die Polyverarmung in der OTP-Zelle kann jedoch beeinflusst werden, ohne alle anderen zu betreffen, z.B. ohne die Dosis des allgemeinen Source/Drain-Implantats zu verändern, das auch zum Dotieren von Gate **106a, 160b** des Feldeffekttransistors **100t** mit geteiltem Gate verwendet wird. Eine Än-

derung der Dosis des allgemeinen Source/Drain-Implantats würde zum Beispiel die Schwellenspannungen aller anderen Vorrichtungen (FETs) auf dem Träger **102** beeinflussen. Ferner würde die Modifizierung des Wärmebudgets nach dem allgemeinen Source/Drain-Implantat alle anderen Vorrichtungen und eine Bildung eines Salicids (z.B. für eine Kontaktbildung) beeinflussen.

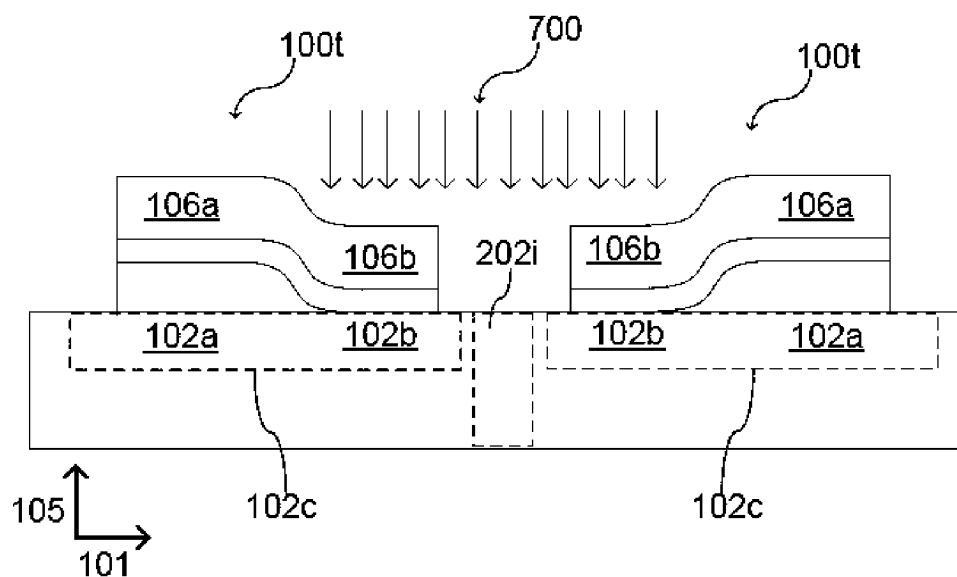

**[0074]** **Fig. 7** zeigt eine Feldeffekttransistorstruktur mit geteiltem Gate **100** mit zwei benachbarten Feldeffekttransistoren **100t** mit geteiltem Gate, z.B. in einer PROM-Region eines Trägers **102**, z.B. eines Chips **102**, gemäß verschiedenen Ausführungsformen. Gemäß verschiedenen Ausführungsformen kann eine Ionenimplantation **700** ausgeführt werden, um die jeweiligen zweiten Gate-Abschnitte **106b** über den dünnen geteilten Gateoxiden **104b** der Feldeffekttransistoren **100t** mit geteiltem Gate lokal zu dotieren. Gemäß verschiedenen Ausführungsformen kann eine Maske über dem Träger **102** vorgesehen sein, die die Gate-Abschnitte **106b** über den dünnen geteilten Gateoxiden **104b** definiert (freilegt), um die elektrische Leitfähigkeit der Gate-Abschnitte **106b** zu erhöhen.

**[0075]** Für dieses zusätzliche Implantat **700** können positiv geladene Ionen verwendet werden. Ferner kann gemäß verschiedenen Ausführungsformen die Dosis des zusätzlichen Implantats (die z.B. in der Implantationsrezeptur verwendet wird) im Bereich von etwa  $5 \cdot 10^{14} \text{ cm}^{-2}$  bis etwa  $1 \cdot 10^{16} \text{ cm}^{-2}$  eingestellt werden, z.B. abhängig von der letztendlichen Polyverarmung des Prozesses. Das Implantat kann durch Messen der elektrischen Oxiddicke des Sicherungsteils der OTP-Zelle im Vergleich zur elektrischen Oxiddicke eines regulären logischen Transistors mit der selben physischen Gateoxiddicke verifiziert werden. Ferner kann gemäß verschiedenen Ausführungsformen das zusätzliche Implantat zu einer endgültigen Dotierungskonzentration im Poly-Gate von etwa  $1 \cdot 10^{21} \text{ cm}^{-3}$  führen (z.B. zu einer Dotierungsendkonzentration nahe dem jeweiligen Löslichkeitsgrenzwert).

**[0076]** **Fig. 8** zeigt einen Träger **102** mit einer Hauptbearbeitungsfläche **102s** in einer Draufsicht, z.B. während der Bearbeitung. Der Träger **102** kann ein Wafer, z.B. ein Siliziumwafer sein. Der Wafer **102** kann Chipregionen oder die Regionen **802** zum Herstellen mehrerer Chips oder Nacktchips aus dem Wafer **102** enthalten. Gemäß verschiedenen Ausführungsformen kann eine Chipregion **802** (oder der Träger **102**) eine Kernregion (eine erste Trägerregion) **802c** enthalten, in der mehrere FETs vom ersten Typ zu bearbeiten sind, z.B. eine CMOS-Logik als Kern des Chips. Ferner kann die Chipregion **802** einen OTP-Bereich (eine dritte Trägerregion) **802a** zum Bearbeiten der Feldeffekttransistorstruktur mit geteiltem Gate **100** oder zum Bearbeiten mehrerer Feldeffekt-

transistoren **100t** mit geteiltem Gate enthalten, z.B. um einen PROM auf dem Chip vorzusehen. Ferner kann die Chipregion **802** eine periphere Region (eine zweite Trägerregion) **802b** enthalten, in der mehrere FETs des zweiten Typs zu bearbeiten sind, z.B. eine auf CMOS beruhende I/O-Region als Peripherie des Kerns des Chips. Gemäß verschiedenen Ausführungsformen kann der Wafer **102** mehrere Chipregionen **802** enthalten.

**[0077]** Im Vergleich zum Beispiel mit **Fig. 4A** bis **Fig. 4E** und **Fig. 5** kann die erste Trägerregion **802c** die dritte Oberflächenregion **402c** enthalten, die zweite Trägerregion **802b** kann die zweite Oberflächenregion **402b** enthalten und/oder die dritte Trägerregion **802a** kann die erste Oberflächenregion **402a** enthalten. Mit anderen Worten, die erste Oberflächenregion **402a** kann in der dritten Trägerregion **802a** vorgesehen sein, die zweite Oberflächenregion **402b** kann in der zweiten Trägerregion **802b** vorgesehen sein und die dritte Oberflächenregion **402c** kann in der ersten Trägerregion **802c** vorgesehen sein.

**[0078]** Gemäß verschiedenen Ausführungsformen kann die Feldeffekttransistorstruktur mit geteiltem Gate **100** im OTP-Bereich **802a** (OTP-Zellenbereich **802a**) mit einer anderen Gateoxid Dicke versehen sein als ein Feldeffekttransistor in einer anderen Region, wenn dieselben Oxidationsprozesse zum Wachsen der Oxide angewendet werden. Daher kann eine Präimplantation von Fluor in den OTP-Bereich **802a** angewendet werden. Ferner kann eine Präimplantation von Stickstoff in alle Bereiche des Chips, mit Ausnahme des OTP-Bereichs **802a** angewendet werden. Gemäß verschiedenen Ausführungsformen führt ein anschließend durchgeführter Ofenprozess (thermische Oxidation) für dünne Gateoxide und dicke Gateoxide zu einer verringerten Dicke des dünnen Oxsids im OTP-Bereich **802a** des Chips und zu einer erhöhten Dicke des dicken Oxsids im OTP-Bereich **802a** des Chips.

**[0079]** Gemäß verschiedenen Ausführungsformen kann der OTP-Bereich **802a** ferner Regionen zur Bildung eines dualen Gateoxids und Regionen zur Bildung eines einzelnen Gateoxids für die jeweilige Feldeffekttransistorstruktur mit geteiltem Gate **100** enthalten, wobei das Fluor in die Regionen des OTP-Bereichs **802a** zur Bildung des dualen Gateoxids implantiert werden kann und wobei Stickstoff in die Regionen des OTP-Bereichs **802a** zur Bildung des einzelnen Gateoxids implantiert werden kann.

**[0080]** Gemäß verschiedenen Ausführungsformen können zusätzlich andere Prozesse angewendet werden, die allgemein in der CMOS-Bearbeitung verwendet werden, z.B. kann ein thermisches Ausheilen verwendet werden (z.B. kann ein Wärmebudget vorgesehen sein), um implantierte Ionen zu aktivieren. Ferner können Strukturierungs- und Schichtungspro-

zesse angewendet werden und zum Beispiel können strukturierte Maskenschichten während der Bearbeitung vorgesehen sein, um die gewünschten Strukturen auf dem Träger zu bilden.

**[0081]** Gemäß verschiedenen Ausführungsformen wird hier eine 1T (Ein-Transistor) OTP-Architektur mit geteiltem Kanal vorgesehen, die auf Basis einer Anti-Schmelzsicherung konfiguriert ist. Die Bits können zuverlässig durch einen gesteuerten, irreversiblen Oxiddurchbruch in der Bit-Zelle der 1T OTP-Architektur mit geteiltem Kanal programmiert werden. Eine Integration einer solchen 1T OTP-Architektur mit geteiltem Kanal in eine etablierte Technologie kann zum Beispiel die Verwendung von nur zwei verfügbaren Gateoxiden (von logischen Vorrichtungen) ermöglichen: z.B. ein dünnes Gateoxid von zum Beispiel etwa 2,2 nm und ein dickes Gateoxid von zum Beispiel etwa 5,2 nm oder z.B. sämtlicher anderer zwei spezifischer Dicken für das dünne Gateoxid und das dicke Gateoxid.

**[0082]** Gemäß verschiedenen Ausführungsformen kann es wünschenswert sein, geringere Werte als 2,2 nm für das dünne Gateoxid in der OTP-Zelle zu haben, die ermöglichen, dass eine niedrigere Spannung zum Sichern der OTP-Zelle und eine stabilere Sicherung aufgrund eines stabileren Perkolationspfades erreicht wird. Ferner kann es gemäß verschiedenen Ausführungsformen wünschenswert sein, höhere Werte als 5,2 nm für das dicke Gateoxid in der OTP-Zelle zu haben: z.B. kann im Bereich von etwa 7 nm bis etwa 8 nm die Wahrscheinlichkeit für ein Trap-unterstütztes Tunneln abnehmen. Verschiedene Ausführungsformen können auf der Erkenntnis beruhen, dass das Optimum der Oxide, die in einer Sicherungsanwendung verwendet werden, sich von den Gateoxiden der regulären logischen Vorrichtungen einer Technologie unterscheiden kann. Eine Einführung weiterer Oxide nur für eine optimierte Sicherungsanwendung kann teuer sein und kann das Wärmebudget verschieben und/oder kann die Vorrichtungen einer bereits bestehenden Technologie beeinflussen.

**[0083]** Gemäß verschiedenen Ausführungsformen kann ein modifizierter Prozessablauf angewendet werden, um optimierte Oxide für eine Sicherungsanwendung zu erzeugen, ohne Auswirkung auf das Wärmebudget der bereits bestehenden Technologie und ohne Einführung neuer Oxide (z.B. ohne Einführung eines dritten thermischen Oxidationsprozesses). Daher kann gemäß verschiedenen Ausführungsformen das Oxid wachsen lokal durch Präimplantation von Stickstoff und/oder Fluor verändert werden. Mit Stickstoff kann ein verlangsamtes und mit Fluor ein beschleunigtes Wachsen in dem späteren Oxidofenprozess erreicht werden. Die Auswirkung einer Stickstoff-Präimplantation ist nur für eine Nassofenoxidation gegeben. Die Auswirkung ei-

ner Fluor-Präimplantation ist nur für Nassofenoxidationen (z.B. Verwendung von Wasser oder einer anderen Flüssigkeit als Oxidationsmittel) und Trockenofenoxidationen (z.B. Verwendung von gasförmigen Sauerstoff oder einem anderen Gas als Oxidationsmittel) gegeben.

**[0084]** Gemäß verschiedenen Ausführungsformen kann ein zusätzlicher Lithographieprozess in einer bereits bestehenden Technologie angewendet werden, um eine Blockmaske für einen anschließenden Implantationsschritt vorzusehen. Unter Verwendung der Blockmaske kann eine lokale Implantation von Stickstoff oder Fluor ausgeführt werden. Daher kann ein verlangsamtes oder beschleunigtes Sauerstoffwachsen während des Ofenprozesses in jenen Bereichen erhalten werden, was zu veränderten Oxiddicken führt. Die Fluor-Präimplantation kann die Oxidqualität verbessern. Der Prozessablauf (die Präimplantation von Stickstoff und/oder Fluor) kann durch SIMS (sekundäre Ionenmassenspektrometrie) Analyse (für Konzentrationen höher als etwa  $10^{12} \text{ cm}^{-3}$ ) verifiziert werden.

**[0085]** Gemäß verschiedenen Ausführungsformen kann die Bearbeitung, wie hier beschrieben, ein Vorsehen optimierter Oxiddicken für eine Sicherungsanwendung unabhängig von den Oxiden der logischen Vorrichtungen des Grundprozesses ermöglichen. Dies kann ohne Auswirkung auf das Wärmebudget der Grundtechnologie und ohne Einführung einer neuen Oxidabscheidung erfolgen. Mit einem optimierten dünnen Oxid in der Sicherungsanwendung (in der Sicherungszelle) kann die Sicherungsspannung verringert werden. Ferner kann der Sicherungsprozess selbst stabiler sein, was zum Beispiel zu einer verringerten Versagensrate und einer höheren Zuverlässigkeit und/oder einem stabilen Sicherungsverhalten in einem weiten Temperaturbereich führt, z.B. im Bereich von etwa  $-50^\circ\text{C}$  bis etwa  $150^\circ\text{C}$ . Ferner kann mit einem Oxid optimaler Dicke in der Sicherungsanwendung die erzeugte Sicherungsspannung erhöht werden oder die geeignete Sicherungsspannung kann erhöht werden. Die Zugangsvorrichtung (mit dem dicken geteilten Gateoxid) der 1T OTP-Architektur mit geteiltem Kanal kann gegenüber parasitären Leckpfaden während des Sicherungsprozesses stabiler sein.

**[0086]** Gemäß verschiedenen Ausführungsformen kann eine 1T OTP-Architektur mit geteiltem Kanal (eine Feldeffekttransistorstruktur mit geteiltem Gate **100**) in eine bereits etablierte Technologie integriert werden, einschließlich FETs in CMOS-Technologie, wobei nur zwei verfügbare Gateoxide (von logischen Vorrichtungen) zur Herstellung der 1T OTP-Architektur mit geteiltem Kanal und der FETs auf einem Träger verfügbar sein können: z.B. können zwei Gateoxidprozesse zur Herstellung eines dünnen Gate-

oxids und eines dicken Gateoxids angewendet werden.

**[0087]** Es kann jedoch der Fall eintreten, dass die zwei verfügbaren Gateoxidprozesse an sich die Herstellung einer zuverlässigen OTP-Zelle nicht ermöglichen, wobei zum Beispiel die OTP-Zelle mit einem dickeren dicken Gateoxid (z.B. einer dickeren geteilten Gateoxid mit Dualschicht) und einem dünneren dünnen Gateoxid (z.B. einem dünneren geteilten Gateoxid mit Einzelschicht) stabiler und/oder zuverlässiger sein können. Gemäß verschiedenen Ausführungsformen können Regionen im OTP-Bereich des Trägers (z.B. die zweite Body-Region **102b** in der ersten Oberflächenregion **402a** des Trägers **102**), die eine dünne Gateoxid Dicke haben sollten, einer Stickstoff-Präimplantation unterzogen werden. Ferner können gemäß verschiedenen Ausführungsformen Regionen im OTP-Bereich des Trägers (z.B. die erste Body-Region **102a** in der ersten Oberflächenregion **402a** des Trägers **102**), die eine dicke Gateoxiddicke haben können, einer Fluor-Präimplantation unterzogen werden. Daher kann der Gateoxid-Ofenprozess verlangsamt und/oder beschleunigt werden, was zu lokal unterschiedlichen Dicken für das gewachsene Gateoxid führen kann. Daher können gemäß verschiedenen Ausführungsformen das dünne geteilte Gateoxid und das dicke geteilte Gateoxid der OTP-Zelle (die Feldeffekttransistorstruktur mit geteiltem Gate **100**) unabhängig von dem zugrunde liegenden Prozess vorgesehen werden.

**[0088]** Im Allgemeinen kann das Poly des Gates eines Feldeffekttransistors wie folgt hergestellt werden: das Poly kann über dem Gateoxid abgeschieden werden, das Poly kann dotiert werden (z.B. in demselben Implantationsprozess, der zum Vorsehen der Source/Drain-Regionen verwendet wird), ein Wärmebudget kann angewendet werden und/oder das Poly kann strukturiert werden. Daher können die Eigenschaften des Gates von Folgendem abhängig sein: dem Dotieren, dem Wärmebudget und der Struktur des Poly (z.B. der Korngröße). Für höhere Salicid-Ausheilungstemperaturen kann eine Deaktivierung der Dotierungsmittel bezogen auf eine höhere Polyverarmung im Falle einer angelegten Spannung erfolgen. Während der Sicherung der OTP-Zelle kann eine hohe Spannung bis zu 8 V an das Gate angelegt werden (z.B. als ein sogenannter Programmierungspuls mit einer Pulsdauer im Bereich von etwa mehreren Nanosekunden bis etwa einhundert Nanosekunden). Durch diese hohe Spannung kann eine große Polyverarmungsschicht gebildet werden, die mit einem hohen Spannungsabfall bereits im Poly des Gates verbunden ist. Infolgedessen kann der verbleibende Spannungsabfall über dem dünnen Gateoxid nicht ausreichend sein, um das dünne Gateoxid durchzubrennen (durchzubrechen). Ferner kann gemäß verschiedenen Ausführungsformen der Programmierungspuls zum Durchbrennen der OTP-Zel-

le zu kurz sein, um eine Umkehr des Poly-Gates zu ermöglichen, die bei Spannungen eintreten kann, die höher als etwa 4 V oder höher als etwa 5 V sind. Für eine große Speicherkapazität oder einen großen Programmierungsinhalt können kurze Programmierungspulse für eine zeiteffiziente Programmierung gewünscht sein. Daher kann ein Vermeiden oder zumindest Verringern der Verarmung des Poly-Gates für die Programmierung der OTP-Zelle relevant sein.

**[0089]** Wenn ein OTP (einmalig programmierbarer) Zellaufbau, z.B. mit einem Polysilizium-Siliziumoxid-Kontakt, in einen bereits bestehenden Prozess eingeführt werden kann, kann eine hohe Poly-Verarmung eintreten, wenn hohe Sicherungsspannungen angelegt werden. Während des Sicherungsprozesses fällt bereits ein Teil der Sicherungsspannung in dieser Verarmung und die effektive erhaltene Sicherungsspannung für das Oxid ist verringert (z.B. zumindest für kurze Programmierungspulse mit einer Dauer von weniger als etwa 100 ns). Infolgedessen muss die Sicherungsspannung in diesem Fall erhöht werden, um die Sicherungszelle der OTP-Zelle durchzubrennen. Wenn jedoch die Peripherie der OTP-Zelle keine weitere Erhöhung der Sicherungsspannung zulässt, muss das Design des OTP-Speichermakros geändert werden, z.B. um das Anlegen höherer Sicherungsspannungen zu ermöglichen. Dies kann im Allgemeinen einen größeren Bereich des Makros oder die Verwendung von Peripherievorrichtungen, die für höhere Spannungen geeignet sind, erfordern.

**[0090]** Gemäß verschiedenen Ausführungsformen kann die Poly-Verarmung in der OTP Sicherungszelle durch einen zusätzlichen Verfahrensschritt während der Herstellung der OTP Sicherungszelle verhindert werden. Dies kann ohne Auswirkung auf andere Teile der Chipfläche erfolgen. Ferner kann das OTP Design unverändert bleiben, da z.B. das Anlegen einer höheren Sicherungsspannung nicht erforderlich sein kann. Der zusätzliche Verfahrensschritt kann an individuelle Verfahrensbedingungen für eine Poly-Verarmung angepasst werden, um die Poly-Verarmung zu verhindern oder zu verringern. Der zusätzliche Verfahrensschritt kann eine lokale Implantation in das Polysilizium der Sicherung enthalten, um die Dotierungsmittelkonzentration des Polysiliziums zu erhöhen und die Bildung einer verarmten Zone während einer Hochsicherungsspannungsanwendung zu vermeiden. Gemäß verschiedenen Ausführungsformen können die Poly-Verarmung und der zugehörige Spannungsabfall in diesem Bereich während des Schmelzens der OTP-Zelle vermieden oder verringert werden.

**[0091]** Gemäß verschiedenen Ausführungsformen kann die elektrische Gateoxid Dicke mittels einer Mikrosondierung des Sicherungsteils der OTP-Zelle bestimmt werden. Dieser Wert kann mit jenem eines re-

gulären Transistors mit derselben physischen Gateoxid Dicke verglichen werden. Die elektrische Gateoxid Dicke der OTP-Zelle mit verringelter Poly-Verarmung kann geringer sein und besser zu dem durch die physische Dicke bestimmten Wert passen.

**[0092]** Gemäß verschiedenen Ausführungsformen kann ein Verfahren zum Bearbeiten eines Trägers enthalten: Dotieren des Trägers mit Fluor, so dass eine erste Oberflächenregion des Trägers fluordotiert ist und eine zweite Oberflächenregion des Trägers frei von der Fluordotierung und/oder weniger fluordotiert als die erste Oberflächenregion ist; und Oxidieren des Trägers, um ein erstes Gateoxid von der ersten Oberflächenregion des Trägers mit einer ersten Dicke zu wachsen und gleichzeitig ein zweites Gateoxid von der zweiten Oberflächenregion des Trägers mit einer zweiten Dicke zu wachsen, die sich von der ersten Dicke unterscheidet.