(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5316612号

(P5316612)

(45) 発行日 平成25年10月16日(2013.10.16)

(24) 登録日 平成25年7月19日(2013.7.19)

|              |               |

|--------------|---------------|

| (51) Int.Cl. | F 1           |

| H01L 21/205  | (2006.01)     |

| C23C 16/42   | (2006.01)     |

| C30B 29/36   | (2006.01)     |

| C30B 33/02   | (2006.01)     |

|              | HO 1 L 21/205 |

|              | C 23 C 16/42  |

|              | C 30 B 29/36  |

|              | C 30 B 33/02  |

請求項の数 5 (全 12 頁)

|            |                                     |

|------------|-------------------------------------|

| (21) 出願番号  | 特願2011-173502 (P2011-173502)        |

| (22) 出願日   | 平成23年8月9日(2011.8.9)                 |

| (62) 分割の表示 | 特願2006-226368 (P2006-226368)<br>の分割 |

| 原出願日       | 平成18年8月23日(2006.8.23)               |

| (65) 公開番号  | 特開2011-233932 (P2011-233932A)       |

| (43) 公開日   | 平成23年11月17日(2011.11.17)             |

| 審査請求日      | 平成23年8月9日(2011.8.9)                 |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000005083<br>日立金属株式会社<br>東京都港区芝浦一丁目2番1号    |

| (74) 代理人  | 100101683<br>弁理士 奥田 誠司                     |

| (74) 代理人  | 100155000<br>弁理士 喜多 修市                     |

| (72) 発明者  | 堀 勉<br>大阪府三島郡島本町江川2丁目15番17号 日立金属株式会社山崎製作所内 |

審査官 大塚 徹

最終頁に続く

(54) 【発明の名称】炭化珪素半導体エピタキシャル基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

オフセット角が2°以上10°以下である4H炭化珪素単結晶基板を用意する工程と、化学気相堆積法により、1400以上1650以下の温度で、炭化珪素からなるエピタキシャル層を前記炭化珪素単結晶基板上に成長させる工程と、前記エピタキシャル層を1300以上1800以下の温度で熱処理する工程と、を包含し、

前記エピタキシャル層を成長させる工程において、原料ガス中の炭素原子の珪素原子に対する比C/Siは1.5以上2以下であり、

前記エピタキシャル層を成長させる工程を、3kPa以上54kPa以下の圧力で行い

10

前記エピタキシャル層を成長させる工程は、前記エピタキシャル層中の点欠陥Z<sub>1/2</sub>センターの密度が1×10<sup>12</sup>cm<sup>-3</sup>以下であり、点欠陥E<sub>H<sub>6/7</sub></sub>センターの密度が5×10<sup>1</sup>cm<sup>-3</sup>以下となる成長条件で前記エピタキシャル層を成長させ、

前記エピタキシャル層を10μm/h以上、23μm/h以下の速度で成長させる、炭化珪素半導体エピタキシャル基板の製造方法。

## 【請求項 2】

前記エピタキシャル層を成長させる工程において成長するエピタキシャル層は、深い準位過渡分光法において、炭化珪素半導体の伝導帯の下端からの活性化エネルギー差E<sub>a</sub>が1.33eV以上1.53eV以下である準位のピークが、点欠陥E<sub>H<sub>6/7</sub></sub>センターの

20

ピークから分離して観測される請求項 1 に記載の炭化珪素半導体エピタキシャル基板の製造方法。

**【請求項 3】**

前記エピタキシャル層を成長させる工程は、前記エピタキシャル層中において、炭化珪素半導体の伝導帯の下端からの活性化エネルギー差  $E_a$  が  $1.33\text{ eV}$  以上  $1.53\text{ eV}$  以下の準位を持つ点欠陥の密度が  $3 \times 10^{11}\text{ cm}^{-3}$  以上となる成長条件で前記エピタキシャル層を成長させる請求項 2 に記載の炭化珪素半導体エピタキシャル基板の製造方法。

**【請求項 4】**

前記エピタキシャル層を熱処理する工程は、前記エピタキシャル層中において、前記  $E_a$  が  $1.33\text{ eV}$  以上  $1.53\text{ eV}$  以下の準位を持つ点欠陥の密度が前記熱処理を行う前の  $1/2$  以下となる条件で前記エピタキシャル層を熱処理する請求項 1 に記載の炭化珪素半導体エピタキシャル基板の製造方法。 10

**【請求項 5】**

前記エピタキシャル層を熱処理する工程は、前記エピタキシャル層中において、前記  $1.33\text{ eV}$  以上  $1.53\text{ eV}$  以下の準位を持つ点欠陥の密度が  $3 \times 10^{11}\text{ cm}^{-3}$  以下となる条件で前記エピタキシャル層を熱処理する請求項 4 に記載の炭化珪素半導体エピタキシャル基板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、炭化珪素半導体エピタキシャル基板の製造方法に関する。 20

**【背景技術】**

**【0002】**

従来、高周波、大電力の制御を目的として、シリコンを用いた電力用半導体素子（パワー・デバイス）の開発が進められ、様々な改良により大幅な素子特性の向上が図られてきた。しかし、現在こうした電力用半導体素子の素子性能は、ほぼシリコンの物性から計算される理論上の限界値に近づいている。このため、素子特性をさらに向上させる目的で、新たな半導体材料を用いた電力用半導体素子が検討されている。

**【0003】**

そのような電力用半導体素子の半導体材料として、炭化珪素半導体が注目されている。炭化珪素半導体はシリコン半導体より一桁以上高い絶縁破壊電界を持つため、高耐圧デバイスへの適用が可能と見られるほか、耐熱性に優れるなどシリコンと比較してはるかに優れた半導体特性をもつと期待されている。 30

**【0004】**

炭化珪素半導体を用いて電力用半導体素子を作製する場合、通常、化学気相堆積法と呼ばれる方法を用いて、炭化珪素単結晶基板上に炭化珪素単結晶薄膜をエピタキシャル成長させる必要がある。たとえば、炭化珪素基板を加熱した状態で、 $\text{Si}$  原子を供給するための  $\text{SiH}_4$  ガスおよび  $\text{C}$  原子を供給するための  $\text{C}_2\text{H}_2$  ガスや  $\text{C}_3\text{H}_8$  ガスを導入することにより、基板上にエピタキシャル層を成長させる。

**【0005】**

しかし、一般に高品位の炭化珪素半導体単結晶を得ることはシリコン半導体やガリウム砒素半導体に比べて難しい。このため、炭化珪素半導体を用いた電力用半導体素子を実現するために解決すべき課題の 1 つは、高品位の炭化珪素半導体層を得る技術を確立することである。 40

**【0006】**

半導体単結晶の品質は欠陥の密度により評価される。結晶の欠陥としては、点欠陥、線欠陥、面欠陥、体積欠陥に大別され、これらの欠陥が少ないほど結晶の品質は高いと評価される。一般に、これらの欠陥のうち次元の高い欠陥ほど得られる単結晶半導体の物理特性に悪影響を及ぼし、結晶品位を低下させる。

**【0007】**

10

20

30

40

50

特許文献 1 は、エピタキシャル成長の際、異相の混入を防ぐために(0001)面を3~12°傾けた基板を用いて成長を行う方法を開示している。この方法により、線欠陥、面欠陥および体積欠陥を大きく減少させ、結晶品位を高めることができる。現在、炭化珪素単結晶基板上にエピタキシャル層を形成する場合にはこの方法が広く採用されている。

**【先行技術文献】**

**【特許文献】**

**【0008】**

**【特許文献 1】**米国特許第4,912,064号明細書

**【非特許文献】**

**【0009】**

**【非特許文献 1】**K.Fujihira et. al., "High-purity and high-quality 4H-SiC grown at high speed by chimney-type vertical hot-wall chemical vapor deposition", Applied Physics Lett., Vol. 80, No. 9, pp1586-1588

10

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0010】**

一方、点欠陥については、炭化珪素単結晶の結晶品位を評価する1つの指標として、点欠陥密度が計測され、結晶成長条件と点欠陥密度との関係が調べられている(非特許文献1など)。しかし、点欠陥を減少させるための具体的な手法については、これまであまり研究されていない。

20

**【0011】**

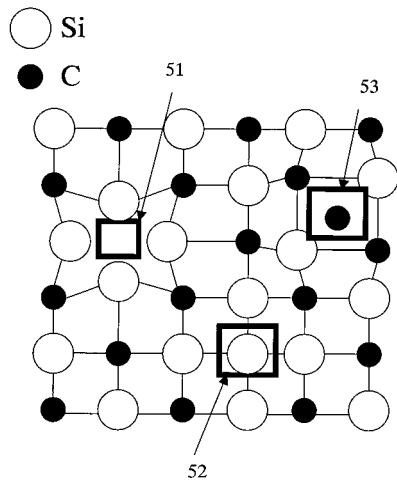

図8は、炭化珪素単結晶中の点欠陥を説明する模式図である。炭化珪素単結晶は、ケイ素原子と炭素原子とが3次元的に交互に配置されることによって構成されている。図8に示すように、本来原子が存在すべき位置に原子が存在しない場合、空孔欠陥51が生じる。また、反対の原子が存在すべき位置に隣接する原子と同じ種類の原子が存在する場合、アンチサイト欠陥52が生じる。さらに、本来珪素および炭素のいずれの原子も存在しない位置にいずれかの原子が存在する場合、格子間原子欠陥53が生じる。点欠陥とは、主にこうした単結晶の結晶格子中に原子1個程度で存在する格子欠陥をいう。広義には不純物との結合体なども点欠陥に含められる。

**【0012】**

30

図8には原子1個による点欠陥しか示していないが、実際には複数個の原子による点欠陥や、これらが組み合わさった複合欠陥(例えば、炭素原子空孔欠陥と、炭素原子がシリコンの位置に収まったアンチサイト欠陥が組み合わさったもの)として存在することもある。

**【0013】**

炭化珪素を電力用半導体素子に用いる場合、数kV以上の耐圧が要求されるため、炭化珪素半導体層を10μm以上形成することが好ましい。このため、実用的な時間で炭化珪素半導体層を形成するためには、10μm/h以上の成長速度で炭化珪素半導体層を成長させることが好ましい。

**【0014】**

40

しかし、10μm/h以上の成長速度が得られるような条件で、成長した従来の炭化珪素半導体層には、 $10^{13} \text{ cm}^{-3}$ 程度の点欠陥が存在している。半導体層中に点欠陥が存在すると、図9に示すように、伝導帯55と価電子帯56との間の本来準位が存在しない禁制帯に、準位57が発生する。これを一般的に「深い準位(deep level)」と呼ぶ。こうした点欠陥による準位は、点欠陥の種類などによって異なるエネルギーを持つ。半導体中の深い準位は、バイポーラデバイスの伝導度変調の効果を低減させ、この結果、バイポーラデバイスの順方向の抵抗が増加するといった悪影響を及ぼすと考えられる。また、逆方向の漏れ電流を増加させるといった問題点も指摘されている。

**【0015】**

本発明はこのような従来技術の上記の課題を解決するためになされたものであり、点欠

50

陥の少ない炭化珪素半導体エピタキシャル基板を製造する方法を提供することを目的とする。

**【課題を解決するための手段】**

**【0016】**

本発明の炭化珪素半導体エピタキシャル基板の製造方法は、オフセット角が2°以上10°以下である4H炭化珪素単結晶基板を用意する工程と、化学気相堆積法により、1400以上1650以下の温度で、炭化珪素からなるエピタキシャル層を前記炭化珪素単結晶基板上に成長させる工程と、前記エピタキシャル層を1300以上1800以下の温度で熱処理する工程とを包含する。

**【0017】**

ある好ましい実施形態において、前記エピタキシャル層を成長させる工程は、前記エピタキシャル層中の点欠陥 $Z_{1/2}$ センターの密度が $1 \times 10^{12} \text{ cm}^{-3}$ 以下であり、点欠陥 $E_{H_{6/7}}$ センターの密度が $5 \times 10^{11} \text{ cm}^{-3}$ 以下となる成長条件で前記エピタキシャル層を成長させる。

**【0018】**

ある好ましい実施形態において、前記エピタキシャル層を成長させる工程は、前記エピタキシャル層において、炭化珪素半導体の伝導帯の下端からの活性化エネルギー差 $E_a$ が1.33eV以上1.53eV以下の準位を持つ点欠陥の密度が $3 \times 10^{11} \text{ cm}^{-3}$ 以上となる成長条件で前記エピタキシャル層を成長させる。

**【0019】**

ある好ましい実施形態において、前記エピタキシャル層を熱処理する工程は、前記エピタキシャル層中において、前記 $E_a$ が1.33eV以上1.53eV以下の準位を持つ点欠陥の密度が前記熱処理を行う前の1/2以下となる条件で前記エピタキシャル層を熱処理する。

**【0020】**

ある好ましい実施形態において、前記エピタキシャル層を熱処理する工程は、前記エピタキシャル層において、前記1.33eV以上1.53eV以下の準位を持つ点欠陥の密度が $3 \times 10^{11} \text{ cm}^{-3}$ 以下となる条件で前記エピタキシャル層を熱処理する。

**【0021】**

ある好ましい実施形態において、前記エピタキシャル層を成長させる工程は、前記エピタキシャル層を $10 \mu\text{m}/\text{h}$ 以上の速度で成長させる。

**【0022】**

ある好ましい実施形態において、前記エピタキシャル層を成長させる工程における、原料ガス中の炭素原子の珪素原子に対する比 $C/Si$ は1.5以上2以下である。

**【0023】**

ある好ましい実施形態において、前記エピタキシャル層を成長させる工程により成長するエピタキシャル層は、深い準位過渡分光法において、炭化珪素半導体の伝導帯の下端からの活性化エネルギー差 $E_a$ が1.33eV以上1.53eV以下の準位のピークが、点欠陥 $E_{H_{6/7}}$ センターのピークから分離して観測される。

**【発明の効果】**

**【0024】**

本発明によれば、点欠陥密度が小さく、良好な品質のエピタキシャル層を有する炭化珪素半導体エピタキシャル基板が得られる。この基板を用いて作成された半導体素子は、優れた半導体特性を備える。

**【図面の簡単な説明】**

**【0025】**

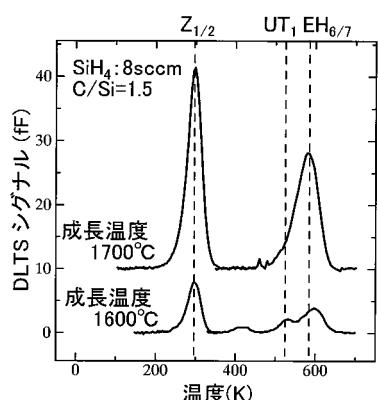

【図1】1700および1600で成長させた炭化珪素エピタキシャル層を深い準位過渡分光法により解析した結果を示している。

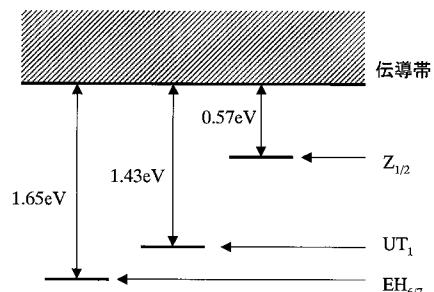

【図2】炭化珪素エピタキシャル層中の点欠陥の準位を示す図である。

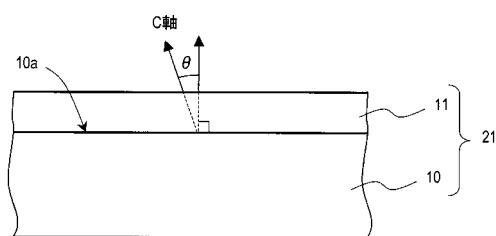

【図3】本発明の炭化珪素半導体エピタキシャル基板の製造方法によって製造される炭化

10

20

30

40

50

珪素半導体エピタキシャル基板の構造を示す模式図である。

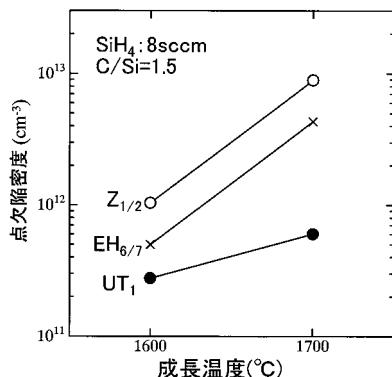

【図4】炭化珪素エピタキシャル層中の点欠陥密度の成長温度依存性を示すグラフである。

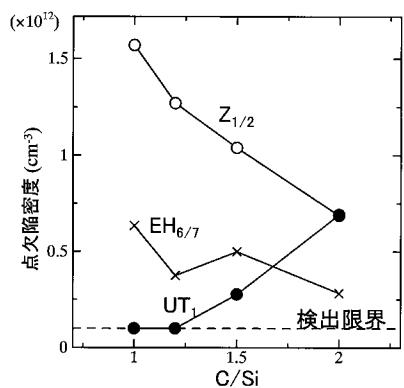

【図5】炭化珪素エピタキシャル層中の点欠陥密度のC/Si比依存性を示すグラフである。

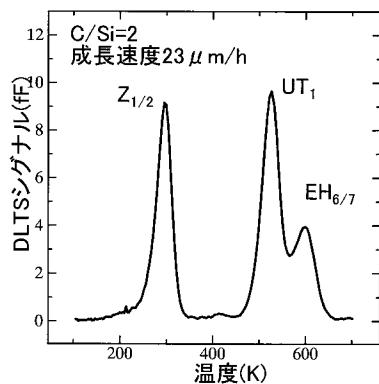

【図6】本発明の炭化珪素半導体エピタキシャル基板の製造方法によって形成した熱処理前のエピタキシャル層を深い準位過渡分光法により解析した結果を示している。

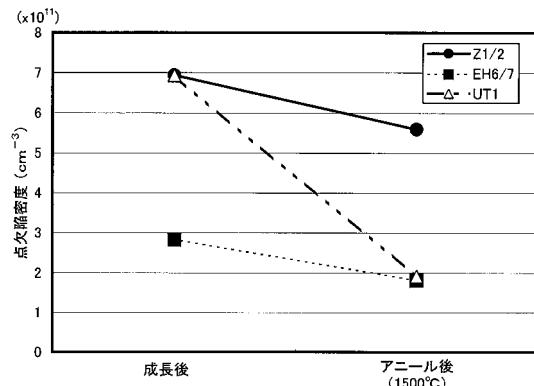

【図7】熱処理前後のエピタキシャル層中の点欠陥密度を示すグラフである。

【図8】点欠陥を説明する模式図である。

【図9】点欠陥の準位を示す図である。

【発明を実施するための形態】

【0026】

本願発明者は、炭化珪素単結晶基板上に種々の条件で炭化珪素からなるエピタキシャル層を形成し、エピタキシャル層中の点欠陥密度が減少する条件について、詳細に検討を行った。

【0027】

これまでの研究報告では、電力用半導体素子を実現するため、エピタキシャル層の成長を実用的な時間で行うことを重視し、エピタキシャル層の成長条件が検討されてきた。このため、概ね $10\text{ }\mu\text{m/h}$ 以上の成長速度を達成することが可能なように、原料ガスの分解を促進することのできる $1700$ 以上的温度でエピタキシャル層を成長させることができた。

【0028】

しかし、成長温度が高いと、反応系中のエントロピーが高くなることにより、エピタキシャル層中の点欠陥が増加してしまう可能性があると考えられる。本願発明者は、従来の炭化珪素エピタキシャル層における深い準位密度が高い原因是、高い成長温度にあると考え、エピタキシャル層を成長させる条件を検討した。

【0029】

その結果、成長温度を $1650$ 以下に設定することにより、エピタキシャル層中の点欠陥の密度を減少させることできることがわかった。図1は、 $1700$ および $1600$ の温度で成長させた炭化珪素からなるエピタキシャル層を、深い準位過渡分光法(DLTS)により解析した結果を示している。図において、横軸は温度を示し、縦軸はシグナル強度を示している。

【0030】

図1に示すように $1700$ の温度で成長させたエピタキシャル層には、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $E_{H_{6/7}}$ センターに基づく強いピークが観測される。ここで、点欠陥は、炭化珪素半導体の伝導帯の下端からの活性化エネルギー差 $E_a$ で示されるエネルギー準位を有し、通常、発見者等にちなんだ名称がつけられる。DLTSのグラフでは、

$E_a$ に対応する温度において、その点欠陥に対応するピークが観測される。点欠陥 $Z_{1/2}$ センターは、 $Z_1$ センターおよび $Z_2$ センターを含む総称である。 $Z_1$ センターおよび $Z_2$ センターに帰属するピークは近接しており、また、 $Z_2$ センターのピークは小さい。このため、通常、2つのピークは分離して観測されない。 $E_{H_{6/7}}$ センターも同様である。

【0031】

図1から明らかなように、 $1600$ の温度で成長させたエピタキシャル層にも、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $E_{H_{6/7}}$ センターは観測される。しかし、これらのピークは $1700$ の温度で成長させたエピタキシャル層に比べて、小さくなっている。このことは、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $E_{H_{6/7}}$ センターの密度が小さくなっていることを示している。

【0032】

また、図1に示すように、 $1600$ の温度で成長させたエピタキシャル層には、 $1700$ の温度で成長させたエピタキシャル層では観測されなかった新たなピークが、 $52$

10

20

30

40

50

0 K付近の温度において、点欠陥E H<sub>6/7</sub>センターのピークから分離して観測される。このピークに帰属する点欠陥はこれまで報告されておらず、本願発明者が発見した。以下、このピークに由来する点欠陥をU T<sub>1</sub>(Unknown Trap 1)センターと称する。

#### 【0033】

図2は、1600 の温度で成長させたエピタキシャル層で観測された欠陥のエネルギー準位を模式的に示している。図2に示すように、点欠陥Z<sub>1/2</sub>センターおよび点欠陥E H<sub>6/7</sub>センターは、炭化珪素半導体の伝導帯下端からそれぞれ0.57 eVおよび1.65 eVの活性化工エネルギー差を有する準位に位置している。また、本願発明者が発見した点欠陥U T<sub>1</sub>センターは1.33 eVから1.53 eVの準位を有し、典型的には1.43 eVのエネルギー準位を有していることが分かった。

10

#### 【0034】

六方晶炭化珪素半導体(4H)の禁制帯は3.26 eVであり、点欠陥E H<sub>6/7</sub>センターおよび点欠陥U T<sub>1</sub>センターによる準位は、禁制帯のほぼ中間に位置する。このため、点欠陥E H<sub>6/7</sub>センターおよび点欠陥U T<sub>1</sub>センターは、キャリアが禁制帯を超えて再結合する原因となりやすい。したがって、発見した点欠陥U T<sub>1</sub>の密度も低減しなければ、良好な品位を有する炭化珪素半導体エピタキシャル基板は得られない。

#### 【0035】

さらに詳細に実験を行い、実験結果を検討することにより、発見した点欠陥U T<sub>1</sub>センターは、生成したエピタキシャル層を熱処理することによって、低減できることが分かった。また、エピタキシャル層の点欠陥の密度はエピタキシャル層を生成する際の原料比にも依存することが分かった。

20

#### 【0036】

これら検討の結果、従来に比べ比較的低温でエピタキシャル層を成長させることによって、公知の点欠陥Z<sub>1/2</sub>センターおよび点欠陥E H<sub>6/7</sub>センターの密度を低減させることができ、その後エピタキシャル層を熱処理することによって点欠陥U T<sub>1</sub>センターの密度を低減できることが分かった。これにより、点欠陥密度が小さく、良好な品質のエピタキシャル層を有する炭化珪素半導体エピタキシャル基板が得られる。

#### 【0037】

以下、本発明による炭化珪素半導体エピタキシャル基板の製造方法を詳細に説明する。

#### 【0038】

30

まず、図3に示すように炭化珪素単結晶基板10を用意する。炭化珪素単結晶基板10を構成する炭化珪素単結晶は六方晶構造を備え、4H-SiCである。炭化珪素単結晶基板10の表面(主面)10aの(0001)面のC軸に対するオフセット角θは2°以上10°以下である。オフセット角が2°未満である場合や10°より大きい場合には、異相が生じるなど、体積欠陥、面欠陥、線欠陥が生じやすく、不純物を含まない炭化珪素エピタキシャル層の成長が困難となる。

#### 【0039】

炭化珪素単結晶基板10は、たとえば、公知の方法を用いて単結晶炭化珪素の塊体から切り出される。炭化珪素の塊体の切断には、外周刃または内周刃のカッティングブレードや、ワイヤーソーなどを用いることができる。炭化珪素の塊体は、SiおよびC以外のP型あるいはN型不純物となる元素を含んでいてもよい。また、置換元素としてGeなどの他のIV族元素を含んでいてもよい。また、重金属不純物としてバナジウム(V)などを含んでいてもよい。本願明細書では、これら、不純物元素や置換元素を含む炭化珪素を総称して、炭化珪素と呼ぶ。炭化珪素基板10の外形に特に制限はなく、種々の大きさ、厚さおよび平面形状のものを本発明に用いることができる。たとえば、2インチの直径および500 μm程度の厚さを備えた円板状の炭化珪素単結晶基板を用意する。

40

#### 【0040】

塊体から切り出された炭化珪素単結晶基板10は、公知の手順によって、表面に生じた加工変質層が除去され、基板表面及び裏面の面粗度が所定の値になるまで機械的研磨が施される。さらに、エピタキシャル成長を行う表面10aは、ダイヤモンドなどの砥粒によ

50

り面粗度 R M S が 0 . 2 ~ 2 nm になるまで鏡面研磨される。ここで、面粗度 R M S は、原子間力顕微鏡 ( A F M ) にて試料の 10 μm のエリアを測定した値をいう。

#### 【 0 0 4 1 】

機械的研磨の後、化学的機械研磨や、反応性イオンエッティングにより、表面 10 a をさらに平滑にし、面粗度 R M S を 0 . 1 nm 以下することが好ましい。特開 2005 - 064392 号公報に開示されるように、プラズマ酸化と反応性イオンエッティングを繰り返し研磨する方法を併用してもよい。より平滑に研磨するには少なくとも最後の研磨工程で化学的機械研磨を施すことが好ましい。

#### 【 0 0 4 2 】

表面 10 a の面粗度 R M S が 0 . 1 nm を越えると、炭化珪素単結晶基板 10 の表面 10 a 近傍のみに存在する基底面転位が除去しきれずに残存し、成長するエピタキシャル層 11 の特性に影響を及ぼす可能性がある。表面 10 a の面粗度 R M S は、より好ましくは、0 . 05 nm 以下である。

#### 【 0 0 4 3 】

次に、炭化珪素単結晶基板 10 の表面 10 a 上にエピタキシャル層 11 を成長させる。エピタキシャル層 11 を成長させる前に炭化珪素単結晶基板 10 の表面 10 a を水素エッティングしてもよい。水素エッティングは、たとえばエピタキシャル成長を行う炉内において、水素雰囲気下で炭化珪素単結晶基板 10 を加熱することによって行うことができる。水素ガス中には C<sub>3</sub>H<sub>8</sub>などの炭化水素や HCl などのハロゲン化水素が含まれていてもよい。これにより、基板表面の加工変質層を除去し、加工により基板表面に導入された基底面転位を除去でき、エピタキシャル薄膜に伝播する基底面転位を減少させることができる。水素エッティングは 1300 以上 1800 以下の温度で炭化珪素単結晶基板 10 を保持しながら行うことが好ましい。1300 未満では加工変質層を除去しきれない可能性がある。加工変質層を除去するには 1800 で充分でありこれを越える温度は非実用的である。水素エッティングに要する時間は通常、10 分以上 90 分以下程度である。またエッティングを行う炉内の圧力は 3 kPa 以上 32 kPa 以下程度で、水素ガスの流量は 1 s 1 m ( 1 × 10<sup>-3</sup> s m<sup>3</sup> / 分 ) 以上 30 s 1 m ( 30 × 10<sup>-3</sup> s m<sup>3</sup> / 分 ) 以下程度が好ましい。ここで s は標準状態を意味する。

#### 【 0 0 4 4 】

エピタキシャル成長は、化学気相堆積法により行う。具体的には、炭化珪素単結晶基板 10 を 1400 以上 1650 以下に加熱し、炉内の圧力を 3 kPa 以上 54 kPa 以下に保ちながらエピタキシャル層の成長を行う。原料ガスには、たとえば、Si 原子の供給源として SiH<sub>4</sub> ガスを用い、C 原子の供給源として C<sub>2</sub>H<sub>2</sub> ガスまたは C<sub>3</sub>H<sub>8</sub> ガスを用いる。

#### 【 0 0 4 5 】

図 4 はエピタキシャル層 11 の成長温度と成長したエピタキシャル層 11 中の点欠陥の密度との関係を示している。原料ガスの供給比 ( C / Si 比 ) が 1 . 5 となるように SiH<sub>4</sub> ガスを 8 sccm の流量で炉内に導入し、エピタキシャル層 11 を成長させた。図 4 に示すように、1700 でエピタキシャル層 11 を形成した場合、点欠陥 Z<sub>1/2</sub> センター、点欠陥 E<sub>H<sub>6/7</sub></sub> センターおよび点欠陥 U<sub>T<sub>1</sub></sub> センターの密度は、それぞれ約 1 × 10<sup>13</sup> cm<sup>-3</sup>、約 5 × 10<sup>12</sup> cm<sup>-3</sup> および約 6 × 10<sup>12</sup> cm<sup>-3</sup> である。これに対し、1600 でエピタキシャル層 11 を形成した場合、点欠陥 Z<sub>1/2</sub> センター、点欠陥 E<sub>H<sub>6/7</sub></sub> センターおよび点欠陥 U<sub>T<sub>1</sub></sub> センターの密度は、それぞれ約 1 × 10<sup>12</sup> cm<sup>-3</sup>、約 5 × 10<sup>11</sup> cm<sup>-3</sup> および約 3 × 10<sup>11</sup> cm<sup>-3</sup> であり、点欠陥 Z<sub>1/2</sub> センターおよび点欠陥 E<sub>H<sub>6/7</sub></sub> センターの密度は、1700 で成長させた場合に比べて 1 / 10 程度になっている。

#### 【 0 0 4 6 】

このように、点欠陥密度、特に、点欠陥 Z<sub>1/2</sub> センターおよび点欠陥 E<sub>H<sub>6/7</sub></sub> センターの密度を減少させるためにはエピタキシャル層 11 をできるだけ低温で成長させることが好ましい。しかし、成長温度を 1400 未満に設定した場合、エピタキシャル層 11 上に Si が析出するなどしてエピタキシャル層が良好に成長しない可能性がある。

10

20

30

40

50

## 【0047】

点欠陥が減少した高品質の炭化珪素半導体エピタキシャル基板を得るために、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターの密度は、1700でエピタキシャル層を成長させた場合に比べて1/5程度以下であることが好ましい。このため、エピタキシャル層11の成長温度は1400以上1650以下であることが好ましく、1600以下であることがより好ましい。

## 【0048】

図5は、炭素原子の珪素原子に対する比 $C/Si$ を変化させて1600の成長温度で形成したエピタキシャル層中の点欠陥密度を示している。図5に示すように、 $C/Si$ 比が大きくなるほど点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターの密度は減少する。

一方、 $C/Si$ 比が大きくなるほど点欠陥 $UT_1$ センターの密度は大きくなる。以下において説明するように、点欠陥 $UT_1$ センターは熱処理によって減少させることができるため、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターの密度ができるだけ小さくなるよう、 $C/Si$ 比は大きい方が好ましい。具体的には、 $C/Si$ 比は1.5以上2以下であることが好ましい。 $C/Si$ 比が1.5より小さい場合、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターの密度の低減が十分ではない。また、 $C/Si$ 比が2より大きい場合、エピタキシャル層を形成するのが困難となる。 $C/Si$ 比は1.5以上である場合、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターの密度を、1700でエピタキシャル層を成長させた場合に比べて1/10以下にすることができる。このとき、点欠陥 $UT_1$ センターの密度は、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターの密度とトレードオフの関係にあるため、 $3 \times 10^{11} \text{ cm}^{-3}$ 以上になる。

## 【0049】

なお、エピタキシャル層中の点欠陥密度に影響を与える要因は、厳密な意味では炭化珪素単結晶基板10の表面11a近傍における $C/Si$ 比である。しかし、表面11a近傍における $C/Si$ 比を測定するのは困難であるため、原料ガス中の $C/Si$ 比を調節することによって、表面11a近傍における $C/Si$ 比を制御することになる。

## 【0050】

この場合、エピタキシャル層の成長に用いる化学気相堆積装置によって、原料ガスの炉内における分布が異なったり、サセプタなどが炭素からなる場合においてサセプタから放出される炭素などの影響を受けたりする。このため、用いる化学気相堆積装置によって好ましい原料ガス中の炭素原子の珪素原子に対する比 $C/Si$ は上述の範囲から多少ずれる可能性がある。本実施形態では、横型ホットウォール式の化学気相堆積装置を用い、炭素を放出する可能性のないサセプタなどを用いた。

## 【0051】

エピタキシャル層11を成長中の炉内の圧力は3kPaより小さいと、エピタキシャル層表面にピットが発生する可能性がある。また、炉内の圧力が54kPaを越えると、エピタキシャル層上にSiが析出するなどしてエピタキシャル層が良好に成長しない可能性がある。

## 【0052】

エピタキシャル層11の成長速度は、生産性の観点から10 $\mu\text{m}/\text{h}$ 以上であることが好ましい。エピタキシャル層11の成長温度を1400以上に設定し、原料ガスの流量を調節することによって、10 $\mu\text{m}/\text{h}$ 以上の成長速度を達成することが可能である。エピタキシャル層11の成長温度を高く設定するほど、より原料ガスの分解を促進することができるようになるので、より多くの原料ガスを導入でき、速い速度でエピタキシャル層11を成長させることができると、前述したように成長温度が高いと、点欠陥の密度は増大する。成長温度を1650に設定した場合、エピタキシャル層11の成長速度は、20 $\mu\text{m}/\text{h}$ 程度以上にできる。

## 【0053】

図6は、このように得られたエピタキシャル層11を深い準位過渡分光法により解析した結果を示している。 $C/Si$ 比が2となるように原料ガスを調整し、1600の成長

10

20

30

40

50

温度および $2\text{3}\mu\text{m/h}$ の速度でエピタキシャル層11を成長させた。図6に示すように、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターに帰属するピークの強度が、図1に示すグラフに比べて大きく低下している。また、図1に示す1700で成長したエピタキシャル層には見られなかった点欠陥 $UT_1$ センターに帰属する強いピークが観測される。

#### 【0054】

次に、このようにして得られたエピタキシャル層11を熱処理する。熱処理は、エピタキシャル層11の表面が酸化したり反応しないようなガス雰囲気下で行う。例えば、エピタキシャル層11が形成された炭化珪素単結晶基板10を熱処理炉に導入し、アルゴン、ヘリウムなどの雰囲気中、1300以上1800以下の温度で1分以上120分以下の時間熱処理する。熱処理は、点欠陥 $UT_1$ センターの密度が熱処理前の半分以下、好ましくは、 $3\times10^{11}\text{cm}^{-3}$ 以下となるように、温度および時間を調整することが好ましい。

#### 【0055】

熱処理の温度が1800よりも高い場合、点欠陥 $UT_1$ センターは減少するが、エピタキシャル層11に新たな面欠陥が生じるため、好ましくない。一方、熱処理温度が1300よりも低いと点欠陥 $UT_1$ センターを低減させる効果があまり得られず、長時間熱処理を行っても点欠陥 $UT_1$ センターの密度が $3\times10^{11}\text{cm}^{-3}$ 以下にはならない。

#### 【0056】

エピタキシャル層11中に点欠陥が存在するといえども、エピタキシャル層の結晶性が著しく悪化しているのではないので、上述の温度範囲において、点欠陥 $UT_1$ センターを減少させるための熱処理を行ってもエピタキシャル層11の表面モフォロジーが悪化することはない。

#### 【0057】

熱処理は、上述した雰囲気、熱処理温度および熱処理時間を満たす限り、種々の装置を用いて熱処理を行うことができる。例えば、エピタキシャル層11を形成した装置内において形成したエピタキシャル層11を熱処理してもよい。また、エピタキシャル層11の熱処理は、エピタキシャル層11を形成した炭化珪素半導体エピタキシャル基板に半導体プロセスを施し、半導体素子を作製する途中に行なってもよい。ただし、半導体プロセスで形成される金属薄膜や絶縁膜が熱処理によって変質したり反応したりする可能性がある場合や半導体プロセス後に熱処理を行うとエピタキシャル層自体が変質したり、反応したりしてしまう可能性がある場合が考えられる。この場合には、エピタキシャル層11を形成後、引き続いて熱処理を行う、つまり、炭化珪素半導体エピタキシャル基板に半導体プロセスを施す前に行なうことが好ましい。この場合、エピタキシャル層を形成後、いったんエピタキシャル層11が形成された炭化珪素単結晶基板10の温度を常温程度にまで低下させた後、熱処理を開始することが好ましい。半導体素子を形成する際に用いられる半導体プロセスでは、通常1300を超える温度で炭化珪素半導体エピタキシャル基板を処理することはない。このため、半導体素子を形成する際に用いられる半導体プロセスのいずれかの工程を上述の熱処理工程と兼ねることはできない。また、半導体素子を形成する際に用いられる半導体プロセスによっては、点欠陥 $UT_1$ センターの密度を低減させる効果はほとんど得られない。

#### 【0058】

図7は、エピタキシャル層11を形成した直後および熱処理後の点欠陥密度を示すグラフである。図7に示すように、点欠陥 $UT_1$ センターの密度が約 $7\times10^{11}\text{cm}^{-3}$ から $2\times10^{11}\text{cm}^{-3}$ 程度に大きく減少している。これに対し、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターの密度も減少はするが、点欠陥 $UT_1$ センターほど大きく欠陥密度が減少する効果は得られない。

#### 【0059】

このようにして得られたエピタキシャル層11を有する炭化珪素半導体エピタキシャル基板21では、点欠陥 $Z_{1/2}$ センターおよび点欠陥 $EH_{6/7}$ センターが少なく、また、公知

10

20

30

40

50

ではない  $1.33\text{ eV}$  から  $1.53\text{ eV}$  の準位をもつ点欠陥センターの密度も低減している。このため、本発明の炭化珪素半導体エピタキシャル基板 21 を用いて作製される半導体素子では、禁制帯中に生じた準位に起因する半導体特性の劣化が抑制される。具体的には、P N 接合の順方向抵抗、逆方向リーク電流、およびショットキー接合の逆方向リーク電流などを低減することができる。したがって、本発明の炭化珪素半導体エピタキシャル基板を用いることにより、オン抵抗が低減することによる低消費電力で発熱の少ない電力用半導体素子が得られる。また、耐圧が向上することによる信頼性が高い電力用半導体素子が得られる。

## 【0060】

なお、本実施形態では、点欠陥をできるだけ低減させた炭化珪素半導体エピタキシャル基板を製造する方法を説明した。一般的には、優れた特性の半導体素子を製造するためには点欠陥はできるだけ少ないほうが好ましいからである。しかし、半導体素子に求められる特性によっては、点欠陥が所定の密度で存在していたほうが好ましい場合もある。そのような場合には、エピタキシャル層を熱処理する時間および温度を調節することによって、点欠陥 U T<sub>1</sub> センターの密度を所望の値に調節することができる。

## 【産業上の利用可能性】

## 【0061】

本発明は、炭化珪素半導体エピタキシャル基板の製造に好適に用いられ、特に低消費電流で信頼性の高い半導体素子を製造するための炭化珪素半導体エピタキシャル基板の製造に好適に用いられる。

## 【符号の説明】

## 【0062】

1 0 炭化珪素半導体基板

1 1 エピタキシャル層

2 1 炭化珪素半導体エピタキシャル基板

## 【図1】

## 【図2】

## 【図3】

## 【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開2003-234301(JP,A)

特開平11-157988(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 205

C 23 C 16 / 42

C 30 B 29 / 36

C 30 B 33 / 02