(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3901906号

(P3901906)

(45) 発行日 平成19年4月4日(2007.4.4)

(24) 登録日 平成19年1月12日(2007.1.12)

(51) Int.C1.

F 1

HO3K 19/0948 (2006.01)

HO3K 19/094

B

HO3K 19/096 (2006.01)

HO3K 19/096

B

請求項の数 5 (全 17 頁)

(21) 出願番号 特願2000-44307 (P2000-44307)

(22) 出願日 平成12年2月22日 (2000.2.22)

(65) 公開番号 特開2001-237691 (P2001-237691A)

(43) 公開日 平成13年8月31日 (2001.8.31)

審査請求日 平成16年9月3日 (2004.9.3)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100064285

弁理士 佐藤 一雄

(74) 代理人 100088889

弁理士 橋谷 英俊

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100096921

弁理士 吉元 弘

(72) 発明者 香 西 昌 平

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

## (57) 【特許請求の範囲】

## 【請求項1】

第1の入力信号により動作する1または複数の第1の論理回路と、前記第1の入力信号が入力される入力容量等化回路と、1または複数の第2の入力信号および前記入力容量等化回路から出力された出力信号が入力される1または複数の第2の論理回路と、を備え、

前記入力容量等化回路は、前記第2の入力信号の状態に依存することなく前記第1の入力信号の入力容量を等価にする入力容量無依存化回路を備えると共に、

前記第1の論理回路は、前記第1の入力信号に基づいて所定の論理動作を行なうために一定の入力容量を有するゲートブロックを備え、前記第2の論理回路は、前記複数の第2の入力信号および前記入力容量無依存化回路の出力が供給される複数の論理ゲートブロックを備えることを特徴する半導体集積回路装置。

## 【請求項2】

前記入力容量無依存化回路は、インバータであることを特徴とする請求項1に記載の半導体集積回路装置。

## 【請求項3】

前記第1および第2の論理回路は、所定の論理動作を行なうために同一の回路構成を有する2入力1出力の論理動作素子を備え、前記論理動作素子の一方の入力には選択回路から選択信号が供給され、前記論理動作素子の他方の入力には前記入力容量無依存化回路から出力されたクロック信号が供給されていることを特徴とする請求項1に記載の半導体集積回路装置。

**【請求項 4】**

前記入力容量無依存化回路は、前記第1および第2の論理回路としての機能を果たす論理動作素子に対してクロック信号を供給するクロックバッファを備えることを特徴とする請求項3に記載の半導体集積回路装置。

**【請求項 5】**

クロック信号と制御信号とが入力される多入力論理回路を含む半導体集積回路装置において、

前記多入力論理回路の1つの入力としての前記クロック信号は、前記多入力論理回路の電源電位に直接接続される第1のMOSトランジスタと、接地電位に直接接続される第2のMOSトランジスタとの双方のゲート端子に供給されることを特徴とする半導体集積回路装置。

10

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、半導体集積回路装置に係り、特にクロックツリーを構成する論理ゲートの構成の仕方に改良を加えた半導体集積回路装置に関する。

**【0002】****【従来の技術】**

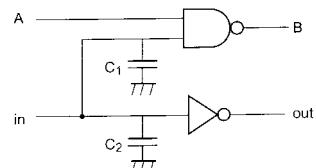

集積回路を伝搬する信号の遅延時間は、負荷となる論理ゲートの入力容量により決められるが、多入力ゲートを負荷として有する回路における入力容量すなわち遅延時間は多入力ゲートの他方の入力信号の状態の影響を受けることになる。図21は2入力NANDゲートを負荷として有する回路を示しており、図21において、入力端子inからみた入力容量は( $C_1 + C_2$ )であるが、NANDゲートの入力容量 $C_1$ はもう一方の入力Aの状態により影響を受ける。

20

**【0003】**

すなわち、入力Aがハイであるかローであるかによって、見かけ上の容量 $C_1$ が異なることになる。その結果として、入力端子inから出力端子outに伝わる信号の遅延時間が変わってしまうことになる。従来、このような場合には、入力端子inから出力端子outに伝わる信号の遅延時間を最大にする入力Aの状態を想定してタイミング設計を行なっていた。この場合、遅延時間を余分に見積もることによりマージンが大きめになるという問題がある。また、遅延時間が最小となる入力Aの状態を想定してタイミングチェックを別途行なう必要が生じる可能性もあった。

30

**【0004】**

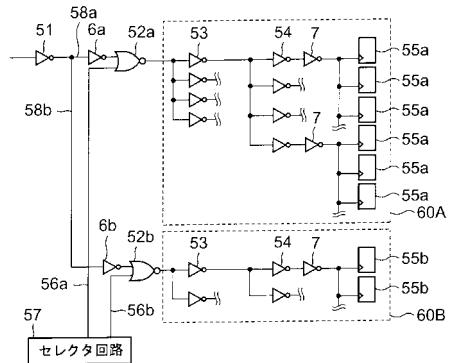

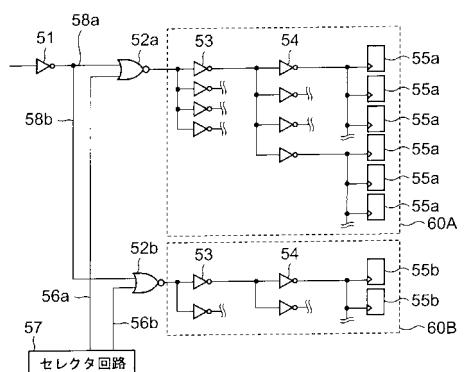

特に、LSI (Large Scale Integrated-circuit 大規模集積回路) 全体にクロック信号を分配するクロックツリーにおいては、タイミング設計を正確に行なう必要がある。また、近年、LSIの消費電力の低減のため、特開平10-308450号公報に開示されている技術のように、必要に応じて部分的にクロック信号の供給を停止するゲーティッドクロック手法が用いられるようになってきている。図22は、上記公報の図5において従来技術とされているゲーティッドクロック回路の構成例を示している。この回路において、クロック信号はルートバッファ51により、多入力ゲートとしてのNOR回路52aおよび52bに信号58aおよび58bとして入力されている。セレクタ回路57より出力される信号56aまたは56bがローのとき、クロック信号は次段のバッファ回路53に伝達されるが、信号56aまたは56bがハイの時には出力は常にローとなりクロック信号は伝達されない。このように、セレクタ回路57からの出力によりクロックバッファの余分な遷移を停止させることにより、消費電力の低減を図っている。

40

**【0005】**

ここで、論理ブロック60A, 60Bの動作の間には一般に相関はなく、セレクタ回路57からの出力信号56aと56bの状態の組合せはどのようにも設定することができる。ルートバッファ51から見ると、NOR回路52aの入力容量とNOR回路52bの入力容量は、それぞれ信号56a, 56bの状態に依存している。例えば、NOR回路52a

50

の出力信号に注目すると、信号 5 6 b がハイである場合とローである場合とではタイミングが異なることになる。したがって、フリップフロップ回路 5 5 a に入力されるクロック信号もタイミングが異なることになる。

【 0 0 0 6 】

L S I では、フリップフロップ回路 5 5 a , 5 5 b の全てのクロック信号がずれることなく動作するように設計することが一般的である。クロック信号のずれはクロックスキューと呼ばれており、可及的に小さくする必要がある。図 2 2 に示したゲーティッドクロック回路においては、セレクタ回路 5 7 から出力される信号の状態によってN O R 回路 5 2 a , 5 2 b の 2 入力論理ゲートのクロック信号の入力容量が異なることになり、セレクタ回路 5 7 の特定の 1 つの信号の状態を仮定してクロックスキューを小さくするように設計すると、他の状態ではクロックスキューが大きくなってしまうことになる。

10

【 0 0 0 7 】

【発明が解決しようとする課題】

このように、全ての状態でクロックスキューを小さくできるタイミング設計を行なうことは不可能である。上述の特開平 1 0 - 3 0 8 4 5 0 号公報において実施形態として挙げられている図 1 および図 3 に開示されている技術内容から見ても明らかのように、このタイミング設計の問題は解決されていない。

【 0 0 0 8 】

本発明は、多入力論理ゲートの入力ピン容量を他の入力信号の状態に関係なく一定のものとすることにより、集積回路中を伝搬する信号の遅延時間を正確に見積もることができるよう論理回路を設計できる半導体集積回路装置を提供することを目的としている。

20

【 0 0 0 9 】

【課題を解決するための手段】

上記目的を達成するための、本発明の第 1 の基本構成に係る半導体集積回路装置は、第 1 の入力信号により動作する 1 または複数の第 1 の論理回路と、前記第 1 の入力信号が入力される入力容量等化回路と、1 または複数の第 2 の入力信号および前記入力容量等化回路から出力された出力信号が入力される 1 または複数の第 2 の論理回路と、を備え、前記入力容量等化回路は、前記第 2 の入力信号の状態に依存することなく前記第 1 の入力信号の入力容量を等価にする入力容量無依存化回路を備えると共に、前記第 1 の論理回路は、前記第 1 の入力信号に基づいて所定の論理動作を行なうために一定の入力容量を有するゲートブロックを備え、前記第 2 の論理回路は、前記複数の第 2 の入力信号および前記入力容量無依存化回路の出力が供給される複数の論理ゲートブロックを備えることを特徴としている。

30

【 0 0 1 0 】

上記第 1 の基本構成に係る半導体集積回路装置において、前記入力容量無依存化回路は、インバータであることを特徴としても良い。

【 0 0 1 1 】

上記第 1 の基本構成に係る半導体集積回路装置において、前記第 1 および第 2 の論理回路は、所定の論理動作を行なうために同一の回路構成を有する 2 入力 1 出力の論理動作素子を備え、前記論理動作素子の一方の入力には選択回路から選択信号が供給され、前記論理動作素子の他方の入力には前記入力容量無依存化回路から出力されたクロック信号が供給されていることを特徴としても良い。

40

【 0 0 1 2 】

上記段落に記載の半導体集積回路装置において、前記入力容量無依存化回路は、前記第 1 および第 2 の論理回路としての機能を果たす論理動作素子に対してクロック信号を供給するクロックバッファを備えることを特徴としても良い。

【 0 0 1 6 】

本発明の第 2 の基本構成に係る半導体集積回路装置は、クロック信号と制御信号とが入力される多入力論理回路を含む半導体集積回路装置において、前記多入力論理回路の 1 つの入力としての前記クロック信号は、前記多入力論理回路の電源電位に直接接続される第

50

1のMOSトランジスタと、接地電位に直接接続される第2のMOSトランジスタとの双方のゲート端子に供給されることを特徴としている。

【0017】

【発明の実施の形態】

以下、本発明に係る半導体集積回路装置の好適な実施形態について、添付図面を参照しながら詳細に説明する。図1ないし図20を用いて第1ないし第20実施形態に係る半導体集積回路装置について説明する。この発明の第1の要旨は、論理回路が複数の入力を有すると共にこれら複数の入力の信号状態がそれぞれ異なることにより、それぞれの入力ピンの容量に違いが発生する論理回路よりなるものにおいて、前記複数の入力を有する前記論理回路の入力の1つもしくは複数に設けられ、前記複数の入力の状態の如何に拘わらず、この入力が有する入力容量を一定に保つ入力容量等化回路を備えることを特徴としている。したがって、多段論理素子による論理回路の具体的な回路としては、クロックツリー回路であっても、論理ゲートまたは論理ブロックであっても何れのものでも包含され得るものである。以下、各実施形態について詳述する。

【0018】

(第1実施形態)

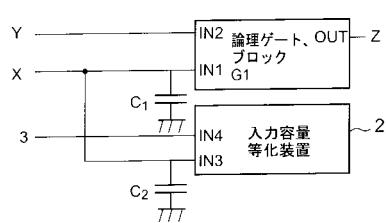

本発明の第1実施形態に係る半導体集積回路装置を図1に従って説明する。2入力の論理ゲートまたは論理ゲートによって構成されるブロックG1に入力IN1, IN2があるとき、入力信号Yの状態に依存することなく、入力信号Xが入力されるブロックG1のIN1端子と、入力容量等化回路のIN3端子の入力容量の和( $C_1 + C_2$ )を常に一定にするような入力等化回路2を構成する。

【0019】

この結果、入力信号Xから見た入力容量を一定にすることができる。入力容量等化回路2の入力は、入力Xのみでなく、図示のように他の入力3が入力端子IN4に供給されている場合もある。本発明の第1実施形態に係る半導体集積回路装置を用いることにより、2入力ゲートに入力する一方の入力の入力容量が他方の入力信号の状態の影響を受けないようにすることができる。

【0020】

(第2実施形態)

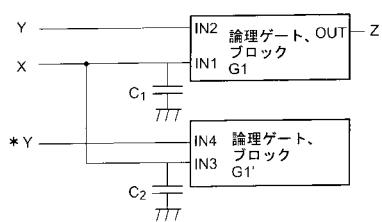

次に、図2を用いて、本発明の第2実施形態に係る半導体集積回路装置について説明する。この第2実施形態は、図1に示されている第1実施形態の入力容量等化回路2を、ブロックG1と等価な2入力の論理ゲートまたは論理ゲートにより構成されるブロックG1'により構成したものである。

【0021】

ブロックG1は信号Xが入力される入力端子IN1と、信号Yが入力される入力端子IN2と、信号Zが出力される出力端子OUTとを有し、ブロックG1'は信号Xが入力される入力端子IN3と、信号Yの反転信号\*Yが入力される入力端子IN4を有している。符号C1およびC2は、ブロックG1のIN1およびブロックG1'のIN3への入力容量である。この等化回路としてのブロックG1'の回路パラメータはブロックG1の回路パラメータと等しくしておいた方が効果的である。なお、この明細書において、「\*」は反転符号として用いられている。

【0022】

本発明の第2実施形態に係る半導体集積回路装置を用いることにより、2入力ゲートに入力する一方の入力の入力容量が他方の入力信号の状態の影響を受けないようにすることができる。

【0023】

(第3実施形態)

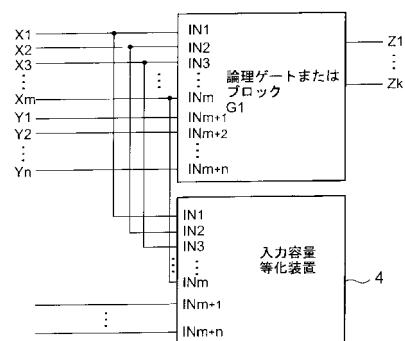

次に、図3を用いて、本発明の第3実施形態に係る半導体集積回路装置について説明する。信号X1～Xmと信号Y1～Ynの(m+n)個の信号がそれぞれ入力される(m+n)本の入力端子IN1～INm+nを有する論理ゲートによって構成される論理ブロック

10

20

30

40

50

G 1において、入力端子 I N 1 ~ I N m の入力容量を入力信号 Y 1 ~ Y n の状態によらずに一定とするような入力容量等化回路 4 を構成する。m = 1 かつ n = 1 の場合が第 1 実施形態に相当している。

【 0 0 2 4 】

この第 3 実施形態において、ブロック G 1 の出力信号は Z 1 ~ Z k のように複数であっても良い。また、入力等化回路 4 の入力は X 1 ないし X m のみでなくとも良い。

【 0 0 2 5 】

本発明の第 3 実施形態に係る半導体集積回路装置を用いることにより多入力ゲートに入力する少なくとも 1 つの入力の入力容量が他の入力信号のうちのいくつかの入力信号の状態の影響を受けないようにすることができる。

10

【 0 0 2 6 】

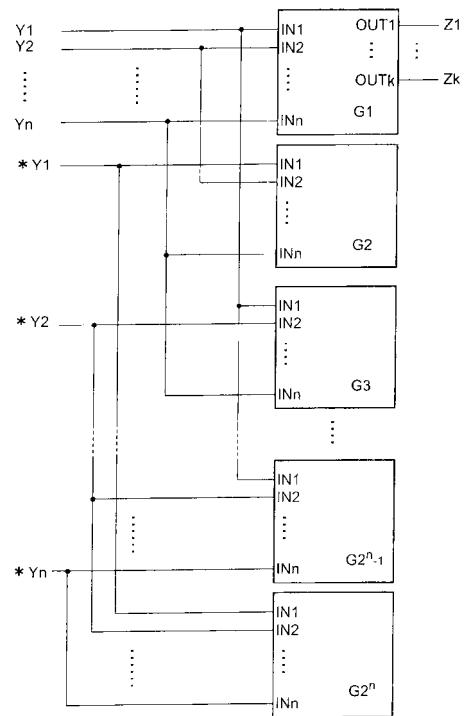

( 第 4 実施形態 )

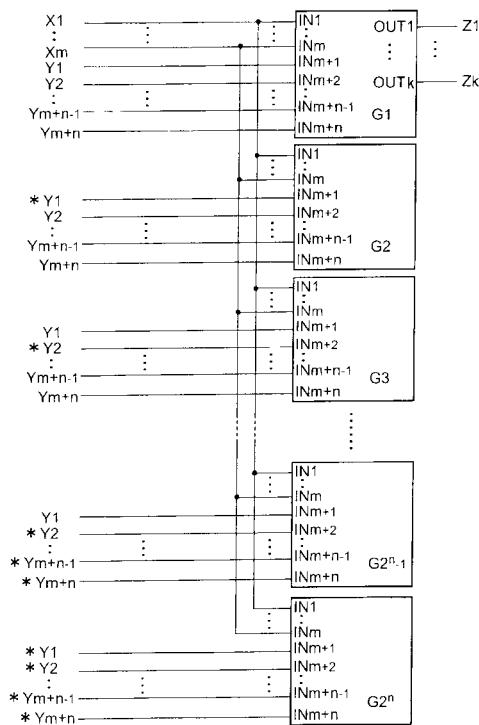

次に図 4 を用いて、本発明の第 4 実施形態に係る半導体集積回路装置について説明する。この第 4 実施形態の回路装置は、第 3 実施形態の回路装置における入力等化回路を論理ゲート G 1 と等価な論理ゲートあるいは論理ゲートによって構成される等価なブロック G 2 ないし G 2<sup>n</sup> によって構成したものである。この場合、2 の n 乗個の論理ゲートまたはブロックが必要になる。

【 0 0 2 7 】

本発明の第 4 実施形態に係る半導体集積回路装置を用いることにより、多入力ゲートに入力する少なくとも 1 つの入力の入力容量が多の入力信号のうちのいくつかの入力信号の状態を受けないようにすることができる。

20

【 0 0 2 8 】

( 第 5 実施形態 )

次に図 5 を用いて、本発明の第 5 実施形態に係る半導体集積回路装置について説明する。この第 5 実施形態の回路装置は、第 4 実施形態の回路装置において、入力 X 1 ~ X m が存在しない場合の構成例である。このとき、入力信号は Y 1 ~ Y n の n 本となり、論理ゲートあるいは論理ブロック G 1 は n 入力となる。

【 0 0 2 9 】

入力容量等化回路は、第 4 実施形態と同様に、論理ゲート G 1 と等価な論理ゲート、あるいは論理ゲートによって構成される等価なブロック G 2 ~ G 2<sup>n</sup> によって構成される。

30

【 0 0 3 0 】

このとき、Y 1 ~ Y n の n 個の入力信号から見た入力容量は、他の全ての入力信号の状態によらず一定となる。なお、このとき、Y 1 ~ Y n の反転信号のみが入力される G 2<sup>n</sup> は省略することもできる。

【 0 0 3 1 】

本発明の第 5 実施形態に係る半導体集積回路装置を用いることにより、多入力ゲートに入力する全ての入力信号から見た入力容量が他の全ての入力信号の状態の影響を受けないようにすることができる。

【 0 0 3 2 】

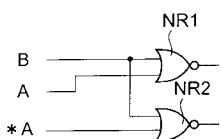

( 第 6 実施形態 )

次に図 6 を用いて、本発明の第 6 実施形態に係る半導体回路装置について説明する。この第 6 実施形態は、2 入力 NOR 回路の一方の入力ピン容量を他方の入力信号の状態に依存することなく一定にするためのものである。信号 A と信号 B が入力される第 1 の 2 入力 NOR 回路 N R 1 と、信号 A の反転信号 \* A と信号 B が入力される第 2 の 2 入力 NOR 回路 N R 2 とから構成されている。信号 \* A はインバータ回路などを用いて適宜生成する。ここで、第 1 の NOR 回路 N R 1 の他方の入力と第 2 の NOR 回路 N R 2 の他方の入力信号は相補的であり、言い換えると、信号 A の電位がハイ状態であるときには信号 \* A の電位はロー状態であり、信号 A の電位がロー状態であるときには信号 \* A の電位はハイ状態となる。つまり、信号 B から見ると、信号 A の状態に拘わらず、他方の入力がハイの 2 入力 NOR 回路と他方の入力がローの 2 入力 NOR 回路が 1 つずつ存在するので、入力容量は

40

50

信号 A の状態に拘わらず一定となる。

【 0 0 3 3 】

第 1 および第 2 の N O R 回路 N R 1 と N R 2 の回路パラメータは同一に近ければ近いほど効果的である。また、第 2 の N O R 回路 N R 2 の出力に対する負荷は第 1 の N O R 回路 N R 1 の出力負荷に大きさが近ければ近いほど効果的である。また、本第 6 実施形態においては、2 入力 N O R 回路を用いて説明したが、本発明は他の 2 入力論理回路についても応用可能である。

【 0 0 3 4 】

このように構成された第 2 実施形態に係る半導体集積回路装置によれば、2 入力論理回路の一方の入力ピンの入力容量を他方の入力信号の状態の影響を受けないようにすることができる。

10

【 0 0 3 5 】

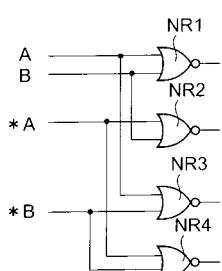

( 第 7 実施形態 )

次に図 7 を用いて、本発明の第 7 実施形態に係る半導体集積回路装置について説明する。この第 7 実施形態は、2 入力 N O R 回路の 2 つの入力ピンの入力ピン容量を他方の入力ピンの入力信号の状態に依らずに一定とするものである。この第 7 実施形態に係る半導体集積回路装置は、第 1 ないし第 4 の 2 入力 N O R 回路 N R 1 , N R 2 , N R 3 , N R 4 から構成されている。第 1 の N O R 回路 N R 1 には信号 A と信号 B が入力され、第 2 の N O R 回路 N R 2 には信号 A の反転信号 \* A と信号 B が入力され、第 3 の N O R 回路 N R 3 には信号 A と信号 B の反転信号 \* B が入力され、第 4 の N O R 回路 N R 4 には信号 A の反転信号 \* A と信号 B の反転信号 \* B が入力されている。反転信号 \* A 、 \* B は必要に応じてインバータなどを用いて生成することができる。

20

【 0 0 3 6 】

ここで、入力 A から見ると、負荷は第 1 および第 3 の N O R 回路 N R 1 、 N R 3 である。第 1 および第 3 の N O R 回路 N R 1 、 N R 3 の他方の入力は、それぞれ信号 B および信号 \* B であり、信号 B の状態に拘わらず、入力 A のピン容量は一定である。これとは別に、信号 \* A を生成するインバータがある場合にはその容量が加えられる。次に、入力 B から見ると、負荷は第 1 および第 2 の N O R 回路 N R 1 、 N R 2 である。第 1 および第 2 の N O R 回路 N R 1 、 N R 2 の他方の入力は、信号 A および信号 \* A であり、信号 A の状態に拘わらず、入力 B の入力ピン容量は一定である。これとは別に、信号 \* B を生成するインバータがある場合にはその容量が加えられる。

30

【 0 0 3 7 】

いま、元々は 2 入力 N O R 回路の出力が必要だったので、第 1 の N O R 回路 N R 1 の出力が次段の回路に接続される。ここで、第 2 ないし第 4 の N O R 回路 N R 2 , N R 3 , N R 4 の出力負荷は、第 1 の N O R 回路 N R 1 と同様とするのがより効果的である。また、第 1 ないし第 4 の N O R 回路 N R 1 ~ N R 4 の回路パラメータはできるだけ等しくすることが効果的である。第 4 の N O R 回路 N R 4 については省略することも可能である。本第 7 実施形態においては、2 入力 N O R 回路を用いて説明したが、本発明は他の 2 入力論理回路についても応用可能である。

40

【 0 0 3 8 】

第 7 実施形態に係る半導体集積回路装置を用いることにより、2 入力論理回路の任意の一方の入力ピンの入力容量を他方の入力信号の状態の影響を受けないようにすることができる。

【 0 0 3 9 】

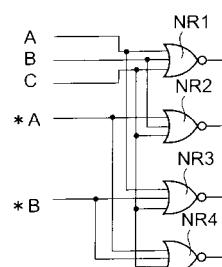

( 第 8 実施形態 )

次に図 8 を用いて、本発明の第 8 実施形態に係る半導体集積回路装置について説明する。この第 8 実施形態は、第 7 実施形態の回路装置を 3 入力の論理回路に応用した例である。第 8 実施形態に係る半導体集積回路装置は、第 1 ないし第 4 の 3 入力 N O R 回路 N R 1 ~ N R 4 から構成されている。第 1 の N O R 回路 N R 1 には信号 A , 信号 B , 信号 C が入力される。第 2 の N O R 回路 N R 2 には信号 A の反転信号 \* A , 信号 B , 信号 C が入力され

50

る。第3のNOR回路NR3には信号A, 信号Bの反転信号\*B, 信号Cが入力される。第4のNOR回路NR4には信号Aの反転信号\*A, 信号Bの反転信号\*B, 信号Cが入力されている。信号Cから見ると、信号Aおよび信号Bの状態に拘わらず、第1の入力がハイで第2の入力がハイの3入力NOR回路、第1の入力ハイで第2の入力がローの3入力NOR回路、第1の入力がローで第2の入力がハイの3入力NOR回路、第1の入力がローで第2の入力がローの3入力NOR回路が負荷となる。結果として、入力Cの入力ピン容量は常に一定に保たれる。

#### 【0040】

いま、元々は3入力NOR回路の出力が必要だったので、第1のNOR回路NR1の出力が次段の回路に接続される。ここで、第2ないし第4のNOR回路NR2, NR3, NR4の出力負荷は、第1のNOR回路NR1と同様とするのがより効果的である。また、第1ないし第4のNOR回路NR1～NR4の回路パラメータはできるだけ等しくすることが効果的である。本第8実施形態においては、3入力NOR回路を用いて説明したが、本発明は他の3入力論理回路についても応用可能である。

#### 【0041】

第8実施形態に係る半導体集積回路装置を用いることにより、3入力論理回路の任意の一方の入力ピンの入力容量を他方の入力信号の状態の影響を受けないようにすることが可能である。

#### 【0042】

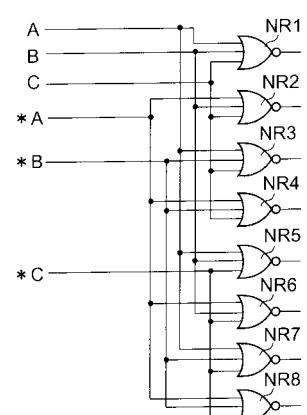

##### (第9実施形態)

次に図9を用いて、本発明の第9実施形態に係る半導体集積回路装置について説明する。第9実施形態の回路装置は、第7実施形態の回路装置を3入力の論理回路に応用した例である。第9実施形態は、第1ないし第8の3入力NOR回路NR1～NR8からなる。第1のNOR回路NR1には信号A, 信号B, 信号Cが入力される。第2のNOR回路NR2には信号Aの反転信号\*A, 信号B, 信号Cが入力される。第3のNOR回路NR3には信号A, 信号Bの反転信号\*B, 信号Cが入力される。第4のNOR回路NR4には信号Aの反転信号\*A, 信号Bの反転信号\*B, 信号Cが入力されている。

#### 【0043】

第5のNOR回路NR5には信号A, 信号B, 信号Cの反転信号\*Cが入力される。第6のNOR回路NR6には信号Aの反転信号\*A, 信号B, 信号Cの反転信号\*Cが入力される。第7のNOR回路NR7には信号A, 信号Bの反転信号\*B, 信号Cの反転信号\*Cが入力される。第8のNOR回路NR8には信号Aの反転信号\*A, 信号Bの反転信号\*B, 信号Cの反転信号\*Cが入力されている。

#### 【0044】

信号Cから見ると、信号Aおよび信号Bの状態に拘わらず、第1の入力がハイで第2の入力がハイの3入力NOR回路、第1の入力ハイで第2の入力がローの3入力NOR回路、第1の入力がローで第2の入力がハイの3入力NOR回路、第1の入力がローで第2の入力がローの3入力NOR回路が負荷となる。信号Cの反転信号\*Cをインバータで生成した場合には、これらにインバータ容量が加えられる。結果として、入力Cの入力ピン容量は常に一定に保たれる。入力Aおよび入力Bについても同様である。

#### 【0045】

いま、元々は3入力NOR回路の出力が必要だったので、第1のNOR回路NR1の出力が次段の回路に接続される。ここで、第2ないし第8のNOR回路NR2～NR8の出力負荷は、第1のNOR回路NR1と同様とするのがより効果的である。また、第1ないし第8のNOR回路NR1～NR8の回路パラメータはできるだけ等しくすることが効果的である。本第9実施形態においては、3入力NOR回路を用いて説明したが、本発明は他の3入力論理回路についても応用可能である。また、第8のNOR回路NR8については省略することも可能である。

#### 【0046】

本発明の第9実施形態に係る半導体集積回路装置を用いることにより、3入力論理回路の

10

20

30

40

50

全ての入力ピンの入力容量を他の入力信号の状態の影響を受けないようにすることが可能である。

【0047】

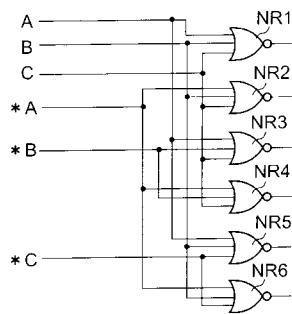

(第10実施形態)

次に図10を用いて、本発明の第10実施形態に係る半導体集積回路装置について説明する。第10実施形態の回路装置は、3つの入力信号のうち2つの入力信号について、入力ピン容量を等化する例である。第10実施形態は、第1ないし第6の3入力NOR回路NR1～NR6からなる。第1のNOR回路NR1には信号A、信号B、信号Cが入力される。第2のNOR回路NR2には信号Aの反転信号\* A、信号B、信号Cが入力される。第3のNOR回路NR3には信号A、信号Bの反転信号\* B、信号Cが入力される。第4のNOR回路NR4には信号Aの反転信号\* A、信号Bの反転信号\* B、信号Cが入力されている。第5のNOR回路NR5には信号A、信号B、信号Cの反転信号\* Cが入力される。第6のNOR回路NR6には信号Aの反転信号\* A、信号B、信号Cの反転信号\* Cが入力される。

10

【0048】

信号Cから見ると、信号Aおよび信号Bの状態に拘わらず、第1の入力がハイで第2の入力がハイの3入力NOR回路、第1の入力がハイで第2の入力がローの3入力NOR回路、第1の入力がローで第2の入力がハイの3入力NOR回路、第1の入力がローで第2の入力がローの3入力NOR回路が負荷となる。信号Cの反転信号\* Cをインバータで生成した場合には、これらにインバータ容量が加えられる。結果として、入力Cの入力ピン容量は常に一定に保たれる。入力Bについても同様である。しかしながら、信号Aについては、3つのNOR回路が接続されるだけなので、信号Bおよび信号Cの状態により、信号Aから見た入力容量は変化する。

20

【0049】

いま、元々は3入力NOR回路の出力が必要だったので、第1のNOR回路NR1の出力が次段の回路に接続される。ここで、第2ないし第6のNOR回路NR2～NR6の出力負荷は、第1のNOR回路NR1と同様とするのがより効果的である。また、第1ないし第6のNOR回路NR1～NR6の回路パラメータはできるだけ等しくすることが効果的である。本第10実施形態においては、3入力NOR回路を用いて説明したが、本発明は他の3入力論理回路についても応用可能である。

30

【0050】

本発明の第10実施形態に係る半導体集積回路装置を用いることにより、3入力論理回路の全ての入力ピンの入力容量を他の入力信号の状態の影響を受けないようにすることが可能である。

【0051】

(第11実施形態)

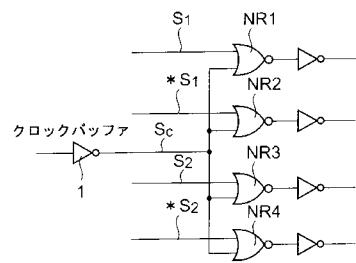

図11は、本発明の第11実施形態に係る半導体集積回路装置の構成を示す回路図である。図11に示す第11実施形態の半導体集積回路装置は、クロックバッファ1から出力されたクロック信号SCを入力する第1ないし第4の2入力NOR回路NR1、NR2、NR3、NR4を備えている。クロック制御信号S1が第1のNOR回路NR1に入力され、クロック制御信号S1の反転信号\* S1が第2のNOR回路NR2に入力され、クロック制御信号S2が第3のNOR回路NR3に入力され、クロック制御信号S2の反転信号\* S2第4のNOR回路NR4に入力されている。ここで、第1のNOR回路NR1と第3のNOR回路NR3のクロック信号として用いるとすると、それぞれはクロック制御信号S1およびS2に応じてクロックを伝達するかしないかが制御される。

40

【0052】

ここで、クロックバッファ1から見ると、第1のNOR回路NR1の他方の入力信号S1と第2のNOR回路NR2の他方の入力信号\* S1は相補的であるので、クロック制御信号S1の状態に拘わらず一定の負荷を有することになる。これは第3のNOR回路NR3と第4のNOR回路NR4についても同様である。その結果として、クロックバッファ1

50

の負荷は制御信号 S 1 および S 2 の状態に拘わらず一定にすることができる。

【 0 0 5 3 】

なお、より効果的な構成とするためには、第 1 および第 2 の N O R 回路 N R 1 および N R 2 の回路パラメータを同一とし、第 3 および第 4 の N O R 回路 N R 3 および N R 4 の回路パラメータを同一にすることが望ましい。また、第 2 の N O R 回路 N R 2 の出力負荷を第 1 の N O R 回路 N R 1 の出力負荷と等しくし、第 4 の N O R 回路 N R 4 の出力負荷を第 3 の N O R 回路 N R 3 の出力負荷と等しくすることも効果的である。

【 0 0 5 4 】

本第 1 1 実施形態においては、2 入力 N O R 回路を用いているが、本発明は他の 2 入力論理回路においても応用可能である。制御信号 S 1 と制御信号 S 2 が入力される論理回路の種類が異なる場合についても応用可能である。

10

【 0 0 5 5 】

また、本第 1 1 実施形態ではクロック制御信号 S 1 および S 2 のそれぞれの反転信号 \* S 1 および \* S 2 をインバータにより生成しても良く、また、全体の回路構成における何れかの箇所で既に反転信号が生成されている場合には、その信号をそのまま用いるようにすれば、新たに生成する必要はない。

【 0 0 5 6 】

この第 1 1 実施形態に係る半導体集積回路装置によれば、ゲーティッドクロック信号が他のブロックに供給されるゲーティッドクロック信号を制御する信号の状態により影響を受けないようにすることができる。

20

【 0 0 5 7 】

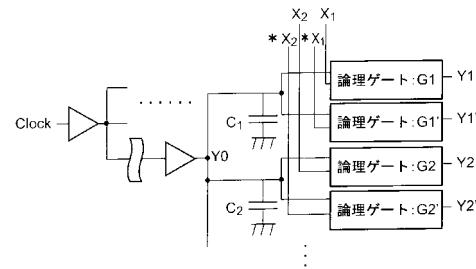

( 第 1 2 実施形態 )

次に、図 1 2 を参照しながらこの発明の第 1 2 実施形態に係る半導体集積回路装置について説明する。第 1 2 実施形態は本発明をクロックツリーに適用したものである。信号 C 1 o c k はクロック信号である。Y 0 は、クロックツリー中の信号、X 1 , X 2 , ... は制御信号であり、論理ゲート G 1 , G 2 , ... によって制御されたクロック信号 Y 1 , Y 2 , ... を作成する。このとき、図 1 2 に示すように、論理ゲート G 1 , G 1 ' , G 2 , G 2 ' , ... はそれぞれ X 1 , \* X 1 , X 2 , \* X 2 ... とクロックツリー中の Y 0 を入力として有するような構成とすることにより、Y 0 からの入力容量 C 1 , C 2 , ... は、信号 X 1 , X 2 , ... の状態によらずに一定とすることができます。また、必要に応じて Y 1 ' , Y 2 ' を用いることもできる。

30

【 0 0 5 8 】

このように、本発明の第 1 2 実施形態に係る半導体集積回路装置を用いることにより、制御信号と論理ゲートにより制御されたクロック信号の遅延時間のばらつき（スキュー、ジッタ）を抑制することができます。

【 0 0 5 9 】

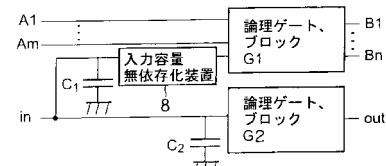

( 第 1 3 実施形態 )

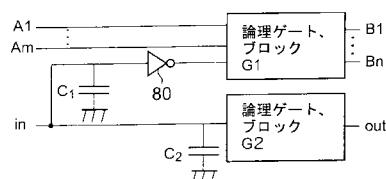

次に、図 1 3 を用いて本発明の第 1 3 実施形態に係る半導体集積回路装置について説明する。この第 1 3 実施形態においては、多入力の論理ゲートまたはそれによって構成されるブロック G 1 への入力に入力容量無依存化装置 8 を挿入することによって、ブロック G 1 への入力容量 C 1 が入力 A 1 ~ A m の状態に依存しない構成とすることができます。論理ゲートまたはブロック G 1 からは出力 B 1 ~ B n が output されている。なお、論理ゲートまたはブロック G 2 は入力容量 C 2 が一定であるような論理ゲートあるいはブロックである。このとき、入力容量 ( C 1 + C 2 ) が一定となり、入力 i n から出力 o u t への遅延時間を入力 A 1 ~ A m の状態に依らず一定にすることができる。

40

【 0 0 6 0 】

本発明の第 1 3 実施形態に係る半導体集積回路装置を用いることにより、入力容量無依存化装置 8 に供給される入力について、入力容量無依存化装置を介して入力する 1 つの論理ゲートやブロックの他の全ての入力の状態に依らず入力容量が一定となる。

【 0 0 6 1 】

50

## (第14実施形態)

次に、図14を用いて、本発明の第14の実施形態に係る半導体集積回路装置について説明する。図14に示すように、この第14実施形態は、第13実施形態における入力容量無依存化装置8をインバータ80によって構成したものである。その他の構成は、図13と同一なので重複説明を省略する。

## 【0062】

本発明の第14実施形態に係る半導体集積回路装置を用いることにより、入力容量無依存化装置につなげた入力について、入力容量無依存化装置を介して入力する論理ゲートやブロックの他の全ての入力の状態に依らず入力容量が一定となる。

## 【0063】

10

## (第15実施形態)

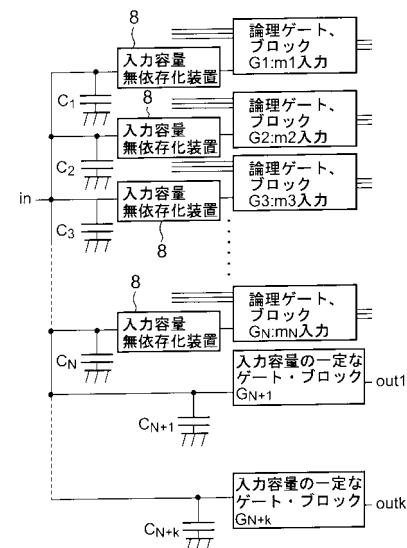

次に、図15を用いて、本発明の第15実施形態に係る半導体集積回路装置について説明する。

## 【0064】

図15において、入力inが全ての入力容量無依存化装置8または入力容量の一定な論理ゲートあるいはブロックに入力していれば、入力inの入力容量(Cin)をG1~GNまでのゲートの入力in以外の全ての入力の状態に依存することなく一定とすることができます。このとき、入力inから入力容量無依存化装置8の出力までの遅延と、入力inから入力容量の一定なゲート、ブロックの出力(out1~outk)までの遅延が他の論理ゲートあるいはブロックの入力信号の状態を受けることが無くなる。入力容量の一定な論理ゲートあるいはブロックがない場合もある。

## 【0065】

本発明の第15実施形態に係る半導体集積回路装置を用いることにより、入力容量無依存化装置につなげた入力について、入力容量無依存化装置を介して入力する全ての論理ゲートやブロックの他の全ての入力の状態に依らず入力容量が一定となる。

## 【0066】

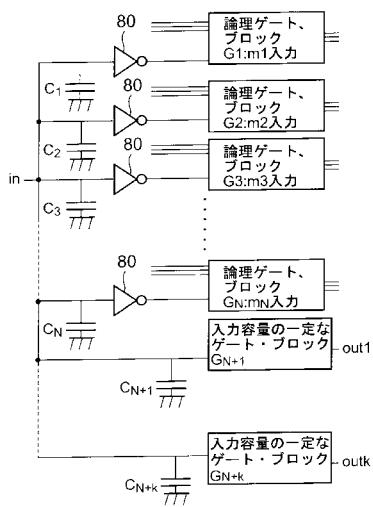

## (第16実施形態)

次に、図16を参照しながら、本発明の第16実施形態に係る半導体集積回路装置について説明する。

## 【0067】

30

第16実施形態は、図16に示すように、第15実施形態の入力容量無依存化装置8をインバータ80により実現したものである。このように構成しても、入力inの入力容量を一定とすることができます。その他の構成については、図15と同一なので重複説明を省略する。

## 【0068】

本発明の第16実施形態に係る半導体集積回路装置を用いることにより、入力容量無依存化装置に接続された入力について、入力容量無依存化装置を介して入力する全ての論理ゲートやブロックの他の全ての入力の状態に依らず入力容量が一定となる。

## 【0069】

## (第17実施形態)

40

従来のゲーティッドクロック回路では、図22に示すようにクロックバッファ51の出力を直接に2入力NOR回路に入力していたが、本第17実施形態においては、クロック信号が入力されるすべての多入力論理回路について、クロック信号の入力ピンに、バッファ回路6a, 6bを入れることとする。このように構成すると、例えば図22の回路は、図17に示されるような回路となる。

## 【0070】

ルートバッファ51からは2つのバッファ回路6a, 6bの容量が見えるだけなので、セレクタ回路57の出力56aおよび56bの状態には無関係になる。その結果として、フリップフロップ55aへのクロック入力のタイミングは出力56bの影響を受けなくなり、フリップフロップ55bへのクロック入力のタイミングは出力56aの影響を受けなく

50

なる。挿入されたバッファ回路 6 a, 6 b によりクロック信号が反転する場合には N O R 回路 5 2 a および 5 2 b 以降において可能である。本実施形態ではバッファ回路 5 4 の後段において、もう 1 つバッファ回路 7 をそれぞれ挿入することによってその調節を行なっている。

【 0 0 7 1 】

本発明の第 1 7 実施形態に係る半導体集積回路装置を用いることにより、あるブロックに属するフリップフロップ 5 5 a または 5 5 b に入力されるクロック信号のタイミングが、他のブロックへ供給されるクロック信号を制御する信号の状態の影響を受けなくなる。

【 0 0 7 2 】

( 第 1 8 実施形態 )

次に、図 1 8 を参照しながら、本発明の第 1 8 実施形態に係る半導体集積回路装置について説明する。

【 0 0 7 3 】

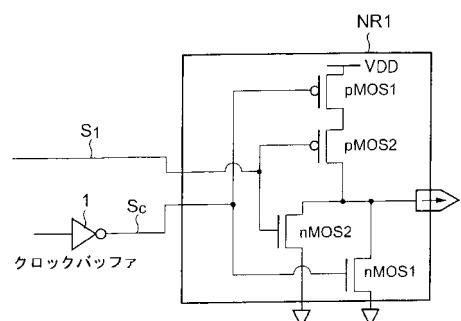

この第 1 8 実施形態に係る半導体集積回路装置は、図 1 1 の N O R 回路 N R 1 の詳細な構成を示すものである。図 1 8 において、クロックバッファ 1 から出力されたクロック信号 S C は 2 入力 N O R 回路 ( N R 1 ) に入力されている。クロック制御信号 S 1 が N O R 回路 N R 1 に入力されている。ここで、N O R 回路 N R 1 の出力信号はクロック信号として用いられており、クロック制御信号 S 1 に応じて、クロックを伝達するか、しないかが制御される。

【 0 0 7 4 】

クロック信号 S C は電源 V D D に直接接続された p M O S 1 と n M O S 1 に入力される。クロック制御信号 S 1 は p M O S 2 と n M O S 2 に入力される。このように接続することにより、クロックバッファ 1 から見た N O R 回路 N R 1 の入力ピン容量は、クロック制御信号 S 1 がハイであるかローであるかの影響を受け難くなる。図 1 1 に示した第 2 ないし第 4 の N O R 回路 N R 2 ~ N R 4 についても図 1 8 と同一の回路構成が適用可能である。ただし、第 4 の N O R 回路 N R 4 は省略することもできる。

【 0 0 7 5 】

本発明の第 1 8 実施形態に係る半導体集積回路装置を用いることにより、2 入力 N O R 回路のクロック信号入力ピンの入力ピン容量が、制御入力の信号の状態の影響を受け難くすることができる。

【 0 0 7 6 】

( 第 1 9 実施形態 )

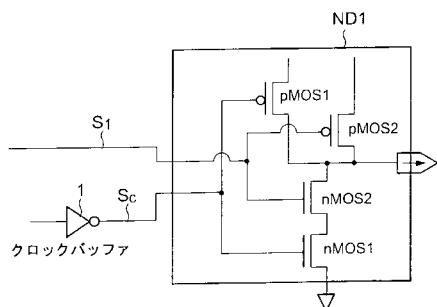

次に、図 1 9 を参照しながら本発明の第 1 9 実施形態に係る半導体集積回路装置について詳細に説明する。

【 0 0 7 7 】

クロックバッファ 1 から出力されたクロック信号 S C は、2 入力 N A N D 回路 N D 1 に入力され、クロック制御信号 S 1 も N A N D 回路 N D 1 に入力されている。ここで、N A N D 回路 N D 1 の出力信号はクロック信号として用いられ、クロック制御信号 S 1 に応じて、クロックを伝達するか、しないかが制御される。クロック信号 S C は p M O S 1 と接地 G N D に直接接続された n M O S 1 に入力される。クロック制御信号 S 1 は p M O S 2 と n M O S 2 に入力される。

【 0 0 7 8 】

このように接続することにより、クロックバッファ 1 から見た N A N D 回路 N D 1 の入力ピン容量は、クロック制御信号 S C がハイであるかローであるかの影響を受け難くなる。

【 0 0 7 9 】

本発明の第 1 9 実施形態に係る半導体集積回路装置を用いることにより、2 入力 N A N D 回路のクロック信号入力ピンの入力ピン容量が、制御入力の信号の状態の影響を受け難くすることができる。

【 0 0 8 0 】

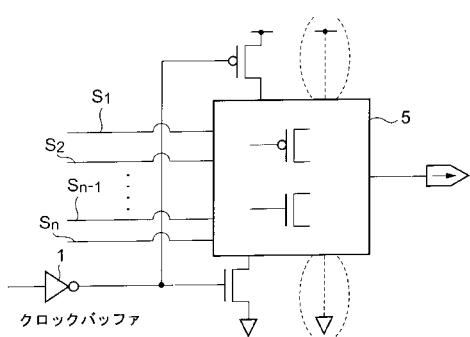

( 第 2 0 実施形態 )

10

20

30

40

50

次に、図20を参照しながら本発明の第20実施形態に係る半導体集積回路装置について説明する。第20実施形態は、第18実施形態および第19実施形態を一般的な多入力論理回路5に応用した例である。ゲーティッドクロック用のクロックツリーを構成することにより、多入力論理回路5を用いてクロックの制御を行なう場合、その多入力論理回路5における必要な論理を形成するために、クロック信号を入力するpMOSおよびnMOSが、図20に破線で示すように、pMOSは直接VDD電源に接続され、nMOSは直接GND電位に接続されるように構成する。

#### 【0081】

本発明の第20実施形態に係る半導体集積回路装置を用いることにより、多入力論理回路のクロック信号入力ピンの入力ピン容量が、制御入力の信号の状態の影響を受け難くすることができる。

10

#### 【0082】

#### 【発明の効果】

以上、詳細に説明したように、本発明に係る半導体集積回路装置によれば、論理回路が複数の入力を有すると共にこれら複数の入力の信号状態がそれぞれ異なることにより、それぞれの入力ピンの容量に違いが発生する論理回路よりなるものにおいて、前記複数の入力を有する前記論理回路の入力の1つもしくは複数に設けられ、前記複数の入力の状態の如何に拘わらず、この入力が有する入力容量を一定に保つ入力容量等化回路を備えるようにしたので、多入力論理ゲートの入力ピン容量を他の入力信号の状態に関係なく一定にし、集積回路中を伝搬する信号の遅延時間を正確に見積もることができ、複数段または複数並列に設けられた論理素子間の遅延時間を全て一致させることができとなる。

20

#### 【図面の簡単な説明】

【図1】本発明の第1実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図2】本発明の第2実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図3】本発明の第3実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図4】本発明の第4実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図5】本発明の第5実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図6】本発明の第6実施形態に係る半導体集積回路装置の構成を示す回路図。

【図7】本発明の第7実施形態に係る半導体集積回路装置の構成を示す回路図。

【図8】本発明の第8実施形態に係る半導体集積回路装置の構成を示す回路図。

30

【図9】本発明の第9実施形態に係る半導体集積回路装置の構成を示す回路図。

【図10】本発明の第10実施形態に係る半導体集積回路装置の構成を示す回路図。

【図11】本発明の第11実施形態に係る半導体集積回路装置の構成を示す回路図。

【図12】本発明の第12実施形態に係る半導体集積回路装置の構成を示す回路図。

【図13】本発明の第13実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図14】本発明の第14実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図15】本発明の第15実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図16】本発明の第16実施形態に係る半導体集積回路装置の構成を示すブロック図。

【図17】本発明の第17実施形態に係る半導体集積回路装置の構成を示す回路図。

【図18】本発明の第18実施形態に係る半導体集積回路装置の構成を示す回路図。

40

【図19】本発明の第19実施形態に係る半導体集積回路装置の構成を示す回路図。

【図20】本発明の第20実施形態に係る半導体集積回路装置の構成を示す回路図。

【図21】従来の半導体集積回路装置の構成を示す論理ブロック図。

【図22】従来の半導体集積回路装置の構成を示す回路図。

#### 【符号の説明】

1 クロックバッファ

2, 4 入力容量等化装置

6a, 6B, 7 バッファ回路

5 多入力論理回路

8 入力容量無依存装置

50

## 80 インバータ

N R 1 ~ N R 8 第1ないし第8のN O R回路

G 1 ~ G 2<sup>n</sup> 論理ゲート/ブロック

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図13】

【図11】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(72)発明者 濱 田 基 翔

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 黒 田 忠 広

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

審査官 宮島 郁美

(56)参考文献 特開平11-340802(JP, A)

特開平06-230934(JP, A)

特開平06-197002(JP, A)

特開平08-162945(JP, A)

特開平06-085658(JP, A)

特開平05-063544(JP, A)

実開平05-031363(JP, U)

特開平04-357710(JP, A)

特開平04-317221(JP, A)

特開平01-314015(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096