US 20060131177A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2006/0131177 A1

## (10) Pub. No.: US 2006/0131177 A1 (43) Pub. Date: Jun. 22, 2006

### Bogart et al.

### (54) MEANS TO ELIMINATE BUBBLE ENTRAPMENT DURING ELECTROCHEMICAL PROCESSING OF WORKPIECE SURFACE

(76) Inventors: Jeffrey Bogart, Los Gatos, CA (US);

Bulent M. Basol, Manhattan Beach, CA (US)

Correspondence Address: KNOBBE MARTENS OLSON & BEAR LLP 2040 MAIN STREET FOURTEENTH FLOOR IRVINE, CA 92614 (US)

- (21) Appl. No.: 11/283,004

- (22) Filed: Nov. 18, 2005

### **Related U.S. Application Data**

(60) Continuation-in-part of application No. 10/816,340, filed on Mar. 31, 2004, which is a continuation-in-part of application No. 10/152,793, filed on May 23, 2002, which is a division of application No. 09/511,278, filed on Feb. 23, 2000, now Pat. No. 6,413,388. (60) Provisional application No. 60/635,112, filed on Nov. 19, 2004. Provisional application No. 60/462,919, filed on Apr. 14, 2003.

### **Publication Classification**

### (57) **ABSTRACT**

Methods and systems are provided to eliminate bubble entrapment during electrochemical processing of a substrate, wherein a rigid plate with fluid openings allow process solution to flow between the front surface of the substrate and an electrode. The plate includes a protruding region. In operation, the protruding region causes a raised solution surface to touch the front surface of the wafer prior to complete immersion of the substrate in the solution. In other embodiments, the raised surface of the solution can be provided by applying pressure to a flexible pad or other workpiece surface influencing device (WSID).

FIG. 3

FIG. 6D

7G. 11

## FIG. 15A

FIG. 15B

FIG. 16C

## FIG. 17A

FIG. 17B

### MEANS TO ELIMINATE BUBBLE ENTRAPMENT DURING ELECTROCHEMICAL PROCESSING OF WORKPIECE SURFACE

#### REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the priority benefit under 35 U.S.C. § 119(e) of U.S. provisional application No. 60/635,112, filed Nov. 19, 2004, and is a continuation-inpart (CIP) of U.S. application Ser. No. 10/816,340, filed Mar. 31, 2004 (attorney docket No. ASMNUT.2DVCP1; NT-295), which is a CIP of U.S. application Ser. No. 10/252,793, filed May 23, 2002 (attorney docket No. ASMNUT.041DV1; NT-102D), which is a divisional of U.S. application Ser. No. 10/511,278, filed Feb. 23, 2000 (issued as U.S. Pat. No. 6,413,388, issued Jul. 2, 2002). This Application also claims priority to U.S. provisional application No. 60/462,919, filed Apr. 4, 2003 by way of application Ser. No. 10/816,340.

### FIELD

**[0002]** The present invention generally relates to semiconductor integrated circuit technology and, more particularly, to a device for electrotreating or electrochemically processing a workpiece.

#### BACKGROUND

**[0003]** Conventional semiconductor devices such as integrated circuits (IC) generally comprise a semiconductor substrate, usually a silicon substrate, and a plurality of conductive material layers separated by insulating material layers. Conductive material layers, or interconnects, form the wiring network of the integrated circuit. Each conductor in the wiring network is isolated from the neighboring conductors by the insulating layers, also known as interlayer or interlevel dielectrics (ILDs). One dielectric material that is commonly used in silicon integrated circuits is silicon dioxide, although there is now a trend to replace at least some of the standard dense silicon dioxide material in IC structures with low-k dielectric materials such as organic, inorganic, spin-on and CVD candidates.

[0004] Conventionally, IC interconnects are formed by filling a conductor such as copper in features or cavities etched into the dielectric interlayers by a metallization process. Copper is becoming the preferred conductor for interconnect applications because of its low electrical resistance and good electromigration property. The preferred method of copper metallization is electroplating. In an integrated circuit, multiple levels of interconnect networks laterally extend with respect to the substrate surface. Interconnects formed in sequential layers can be electrically connected using features such as vias or contacts. In a typical interconnect fabrication process, first an insulating layer is formed on the semiconductor substrate, and patterning and etching processes are then performed to form features or cavities such as trenches, vias, and pads etc., in the insulating layer. Then copper is electroplated to fill all the features. In such electroplating processes, the wafer is placed on a wafer carrier and a cathodic (-) voltage with respect to an electrode is applied to the wafer surface while a deposition electrolyte wets both the wafer surface and the electrode.

**[0005]** Once the plating is over, a material removal step such as a chemical mechanical polishing (CMP) process step

is conducted to remove the excess copper layer, which is also called copper overburden, from the top surfaces (also called the field region) of the workpiece, leaving copper only in the features. An additional material removal step is then employed to remove the other conductive layers such as the barrier/glue layers that are on the field region. Fabrication in this manner results in copper deposits within features that are physically as well as electrically isolated from each other. Another important material removal technique, especially for wafers with low-k dielectrics, is the electrochemical polishing (electropolishing) or electrochemical etching process. In electropolishing, an anodic voltage is applied to the wafer surface with respect to a cathodic electrode in an electropolishing electrolyte. Excess conductor, such as overburden copper is removed without physically touching and stressing the interconnect structure. It is possible to perform electropolishing on a wafer surface while physically touching the surface with a pad material. Such techniques are called electrochemical mechanical polishing or etching methods.

**[0006]** One technique used for planar deposition and removal of materials is collectively referred to as Electrochemical Mechanical Processing (ECMPR), which term is used to include Electrochemical Mechanical Deposition (ECMD) processes as well as Electrochemical Mechanical Polishing (ECMP) (also known as Electrochemical Mechanical Etching (ECME)). It should be noted that in general both ECMD and ECMP processes are referred to as electrochemical mechanical processing (ECMPR) since both involve electrochemical processes and physical touching of, or mechanical action on, the workpiece surface. All electrochemical techniques for material deposition and removal may be referred to as "electrotreatment."

[0007] In one aspect of an ECMPR method, a workpiecesurface-influencing-device (WSID) such as a mask, pad or a sweeper is used during at least a portion of the electrotreatment process when there is physical contact or close proximity and relative motion between the workpiece surface and the WSID. Descriptions of various planar deposition and planar etching methods and apparatus can be found in the following patents and pending applications, all commonly owned by the assignee of the present invention. U.S. Pat. No. 6,176,992, issued Jan. 23, 2001, entitled "Method and Apparatus for Electrochemical Mechanical Deposition." U.S. Pat. No. 6,534,116, issued Mar. 18, 2003, entitled "Plating Method and Apparatus that Creates a Differential Between Additive Disposed on a Top Surface and a Cavity Surface of a Workpiece Using an External Influence," filed on Dec. 18, 2000 and U.S. Pat. No. 6,951,551, issued Jul. 26, 2005, entitled "Plating Method and Apparatus for Controlling Deposition on Predetermined Portions of a Workpiece". These methods can deposit metals in and over cavity sections on a workpiece in a planar manner. The disclosures of these patents are incorporated herein by reference. They also have the capability of yielding novel structures with excess amount of metals over the features irrespective of their size, if desired.

**[0008]** In ECMD methods, the surface of the workpiece is wetted by the electrolyte and is rendered cathodic with respect to an electrode, which is also wetted by the electrolyte. During ECMD, the wafer surface is pushed against or in close proximity to the surface of the WSID or vice versa when relative motion between the surface of the workpiece

and the WSID results in sweeping of the workpiece surface. Planar deposition is achieved due to this sweeping action as described in the above-cited patent applications.

**[0009]** In ECMP methods, the surface of the workpiece is wetted by the electropolishing electrolyte or etching solution, but the polarity of the applied voltage is reversed, thus rendering the workpiece surface more anodic compared to the electrode. A WSID touches the surface during removal of the layer from the workpiece surface.

**[0010]** Very thin planar films can be obtained by first depositing a planar layer using an ECMD technique and then applying an ECMP technique on the planar film in the same electrolyte by reversing the applied voltage. Alternatively, the ECMP step can be carried out in a separate machine and a different etching electrolyte or electropolishing solution. This way the thickness of the deposit may be reduced in a planar manner. In fact, an ECMP technique may be continued until all the metal on the field regions is removed. It should be noted that a WSID may or may not be used during the electroetching process since substantially planar etching can be achieved either way as long as the starting layer surface is planar.

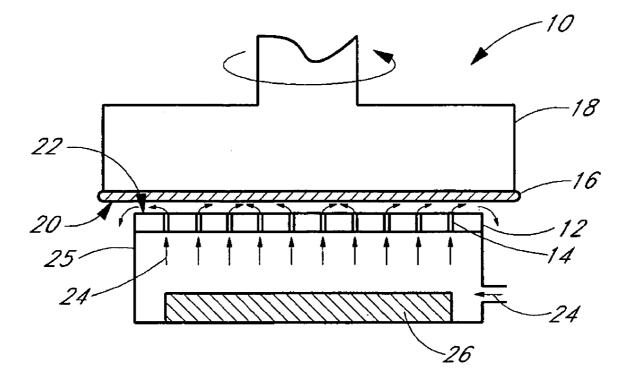

[0011] FIG. 1 is a schematic illustration of an exemplary conventional ECMPR system 10 used for processing wafers. In FIG. 1, a WSID 12 having openings 14 in it, is disposed in close proximity of a workpiece or wafer 16 to be processed. The wafer 16 is a silicon wafer to be plated with a conductor metal, preferably copper or copper alloy. The wafer may or may not have a previously plated copper layer on it. The wafer 16 is retained by a wafer carrier 18 so as to position front surface 20 of the wafer against top surface 22 of the WSID 12. The openings 14 are designed to assure uniform deposition of copper from an electrolyte solution 24, depicted by arrows, onto the front surface 22, or uniform electropolishing from the front surface 22. The top surface 22 of the WSID 12 facing the front surface 20 of the wafer is used as the sweeper and the WSID 12 itself establishes appropriate electrolyte flow and electric field flow to the front surface 22 for globally uniform deposition or electroetching. Such an ECMPR system 10 also includes an electrode 26, which is immersed in the electrolyte 24. The electrolyte solution 24 is contained in a process chamber 25. The electrolyte 24 is in fluid communication with the electrode 26 and the front surface 20 of the wafer 16 through the openings 14 in the WSID 12.

[0012] It should be noted that the electrode 26 is only schematically shown in FIG. 1. In actual practice, the electrodes are shielded with a particle filter and other precautions are taken to avoid bubble accumulation under the WSID and to avoid particles generated on the electrode 26 to reach the surface of the wafer 16. An exemplary copper electrolyte may be copper sulfate solution with additives such as accelerators, suppressors, leveler, chloride and such, which are commonly used in the industry. The top surface 22 of the WSID 12 sweeps the front surface 20 the wafer while an electrical potential is established between the electrode 26 and the front surface 20 of the wafer. For deposition of a planar film such as copper, the front surface of the wafer 12 is made more cathodic (negative) compared to the electrode 26, which becomes the anode. For electropolishing in the same system the wafer surface is made more anodic than the electrode.

[0013] U.S. application Ser. No. 09/960,236 filed on Sep. 20, 2001, entitled "Mask Plate Design," assigned to the assignee of the present invention, discloses various WSID embodiments. Also, U.S. application Ser. No. 10/155,828 filed on May 23, 2002, entitled Low Force Electrochemical Mechanical Deposition Method and Apparatus, also assigned to the same assignee of the present invention teaches means of applying force to the wafer surface by a WSID for ECMPR.

**[0014]** To this end, there is still a need for further development of high-throughput electrochemical processes and apparatus that can yield deposits with less defect and high yield, and methods and apparatus that provide more uniform material removal from workpiece surfaces.

### SUMMARY OF THE INVENTION

**[0015]** In accordance with one aspect of the invention, a method is provided for immersing a surface of a wafer in a solution for processing the surface. The method included flowing the solution through openings of a rigid plate having a protruding region to form a raised solution surface over the protruding region. A selected portion of the wafer surface is contacted with the raised solution surface. The wafer surface is immersed fully into the solution.

**[0016]** In accordance with another aspect of the invention, a system is provided for eliminating bubble entrapment under a surface of a wafer when the surface is immersed into a process solution to process the surface of a wafer. The system includes a rigid plate, having a protruded region and fluid openings. The plate is configured such that when the solution flows through the rigid plate, a raised solution surface forms over the protruded region. The system also includes a moving mechanism configured to move the wafer such that, as the wafer is moved towards the solution, a selected portion of the surface of the wafer contacts the raised solution surface before immersing the surface of the wafer fully into the solution.

**[0017]** In accordance with another aspect of the invention, a method of processing a conductive surface of a wafer using a process solution is provided. The method includes flowing the solution through openings of a plate having a protruding region to form a raised solution surface over the protruding region. A selected portion of the conductive surface is contacted with the raised solution surface. The conductive surface is fully immersed into the solution and the conductive surface is processed.

**[0018]** In accordance with another aspect of the invention, a system is provided for electroprocessing a conductive surface of a wafer using a process solution. The system includes an electrode configured to be placed in the process solution. A rigid plate, having a protruded region and fluid openings, is configured to be immersed in the solution and positioned between the electrode and the conductive surface. The plate is configured such that as the solution flows through the rigid plate, a raised solution surface forms over the protruded region. A moving mechanism is configured to move the wafer such that as the wafer moves towards the solution, a selected portion of the conductive surface contacts the raised solution surface before immersing the surface fully into the solution.

### BRIEF DESCRIPTION OF THE DRAWINGS

**[0019] FIG. 1** is a schematic illustration of an exemplary conventional electrochemical mechanical processing system;

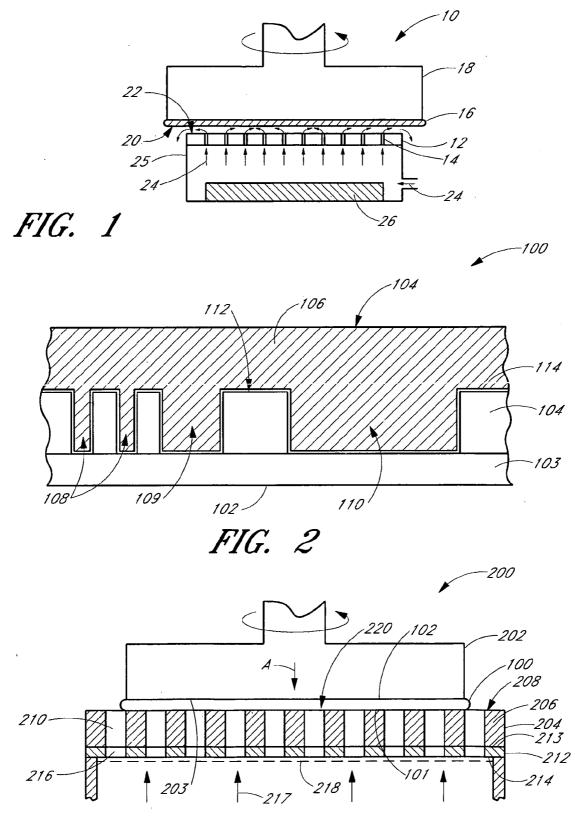

**[0020]** FIG. 2 is an exemplary portion of a wafer surface with a planar conductive layer;

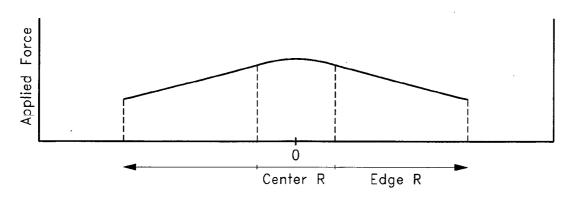

**[0021] FIG. 3** is a schematic illustration of an electrochemical mechanical processing system where a force is applied to the back surface of the wafer;

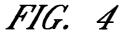

**[0022]** FIG. 4 is a graph showing the distribution of the applied force over the wafer surface as the force is applied in the manner shown in FIG. 3;

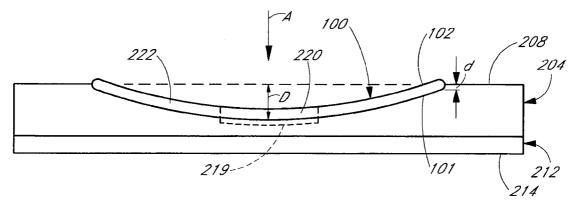

**[0023] FIG. 5** is a schematic illustration of interaction between a wafer front surface and the workpiece surface influencing device (WSID) as the center region of the wafer back surface is pressed against the WSID;

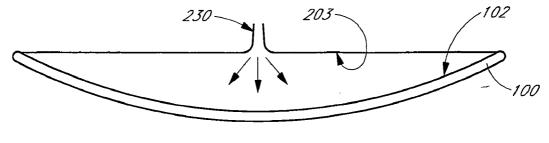

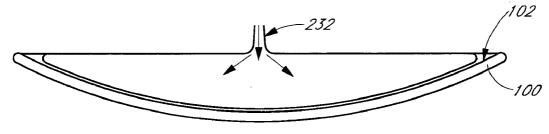

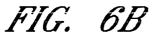

**[0024] FIGS. 6A-6D** are schematic illustrations of various force sources to apply force on the back surface of a wafer;

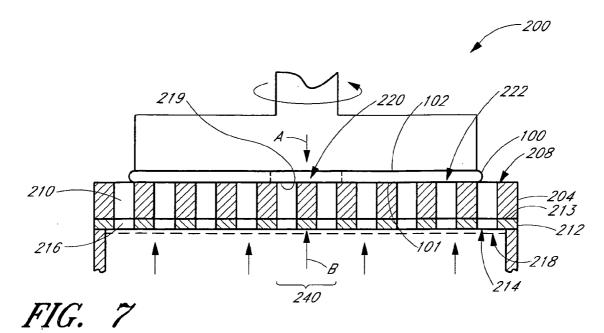

**[0025] FIG. 7** is a schematic illustration of the electrochemical mechanical processing system where a force is applied to the back surface of the workpiece surface influencing device;

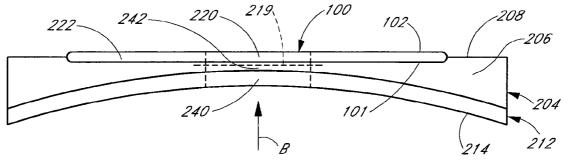

**[0026] FIG. 8** is a schematic illustration of the interaction between a wafer front surface and the workpiece surface influencing device as the surface of the workpiece surface influencing device is pressed against the center region of the wafer front surface;

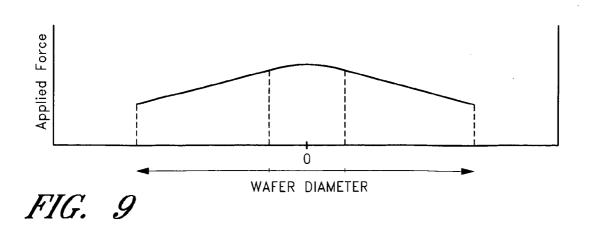

**[0027] FIG. 9** is a graph showing the distribution of the applied force over the wafer surface as the force is applied in the manner shown in **FIG. 8**;

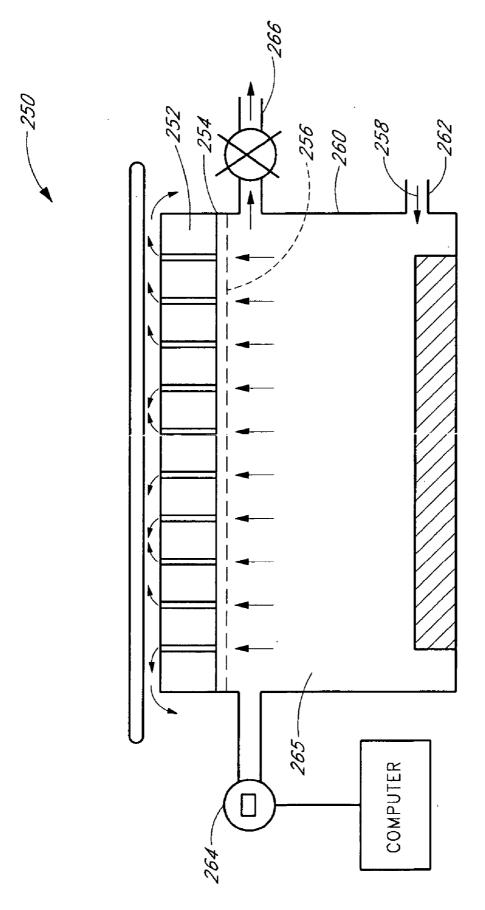

**[0028] FIG. 10** is a schematic illustration of an embodiment of a smart electrochemical mechanical processing system where a force is applied to the back surface of the workpiece surface influencing device;

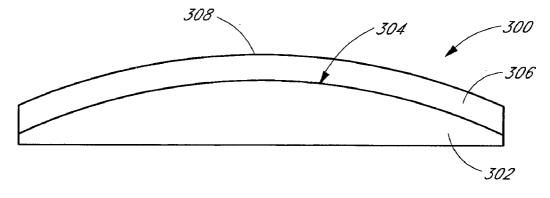

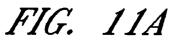

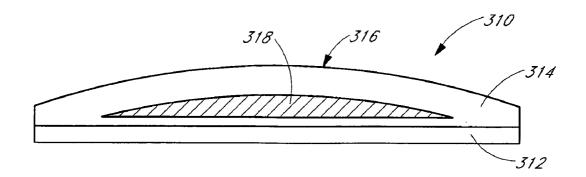

**[0029] FIG. 11A-11B** are schematic illustrations of various combinations of support plate and workpiece influencing device having convex profiles;

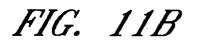

**[0030] FIGS. 12A-14B** are schematic illustrations of various plates having varying thickness and resulting degrees of bowing under applied pressure;

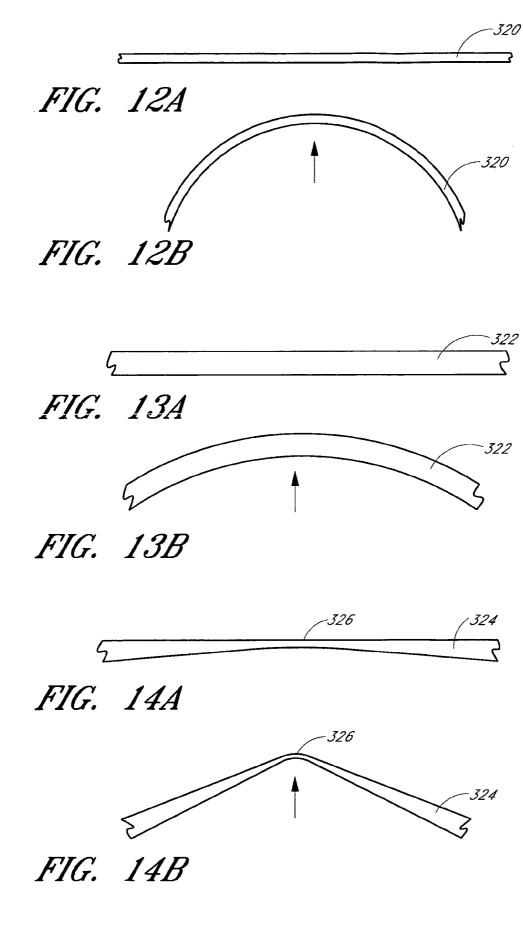

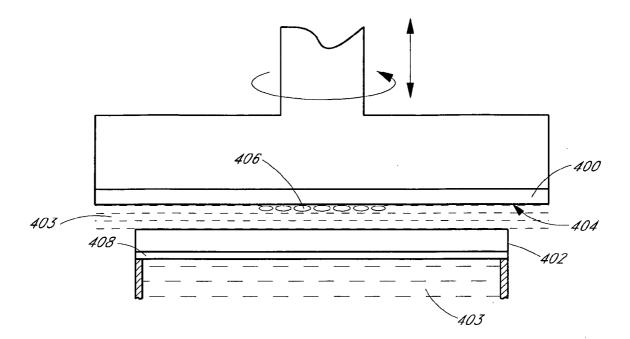

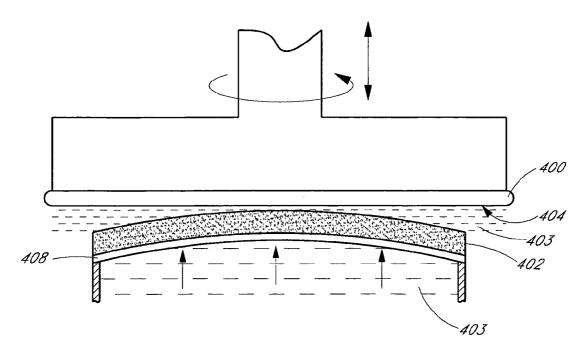

**[0031] FIG. 15A-15B** are schematic illustrations of removing entrapped bubbles by bowing the WSID towards the center of a wafer during a process;

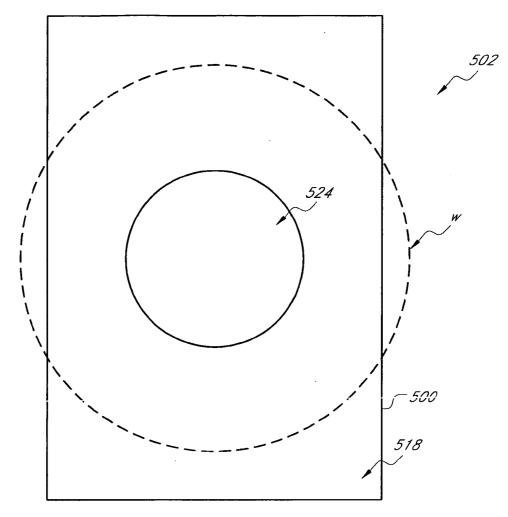

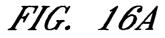

**[0032] FIG. 16A** is a schematic illustration of the relative positions of a wafer and an embodiment of a rigid plate having a protruding region in top view;

**[0033] FIG. 16B** is a schematic illustration of an alternative electrochemical mechanical processing system including the rigid plate shown in **FIG. 16A**, wherein the surface of the wafer contacts a raised solution surface formed over the protruding region;

**[0034] FIG. 16C** is a schematic illustration of system shown in **FIG. 16B**, after the surface of the wafer has been moved to be immersed into the solution;

**[0035] FIG. 17A-17B** are schematic illustrations of the relative positions of a wafer and another embodiment of a rigid plate having a protruding region in top view and side views;

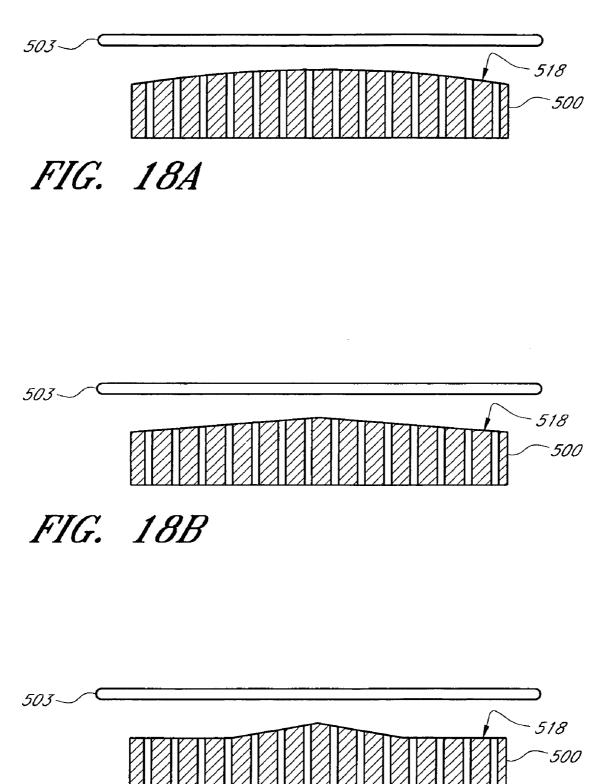

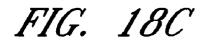

**[0036] FIGS. 18A-18F** are schematic illustrations of various embodiments of rigid plates; and

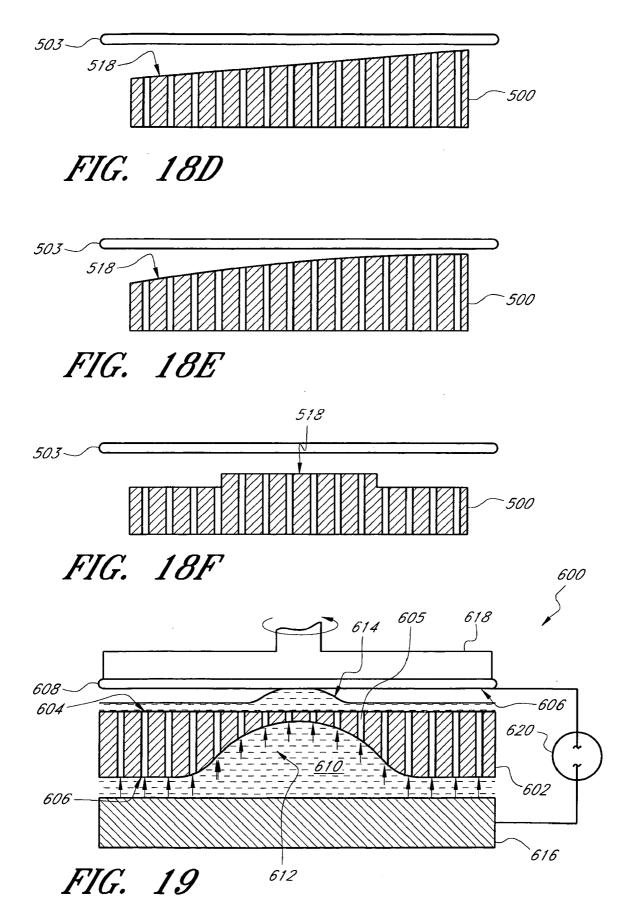

**[0037] FIG. 19** is a schematic illustration of an electrochemical mechanical processing system including an embodiment of a rigid plate having a cavity.

#### DETAILED DESCRIPTION

[0038] The preferred embodiments will now be described using the example of fabricating interconnects for integrated circuit applications. It should, however, be recognized that present invention can be used to operate on any workpiece with various electroplated materials such as Au, Ag, Ni, Pt, Pd, Fe, Sn, Cr, Pb, Zn, Co and their alloys with each other or other materials, for many different applications such as packaging, flat panel displays, magnetic heads and such. In the examples provided below, the example material that is electroplated or electropolished will be copper, but it will be understood that other materials can instead be used.

**[0039]** In electrochemical mechanical processing (ECMPR) such as electrochemical mechanical deposition (ECMD) and electrochemical mechanical polishing (ECMP) or etching (ECME), since the mechanical action on wafer surface assists planarization of the surface of the wafer, uniformity of this mechanical action is important to obtain uniform process results, such as a uniformly planarized wafer surface.

[0040] FIG. 2 shows an exemplary portion of a substrate or workpiece 100 such as a wafer having a front and a back surface 101 and 102. The wafer 100 comprises a semiconductor substrate 103 and an insulation or dielectric layer 104 on which a planar conductive layer 106 such as a planar copper layer is formed in accordance with embodiments described herein. The copper layer 106 maintains a uniform overburden thickness over the entire wafer surface. The copper layer 106 is plated to fill features in the dielectric layer using an ECMD process in which the wafer surface is mechanically swept with a pad mask or WSID during plating. Further, in an exemplary process the copper layer 106 may be electropolished using ECMP. Before the plating process, the dielectric layer 104 is processed to form features such as vias 108 and trenches 109 and 110. The features 108, 109 and 110 and top surface 112 of the dielectric layer, which is often referred to as a field region or surface, are lined with one or more conductive layers such as a barrier layer 114 and a copper seed layer (not shown) before forming the copper layer 106. Interconnects are formed when the copper layer **106** is removed down to the level of field regions 112 and the barrier layer 144 covering the field regions 112 is also removed. Overall efficiency of this process depends on the thickness uniformity of the copper layer 106 over the entire wafer surface. As will be described more fully below, the present invention provides a method of forming a planar conductive layer while maintaining its thickness uniformity.

**[0041]** During ECMD and ECMP processes, wafers are typically rotated and may additionally be moved laterally. As can be appreciated, on a rotating wafer surface the linear

velocity due to rotation is zero right at the center of the wafer and it increases linearly towards the edge of the wafer in proportion to the distance to the center. The linear velocity is highest right at the edge of the wafer and it is given by the relationship:  $V=(2\pi rR/60)$  cm/second, where "r" is the radius of the wafer in centimeters and "R" is the rotation in revolution per minute (rpm). As can be seen from this relationship, velocity "V" increases as the radius of the wafer "r" increases. Mechanical action delivered by a WSID (see FIG. 1) onto wafer surface increases with the relative velocity between the WSID and wafer surface as well as the force applied onto the surface by the WSID. Therefore, in an electrochemical mechanical process, in one method, the uniformity of the mechanical action on the wafer surface may be improved by keeping the relative velocity between the WSID and the whole wafer surface substantially the same while keeping the force applied by the WSID onto the wafer surface substantially constant. An example of this method can be found in U.S. patent application Ser. No. 10/288,558, entitled Electrochemical Mechanical Deposition with Advancible Sweeper, filed Nov. 4, 2002. In that application, a belt-type WSID is used for ECMD and ECMP processes. The belt WSID or the wafer may be moved linearly. The high linear velocity of the belt WSID is constant everywhere on the wafer surface as long as the velocity on the wafer surface due to rpm is much lower than the linear velocity of the belt WSID. For example, if the wafer is rotated with 5 rpm and belt linear velocity is 100 cm/sec, the linear velocity at the edge of the wafer due to rpm would be about 5 cm/sec for an 8" wafer. This is negligible compared to the belt speed of 100 cm/sec.

**[0042]** In another method, if the relative velocity between the WSID and the wafer surface is not constant, the force applied by the WSID is adjusted such that a higher force is applied onto certain surface regions, such as the central region of the wafer, where the relative velocity is low. As previously mentioned, in exemplary ECMD or ECMP processes, the wafer is rotated and also translated over a stationary WSID surface. If the velocity of the lateral motion is lower than the motion near the edge of the wafer due to rotation, velocity near the center of the wafer would be lower than at the edge. Therefore, additional force should be applied near the center of the wafer to improve process results.

[0043] There are various approaches that may be used to apply additional force on the wafer surface near its center. One such approach involves shaping of the wafer surface. When such shaped wafer surface is pushed against a pad structure, its center gets the highest force. An example of shaping wafer 100 while it is processed may be described in connection with FIG. 3, which illustrates a partial view of an ECMPR system 200. In FIG. 3, only components such as a wafer carrier 202 and a WSID 204 of the system 200 are illustrated for the purpose of clarity. The wafer carrier 202 holds the wafer 100 by the back surface 102 while exposing the front surface 101 of the wafer to the WSID 204. The wafer is held on a chuck face 203 of the wafer carrier 202.

[0044] The WSID 204 may have a compressible layer 206 having a top surface 208. The top surface 208 may be made of a flexible material and may be abrasive or it may contain a polishing pad material. The top surface 208 is brought to physical contact with the front surface 101 of the wafer during the ECMD or ECMP processes. The WSID 204

comprises openings 210, such as holes with various geometrical shapes or slits with varying width, or may be made of a porous material that allows a process solution (not shown) to flow through the WSID and wet the surface of the wafer. The WSID 204 is supported by a support plate 212, which has a top surface 213 and a back surface 214. The WSID 204 is placed on the top surface 213 of the support plate 212. The support plate 212 is fixed on sidewalls 25 of a process chamber, which is not shown in FIG. 3 but can be seen in FIG. 1. The openings 210 may continue through the support plate 214 as support plate openings 216, although size and location of the openings 216 may be different from the openings 210 in the WSID. For example, support plate openings 216 may be made of narrow slits or very small holes. Alternately, support plate openings 216 may be larger than openings 210 of the WSID. Optionally a flow restrictor such as a filter 218 may be placed under the support plate. This filter 218 also reduces the number of particles that may reach the wafer surface. A process solution 217 in the process chamber is delivered to the front surface 101 of the wafer 100. Process solution 217 flows through the pores of the filter 218, openings 216, 210 of the support plate 212 and the WSID 204 to reach the front surface during the process.

[0045] Referring to FIGS. 3-5, shaping of the front surface 101 of the wafer 100 may be performed by applying a force to the back surface 102 of the wafer 100 to deflect the front surface 101. As shown in FIG. 5, as the force is applied to the back surface of the wafer 100, the wafer bows into the WSID and a higher-pressure interface 219 forms between the center region 220 of the front surface of the wafer and the top surface 208 of the WSID 204. This is because the support plate 212 is relatively rigid in this example and extra compression of the compressible layer of the WSID in the central region applies higher force to the wafer surface in this region compared to the edge region. The size of the pressure interface depends on the applied force and depending on the force it may get smaller or larger. A force source in the wafer carrier 202 may apply a force A to the back of the wafer and cause the wafer to bow into the WSID 204, thereby pushing a center region 220 of the wafer 100 in the direction of the arrow A. The force source may use a pressurized fluid, inflatable membranes, or a mechanism using shims or pins to physically apply force to the back surface 102 of the wafer. Application of the force A, gives the wafer 100 and hence the front surface 101 a convex shape which allows WSID to exert more force on the center region 220 than edge region 222 of the wafer 100. In FIG. 4, this can be seen in the force distance graph 224. As seen in the graph, the force applied to the center region is higher than the edge region of the wafer.

[0046] As shown in FIG. 5, as the force A is applied, the center region is pushed into the WSID 204 by a distance D at the center region 220 and a distance d at the edge region 222. Since the force applied by the WSID onto the wafer surface is proportional to the distance the surface is pressed into the WSID, as the D distance becomes larger than the d-distance, the force, which is applied to the center region becomes higher than the edge region. It should be understood that the distances and the convex shape of the wafer are exaggerated in the figures for clarity. In practice the difference between the distance D and distance d may be in the range of 0.1-1 mm for an 8" wafer or as much as 2 mm for a 300 mm wafer. For the purpose of clarity, openings in the WSID are not shown in FIG. 5.

[0047] FIGS. 6A-6D illustrate various configurations of force source. In each configuration edges of the wafer are held by a holding mechanism on the wafer carrier and the force is applied on the back surface of the wafer. FIG. 6A shows a pressurized fluid source 230, preferably air to apply pressure to the back surface of the wafer. The fluid source 230 may be in the chuck face 203 of the wafer carrier (see FIG. 3). FIG. 6B illustrates an inflatable member 232 such as a bladder to fill with pressurized air or another gas to apply pressure. The bladder may be placed between the chuck face and the back surface of the wafer 100, and attached to the fluid source 230. FIG. 6C shows a curved object 234, which may be placed between the back surface of the wafer 100 and the chuck face to press against the back surface 102 of the wafer to shape it. FIG. 6D shows use of pins 236 configured to have varying lengths so that more force is applied to the center region on the back of the wafer 100. The pins 236 may be placed in the chuck face and moved by a moving mechanism.

[0048] As shown in FIG. 7 in system 200, another method for achieving the same result involves applying force to the center region of the WSID 204 and thereby compressing a portion of the WSID more against the center region 220. As shown in FIGS. 7 and 8, since the edges of the support plate 212 are substantially fixed on the side walls of the process chamber, by applying a force in the direction of arrow B to the back surface 214 of the support plate 212, the support plate 212 is bowed towards the front surface 101 of the wafer. This way, a selected region 240 of the support plate 212 is brought closer to the center region 220 of the wafer 100 and forms a high-pressure interface 219. The location of the selected region 240 is configured to correspond to the center region 220 of the wafer. The bowing effect shown in FIG. 8 and other figures are highly exaggerated for the purpose of clarity. In practice, during bowing, the selected region may move up a distance only in the range of 0.1 to 2 millimeters. As the selected region of the support plate is moved closer to the center region 220 of the wafer, a portion 242 of the compressible layer 206 between the center region 220 and the selected region 240 is compressed between these two surfaces. This, in turn, pushes the top surface 208 of the WSID against the center region and applies more force to the center region 220 than the edge region 222. It should be noted that in this method a relatively flexible support plate 212 may be used. By selecting the thickness and flexibility of the support plate and the magnitude of the applied force, the degree of bowing and the magnitude of the extra force applied to the central region may be controlled.

[0049] Referring back to FIG. 7, the force maybe applied to the support plate 212 by exerting more process solution pressure to the back surface of the support plate 212 or the filter 218 placed under it. Such pressure gives the support plate 212 a convex shape. The pressure and thus the magnitude of the applied force may be controlled by various means such as flow restrictors, filters with varying porosity or bleed valves.

[0050] One exemplary method of controlling force involves controlling the flow rate of the process solution. Depending on the porosity of the filter 218, as the flow rate of the process solution increases, the pressure under the filter 218 increases. Since the edges of the support plate 212 are fixed, the support plate 212 bows up under increased process solution flow as shown in FIG. 8. It is also possible to increase or decrease the amount of bowing by keeping the flow constant but by using one or more bleed valves that can control the pressure under the filter. In this case, by controlling the amount of solution that is bled through these valves, the pressure under the filter **218** maybe increased (when valves are closed, restricting the amount of solution bleeding out through them) or decreased (when valves are opened, increasing the amount of solution bleeding out through them) or kept constant at a predetermined pressure level. It should be noted that this process may be automated using feedback control as will be discussed later. For the purpose of clarity, openings in the WSID are not shown in **FIG. 8**.

[0051] Another way of controlling the bowing and thus the force on the central region of the wafer involves controlling the porosity of the filter **218**. At a given solution flow rate, filters with smaller pore size would give more bowing and thus more additional force would be applied to the central section of the wafer. As can be seen in the force-distance graph in **FIG. 9**, the force applied to the center **220** of the wafer is preferably higher than the force applied to the edge **222**.

[0052] FIG. 10 illustrates a smart system 250 which can sense the pressure under the filter element 256 using a transducer. The system 250 includes a WSID 252 supported by a support plate 254. A filter 256 is placed under the support plate 254. The filter 256 may not be needed if the openings in the WSID are small enough to keep the cavity 265 pressurized. However, presence of the filter 256 is preferable since it also filters out any particulates from the process solution before delivering it to the wafer surface. Process solution 258 enters chamber 260 through an inlet 262. Differing from the previously described embodiments, a pressure-monitoring device 264 such as a pressure transducer monitors the solution pressure and turns on and off a bleed valve 266 to keep the pressure, and hence the bowing of the support plate 254 at a predetermined desired value. For example, if the flow is set to a constant value and the pressure in the cavity 265 is higher than the pre-determined value, the bleed valve 266 is automatically opened more to let more solution out and bring the pressure down to the pre-determined level. Similarly, if the actual pressure within cavity 265 is lower than the pre-determined value, then the bleed valve 266 would automatically close to restrict flow through it and bring the pressure up to the pre-determined level. This way, using feedback and computer control, a predetermined value for the pressure is selected and kept through the process. Also, by changing the pressure during the process, more or less force may be applied on the surface in a controlled manner. Bowing is a strong function of the choice of filter, flexibility of the support plate and the pressure under the support plate.

**[0053]** The force may also be controlled by shaping the WSID itself or by constructing the support plate to make it more or less compliant along the diameter of the wafer. Other stiffeners or flexural members can be added to WSID to produce a force curve of any desired shape for planarization, especially at the center region.

[0054] In this respect, FIGS. 11A-11B illustrate various support plate and WSID combined structures to create a bowing effect. As shown in FIG. 11A a first structure 300 includes a support plate 302 having a curved top surface

**304.** A WSID **306** is attached on the curved top surface **304** so that a top surface **308** of the WSID is in compliance with the curved top surface **304** of the support plate **302**. As shown in **FIG. 11B**, a support plate and WSID combined structure **310** includes a support plate **312** and a WSID **314**. In this example, a curved top surface **316** of the WSID is provided using a curved insert **318**. In **FIGS. 11A-11B**, for the purpose of clarity openings of the support plates and the WSIDs are not shown.

[0055] By varying the thickness of the support plate, the applied pressure and the size of the high-pressure interface may be changed. FIGS. 12A-12B illustrate a support plate 320 before and after the application of the force. The support plate 320 is a thin support plate; therefore, with the applied pressure it bows more in comparison to a thicker support plate. This may allow the support plate 320 to apply more localized pressure and to a smaller area of the wafer.

[0056] FIGS. 13A-13B show a support plate 322, which is thicker than the support plate 320 described above. Since it is thicker, the support plate 322 bows less and thereby, it may apply a force to a larger (central) area on the wafer. FIGS. 14A-14B illustrate a support plate 324 before and after the application of the force. The support plate 324 has a thin section 326; therefore, when a pressure is applied to the thin section, the thin section 326 protrudes more. This may allow the support plate 324 to apply more localized pressure and to a smaller area of the wafer. Again, the bowing effects in all these drawing are greatly exaggerated to clearly explain the principles, advantages and distinctions. For the purpose of clarity, openings in the support plates are not shown in FIGS. 12A-14B.

[0057] The above-noted methods and structures may also be used for eliminating bubbles that may be trapped between the wafer surface and the process solution during electroplating and electropolishing processes. As shown in FIG. 15A, as a wafer is first lowered towards the WSID 402 and enters the process solution 403, bubbles 406 may get trapped under the wafer surface 404, especially near the center of the wafer. This is a common problem in electroplating and electropolishing technologies and is generally due to the fact that the edges of the wafer may get wetted by the process solution before its center. If these bubbles stay on the wafer surface during the process, they may generate defects in the forming layers and therefore they should be removed. As shown in FIG. 15B, when the pressure of the solution 403 is increased to bow the support plate 408 towards the wafer 400 at least during the first stage of process when wafer is being lowered down towards the WSID 402, the WSID 402 bows and the solution flowing from the WSID 402 also takes a convex shape. This way when the wafer is lowered towards the WSID 402, the central region of the wafer 400 gets wetted by the process solution 403 first. Because of the convex shape of the WSID 402, the solution from the top of the convex shape reaches the center of the conductive surface of the wafer 400 and wets the center region before the solution flowing from the rest of the WSID 402 reaches and wets the rest of the surface of the wafer 400. This way, since the bubbles are swept away from the center, and no bubble entrapment occurs. For the purpose of clarity, openings in the WSID and the support plates are not shown in FIGS. 15A-15B.

[0058] As will be described more fully below, alternatively, from the foregoing bowed WSID surface principle, the surface of the support plate or solution supply plate through which the solution flows towards the workpiece surface can itself be given a profile to assist removal of bubbles in electrochemical processes without having a compressible layer or a pad on it, particularly in a non-contact ECMPR. Since in a non-contact ECMPR there is no need to touch the wafer surface with a WSID, there is no need for a pad, and the WSID may be formed as a rigid structure. In that respect, non-contact ECMPR may actually be called ECPR (electrochemical processing) since there is no mechanical action applied to the wafer surface during process.

[0059] The support plate may be a rigid plate having openings and a surface profile, which will be referred to as a plate hereinbelow. In this embodiment, a surface of the plate includes a protruding profile or region, which may be any curved or protruding surface or surface portion, including but not limited to, spherical, cylindrical, conical, pyramidal, rectangular, trapezoidal, or triangular surfaces. During the process, the plate is placed in a process solution and the solution is flowed through openings of the plate. The solution flowing through the protruding region of the plate conforms to the top surface profile and forms a raised solution surface over the protruding region. When a workpiece is lowered towards the process solution, the workpiece surface first touches the raised surface of the solution which corresponds to the location of the protruding region of the plate. If so configured, the central region of the workpiece may be wetted first by the process solution, and then the solution moves towards the periphery of the wafer, sweeping any bubbles out with it. This prevents bubble entrapment under the workpiece before the rest of the surface of the workpiece is wetted by the solution. This way, since the bubbles are eliminated or swept away from the center, and no bubble entrapment occurs.

[0060] The protruding region may be placed about the center of the plate surface or may extend along the length or width of the plate surface. As the workpiece surface moves towards the surface of the plate, a gap filled with solution is formed between the workpiece surface and the surface of the plate. Peripheral ends of the gap are unblocked so that the solution is moved laterally to the open ends of the gap as the pressure from the moving workpiece surface pushes the solution while the workpiece surface is getting closer to the surface of the plate. At the protruding region, the surface profile of the plate locally narrows the gap and applies more pressure to the adjacent solution. For example if a protrusion on the plate is placed across from the center of the workpiece surface, the gap between the two surfaces, i.e. the wafer surface and the plate surface, will be narrower at this location. Solution between the surface about the center of the wafer and the protruding region on the plate surface will be squeezed more than the solution in the rest of the gap, which will cause solution to flow outwardly into this low pressure zone. This outwardly flow also sweeps away any remaining or forming bubbles with the solution.

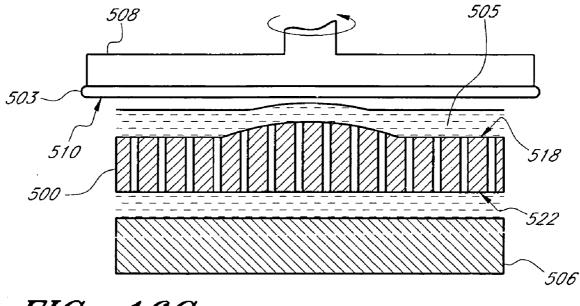

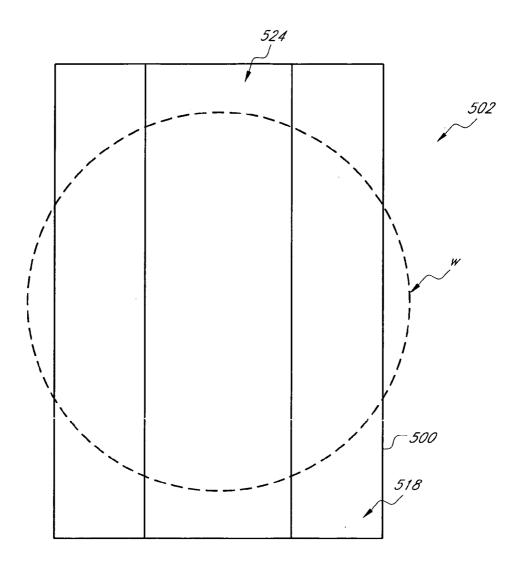

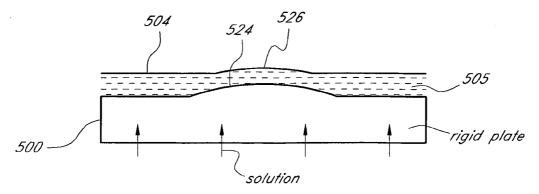

[0061] FIGS. 16A, 16B and 16C illustrate a plate 500 in top view, and in side views of a ECMPR system 502. In FIG. 16A, circle W in dotted lines shows the position of a wafer 503 facing towards the plate 500. Although in this embodiment, the plate 500 has a rectangular shape, it may have any geometrical shape, preferably allowing side electrical contacts to touch the front surface of the wafer 503 (i.e., allowing the wafer W to overhang). Accordingly FIGS. 16B-16C show side views along from the short edge of the plate 500. It should be noted that all dimensions of the plate 500 may be larger than the diameter of the wafer if other means of making electrical contact to the wafer, such as a clamp ring contact, are employed. We will, however continue to refer to the exemplary geometry shown in FIGS. 16A, 16B and 16C. In FIG. 16B, a wafer 503 is above the surface 504 of a process solution 505, and in FIG. 16C the wafer is immersed in the solution 505. As shown in FIGS. 16B and 16C, the plate 500 is placed between the wafer 503 and an electrode 506. A carrier head 508 holds the wafer 503 by its back surface while exposing a front surface 510 of the wafer 503. The carrier head 508 may rotate and move the wafer laterally over the plate 500. As described above, the front surface 510 includes a conductive layer, e.g., a copper seed layer, a barrier layer or a nucleation layer etc., for electrodeposition or a copper layer for electropolishing. The electrode 506 may be an anode for electrodeposition, and may be a cathode if the process is electropolishing. A power supply 512 is electrically connected to the electrode 506 and the front surface 510 to apply a potential difference while the process solution 505 is contacting the electrode 506 and the front surface 510 during the electrochemical process. As shown in FIG. 16B, electrical connection to the front surface 510 is made using movable electrical contacts 516 adjacent and along the long edge of the plate 500.

[0062] During the process, the front surface 510 of the wafer to be processed is placed across from a first surface 518 of the plate 500. Fluid openings 520 between the first surface 518 and the second surface 522 of the plate 500 allow the process solution 505 to flow between the front surface 510 of the wafer 503 and the electrode 506. The openings 520 may be shaped as holes or slits and may have any geometrical shape. The first surface 518 includes a protruding region 524 or a protruding surface or a bump to eliminate bubble entrapment under the front surface 510. The protruding region 524 may be a portion of the first surface or may be the entire first surface. The second surface 522 may be flat as shown in FIG. 16B, but it may also be curved.

[0063] As shown in FIG. 16B, in this embodiment, the protruding region 524 has a spherical surface and is placed at a central location of the first surface 518. As exemplified above, the protruding region of the first surface 518 may be any three dimensional surface. As also shown in FIGS. 17A and 17B, the protruding region 524 may extend along the length of the first surface 518 of the plate 500 and again may have any geometrical surface such as cylindrical, rectangular, etc. Referring back to FIG. 16B, the process solution 505 flowing through the plate 500 forms a raised surface 526 over the protruding region 524 of the plate 500. The raised surface 526 of the process solution 505 is closer to the front surface 510 than the rest of the surface 504 of the process solution 505. Accordingly, as the wafer is lowered towards the process solution 505, the center of the front surface 510 touches the raised surface 526 of the process solution 505 first and gets wet without bubble entrapment, and as the wafer 503 is further advanced towards the process solution 505 the rest of the front surface immerses into the solution without bubble entrapment. FIG. 17B shows the raised surface 526 of the process solution 505 over the protruding region 524 of the plate 500. FIGS. 18A-18F illustrate various first or top surfaces of exemplary plates 500 placed across the wafers **503** to be processed. As shown in **FIGS**. **18A**, **18B**, **18**D and **18**E the first surfaces **518** are shaped to have protruded regions to form the raised solution surfaces over them. In this respect, **FIG**. **18A** shows a cylindrical first surface profile; **FIG**. **18B** shows a triangular first surface profile; **FIG**. **18D** shows a slanted first surface profile; and **FIG**. **18E** shows a curved and slanted first surface profile. However, in **FIGS**. **18C** and **18F** a portion of the first surfaces includes protruded regions, which is triangular in **FIG**. **18C** and rectangular in **FIG**. **18F**.

[0064] FIG. 19 shows an electrochemical processing system 600 employing another embodiment of a rigid plate 602. The rigid plate 602 has a top surface 604, which faces a front surface 606 of a wafer 608, and the rigid plate 502 has a back surface 606. Fluid channels or openings 605 extend between the top surface 604 and the back surface 606 to flow a process solution 610 towards the surface 606 of the wafer 608. Different than the above embodiments, the top surface 604 of the rigid plate 602 is substantially flat and the back surface includes a cavity 612. In the region of the cavity 612, the thickness of the rigid plate 602 is reduced, which is at a minimum at the top of the cavity 612. The cavity 612 helps forming a raised solution surface 614 over the top surface 604 of the plate 602, with the pressure of the process solution 610 filling the cavity 612. The level of the solution above the cavity 612 is higher (highest at the top of the cavity), than its level over the rest of the rigid plate 602, due to the fact that the resistance to fluid flow is the lowest at that location. As a selected portion of the surface of the wafer 608 (e.g. the center of the surface of the wafer) is touched to the raised surface 614, entrapped bubbles are swept away with the solution flowing over the top surface 604 of the rigid plate 602 from the center towards the edge of the wafer. A sequence of touching the surface 606 of the wafer 608 to the raised solution surface 614 and then immersing the surface 606 into the process solution is performed as described above. In the system 600, the rigid plate 602 is positioned between an electrode 616 and the wafer 608. which is moved and rotated by a wafer holder 618 during the process. A power supply 620 applies a potential difference between the surface of the wafer 608 and the electrode 616 for electrochemically processing the surface 606 of the wafer 608. The rigid plate 602 may be rectangular as in the other embodiments. The cavity 612 may be positioned under the center of the wafer or may extend along the long edge of the rigid plate (see also FIGS. 17A-17B). The cavity 612 may be shaped in any 3-D form, such as hemispherical, cylindrical, conical, pyramidal, rectangular.

**[0065]** Although various preferred embodiments and the best mode of the present invention have been described in detail above, those skilled in the art will readily appreciate that many modifications of the exemplary embodiment are possible without materially departing from the novel teachings and advantages of this invention.

What is claimed is:

**1**. A method of immersing a surface of a wafer in a solution for processing the surface, comprising:

flowing the solution through openings of a rigid plate having a protruding region to form a raised solution surface over the protruding region; immersing the wafer surface fully into the solution.

**2**. The method of claim 1, further comprising rotating the wafer before contacting.

**3**. The method of claim 1, wherein the selected portion of the surface is a center of the surface of the wafer.

**4**. The method of claim 1, further comprising placing the rigid plate into the solution.

**5**. The method of claim 1, further comprising processing the surface of the wafer.

**6**. A system for eliminating bubble entrapment under a surface of a wafer when the surface is immersed into a process solution to process the surface of the wafer, comprising:

- a rigid plate, having a protruded region and fluid openings, wherein the plate is configured such that as the solution flows through the rigid plate, a raised solution surface forms over the protruded region; and

- a moving mechanism configured to move the wafer, wherein as the wafer is moved towards the solution, a selected portion of the surface of the wafer contacts the raised solution surface before immersing the surface fully into the solution.

7. The system of claim 6, wherein the protruded region forms a portion of a top surface of the rigid plate.

**8**. The system of claim 6, wherein the protruded region forms a top surface of the rigid plate.

**9**. The system of claim 6, further including an electrode placed in the process solution.

**10**. The system of claim 9, further including a power supply connected to the electrode and the surface of the wafer to apply a potential difference between the surface of the wafer and the electrode to process the surface.

**11**. The system of claim 9, wherein the rigid plate is placed between the electrode and the surface of the wafer.

**12**. The system of claim 6, wherein the rigid plate has a rectangular shape.

**13**. The system of claim 6, wherein the selected portion of the surface is a center of the surface of the wafer.

**14**. A method of processing a conductive surface of a wafer using a process solution, comprising:

- flowing the solution through openings of a plate having a protruding region to form a raised solution surface over the protruding region;

- contacting a selected portion of the conductive surface with the raised solution surface;

immersing the conductive surface fully into the solution; and

processing the conductive surface.

**15**. The method of claim 14, further comprising applying a potential difference between the conductive surface and an electrode.

**16**. The method of claim 15, wherein processing is electropolishing.

**17**. The method of claim 15, wherein processing is electrodeposition.

**18**. The method of claim 14, further comprising rotating the conductive surface before the step of contacting.

**19**. The method of claim 14, wherein the selected portion of the conductive surface is a center of the conductive surface of the wafer.

20. The method of claim 14, wherein the plate is rigid.

**21**. A system for electroprocessing a conductive surface of a wafer using a process solution, comprising:

- an electrode configured to be placed in the process solution;

- a rigid plate, having a protruded region and fluid openings, configured to be immersed in the solution and positioned between the electrode and the conductive surface, wherein the rigid plate is configured such that as the solution flows through the rigid plate, a raised solution surface forms over the protruded region; and

- a moving mechanism configured to move the wafer, wherein as the wafer is moved towards the solution, a selected portion of the conductive surface contacts the raised solution surface before immersing the surface fully into the solution.

**22**. The system of claim 21, wherein the rigid plate is placed between the electrode and the conductive surface of the wafer.

**23**. The system of claim 21, wherein the rigid plate has a rectangular shape.

**24**. The system of claim 21, wherein the selected portion of the conductive surface is s center of the conductive surface of the wafer.

**25**. The system of claim 21, wherein the protruded region forms a portion of a top surface of the rigid plate.

**26**. The system of claim 21, wherein the protruded region forms a top surface of the rigid plate.

**27**. The system of claim 21, further including a power supply connected to the electrode and the surface of the wafer to apply a potential difference between the conductive surface of the wafer and the electrode to process the conductive surface of the wafer.

\* \* \* \* \*