(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년05월24일

(11) 등록번호 10-1266335

(24) 등록일자 2013년05월15일

- (51) 국제특허분류(Int. Cl.)

*H01L 21/60* (2006.01) *H01L 23/48* (2006.01)

*H01L 23/485* (2006.01)

- (21) 출원번호 10-2007-7019305

- (22) 출원일자(국제) 2006년02월24일

심사청구일자 2011년02월24일

- (85) 번역문제출일자 2007년08월23일

- (65) 공개번호 10-2007-0104919

- (43) 공개일자 2007년10월29일

- (86) 국제출원번호 PCT/US2006/006673

- (87) 국제공개번호 WO 2006/091856

국제공개일자 2006년08월31일

- (30) 우선권주장

60/655,816 2005년02월24일 미국(US)

- (56) 선행기술조사문헌

US06462426 B1\*

US06596619 B1\*

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

에이제 시스템즈 엘엘시

미합중국 펜실베니아 18109 알렌타운 노스이스트

아메리칸 파크웨이 1110

- (72) 발명자

바흐만, 마크, 아담

미국 펜실베니아 19608 싱킹 스프링, 에스더 서

클 3

- 비팅, 도널드, 스템판

미국 펜실베니아 19608 싱킹 스프링, 파이우드 에

비뉴 57

(뒷면에 계속)

- (74) 대리인

장훈

전체 청구항 수 : 총 17 항

심사관 : 이명진

(54) 발명의 명칭 플립 칩 장치를 제조하기 위한 구조 및 방법

### (57) 요 약

본원 발명은 땜납 범프 구조 및 언더범프 금속(under-bump metallurgical) 구조에 관한 것이다. 반도체 기판의 상부 표면은 그것 상에 배치된 제1 도전성 패드(200)를 포함한다. 패시베이션 층(202)은 상부 표면 위에 놓인다. 제2 도전성 패드(212)는 패시베이션 층 내의 개구(204)에 제1 도전성 패드에 접하여 배치된다. 언더범프 금속 구조(300)는 제2 도전성 패드를 캡슐화하여 제2 도전성 패드의 측벽 표면 및 상부 표면을 덮고 주변환경 및 공정 영향으로부터 제1 및 제2 도전성 패드를 보호한다. 본 발명에 따라, 종래의 제2 패시베이션 층은 불필요하다. 다양한 구조를 형성하기 위한 방법이 또한 제공된다.

### 대 표 도

(72) 발명자

체셔, 다니엘, 패트릭

미국 플로리다 34787, 원터 가든, 원더미어 푸앙트

드라이브 2018

국, 태호

미국 플로리다 32836, 올랜도, 위크햄 웨이 9253

---

머천트, 사일레쉬, 만신

미국 펜실베니아 18062, 마운지, 문빔 레인 7156

## 특허청구의 범위

### 청구항 1

반도체 기판에 형성된 트렌치에, 노출된 상부 표면을 갖는 제1 도전성 패드를 형성하는 단계;

상기 상부 표면 위에 패시베이션 층(passivation layer)을 형성하는 단계;

상기 제1 도전성 패드의 상부 표면을 노출시키기 위해 상기 패시베이션 층에 개구를 형성하는 단계;

상기 개구를 통해 상기 제1 도전성 패드의 상기 상부 표면에 접하여 제2 도전성 패드를 형성하고, 상기 개구에 인접한 패시베이션 층의 영역들에 확장시키는 단계;

상기 제2 도전성 패드의 노출된 표면들 상에 언더 bump 금속(under-bump metallurgical) 구조를 형성하는 단계로서, 상기 언더 bump 금속 구조는 상기 제2 도전성 패드의 노출된 측벽 표면들 및 노출된 상부 표면상에 형성되는, 상기 언더 bump 금속 구조를 형성하는 단계; 및

상기 언더 bump 금속 구조의 상부 표면 상에 땜납 범프를 형성하는 단계를 포함하는, 땜납 범프를 형성하는 방법.

### 청구항 2

제1항에 있어서,

상기 언더 bump 금속 구조를 형성하는 단계는 상기 언더 bump 금속 구조 내에 상기 제2 도전성 패드를 캡슐화하는 단계를 더 포함하는, 땜납 범프를 형성하는 방법.

### 청구항 3

삭제

### 청구항 4

제1항에 있어서,

상기 제1 도전성 패드를 형성하는 단계는 구리 패드를 형성하는 단계를 포함하는, 땜납 범프를 형성하는 방법.

### 청구항 5

제1항에 있어서,

상기 제2 도전성 패드를 형성하는 단계는 알루미늄 패드를 형성하는 단계를 포함하는, 땜납 범프를 형성하는 방법.

### 청구항 6

제1항에 있어서,

상기 반도체 기판은 상기 제1 도전성 패드 밑에 있는 상호접속 구조들을 포함하고, 상기 제1 도전성 패드는 상기 상호접속 구조들 중 적어도 하나와 도전적으로 연통하는, 땜납 범프를 형성하는 방법.

### 청구항 7

제1항에 있어서,

상기 땜납 범프는 상기 기판 내의 도전성 영역들과 접적 회로 패키지, 전자 부품 어셈블리 보드 또는 수신 기판 사이의 전기 접속을 제공하는, 땜납 범프를 형성하는 방법.

### 청구항 8

제1항에 있어서,

상기 제1 도전성 패드의 재료는 상기 제2 도전성 패드의 재료와 상이한, 땜납 범프를 형성하는 방법.

#### 청구항 9

기판의 상부 표면에 형성된 트렌치에 배치된 본드 패드들 및 패시베이션 층을 갖는 접적 회로를 제공하는 단계로서, 각각의 본드 패드는 상기 패시베이션 층 내의 개구를 통해 노출되는, 상기 접적 회로를 제공하는 단계;

상기 개구를 통해 상기 본드 패드의 상기 상부 표면에 접하여 도전성 패드를 형성하는 단계로서, 상기 도전성 패드는 상기 개구에 인접한 상기 패시베이션 층의 영역들로 확장되는, 상기 도전성 패드를 형성하는 단계;

상기 도전성 패드의 노출된 표면들 상에 언더범프 금속 구조를 형성하는 단계로서, 상기 언더범프 금속 구조는 상기 도전성 패드의 노출된 측벽 표면들 및 노출된 상부 표면상에 형성되는, 상기 언더범프 금속 구조를 형성하는 단계; 및

상기 언더범프 금속 층의 상부 표면 상에 땜납 범프를 형성하는 단계를 포함하는, 반도체 장치를 제조하는 방법.

#### 청구항 10

제9항에 있어서,

상기 본드 패드를 형성하는 단계는 구리 본드 패드를 형성하는 단계를 포함하는, 반도체 장치를 제조하는 방법.

#### 청구항 11

제9항에 있어서,

상기 도전성 패드를 형성하는 단계는 알루미늄 도전성 패드를 형성하는 단계를 포함하는, 반도체 장치를 제조하는 방법.

#### 청구항 12

삭제

#### 청구항 13

제9항에 있어서,

상기 땜납 범프는 상기 기판 내의 도전성 영역들과 접적 회로 패키지, 전자 부품 어셈블리 보드 또는 수신 기판 사이의 전기 접속을 제공하는, 반도체 장치를 제조하는 방법.

#### 청구항 14

반도체 기판;

상기 기판의 형성된 트렌치에 배치되고, 노출된 상부 표면을 갖는 제1 도전성 영역;

상기 제1 도전성 영역 위에 놓이고, 상기 제1 도전성 영역의 일부를 노출시키기 위해 상기 제1 도전성 영역에 규정된 개구를 갖는 패시베이션 층;

상기 개구 내의, 상기 제1 도전성 영역에 접하는 제2 도전성 영역;

상기 제2 도전성 영역의 노출된 표면들 상에 배치된 단일 마스킹 단계에서 형성된 언더범프 금속 구조로서, 상기 제2 도전성 영역의 측벽 표면들 및 상부 표면에 놓여지는, 상기 언더범프 금속 구조; 및

상기 언더범프 금속 구조 위에 놓인 땜납 범프를 포함하는, 땜납 범프 구조.

#### 청구항 15

제14항에 있어서,

상기 제1 도전성 구조는 접적 회로용 본드 패드를 포함하고, 상기 기판은 도핑된 반도체 영역들 및 상호접속 구조들을 포함하고, 상기 본드 패드는 상호접속 구조와 도전적으로 연통하는, 땜납 범프 구조.

**청구항 16**

제14항에 있어서,

상기 제2 도전성 영역은 상기 개구의 주변에 인접한 상기 패시베이션 층의 영역 위에 놓인, 땜납 범프 구조.

**청구항 17**

삭제

**청구항 18**

제14항에 있어서,

상기 제1 도전성 영역의 재료는 구리를 포함하고, 상기 제2 도전성 영역의 재료는 알루미늄을 포함하는, 땜납 범프 구조.

**청구항 19**

제14항에 있어서,

상기 땜납 범프는 광 상호접속 시스템에서 전기 상호접속을 제공하는, 땜납 범프 구조.

**청구항 20**

제14항에 있어서,

패키지를 더 포함하고,

상기 땜납 범프는 상기 기판 내의 도전성 영역들과 상기 패키지 외부에 배치된 도전성 소자들 사이의 전기 접속을 제공하는, 땜납 범프 구조.

**명세서****기술 분야**

[0001] 본 발명은 일반적으로 집적 회로 및 보다 구체적으로 플립 칩 패키지 접속 구조 및 플립 칩 패키지 접속을 형성하기 위한 방법에 관한 것이다.

**배경기술**

[0002] 집적 회로는 반도체 기판 및 기판 내의 도핑된 영역으로부터 형성된 트랜지스터와 같은 반도체 장치를 포함한다. 기판 위에 놓인 대안적인 도전성 및 유전체 층들을 포함하는 상호접속 시스템은 도핑된 영역에 전기적으로 접속하여 전기 회로를 형성한다.

[0003] 도전성 층은 금속 퇴적 및 감산 에칭(subtractive etch process)에 따라 형성된 도전성 트레이스 또는 다마신 공정(damascene process)에 따라 홈에 형성된 도전성 러너(conductive runner)를 포함한다. 실질적으로 유전체 층 내의 수직 도전성 플러그 또는 비아(via)는 위에 놓이고 밑에 있는(underlying) 도전성 트레이스 및 러너에 접속하고, 기판 내의 도핑된 영역에의 접속을 포함한다. 도전성 비아 및 도전성 라인은 금속 퇴적, 포토리소그래픽 마스킹(photolithographic masking), 패터닝, 및 감산 에칭을 포함하는 종래 제조 기술을 사용하여 형성된다.

[0004] 제조 및 금속화 (상호접속 시스템의 제조) 이후, 집적 회로는 전형적으로 패키지의 외부 도전성 소자를 회로 보드 상의 도전성 트레이스에 도전적으로 부착시킴으로써 패키징된 칩을 전자 장치 내의 전자 부품에 접속시키기 위한 리드, 펀 또는 볼과 같은 복수의 외부 도전성 소자를 포함하는 패키지에 포함된다.

[0005] 집적 회로를 패키지의 도전성 소자에 접속시키기 위해, 집적 회로의 최상위 표면(본드 패드 층으로 언급됨)은 본드 패드를 패키지의 외부 도전성 소자에 접속시키는 도전성 소자(예를 들어, 본드 와이어, 땜납 범프(solder bump) 또는 땜납 볼)에 부착된 복수의 도전성 본드 패드를 포함한다. 알루미늄-기반 상호접속 시스템에서, 최상위 퇴적 알루미늄 층이 마스킹, 패터닝 및 에칭되어 알루미늄 본드 패드를 형성한다. 밑에 있는 도전성 플러그는 집적 회로의 전기 회로에 본드 패드를 접속시킨다.

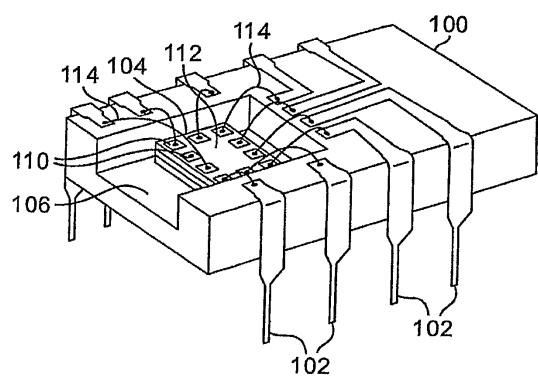

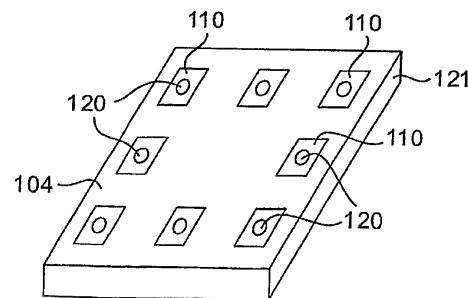

- [0006] 도 6은 외부 패키지 리드(102)를 포함하는 집적 회로 듀얼-인-라인(dual-in-line) 패키지(100)를 나타낸다. 집적 회로(104)는 다이 부착 영역(106)에 부착된다. 집적 회로(104)의 상부 표면(112) 상의 본드 패드(110)(일 실시예 내에서 알루미늄으로부터 형성됨)는 통상 금(또는 금 합금) 본드 와이어(114)에 의해 패키지 리드(102)에 접속된다. 일반적으로, 본드 패드(110)의 길이 및 폭 각각은 대략 40-80 미크론 및 50-150 미크론 사이에서 가변적이다. 본드 패드(110)를 패키지 리드(102)에 전기적으로 접속시키는 공정은 와이어 본딩이라 언급된다.

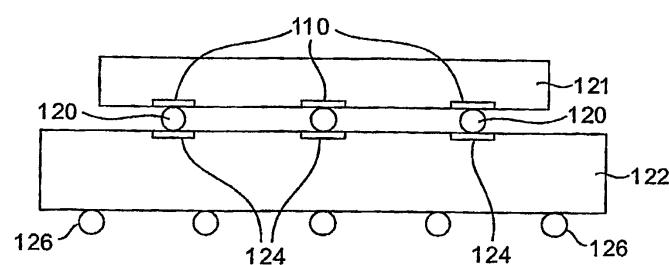

- [0007] 플립 칩 또는 범프 본딩으로 언급되는 또 다른 알려진 패키지 구조에서, 상호접속 본드 와이어는 집적 회로(121)의 본드 패드(110) 상에 형성된 퇴적된 땜납 범프(120)로 대체된다. 도 7을 보자. 도 8의 패키지(122)에 플립 칩 어셈블리를 전기 접속하는 것은 집적 회로(121)를 전도시켜(inverting) 범프(120)를 패키지(122) 상의 수신 패드(124)에 땜납함으로써 이루어진다. 수신 패드(124)는 도 8에 나타내지 않은 내부 도전성 구조를 통해 대응하는 외부 패키지 도전성 소자와 도전적으로 연통한다. 도 8의 예에서, 외부 패키지 도전성 소자는 볼들(126) 어레이를 포함하는데, 이는 패키징된 집적 회로(121)를 전자 장치에 전기적으로 접속시키기 위한 볼 그리드 어레이(ball grid array)를 형성한다. 대안적으로, 패키지는 도 6의 핀(102)과 같은 외부 핀, 또는 집적 회로(121)를 전자 장치에 접속시키기 위한 다른 기술들을 포함한다.

- [0008] 알루미늄 상호접속 시스템 및 알루미늄 본드 패드(110)와 함께 형성된 집적 회로는 도 6에 나타낸 와이어 본드 공정, 또는 도 7 및 8에 나타낸 플립 칩 및 범프 본드 공정을 사용하여 패키징될 수 있다.

- [0009] 집적 회로 장치 및 상호접속 시스템이 크기가 작아지고 고주파수 아날로그 신호 및 보다 높은 데이터-율 디지털 신호를 전달하도록 만들어지면서, 알루미늄 상호접속 구조는 칩에 수용불가능한 신호 전파 지연을 줄 수 있다. 또한, 비아 개구가 계속 줄어들면서, 보다 작은 개구에 도전성 물질을 퇴적하여 도전성 플러그를 형성하는 것이 점차 힘들어졌다.

- [0010] 알루미늄 상호접속 구조의 이들 알려진 단점이 주어지면, 구리(및 그들의 합금)가 상호접속 물질로 선택된다. 구리는 알루미늄보다 양호한 도전체이고(저항력이 2.7 내지 3.1 micro-ohms-cm인 알루미늄에 비해 1.7 내지 2.0 micro-ohms-cm임), 전자이동(알루미늄 상호접속 라인을 통한 전류 흐름에 의해 형성된 전계 및 열 증감에 의해 알루미늄 상호접속 라인이 얇아지고 결국 분리될 수 있는 현상)에 영향을 덜 받고, 보다 작은 개구에서 보다 낮은 온도에서 퇴적될 수 있다(이에 따라 집적 회로의 다른 소자들 상에서의 해로운 영향을 피할 수 있음). 구리의 저항이 보다 낮으면 상호접속 구조에서의 신호 전파 시간이 준다.

- [0011] 구리 상호접속 구조를 형성하기 위한 바람직한 기술인 다마신 공정은 구리 상호접속 구조의 각 층의 도전성 수직 비아 및 도전성 수평부를 반드시 형성한다. 다이신 공정은 유전체 층 내에 위에 놓인 수평 홈이 뒤따르는 수직 비아 개구를 형성한다. 금속 퇴적 단계는 비아와 홈을 동시에 채워, 실질적으로 수직인 도전성 비아 및 실질적으로 수평인 도전성 러너를 포함하는 완벽한 금속 상호접속 층을 형성한다. 화학/금속-폴리싱(polishing) 단계는 구리 퇴적 동안 표면 상에 형성된 구리 퇴적물을 제거함으로써 유전체 표면을 평탄화시킨다.

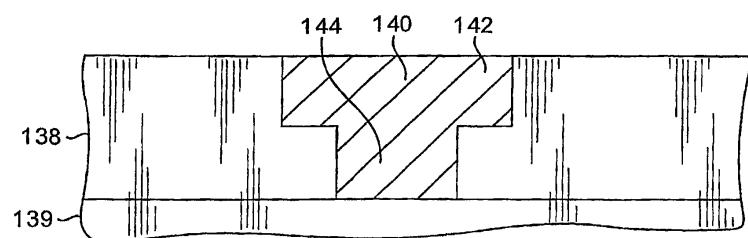

- [0012] 완성된 종래 기술 다마신 구조의 예가 도 9의 단면도에 나타나있는데, 이는 보다 낮은 레벨의 상호접속 구조(139) 상에 퇴적 또는 형성된 유전체 층(138)을 포함한다. 유전체 층(138)에 형성된 개구는 구리와 같은 적절한 도전성 물질(140)로 치워져 보다 낮은 레벨의 상호접속 구조(139)와 접하는 도전성 홈(142) 및 도전성 비아(144)를 형성한다. 본 기술에 잘 알려진 바와 같이, 다마신 공정을 사용하여 도전성 상호접속 시스템을 형성할 때는, 구리 본드 패드가 집적 회로의 최상위 금속화 층에 형성된다.

- [0013] 범프가 도 6의 본드 패드(110)보다 고밀도로 집적 회로(영역-어레이 범프 구성이라 언급된)의 전면 위에 형성될 수 있으면서, 플립 칩 기술은 다수의 입력/출력 단자를 갖는 장치들에 대해서 점차 인기가 높아졌다. 영역-어레이 범프 구성은 와이어 본딩에 상당한 장점을 제공하고, 전형적으로 칩 성능 및/또는 형성 요소가 모든 다른 고려사항들보다 중요한 경우에 사용된다. 주변-어레이 범프 구성(선형 또는 엇갈린 정렬의 1개 또는 2개의 범프 열이 집적 회로의 주변에 근접하게 배치됨)은 보다 짧은 상호접속 거리를 제공하여 보다 짧은 전송 지연 시간을 제공한다.

- [0014] 와이어 본드를 구리 본드 패드에 직접 공급하고자하는 시도가 이루어졌지만, 구리 표면이 쉽게 산화되고 이에 따라 종래 프로브(probe) 기술을 사용하여 프로브하기가 난해하기 때문에, 이들 기술은 상업적인 제조 공정에서 광범위하게 사용되지 않는다. 플립-칩 땜납 범프 방법은 구리 본드 패드와의 사용에 보다 적용가능하다. 범프는 프로브된 범프 및 구리 상에 형성될 수 있지만, 공정-내 프로빙(in-process probing)은 여전히 문제가 있다. 반대로, 알루미늄 패드는 공정-내 및 웨이퍼 프로빙에 잘 알려진 전기 접촉 패드를 제공한다.

- [0015] 플립 칩 기술은 추가적인 공정 단계들을 요구하기 때문에 종래 와이어 본딩 기술에 비해 고가이다. 본딩 패드와 땜납 범프에 대한 중간물을 요구하는 언더 bump 금속 층(under-bump metallurgical layer)을 제조하기 위해 2개 이상의 추가적인 금속 층 퇴적 및 적어도 동일한 개수의 마스크 레벨 및 에칭 단계들이 필요하다.

- [0016] 종래 플립 칩 제조 공정은 또한 집적 회로의 상부 표면 상에 듀얼 패시베이션 층 스택(dual passivation layer stack)(각각의 층은 상이한 유전체 물질의 서브-층을 포함할 수 있음)을 형성한다. 각각의 패시베이션 층은 다층 유전체 퇴적 단계(하나 이상의 클러스터 틀로 수행될 수 있음)에 따라 제조되며, 패터닝, 리소그래픽(lithographic), 에칭, 및 사후-에칭 단계들이 뒤따른다. 반도체 제조업자는 공정 비용을 줄이도록 마스킹 및 에칭 단계를 제한하고자 한다.

- [0017] 제1 패시베이션 층(종종 웨이퍼 패시베이션 층으로 언급됨)은 그것에 퇴적된 상부 또는 마지막 구리 금속 상호 접속 층 및 구리 패드를 보호한다. 제2 패시베이션 층(마지막 패시베이션 층으로 언급됨)은 구리 패드 위에 형성된 알루미늄 패드를 보호한다.

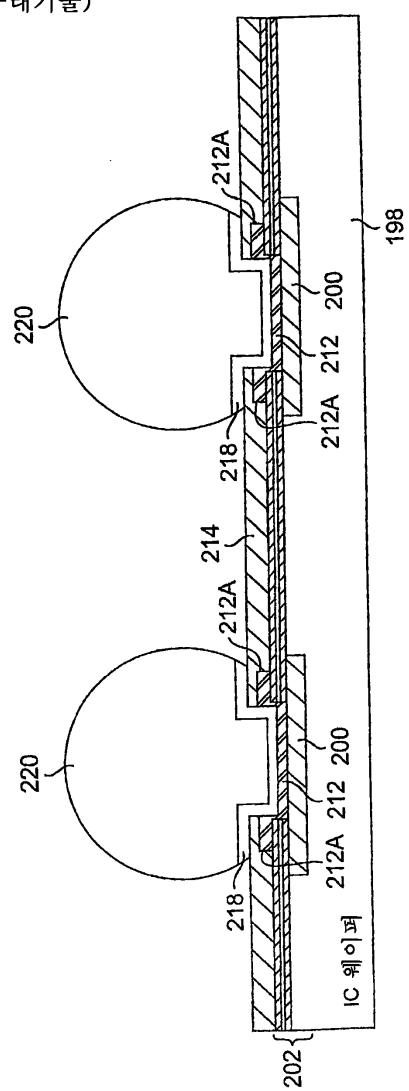

- [0018] 도 10은 종래 기술 공정에 따른 구리-기반 상호접속 구조에 대한 플립 칩 구조 또는 땜납 범프의 마지막 어셈블리를 나타낸다. 기판(198)은 도핑된 영역이 형성된 반도체 물질 위에 놓인 구리 상호접속 및 유전체 물질의 다수의 대안 층을 포함한다. 구리 본드 패드(200)가, 기판(198) 내의 상호접속 구조(및 이에 따라 기판(198) 내의 전기 회로)를 도 6의 패키지(100)의 패키지 리드(102)에 또는 도 8의 패키지(122)의 볼(126)에 접속시키기 위한 다마신 공정(damascence process)에 따라 기판(198) 내의 홈 또는 개구에 형성된다.

- [0019] 웨이퍼 패시베이션 스택(202)(전형적으로 예를 들어 이산화규소, 질화규소, 탄화규소 또는 그들의 혼합물을 포함하는 유전체 물질 층의 스택)이 본드 패드(200) 위에 퇴적되고 선택적으로 에칭되어 구리 본드 패드(200)의 영역을 노출시키는 개구가 형성된다. 알루미늄 패드 및 캡(212)이 개구에 퇴적된다.

- [0020] 예를 들어 탄화규소, 질화규소, 이산화규소 또는 그들의 혼합물을 포함하는 마지막 패시베이션 층(214)(전형적으로 도 10에 도시되지 않은 구성 층을 갖는 다층 스택)이 퇴적되고 선택적으로 에칭되어 밑에 있는 알루미늄 패드(212)를 노출시키는 개구가 형성된다. 언더 bump 금속 층(또는 층들)이 퇴적되고 선택적으로 에칭되어, 알루미늄 패드(212) 위에 놓여 접하고 마지막 패시베이션 층(214)의 영역 위에 놓인 언더 bump 금속 구조(218)가 형성된다. 땜납 범프(220)가 언더 bump 금속 구조(218) 위에 형성되어 플립-칩 상호접속이 형성된다.

- [0021] 알루미늄 캡(212) 위에 퇴적된 마지막 패시베이션 층(214)에 대해서, 언더 bump 금속 구조(218) 및 땜납 범프(220)를 수용하기 위해 층(214)에 개구를 위치시키고 형성할 때, 특정한 구조 포지션 관리요소가 고려되어야 한다. 전형적으로 이 개구(최대 크기가 약 70-80 미크론임)는 알루미늄 패드(212)(최대 크기가 약 100 미크론 이상임)보다 작아 패드(212)에 관련하여 적절하게 위치되어야만 한다. 언더 bump 금속 구조(218)는 전형적으로 알루미늄 패드(212)보다 작다. 이들 크기의 다양성은 적절하게 관리되고 포지션 내구성이 확립되어 땜납 범프(220)가 궁극적으로 구리 패드(200)에 도전적으로 접속된다.

- [0022] 도 10에 나타낸 바와 같이, 마지막 패시베이션 층(214)이 알루미늄 패드(212)의 에지(212A) 위에 확장되는 것이 또한 바람직하다. 예를 들어, 패시베이션 층(214) 내의 개구는 전형적으로 알루미늄 패드(212)보다 몇 미크론(일 예에서 약 4 미크론) 작아, 패시베이션 층 물질이 에지(212A)를 덮어 보호하고 산화와 같은 외부 영향으로부터 알루미늄 패드(212)를 보호하는 것을 허용한다. 패시베이션 층 개구가 줄어들어 위에 놓인 영역이 증가함에 따라, 패시베이션 층(214)에 의해 제공되는 보호가 향상된다(그리고 전자이동에 대한 저항이 낮아질 수 있음).

- [0023] 땜납 범프(220)가 도 6의 본드 와이어(114)보다 넓은 본딩 영역을 요구하기 때문에, 플립 칩 상호접속에 사용된 알루미늄 패드(212)는 도 6의 종래 본드 패드(110)보다 커야하며, 이에 따라 마지막 패시베이션 층(214) 내의 개구도 또한 크게 만들어지도록 요구된다. 이들 크기를 크게 할 때, 알루미늄 패드(212)와 마지막 패시베이션 층 개구 사이의 관계는 알루미늄 패드(212)를 보호하도록 유지되어야만 한다. 본 발명은 이러한 보호를 제공하기 위한 방법 및 구조를 교시한다.

### 발명의 상세한 설명

- [0024] 일 실시예에 따라, 본 발명은 땜납 범프를 형성하기 위한 방법을 포함한다. 이 방법은 반도체 기판의 상부 표면에 제1 도전성 패드를 형성하는 단계, 상부 표면 위에 패시베이션 층을 형성하는 단계, 제1 도전성 패드의 상부 표면을 노출시키도록 패시베이션 층에 개구를 형성하는 단계, 제1 도전성 패드의 상부 표면에 접하여 개구를 통해 제2 도전성 패드를 형성하고 패시베이션 층의 인접 영역으로 확장시키는 단계, 제2 도전성 패드의 노출된

표면 상에 언더베프 금속 구조를 형성하는 단계 및 언더베프 금속 구조의 상부 표면 상에 땜납 범프를 형성하는 단계를 더 포함한다.

[0025] 다른 실시예에 따라, 땜납 범프 구조는 반도체 기판, 기판의 상부 표면에 퇴적되는 제1 도전성 영역, 제1 도전성 영역 위에 놓이고 제1 도전성 영역의 일부를 노출시키기 위한 제1 도전성 영역에 규정된 개구를 갖는 패시베이션 층, 및 개구 내의 제1 도전성 영역에 접한 제2 도전성 영역, 제2 도전성 영역의 노출된 표면 상에 퇴적된 언더베프 금속 구조 및 언더베프 금속 구조 위에 놓인 땜납 범프를 포함한다.

## 실시예

[0033] 본 발명의 교시에 따른, 땜납 범프 또는 플립 칩을 형성하기 위한 예시적인 공정들 및 땜납 범프 또는 플립 칩 구조들을 상세하게 설명하기 전에, 본 발명은 주로 소자 및 공정 단계들의 새로운 및 전에 없는 조합물에 속한다는 것이 관찰된다. 당업자에게 쉽게 자명해질 세부 내용으로 본 발명의 공개되는 내용을 모호하게 하지 않기 위해, 어떤 인습적인 소자 및 단계들은 보다 덜 상세하게 제시한, 반면 도면 및 명세에서 본 발명을 이해하는데 적절한 다른 소자 및 단계들을 더욱 상세하게 설명했다.

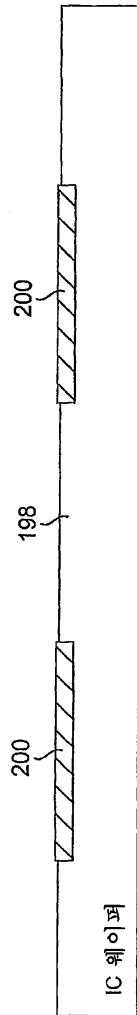

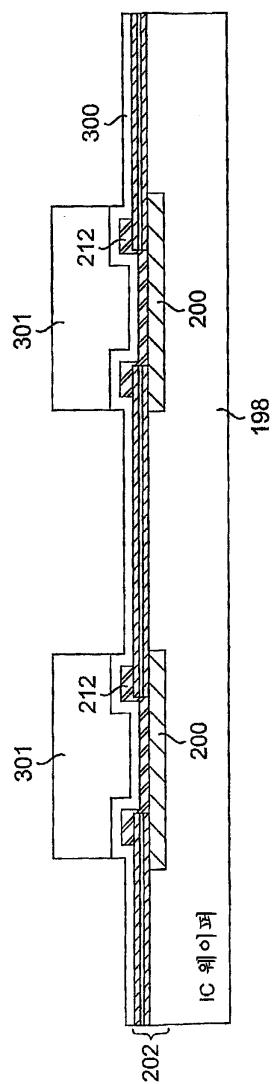

[0034] 도 1에 나타낸 바와 같이, 구리 본드 패드(200)가, 기판(198)에 배치된 접적 회로 장치와 도 6의 패키지(100)의 외부 패키지 리드(102) 또는 도 8의 패키지(122)의 볼(126)들의 어레이와 같은 패키지의 도전성 외부 단자들 사이의 상호접속을 제공하기 위한 기판(198)의 홈 또는 개구에 형성된다. 본드 패드(200)는 기판(198) 내의 비아 개구 및/또는 홈에, 알려진 다마신 또는 듀얼 다마신 기술에 따라 형성될 수 있다. 전형적으로 본드 패드(200)는 기판 홈에 구리를 전착함으로써 형성되며, 여기서 기판은 예를 들어 이산화규소-기반 물질, 유기-규산염 물질, 규산염, 플루오르-기반 유전체, 크세로겔(xerogel), 에어로겔(aerogel), 스판-온 유전체(spin-on dielectrics) 등의 저유전율 물질, 및 그들의 화합물을 또는 다층을 포함한다.

[0035] 도 2에 나타낸 바와 같이, 웨이퍼 패시베이션 스택(202)(전형적으로, 예를 들어 이산화규소, 질화규소, 탄화규소 또는 그들의 화합물을 포함하는 하나 이상의 유전체 물질 층을 포함함)이 본드 패드(200) 위에 형성된다. 포토레지스트 층(photoresist layer)(도 2에 도시되지 않음)이 퇴적되고 마스킹되고 현상되어 포토레지스트 층에 개구가 형성된다. 그 후 패터닝된 포토레지스트 층에 따라 패시베이션 스택(202)에 개구(204)가 형성된다. 일 실시예에서, 3개 층의 스택(202)은 이산화규소 물질 층, 및 위에 놓이고 밑에 깔린 질화규소 층을 포함한다. 다른 실시예에 따라서는, 웨이퍼 패시베이션 스택이 질화규소, 이산화규소, 탄화규소 및 그들의 화합물을 포함하는 3개보다 많은 또는 적은 물질 층을 포함한다.

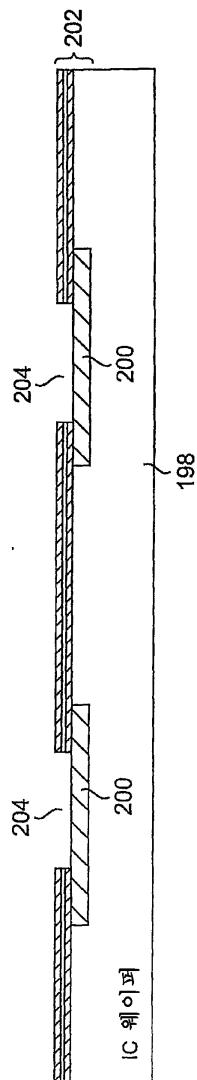

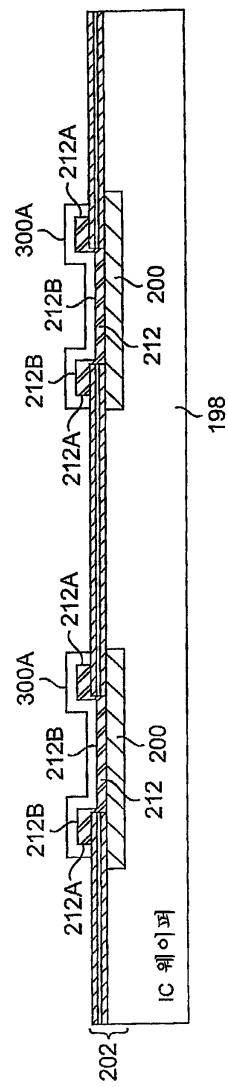

[0036] 알루미늄 층은 퇴적되고 도시되지 않은 마스크 패턴에 따라 에칭되어, 도 3에 나타낸 바와 같은 알루미늄 패드 또는 알루미늄 캡(212)을 형성한다. 본드 패드(200)와 알루미늄 패드(212) 사이의 계면에서, 하나의 물질의 금속 원소가 다른 물질로 확산되어 금속간화합물이 형성된다. 이러한 금속간화합물은 부서지기 쉽고 크래킹에 영향을 받기 쉬워, 계면 도전성의 불규칙을 야기하고 장치 성능을 낮춘다. 금속간 층의 형성을 피하기 위해, 도전성 배리어 층(도 3에 도시되지 않음)이 알루미늄 패드(212)와 구리 본드 패드(200) 사이에 형성된다. 도전성 배리어 층을 포함하는 예시적인 물질은 탄탈, 질화탄탈 및 질화티타늄을 포함한다.

[0037] 종래 기술에 따라, 제조 공정 내의 이 단계에서, 도 10의 마지막 패시베이션 층(214)이 형성되고 패터닝되어(포토리소그래픽 마스킹 기술을 사용함), 도 10의 언더베프 금속 물질(218)을 수용하기 위한 개구들이 규정된다. 마지막 패시베이션 층(214)의 형성 및 패터닝은 몇몇의 공정 단계들 및 적어도 하나의 마스크 층을 필요로 한다.

[0038] 본 발명에 따라, 도 3에 나타낸 바와 같이, 언더베프 금속 구조(300)(전형적으로 다층 구조이지만 도 3에는 개별 층들이 나타나지 않음)가 알루미늄 패드(212)를 포함하여 기판(198) 위에 블랭킷 퇴적된다(blanket deposit). 언더베프 금속 구조(300)의 상부 물질 층은 향후-형성되는 땜납 범프(220)의 보다 양호한 본딩 및 습윤(wetting)을 허용하여 기계적 무결성과 기계 및 열 스트레스 하에서의 수용가능한 신뢰성을 갖춘 접착 본드를 형성하게 한다. 언더베프 금속 구조(300)의 보다 낮은 물질 층은 알루미늄 패드(212)에 대한 양호한 접착력을 제공한다. 중간 층이 배리어로서 동작하여 위에 놓이고 밑에 있는 물질 층의 금속간화합물의 형성을 줄인다. 언더베프 금속 구조는 또한 향후

[0039] -형성되는 땜납 범프(220)의 크기를 규정한다.

[0040] 바람직한 실시예에 따라, 언더베프 금속 구조는 하부 알루미늄 층, 중간 니켈-바나듐 층 및 상부 구리 층을 포함하고 약 1.5 미크론의 두께를 갖는 3-층 구조이다. 언더베프 금속 구조의 다른 실시예는 크롬, 티타늄, 텉스

텐, 니켈, 탄탈, 내화 물질, 몰리브덴 및 이들 물질의 화합물을 포함할 수 있다.

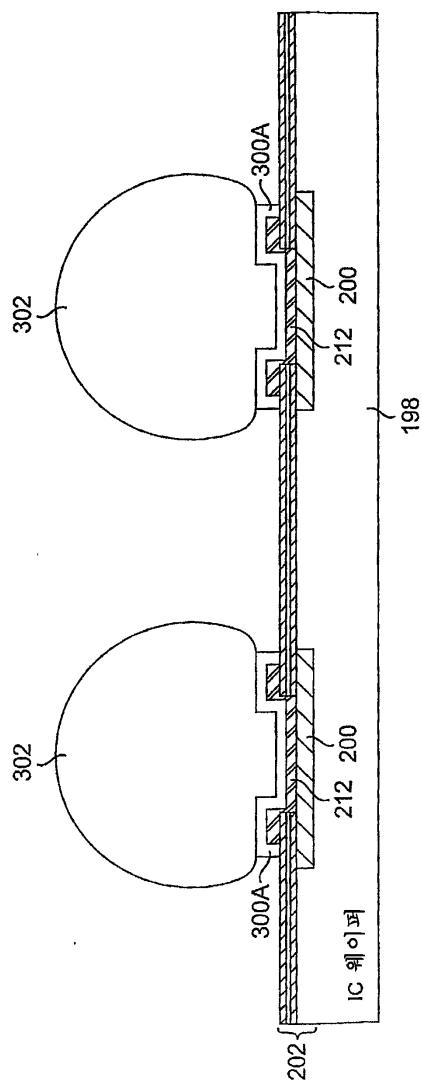

- [0041] 포토레지스트 층이 퇴적되고 패터닝되어 도 3 내의 포토레지스트 구조(301)가 형성된다. 즉 표면(212A) 및 상부 표면(212B) 위에 확장되는 언더볍프 금속 구조(300A)(원형이 바람직함)를 형성하도록 언더볍프 금속 층(300)을 포토레지스트 구조(301)에 따라 패터닝하여 알루미늄 패드(212)를 캡슐화한다. 도 4를 보자. 습식 에칭 또는 건식 에칭 공정을 사용하여 언더볍프 금속 층(300)을 에칭할 수 있다. 에칭 공정은 언더볍프 금속 층(300)의 개별 물질 층을 제거하기에 적절한 습식 에칭 화학 성질을 사용하는 것이 바람직하다.

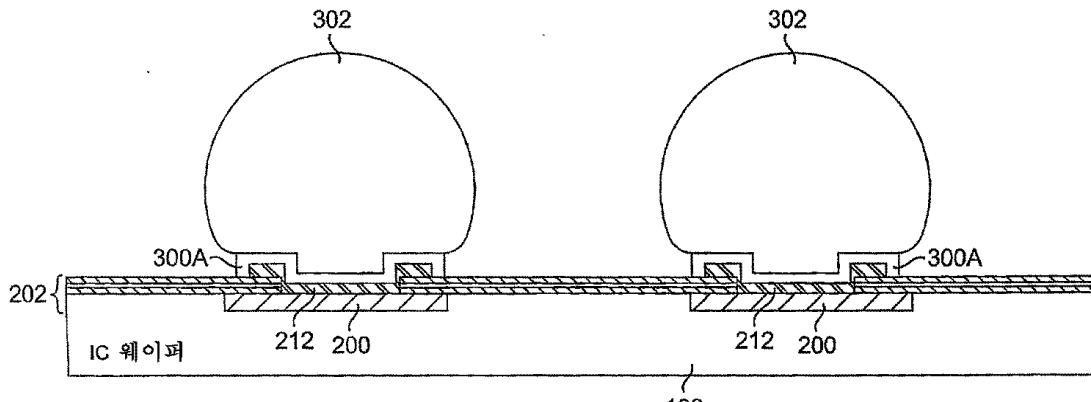

- [0042] 도 5는 알려진 공정에 따라 (일반적으로 땜납 역류 공정에 따라) 언더볍프 금속 구조(300A) 위에 형성된 땜납 범프(302)를 나타낸다. 땜납 범프(302)는 리드-기반 또는 리드-프리(lead-free) 물질을 포함한다.

- [0043] 본 발명은 플립 칩 또는 땜납 범프 본딩된 집적 회로에 대한 제2 패시베이션 층, 즉 도 10의 종래 기술에서의 마지막 패시베이션 층(214)을 제거한다. 도 5로부터 알 수 있는 바와 같이, 본 발명에 따라, 언더볍프 금속 구조(300A)는 알루미늄 패드(212)(알루미늄의 직접 범프로 언급됨)를 캡슐화한다. 완벽한 패드 캡슐화는 다음의 공정 단계 동안 형성될 수 있는 언더컷(undercut)으로부터 및 오염물질에의 노출로부터 알루미늄 패드(212)를 보호한다. 따라서 언더볍프 금속 구조(300A)에 의한 캡슐화는 도 10의 종래 기술의 마지막 패시베이션 층(214)과 동일한 기능을 수행한다. 제1 패시베이션 층, 즉 웨이퍼 패시베이션 층(202)이 존재함으로써 장치가 환경 영향에 의해 잠재적으로 손상을 입는 것으로부터 보호되기 때문에, 집적 회로 무결성은 손상되지 않는다.

- [0044] 본 발명에 따른 마지막 패시베이션 층(214)의 제거는 상당한 비용 절약을 제공하고(예를 들어, 웨이퍼 크기, 제조 라인 특성 및 응용 가능한 기술 노드에 따라 웨이퍼당 약 \$60 내지 \$150), 사이클 시간을 향상시키고(유전체 제2 또는 마지막 패시베이션 층을 퇴적하고 패터닝하기 위한 하나의 전체 공정 모듈이 제거됨), 플립 칩 또는 범프 본딩 기술을 사용하는 웨이퍼들의 웨이퍼 수율을 향상시킨다.

- [0045] 추가적으로, 언더볍프 금속 구조(300A)(마지막 패시베이션 층(214)(도 10 참조)이 아님)가 알루미늄 패드(212)를 캡슐화하기 때문에, 본 발명의 구조 및 공정 특징은 알루미늄 패드(212) 위에 언더볍프 금속 구조(300A)의 스텝 커버리지(step coverage)를 향상시킨다. 언더볍프 금속 구조(300A)를 통한 전류 재배포가 알루미늄 패드(212) 내의 잠재적 전류 클라우딩(crowding) 영향을 감소시킴에 따라, 전자이동 성능이 향상된다. 다양한 물질 층의 기계 및 금속 계면이 향상된다. 알루미늄 패드(212)가 언더볍프 금속 구조(300A)에 의해 완벽하게 캡슐화됨에 따라 전류량은 증가할 것이라고 예상된다. 언더볍프 금속 구조(300A)(웨이퍼 패시베이션 층(212)에 관련됨)가 완벽하게 캡슐화되고 이에 따라 금속 패드(구리 패드(200) 및 알루미늄 패드(212) 모두)의 노출이 줄어듦에 따라 전기 작용에 의한 부식 영향이 감소한다. 상호접속을 규정하고 불순물의 확산으로부터 집적 회로 구조를 보호하기 위한 종래 기술의 마지막 패시베이션 층(214)에 대한 요구가 더 이상 불필요한데, 이는 언더볍프 금속 구조(300A)가 이들 기능을 제공하기 때문이다.

- [0046] 본 발명의 교시는 구리 패드(200)와 함께 사용하는 것에만 제한되지 않고 마이크로 전자 장치 또는 부품을 패키지, 어셈블리 보드 또는 기관에 접속시키는 다른 도전성 물질과 함께 사용될 수 있다. 본 발명은 또한 여기에 설명된 바와 같이 구리 및 알루미늄 금속화에만 제한되는 것은 아니라, 당업자는 광 상호접속 시스템과 함께 사용될 수 있는 도전 시스템을 포함하는 다른 도전 시스템이 대신할 수 있다는 것을 인식한다.

- [0047] 본 발명이 바람직한 실시예를 참조하여 설명되었지만, 당업자는 다양한 변형이 만들어질 수 있고 등가의 소자가 본 발명의 영역으로부터 벗어나지 않으면서 소자를 대신할 수 있다는 것을 이해할 것이다. 본 발명의 영역은 여기서 설명된 다양한 실시예들로부터의 소자들의 임의의 조합을 더 포함한다. 추가로, 그것의 핵심 영역으로부터 벗어나지 않으면서 본 발명의 교시에 특정한 상황에 적응하도록 수정될 수 있다. 따라서, 본 발명은 본 발명을 수행하기 위해 계획된 최적 모드로 공개된 특정 실시예에만 제한되는 것이 아니라 첨부된 청구항의 영역에 속하는 모든 실시예를 포함할 것임이 의도된다.

### 도면의 간단한 설명

- [0026] 본 발명은, 다음의 도면들을 참조하여 읽을 때 다음의 상세한 설명의 관점에서 고려되면 본 발명은 보다 용이하게 이해되고 그것의 장점 및 사용이 보다 쉽게 명백해질 수 있다.

- [0027] 도 1-5는 본 발명의 실시예에 따른 땜납 범프 및 관련 구조의 제조에의 일련의 공정 단계를 나타내는 공통 평면에 따라 취해진 단면도.

- [0028] 도 6은 집적 회로에 대한 종래 기술의 와이어 본드 패키지의 절단 투시도(perspective cut-away view).

- [0029] 도 7 및 8은 종래 기술의 플립-칩 접적 회로 장치 구조를 나타내는 도면.

- [0030] 도 9는 종래 기술의 듀얼 다마신 상호접속 구조를 나타내는 단면도.

- [0031] 도 10은 종래 기술의 땜납 범프 구조를 나타내는 단면도.

- [0032] 통상의 구현에 따라, 다양하게 나타낸 장치 특징들은 크기에 맞춰 그려지지 않았으며, 오히려 본 발명에 관련된 특정 특징들이 강조되어 그려졌다. 도면 및 본문에서 참조 번호는 유사한 구성요소들을 나타낸다.

## 도면

### 도면1

도면2

도면3

도면4

도면5

도면6

(종래기술)

도면7

(종래기술)

도면8

(종래기술)

도면9

(종래기술)

도면10

(종래기술)