(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년02월22일

(11) 등록번호 10-0806262

(24) 등록일자 2008년02월15일

(51) Int. Cl.

*H01L 33/00* (2006.01)

(21) 출원번호 10-2006-7006741

(22) 출원일자 2006년04월07일

심사청구일자 2006년04월07일

번역문제출일자 2006년04월07일

(65) 공개번호 10-2006-0085662

(43) 공개일자 2006년07월27일

(86) 국제출원번호 PCT/JP2004/016699

국제출원일자 2004년11월04일

(87) 국제공개번호 WO 2005/043582

국제공개일자 2005년05월12일

(30) 우선권주장

JP-P-2003-00374478 2003년11월04일 일본(JP)

(56) 선행기술조사문헌

JP05183189 A

JP15273473 A

전체 청구항 수 : 총 6 항

심사관 : 이진홍

(54) 3족 질화물 p형 반도체의 제조방법, 및 3족 질화물 반도체발광 소자

### (57) 요 약

본 발명의 목적은 충분한 캐리어 농도를 갖고 결정결함이 적은 표면을 갖는 III족 질화물 p형 반도체의 효율적인 제조방법을 제공하는 것이다. 본 발명의 III족 질화물 p형 반도체의 제조방법은 (a)H<sub>2</sub>가스 및/또는 NH<sub>3</sub>가스를 함유하는 분위기에서 1000°C 이상의 온도에서 p형 도편트를 함유하는 III족 질화물 반도체를 성장시키고; (b)III족 질화물 반도체를 성장시킨 후, 강온하면서, 800°C보다 높은 온도에서 H<sub>2</sub>가스 및 NH<sub>3</sub>가스를 비활성 가스로 대체하는 것을 포함한다.

**대표도** - 도1

## 특허청구의 범위

### 청구항 1

(a) H<sub>2</sub>가스 및 NH<sub>3</sub>가스 중 어느 하나 이상을 함유하는 분위기에서 1000°C 이상의 온도에서 p형 도편트를 함유하는 III족 질화물 반도체를 성장시키고;

(b) III족 질화물 반도체의 성장 후, 0.5°C/초 이상의 속도로 강온하면서, 800°C보다 높은 온도에서 상기 분위기 를 비활성 가스로 대체하고, 실온까지 강온하는 것을 포함하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

### 청구항 2

제1항에 있어서, III족 질화물 반도체의 성장중에 유지된 온도로부터 50°C 이상까지 강온한 후 비활성 가스로 대체하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

### 청구항 3

제1항 또는 제2항에 있어서, 900°C 이상의 온도에서 비활성 가스로 대체하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

### 청구항 4

제1항 또는 제2항에 있어서, III족 질화물 반도체의 성장중에 온도는 1050°C 이상이고, 1000°C 이상에서 비활성 가스로 대체하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

### 청구항 5

제1항 또는 제2항에 있어서, III족 질화물 반도체가 식 Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>N(x= 0~0.5 및 y=0~0.1)로 나타내는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

### 청구항 6

제1항 또는 제2항에 있어서, III족 질화물 p형 반도체는 p형 도편트로서 마그네슘을 함유하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

### 청구항 7

삭제

### 청구항 8

삭제

### 청구항 9

삭제

## 명세서

### 기술분야

<1>

본 발명은 3족 질화물 p형 반도체의 제조방법 및 이를 사용한 3족 질화물 반도체 발광소자에 관한 것이고, 특히 기판의 표면에 충상으로 형성되고 충분한 캐리어 농도 및 결정결함이 적은 표면을 갖는 3족 질화물 p형 반도체 제조방법에 관한 것이다.

### 배경기술

<2>

최근 단파장 발광용 발광 소자에 사용되는 반도체재료로는 3족 질화물 반도체 재료가 주목을 끌고 있다. 일반적 으로 III족 질화물 반도체는 사파이어 결정 및 다른 산화물 결정 이외에 III-V 화합물 반도체 결정 기판으로서

사용하는 금속 유기 화학 증착법(MOCVD), 분자선 에피택시(MBE), 수소화물 기상 에피택시법(HVPE) 등에 의해 층상으로 형성된다.

<3> III족 질화물 반도체로부터 충분한 캐리어 농도를 갖는 p형 반도체를 형성하는 것이 곤란하다. 그러나, Mg를 도프한 갈륨 니트라이드에 저속 전자선으로 조사하는 방법(일본 특허공개 제2-257679호 공보 참조); 동일한 방법으로 Mg를 도프한 갈륨 니트라이드를 수소를 포함하지 않는 분위기에서 열처리하는 방법(일본 특허공개 제5-183189호 공보 참조); 및 다른 방법으로 충분한 캐리어 농도를 갖는 p형 반도체를 얻을 수 있다는 것이 발견되었다.

<4> 충분한 캐리어 농도를 얻을 수 있는 메카니즘은 수소 보호막이 형성된 p형 도편트를, 상기 방법으로 도편트를 탈수소화시킴으로써 활성화시키는 것이다. 금속 유기 화학증착법(MOCVD)는 결정성이 양호한 3족 니트리아드 반도체를 성장시키는데 일반적으로 사용된다. 그러나, MOCVD법에서 결정을 성장시키기 위한 성장장치에서 기관에 출발원료 화합물을 수송하는 캐리어 가스로서 사용하는 수소가스, 5족 출발원료로 사용되는 암모니아(NH<sub>3</sub>)의 분해에 의해 발생되는 수소분자 또는 라디칼 또는 원자상 수소가 고농도로 존재한다. 이 수소가 3족 질화물 반도체의 결정층의 성장시에 결정내에 혼입되고 결정에 도프하는데 사용되는 p형 도편트와 결정층의 성장온도로부터 냉각중에 결합을 형성한다. 이러한 방법으로 수소에 의한 보호막을 형성한 p형 도편트는 활성되지 않고 정공을 발생하지 않는다. 그러나 전자선으로 결정층을 조사하고, 열처리를 실시하여 결정내의 p형 도편트와 수소사이에 결합이 끊어져서 결정으로부터 수소를 방출하여 p형 도편트를 활성화할 수 있다.

<5> 그러나, 상술한 방법에서는 성장장치로부터 3족 질화물 반도체를 꺼내고 후처리를 실시하는 공정이 번잡하고, 가격은 고가이다. 이 방법은 열처리로 탈수소화 처리를 실시하는 경우에, 동시에 질소도 이탈하기 때문에, 이 방법을 사용하여 제작한 발광소자는 발광강도가 낮다고 하는 문제가 있다.

<6> 또한, III족 질화물 반도체를 성장 후 실온까지 냉각할 때에 H<sub>2</sub>가스 및 NH<sub>3</sub>가스를 비활성 가스로 대체하여 충분한 캐리어 농도를 얻을 수 있다는 것이 보고되어 있다(일본 특허공개 제8-125222호 공보 참조). 그러나, 이 방법에서는 진공에서 질소를 대체하고, 진공상태를 거치기 때문에, 질소가 결정으로부터 이탈되어 결정성이 저하된다. 진공상태를 거치지 않고 비활성 가스로 대체하는 일도 제안되어 있다(일본 특허공개 제9-129929호 공보 참조). 그러나, 이 방법에서는, 질화물 반도체의 성장온도인 1100°C에서 비활성 가스로 대체하면, 결정으로부터 질소가 이탈되어 결정성이 저하한다. 이 방법에서는 비활성 가스로 대체한 후 실온으로 도달하기 위해 2~3시간이 필요하다.

### 발명의 상세한 설명

<7> 본 발명은 종래 기술의 상기 문제점을 해결하기 위해서 개발되었고, 본 발명의 목적은 충분한 캐리어 농도를 갖고 결정결함이 적은 표면을 갖는 III족 질화물 p형 반도체의 제조방법을 제공하는 것이다.

<8> 본 발명은 하기 기재된 항목을 제공한다.

<9> (1) (a)H<sub>2</sub>가스 및/또는 NH<sub>3</sub>가스를 함유하는 분위기에서 1000°C 이상의 온도에서 p형 도편트를 함유하는 III족 질화물 반도체를 성장시키고;

<10> (b)III족 질화물 반도체를 성장시킨 후, 강온하면서, 800°C보다 높은 온도에서 H<sub>2</sub>가스 및 NH<sub>3</sub>가스를 비활성 가스로 대체하는 것을 포함하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

<11> (2) (1)에 있어서, III족 질화물 반도체의 성장중에 유지된 온도로부터 50°C 이상까지 강온한 후 비활성 가스로 대체하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

<12> (3) (1) 또는 (2)에 있어서, 900°C 이상의 온도에서 비활성 가스로 대체하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

<13> (4) (1) 내지 (3) 중 어느 하나에 있어서, III족 질화물 반도체의 성장중에 온도는 1050°C 이상이고, 1000°C 이상에서 비활성 가스로 대체하는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

<14> (5) (1) 내지 (4) 중 어느 하나에 있어서, III족 질화물 반도체가 식Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>N(x=0~0.5 및 y=0~0.1)로 나타내는 것을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

<15> (6) (1) 내지 (5) 중 어느 하나에 있어서, III족 질화물 p형 반도체는 p형 도편트로서 마그네슘을 함유하는 것

을 특징으로 하는 III족 질화물 p형 반도체의 제조방법.

- <16> (7) 기판상에 적어도 III족 질화물의 n형 반도체층, 발광층 및 p형 반도체층을 이 순서대로 적층하고, 상기 n형 반도체층 및 상기 p형 반도체층에 접하도록 음극 및 양극이 각각 설치된 III족 질화물 반도체 발광소자로서, 상기 p형 반도체층은 (1) 내지 (6) 중 어느 하나에 기재된 제조방법에 의해 제조되는 것을 특징으로 하는 III족 질화물 반도체 발광소자.

- <17> (8) (7)에 기재된 III족 질화물 반도체 발광소자를 포함하는 발광 다이오드.

- <18> (9) (7)에 기재된 III족 질화물 반도체 발광소자를 포함하는 레이저 다이오드.

- <19> 본 발명에 의하면, 반도체 소자로서 이용할 수 있는 충분한 p형 캐리어 농도를 갖는 III족 질화물 p형 반도체를, III족 질화물 반도체층의 최표면의 형태를 열화시키지 않고 최표면의 결정성에 결함을 일으키지 않도록 제작할 수 있다. 본 발명의 방법은 성장장치에서 성장을 종료한 후에 실시된 처리에 의해 p형으로 전환되기 때문에, 종래 방법에 의한 활성화 아닐 처리에 비해 공정수가 줄어들고, 생산성이 우수하다.

- <20> 본 발명의 제조방법을 적용할 수 있는 III족 질화물 p형 반도체에 있어서 III족 질화물 반도체로는 GaN이외에, InN, AlN 및 다른 2원계 혼합 결정; InGaN, AlGaN 및 다른 3원계 혼합 결정; InAlGaN 및 다른 4원계 혼합결정; 종래에 공지된 다른 모든 III족 질화물 반도체를 들 수 있다. 본 발명의 III족 질화물 반도체에 질소 이외에 V족 원소를 함유하는 GaPN, GaNAs 및 다른 3원계 혼합 결정; In 또는 Al을 함유하는 InGaPN, INGaAsN, AlGaPN, AlGaAsN 및 다른 4원계 혼합 결정; In 및 Al을 함유하는 AlInGaPN 및 AlInGaAsN, P 및 As를 함유하는 AlGaPAsN 및 InGaPAsN, 또는 다른 5원계 혼합결정; 및 이들 모든 원소를 함유하는 AlInGaPAsN 등의 6원계 혼합 결정을 들 수 있다.

- <21> 본 발명은 GaN, InN 및 AlN 등의 2원계 혼합결정; InGaN 및 AlGaN 등의 3원계 혼합 결정; InAlGaN 등의 4원계 혼합결정; V족 원소로서 N만을 함유하는 다른 III족 질화물 반도체가 특히 적합하다. 이들 결정체는 제조가 비교적 용이하고 상기 물질중에서 분해의 위험이 적다. III족 질화물 반도체는 일반식  $Al_xIn_yGa_{1-x-y}N$ 으로 나타내는 경우, x는 0~0.5의 범위가 바람직하고 y는 0~0.1의 범위가 바람직하다.

- <22> 본 발명에서 이용할 수 있는 p형 도편트로는, III족 질화물 반도체를 도프하는데 이용하는 경우 p형 도전성을 나타낸다고 보고되거나 예상되는 Mg, Ca, Zn, Cd, Hg 등을 들 수 있다. 이들 원소중에서 열처리에 의해 활성화율이 높은 Mg가 p형 도편트로서 특히 바람직하다. 도편트 함유량은  $1 \times 10^{18}$ ~ $1 \times 10^{21} cm^{-3}$ 이 바람직하다. 상기 함유량보다 낮은 도편트 함유량으로 p형으로의 전환이 발생될 수 있지만, 반도체 소자가 형성된 경우에는 충분한 접촉저항을 얻을 수 없다.  $1 \times 10^{21} cm^{-3}$  이상의 도편트를 함유하면 결정성이 열화되므로 바람직하지 않다.  $1 \times 10^{19}$ ~ $1 \times 10^{20} cm^{-3}$ 이 보다 바람직하다.

- <23> 본 발명이 적용된 III족 질화물 p형 반도체의 성장방법은 특별히 제한되지 않는다. MOCVD(금속 유기 화학 증착법), HVPE(하이드라이드 기상에피택시법), MBE(분자선 에피택시법) 및 III족 질화물 반도체를 성장시키는데에 공지된 다른 모든 방법을 적용할 수 있다. 바람직한 성장방법은 질량 생산성 및 막두께 제어의 관점에서 MOCVD 법이다.

- <24> MOCVD법에서, 캐리어 가스로서 수소( $H_2$ ) 또는 질소( $N_2$ )가 사용되고, III족 출발원료인 Ga원으로 트리메틸갈륨(TMГ) 또는 트리에틸갈륨(TEG)이 사용되고, Al원으로 트리메틸 알루미늄(TMA) 또는 트리에틸 알루미늄(TMA)이 사용되고, In원으로 트리메틸인듐(TMI) 또는 트리에틸인듐(TEI)이 사용되고, 질소원으로 암모니아( $NH_3$ ), 하이드라진( $N_2H_4$ ) 등이 사용된다. p형 도편트로는 Mg 출발원료로, 예를 들면 비스시클로펜타디에닐 마그네슘( $Cp_2Mg$ ) 또는 비스에틸시클로펜타디에닐 마그네슘( $EtCp_2Mg$ )이 사용되고, Zn 출발원료로 디메틸 아연( $Zn(CH_3)_2$ )이 사용된다.

- <25> 본 발명의 효과는 수소에 의한 p형 도편트 보호막이 발생하는 상황하에서, 특히 캐리어가스로  $H_2$ 가 사용되고 및/ 또는 질소원으로  $NH_3$ 가 사용된다. p형 도편트의 수소에 의한 보호막이 발생할 수 있는 상황이면, 캐리어 가스로  $N_2$  또는 다른 비활성 가스를 사용하는 경우에도 효과적이다.

- <26> 성장온도는 양호한 결정성과 접촉 저항을 얻기 위해서 1000°C 이상을 유지하는 것이 바람직하다. 1050°C 이상 및 1150°C 이하의 온도가 보다 바람직하다.

- <27> p형 도편트를 함유한 III족 질화물 반도체를 성장시킨 후, 실온까지 강온하고 반도체 적층물을 성장장치로부터 꺼낼 때, H<sub>2</sub> 및 NH<sub>3</sub>를 비활성가스로 대체하는 것이 필요하다. 진공상태를 거치지 않고 비활성 가스로 직접 대체하는 것이 중요하다. 진공상태를 거치면, 반도체 결정의 표면으로부터 질소의 이탈이 많아져서 결정성이 저하된다. 이탈되는 양은 감압의 정도에 따라서 변화되고, 10kPa(100mbar) 이하의 압력을 거치지 않는 것이 바람직하고, 20kPa(200mbar) 이하, 특히 바람직하게는 40kPa(400mbar)이하이다.

- <28> 기판 온도를 강온하면서 대체하는 것이 중요하다. 성장 반응시의 온도가 변화되지 않게 유지하면서 비활성 가스로 대체하는 경우 반도체 결정의 표면으로부터 질소의 이탈이 발생되어 결정성이 저하한다. 성장 반응시의 온도보다 적어도 50°C 이하의 온도로 강온한 후 대체하는 것이 바람직하다. 너무 많이 강온하면, 충분한 캐리어 농도를 얻을 수 없기 때문에 바람직하지 않다. 성장반응시 온도의 200°C 이내에서 대체하는 것이 바람직하고, 보다 바람직하게는 150°C 이내, 특히 바람직하게는 100°C 이내이다. 800°C 이하의 기판온도에서 대체해도 충분한 캐리어 농도를 얻을 수 없다. 900°C 이상의 기판온도에서 대체하는 것이 바람직하다. 성장 온도가 1050°C 이상이면 1000°C 이상에서 대체하는 것이 바람직하다.

- <29> 기판의 강온속도를 제어하는 것이 중요하다. 강온속도가 너무 느리면 질소 이탈에 의해 결정성이 저하되어 바람직하지 않다. 온도는 성장 종료시의 온도로부터 0.5°C/초 이상으로 강온하는 것이 바람직하고, 보다 바람직하게는 1.0°C/초 이상, 특히 바람직하게는 2.0°C/초 이상이다.

- <30> 비활성 가스로는 질소가 바람직하지만, 아르곤, 헬륨 등 또는 이들 가스의 혼합물을 사용해도 좋다.

- <31> 본 발명에 의한 III족 질화물 p형 반도체의 제조방법은 III족 질화물 p형 반도체를, 반도체 소자를 구성하는 다층 구조의 한 층으로 기판상에 형성하는 반도체 소자의 제조에 있어서 사용될 수 있다. 예를 들면, 발광 다이오드, 레이저 다이오드 등의 반도체 발광 소자의 제조 이외에, 각종 고속 트랜지스터, 수광소자 등의 III족 질화물 p형 반도체를 필요로 하는 반도체 소자를 제작하면, 어떠한 반도체 소자의 제작에 있어서도 이 방법을 이용할 수 있고, 특히 pn 접합의 형성 및 양호한 특성을 갖는 전극의 형성을 필요로 하는 반도체 발광소자의 제작에 있어서 사용하는 것이 적합하다.

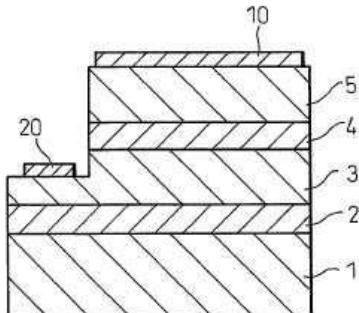

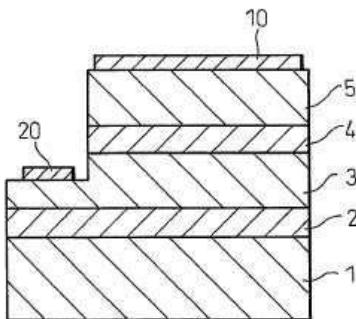

- <32> 도1은 본 발명의 III족 질화물 p형 반도체의 제조방법을 사용하여 제조된 III족 질화물 반도체 발광소자의 모식도이다. 기판(1)상에 필요에 따라서 베퍼층(2)을 통해 III족 질화물 반도체로 구성된 n형 반도체층(3), 발광층(4) 및 p형 반도체층(5)을 이 순서대로 적층하고, n형 반도체층(3)에 음극(20)을 설치하고, p형 반도체층(5)에 양극(10)을 설치한다.

- <33> 기판(1)에 사파이어, SiC, GaN, AlN, Si, ZnO 또는 다른 산화물 기판, 또는 어떤 다른 종래의 공지된 재료를 제한없이 사용할 수 있다. 사파이어가 바람직하다. 베퍼층(2)은 필요에 따라서 기판과 그 위에 형성된 n형 반도체층(3) 사이에 격자 부정합을 조정하기 위해 설치된다. 종래에 공지된 베퍼층은 필요에 따라서 사용된다.

- <34> n형 반도체층(3)을 위해 이 기술분야에서 공지된 기술을 사용하여 소망하는 조성 및 구조로 해도 좋다. n형 반도체층은 통상 음극과 양호한 음접촉을 얻을 수 있는 콘택트층과 발광층 보다 큰 밴드갭 에너지를 갖는 클래드층으로 구성된다.

- <35> 발광층(4)에 단일 양자 우물구조(SQW) 및 다중 양자 우물 구조(MQW), 또는 다른 종래에 공지된 조성 및 구조는 제한없이 사용될 수 있다.

- <36> p형 반도체층(5)은 본 발명의 제조방법에 의해 형성된다. 이 기술분야에서 잘 알려진 기술을 사용하여 소망하는 조성 및 구조로 해도 좋다. n형 반도체와 동일한 방법으로, 양극과 양호한 음접촉을 얻을 수 있는 콘택트층과 발광층보다 큰 밴드갭 에너지를 갖는 클래드층으로 이루어진다.

- <37> n형 반도체층(3)(콘택트층) 및 p형 반도체층(5)(콘택트층)에 각각 음극(20) 및 양극(10)을 이 기술분야에서 잘 알려진 통상의 방법으로 설치한다. 그 구조에 종래에 공지된 구조를 어떤 제한없이 사용할 수 있다.

### 실시예

- <39> 이하, 실시예를 사용하여 본 발명을 보다 상세하게 기재하지만, 본 발명은 이들 실시예로 제한되지 않는다.

- <40> (실시예1)

- <41> 본 실시예에서, MOCVD법을 사용하여 사파이어 기판상에 GaN층을 베퍼층으로 형성하고, 그 위에 Mg를 도포한 GaN 층을 1100°C에서 적층하는 방법으로 시료를 제작했다. 더욱이 적층 후, 1050°C의 온도에서 암모니아 가스 및 H<sub>2</sub>

의 공급을 중단하고, 그 대신에 질소가스를 공급하고, 냉각하여, Mg-p형 도편트를 활성화한 상태로 제작하였다. 이하에 상세하게 기재한다.

<42> MOCVD법을 이용하여 하기 기재된 절차로 GaN층을 갖는 시료를 제작하였다. 우선, 사파이어 기판을 유도 가열로의 RF 코일안에 설치된 석영제 반응로안에 도입했다. 가열용 탄소제 서셉터위에 사파이어 기판을 배치했다. 기판을 도입한 후, 반응로내를 진공으로 만들어, 공기를 제거하고, 질소가스를 순환시켜, 반응로내를 퍼지했다. 질소가스를 10분간 순환시킨 후, 유도 가열로를 작동시키고, 10분에 걸쳐서 1180°C까지 기판온도를 상승시켰다. 기판온도를 1180°C로 유지하면서, 수소가스와 질소가스를 순환시키면서 10분간 방치하고, 기판표면의 씨멀 클리닝을 실시하였다. 클리닝을 실시하면서, 반응로에 접속된 출발원료 트리메틸 갈륨(TMГ) 및 시클로펜타디에닐 마그네슘(Cp<sub>2</sub>Mg)을 함유하는 용기(버블러)의 배관을 통해 수소 캐리어 가스를 흘려주고 버블링을 시작했다. 각 버블러의 온도는 온도 조정 항온조를 이용하여 일정한 값으로 조정했다. 버블링에 의해 형성된 출발원료의 증기는 GaN층의 성장이 시작되기 전에, 캐리어 가스와 함께 제해장치의 배관으로 순환시켜, 제해장치를 통해 방출되었다.

<43> 씨멀 클리닝 종료후, 유도 가열로를 조절하여, 기판온도를 510°C로 강온하고, 10분 후 TMG 배관과 암모니아 가스 배관의 밸브를 전환하여, TMG 및 암모니아를 반응로로 공급하고, GaN을 구성하는 베퍼층을 기판에 형성했다. 이 때에 반응에 상용되는 압력은 20kPa이었고, 암모니아 유량은 3L/분이었고, TMG 유량은 35cc/분이었고, 수소 가스 유량은 8L/분이었다. 베퍼층을 약 10분간 성장시킨 후, TMG 배관의 밸브를 전환하여, 베퍼층의 성장을 종료했다.

<44> 베퍼층을 형성한 후, 기판온도를 1100°C로 상승시켰다. 온도상승중 베퍼층이 승화되지 않도록 수소 캐리어 가스 이외에 암모니아 가스를 반응로에 공급했다. 온도가 1100°C로 안정한 것을 확인한 후, TMG 및 Cp<sub>2</sub>Mg 배관의 밸브를 전환하여 이들 출발원료의 증기를 함유한 가스를 반응로에 공급하고, 베퍼층상에 Mg를 도프한 GaN층을 성장시켰다. 상술한 GaN층을 하기 기재된 조건을 사용하여 2시간 동안 성장시킨 후, TMG 및 Cp<sub>2</sub>Mg 배관의 밸브를 전환하여, 반응로로 출발원료의 공급을 중단하고 성장을 종료하였다. 조건은 압력은 20kPa, 암모니아 유량 3L/분, TMG 유량 35cc/분, 수소가스 유량 8L/분, 및 Cp<sub>2</sub>Mg 유량 240cc/분이었다.

<45> GaN층의 성장을 종료한 후, 유도 가열로를 제어하여 기판온도를 실온까지 20분에 걸쳐서 강온했다. 결정표면으로부터 N이탈을 최소화하기 위해 반응로내의 분위기를 성장중과 동일하게 암모니아 및 수소로 구성되어 있고, 기판온도가 1050°C가 된 것을 확인한 후, 암모니아 및 수소의 공급을 중단하고, 질소가스로 공급을 전환했다. 질소가스를 30L/분의 유량을 공급하면서 기판온도를 실온으로 강온하고, 시료를 대기중으로 꺼냈다.

<46> 상기 방법에 의해, 사파이어 기판에 20nm의 막두께를 갖는 GaN 베퍼층을 형성하고, 그 위에  $1 \times 10^{20} \text{ cm}^{-3}$ 의 Mg를 도프하고  $2\mu\text{m}$ 의 두께를 갖는 GaN층을 형성한 시료를 제작했다.

<47> Mg를 도프한 GaN층 시료의 캐리어 농도를 측정했다. 캐리어 농도는 반데르파우 방법의 홀효과측정을 사용하여 하기 기재된 것처럼 측정했다. 초음파를 처리한 비이커에 아세톤에 7mm각의 정방형으로 절단한 시료를 10분간 침지시키고, 10분간 염산에서 가열하고, 3분간 흐르는 물로 세척하였다. 금속 마스크를 이용한 증착에 의해 시료의 네모서리에서 3000Å의 막두께를 갖는 Ni로 이루어지는 0.5mm의 직경을 갖는 원형전극이었다. 전극과 시료 사이에 음접촉을 형성하기 위해, 시료를 아르곤 분위기에서 450°C에서 10분간 아닐했다. 홀효과측정은 상기 시료에 3000-G자장안으로  $10\mu\text{A}$ 의 전류를 가하여 실시하였다. 전극의 접촉특성은 음특성이 있고, 정확한 측정을 실시하였다는 것을 확인하였다. 이 측정의 결과, Mg를 도프한 GaN층은 p형이었고, 캐리어 농도는  $2 \times 10^{17} \text{ cm}^{-3}$ 이었다. GaN층의 상부표면은 원자간력 현미경(AFM)을 사용하여 관찰했다. 그 결과, 암모니아 및 수소를 고온에서 중지했기 때문에 승화/분해된 흔적을 찾을 수 없고 양호한 형태의 표면이 관찰되었다. AFM으로부터 계산된 표면조도는 20~30Å이었다.

<48> (비교예1)

<49> 실시예1과 동일한 방법으로 사파이어 기판상에 베퍼층으로 GaN층을 형성하고, 그 위에 Mg를 도프한 GaN층을 적층했다. 적층을 종료한 후에 시료를 실온으로 냉각하는 조작은 기판이 800°C로 도달한 것을 확인한 후 암모니아 및 수소의 공급을 중단하고 질소가스로 전환하는 것을 제외하고는 실시예1과 동일하다.

<50> 실시예1과 동일한 방법으로 캐리어 농도를 측정했을 때, 캐리어 농도는  $7 \times 10^{15} \text{ cm}^{-3}$ 으로 실시예1에 비해 작은 것을 알았다.

&lt;51&gt; (비교예2)

<52> 실시예1과 동일한 방법으로 사파이어 기판상에 GaN층을 벼파층으로 형성하고, 그 위에 Mg를 도프한 GaN층을 적층하였다. 성장 종료직후, 암모니아 및 수소의 공급을 중단하고, 질소가스로 전환하는 것을 제외하고는 실시예1과 동일한 방법으로 기판온도를 실온으로 강온하고, 시료를 대기중으로 꺼냈다.

<53> 실시예1과 동일한 방법으로 캐리어 농도를 측정했을 때, GaN층은 p형으로 그 캐리어 농도는  $6 \times 10^{17} \text{ cm}^{-3}$  이었다. 그러나, GaN층의 최표면을 AFM으로 관찰한 결과, GaN층의 표면에는 승화/분해되었다고 생각되는 흔적이 관찰되었다. AFM관찰로부터 계산된 Ra는 200 Å 이었다.

&lt;54&gt; (실험예1)

<55> 실시예1 및 비교예1의 시료를 상술한 일본 특허공개 제5-183189호 공보에 기재된 방법에 의해 열처리되고, 본 발명에 의한 실시예1에서 얻어진 시료에서는 한층 더 열처리하는 것이 필요하지 않지만, 비교예1에서 얻어진 시료에서는 한층 더 열처리 하는 것이 필요하다는 것을 확인하였다. 이 조작의 세부사항을 이하에 기재한다.

<56> 열처리에 열처리로를 사용했다. 열처리로는 열처리에 사용되는 각종 가스가 가스 도입부를 통해서 공급하도록 석영체 반응로 튜브의 내부에 탄소제 서셉터를 배치하도록 설치한 적외선로이다.

<57> 열처리로는 진공 플랜지와 가스 배기구에 접속된 진공펌프에 설치하고, 반응로 튜브내부에 진공을 만들 수 있다. 온도를 모니터링하기 위한 열전대를 탄소제 서셉터에 삽입하여 열전대로부터 신호를 기본으로, 적외선 히터의 파워를 제어하고, 시료의 온도를 제어할 수 있다. 펌프로 배기된 가스는 물을 통해 외부 공기로 배출되고, 열처리로의 내부를 통해 흐르는 암모니아는 물에 용해되어 외부로 배출되지 않는다.

<58> 상기 열처리로를 이용하여 하기 조작순서에 따라서 시료에 열처리를 실시했다. 처음에 외부로 서셉터를 꺼내고, 시료를 그 위에 배치하고 다시 반응로 튜브로 도입하고, 진공 플랜지를 고정했다. 진공펌프로 반응로 튜브 내부를 진공으로 만들고 열처리에 사용되는 분위기 가스인 질소가스로 펴지했다. 이 작업을 3회 반복한 후, 반응관 튜브내부를 대기압으로 만들고 상기 분위기 가스를 유량 0.5cc/분으로 5분간 반응로 튜브로 흘려주었다. 분위기 가스를 5분간 흘려준 후, 적외선 히터로 통전을 한 후, 시료를 가열했다. 분위기 가스를 상기 유량으로 공급한 채로, 처음에 1분에 걸쳐 시료의 온도를 900°C까지 가열했다. 1분간 이 상태에서 900°C의 온도를 유지한 후, 적외선 히터의 전류를 0으로 하고 시료의 가열을 중지했다. 이 상태에서 시료의 온도를 실온까지 20분에 걸쳐서 강온했다. 서셉터의 온도가 실온인 것을 확인한 후, 진공 플랜지를 개방하고, 서셉터를 외부로 꺼내 시료를 회수했다.

<59> 열처리된 시료의 Mg 도프된 GaN층에 캐리어 농도를 실시예1의 방법으로 측정했다.

<60> 실시예1의 캐리어 농도는  $3 \times 10^{17} \text{ cm}^{-3}$  으로 거의 변화가 없고, 비교예1에 시료의 캐리어 농도는  $1 \times 10^{17} \text{ cm}^{-3}$  으로 향상되었다.

&lt;61&gt; (실시예2)

<62> 도1에 나타내는 III족 질화물 반도체 발광소자는 본 발명의 제조방법에 의해 얻어진 III족 질화물 p형 반도체를 이용하여 제작하였다.

<63> 사파이어 c면((0001)결정면)으로 이루어지는 기판(1)상에 AlN으로 이루어지는 벼파층(2)을 통해 n형 반도체층(3), 발광층(4) 및 p형 반도체층(5)을 기술로 널리 알려진 기술로 일반적인 진공 MOCVD법에 의해 이 순서대로 적층시켜서 제작했다. n형 반도체층(3)으로서 도프되지 않은 GaN층(기초층:층두께=2μm) 및 Ge 도프된 n형 GaN층(n콘택트층:층두께=2μm, 캐리어 농도= $1 \times 10^{19} \text{ cm}^{-3}$ )을 동일한 순서로 적층하였다. 발광층(4)은 6층 Ge 도프된 GaN 배리어층(층두께=14.0nm, 캐리어 농도= $1 \times 10^{18} \text{ cm}^{-3}$ ) 및 5층의 도프되지 않은 In<sub>0.20</sub>Ga<sub>0.80</sub>N 우물층(층두께=2.5nm)으로 이루어지는 다중 양자 구조를 갖는다. p형 반도체층(5)은 Mg 도프된 p형 Al<sub>0.07</sub>Ga<sub>0.93</sub>N층(p클래드층:층두께=10nm) 및 Mg 도프된 p형 Al<sub>0.02</sub>Ga<sub>0.98</sub>N층(p콘택트층:층두께=150nm)을 동일한 순서로 적층했다.

<64> 또한, Mg 도프된 Al<sub>0.02</sub>Ga<sub>0.98</sub>N 콘택트층은 하기 기재된 방법에 의해 제작했다.

<65> (1)Mg 도프된 Al<sub>0.07</sub>Ga<sub>0.93</sub>N 클래드층의 성장을 종료한 후, 성장 반응로 내부에 압력을  $4 \times 10^4$  파스칼(Pa)로 하였

다.

<66> (2) 트리메틸갈륨, 트리메틸 알루미늄 및 암모니아를 출발원료로, 비스시클로펜타디에닐 마그네슘을 Mg 도핑원으로서 사용하여 1100°C에서 Mg 도프된 AlGaN층의 기상 성장을 시작했다. 성장중 캐리어 가스로서 수소를 사용했다.

<67> (3) 트리메틸 갈륨, 트리메틸 알루미늄, 암모니아 및 비스시클로펜타디에닐 마그네슘을 4시간동안 연속적으로 성장 반응로로 공급하고, Mg 도프된 Al<sub>0.02</sub>Ga<sub>0.98</sub>N층을 두께 150nm로 성장시켰다.

<68> (4) 트리메틸 갈륨, 트리메틸 알루미늄 및 비스시클로펜타마그네슘을 성장 반응로로 공급하는 것을 중단하고, Mg 도프된 AlGaN층의 성장을 중단하였다.

<69> (5) Mg 도프된 Al<sub>0.02</sub>Ga<sub>0.98</sub>N층으로 이루어지는 p형 콘택트층의 기상 성장을 종료한 후, 즉시 히터로의 통전을 정지하고 20초후에 캐리어 가스를 수소로부터 질소로 전환하고, 암모니아를 차단하였다. 이 때에 반응로의 온도는 1050°C이었다.

<70> (6) 이 상태에서 실온으로 냉각한 후, 적층된 구조를 성장 반응로에서 꺼냈다.

<71> 이와같이 얻어진 적층된 구조의 p콘택트층에 마그네슘 및 수소원자의 농도는 2차 이온질량분석기(SIMS) 분석방법에 의해 결정되었다. Mg원자를  $7 \times 10^{19} \text{ cm}^{-3}$ 의 농도로, 표면으로부터 깊이 방향으로 매우 일정한 농도로 구배되었다. 수소원자는  $6 \times 10^{19} \text{ cm}^{-3}$ 의 매우 일정한 농도로 존재하였다. 또한, 실시예1에서 동일한 방법으로 측정된 캐리어농도는  $3 \times 10^{17} \text{ cm}^{-3}$ 이었다. TLM방법으로 측정된 저항율은 약  $150\Omega\text{cm}$ 로 추측되었다.

<72> 발광소자(LED)는 III족 질화물 p형 반도체층에 제공된 적층된 구조를 사용하여 제작되었다. 우선, 음극(20)이 형성된 면적에 통상 건식에칭을 실시하고, 이 영역에서 Ge 도프된 GaN층(n콘택트층)의 표면만을 노광시켰다. 적층된 티타늄(Ti)/알루미늄(Al)으로 이루어진 음극(20)을 표면의 노광부상에 형성되었다. n콘택트층(3)의 표면에 접촉한 금속막은 티타늄막이었다.

<73> 낱은 p콘택트층의 표면 전체에 발광층으로부터 발광을 사파이어 기판에 반사시키는 기능을 제공하는 적층된 플라티늄(Pt)막/로듐(Rh)막/금(Au)막으로 이루어진 반사성 양극(10)을 형성했다. p콘택트층(5)의 표면에 접촉시킨 금속막은 플라티늄막이었다.

<74> 음극(20) 및 양극(10)을 형성한 후, 사파이어 기판(1)의 이면은 다이아몬드 입자의 연마용 입자를 사용하여 연마하고, 최종적으로 경면에 마무리했다. 이와같이 얻어진 적층구조를 절단하고 350μm각의 정방형의 개개의 발광소자로 분리했다.

<75> 이와같이 얻어진 발광소자의 음극 및 양극을 마운트에 접착하고 플립형 칩으로 했다. 이 때, 칩전극에 대략 300°C의 열로 처리한다. 칩을 리드 프레임상에 배치하고 금(Au)와이어로 리드 프레임에 접속된다.

<76> 이와같이 얻어지는 LED칩의 음극(20)과 양극(10)사이에 순방향으로 전류를 흘려주고, 전기적 특성 및 발광특성을 평가했다. 순방향 전류가 20mA로 했을 때 순방향 구동전압(Vf)은 3.0V이고, 통상 적분구로 측정된 발광 출력은 10mW이었다. 역방향 전류를 10μA로 했을 때에 역방향전압(Vr)은 20V이상이었다. 사파이어 기판을 통해 외부로의 발광 파장은 455nm이었다. 직경 5.1cm(2인치)의 웨이퍼로부터 외관 불량품을 제외하고 대략 10,000개의 LED칩을 얻을 수 있었고, 상기 기재된 것 등의 균일한 특성이 관찰되었다.

<77> (실시예3)

<78> 양극으로 파랑으로부터 자외선 범위로 빛을 투과하는 기능을 갖는, 니켈(Ni)막/금(Au)막을 적층시켜서 형성되는 투과성 양극을 사용하고, p 콘택트층(5)에 접촉하는 금속막을 니켈막으로 구성하는 것을 제외하고는 실시예2와 동일하게 발광소자를 제작하였다.

<79> 이와같이 얻어진 발광소자의 사파이어면을 마운트에 접착하고, 음극 및 양극을 금배선으로 리드 프레임에 접속하고, 실시예2와 동일한 방법으로 평가하였다.

<80> 순방향 전류를 20mA로 했을 때의 순방향 구동전압(Vf)은 3.0V이고, 일반적인 적분구로 측정된 발광출력은 6mW이며, 발광파장은 455nm였다. 역방향 전류를 10μA로 했을 때에 역방향 전압(Vr)은 20V 이상이었다. 직경 5.1cm(2인치)의 웨이퍼로부터 외관 불량품을 제외하고 약 10,000개의 LED칩을 얻을 수 있었고, 상기 기재된 것과 동일한 특성이 관찰되었다.

<81> (실시 예4)

<82> 양극으로 파랑으로부터 자외선 범위로 빛을 투과하는 기능을 갖는, 코발트(Co)막/금(Au)막을 적층시켜서 형성되는 투과성 양극을 사용하고, p 콘택트층(5)에 접촉하는 금속막을 코발트막으로 구성하는 것을 제외하고는 실시 예2와 동일하게 발광소자를 제작하였다.

<83> 이와같이 얻어진 발광소자는 실시예3과 동일한 방법으로 평가하였다.

<84> 순방향 전류를 20mA로 했을 때의 순방향 구동전압(Vf)은 3.0V이고, 일반적인 적분구로 측정된 발광출력은 6mW이며, 발광파장은 455nm였다. 역방향 전류를 10 $\mu$ A로 했을 때에 역방향 전압(Vr)은 20V 이상이었다. 직경 5.1cm(2인치)의 웨이퍼로부터 외관 불량품을 제외하고 약10,000개의 LED칩을 얻을 수 있었고, 상기 기재된 것과 동일한 특성이 관찰되었다.

<85> (실시 예5)

<86> 양극으로 파랑으로부터 자외선 범위로 빛을 투과하는 기능을 갖는, 플라티늄(Pt)막/금(Au)막을 적층시켜서 형성되는 투과성 양극을 사용하고, p 콘택트층(5)에 접촉하는 금속막을 플라티늄막으로 구성하는 것을 제외하고는 실시 예2와 동일하게 발광소자를 제작하였다.

<87> 이와같이 얻어진 발광소자는 실시예3과 동일한 방법으로 평가하였다.

<88> 순방향 전류를 20mA로 했을 때의 순방향 구동전압(Vf)은 3.0V이고, 일반적인 적분구로 측정된 발광출력은 6mW이며, 발광파장은 455nm였다. 역방향 전류를 10 $\mu$ A로 했을 때에 역방향 전압(Vr)은 20V 이상이었다. 직경 5.1cm(2인치)의 웨이퍼로부터 외관 불량품을 제외하고 약10,000개의 LED칩을 얻을 수 있었고, 상기 기재된 것과 동일한 특성이 관찰되었다.

<89> 상기 기재된 것처럼, 모든 실시예에서 양호한 접촉성능이 존재하고, 양극의 조성 및 구조에 관계없이 본 발명의 효과를 얻을 수 있는 것이 증명되었다.

### 산업상 이용 가능성

<90> 본 발명에 의해 제공된 III족 질화물 p형 반도체를 제조하는 방법은 종래의 활성화 후처리가 필요하지 않고 생산성이 우수하다. 결과적으로, 본 발명의 제조방법은 III족 질화물 반도체 소자의 제조에 있어서 매우 유용하다.

### 도면의 간단한 설명

<38> 도1은 본 발명에 의한 III족 질화물 p형 반도체의 제조방법을 사용하여 얻어진 III족 질화물 반도체 발광 소자의 모식도이다.

### 도면

#### 도면1