# (12) UK Patent Application (19) GB (11) 2 107 542 A

- (21) Application No 8228247

- (22) Date of filing 4 Oct 1982

- (30) Priority data

- (31) 309756

- (32) 8 Oct 1981

- (33) United States of America (US)

- (43) Application published 27 Apr 1983

- (51) INT CL3 HO3K 17/04

- (52) Domestic classification

H3T 2B3 2T2X 2T4 3C1

3N 4E1N 4E2N 4S 5E

HX

H1K 11A3 11B3 11B4

11C1A 11C4 11D 1AA9

1BC 1BD 1FJ 4C11

4C1R 9B1 9B1A 9D1 9E

9N2 9N3 9R2 GAX

- (56) Documents cited

GB 1349445

GB 1203626

GB 1118640

GB 1130192

GB 1097956

GB 1028656

GB 0997582

- (58) Field of search

H3T

- (71) Applicant

NV Philips

Gloeilampenfabrieken

(Netherlands)

Groenewoudseweg 1

5621 BA Eindhoven

The Netherlands

- (72) Inventor

Thomas Dale Fletcher

- (74) Agents

R J Boxall

Mullard House

Torrington Place

London WC1E 7HD

## (54) Bipolar logic inverter

(57) A logic inverter comprises a first transistor (QA) having its collector coupled to a voltage source (V<sub>cc</sub>) via a load (RC) and its emitter connected to the base of a second transistor (QB). The collector of the second transistor is also fed from the load (RC). In order to reduce the switching time of the circuit means are provided for preventing the second transistor from either turning off or normally going into deep saturation. These means comprise a first diode (DF) feeding the base of the second transistor and a second diode (DE) which feeds the collector of the second transistor, the second diode acting, when the input voltage (VIN) is high, in conjunction with a Schottky clamp (DA) provided for the first transistor to hold up the voltage on the collector

of the second transistor relative to that on its base. The Schottky clamp may be replaced by a diode connected between the base of the first transistor and the collector of the second transistor. (Fig. 3).

GB 2 107 542 /

### **SPECIFICATION**

#### Logic circuit

5 This invention relates to logic circuits including bipolar transistors. 5 In designing a digital logic gate in a semiconductor integrated circuit, an important objective is to reduce the gate propagation delay. This is the average time needed for an output signal of the gate to switch from a desired logical or "O" value to a desired logical high or "1" value and vice versa in response to a change in the logical value of an input signal to the gate. Such a 10 gate typically consists of a switching transistor in combination with a mechanism to pull the 10 output signal rapidly down to logical "O" and/or a mechanism to pull the output signal rapidly up to logical "1". Referring to the drawings, Fig. 1 illustrates a conventional inverting logic gate of the type briefly mentioned by H. Ishino in U.S. Patent 4,107,547. This transistor-transistor logic (TTL) 15 inverter receives an input voltage V<sub>IN</sub> at the base of a bipolar NPN transistor QA and provides an 15 output voltage Vout at the collector of another bipolar NPN transistor QB having its emitter grounded and its base connected to the emitter of transistor QA. The collector of transistor QA is resistively coupled to a voltage/current source V<sub>cc</sub> and is coupled through a conventional PN diode DD to the collector of transistor QB. Transistor QA or QB is in the on or conductive state when its base-to-emitter junction voltage  $V_{\text{BEQA}}$  or  $V_{\text{BEQB}}$  equals a PN diode-drop voltage termed a " $V_{\text{BE}}$ " and is in the off or substantially 20 non-conductive state when voltage  $V_{\text{BEOA}}$  or  $V_{\text{BEOB}}$  is less than  $1V_{\text{BE}}$ . Accordingly, transistors QA and QB both turn on as input voltage  $V_{\text{IN}}$  is raised from a logical "O" of less than  $1V_{\text{BE}}$  to a logical "1" of 2VBE. Both transistors QA and QB go into "deep" saturation. This means that the 25 base-collector junction of transistor QA or QB is sufficiently forward biassed so as to be fully 25 conductive . As transistor QB saturates, it draws progressively more current from source  $V_{CC}$  to actively pull output voltage  $V_{OUT}$  down to a logical ''O'' near 0 volt. When voltage  $V_{IN}$  is brought back down to its logical ''O'', transistors QA and QB both turn off. Depending on the load which voltage  $V_{\text{OUT}}$  is applied to, diode DD may be conductive. If so, a PN diode-drop voltage of  $1V_{\text{BE}}$  30 occurs across diode DD, and voltage  $V_{\text{OUT}}$  rises up to a logical "1" of at least  $1V_{\text{BE}}$  below  $V_{\text{CC}}$ . 30 A significant drawback of this inverter is that there is a rather large output voltage swing since transistor QB turns off when voltage  $V_{\text{OUT}}$  rises to logical "1". This voltage swing limits the output switching speed. Another disadvantage is that transistors QA and QB are initially both in deep saturation as voltage  $V_{IN}$  is switched from logical "1" to logical "0", and their bases 35 therefore contain large amounts of stored charge. In transistors not made by gold-doped 35 processes, these charges take a rather long time to flow to ground compared to the input switching time. As a result, the low-to-high output switching speed is limited by the time needed to discharge transistors QA and QB from deep saturation. Even with gold-doped transistors, the average propagation delay is usually about 3 nanoseconds. Another conventional inverter, this time as disclosed by J. Kane et al. in U.S. Patent 40 3,962,590, is shown in Fig. 2. This TTI inverter contains all of the elements of Fig. 1 plus an NPN bipolar transistor QC having its collector connected to source Vcc and its base and emitter coupled, respectively, to the collector of transistor QA and the anode of diode DD. A Schottky diode DA connected between the base and collector of transistor QA Schottky clamps it. 45 45 Transistor QB is similarly Schottky clamped with a Schottky diode DB. Although Kane et al. do not describe the switching operation of this inverter in detail, it appears to operate as follows: As voltage  $V_{IN}$  is raised to a logical "1" of  $2V_{BE}$ , transistors QA and QB both turn on and saturate. Because they are Schottky clamped, neither normally goes into deep saturation. Instead, both go into "low" saturation where their base-collector junctions 50 are forward biassed, but below the normal fully conductive level. This occurs because diodes DA 50 and DB become conductive and clamp the voltages across the base-collector junctions of transistors QA and QB at a Schottky diode-drop voltage which may be termed a "Vsh" and is normally slightly less than 1VBE. This clamped value of 1VSH is usually not high enough to alllow either of these base-collector junctions to become full conductive in the forward direction. As 55 transistor QB turns on, it actively pulls voltage V<sub>OUT</sub> down. Meanwhile, transistor QC turns off. 55 When voltage V<sub>IN</sub> is brought back down to a logical "O" of 1V<sub>BE</sub> or lower, transistors QA and QB turn off. Transistor QC turns on to actively pull voltage  $V_{\text{OUT}}$  up to a logical "1" of at least  $2V_{\text{BE}}$ below  $V_{cc}$  if diode DD is conductive. By having transistors QA and QB Schottky clamped, less charge must be dissipated from their 60 bases as voltage V<sub>IN</sub> switches from logical "1" to logical "0". This reduces the low-to-high 60 output switching time compared to that of Fig. 1. However, diode DA or DB may not always keep its transistor QA or QB from going into deep saturation. Because of processing variations from transistor to transistor and different doping levels in the collector and base compared to the emitter and base, the base-collector junction may become conductively forward biassed at a 65 voltage less than  $1V_{\text{BE}}$ . Sometimes the base-collector junction becomes conductively forward 65

| 5  | biassed at a voltage of 1V <sub>SH</sub> or less. A Schottky-clamped transistor may also go into deep saturation if its Schottky diode is improperly designed or is operated at a high current level. Moreover, there is a rather sharp bend in the curve of collector-to-emitter voltage as a function of collector current that defines the low and deep saturation regions. In short, a Schottky-clamped transistor may still accumulate a moderately large amount of charge. In addition, the output swing is again rather large since transistor QB turns off during a corresponding switching | 5  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | operation. The average propagation delay for a gate such as that of Fig. 2 is usually about 2 nanoseconds.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 10 | In accordance with the invention, a logic circuit comprising a first bipolar transistor having a base, an emitter, and a collector coupled to a voltage/current source, and a second bipolar transistor having a base coupled to the emitter of the first transistor, an emitter coupled to a constant voltage source, and a collector coupled to the voltage/current source for supplying an output signal is characterized by means for preventing the second transistor from either turning substantially off or normally going into deep saturation.                                            | 10 |

| 15 | Because the second transistor always remains on the output voltage swing occuring during a swiching operation can be less than that which occurs when pull-down/pull-up transistors that switch on and off are employed, as is the case in comparable prior art logic gates, giving a corresponding reduction in the average propagation delay of the circuit.                                                                                                                                                                                                                                      | 15 |

| 20 | Each transistor may be an NPN transistor. The said means then preferably comprises first means for providing positive current from the voltage/current source in a single current-flow direction to the collector of the second transistor and second means for providing positive current from the first means in a single current-flow direction to the base of the second transistor.                                                                                                                                                                                                            | 20 |

| 25 | The first means may comprise a first diode, for example a Schottky diode, having its anode and cathode coupled respectively to the collectors of the first and second transistors, and clamping means for preventing the first transistor from going into deep saturation. The clamping means may comprise a Schottky diode having its anode and cathode connected respectively to the base and collector of the first transistor. As an alternative to the clamping means the first                                                                                                                | 25 |

| 30 | means may include a Schottky diode having its anode and cathode coupled respectively to the base of the first transistor and the collector of the second transistor.  The second means may comprise a further diode, for example a PN diode, having its anode and cathode coupled respectively to the cathode of the first diode and the base of second transistor. (This is the opposite direction to which a Schottky diode would be connected for                                                                                                                                                | 30 |

| 35 | Schottky clamping the second transistor).  An advantage of the present logic circuit is that its average propagation delay can be about 1 nanosecond. This is less than that of otherwise comparable prior art devices. Moreover, the noise margin for both high-to-low and low-to-high switching is an adequate value of about 0.5 volt in a given embodiment. If Schottky diodes are included, the present logic circuit can be such as to perform very well over the temperature range of — 55°C to 150°C. An inverter                                                                           | 35 |

| 40 | constituted by the present logic circuit may occupy as little as 4800 microns² which is smaller than prior art TTL and emitter-coupled logic (ECL) inverters. Such an inverter may also require less power than conventional ECL inverters.  The logic circuit can be used as a building block in the logic portions of numerous types of                                                                                                                                                                                                                                                           | 40 |

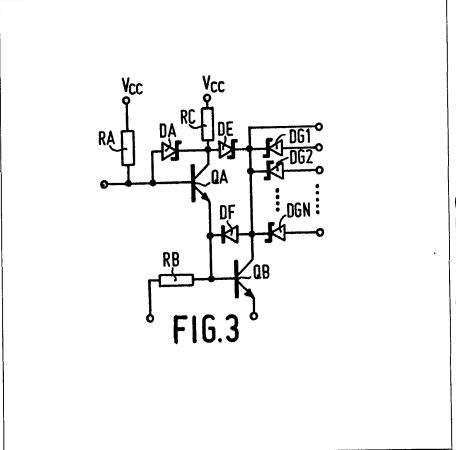

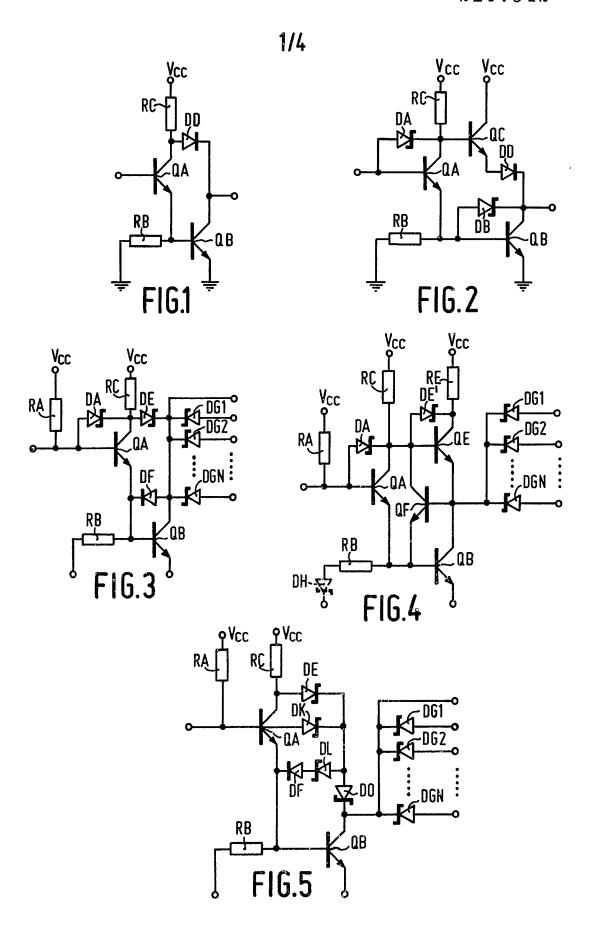

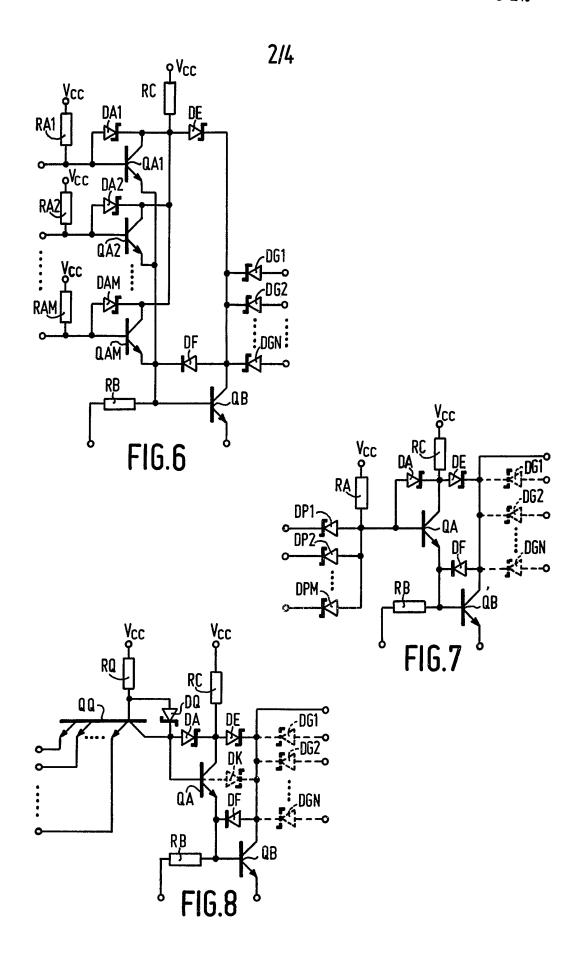

| 45 | integrated circuits. It can have a high fan-out capability and can be generally compatible with TTL systems.  Embodiments of the invention will be described, by way of example, with reference to the accompanying diagrammatic drawings in which:—  Figures 1 and 2 are circuit diagrams of prior art inverting logic gates,                                                                                                                                                                                                                                                                      | 45 |

| 50 | Figure 3 is a circuit diagram of a first embodiment in the form of an inverting logic gate, Figure 4 is a circuit diagram of a variation of the inverter of Fig. 3  Figure 5 is a circuit diagram of another embodiment of the invention in the form of an inverting logic gate,  Figure 6 is a circuit diagram of a NOR logic gate employing the inverter of Fig. 3,                                                                                                                                                                                                                               | 50 |

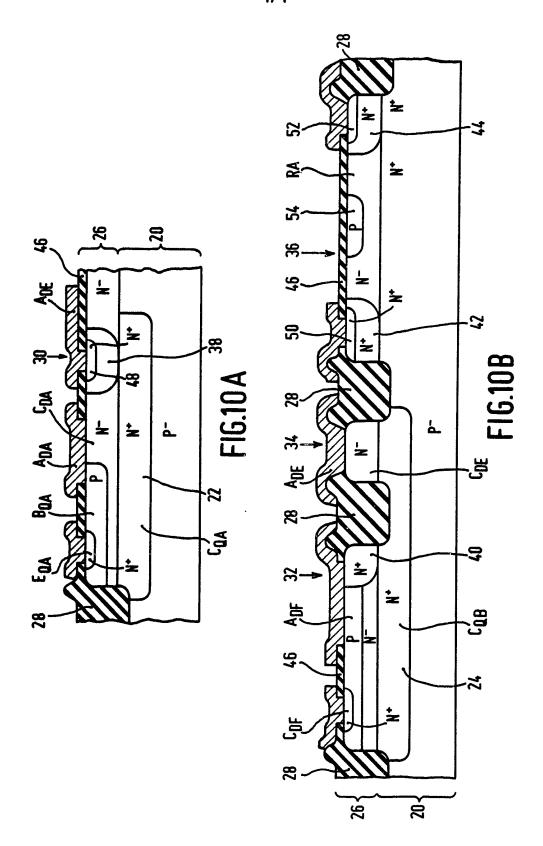

| 55 | Figures 7 and 8 are circuit diagrams of NAND logic gates employing the inverter of Fig. 3, Figure 9 is a topographical view of a possible layout for the inverter of Fig. 3, and Figures 10A and 10B are cross-sectional views of portions of the inverter shown in Fig. 9. Likewise reference symbols are employed in the drawings and in the description of the embodiments to denote corresponding items.                                                                                                                                                                                        | 55 |

| 60 | Referring to the drawings, Fig. 3 illustrates an inverting logic gate having a very high switching speed. Input voltage $V_{IN}$ is applied to the base of silicon NPN bipolar transistor QA whose base and collector are tied to voltage/current source $V_{CC}$ through a resistor RA and a resistor RC, respectively. Aluminium-silicon Schottky diode DA is connected between the base and collector of transistor QA to prevent its base-collector junction from becoming forward biassed more than $1V_{SH}$ which is $0.4-0.7$ volts depending on the diode current and typically is         | 60 |

| 65 | 0.5 volt. The base-collector junction of transistor QA normally does not become fully conductive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65 |

until its base-to-collector voltage V<sub>BCOA</sub> exceeds 1V<sub>SH</sub>. Accordingly, diode DA normally prevents transistor QA from going into deep saturation.

The anide and cathode of an aluminium-silicon Schottky diode DE are connected to the collectors of transistors QA and QB, respectively. The collector of transistor QB is also connected to the anode of a silicon PN diode DF whose cathode is connected to the base of transistor QB. This base is further connected to the emitter of transistor QA and through a resistor RB to a source V<sub>REF</sub> of a constant reference voltage. The emitter of transistor QB is connected to constant voltage source V<sub>REF</sub> which preferably is ground potential.

Output voltage Vout can be taken directly from the collector of transistor QB. Preferably, a 10 series of N output voltages V<sub>OUT1</sub>, V<sub>OUT2</sub>, ... V<sub>OUTN</sub> are taken from the aniodes of N corresponding aluminium-silicon output Schottky diodes DG1, DG2, ... DGN, respectively, whose cathodes are connected to the collector of transistor QB. This arrangement provides both a high fanout and suitable input voltage levels for additional logic gates connected to the inverter of Fig. 3 for receiving voltages V<sub>OUT1</sub>-V<sub>OUTN</sub>.

The inverter of Fig. 3 operates as follows: In the situation where voltage  $V_{\text{REF}}$  is ground potential, the desired logical "1" input value for voltage  $V_{\text{IN}}$  is a threshold value of  $2V_{\text{BE}}$ . For 15 silicon bipolar transistors and silicon PN diodes,  $1V_{BE}$  is 0.6-1.0 volt depending on the current and typically equals 0.8 volt. The desired logical "1" input value exceeds the desired logical "O" input value for voltage VIN by a suitable amount which may be termed the logical "O"

20 input noise margin. To facilitate connection of the present inverter to another logic circuit having the same input/output characteristics as the present inverter, the logical "0" input noise margin preferably equals the corresponding logical "0" output noise margin which is  $1V_{SH}$  as discussed below. Accordingly, the desired logical "0" input value is  $2V_{BE}-V_{SH}$ . The desired output logic levels are the same for each voltage V<sub>OUTJ</sub> where J varies from 1 to N. That is, the desired

25 logical "1" output value is 2VBE (with a suitable logical "1" output noise margin); the desired logical "0" output value is  $2V_{BE}-V_{SH}$ .

When voltage V<sub>IN</sub> is raised from logical "0" to logical "1", transistor QA turns on. This establishes a current path from source Vcc through resistor RC and transistor QA to the base of transistor QB that acts to pull its base voltage up. Transistor QB which was previously on turns 30 on harder. Transistor QA draws current from source Vcc to cause a greater voltage drop across resistor RC. The voltage at the anode of diode DE which was previously conductive drops accordingly. Nonetheless, diode DE remains conductive. Diode DA becomes conductive to Schottky clamp transistor QA.

The voltage at the base of transistor QB is  $V_{BEQB}$  and equals  $1V_{BE}$ . If  $V_{DDA}$  and  $V_{DDE}$  are the 35 conductive voltages across diodes DA and DE, respectively, the voltage at the collector of transistor QB is  $V_{BEQB} + V_{BEQA} - V_{DDA} - V_{DDE}$  and equals  $2V_{BE} - 2V_{SH}$  here. The base-to-collector voltage  $V_{BCQB}$  for transistor QB is therefore  $1V_{BE} - (2V_{BE} - 2V_{SH})$  which is  $2V_{SH} - V_{BE}$  or about 2 volt. This is significantly below the forward voltage needed to make the base-collector junction of transistor QB fully conductive. Transistor QB cannot deeply saturate. Its operation is limited to 40 its low saturation range. In effect diode DE in combination with transistor QA and its Schottky clamp DA act to clamp transistor QB well out of deep saturation. This substantially reduces the

low-to-high output switching time when voltage V<sub>IN</sub> is later brought back down to its logical "O" since the charge that must be dissipated from the base of transistor QB is substantially reduced because it does not approach deep saturation.

During low-to-high input switching, the collector-to-emitter resistance of transistor QB decreases when it turns on harder. This actively pulls each output voltage Vout down to its logical "0" to decrease the high-to-low output switching time. The voltage  $V_{\tiny DDGJ}$  across each diode DDJ is  $1V_{SH}$  while voltage  $V_{OUTJ}$  equals  $V_{DDGJ}$  plus the collector voltage of transistor QB. As a result, voltage  $V_{OUTJ}$  reaches the desired logical "O" outpit value of  $2V_{BE} - V_{SH}$ . Since the desired output 50 logical "1" is  $2V_{BE}$ , the logical "0" output noise margin is  $1V_{SH}$ .

The voltage across diode DF goes to  $-V_{BCQB}$  which is  $1V_{BE}-2V_{SH}$  or about -0.2 volt when voltage V<sub>IN</sub> reaches its logical "1". Diode DF is reverse biassed and therefore inactive at this

As voltage VIN is returned to logical "O", transistor QA turns off. Likewise, diode DA becomes 55 non-conductive. The voltage at the base of transistor QA decreases as it moves toward the nonconductive state. However, transistor QB cannot turn off. As the base voltage for transistor QB drops, diode DF becomes forward biassed and finally conductive until another current path from source V<sub>cc</sub> to the base of transistor QB is established through resistor RC by way of diode DE which remains conductive and diode DF. The current through diode DF to the base of transistor 60 QB keeps it on.

The base voltage for transistor QB is V<sub>BEQB</sub> which again equals 1V<sub>BE</sub>. If V<sub>DDF</sub> is the voltage across diode DF when it is conductive, the collector voltage for transistor  $\overline{QB}$  is  $V_{BEQB} + V_{DDF}$  and equals  $2V_{BE}$  here. Voltage  $V_{BCQB}$  is therefore  $-1V_{BE}$  so that the base collector junction of transistor QB is reversed biassed and it operates in the linear range.

Were diode DF non-existent, there would be no alternative current path to the base of

10

15

20

25

30

35

40

45

50

55

60

transistor QB to keep it on when voltage V<sub>IN</sub> drops to its logical "0". Thus diode DF prevents transistor QB from turning off. This decreases the voltage swing across transistor QB and in turn, reduces the average gate propagation delay. During high-to-low input switching, each voltage V<sub>OUTJ</sub> moves upward as the collector-to-5 emitter resistance of transistor QB increases, causing the current through resistor RC to 5 decrease. Voltage  $V_{\text{OUTJ}}$  can rise as high as  $V_{\text{DDGJ}}$  plus the collector voltage of transistor QB, i.e. to  $2V_{\text{BE}} + 1V_{\text{SH}}$ . However, the desired logical ''1'' output level is  $2V_{\text{BE}}$ . Accordingly the inverter of Fig. 3 provides a logical ''1'' output signal of  $2V_{\text{BE}}$  with a logical ''1'' output noise margin of  $1V_{\text{SH}}$  (which is the same as the logical ''0'' output noise margin). The output voltage swing is 10 the difference between the maximum and minimum values of voltage Vout and here equals 10  $2V_{BE} + V_{SH} - (2V_{BE} - V_{SH})$  which is  $2V_{SH}$  or about 1.0 volt.

Diode DF may be configured in any one of several ways. Preferably, diode DF consists of an NPN bipolar transistor in which its emitter serves as the cathode and its base is tied to its collector to serve as the anode. Alternatively, diode DF may be a conventional two-element 15 diode having a P-type region as the anode and an N-type region as the cathode. 15 Still further, diode DF may consist of the base-emitter junction of an NPN bipolar transistor QF. Fig. 4 shows a circuit diagram of an inverter in which this is the case; transistor QF has its collector tied, in common with the collector of transistor QA, through resistor RC to source  $V_{\rm cc}$ . Insofar as transistor QF is concerned, the operation of the inverter of Fig. 4 is substantially the 20 same as that described above for Fig. 3. 20 Diode DF may be replaced by a Schottky diode connected in the same manner as diode DF. Operation is basically the same as when diode DF is a PN diode except that the logical "1" output noise margin decreases slightly to  $2V_{SH}-V_{BE}$  or about 2.0 volt. This makes the output switching speed slightly greater due to the resulting slightly smaller output voltage swing. 25 Even further, PN diode DF may have one or more additional diodes in series with it. In this case, operation is substantially the same as that described above for Fig. 3, except that the logical "1" output noise margin is greater. If, for example, a single Schottky diode is connected in series with PN diode DF, the logical "1" output noise margin becomes 2V<sub>SH</sub> or about 1.0 volt. This tends to make the output switching speed decrease slightly because of greater output 30 voltage swing, but the provision of the Schottky diode might also tend to make the switching 30 speed increase due to less parasitic capacitance at the collector of transistor QB. As long as diode DE is a Schottky diode, transistor QB never goes into deep saturation irrespective of whether diode DF is a PN diode, is replaced by a Schottky diode, or includes one or more other diodes in series with it. Voltage  $V_{\text{BCQB}}$  goes no higher than  $2V_{\text{SH}}-V_{\text{BE}}$  or about 0.2 35 35 volt so that the base-collector junction never becomes fully conductively forward biassed. In some applications, it may be desirable to substitute a PN diode for Schottky diode DE. In such case, voltage V<sub>BCQB</sub> at input logical "1" becomes 1V<sub>SH</sub>. This is the condition that exists when a transistor is Schottky clamped. Accordingly, transistor QB will be effectively Schottky clamped and normally will not go into deep saturation. The logical "1" output noise margin will 40 be a slightly higher value of 1V<sub>BE</sub>, resulting in a slightly higher propagation delay. Transistor QB 40 otherwise will operate in precisely the same manner as described above for Fig. 3. Where diode DF is also replaced by a Schottky diode or is in series with one or more other diodes, the logical "O" output noise margin will be the same as that described above. When diode DE is replaced with a PN diode it may be configured in any one of several ways. 45 It may be a conventional two-element PN diode or an NPN bipolar transistor in which its emitter 45 is the cathode and its base is connected to its collector to serve as the anode. Alternatively, the PN diode may consist of the base-emitter junction of an NPN bipolar transistor QE having its

collector connected through a resistor RE to source Vcc as shown in Fig. 4. Preferably, a Schottky diode DE' Schottky clamps transistor QE. Aside from the use of diode DE', the 50 operation of the inverter of Fig. 4 with respect to transistor QE is otherwise the same as that described above for the case in which diode DE is replaced with a PN diode.

Table I below summarizes the operating characteristics of the embodiment and the principal variations to it. The entries "SH" and "PN" for the category "DE" indicate the cases where diode DE is a Schottky diode or is replaced by a PN diode, respectively. Likewise, the entries "PN", "SH", and "PN + SH" for the category "DF" indicate the cases where diode DF is a PN diode, is replaced by a Schottky diode, or is in series with a Schottky diode, respectively.

30

35

40

45

50

65

35

|    | ~ . | _        |   |

|----|-----|----------|---|

| ΙΔ | BL  | <b>j</b> | • |

|    | u   |          |   |

| _  | DE | DF      | $V_{IN}$ | $V_{\text{out}}$ | $V_{BCQB}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Noise Margin                                              | 5  |

|----|----|---------|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----|

| 5  | SH | PN      | 1<br>0   | 0                | 2V <sub>SH</sub> -V <sub>BE</sub><br>-V <sub>BE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>sH</sub>                                           | J  |

| 10 | SH | SH      | 1<br>0   | 0<br>1           | $\begin{array}{l} 2V_{\text{SH}} - V_{\text{BE}} \\ -V_{\text{SH}} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{SH} = V_{SH} - V_{BE}$                                | 10 |

|    | SH | PN + SH | 1<br>0   | 0<br>1           | $\begin{array}{l} 2V_{\mathtt{SH}} - V_{\mathtt{BE}} \\ - V_{\mathtt{BE}} - V_{\mathtt{SH}} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ${\sf V}_{\sf SH}$ $2{\sf V}_{\sf SH}$                    |    |

| 15 | PN | PN      | 1<br>0   | 0<br>1           | $egin{array}{c} oldsymbol{V}_{\mathtt{SH}} \ -oldsymbol{V}_{\mathtt{BE}} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $oldsymbol{V}_{\mathtt{BE}}$ $oldsymbol{V}_{\mathtt{SH}}$ | 15 |

| 20 | PN | SH      | 1<br>0   | 0<br>1           | $egin{array}{c} egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}$ | ${\sf V}_{\sf BE} \ {\sf 2V}_{\sf SH} {\sf -V}_{\sf BE}$  | 20 |

|    | PN | PN + SH | 1<br>0   | 0                | $V_{SH}$ $-V_{BE}$ $-V_{SH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>BE</sub> 2V <sub>SH</sub>                          | 20 |

25 Referring again to Fig. 4, an aluminium-silicon Schottky diode DH is optionally included between resistor RB and source V<sub>REF</sub>. Diode DH in combination with resistor RB acts to turn off transistor QB in certain high-speed switching operations.

Figure 5 shows another inverting logic gate of very high switching speed. This inverter contains all the elements of Fig. 3 except that transistor QA is not Schottky clamped by means of diode DA. Instead, the base of transistor QA is connected to the anode of an aluminium-silicon Schottky diode DK whose cathode is connected to the cathode od diode DE. An aluminium-silicon Schottky diode DL is connected in series with diode DF. Another aluminium-silicon Schottky diode DO has its anode connected to the anode of diode DL and its cathode connected to the collector of transistor QB.

The inverter of Fig. 5 operates similarly to the inverter of Fig. 3. The input and output logical levels are the same. Transistor QB is continuously on and does not go into deep saturation. Diode DE is always conductive as long as power is supplied to the inverter.

When voltage  $V_{IN}$  is brought to logical "1", transistor QA turns on. Current from source  $V_{CC}$  flows through transistor QA to the base of transistor QB to turn it on harder. Diode DK becomes 40 conductive while diode DO which was conductive remains conductive.

The collector voltage of transistor QB is V<sub>BEQB</sub> + V<sub>BEQA</sub>-V<sub>DDK</sub>-V<sub>DDO</sub> which again equals 2V<sub>BE</sub>-2V<sub>SH</sub> (V<sub>DDK</sub> and V<sub>DDO</sub> are the conductive voltages across diodes DK and DO respectively). Accordingly, voltage V<sub>BCQB</sub> is 2V<sub>SH</sub>-V<sub>BE</sub> just as in the inverter of Fig. 3. Again, transistor QB cannot go into deep saturation. Its operation is limited to its low saturation range. In effect, diodes DK and DO in combination with transistor QA clamp transistor QB well out of deep saturation. Diodes DF and DL are non-conductive. As transistor QB turns on harder, it actively pulls each voltage V<sub>OUTJ</sub> down to its logical "O". The logical "O" output noise margin is again 1V<sub>SH</sub>.

down to its logical ''0''. The logical ''0'' output noise margin is again  $1V_{SH}$ .

When voltage  $V_{IN}$  is returned to logical ''0'', transistor QA turns off and diode DK becomes non-conductive. As the base voltage for transistor QA drops, diodes DF and DL become conductive to establish an alternative current path from source  $V_{CC}$  through them to the base of transistor QB. The current flowing through this path keeps transistor QB on. The collector voltage for transistor QB is  $V_{BEQB} + V_{DDF} + V_{DDL} - V_{DDO}$  which again is  $2V_{BE}$ . ( $V_{DDI}$  is the conductive voltage for diode DDL.) As with Fig. 3, each voltage  $V_{OUTJ}$  rises to its logical ''1'' of  $2V_{BE}$  with a logical ''1'' output noise margin of  $1V_{SH}$ .

The inverter of Fig. 5 can provide a slightly greater switching speed than that of Fig. 3 at the cost of adding diodes DL and DO and using diode DK instead of diode DA.

The inverter circuits described can be used as basic building blocks for more advanced logic gates. Fig. 6 illustrates a multi-input NOR gate employing the basic inverter of Fig. 3. Instead of transistor QA, this NOR gate has M transistors QA1, QA2 . . . QAM having their simple emitters connected in common to the base of transistor QB and having their single collectors connected in common through resistor RC to source V<sub>CC</sub>. Each transistor QAI, where I varies from 1 to M, receives a corresponding input signal V<sub>INI</sub> at its base which is coupled through a corresponding resistor RAI to source V<sub>CC</sub>. Likewise, each transistor QAI is Schottky clamped with

a corresponding Schottky diode DAI.

The NOR gate operates basically in the same manner and at the same logical levels as the

|     | inverter of Fig. 3. When all voltages $V_{\text{INI}} - V_{\text{INM}}$ go to logical "0", transistors QA1-QAM all turn off. Diode DF becomes conductive to provide a current path from source $V_{\text{CC}}$ to the base of transistor QB to prevent it from turning off. Each voltage $V_{\text{OUTJ}}$ rises to logical "1". When any |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | voltage V <sub>INI</sub> is raised to logical "1", corresponding transistor QAI turns on to cause diode DF to                                                                                                                                                                                                                             |    |

| 5   | become non-conductive. Current from source V <sub>cc</sub> is supplied through this transistor QAI to the                                                                                                                                                                                                                                 | 5  |

| U   | base of transistor QB which turns on harder but does not go into deep saturation. Voltage V <sub>out</sub>                                                                                                                                                                                                                                | •  |

|     | drops to logical "O".                                                                                                                                                                                                                                                                                                                     |    |

|     | Figure 7 shows a multi-input NAND logic gate in which the inverter of Fig. 3 is the basic                                                                                                                                                                                                                                                 |    |

|     | building block. In this NAND gate, the anodes of M aluminium-silicon input Schottky diodes                                                                                                                                                                                                                                                |    |

| 10  | DP1, DP2, DPM are connected to the base of transistor QA. Each input voltage V <sub>INI</sub> applied                                                                                                                                                                                                                                     | 10 |

| 10  | to the cathode of corresponding diode DPI is $1V_{SH}$ lower than the voltage ( $V_{IN}$ of Fig. 3) at the                                                                                                                                                                                                                                | 10 |

|     | base of transistor QA when diode DPI is conductive. The output signal, which should also be                                                                                                                                                                                                                                               |    |

|     |                                                                                                                                                                                                                                                                                                                                           |    |

|     | $1V_{SH}$ lower so as to be compatible with other logic gates connected to this NAND gate, is voltage $V_{OUT}$ taken directly from the collector of transistor QB. In some applications—e.g. where                                                                                                                                       |    |

| 15  |                                                                                                                                                                                                                                                                                                                                           | 15 |

| 15  | this NAND gate is the last of a series of logic gates-it may be desirable or necessary to take the                                                                                                                                                                                                                                        | 10 |

|     | output signal(s) from one or more Schottky diodes connected to the collector of transistor QB.                                                                                                                                                                                                                                            |    |

|     | For this reason, Fig. 7 shows diodes DG1-DGN in dotted line form for providing output voltages                                                                                                                                                                                                                                            |    |

|     | V <sub>OUT1</sub> -V <sub>OUTN</sub> . Except in unusual situations, the NAND gate normally contains either input diodes                                                                                                                                                                                                                  |    |

| 20  | DP1-DPM or output diodes DG1-DGN but not both sets of diodes because the set not included                                                                                                                                                                                                                                                 | 20 |

| 20  | forms either the output diodes to a preceding logic gate or the input diodes to a following gate.                                                                                                                                                                                                                                         | 20 |

|     | The NAND gate of Fig. 7 operates basically in the same manner as the inverter of Fig. 3. The                                                                                                                                                                                                                                              |    |

|     | desired logical "O" and logical "1" levels are $2V_{BE}-2V_{SH}$ and $2V_{BE}+V_{SH}$ , respectively. The                                                                                                                                                                                                                                 |    |

|     | resistance of resistor RA is chosen appropriately to match the logical "1" input level. When any                                                                                                                                                                                                                                          |    |

| 25  | voltage $V_{\text{INI}}$ is at logical "O", corresponding diode DPI conducts so as to cause a sufficiently large voltage drop across resistor RA to turn transistor QA off. Transistor QB then operates as                                                                                                                                | 25 |

| 25  | described above for Fig. 3. When all diodes DP1–DPM are at logical "1", the current through                                                                                                                                                                                                                                               | 25 |

|     | resistor RA decreases to reduce its voltage drop sufficiently to turn transistor QA on. Transistor                                                                                                                                                                                                                                        |    |

|     | QB again operates as described for Fig. 3.                                                                                                                                                                                                                                                                                                |    |

|     | Figure 8 illustrates another multi-input NAND logic gate in which the inverter of Fig. 3 is the                                                                                                                                                                                                                                           |    |

| 30  | basic building block. In addition to the basic elements of Fig. 3, this NAND gate contains a                                                                                                                                                                                                                                              | 30 |

| 30  | multiple-emitter transistor QQ having its collector connected to the base of transistor QA. The                                                                                                                                                                                                                                           | 00 |

|     | base of transistor QQ is tied to source V <sub>cc</sub> through a resistor RQ which replaces resistor RA of                                                                                                                                                                                                                               |    |

|     | Fig. 3. A Schottky diode DQ Schottky clamps transistor QQ which has M emitters, each of                                                                                                                                                                                                                                                   |    |

|     | which receives one of M input signals $V_{IN1}$ , $V_{IN2}$ , $V_{INM}$ . The output signal is normally voltage                                                                                                                                                                                                                           |    |

| 35  | V <sub>out</sub> from the collector of transistor QB. Diodes DG1-DGN are illustrated in dotted line form for                                                                                                                                                                                                                              | 35 |

| 00  | the situations in which the output signal(s) must be higher. Diode DK is also optionally included                                                                                                                                                                                                                                         |    |

|     | in the NAND gate to replace diode DA in the manner generally described above for Fig. 5.                                                                                                                                                                                                                                                  |    |

|     | Each emitter-base junction of transistor QQ functions basically in the same manner as one of                                                                                                                                                                                                                                              |    |

|     | input diodes DP1-DPM of the NAND gate of Fig. 7 except that each input voltage 1V <sub>INI</sub> is                                                                                                                                                                                                                                       |    |

| 40  | $1V_{BE}$ – $1V_{SH}$ lower than the base voltage ( $V_{IN}$ of Fig. 3) of transistor QA because transistor QQ is                                                                                                                                                                                                                         | 40 |

| . • | Schottky clamped. Accordingly, the desired logical "1" level is $1V_{BE} + 1V_{SH}$ at the input and                                                                                                                                                                                                                                      |    |

|     | output. The desired logical "O" level is the minimum value of voltage V <sub>out</sub> . When diode DK is                                                                                                                                                                                                                                 |    |

|     | absent, the desired logical "0" value is $2V_{BE}-2V_{SH}$ . which is $1V_{SH}$ lower than that of Fig. 3.                                                                                                                                                                                                                                |    |

|     | Transistors QA and QB are controlled in the same manner as described above for Fig. 3. The                                                                                                                                                                                                                                                |    |

| 45  | output noise margins are, however, slightly different because of the different logical levels.                                                                                                                                                                                                                                            | 45 |

|     | When diode DK is present (and diode DA is preferably absent), the desired logical "O" level is                                                                                                                                                                                                                                            |    |

|     | 2V <sub>BF</sub> -2V <sub>SH</sub> . Transistor QA is controlled in substantially the same manner as described above for                                                                                                                                                                                                                  |    |

|     | Fig. 5. Transistor QB, however, operates somewhat differently. When voltage V <sub>out</sub> goes to                                                                                                                                                                                                                                      |    |

|     | logical "1", voltage V <sub>BCQB</sub> is again - 1V <sub>BE</sub> so that transistor QB operates in the linear range, but,                                                                                                                                                                                                               |    |

| 50  | when voltage V <sub>out</sub> goes to logical "O", voltage V <sub>BCQB</sub> is clamped at 1V <sub>SH</sub> higher than described                                                                                                                                                                                                         | 50 |

|     | above for Fig. 3 or 5. In particular, voltage $V_{BCQB}$ is $1V_{SH}-1V_{BE}$ which is negative so that the                                                                                                                                                                                                                               |    |

|     | base-collector junction of transistor QB is reverse-biassed and it does not saturate at all. In short                                                                                                                                                                                                                                     |    |

|     | transistor QB always operates in the linear range when diode DK is employed in the NAND gate                                                                                                                                                                                                                                              | *  |

|     | of Fig. 8. The output voltage swing is 1V <sub>SH</sub> which is one half of that in Fig. 3. The output noise                                                                                                                                                                                                                             |    |

| 55  | margins are likewise about one half of those of Fig. 3.                                                                                                                                                                                                                                                                                   | 55 |

|     | Table II summarizes the operating characteristics for the NAND gate of Fig. 8.                                                                                                                                                                                                                                                            |    |

|     |                                                                                                                                                                                                                                                                                                                                           |    |

25

30

35

40

45

50

| $T\Delta$ | RI | F | 11 |

|-----------|----|---|----|

|           |    |   |    |

|    | TABLE II  |             |                  |                   |                                   |                                                                                        |    |

|----|-----------|-------------|------------------|-------------------|-----------------------------------|----------------------------------------------------------------------------------------|----|

| 5  | DA        | DK          | V <sub>out</sub> | V <sub>BCOA</sub> | V <sub>BCQB</sub>                 | Noise Margin                                                                           | 5  |

|    |           |             | 0                | $V_{\text{SH}}$   | 2V <sub>SH</sub> -V <sub>BE</sub> | 3V <sub>SH</sub> -V <sub>BE</sub>                                                      | _  |

| 10 | Present   | Absent      | 1                |                   | $-V_{BE}$                         | $V_{BE}-V_{SH}$                                                                        |    |

|    | Absent    | Present     | 0                | 0                 | $V_{SH} - V_{BE}$                 | $2V_{SH}-V_{BE}$                                                                       | 10 |

|    |           |             | 1                |                   | $-V_{BE}$                         | $V_{BE}-V_{SH}$                                                                        |    |

| 15 | If transi | stor QQ has | s only on        | e emitter         | (or, equivale<br>8 functions a    | ntly, if all of voltages V <sub>IN1</sub> –V <sub>INM</sub> but one are s an inverter. | 15 |

held at logical "1"), the circuit of Fig. 8 fu

Methods for manufacturing the various elements of the circuits described are well known in the semiconductor art. Preferably, each logic gate is fabricated according to conventional planar processing techniques using oxide isolation to separate active semiconductor regions.

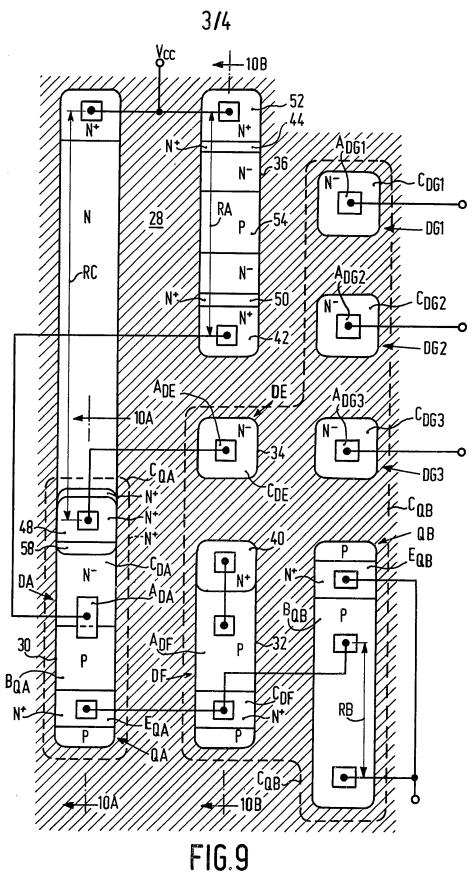

Figure 9 shows a plan view of a possible layout for the inverter of Fig. 3 when it is manufactured according to planar techniques using oxide isolation. In particular, Fig. 9 shows the P-type and N-type regions along the top surface of the inverter below overlaying insulating material and metallic electrical connections. The overlying insulating material is not shown at all. The area shaded in diagonal lines indicates insulating material separating the various active 25 semiconductor regions from one another. The overlying metallic connections are indicated as thick lines extending from the various contact windows schematically depicted as rectangles or

squares. "A" and "C" followed by a subscript which is the symbol for a diode indicate its anode and cathode, respectively. "B", "E", and "C" followed by a subscript which is a symbol for a transistor indicate its base, emitter, and collector, respectively. Three output diodes DG1, 30 DG2, and DG3 are shown in Fig. 9. The size of this inverter is approximately 48 microns by

100 microns.

To further illustrate the construction of the logic gate of Fig. 3, Figs. 10A and 10B depict cross-sectional views of portions of the layout of Fig. 9. The cross-sections are taken through the planes indicated by arrows 10A and arrows 10B in Fig. 9. All of the elements of the inverter of 35 Fig. 3 not shown in Figs. 10A and 10B as well as all of the other transistors, resistors, diodes electrical connections, and other elements of the logic circuit in which it is included are preferably fabricated in the manner described below.

Conventional masking, etching and cleaning techniques, which are well known in the art, are employed in creating the various P-type and N-type regions shown in Figs. 10A and 10B. To 40 simplify the discussion, references to the masking, etching, cleaning and other well-known steps

in the semiconductor art are omitted from the following fabrication discussion.

Boron is utilized as the P-type impurity for creating the various regions of P-type conductivity on a semiconductor wafer. Phosphorous, arsenic, and antimony are used selectively as the complementary N-type dopants. Other appropriate impurities may be used in place of these 45 dopants. In many of the diffusion steps, an impurity may alternatively be introduced to the wafer by ion implantation or vice versa.

The starting material is a P-type monocrystalline silicon substrate having a thickness indicated by reference numeral 20 and a resistivity of 7-15 ohm-centimetres. An N-type impurity (antimony) is selectively diffused into the upper surface of the substrate to form N + regions 22 50 and 24 having a depth of 2.5-3.0 microns and a sheet resistance of approximately 25 ohms/square. The N-type portions  $C_{\text{QA}}$  and  $C_{\text{QB}}$  of regions 22 and 24, respectivley, remaining after subsequent processing steps serve as the collectors for transistors QA and QB, respectively. An N-epitaxial layer having an original thickness of about 1.2 microns indicated by reference

numeral 26 is then grown over the upper surface of the substrate, including over N + regions 55 22 and 24. This epitaxial layer has an original resistivity of approximately 0.5 ohm-centimetre. Oxide-isolation regions 28 having a depth of about 1.3-1.4 microns are then formed according to conventional techniques through the epitaxial layer and partially into the substrate to define active semiconductor regions 30, 32, 34, and 36 and electrically isolate them from one another and from other such active semiconductor regions on the wafer.

An N-type impurity (phosphorous) is selectively ion implanted at an energy of 50 kiloelectron volts and a dosage of 1.4 × 1015 ions/centimetre2 to define deep N + regions 38, 40, 42, and 44. A thin electrically insulating layer 46 consisting of silicon dioxide and silicon nitride is then formed at the top of the wafer. The silicon dioxide is 500 angstroms in thickness while the overlying silicon nitride is 700 angstroms in thickness. After selectively etching oxynitride layer

65 46 to form windows through it, an N-type impurity (arsenic) is diffused into the epitaxial layer

55

60

10

20

25

30

35

45

50

through these windows to define shallow N + regions  $E_{QA}$ , 48,  $C_{DF}$ , 50, and 52 having a sheet resistance of about 30 ohms/square. A p-type impurity (boron) is then selectively ion implanted at an energy of 50 kiloelectron volts and a dosage of  $1.5 \times 10^{14}$  ions/centimetre² through lsyer 46 to form P regions  $B_{QA}$ ,  $A_{DF}$ , and 54. The structure is then annealed for 25–30 minutes at 1000°C to cause the various impurities to diffuse to the locations generally shown in Figs. 10A and 10B.

Regions  $B_{QA}$  and  $E_{QA}$  are the base and emitter, respectively, for transistor QA. The remaining N-portion  $C_{DA}$  of the epitaxial layer between regions  $B_{QA}$  and 38 in island 30 serves as the cathode for diode DA. Deep N + region 38 in combination with shallow contact N + region 48 to connect the collector  $C_{QA}$  of transistor QA to the anode  $A_{DE}$  of diode DE. Diode DF is a transistor in which the cathode is emitter region  $C_{DF}$  while the anode is base region  $A_{DF}$  connected by way of N + collector region 40 to the collector  $C_{QB}$  of transistor QB. The remaining N-portion  $C_{DE}$  of the epitaxial layer in island 34 is the cathode for diode DE. The remaining N-portion of the

epitaxial layer in island 36 forms resistor RA. Deep N + regions 42 and 44 in combination with

15 shallow N + contact regions 50 and 52, respectively, serve as connections for resistor RA while

15 P region 54 "pinches off" resistor RA to control its resistance.

A pattern of leads indicated by diagonal-line shading is formed according to conventional

techniques over the contact windows down to the underlying semiconductor regions, over the remaining portions of insulation layer 46 and over oxide-isolation regions 28 to connect the conductive regions in the desired manner. Each lead consists of a thin lower layer of platinum silicide over the underlying silicon, a thin intermediate layer of titanium-tungsten, and an upper layer of aluminium. Lead A<sub>DE</sub> forms the anode for diode DE. Lead A<sub>DA</sub> forms the anode for diode DA and also serves as the electrical connection to base B<sub>OA</sub> of transistor QA. The structure in Figs. 10A and 10B is then finished in a conventional manner. In the final structure, resistor RA is 20 kiloohms, resistor RB is 3 kiloohms, and resistor RC is 10 kiloohms. Source V<sub>CC</sub> is 5.0 volts.

While the invention has been described with reference to particular embodiments, the description is solely for the purpose of illustration and various modifications, changes and applications may be made by those skilled in the art. For example, semiconductor materials of opposite conductivity type to those described above might be employed to accomplish the same results.

## **CLAIMS**

- 1. A logic circuits comprising a first bipolar transistor having a base for receiving an input signal, an emitter, and a collector coupled to a voltage/current source; and a second bipolar transistor having a base coupled to the emitter of the first transistor, an emitter coupled to a constant voltage source, and a collector coupled to the voltage/current source for supplying an output signal; characterized by means for preventing the second transistor from either turning substantially off or going into deep saturation.

- A logic circuit as claimed in Claim 1 characterized in that earth transistor is an NPN

transisitor.

- A logic circuit as claimed in Claim 2 characterized in that the means comprises first

means for providing positive current from the voltage/current source in a single current flow

direction to the collector of the second transistor; and second means for providing positive

current from the first means in a single current-flow direction to the base of the second

transistor.

- 4. A logic circuit as claimed in Claim 3 characterized in that the first means comprises a first diode having its anode and cathode coupled respectively to the collectors of the first and second transistors.

- 50 5. A logic circuit as claimed in Claim 4 characterized in that the first diode is a Schottky diode.

- 6. A logic circuit as claimed in Claim 4 or Claim 5 characterized in that the first means includes clamping means for preventing the first transistor from going into deep saturation.

- 7. A logic circuit as claimed in Claim 6 characterized in that the clamping means comprises

55 a Schottky diode having its anode and cathode connected respectively to the base and collector of the first transistor.

- 8. A logic circuit as claimed in Claim 4 or Claim 5 characterized in that the first means includes a Schottky diode having its anode and cathode coupled respectively to the base of the first transistor and the collector of the second transistor.

- 9. A logic circuit as claimed in Claim 8, characterized in that a diode having its cathode connected to the collector of the second transistor is included between said collector and both said first diode and the Schottky diode specified in Claim 8.

- 10. A logic circuit as claimed in any of Claims 4 to 9 characterized in that the second means comprises a further diode having its anode and cathode coupled respectively to the cathode of 65 the first diode and the base of the second transistor.

65

10

15

20

the first diode and the base of the second transistor.

- 11. A logic circuit as claimed in Claim 10 characterized in that the further diode is a PN diode.

- 12. A logic circuit as claimed in Claim 11 characterized in that the second means includes a5 Schottky diode in series with the further diode.

- 13. A logic circuit as claimed in any preceding Claim, constructed to function as an inverter.