(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-234613

(P2011-234613A)

(43) 公開日 平成23年11月17日(2011.11.17)

(51) Int.Cl.

HO2M 3/28 (2006.01)

F 1

HO2M 3/28

H

テーマコード(参考)

5H730

審査請求 未請求 請求項の数 40 O L 外国語出願 (全 53 頁)

(21) 出願番号 特願2011-94899 (P2011-94899)

(22) 出願日 平成23年4月21日 (2011.4.21)

(31) 優先権主張番号 12/770,478

(32) 優先日 平成22年4月29日 (2010.4.29)

(33) 優先権主張国 米国(US)

(71) 出願人 511098541

パワー・インテグレイションズ・インコーポレイテッド

アメリカ合衆国・カリフォルニア・95138・サン・ノゼ・ヘルヤー・アヴェニュー

5245

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】絶縁された出力を検知するための装置および方法

## (57) 【要約】

【課題】絶縁された出力を検知するための装置および方法

【解決手段】例示的コントローラは、エネルギー伝達要素および電力変換器の入力に結合される電流コントローラを含む。電流コントローラによって受け取られるように結合されるモード選択信号を生成する制御回路が含まれている。制御回路による、電流コントローラの第1、第2または第3の動作モードの選択に応じて、それぞれ第1、第2または第3の電流が電流コントローラの中で有効になる。第1の電流は実質的にゼロであり、第2の電流は第3の電流より大きく、第3の電流は第1の電流より大きい。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

電力変換器で使用するコントローラであって、

エネルギー伝達要素および前記電力変換器の入力に結合される電流コントローラと、

前記電流コントローラによって受け取られるように結合されるモード選択信号を生成するための制御回路であって、前記制御回路による、前記電流コントローラの第1、第2または第3の動作モードの選択に応じて、それぞれ第1、第2または第3の電流が前記電流コントローラの中で有効になり、前記第1の電流が実質的にゼロであり、前記第2の電流が前記第3の電流より大きく、前記第3の電流が前記第1の電流より大きい制御回路と、

前記制御回路に結合された第1のフィードバック回路であって、前記電流コントローラの前記第2の動作モードの動作期間後の前記第1の動作モードの期間中の前記電力変換器の出力を表す第1のフィードバック信号を生成するように結合された第1のフィードバック回路と、

前記制御回路に結合された第2のフィードバック回路であって、前記電流コントローラの前記第3の動作モードの動作期間後の前記第1の動作モードの期間中の前記電力変換器の前記出力を表す第2のフィードバック信号を生成するように結合された第2のフィードバック回路とを備え、前記制御回路が、前記電力変換器の前記入力から前記電力変換器の前記出力へのエネルギー伝達を制御するために、前記第1および第2のフィードバック信号に応答して前記第1、第2または第3の動作モードの選択を制御するように結合されるコントローラ。

10

20

30

**【請求項 2】**

前記電流コントローラが、前記エネルギー伝達要素および前記電力変換器の前記入力に結合されたトランジスタを備える請求項1に記載のコントローラ。

**【請求項 3】**

前記電流コントローラが、前記モード選択信号に応答して第1、第2および第3の値を有する電圧を前記トランジスタの制御端子に供給するための3段階駆動回路をさらに備える請求項2に記載のコントローラ。

**【請求項 4】**

前記トランジスタが、前記第1の動作モードの期間中オフとなるように結合される請求項2に記載のコントローラ。

30

**【請求項 5】**

前記トランジスタが、前記第2の動作モードの期間中オンとなるように結合される請求項2に記載のコントローラ。

**【請求項 6】**

前記トランジスタが、前記第3の動作モードでは部分放電電流パルスを供給するように結合される請求項2に記載のコントローラ。

**【請求項 7】**

前記トランジスタに結合された静電容量が、前記第3の動作モードでは部分的にのみ放電される請求項2に記載のコントローラ。

**【請求項 8】**

前記トランジスタが、前記第3の動作モードではその飽和領域で動作するように結合される請求項2に記載のコントローラ。

40

**【請求項 9】**

前記第1のフィードバック回路が、前記電力変換器の前記出力を表す反映された信号に応答して前記第1のフィードバック信号を生成するように前記エネルギー伝達要素に結合される請求項1に記載のコントローラ。

**【請求項 10】**

前記第2のフィードバック回路が、前記電力変換器の前記出力を表す反映された信号の減衰振動の一部分に応答して前記第2のフィードバック信号を生成するように前記エネルギー伝達要素に結合される請求項1に記載のコントローラ。

50

**【請求項 1 1】**

電力変換器を制御する方法であって、前記電力変換器の入力から前記電力変換器の出力へのエネルギー伝達を制御するために、第1および第2の動作モードを用いて前記電力変換器の前記入力からの電流を制御するステップであって、前記電力変換器の前記入力に結合された静電容量が、前記第2の動作モードの期間中に完全放電されるステップと、

前記第2の動作モードの動作期間の後の前記第1の動作モードの期間中に前記電力変換器の前記出力を表す第1の量を検知するステップと、

前記電力変換器の前記出力を検知するために、前記第1および第3の動作モードを用いて前記電力変換器の前記入力からの前記電流を制御するステップであって、前記電力変換器の前記入力に結合された前記静電容量が、前記第3の動作モードの期間中に部分的にのみ放電されるステップと、

前記第3の動作モードの動作期間の後の前記第1の動作モードの期間中に前記電力変換器の前記出力を表す第2の量を検知するステップとを含む方法。

**【請求項 1 2】**

前記電力変換器の前記出力を表す前記第1の量の前記検知に応答して、前記コンバータの動作を前記第1および第2の動作モードに維持するステップをさらに含む、請求項11に記載の、電力変換器を制御する方法。

**【請求項 1 3】**

前記第1および第2の動作モードを用いて前記電力変換器の前記入力からの前記電流を制御するステップが、前記第1の動作モードの選択に応答して電流コントローラの第1の電流を有効にするステップと、前記第2の動作モードの選択に応答して前記電流コントローラの第2の電流を有効にするステップであって、前記第2の電流が前記第1の電流より大きく、前記第1の電流が実質的にゼロであるステップとを含む、請求項11に記載の、電力変換器を制御する方法。

**【請求項 1 4】**

前記第1および第3の動作モードを用いて前記電力変換器の前記入力からの前記電流を制御するステップが、前記第3の動作モードの選択に応答して前記電流コントローラの第3の電流を有効にするステップであって、前記第2の電流が前記第3の電流より大きく、前記第3の電流が前記第1の電流より大きいステップをさらに含む、請求項13に記載の、電力変換器を制御する方法。

**【請求項 1 5】**

前記電力変換器の前記出力を表す前記第1の量を検知するステップが、前記電力変換器の前記出力を表す反映された信号を検知するステップを含む請求項11に記載の方法。

**【請求項 1 6】**

前記電力変換器の前記出力を表す前記第2の量を検知するステップが、前記電力変換器の前記出力を表す反映された信号の減衰振動を検知するステップを含む請求項11に記載の方法。

**【請求項 1 7】**

前記第1および第2の動作モードを用いて前記電力変換器の前記入力からの前記電流を制御するステップが、トランジスタのオフとオンを切り換えるステップを含む請求項11に記載の方法。

**【請求項 1 8】**

前記第1および第3の動作モードを用いて前記電力変換器の前記入力からの前記電流を制御するステップが、前記第1の動作モードでトランジスタをオフに切り換えるステップと、前記トランジスタに結合された静電容量を、前記第3の動作モードで、部分的にのみ放電するステップとを含む請求項11に記載の方法。

**【請求項 1 9】**

前記第3の動作モードを用いて前記電力変換器の前記入力からの前記電流を制御するステップが、トランジスタをその飽和領域で動作させるステップを含む請求項11に記載の方法。

10

20

30

40

50

**【請求項 20】**

前記トランジスタがその飽和領域で動作しているとき、前記トランジスタのゲートからソースへの電圧が、前記トランジスタの閾値電圧よりわずかに高いのみである請求項19に記載の方法。

**【請求項 21】**

電力変換器であって、

前記電力変換器の入力と前記電力変換器の出力の間に結合されたエネルギー伝達要素と、

前記エネルギー伝達要素に結合され、第1、第2および第3の動作モードを有する電流コントローラであって、前記第2の動作モードでは前記エネルギー伝達要素を通る第2の電流が有効になり、前記第3の動作モードでは前記エネルギー伝達要素を通る第3の電流が有効になり、前記第1の動作モードでは前記エネルギー伝達要素を通る電流が実質的にゼロであり、前記第2の電流が前記第3の電流より大きく、前記第3の電流が実質的にゼロより大きい電流コントローラと、

前記電流コントローラ向けに前記第1、第2または第3の動作モードを選択するように前記電流コントローラに結合された制御回路と、

前記制御回路に結合された第1のフィードバック回路であって、前記電流コントローラの前記第2の動作モードの動作期間後の前記第1の動作モードの期間中の前記電力変換器の出力を表す第1のフィードバック信号を生成するように結合された第1のフィードバック回路と、

前記制御回路に結合された第2のフィードバック回路であって、前記電流コントローラの前記第3の動作モードの動作期間後の前記第1の動作モードの期間中の前記電力変換器の前記出力を表す第2のフィードバック信号を生成するように結合された第2のフィードバック回路とを備え、前記制御回路が、前記第1および第2のフィードバック信号に応答して、前記第1、第2または第3の動作モードの選択を制御するように結合される電力変換器。

**【請求項 22】**

前記電流コントローラが、前記エネルギー伝達要素および前記電力変換器の前記入力に結合されたトランジスタを備える請求項21に記載の電力変換器。

**【請求項 23】**

前記電流コントローラが、前記制御回路に応答して第1、第2および第3の値を有する電圧を前記トランジスタの制御端子に供給するための3段階駆動回路をさらに備える請求項22に記載の電力変換器。

**【請求項 24】**

前記トランジスタが、前記第1の動作モードの期間中オフとなるように結合される請求項22に記載の電力変換器。

**【請求項 25】**

前記トランジスタが、前記第2の動作モードの期間中オンとなるように結合される請求項22に記載の電力変換器。

**【請求項 26】**

前記トランジスタが、前記第3の動作モードの期間中、部分放電電流パルスを供給するように結合される請求項22に記載の電力変換器。

**【請求項 27】**

前記トランジスタに結合された静電容量が、前記第3の動作モードの期間中、部分的にのみ放電される請求項22に記載の電力変換器。

**【請求項 28】**

前記トランジスタが、前記第3の動作モードの期間中、その飽和領域で動作するように結合される請求項22に記載の電力変換器。

**【請求項 29】**

前記第1のフィードバック回路が、前記電力変換器の前記出力を表す反映された信号に応答して前記第1のフィードバック信号を生成するように前記エネルギー伝達要素に結合

される請求項21に記載の電力変換器。

【請求項30】

前記第2のフィードバック回路が、前記電力変換器の前記出力を表す反映された信号の減衰振動の一部分に応答して前記第2のフィードバック信号を生成するように前記エネルギー伝達要素に結合される請求項21に記載の電力変換器。

【請求項31】

電力変換器で使用する、入力電圧を受け取るように結合されたコントローラであって、電流コントローラに結合された制御回路であって、前記電流コントローラが、エネルギー伝達要素の1次巻線に結合された第1の端子および前記電力変換器の入力に結合された第2の端子を有し、前記1次巻線に結合された前記第1の端子が1次スイッチングノード静電容量を有し、前記電流コントローラの電流が第1の動作モードの期間中は実質的にゼロであり、第2の動作モードの期間中の前記電流コントローラの前記電流が、前記入力電圧、前記エネルギー伝達要素の前記1次巻線のインダクタンス、および前記電流コントローラが前記第2のモードのままである時間によって実質的に決定され、第3の動作モードの期間中の前記電流コントローラの前記電流が、前記1次スイッチングノード静電容量を部分的に放電するように制御され、前記電流コントローラの前記電流が、前記制御回路による、前記電流コントローラの前記第1、前記第2または前記第3の動作モードの選択に応じてそれぞれ選択される制御回路と、

前記制御回路に結合された第1のフィードバック回路であって、前記電流コントローラの前記第2の動作モードの動作期間後の前記第1の動作モードの期間中の前記電力変換器の出力を表す第1のフィードバック信号を生成するように結合された第1のフィードバック回路と、

前記制御回路に結合された第2のフィードバック回路であって、前記電流コントローラの前記第3の動作モードの動作期間後の前記第1の動作モードの期間中の前記電力変換器の前記出力を表す第2のフィードバック信号を生成するように結合された第2のフィードバック回路とを備え、前記制御回路が、前記電力変換器の前記入力から前記電力変換器の前記出力へのエネルギー伝達を制御するために、前記第1および第2のフィードバック信号に応答して前記第1、第2または第3の動作モードの選択を制御するように結合されるコントローラ。

【請求項32】

前記電流コントローラが、前記1次巻線に結合された第1の端子および前記電力変換器の前記入力に結合された第2の端子を有するトランジスタを備える請求項31に記載のコントローラ。

【請求項33】

前記電流コントローラが、前記制御回路に応答して第1、第2および第3の値を有する電圧を前記トランジスタの制御端子に供給するための3段階駆動回路をさらに備える請求項32に記載の電力変換器。

【請求項34】

前記トランジスタが、前記第1の動作モードの期間中オフとなるように結合される請求項32に記載のコントローラ。

【請求項35】

前記トランジスタが、前記第2の動作モードの期間中オンとなるように結合される請求項32に記載のコントローラ。

【請求項36】

前記トランジスタが、前記第3の動作モードでは部分放電電流パルスを供給するように結合される請求項32に記載のコントローラ。

【請求項37】

前記トランジスタに結合された静電容量が、前記第3の動作モードでは部分的にのみ放電される請求項32に記載のコントローラ。

【請求項38】

10

20

30

40

50

前記トランジスタが、前記第3の動作モードではその飽和領域で動作するように結合される請求項32に記載のコントローラ。

【請求項 39】

前記第1のフィードバック回路が、前記電力変換器の前記出力を表す反映された信号に応答して前記第1のフィードバック信号を生成するように前記エネルギー伝達要素に結合される請求項31に記載のコントローラ。

【請求項 40】

前記第2のフィードバック回路が、前記電力変換器の前記出力を表す反映された信号の減衰振動の一部分に応答して前記第2のフィードバック信号を生成するように前記エネルギー伝達要素に結合される請求項31に記載のコントローラ。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング形式の電源の制御に関する。具体的には、本発明は、出力に対する負荷がないとき最大電力消費量に関する規格を満たさなければならず、さらに、負荷が突然与えられたときにも出力を指定限界の範囲内に維持しなければならない、絶縁された安定化出力を供給する低コストの電源に関する。

【背景技術】

【0002】

スイッチング電源の絶縁された出力電圧を安定化する低コストの解決策は、制御回路に20 対して出力に関する情報を供給するのに、一般にエネルギー伝達要素の絶縁巻線間の電磁結合に頼るものである。制御回路は、一般に、出力にエネルギーを送出するスイッチング事象の直後に出力電圧を表す信号を受け取る。信号は、一般に、光結合素子からではなく、エネルギー伝達要素の1次側基準巻線から受け取られる。このタイプの制御は、「1次側制御」または1次側フィードバックを用いた制御と称されることが多い。

【0003】

これらの解決策は、光結合素子によるコストおよび消費電力を解消するが、スイッチングがない状態では出力電圧を検知することができない。電源の出力に対する負荷がゼロに近づくとき問題が生じる。電源は、ほぼ電力ゼロで、規定された安定化出力電圧を供給しなければならない。このような条件下では、総計の消費電力のかなりの部分は、電源自体の動作で浪費される電力である。外部負荷がほぼゼロという条件下の電源による電力消費を制限する要件により、電源内のダミー内部負荷の使用を思いとどまることになる。ブレードと称されることがあるダミー内部負荷は、電源において、過電圧保護、複数の出力間の変動率の改善、およびスイッチング周波数が最小値以下になることの防止を支援するのに有用であり得る。具体的には、ダミー内部負荷は、電源内部の小さな恒久的最小負荷である。しかし、ダミー内部負荷を用いることの不利点に、ダミー負荷が出力電力として測定されない電力を消費するので、電源の効率が低下することがある。また、コントローラは、追加の内部負荷に電力を供給するためにスイッチングの頻度を増す必要があり、これによって、電源が、その出力に負荷が接続されていないときでさえ余分な電力を消費することになる。これらの欠点を回避するために、スイッチングに固有の損失を低減するように、無負荷条件下のスイッチング事象間の時間を増加することが役に立つ。しかし、このような条件下では、コントローラは、スイッチング事象の比較的長い期間中、出力電圧を検知することができない。

30

【0004】

スイッチング事象の比較的長い時間間隔のうちの1つの期間中に、かなりの負荷が出力に突然与えられると、コントローラが状況に対して対応することできないうちに、出力電圧が、たやすく変動率の指定限界外へ下がる恐れがある。このような状況に対する一般的な対応策は、コントローラが出力を検知できない期間中、与えられる可能性がある負荷が必要とするエネルギーを供給するために、出力に高価な大量の静電容量を追加することである。

40

50

## 【発明の概要】

## 【課題を解決するための手段】

## 【0005】

本発明の、限定的でなく、また網羅的でもない実施形態が以下の図を参照しながら説明され、様々な図面を通じて、別段の定めがない限り、同じ参照数字は同一の部分を指す。

## 【図面の簡単な説明】

## 【0006】

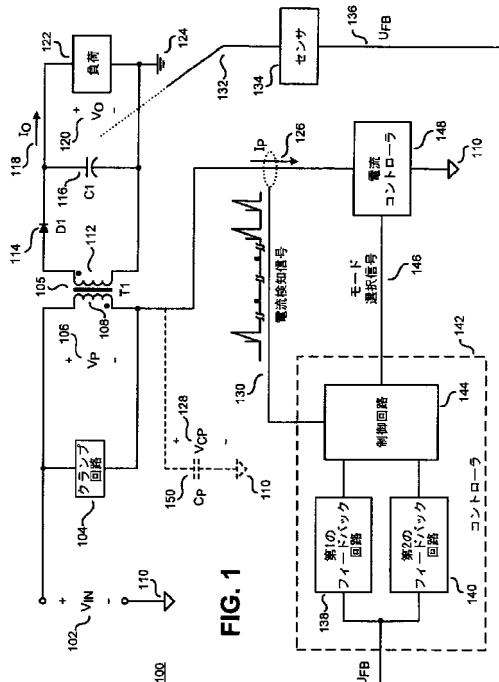

【図1】絶縁された出力の検知を提供する本発明の教示によるコントローラを含む例示的電力変換器を示す図である。

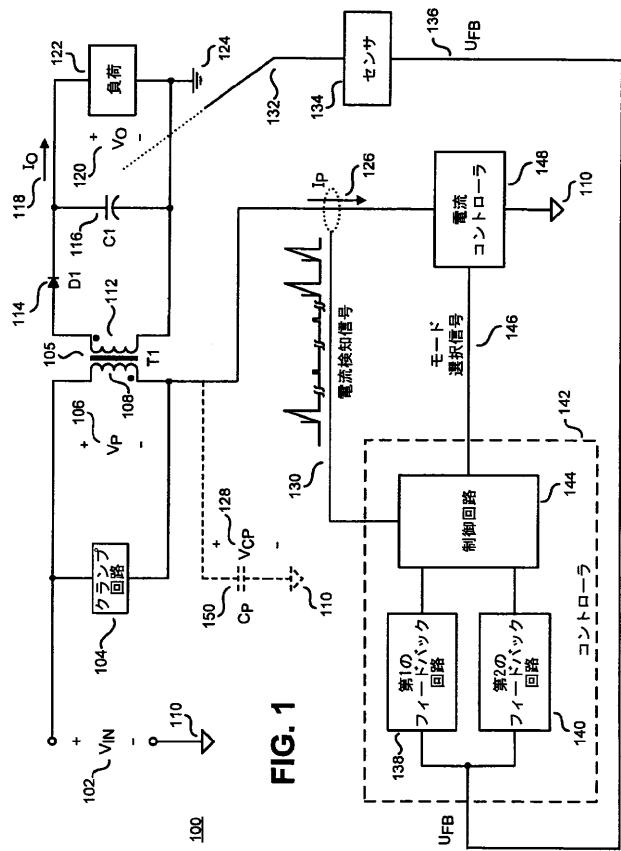

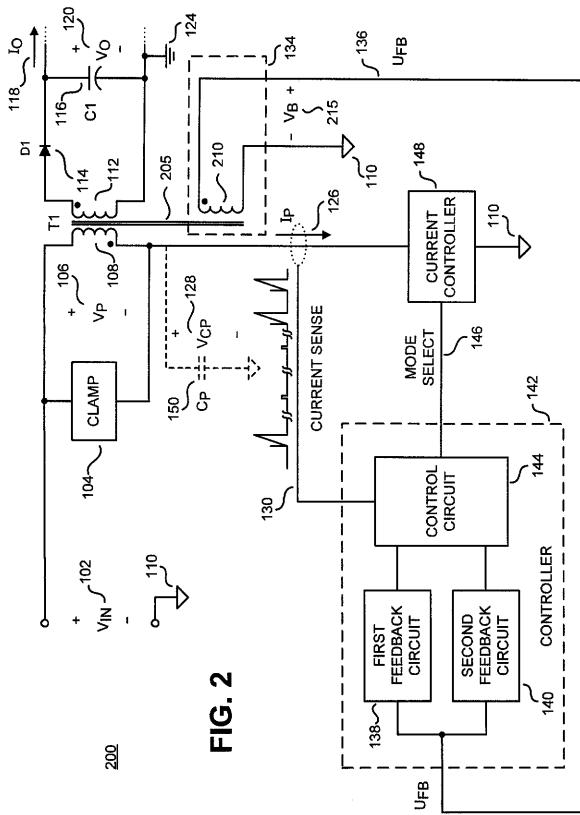

【図2】絶縁された出力の検知を提供する本発明の教示による、出力電圧を検知するのに結合されたインダクタの巻線を使用するコントローラを含む電力変換器の一実施例を示す図である。

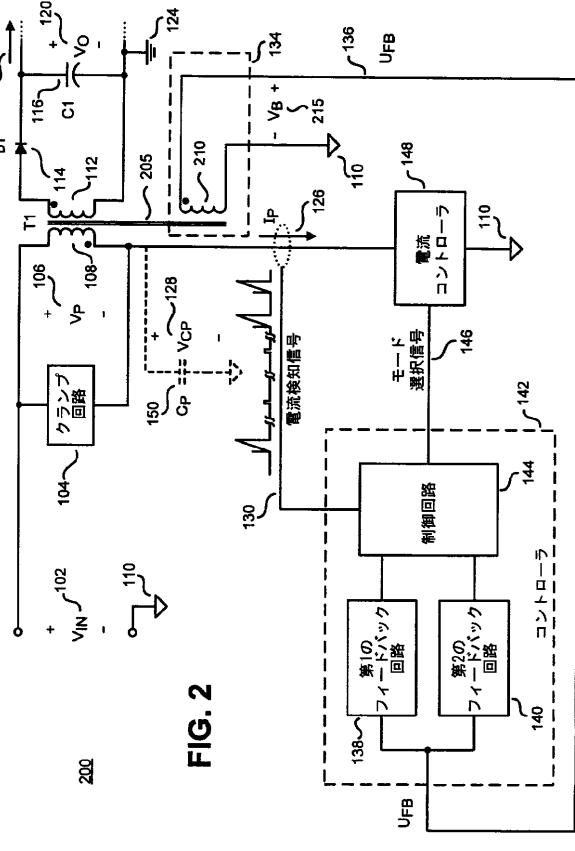

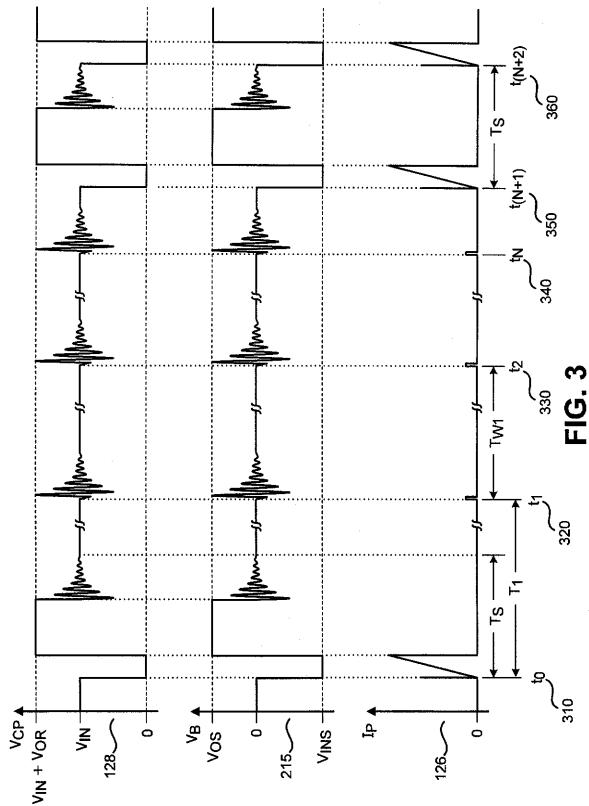

【図3】絶縁された出力電圧の検知を提供する本発明の教示によるコントローラの動作を説明する、例示的電力変換器の電圧波形および電流波形を示す図である。

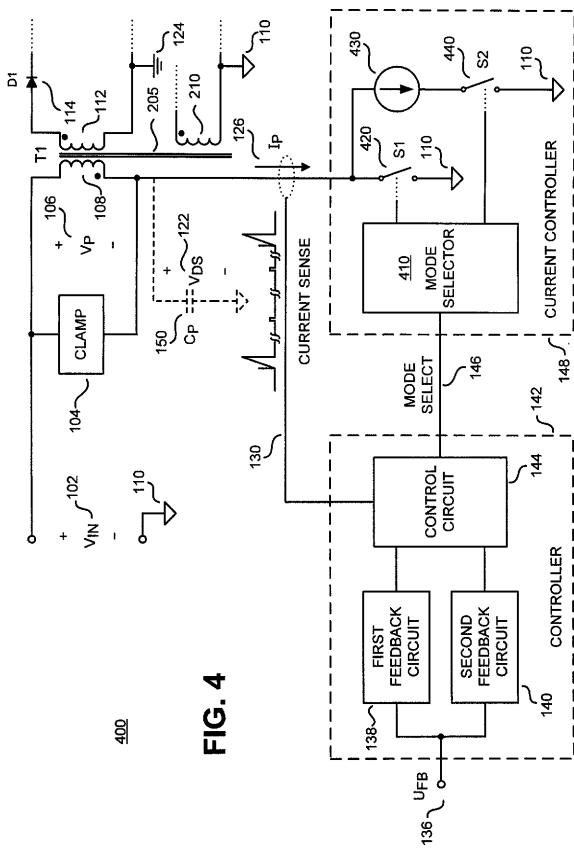

【図4】本発明の教示による電流コントローラの一実施例を説明する電力変換器の一実施例を示す図である。

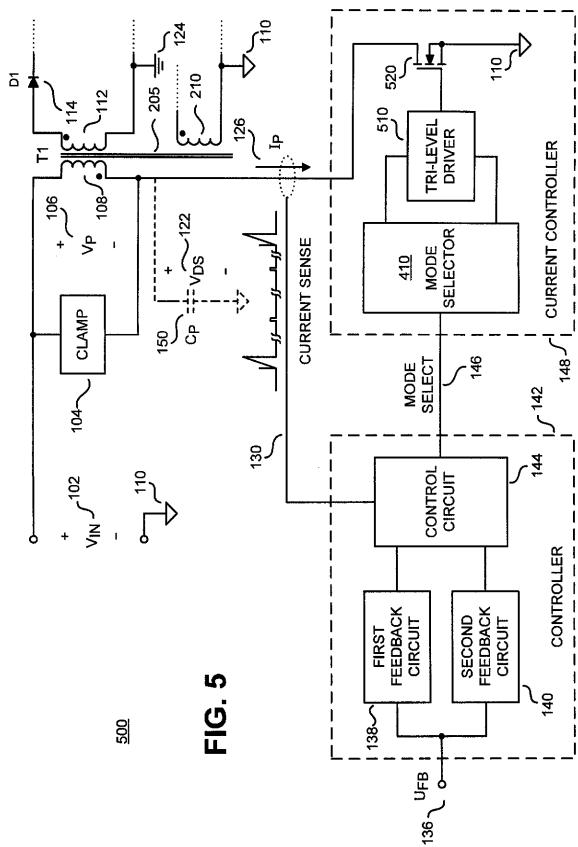

【図5】本発明の教示により、絶縁された出力電圧を検知するためにトランジスタを使用する電流コントローラの別の実施例を説明する電力変換器の一実施例を示す図である。

【図6】絶縁された出力電圧の検知を提供する本発明の教示による電力変換器を制御する方法の一実施例を示す流れ図である。

## 【発明を実施するための形態】

## 【0007】

電力変換器の絶縁された出力の検知を行なう比較的低コストの解決策を提供する、電源コントローラを実施するための方法および装置が開示される。以下の説明では、本発明の十分な理解を提供するために多くの特定の詳細が説明される。しかし、本発明を実施するのに特別な詳細を用いる必要はないということが当業者には明らかであろう。他の例では、本発明が不明瞭になるのを避けるために、周知の材料または方法は詳細には説明されていない。

## 【0008】

本明細書を通じて、「一実施形態」、「ある実施形態」、「一実施例」または「ある実施例」に対する参照は、実施形態または実施例に関連して説明された特定の特徴、構造または特性が、本発明の少なくとも1つの実施形態に含まれることを意味する。したがって、本明細書を通じて、様々な位置における慣用句「一実施形態では」、「ある実施形態では」、「一実施例」または「ある実施例」の出現は、必ずしもすべてが同一の実施形態または実施例を指すわけではない。さらに、特定の特徴、構造または特性は、1つまたは複数の実施形態または実施例の任意の適切な組合せおよび/または副次的組合せで組み合わせられてよい。特定の特徴、構造または特性は、説明された機能をもたらす集積回路、電子回路、組合せ論理回路または他の適切なコンポーネントに含まれ得る。また、添付の図面は当業者に対して説明するためのものであり、図面は必ずしも原寸に比例しないことが理解される。

## 【0009】

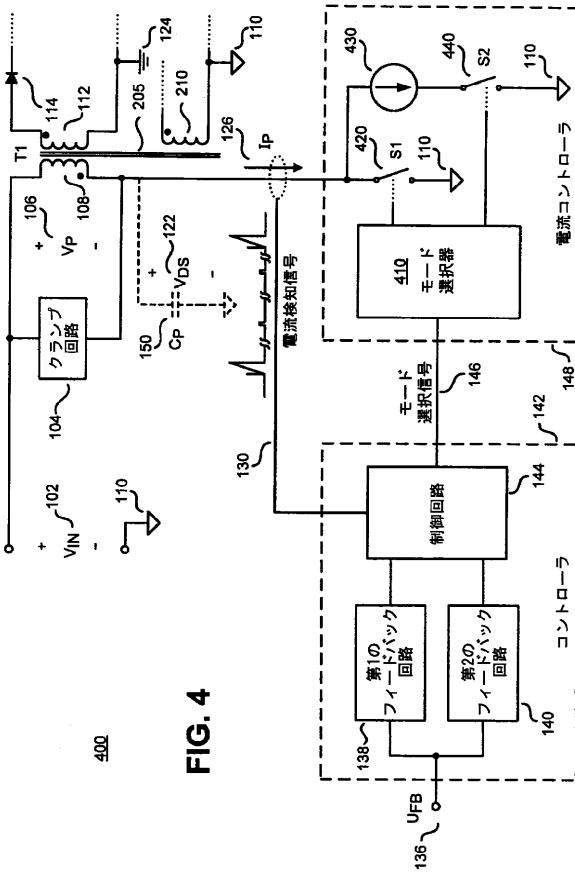

図1は、本発明の教示によるフライバックトポロジを用いたスイッチング電力変換器100の一実施例を全体的に示す概略図である。図示の実施例では、説明のために、電力変換器100はフライバックトポロジを有する電源として示されている。しかし、スイッチング電源向けに他の多くの既知のトポロジおよび構成があることが注目される。図1に示された例示的フライバックトポロジは、本発明の教示による方式を説明するのに適切であり、この方式は、本発明の教示による他のタイプのスイッチングレギュレータにも適合し得ることが理解される。本発明による教示が不明瞭になるのを避けるために、以下により詳細に論じられることになる細部は、図1から省略されている。

## 【0010】

10

20

30

40

50

図1の例示的電力変換器は、電力変換器100の入力における非安定入力電圧 $V_{IN}$  102から電力変換器100の出力における負荷122へのエネルギー伝達を制御する。入力電圧 $V_{IN}$  102は、エネルギー伝達要素T1 105および電流コントローラ148に結合される。図1の実施例では、エネルギー伝達要素T1 105は、1次巻線108および2次巻線112を有する変圧器と称されることがある結合されたインダクタである。図1の実施例では、1次巻線108は入力巻線と見なされてよく、2次巻線112は出力巻線と見なされてよい。電流コントローラ148の最大電圧を制御するために、エネルギー伝達要素T1 105の1次巻線108にクランプ回路104が結合される。

#### 【0011】

図1の実施例では、入力電圧 $V_{IN}$  102は、入力帰路110に対してプラスであり、出力電圧 $V_o$  120は、出力帰路124に対してプラスである。図1の実施例は、入力帰路110および出力帰路124が別々の記号によって示されているので、入力帰路110と出力帰路124の間の直流的絶縁を示す。換言すれば、入力帰路110と出力帰路124の間に直流電圧を印加しても実質的に電流が生じないはずである。したがって、1次巻線108に電気的に結合された回路は、2次巻線112に電気的に結合された回路から直流的に絶縁される。

#### 【0012】

図示の実施例では、電流コントローラ148は、コントローラ142に含まれている制御回路144に応答して、電流を伝導するかまたは電流を伝導しない。電流コントローラ148およびコントローラ142は、集積回路および個別の電気部品を含むことができる。いくつかの実施例では、電流コントローラ148およびコントローラ142は、単一のモノリシック集積回路の中に一緒に一体化され得る。

#### 【0013】

図1の実施例では、電流コントローラ148は、電力変換器100の規定された性能を満たすように、コントローラ142に応答して電流 $I_p$  126を制御する。作動中、電流コントローラ148は、1次巻線108および2次巻線112の中に脈動電流を生成する。2次巻線112の電流は、整流器D1 114によって整流され、次いでコンデンサC1 116によってフィルタリングされて、負荷122において実質的に一定の出力電圧 $V_o$  120または出力電流 $I_o$  118を生成する。電流コントローラ148の動作によって、1次巻線108の両端間の時変電圧 $V_p$  106も生成される。変圧器の作用によって、スケーリングされた電圧 $V_p$ の複製が2次巻線112の両端間に生成され、スケールファクタは2次巻線112の巻数を1次巻線108の巻数で割った比である。

#### 【0014】

図1に示された実施例は、1次巻線108の1つの終端と電流コントローラ148との間のノードにおいてコンデンサ $C_p$  150を破線で示す。図1の実施例におけるコンデンサ $C_p$  150は、電流コントローラ148に結合するすべての静電容量を表す。1次側スイッチングノード静電容量と称され得るコンデンサ $C_p$  150は、電流コントローラ148に内在する固有の静電容量ならびにエネルギー伝達要素T1 105に内在する固有の静電容量を含み得る。コンデンサ $C_p$  150は、ノイズをフィルタリングし、かつスイッチング電圧の変化を遅くするために、回路の様々な部分に意図的に配置された個別のコンデンサも含み得る。コンデンサ $C_p$  150は、入力帰路110に対する1次巻線108の片端における電圧である電圧 $V_{CP}$  128を有する。コンデンサ $C_p$  150の重要性は、本開示において明らかにする。

#### 【0015】

図1の実施例では、センサ134は、電力変換器100の出力において安定化出力量を表す検知信号132を受け取る。コントローラ142によって安定化されるべき出力量は、一般に出力電圧 $V_o$  120であるが、いくつかの実施例では、出力電流 $I_o$  118であり、また、他の実施例では、出力電圧 $V_o$  120および出力電流 $I_o$  118の組合せであり得る。コントローラ142は、センサ134からフィードバック信号 $U_{FB}$  136を受け取る。フィードバック信号 $U_{FB}$  136は、電圧または電流のいずれかであり得る。

#### 【0016】

2次巻線112に電気的結合された回路が、1次巻線108に結合された回路から直流的に絶縁されているので、検知信号132が負荷122から直流的に絶縁されているか、あるいはセンサ

10

20

30

40

50

134が検知信号132とコントローラ142との間に直流的絶縁をもたらす。換言すれば、直流的絶縁は、センサ134の内部または図1に示されていない検知信号132の経路の別の部分に存在し得る。

【0017】

図1の実施例では、コントローラ142は、電流 $I_p$  126を表す電流検知信号130を受け取る。電流検知信号130は、電圧または電流のいずれかであり得て、既知の方法を用いて得ることができる。例えば、電流検知信号130は、変流器の出力、電流検知抵抗の両端の電圧、あるいは電流 $I_p$  126の全体または電流 $I_p$  126の一部分のいずれかを伝導する酸化金属電界効果トランジスタMOSFETのオン抵抗の両端の電圧であり得る。

【0018】

図1の実施例では、コントローラ142は、フィードバック信号 $U_{FB}$  136および電流検知信号130を受け取って、電流コントローラ148によって受け取られるモード選択信号146を生成する。一実施例では、電流コントローラ148は3つの動作モードを有することができる。第1のモードは、電流コントローラ148が第1のモードであるとき電流 $I_p$  126が実質的にゼロになるように、電流を伝導しないものでよい。第2のモードは、例えば、エネルギー伝達要素T1 105の1次巻線108の電流が、入力電圧 $V_{IN}$ 、1次巻線108のインダクタンス、および電流コントローラ148が第2のモードのままである時間によって決定される状況など、外部回路が許すだけの量の電流を伝導するものでよい。第3のモードは、電流コントローラ148が、本発明の教示に従って第3のモードのままである期間中は電流の伝導を比較的小さな値に制限するものでよい。一実施例では、電流の比較的小さな値は、第2のモードの期間中の電流値より実質的に小さい定電流値である。一実施例では、第3のモードの比較的小さな定電流値は、第2のモードで伝導された最大電流の5パーセントである。

【0019】

図1の実施例では、フィードバック信号 $U_{FB}$  136は、本発明の教示による電流コントローラ148のモードの変化によって決まる実質的に様々な特性を有する。例えば、電流コントローラ148が第2のモードと第1モードの間で変化するとき、フィードバック信号 $U_{FB}$  136は、電流コントローラ148が第3のモードと第1モードの間で変化するときにはない特徴を含んでいる。したがって、コントローラ142は、本発明の教示により、電流コントローラ148の別々のモードに対してフィードバック信号 $U_{FB}$  136を適切に解釈するために、第1のフィードバック回路138および第2のフィードバック回路140を含んでいる。他のコントローラの実施例は、別々の動作モードから生じるフィードバック信号を解釈するのに必要とされる2つより多くのフィードバック回路を含むことができる。

【0020】

図1の実施例では、コントローラ142に含まれる制御回路144は、必要に応じて電力変換器の出力を制御するために、第1のフィードバック回路138および第2のフィードバック回路140から信号を受け取る。コントローラ142に含まれるフィードバック回路は、フィードバック信号 $U_{FB}$  136から必要な情報を得るために、フィルタ回路、サンプルアンドホールド回路、およびコンパレータなどの任意のアナログ回路およびデジタル回路を使用することができる。コントローラ142に含まれる制御回路144は、必要に応じてフィードバック回路から受け取った情報を解釈して応答するために、発振器、コンパレータ、デジタル論理、およびステートマシンなど、任意のアナログ回路およびデジタル回路を使用することができる。

【0021】

図1は、別の実施例ではいくつかの個々のアナログ信号またはデジタル信号を表す1つのラインとしてモード選択信号146を示す。例えば、本発明の教示に従って、制御信号146用の2本の2進デジタル信号ラインが、電流コントローラ148の4つの別個のモードを選択することができる。

【0022】

図2は、本発明の教示によるフライバックトポロジを用いたスイッチング電力変換器200の別の実施例を示す概略図である。図2の実施例は、1次巻線108、2次巻線112、およびバ

イアス巻線210を有する結合されたインダクタ205を含む。バイアス巻線210は、補助巻線と称されることもある。一実施例では、図2のバイアス巻線210は、図1で導入されたフィードバック信号 $U_{FB}$  136を生成するセンサ134である。バイアス巻線210は、2次巻線112の整流器D1 114が導通するとき、出力電圧 $V_o$  120に対する応答の電圧 $V_B$  215を生成する。図1に示されているが図2には見られない検知信号132は、バイアス巻線210を結合されたインダクタ205の2次巻線112に結合する磁束である。別の実施例では、バイアス巻線210は、コントローラ142内の回路に電力を供給することもできる。

【0023】

バイアス巻線の使用において、直流的絶縁を有するコントローラに電力を供給する一方で、出力電圧を検知して検知をもたらすための多くの変形形態が可能であることが理解される。例えば、バイアス巻線は、整流器の陽極からの交流フィードバック信号を供給する一方で直流バイアス電圧を生成するために、整流器D1 114に類似の整流器およびコンデンサC1 116に類似のコンデンサを適用することができる。そのため、コントローラ142が巻線から受け取るのにより適切な値へ電圧をスケーリングするために、バイアス巻線に対して抵抗などの追加の受動素子を使用することができる。

10

【0024】

出力電圧 $V_o$  120を検知するのにバイアス巻線210を使用すると、光結合素子の出費なしで出力電圧 $V_o$  120とコントローラ142の間に直流的絶縁をもたらすという利点がある。出力電圧 $V_o$  120を検知するのに、結合されたインダクタ205上の巻線を使用することの不都合は、光結合素子が出力電圧 $V_o$  120の連続的検知をもたらすことができるのに対して、バイアス巻線210の電圧 $V_B$  215は、出力整流器D1 114が導通しているときしか出力 $V_o$  120を表さないことである。出力整流器D1 114が導通するのは、2次巻線112に電流パルスがある間のみである。したがって、2次巻線112における電流のパルス間の時間は、コントローラ142が出力電圧 $V_o$  120を検知することができない時間である。換言すれば、光結合素子を用いて出力電圧 $V_o$  120を連続的に検知するのとは対照的に、結合されたインダクタ205上の巻線を用いて出力電圧 $V_o$  120を検知することは、出力電圧 $V_o$  120の所望の制御のために必要な情報をもたらすほど十分頻繁には生じない可能性があるパルスに限定される。2次巻線112が電流パルスを得るのは1次巻線108が電流パルスを得た後だけであるので、コントローラ142が出力電圧 $V_o$  120をより頻繁に検知することができるよう、1次巻線108における電流パルスの時間間隔を短縮するのが望ましい。

20

30

30

【0025】

負荷122の範囲の値にわたって所望の出力電圧 $V_o$  120を維持するのに必要な電力を供給するように、1次巻線108の脈動電流のレートおよび大きさは、コントローラ142によって制御される。負荷がゼロに近づくとき、所望の出力電圧 $V_o$  120を維持するために、1次巻線108の電流をより小さくする必要がある。そのため、コントローラは、1次巻線108の電流を小さくすること、ならびに電流パルスの時間間隔を増加することができる。

40

【0026】

コントローラ142は、電流コントローラ148を第1のモードから第2のモードへ変化させるモード選択信号146を電流コントローラ148に供給することにより、1次巻線108に電流パルスを生成することができ、第1のモードに戻るのに先立って、電流 $I_p$  126が直線状の傾斜で所望の最大値へ増加することが可能になる。第2のモードの電流コントローラ148の動作によってコンデンサ $C_p$  150が完全放電し、その結果、1次巻線108の電圧 $V_p$  106が入力電圧 $V_{IN}$  102と等しくなる。

【0027】

第1のモードに戻るのに先立って最大電流 $I_p$  126が実際の最低値に増加し得たとしても、電流コントローラ148が第2のモードで動作するとき、コンデンサ $C_p$  150に蓄積されたすべてのエネルギーが失われる。コンデンサ $C_p$  150の全放電から消費される電力を低減する唯一の手段は、放電の時間間隔を増加することである。換言すれば、1次電流のパルス間の時間を増加すると、負荷がゼロに近づくので、コントローラ142が出力電圧 $V_o$  120を検知することができない時間が増加するという犠牲を払って電力変換器で失われる電力

50

を低減することになる。結果として、負荷122が突然増加すると、コントローラ142が電圧を検知してそれに応答することができないうちに、出力電圧 $V_o$  120が受容し難い値に低下する恐れがある。

【0028】

ワット損もゼロ負荷の近くに低減する一方で、コントローラ142が、負荷122の突然の増加に適切に応答するほど出力電圧 $V_o$  120を十分頻繁に検知することを可能にする解決策が以下で論じられる。この解決策は、コンデンサ $C_p$  150を完全放電することなく1次巻線108に電流パルスを生成する。この解決策は、本発明の教示により、電流コントローラ148に第3の動作モードを導入することによって実現される。一実施例では、電流コントローラ148の第3のモードは、電流コントローラ148が第1のモードへ戻った後に出力整流器D1 114が導通するように、1次巻線108に過不足ない電流を加えるように作用する。電流コントローラ148の第3のモードは、本発明の教示により、所望の電流を加えるように十分に小さい大きさおよび持続時間有する電流を1次巻線へ伝導する一方で、コンデンサ $C_p$  150を部分的にのみ放電する。所与の用途向けの電流の適切な値の割出しが、この開示で後に詳細に論じられる。

10

【0029】

図3は、絶縁された出力電圧の検知を提供する本発明の教示による例示的コントローラの動作を説明する、図2の例示的電力変換器の電圧波形および電流波形を示す図である。図示された実施例に示されるように、コンデンサ $C_p$  150を完全放電する電流パルス $I_p$  126は、 $t_0$  310、 $t_{(N+1)}$  350および $t_{(N+2)}$  360の時刻で開始する。本発明の教示により、コンデンサ $C_p$  150を部分的に放電する電流パルス $I_p$  126は、 $t_1$  320、 $t_2$  330、および $t_N$  340の時刻で開始する。

20

【0030】

コンデンサ $C_p$  150を完全に放電する電流パルス $I_p$  126と、コンデンサ $C_p$  150を部分的に放電する電流パルス $I_p$  126との区別は、コンデンサ $C_p$  150の電圧である $V_{cp}$  128の波形から明白である。電圧 $V_{cp}$  128が実質的にゼロであるとき、コンデンサ $C_p$  150は完全に放電されている。電流 $I_p$  126が0より大きいとき電圧 $V_{cp}$  128は実質的に0より大きいままであり、このときコンデンサ $C_p$  150は部分的にしか放電されない。

30

【0031】

示されるように、電流 $I_p$  126の各全放電パルスおよび各部分放電パルスの最後で、電圧 $V_{cp}$  128が入力電圧 $V_{in}$  102より高く上昇し、一方、エネルギー伝達要素(例えば図1のエネルギー伝達要素T1 105および図2の結合されたインダクタ205)からのエネルギーがコンデンサ $C_p$  150を充電する。電圧 $V_{cp}$  128は、出力整流器D1 114が導通して、反映された出力電圧 $V_{or}$ を加えた入力電圧 $V_{in}$ へ電圧 $V_{cp}$ をクランプするまで上昇し、反映された出力電圧 $V_{or}$ は、2次巻線112の電圧に1次巻線108の巻数を掛けて2次巻線112の巻数で割ったものである。

40

【0032】

示されるように、電圧 $V_{cp}$  128は、2次巻線112からの電流がゼロに下がって出力整流器D1 114が導通しなくなるまで、 $V_{or}$ を加えた $V_{in}$ の値でクランプされ続ける。その電圧が $V_{in}$  102より高くなったコンデンサ $C_p$  150に蓄積されたエネルギーは、次いで1次巻線108の自己インダクタンスと回路の有効な寄生抵抗による減衰振動で放散する。

40

【0033】

図3は、コントローラ142へフィードバック信号 $U_{fb}$  136を供給する図2の電圧 $V_b$  215を示している。コントローラ142は、入力電圧 $V_{in}$  102ならびにバイアス電圧 $V_b$  215からの出力電圧 $V_o$  120を検知することができる。電流 $I_p$  126の全放電パルスの期間中、バイアス電圧 $V_b$  215は、入力電圧 $V_{in}$  102を表す大きさ $V_{ins}$ に対してマイナスになる。電流 $I_p$  126の全放電のパルスの後に出力整流器D1 114が導通して、出力電圧 $V_o$  120を表すバイアス巻線210上のプラスの電圧 $V_{os}$ として出力電圧 $V_o$  120を検知することができる。コンデンサ $C_p$  150を部分的にのみ放電する電流パルス $I_p$  126の後に、出力整流器D1 114は、図3に示されたようなバイアス電圧 $V_b$  215の減衰振動により、出力電圧 $V_o$  120の

50

検知を可能にするのに過不足なく導通する。

【0034】

一実施例では、出力電圧 $V_o$  120を所望の値に維持するために電流 $I_p$  126の全放電パルスが必要とされるほど負荷122が十分に大きいとき、すべてのスイッチング期間 $T_s$ 毎に全放電パルスが生じてよい。例示的スイッチング期間 $T_s$ は、図3の $t_{(N+1)}$  350と $t_{(N+2)}$  360の間の時間である。一般に、軽度から中程度の負荷では、電流パルスのないいくつかのスイッチング期間によって分離された全放電パルスのパターンが必要になることがある。

【0035】

この実施例では、本発明の教示により、負荷122がほぼゼロであるとき、全放電スイッチングパルスの間の期間よりはるかに短い部分放電パルスだけが出力電圧 $V_o$  120を検知するのに用いられる。負荷122がゼロより十分に大きいときには、ゼロより十分に大きい負荷において全放電パルスが十分頻繁に生じて出力電圧の適切な検知をもたらすので、出力電圧 $V_o$  120を検知するために部分放電パルスを用いる必要はない。部分放電パルスは、全放電パルスが必要かどうか判断するウェイクアップパルスと考えることができる。部分放電パルス間の時間は、ウェイクアップ期間と考えることができる。

10

【0036】

図示の実施例では、例示的ウェイクアップ期間 $T_{w1}$ は、図3の $t_1$  320と $t_2$  330の間の時間である。一実施例では、ウェイクアップ期間 $T_{w1}$ は、16回のスイッチング期間 $T_s$ である。別の実施例では、ウェイクアップパルスは別々の持続時間のウェイクアップ期間によって分離されてよい。部分放電パルス列の第1の部分放電パルスは、ウェイクアップパルス列のいかなるウェイクアップ期間とも異なる期間で全放電パルスに続いてよい。図3は、全放電パルスの開始における $t_0$  310と部分放電パルス列の第1の部分放電パルスの開始である時刻 $t_1$  320との間の時間である期間 $T_1$ を示す。一実施例では、期間 $T_1$ は9回のスイッチング期間であるが、 $T_{w1}$ は16回のスイッチング期間である。

20

【0037】

一実施例では、コントローラ142に含まれる制御回路144は、本発明の教示により、各電流パルス $I_p$  126の直後に、フィードバック信号 $U_{FB}$  136の値によって、スイッチング期間 $T_s$ 内の、全放電パルス、部分放電パルスまたは無パルスの必要性を判断することができる。例えば、一連の全放電パルスにより、検知された出力電圧 $V_{os}$ が第1の閾値を越えて上昇した場合、制御回路144は、いくつかの後続のスイッチング期間 $T_s$ にわたって電流コントローラ148が電流を伝導しないように、モード選択信号146を設定することができる。次の全放電パルスの後に、検知された出力電圧 $V_{os}$ が第1の閾値より高いままである場合、コントローラ142は、負荷がほぼゼロであると推断することができ、出力電圧 $V_o$  120を検知するために部分放電パルスを用い始める。図3の実施例は、制御回路144が、時刻 $T_N$  340における部分放電パルスの後に検知された出力電圧 $V_{os}$ が低すぎると判断して、時刻 $t_{(N+1)}$  350および $t_{(N+2)}$  360における連続した全放電パルスを必要とする一実施例を説明するものである。

30

【0038】

図2の実施例では、本発明の教示により、制御回路144は、全放電のパルスの後に第1のフィードバック回路138から受け取った信号を解釈し、また、部分放電パルスの後に第2のフィードバック回路140から受け取った信号を解釈する。図2の実施例では、第1のフィードバック回路138は、出力整流器D1 114が導通している間にフィードバック信号 $U_{FB}$  136をサンプリングする。図2の実施例では、第2のフィードバック回路138は、出力整流器D1 114の導通が終えた後に、バイアス電圧 $V_B$  215の減衰振動の間にフィードバック信号 $U_{FB}$  136をサンプリングする。

40

【0039】

この実施例では、出力整流器D1 114が部分放電パルスの後に導通したときの出力電圧 $V_o$  120を表す値までコンデンサ $C_p$  150が充電されるので、バイアス電圧 $V_B$  215の減衰振動のピークは、出力整流器D1 114の導通が終えた後の出力電圧 $V_o$  120を表す。コンデンサ $C_p$  150の最大電圧により、出力整流器D1 114の導通が終えた後の減衰振動の初期条件

50

が設定される。したがって、バイアス電圧 $V_B$  215の減衰振動における各ピークは、部分放電パルスの後のコンデンサ $C_p$  150の最大電圧によって求められる。

【0040】

図2の実施例では、第1のフィードバック回路138は、広範囲の負荷にわたって出力電圧 $V_o$  120を安定化するためにフィードバック信号 $U_{FB}$  136をサンプリングする。第1のフィードバック回路138とは対照的に、一実施例における第2のフィードバック回路140は、広範囲の負荷にわたって出力電圧 $V_o$  120を安定化するためのフィードバック信号 $U_{FB}$  136のサンプリングは行なわない。その代わりに、この実施例の第2のフィードバック回路140は、本発明の教示により、一連の部分放電パルスの期間中に出力電圧 $V_o$  120に十分な変化があって動作モードを変化させる必要があるかどうか判断するためにのみ用いられる。

10

【0041】

具体的には、一実施例では、第2のフィードバック回路140は、例えば図3で、一連の部分放電パルスの第1の部分放電パルスの後の $V_B$  215の減衰振動で示されるように、フィードバック信号 $U_{FB}$  136の減衰振動の第2のピーク値を保持し、この値を、一連の部分放電パルスのそれぞれの後続の部分放電パルスの後に、フィードバック信号 $U_{FB}$  136の減衰振動における第2のピークのサンプルと比較する。後続のサンプルのこの値が、第1のサンプルのこの値よりある閾値だけ小さいとき、制御回路144は、出力電圧 $V_o$  120が小さすぎると判断し、一連の全放電パルスを開始するようにモード選択信号146を設定する。減衰振動における任意のピーク値を、比較に用いるためにサンプリングしてよいことが理解される。一実施例では、第2のピーク値は、最も大きく、しかも出力整流器D1 114が導電している間の第1のピークに現われ得るノイズおよび歪みが比較的存在しないので、好ましいピークであり得る。一実施例では、閾値は30ミリボルトである。

20

【0042】

一実施例では、部分放電パルスの大きさおよび持続時間は、出力整流器D1 114が部分放電パルスの最後で導通することを可能にするのに過不足のないものである。別の実施例では、部分放電パルスの大きさおよび持続時間は、出力整流器D1 114が部分放電パルスの最後で導通することを可能にするのに十分以上のものである。結合されたインダクタ20 5の巻線の非理想の結合に関連した過渡電圧が無視できる値に低下するまで出力整流器D1

30

114が導通することが可能であるとき、出力電圧 $V_o$  120をより高い精度で検知することができる。ダイオードD1 114が導通し始めたとき、漏れインダクタンスとして定量化されることがある非理想の結合が、出力整流器D1 114と2次巻線112の間に電圧を生成することができる。漏れインダクタンスに起因する過渡電圧により、減衰振動の第1のピークが歪む可能性もある。したがって、出力整流器D1 114が導通するのを終えないうちに、コンデンサ $C_p$  150がより正確に出力電圧 $V_o$  120を表す電圧へ充電するように、漏れインダクタンスからの電圧が無視できる値に低下することを可能にするのが望ましい。漏れインダクタンスの影響からの歪みを回避するために、減衰振動の第1のピークをサンプリングしないことも望ましい。

【0043】

一実施例では、部分放電パルスの大きさが16ミリアンペアであるのに対して、全放電パルスのピーク電流は250ミリアンペアである。そのため、伝達されるエネルギーは1次巻線108のピーク電流の2乗に比例するので、部分放電パルスによって出力に伝達されるエネルギーは、全放電パルスによって出力に伝達されるエネルギーと比較して小さいと考えることができる。部分放電パルスが出力に有限のエネルギーを伝達し得るので、最小限のスイッチング周波数を有するとはいえ、その周波数は小さいものであるコントローラは、出力電流 $I_o$  118がゼロに近づくとき、出力電圧 $V_o$  120が所望の電圧より高くならないようにするダミー内部負荷を電源が有する必要性があることが理解される。

40

【0044】

特定の環境の組に対して電力変換器における最小の電力損失を与える部分放電パルスの大きさおよび持続時間があることは、解析的にまたは実験的に求めることができる。部分放電パルスの持続時間は、図3に示されたように、一般にフィードバック信号 $U_{FB}$  136の

50

減衰振動の期間の半分未満である。一実施例では、部分放電パルスの持続時間は、ファイドバック信号 $U_{FB}$  136の減衰振動の一期間の約4分の1である。結合されたインダクタの1次巻線108のインダクタンスが2.2ミリヘンリーである一実施例では、コンデンサ $C_P$  150は約70ピコファラドであり、部分放電パルスは約600ナノ秒の持続時間にわたって16ミリアンペアである。一実施例では、本発明の教示により、制御回路144は、電力変換器において、最小の電力損失を達成し、かつ出力整流器D1 114が導通することを保証するために、部分放電パルスの大きさおよび持続時間を調整することができるよう理解されよう。この調整は、例えばコントローラ144が受け取った外部信号に応答して行なうことができる。この調整は、制御回路144の内部で個別のコンポーネントの値を選択することにより行なうこともできる。制御回路144が集積回路に含まれている実施例では、この調整は、集積回路の内部パラメータを調節することにより行なうことができる。

10

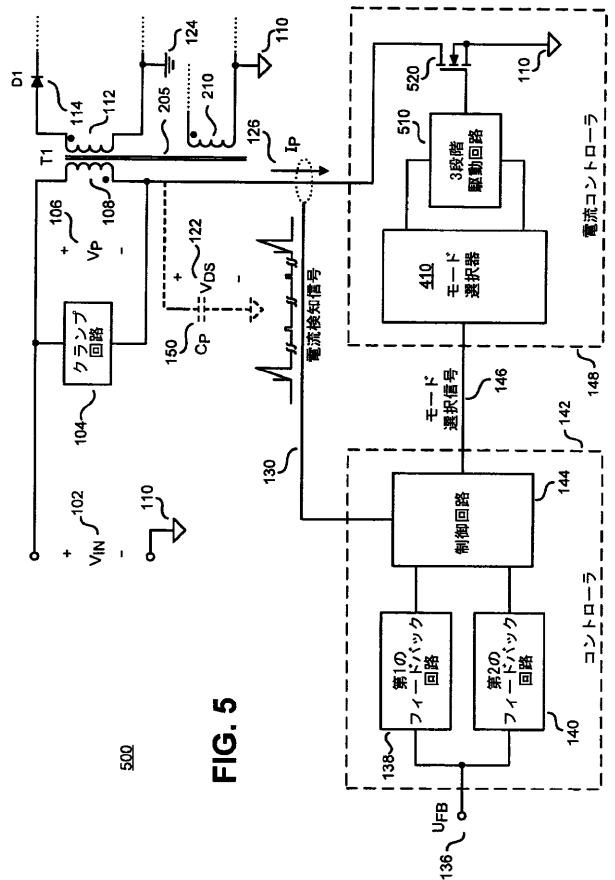

## 【0045】

図4は、電流コントローラ148の一実施例をより詳細に示す電力変換器400の概略図である。図4の実施例では、電流コントローラ148は、コントローラ142からモード選択信号146を受け取るモード選択器410を含む。図4の実施例では、モード選択器410は、モード選択信号146に応答して、スイッチS1 420またはスイッチS2 440のいずれかを閉じるか、あるいはどちらのスイッチも閉じない。

## 【0046】

図4の実施例では、電流コントローラ148が第1のモードであるとき電流 $I_P$  126が実質的にゼロになるように、第1のモードではスイッチS1 420およびスイッチS2 440を開く。

20

図4の実施例で、第2のモードではコンデンサ $C_P$  150を完全放電するように、スイッチS1 420を閉じてスイッチS2 440を開く。図4の実施例で、第3のモードでは、本発明の教示によってコンデンサ $C_P$  150を部分放電するために、電流 $I_P$  126が電流源430の値になるように、スイッチS1 420を開いてスイッチS2 440を閉じる。他の実施例では、電流源430は、コンデンサ $C_P$  150の所望の部分放電の程度によって変化する可変電流源であり得ることが理解される。

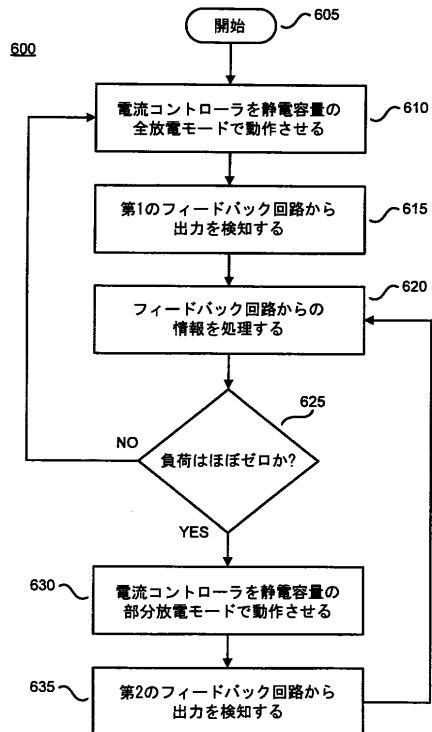

## 【0047】

図5は、酸化金属半導体電界効果トランジスタ(MOSFET)520ならびにモード選択信号146に応答して全放電パルスおよび部分放電パルスの電流 $I_P$  126を生成するための3段階駆動回路510を含む電流コントローラ148の別の実施例を示す電力変換器500の概略図である。

30

図5の実施例では、3段階駆動回路510は、モード選択信号146に応答してnチャンネルMOSFET 520のゲート端子とソース端子の間に少なくとも3つの別個の電圧の値を生成するように、モード選択器410からの信号に応答する。一実施例では、MOSFET 520のゲート端子は、MOSFET 520の制御端子と見なすことができる。

## 【0048】

図5の実施例では、電流コントローラ148の第1のモードでは、ゲートからソースへ、nチャンネルMOSFET 520の閾値より実質的に低い電圧が印加される。その結果、電流コントローラ148の第1の動作モードでは、MOSFET 520は実質的にオフになる。図5の実施例では、電流コントローラ148の第2のモードでは、ゲートからソースへ、nチャンネルMOSFET 520の閾値電圧より実質的に高い電圧が印加される。その結果、電流コントローラ148の第2の動作モードでは、MOSFET 520は実質的にオンになる。図5の実施例では、電流コントローラ148の第3のモードでは、ゲートからソースへ、nチャンネルMOSFET 520の閾値電圧よりわずかに高い電圧が印加される。その結果、第3のモードのMOSFET 520の制御端子でのゲートからソースへの電圧は、MOSFET 520が、電流 $I_P$  126の大きさ向けの部分放電電流パルスを供給するときのものに相当する。換言すれば、第3の動作モードでは、MOSFET 520が、開または閉のいずれかであるスイッチとしてではなく、その、活性領域と称されることがある飽和領域で動作し、同領域では、ドレイン電流が主としてゲートからソースへの電圧によって制御され、ドレインからソースへの電圧には実質的に左右されない。MOSFET 520および3段階駆動回路510が集積回路に含まれる実施例では、3段階駆動回路510は、電流コントローラ148の第3のモードの期間中ゲートに印加される電圧がMOSFET 520の

40

50

閾値電圧を追跡し、それによって温度範囲およびプロセスの変化に対して部分放電電流の変化を低減するように設計することができる。他の実施例では、3段階駆動回路510は、コンデンサC<sub>P</sub> 150の所望の部分放電の程度に従って別々のMOSFET 520の飽和特性を選択するために、4つ以上の駆動レベルを有することができるが理解される。

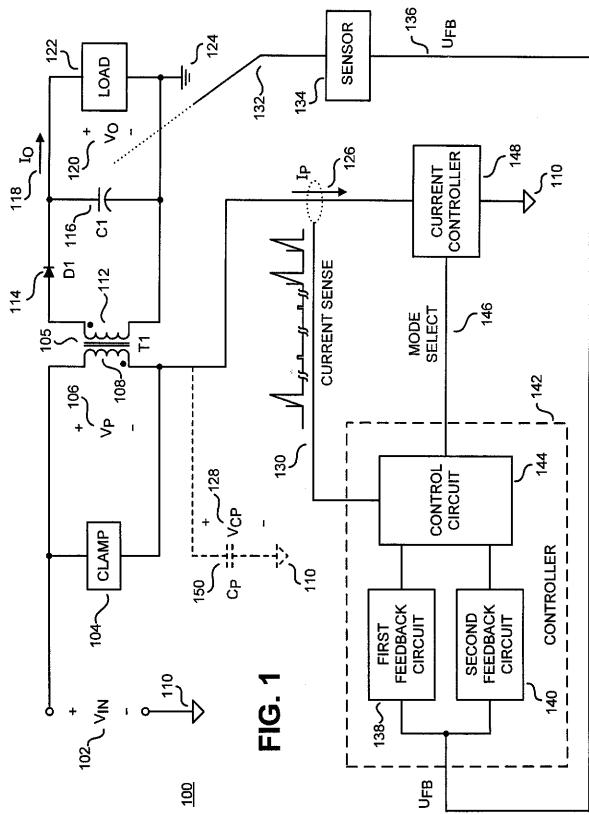

【0049】

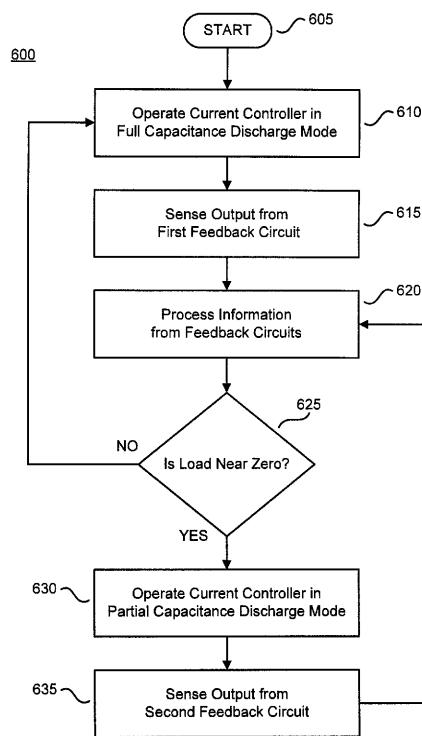

図6は、絶縁された出力の検知を提供する本発明の教示による電力変換器を制御する方法の一実施例を示す流れ図600である。ブロック605で開始した後に、ブロック610で、電流コントローラは静電容量の全放電モードで動作し、電流コントローラのノード上の静電容量を完全放電する電流パルスを生成する。

【0050】

次に、ブロック615で、第1のフィードバック回路が絶縁された出力電圧を検知する。ブロック620で、負荷条件を評価するためにフィードバック回路からの情報が処理される。次いで、判定ブロック625で、負荷がゼロに近い場合には流れがブロック630へ続き、負荷がゼロに近くない場合にはブロック610へ分岐する。一実施例では、全放電パルスが図3のウェイクアップ期間T<sub>W1</sub>より大きな間隔で生じるとき、負荷はゼロに近いものと考えられる。

【0051】

ブロック630で、電流コントローラは静電容量の部分放電モードで動作し、電流コントローラのノード上の静電容量を部分的にのみ放電する電流パルスを生成する。次いで、第2のフィードバック回路は、フィードバック回路からの情報が処理されるブロック620に戻る前に、ブロック635で、絶縁された出力電圧を検知する。

【0052】

本発明の、要約で説明されたものを含む図示された実施例の上記の説明は、開示された正確な諸形態を網羅するかまたは限定するようには意図されていない。本発明の特定の実施形態および実施例が説明の目的で本明細書に記述されているが、本発明の広範な趣旨および範囲からはずれることなく、様々な同等の変更形態が可能である。実際、特定の電圧、電流、周波数、電力範囲値、時刻などは説明のために提供されており、他の実施形態および実施例では、他の値も本発明の教示に従って用いられ得ることが理解される。

【0053】

これらの変更形態は、上記の詳細な説明に照らして本発明の実施例になり得る。以下の特許請求の範囲で用いられる用語は、本発明を、明細書および特許請求の範囲で開示された特定の実施形態に限定するものと解釈されるべきでない。むしろ、その範囲は、完全に以下の特許請求の範囲によって決定されるべきであり、特許請求の範囲は、請求の解釈の確立している教義によって解釈されるべきである。したがって、本明細書および図面は、限定的であるというよりむしろ例示的であると見なされるべきである。

【符号の説明】

【0054】

- 100 スイッチング電力変換器

- 102 非安定入力電圧

- 104 クランプ回路

- 105 エネルギー伝達要素

- 106 時変電圧

- 108 1次巻線

- 110 入力帰路

- 112 2次巻線

- 114 整流器

- 116 コンデンサ

- 118 出力電流

- 120 出力電圧

- 122 負荷

10

20

30

40

50

|     |                           |    |

|-----|---------------------------|----|

| 124 | 出力帰路                      |    |

| 126 | 電流                        |    |

| 128 | 電圧                        |    |

| 130 | 電流検知信号                    |    |

| 132 | 検知信号                      |    |

| 134 | センサ                       |    |

| 136 | フィードバック信号                 |    |

| 138 | 第1のフィードバック回路              |    |

| 140 | 第2のフィードバック回路              |    |

| 142 | コントローラ                    | 10 |

| 144 | 制御回路                      |    |

| 146 | モード選択信号                   |    |

| 148 | 電流コントローラ                  |    |

| 150 | コンデンサ                     |    |

| 200 | スイッチング電力変換器               |    |

| 205 | インダクタ                     |    |

| 210 | バイアス巻線                    |    |

| 215 | 電圧                        |    |

| 310 | 時刻                        |    |

| 320 | 時刻                        | 20 |

| 330 | 時刻                        |    |

| 340 | 時刻                        |    |

| 350 | 時刻                        |    |

| 360 | 時刻                        |    |

| 400 | 電力変換器                     |    |

| 410 | モード選択器                    |    |

| 420 | スイッチ                      |    |

| 430 | 電流源                       |    |

| 440 | スイッチ                      |    |

| 500 | 電力変換器                     | 30 |

| 510 | 3段階駆動回路                   |    |

| 520 | 酸化金属半導体電界効果トランジスタ(MOSFET) |    |

| 600 | 流れ図                       |    |

| 605 | ブロック                      |    |

| 610 | ブロック                      |    |

| 615 | ブロック                      |    |

| 620 | ブロック                      |    |

| 625 | 判定ブロック                    |    |

| 630 | ブロック                      |    |

| 635 | ブロック                      | 40 |

【図 1】

FIG. 1

【図 2】

FIG. 2

【図 3】

FIG. 3

【図 4】

FIG. 4

【 四 5 】

**FIG. 5**

【 図 6 】

**FIG. 6**

---

フロントページの続き

(72)発明者 アレックス・ビー・ジェンゲリアン

アメリカ合衆国・カリフォルニア・95070・サラトガ・セヴィラ・レーン・20602

(72)発明者 アーサー・ビー・オデール

アメリカ合衆国・カリフォルニア・95037・モーガン・ヒル・ヘイ・ロフト・コート・277

6

(72)発明者 ヘンソン・ウ

アメリカ合衆国・カリフォルニア・95070・サラトガ・ボニー・ブレイ・レーン・20150

F ターム(参考) 5H730 AA14 AS01 BB43 DD04 EE02 EE07 EE59 FD01 FD41 FF09

FF17

【外國語明細書】

## APPARATUS AND METHOD FOR SENSING OF ISOLATED OUTPUT

### BACKGROUND INFORMATION

#### Field of the Disclosure

**[0001]** This invention is related to the control of switched-mode power supplies.

Specifically, it is related to low-cost power supplies with regulated isolated outputs that must meet standards for maximum power consumption when the output has no load, and yet must keep the output within specified limits when a load is suddenly applied.

#### Background

**[0002]** Low-cost solutions to regulate an isolated output voltage of a switching power supply typically rely on the magnetic coupling between isolated windings of an energy transfer element to provide information about the output to a control circuit. The control circuit typically receives a signal representative of the output voltage immediately after a switching event that delivers energy to the output. The signal is typically received from a primary-referenced winding of an energy transfer element instead of from an optocoupler. This type of control is often referred to as “primary-side control” or control using primary-side feedback.

**[0003]** Although these solutions eliminate the cost and the power consumed by an optocoupler, they cannot sense the output voltage in the absence of switching. A problem arises when the load on the output of the power supply approaches zero. The power supply must provide the specified regulated output voltage but almost no power. Under such conditions, the power lost in the operation of the power supply itself is a significant part of the total power consumed. Requirements to limit the consumption of power by the power supply under conditions of near zero external loading discourage the use of a dummy internal load in a power supply. A dummy internal load, sometimes called a pre-load, can be useful

in a power supply to help provide overvoltage protection, improve regulation between multiple outputs, and prevent the switching frequency from going below a minimum value. In particular, a dummy internal load is a small permanent minimum load inside a power supply. However, a penalty for using a dummy internal load is that the power supply becomes less efficient because the dummy load dissipates power that is not measured as output power. Also, the controller has to switch more often to power the additional internal load, which results in the power supply consuming additional power even though there is no load connected to the power supply's output. To avoid these drawbacks, it is useful to increase the time between switching events under no-load conditions to reduce the losses inherent in switching. However, under such conditions, the controller is unable to sense the output voltage during the relatively long intervals between switching events.

**[0004]** When a substantial load is suddenly applied to the output during one of the relatively long intervals between switching events, the output voltage can easily fall outside the specified limits of regulation before the controller is able to respond to the condition. A typical remedy for such a condition is the addition of costly bulk capacitance to the output to provide the energy required by a load that could be applied during the time when the controller cannot sense the output.

**BRIEF DESCRIPTION OF THE DRAWINGS**

[0005] Non-limiting and non-exhaustive embodiments of the present invention are described with reference to the following figures, wherein like reference numerals refer to like parts throughout the various views unless otherwise specified.

[0006] FIG. 1 shows an example power converter including a controller in accordance with the teachings of the present invention that provides sensing of an isolated output.

[0007] FIG. 2 is an example of a power converter including a controller that uses a winding on a coupled inductor to sense output voltage in accordance with the teachings of the present invention and that provides sensing of an isolated output.

[0008] FIG. 3 shows voltage and current waveforms from an example power converter that illustrates the operation of a controller in accordance with the teachings of the present invention that provides for sensing of an isolated output voltage.

[0009] FIG. 4 shows one example of a power converter that illustrates one example of a current controller in accordance with the teachings of the present invention.

[0010] FIG. 5 shows one example of a power converter that illustrates another example of a current controller, which uses a transistor for sensing of an isolated output voltage in accordance with the teachings of the present invention.

[0011] FIG. 6 is flow diagram that shows one example method to control a power converter in accordance with the teachings of the present invention that provides for sensing of an isolated output voltage.

## DETAILED DESCRIPTION

**[0012]** Methods and apparatuses for implementing a power supply controller that provide relatively low cost solutions that accomplish sensing of an isolated output of a power converter are disclosed. In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be apparent, however, to one having ordinary skill in the art that the specific detail need not be employed to practice the present invention. In other instances, well-known materials or methods have not been described in detail in order to avoid obscuring the present invention.

**[0013]** Reference throughout this specification to “one embodiment”, “an embodiment”, “one example” or “an example” means that a particular feature, structure or characteristic described in connection with the embodiment or example is included in at least one embodiment of the present invention. Thus, appearances of the phrases “in one embodiment”, “in an embodiment”, “one example” or “an example” in various places throughout this specification are not necessarily all referring to the same embodiment or example. Furthermore, the particular features, structures or characteristics may be combined in any suitable combinations and/or subcombinations in one or more embodiments or examples. Particular features, structures or characteristics may be included in an integrated circuit, an electronic circuit, a combinational logic circuit, or other suitable components that provide the described functionality. In addition, it is appreciated that the figures provided herewith are for explanation purposes to persons ordinarily skilled in the art and that the drawings are not necessarily drawn to scale.

**[0014]** FIG. 1 is a schematic diagram that shows generally one example of a switching power converter 100 that uses a flyback topology in accordance with the teachings of the present invention. In the illustrated example, power converter 100 is shown as a power

supply having flyback topology for explanation purposes. It is noted, however, that there are many other known topologies and configurations for switching power supplies. It is appreciated that the example flyback topology illustrated in FIG. 1 is adequate for explaining principles in accordance with the teachings of the present invention and that the principles may apply also to other types of switching regulators in accordance with the teachings of the present invention. Details that will be discussed in greater detail below are omitted from FIG. 1 to avoid obscuring teachings in accordance with the present invention.

**[0015]** The example power converter in FIG. 1 controls the transfer of energy from an unregulated input voltage  $V_{IN}$  102 at the input of the power converter 100 to a load 122 at the output of the power converter 100. The input voltage  $V_{IN}$  102 is coupled to an energy transfer element T1 105 and a current controller 148. In the example of FIG. 1, the energy transfer element T1 105 is a coupled inductor, sometimes referred to as a transformer, with a primary winding 108 and a secondary winding 112. In the example of FIG. 1, primary winding 108 may be considered an input winding, and secondary winding 112 may be considered an output winding. A clamp circuit 104 is coupled to the primary winding 108 of the energy transfer element T1 105 to control the maximum voltage on the current controller 148.

**[0016]** In the example of FIG. 1, input voltage  $V_{IN}$  102 is positive with respect to an input return 110, and output voltage  $V_O$  120 is positive with respect to an output return 124. The example of FIG. 1 shows galvanic isolation between the input return 110 and the output return 124 because input return 110 and output return 124 are designated by different symbols. In other words, a dc voltage applied between input return 110 and output return 124 will produce substantially zero current. Therefore, circuits electrically coupled to the primary

winding 108 are galvanically isolated from circuits electrically coupled to the secondary winding 112.

**[0017]** In the illustrated example, current controller 148 either conducts current or does not conduct current in response to a control circuit 144 that is included in a controller 142. Current controller 148 and controller 142 may include integrated circuits and discrete electrical components. In some examples, current controller 148 and controller 142 may be integrated together in a single monolithic integrated circuit.

**[0018]** In the example of FIG. 1, current controller 148 controls a current  $I_p$  126 in response to controller 142 to meet a specified performance of the power converter 100. In operation, current controller 148 produces pulsating current in primary winding 108 and in secondary winding 112. Current in secondary winding 112 is rectified by rectifier D1 114 and then filtered by capacitor C1 116 to produce a substantially constant output voltage  $V_o$  120 or output current  $I_o$  118 at the load 122. The operation of current controller 148 also produces a time varying voltage  $V_p$  106 between the ends of primary winding 108. By transformer action, a scaled replica of the voltage  $V_p$  is produced between the ends of secondary winding 112, the scale factor being the ratio that is the number of turns of secondary winding 112 divided by the number of turns of primary winding 108.

**[0019]** The example illustrated in FIG. 1 shows a capacitor  $C_p$  150 in broken lines at the node between one end of primary winding 108 and current controller 148. Capacitor  $C_p$  150 in the example of FIG. 1 represents all the capacitance that couples to current controller 148. Capacitor  $C_p$  150, which could be referred to as the primary switching node capacitance, may include natural capacitance internal to energy transfer element T1 105 as well as the natural internal capacitance of current controller 148. Capacitor  $C_p$  150 may also include discrete capacitors placed intentionally in various parts of the circuit to filter noise

and to slow transitions of switching voltages. Capacitor  $C_P$  150 has a voltage  $V_{CP}$  128 that is the voltage at one end of primary winding 108 with respect to the input return 110. The importance of capacitor  $C_P$  150 will become apparent later in this disclosure.

**[0020]** In the example of FIG. 1, a sensor 134 receives a sense signal 132 that is representative of the output quantity to be regulated at the output of power converter 100. The output quantity to be regulated by controller 142 is typically the output voltage  $V_O$  120, but in some examples is the output current  $I_O$  118, and in other examples may be a combination of output voltage  $V_O$  120 and output current  $I_O$  118. Controller 142 receives a feedback signal  $U_{FB}$  136 from sensor 134. Feedback signal  $U_{FB}$  136 may be either a voltage or a current.

**[0021]** Since circuits electrically coupled to the secondary winding 112 are galvanically isolated from the circuits electrically coupled to the primary winding 108, either the sense signal 132 is galvanically isolated from the load 122, or sensor 134 provides galvanic isolation between sense signal 132 and controller 142. In other words, galvanic isolation may reside in either the sensor 134 or in another part of the path of the sense signal 132 not shown in FIG. 1.

**[0022]** In the example of FIG. 1, controller 142 receives a current sense signal 130 that is representative of the current  $I_P$  126. Current sense signal 130 may be either a voltage or a current and may be obtained using known methods. For example, current sense signal 130 may be the output of a current transformer, the voltage across a current sense resistor, or the voltage across the on-resistance of a metal oxide field-effect transistor MOSFET that conducts either the entire current  $I_P$  126 or a portion of the current  $I_P$  126.

**[0023]** In the example of FIG. 1, controller 142 receives feedback signal  $U_{FB}$  136 and current sense signal 130 to produce a mode select signal 146 that is received by current

controller 148. In one example, current controller 148 may have three modes of operation. A first mode may be one that does not conduct current, such that current  $I_P$  126 is substantially zero when current controller 148 is the first mode. A second mode may be one that conducts as much current as external circuitry allows, such as for example the condition where the current in the primary winding 108 of energy transfer element T1 105 is determined by the input voltage  $V_{IN}$ , the inductance of primary winding 108, and the time that current controller 148 remains in the second mode. A third mode may be one that restricts conduction of current to a relatively small value during the time the current controller 148 remains in the third mode in accordance with the teachings of the present invention. In one example, the relatively small value for the current is a constant current value that is substantially less than the current value during the second mode. In one example, the relatively small constant current value of the third mode is 5 per cent of the maximum current conducted in the second mode.

[0024] In the example of FIG. 1, feedback signal  $U_{FB}$  136 has substantially different characteristics that depend on the changes in modes of current controller 148 in accordance with the teachings of the present invention. For example, when current controller 148 changes between the second mode and the first mode, the feedback signal  $U_{FB}$  136 contains features that are not present when current controller 148 changes between the third mode and the first mode. Therefore, controller 142 includes a first feedback circuit 138 and a second feedback circuit 140 to interpret the feedback signal  $U_{FB}$  136 appropriately for the different modes of current controller 148 in accordance with the teachings of the present invention. Examples of other controllers may include more than two feedback circuits as required to interpret feedback signals that arise from different modes of operation.

**[0025]** In the example of FIG. 1, control circuit 144 included in controller 142 receives signals from first feedback circuit 138 and second feedback circuit 140 to control the output of the power converter as desired. Feedback circuits included in controller 142 may use any analog and digital circuits such as filter circuits, sample and hold circuits, and comparators, to extract necessary information from feedback signal  $U_{FB}$  136. Control circuit 144 included in controller 142 may use any analog and digital circuits, such as oscillators, comparators, digital logic, and state machines, or the like, to interpret and respond as required to information received from the feedback circuits.

**[0026]** FIG. 1 shows mode select signal 146 as a single line that in another example may represent several individual analog or digital signals. For example, two binary digital signals lines for control signal 146 may select as many as four distinct modes of current controller 148 in accordance with the teachings of the present invention.

**[0027]** FIG. 2 is a schematic diagram that shows another example of a switching power converter 200 that uses a flyback topology in accordance with teachings of the present invention. The example of FIG. 2 includes a coupled inductor 205 that has a primary winding 108, a secondary winding 112, and a bias winding 210. Bias winding 210 may also be referred to as an auxiliary winding. In one example, bias winding 210 in FIG. 2 is the sensor 134 introduced in FIG. 1 that produces feedback signal  $U_{FB}$  136. Bias winding 210 produces a voltage  $V_B$  215 that is responsive to the output voltage  $V_O$  120 when rectifier D1 114 on secondary winding 112 conducts. Sense signal 132, shown in FIG. 1 but not visible in FIG. 2, is the magnetic flux that couples bias winding 210 to secondary winding 112 of the coupled inductor 205. In another example, bias winding 210 may also provide a source of power to the circuits within controller 142.

[0028] It is appreciated that many variations are possible in the use of a bias winding to sense an output voltage and for providing sensing while also providing power to a controller with galvanic isolation. For example, a bias winding may apply a rectifier and a capacitor similar to rectifier D1 114 and capacitor C1 116, respectively, to produce a dc bias voltage while providing an ac feedback signal from the anode of the rectifier. As such, additional passive components such as resistors may be used on the bias winding to scale the voltage from the winding to a value that is more suitable to be received by controller 142.

[0029] Use of bias winding 210 to sense output voltage  $V_O$  120 has the advantages of providing galvanic isolation between output voltage  $V_O$  120 and controller 142 without the expense of an optocoupler. A disadvantage of using a winding on coupled inductor 205 to sense output voltage  $V_O$  120 is that the voltage  $V_B$  215 at bias winding 210 is representative of output  $V_O$  120 only when output rectifier D1 114 is conducting, whereas an optocoupler can provide continuous sensing of output voltage  $V_O$  120. Output rectifier D1 114 is conducting only while there is a pulse of current in secondary winding 112. Therefore, the time between pulses of current in secondary winding 112 is the time when controller 142 cannot sense output voltage  $V_O$  120. In other words, in contrast to sensing output voltage  $V_O$  120 continuously with an optocoupler, sensing output voltage  $V_O$  120 with a winding on coupled inductor 205 is limited to pulses that may not occur often enough to provide the necessary information for the desired control of output voltage  $V_O$  120. Since secondary winding 112 has a pulse of current only after primary winding 108 has a pulse of current, it is desirable to decrease the time between pulses of current in primary winding 108 so that controller 142 can sense output voltage  $V_O$  120 more often.

[0030] The rate and magnitude of pulsating current in primary winding 108 is controlled by controller 142 to provide the power required to maintain the desired output

voltage  $V_O$  120 over a range of values of load 122. As the load approaches zero, less current in primary winding 108 is needed to maintain the desired output voltage  $V_O$  120. As such, controllers may reduce the magnitude of the current in primary winding 108 as well as increase the time between pulses of current.

[0031] Controller 142 may produce pulses of current in primary winding 108 by providing current controller 148 with a mode select signal 146 that changes current controller 148 from the first mode to the second mode, allowing current  $I_P$  126 to increase with a linear slope to a desired maximum before returning to the first mode. Operation of current controller 148 in the second mode fully discharges capacitor  $C_P$  150 so that voltage  $V_P$  106 on primary winding 108 is equal to input voltage  $V_{IN}$  102.

[0032] All the energy stored on capacitor  $C_P$  150 is lost when current controller 148 operates in the second mode, even if the maximum current  $I_P$  126 is allowed to increase to the lowest practical value before returning to the first mode. The only way to reduce the power dissipated from the full discharge of capacitor  $C_P$  150 is to increase the time between discharges. In other words, increasing the time between pulses of primary current will reduce the power lost in the power converter as the load approaches zero at the expense of increasing the time where the controller 142 cannot sense the output voltage  $V_O$  120. As a consequence, a sudden increase in the load 122 may reduce the output voltage  $V_O$  120 to an unacceptable value before controller 142 can sense the voltage and respond to it.

[0033] A solution is discussed below that allows the controller 142 to sense the output voltage  $V_O$  120 frequently enough to respond adequately to a sudden increase in the load 122 while also reducing power dissipation at near zero load. This solution produces pulses of current in primary winding 108 without fully discharging capacitor  $C_P$  150. The solution is realized by the introduction of a third mode of operation for current controller 148

in accordance with the teachings of the present invention. In one example, the third mode of current controller 148 operates to put only enough current into primary winding 108 so that output rectifier D1 114 will conduct after current controller 148 returns to the first mode. The third mode of current controller 148 conducts current with a sufficiently low magnitude and duration to put the desired current into the primary winding while only partially discharging capacitor  $C_p$  150 in accordance with the teachings of the present invention. The determination of the proper value of current for a given application is discussed in detail later in this disclosure.

[0034] FIG. 3 shows voltage and current waveforms from the example power converter of FIG. 2 that illustrates the operation of an example controller in accordance with the teachings of the present invention that provides sensing of an isolated output voltage. As shown in the depicted example, pulses of current  $I_p$  126 that fully discharge capacitor  $C_p$  150 begin at times  $t_0$  310,  $t_{(N+1)}$  350, and  $t_{(N+2)}$  360. Pulses of current  $I_p$  126 that partially discharge capacitor  $C_p$  150 begin at times  $t_1$  320,  $t_2$  330, and  $t_N$  340 in accordance with the teachings of the present invention.

[0035] The distinction between pulses of current  $I_p$  126 that fully discharge capacitor  $C_p$  150 and pulses of current  $I_p$  126 that partially discharge capacitor  $C_p$  150 is clear in the waveform of  $V_{CP}$  128 that is the voltage on capacitor  $C_p$  150. Capacitor  $C_p$  150 is fully discharged when the voltage  $V_{CP}$  128 is substantially zero. Capacitor  $C_p$  150 is only partially discharged when the voltage  $V_{CP}$  128 remains substantially greater than zero when current  $I_p$  126 is greater than zero.

[0036] As shown, at the end of each full-discharge pulse and each partial-discharge pulse of current  $I_p$  126, voltage  $V_{CP}$  128 rises above the input voltage  $V_{IN}$  102 while energy from the energy transfer element (e.g., energy transfer element T1 105 in FIG. 1 and coupled

inductor 205 in FIG. 2) charges capacitor  $C_P$  150. Voltage  $V_{CP}$  128 rises until the output rectifier D1 114 conducts, clamping the voltage  $V_{CP}$  to the input voltage  $V_{IN}$  plus the reflected output voltage  $V_{OR}$ , where the reflected output voltage  $V_{OR}$  is the voltage on secondary winding 112 multiplied by the number of turns on primary winding 108 and divided by the number of turns on the secondary winding 112.

[0037] As shown, voltage  $V_{CP}$  128 remains clamped at the value of  $V_{IN}$  plus  $V_{OR}$  until output rectifier D1 114 stops conducting, which happens when the current from secondary winding 112 falls to zero. The energy stored in capacitor  $C_P$  150 that raised its voltage above  $V_{IN}$  102 then dissipates in a decaying oscillation with the self-inductance of primary winding 108 and the effective parasitic resistance of the circuit.

[0038] FIG. 3 also shows the voltage  $V_B$  215 in FIG. 2 that provides feedback signal  $U_{FB}$  136 to controller 142. Controller 142 may sense input voltage  $V_{IN}$  102 as well as output voltage  $V_O$  120 from bias voltage  $V_B$  215. During full-discharge pulses of current  $I_P$  126, bias voltage  $V_B$  215 goes negative to a magnitude  $V_{INS}$  that is representative of input voltage  $V_{IN}$  102. After a full-discharge pulse of current  $I_P$  126, output rectifier D1 114 conducts to allow sensing of output voltage  $V_O$  120 as a positive voltage  $V_{OS}$  on bias winding 210 that is representative of output voltage  $V_O$  120. After a pulse of current  $I_P$  126 that only partially discharges capacitor  $C_P$  150, output rectifier D1 114 conducts just enough to allow sensing of output voltage  $V_O$  120 with a decaying oscillation of bias voltage  $V_B$  215 as shown in FIG. 3.

[0039] In one example, when the load 122 is large enough to require full-discharge pulses of current  $I_P$  126 to maintain output voltage  $V_O$  120 at a desired value, the full-discharge pulses may occur as often as every switching period  $T_S$ . An example switching period  $T_S$  is the time between  $t_{(N+1)}$  350 and  $t_{(N+2)}$  360 in FIG. 3. Typically, light to moderate

loads may require patterns of full-discharge pulses separated by several switching periods of no current pulses.

**[0040]** In the example, when the load 122 is near zero, only partial-discharge pulses are used to sense the output voltage  $V_O$  120 at intervals much shorter than the period between full-discharge switching pulses in accordance with the teachings of the present invention. It is not necessary to use partial-discharge pulses to sense the output voltage  $V_O$  120 when the load 122 is sufficiently greater than zero because full-discharge pulses occur often enough at loads sufficiently greater than zero to provide adequate sensing of the output voltage. The partial-discharge pulses may be considered wake-up pulses that determine whether or not a full-discharge pulse is required. The times between partial-discharge pulses may be considered wake-up periods.

**[0041]** In the illustrated example, an example wake-up period  $T_{W1}$  is the time between  $t_1$  320 and  $t_2$  330 in FIG. 3. In one example, wake-up period  $T_{W1}$  is 16 switching periods  $T_S$ . In another example, wake-up pulses may be separated by wake-up periods of different durations. The first partial-discharge pulse in a train of partial-discharge pulses may follow a full-discharge pulse by a period that is different from any wake-up period within a train of wake-up pulses. FIG. 3 shows a period  $T_1$  that is the time between  $t_0$  310 at the start of a full-discharge pulse and time  $t_1$  320 that is the start of the first partial-discharge pulse in a train of partial-discharge pulses. In one example, the period  $T_1$  is 9 switching periods whereas  $T_{W1}$  is 16 switching periods.

**[0042]** In one example, control circuit 144 included in controller 142 may determine the need for full-discharge pulses, partial discharge pulses, or no pulse within a switching period  $T_S$  according to the value of feedback signal  $U_{FB}$  136 immediately after each pulse of current  $I_P$  126 in accordance with the teachings of the present invention. For

example, if a sequence of full-discharge pulses causes the sensed output voltage  $V_{OS}$  to rise beyond a first threshold value, control circuit 144 may set mode select signal 146 such that current controller 148 conducts no current for several subsequent switching periods  $T_S$ . If sensed output voltage  $V_{OS}$  remains above the first threshold value after the next full-discharge pulse, controller 142 may conclude that the load is near zero and begin using partial discharge pulses to sense the output voltage  $V_O$  120. The example of FIG. 3 illustrates an example in which control circuit 144 determined that sensed output voltage  $V_{OS}$  after the partial-discharge pulse at time  $T_N$  340 was too low, requiring consecutive full-discharge pulses at times  $t_{(N+1)}$  350 and  $t_{(N+2)}$  360.

**[0043]** In the example of FIG. 2, control circuit 144 interprets a signal received from first feedback circuit 138 after a full-discharge pulse, and control circuit 144 interprets a signal received from second feedback circuit 140 after a partial-discharge pulse in accordance with the teachings of the present invention. In the example of FIG. 2, first feedback circuit 138 samples feedback signal  $U_{FB}$  136 during the time when output rectifier D1 114 is conducting. In the example of FIG. 2, second feedback circuit 138 samples feedback signal  $U_{FB}$  136 during a decaying oscillation of the bias voltage  $V_B$  215 after output rectifier D1 114 stops conducting.

**[0044]** In the example, the peaks of the decaying oscillation in the bias voltage  $V_B$  215 are representative of output voltage  $V_O$  120 after output rectifier D1 114 stops conducting because capacitor  $C_P$  150 charges to a value representative of output voltage  $V_O$  120 when output rectifier D1 114 conducts after a partial-discharge pulse. The maximum voltage on capacitor  $C_P$  150 sets the initial condition for the decaying oscillation after output rectifier D1 114 stops conducting. Therefore, each peak in the decaying oscillation of bias

voltage  $V_B$  215 is determined by the maximum voltage on capacitor  $C_P$  150 after a partial-discharge pulse.

[0045] In the example of FIG. 2, first feedback circuit 138 samples feedback signal  $U_{FB}$  136 to regulate output voltage  $V_O$  120 over a wide range of loads. In contrast to first feedback circuit 138, second feedback circuit 140 in one example does not sample feedback signal  $U_{FB}$  136 to regulate output voltage  $V_O$  120 over a wide range of load. Instead, second feedback circuit 140 in the example is used only to determine whether or not there has been a sufficient change in the output voltage  $V_O$  120 during a train of partial-discharge pulses to require a change in operating mode in accordance with the teachings of the present invention.

[0046] Specifically, in one example, second feedback circuit 140 holds the value of the second peak in the decaying oscillation of feedback signal  $U_{FB}$  136, as illustrated for example in FIG. 3 with the decaying oscillations in  $V_B$  215 after the first partial-discharge pulse in a train of consecutive partial-discharge pulses, and compares it to samples of the second peak in the decaying oscillation of feedback signal  $U_{FB}$  136 after each subsequent partial-discharge pulse in the train of consecutive partial-discharge pulses. When the value of a subsequent sample is less than the value of the first sample by a threshold value, control circuit 144 determines that output voltage  $V_O$  120 is too low, and sets mode select signal 146 to start a sequence of full-discharge pulses. It is appreciated that any peak value in the decaying oscillation may be sampled for use in the comparison. In one example, the second peak value may be a preferred peak because it has the highest magnitude and is relatively free from noise and distortion that may be present on the first peak while the output rectifier D1 114 is conducting. In one example, the threshold value is 30 millivolts.

[0047] In one example, the magnitude and duration of a partial-discharge pulse are just sufficient to allow output rectifier D1 114 to conduct at the end of the partial-discharge

pulse. In another example, the magnitude and duration of a partial-discharge pulse are more than sufficient to allow output rectifier D1 144 to conduct at the end of the partial-discharge pulse. The output voltage  $V_O$  120 may be sensed with greater accuracy when output rectifier D1 144 is allowed to conduct until a transient voltage associated with non-ideal coupling of the windings of coupled inductor 205 reduces to a negligible value. The non-ideal coupling, sometimes quantified as a leakage inductance, may produce a voltage between output rectifier D1 144 and secondary winding 112 when diode D1 144 begins to conduct. The transient voltage owing to leakage inductance may also distort the first peak of the decaying oscillation. Therefore, it is desirable to allow the voltage from the leakage inductance to reduce to a negligible value so that capacitor  $C_P$  150 charges to a voltage that more accurately represents output voltage  $V_O$  120 before output rectifier D1 144 stops conducting. It is also desirable not to sample the first peak of the decaying oscillation to avoid distortion from the effects of leakage inductance.

**[0048]** In one example, the magnitude of the partial-discharge pulse is 16 milliamperes whereas the peak current of a full-discharge pulse is 250 milliamperes. As such, the energy transferred to the output by the partial-discharge pulse may be considered insignificant in comparison to the energy transferred to the output by the full-discharge pulse because the energy transferred is proportional to the square of the peak current in primary winding 108. It will be appreciated that since the partial-discharge pulse may transfer finite energy to the output, controllers that have a minimum switching frequency, however small, may require the power supply to have a dummy internal load to keep the output voltage  $V_O$  120 from going higher than desired as the output current  $I_O$  118 approaches zero.

**[0049]** It may be determined either analytically or experimentally that there is a magnitude and a duration for a partial-discharge pulse that gives a minimum power loss in

the power converter for a particular set of circumstances. The duration of the partial-discharge pulse is typically less than half of one period of the decaying oscillation of feedback signal  $U_{FB}$  136 as illustrated in FIG. 3. In one example, the duration of the partial-discharge pulse is approximately one quarter of one period of the decaying oscillation of feedback signal  $U_{FB}$  136. In one example where the inductance of the primary winding 108 of a coupled inductor is 2.2 millihenries, capacitor  $C_P$  150 is approximately 70 picofarads, the partial discharge pulse is 16 milliamperes for a duration of approximately 600 nanoseconds. It will be appreciated that in one example control circuit 144 may adjust the magnitude and duration of partial-discharge pulses to achieve minimum power loss in the power converter and to guarantee that output rectifier D1 114 conducts in accordance with the teachings of the present invention. This adjustment may be done, for example, in response to an external signal received by controller 144. The adjustment may also be done by choosing values of discrete components within control circuit 144. In examples where control circuit 144 is included in an integrated circuit, the adjustment may be done by trimming the internal parameters of the integrated circuit.

**[0050]** FIG. 4 is a schematic diagram of a power converter 400 that illustrates one example of current controller 148 in greater detail. In the example of FIG. 4, current controller 148 includes a mode selector 410 that receives mode select signal 146 from controller 142. In the example of FIG. 4, mode selector 410 closes either switch S1 420, or switch S2 440, or neither switch in response to mode select signal 146.

**[0051]** In the example of FIG. 4, the first mode opens switch S1 420 and switch S2 440 such that current  $I_P$  126 is substantially zero when current controller 148 is in the first mode. In the example of FIG. 4, the second mode closes switch S1 420 and opens switch S2 440 to fully discharge capacitor  $C_P$  150. In the example of FIG. 4, the third mode opens

switch S1 420 and closes switch S2 440 such that current  $I_p$  126 is the value of current source 430 to partially discharge capacitor  $C_p$  150 in accordance with the teachings of the present invention. It is appreciated that in other examples current source 430 could be a variable current source that varies in accordance with the degree of partial discharge of capacitor  $C_p$  150 desired.

**[0052]** FIG. 5 is a schematic diagram of a power converter 500 that shows another example of current controller 148 that includes a metal oxide semiconductor field-effect transistor (MOSFET) 520 and a tri-level driver 510 to produce full-discharge and partial-discharge pulses of current  $I_p$  126 in response to the mode select signal 146. In the example of FIG. 5, tri-level driver 510 responds to signals from mode selector 410 to produce at least three distinct values of a voltage between the gate terminal and the source terminal of n-channel MOSFET 520 in response to mode select signal 146. In one example, the gate terminal of MOSFET 520 may be considered as a control terminal of MOSFET 520.

**[0053]** In the example of FIG. 5, the first mode of current controller 148 applies a gate-to-source voltage substantially less than the threshold voltage of n-channel MOSFET 520. As a result, MOSFET 520 is substantially switched OFF in the first mode of operation of current controller 148. In the example of FIG. 5, the second mode of current controller 148 applies a gate-to-source voltage substantially greater than the threshold voltage of n-channel MOSFET 520. As a result, MOSFET 520 is substantially switched ON in the second mode of operation of current controller 148. In the example of FIG. 5, the third mode of current controller 148 applies a gate-to-source-voltage slightly higher than the threshold voltage of n-channel MOSFET 520. As a result, the gate-to-source voltage at the control terminal of MOSFET 520 in the third mode corresponds to MOSFET 520 providing a partial-discharge current pulse for the magnitude of current  $I_p$  126. In other words, when in the third

mode of operation, MOSFET 520 operates not as a switch that may be either open or closed, but in its saturation region, sometimes called the active region, where the drain current is controlled primarily by the gate-to-source voltage and is substantially independent of the drain-to-source voltage. In examples where MOSFET 520 and tri-level driver 510 are included in an integrated circuit, tri-level driver 510 may be designed such that the voltage applied to the gate during the third mode of current controller 148 tracks the threshold voltage of MOSFET 520, thereby reducing the change in partial-discharge current over a range of temperature and process variations. It is appreciated that in other examples, tri-level driver 510 could have four or more drive levels to select different MOSFET 520 saturation characteristics according to the degree of partial discharge of capacitor  $C_P$  150 desired.

**[0054]** FIG. 6 is a flow diagram 600 that shows one example method to control a power converter in accordance with the teachings of the present invention providing for sensing of an isolated output. After starting in block 605, a current controller is operated in full capacitance discharge mode in block 610 to produce a current pulse that fully discharges capacitance on a node of the current controller.

**[0055]** Next, a first feedback circuit senses the isolated output voltage in block 615. In block 620, information from feedback circuits is processed to estimate the condition of the load. Then, in decision block 625, the flow continues to block 630 if the load is near zero, or branches back to block 610 if the load is not near zero. In one example, the load is considered near zero when the full-discharge pulses occur at intervals greater than the wake-up period  $T_{W1}$  of FIG. 3.

**[0056]** In block 630, the current controller is operated in partial capacitance discharge mode to produce a current pulse that only partially discharges a capacitance on a node of the current controller. Then a second feedback circuit senses the isolated output

voltage in block 635 before returning to block 620 where the information from feedback circuits is processed.

**[0057]** The above description of illustrated examples of the present invention, including what is described in the Abstract, are not intended to be exhaustive or to be limitation to the precise forms disclosed. While specific embodiments of, and examples for, the invention are described herein for illustrative purposes, various equivalent modifications are possible without departing from the broader spirit and scope of the present invention. Indeed, it is appreciated that the specific voltages, currents, frequencies, power range values, times, etc., are provided for explanation purposes and that other values may also be employed in other embodiments and examples in accordance with the teachings of the present invention.

**[0058]** These modifications can be made to examples of the invention in light of the above detailed description. The terms used in the following claims should not be construed to limit the invention to the specific embodiments disclosed in the specification and the claims. Rather, the scope is to be determined entirely by the following claims, which are to be construed in accordance with established doctrines of claim interpretation. The present specification and figures are accordingly to be regarded as illustrative rather than restrictive.

1. A controller for use in a power converter, comprising:

a current controller to be coupled to an energy transfer element and an input of the power converter;

a control circuit to generate a mode select signal coupled to be received by the current controller, wherein a first, second or third current is enabled in the current controller in response to a selection of a first, second or third mode of operation, respectively, of the current controller by the control circuit, wherein the first current is substantially zero, the second current is greater than the third current and the third current is greater than the first current;

a first feedback circuit coupled to the control circuit and coupled to generate a first feedback signal representative of an output of the power converter during the first mode of operation after a period of operation of the second mode of operation of the current controller; and

a second feedback circuit coupled to the control circuit and coupled to generate a second feedback signal representative of the output of the power converter during the first mode of operation after a period of operation of the third mode of operation of the current controller, wherein the control circuit is coupled to control selection of the first, second or third modes of operation in response to the first and second feedback signals to control a transfer of energy from the input of the power converter to the output of the power converter.

2. The controller of claim 1 wherein the current controller comprises a transistor to be coupled to the energy transfer element and the input of the power converter.

3. The controller of claim 2 wherein current controller further comprises a tri-level driver to provide a voltage having first, second and third values to a control terminal of the transistor in response to the mode select signal.

4. The controller of claim 2 wherein the transistor is coupled to be OFF during the first mode of operation.

5. The controller of claim 2 wherein the transistor is coupled to be ON during the second mode of operation.

6. The controller of claim 2 wherein the transistor is coupled to provide a partial-discharge current pulse in the third mode of operation.

7. The controller of claim 2 wherein a capacitance coupled to the transistor is only partially discharged in the third mode of operation.

8. The controller of claim 2 wherein the transistor is coupled to operate in its saturation region in the third mode of operation.

9. The controller of claim 1 wherein the first feedback circuit is coupled to the energy transfer element to generate the first feedback signal in response to a reflected signal representative of the output of the power converter.

10. The controller of claim 1 wherein the second feedback circuit is coupled to the energy transfer element to generate the second feedback signal in response to a portion of a decaying oscillation in a reflected signal representative of the output of the power converter.

11. A method of controlling a power converter, comprising:

controlling a current from an input of the power converter using a first and a second mode of operation to control a transfer of energy from the input of the power converter to an output of the power converter, wherein a capacitance coupled to the input of the power converter is fully discharged during the second mode of operation;

sensing a first quantity representative of the output of the power converter during the first mode of operation after a period of operation of the second mode of operation;

controlling the current from the input of the power converter using the first and a third mode of operation to sense the output of the power converter, wherein the capacitance coupled to the input of the power converter is only partially discharged during the third mode of operation; and

sensing a second quantity representative of the output of the power converter during the first mode of operation after a period of operation of the third mode of operation.

12. The method of controlling the power converter of claim 11 further comprising maintaining operation of the converter in the first and the second mode of operation in

response to the sensing of the first quantity representative of the output of the power converter.

13. The method of controlling the power converter of claim 11 wherein controlling the current from the input of the power converter using the first and the second mode of operation comprises enabling a first current in a current controller in response to a selection of the first mode of operation, and enabling a second current in the current controller in response to a selection of the second mode operation, wherein the second current is greater than the first current, and wherein the first current is substantially zero.

14. The method of controlling the power converter of claim 13 wherein controlling the current from the input of the power converter using the first and the third mode of operation further comprises enabling a third current in the current controller in response to a selection of the third mode of operation, wherein the second current is greater than the third current, and wherein the third current is greater than the first current.

15. The method of claim 11 wherein sensing the first quantity representative of the output of the power converter comprises sensing a reflected signal representative of the output of the power converter.

16. The method of claim 11 wherein sensing the second quantity representative of the output of the power converter comprises sensing a decaying oscillation of a reflected signal representative of the output of the power converter.

17. The method of claim 11 wherein controlling the current from the input of the power converter using the first and the second mode of operation comprises switching a transistor OFF and ON.

18. The method of claim 11 wherein controlling the current from the input of the power converter using the first and the third mode of operation comprises switching a transistor OFF in the first mode of operation, and discharging only partially a capacitance coupled to the transistor in the third mode of operation.

19. The method of claim 11 wherein controlling the current from the input of the power converter using the third mode of operation comprises operating a transistor in its saturation region.

20. The method of claim 19 wherein a gate-to-source-voltage of the transistor is only slightly higher than a threshold voltage of the transistor when the transistor is operating in its saturation region.

21. A power converter, comprising:

an energy transfer element coupled between an input of the power converter and an output of the power converter;

a current controller coupled to the energy transfer element, the current controller having a first, second and third mode of operation, wherein the second mode of operation enables a second current through the energy transfer element, wherein the third mode of operation enables a third current through the energy transfer element, wherein the first mode

of operation enables substantially zero current through the energy transfer element, wherein the second current is greater than the third current and wherein the third current is greater than substantially zero;

a control circuit coupled to the current controller to select the first, second or third mode of operation for the current controller;

a first feedback circuit coupled to the control circuit and coupled to generate a first feedback signal representative of an output of the power converter during the first mode of operation after a period of operation of the second mode of operation of the current controller; and