(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6251661号

(P6251661)

(45) 発行日 平成29年12月20日(2017.12.20)

(24) 登録日 平成29年12月1日(2017.12.1)

|              |            |

|--------------|------------|

| (51) Int.Cl. | F 1        |

| HO4R 19/00   | (2006.01)  |

| HO4R 31/00   | (2006.01)  |

| HO1L 29/84   | (2006.01)  |

| B81C 1/00    | (2006.01)  |

| B81B 3/00    | (2006.01)  |

| HO4R 19/00   | HO4R 31/00 |

| HO1L 29/84   | B81C 1/00  |

| B81B 3/00    | B81B 3/00  |

請求項の数 15 (全 23 頁) 最終頁に続く

(21) 出願番号 特願2014-196805 (P2014-196805)

(22) 出願日 平成26年9月26日 (2014.9.26)

(65) 公開番号 特開2016-72661 (P2016-72661A)

(43) 公開日 平成28年5月9日 (2016.5.9)

審査請求日 平成28年9月28日 (2016.9.28)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 110000888

特許業務法人 山王坂特許事務所

(72) 発明者 町田 俊太郎

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72) 発明者 龍崎 大介

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72) 発明者 永田 達也

東京都三鷹市牟礼六丁目22番1号 日立アロカメディカル株式会社内

最終頁に続く

(54) 【発明の名称】超音波トランステューサ、その製造方法、超音波トランステューサアレイ及び超音波検査装置

## (57) 【特許請求の範囲】

## 【請求項1】

基板と、前記基板の上に形成された第一導電膜と、前記第一導電膜の上に形成された第一絶縁膜及び第二絶縁膜と、前記第一絶縁膜と第二絶縁膜との間に設けられた空洞部と、前記第二絶縁膜の上に形成された第二導電膜と、前記第二導電膜を覆う第三絶縁膜と、を備え、

前記基板と前記第一導電膜との間に、前記基板の反りを防止する反り防止層を設けたことを特徴とする超音波トランステューサ。

## 【請求項2】

請求項1に記載の超音波トランステューサであって、

10

前記基板側を下側、前記第三絶縁膜側を上側とするとき、

前記反り防止層は、前記第一絶縁膜より上側にある層で構成されるメンブレンの残留応力を打ち消す方向の応力を発生する材料からなる膜を含むことを特徴とする超音波トランステューサ。

## 【請求項3】

請求項1又は2に記載の超音波トランステューサであって、

前記第一及び第二絶縁膜はシリコン酸化膜で構成され、前記反り防止層はシリコン窒化膜を含むことを特徴とする超音波トランステューサ。

## 【請求項4】

請求項1又は2に記載の超音波トランステューサであって、

20

前記第一導電膜と前記反り防止層との間に、第四絶縁膜を設けたことを特徴とする超音波トランスデューサ。

【請求項 5】

請求項 4 に記載の超音波トランスデューサであって、

前記反り防止層はシリコン窒化膜であり、前記第四絶縁膜はシリコン酸化膜であることを特徴とする超音波トランスデューサ。

【請求項 6】

基板上の所定の領域に、第一導電膜、第一絶縁膜、第二絶縁膜、第二導電膜及び第三絶縁膜を含む複数の層をパターニングによって形成し、複数の超音波トランスデューサを製造する方法であって、

10

前記パターニングと同じ工程において、前記基板上の、前記所定の領域を除く外側の領域に、前記基板の反りを抑制する反り防止層を所定のパターンで形成することを特徴とする超音波トランスデューサの製造方法。

【請求項 7】

請求項 6 に記載の超音波トランスデューサの製造方法であって、

前記反り防止層は、超音波トランスデューサと共に有する積層膜であることを特徴とする超音波トランスデューサの製造方法。

【請求項 8】

請求項 7 に記載の超音波トランスデューサの製造方法であって、

前記所定のパターンは、複数の超音波トランスデューサからなる超音波トランスデューサアレイのパターンと同一のパターンであることを特徴とする超音波トランスデューサの製造方法。

20

【請求項 9】

請求項 7 に記載の超音波トランスデューサの製造方法であって、

前記所定のパターンは、大きさの異なる複数のパターンから構成されていることを特徴とする超音波トランスデューサの製造方法。

【請求項 10】

請求項 6 に記載の超音波トランスデューサの製造方法であって、

前記所定のパターンは、前記反り防止層を互いに独立した複数の区分に分割するパターンであることを特徴とする超音波トランスデューサの製造方法。

30

【請求項 11】

請求項 6 に記載の超音波トランスデューサの製造方法であって、

前記基板は円形であって、前記所定の領域は前記円に内接する多角形であることを特徴とする超音波トランスデューサの製造方法。

【請求項 12】

基板と、前記基板の上に形成された第一導電膜と、前記第一導電膜の上に形成された第一絶縁膜及び第二絶縁膜と、前記第一絶縁膜と第二絶縁膜との間に設けられた空洞部と、前記第二絶縁膜の上に形成された第二導電膜と、前記第二導電膜を覆う第三絶縁膜と、を備えた超音波トランスデューサを複数配列してなる超音波トランスデューサアレイであつて、請求項 6 記載の製造方法で製造された超音波トランスデューサアレイ。

40

【請求項 13】

請求項 12 に記載の超音波トランスデューサアレイであって、

前記第一絶縁膜及び第二絶縁膜はシリコン酸化膜で構成され、前記基板と前記第一導電膜との間に、シリコン窒化膜を含む反り防止層を有することを特徴とする超音波トランスデューサアレイ。

【請求項 14】

請求項 13 に記載の超音波トランスデューサアレイであって、

前記反り防止層と前記第一導電膜との間に、さらに、シリコン酸化膜で構成される絶縁膜を含むことを特徴とする超音波トランスデューサアレイ。

【請求項 15】

50

超音波トランスデューサを内蔵する超音波探触子と、前記超音波探触子に超音波信号を送信するとともに前記超音波探触子が検出した超音波信号を受信する超音波送受信回路と、前記超音波送受信回路が受信した超音波信号を用いて画像を作成する画像作成部とを備え、

前記超音波探触子が、基板と、前記基板の上に形成された第一導電膜と、前記第一導電膜の上に形成された第一絶縁膜及び第二絶縁膜と、前記第一絶縁膜と第二絶縁膜との間に設けられた空洞部と、前記第二絶縁膜の上に形成された第二導電膜と、前記第二導電膜を覆う第三絶縁膜と、前記基板と前記第一導電膜との間に配置され、前記基板の反りを防止する反り防止層と、を備えた超音波トランスデューサを内蔵する超音波探触子である超音波検査装置。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、超音波トランスデューサの製造技術に関し、特にMEMS (Micro Electro Mechanical System) 技術により製造した超音波トランスデューサの構造と、その製造方法に適用して有効な技術に関する。

##### 【背景技術】

##### 【0002】

超音波トランスデューサは、超音波を送信、受信することにより、人体を非侵襲的に検査、診断する超音波診断装置や、建造物に発生した亀裂などを検査する超音波検査装置など様々な用途に用いられている。

20

##### 【0003】

従来の超音波トランスデューサは、圧電体の振動を利用したものであるが、近年のMEMS技術の進歩により、振動部をシリコン基板上に作製した静電容量検出型超音波トランスデューサ(CMUT: Capacitive Micromachined Ultrasonic Transducer)が開発されている(特許文献1)。

##### 【0004】

CMUTは、空洞部を挟んで上下電極を配置した構造を有し、従来の圧電体を用いた超音波トランスデューサと比較して、使用できる超音波の周波数帯域が広い、あるいは高感度である、またLSI加工技術を用いて作製するので微細加工が可能である、などの利点があり、上述した超音波検査装置等にも実用化が進んでいる(特許文献2、特許文献3)。

30

##### 【0005】

特許文献2には、空洞部に面する下部電極と上部電極をそれぞれ絶縁膜で覆った構造が開示され、特許文献3には、シリコン基板とCMUTとの電極の間の電気的な絶縁のため、空洞部を除いて、上部電極及び下部電極をシリコン窒化膜からなる絶縁層で覆った構造を持つCMUTが開示されている。

##### 【0006】

40

CMUTによる超音波の送信は、空洞を挟んで配置される上下電極間に直流電圧と交流電圧を重畠印加することによって、上下電極間に静電気力が発生し、空洞から上の膜で構成されるメンブレンが交流電圧の周波数で振動することにより実現される。またCMUTによる超音波の受信は、超音波の圧力を受けてメンブレンが振動することによって、上下電極間の距離が変化し、この距離の変化が静電容量の変化として検出されることにより実現される。

##### 【0007】

このようなCMUTの超音波送受信の原理から、CMUTの設計においては上下電極間の距離を適切に決めることが重要である。上下電極間の距離は、空洞部の厚みと空洞を挟んで設けられる絶縁膜の厚みで決まり、空洞部の厚みを一定にするためにメンブレンの形

50

状を平坦に保つこと、すなわちメンブレンが変形して空洞部の厚みが変化しないことが重要である。このため従来の CMUT 設計（例えば、特許文献 2）では、空洞部の直上となる絶縁層に低い引張応力の窒化シリコンからなる絶縁膜を配置する等、メンブレンの層構成を工夫している。

【先行技術文献】

【特許文献】

【0008】

【特許文献 1】米国特許第 6 3 2 0 2 3 9 B 1 明細書

【特許文献 2】特開 2013 - 150198 号公報

【特許文献 3】特開 2009 - 207882 号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0009】

MEMS 技術では、CMUT は基板上に CMUT を構成する各層を順次パターニングして成膜することにより製造される。この際、空洞部については、まず犠牲層を成膜し、その上に絶縁膜等を形成した後に、エッチング孔を介して犠牲層をエッチング除去することにより形成される。

【0010】

このような製造工程において、基板上に形成される各膜の残留応力によって、基板に反りが生じる場合がある。基板に大きな反りが生じると、CMUT の製造工程において製造装置のステージへ吸着ができないなどの不具合を生じ、プロセス処理ができなくなる。また、ウェハからチップを切り出して、超音波探触子に組み立てる工程において、ウェハやチップの反りにより、ウェハやチップの割れやその他の不良が発生する可能性も大きい。

20

【0011】

基板の反りは、基板の上に積層される膜の性質を制御することにより抑制できる可能性があるが、上述したように、基板上に形成される絶縁膜等の膜は CMUT の特性（駆動電圧や受信感度）を最適化するように設計されており、基板の反りを防止するために膜構成を変化させることは好ましくない。

【0012】

そこで本発明は、CMUT の特性を保ち、且つメンブレンの歪みを抑制するように最適化した膜構成に影響を与えることなく、CMUT を形成した基板の反りの抑制できる構造とその製造方法を提供することである。

30

【課題を解決するための手段】

【0013】

本発明は、CMUT の特性を決定するメンブレン以外の領域或いは位置に、基板の反りを防止する構造を設けたことが特徴である。反り防止構造には、大きく分けて次の 2 つの態様がある。

【0014】

一つは、CMUT の下部電極より下側、即ち下部電極と基板との間に、基板の反りを防止する層を設ける態様である。他の一つは、基板の、CMUT が設けられる領域以外の領域に、基板の反りを防止する層を設ける態様である。これら二つの態様は、組み合わせることも可能である。

40

【発明の効果】

【0015】

本発明によれば、超音波トランステューサの特性を阻害することなく、基板の反りを防止することができる。これにより超音波トランステューサ製造時や超音波探触子組み立て時において、基板の反りに起因する諸問題を解決することができる。

【図面の簡単な説明】

【0016】

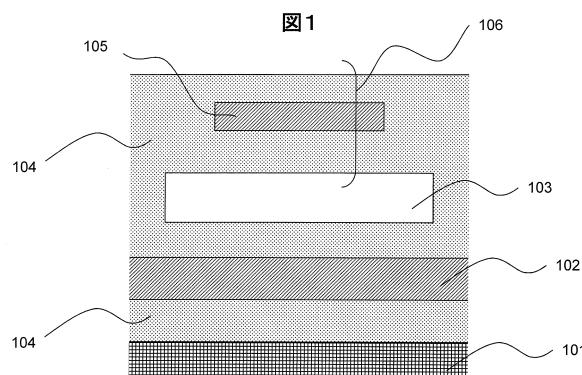

【図 1】一般的な CMUT の構造を示す断面図

50

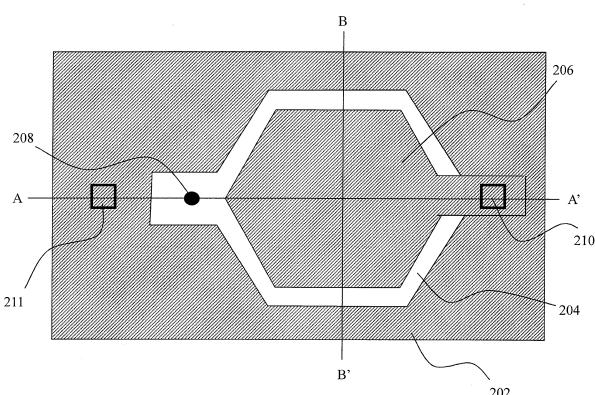

**【図2】第一の実施形態の超音波トランスデューサの上面から見た第一導電膜、空洞部及び第二導電膜の関係を示す図**

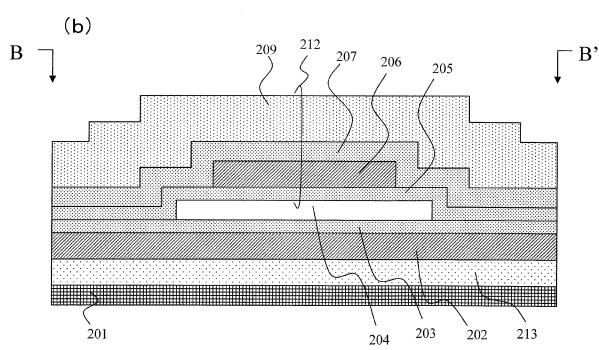

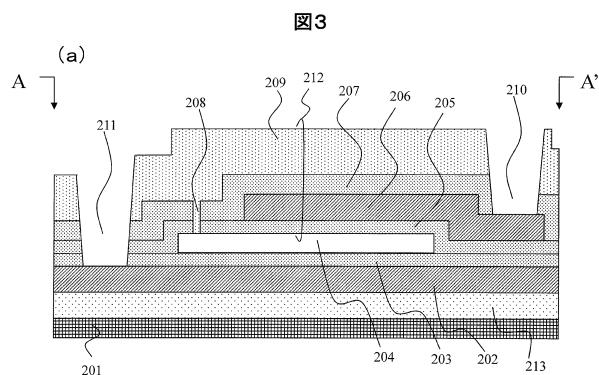

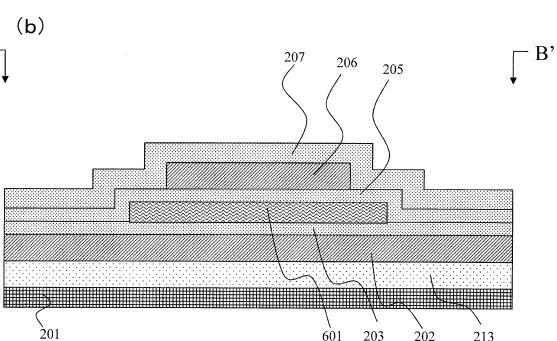

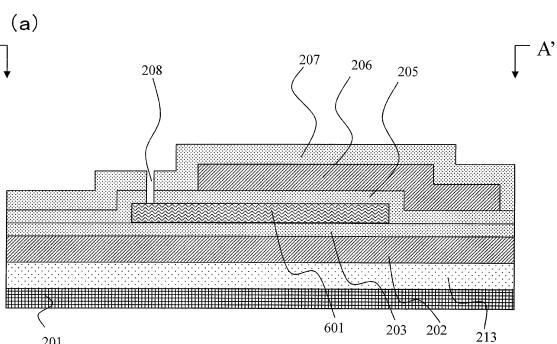

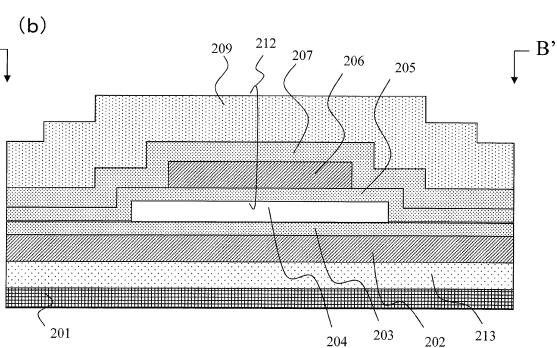

**【図3】第一の実施形態（第一実施例）の超音波トランスデューサを示す図で、（a）は図2のA-A'線断面図、（b）はB-B'線断面図**

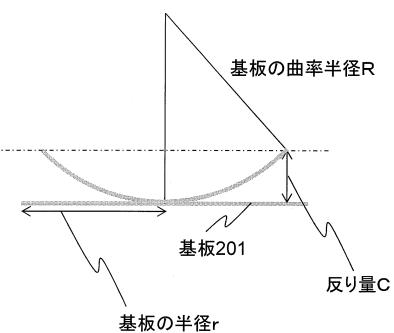

**【図4】CMUTの基板の反りの発生と反り量を説明する図**

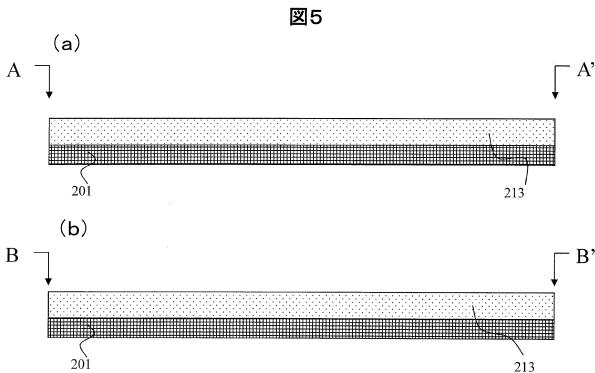

**【図5】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第一工程を示す図**

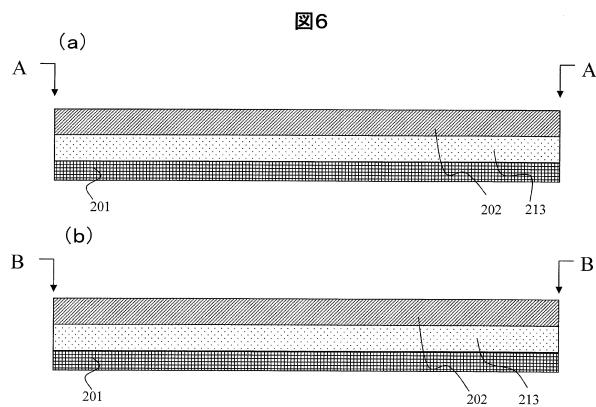

**【図6】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第二工程を示す図**

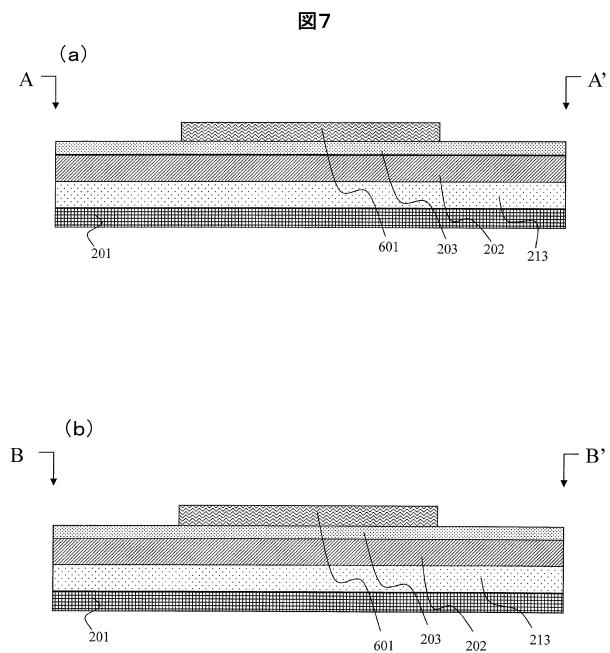

**【図7】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第三工程を示す図**

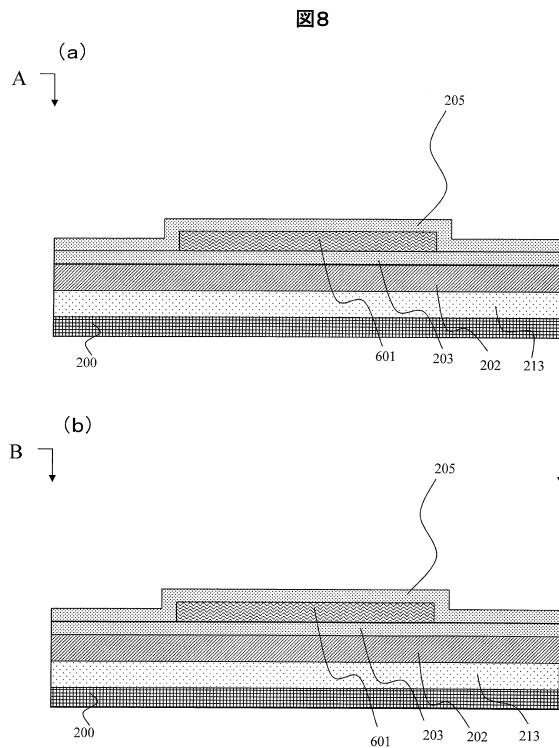

**【図8】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第四工程を示す図**

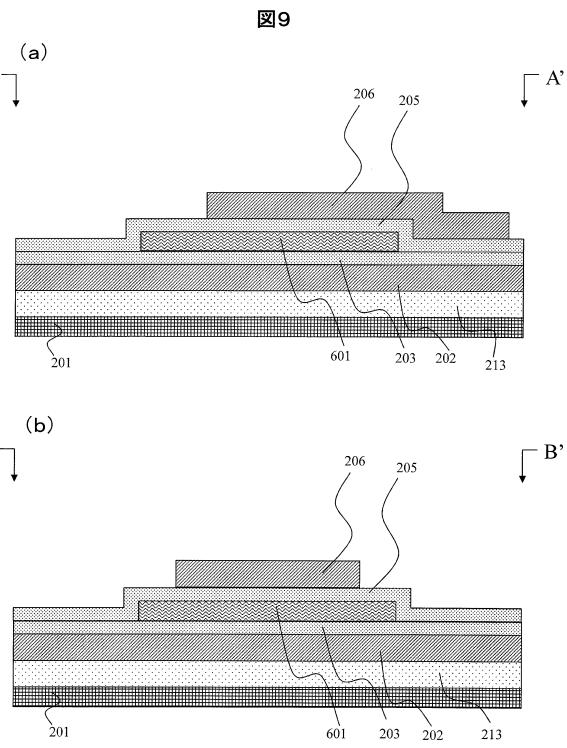

**【図9】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第五工程を示す図**

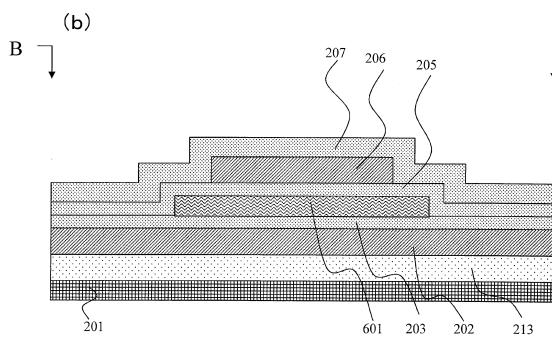

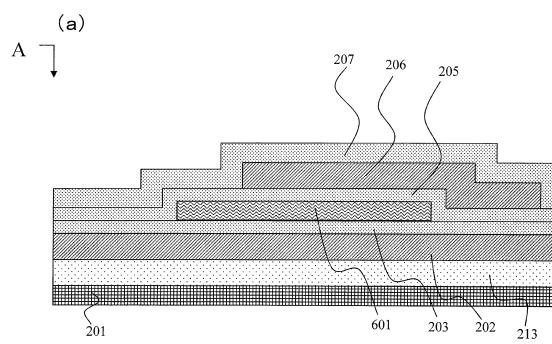

**【図10】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第六工程を示す図**

**【図11】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第七工程を示す図**

**【図12】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第八工程を示す図**

**【図13】（a）、（b）は、第一実施形態の超音波トランスデューサの製造方法の第九工程を示す図**

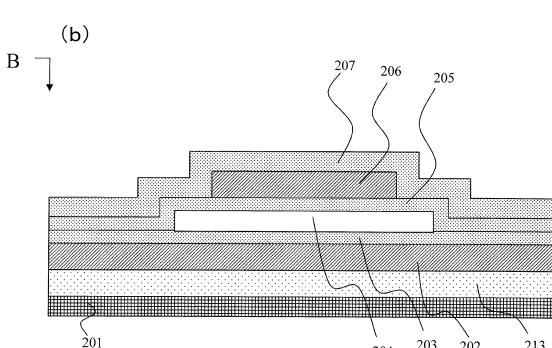

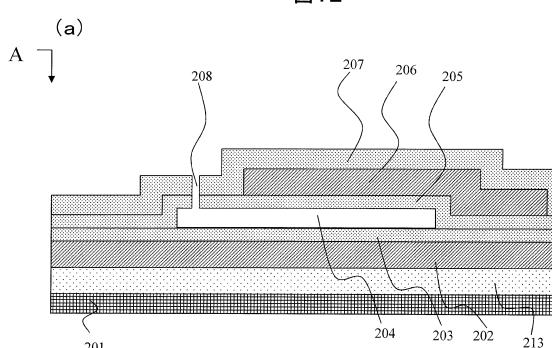

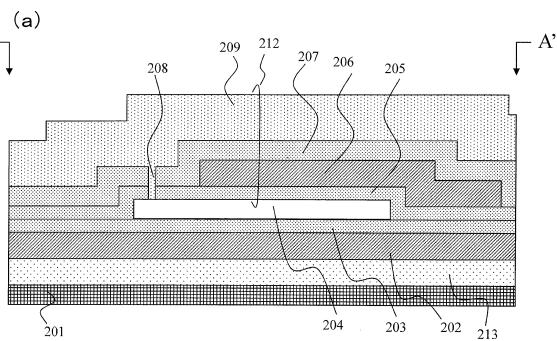

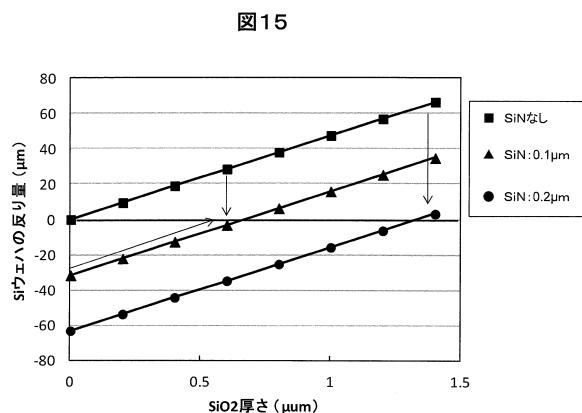

**【図14】第一の実施形態（第二実施例）の超音波トランスデューサを示す図で、（a）は図2のA-A'線断面図、（b）はB-B'線断面図**

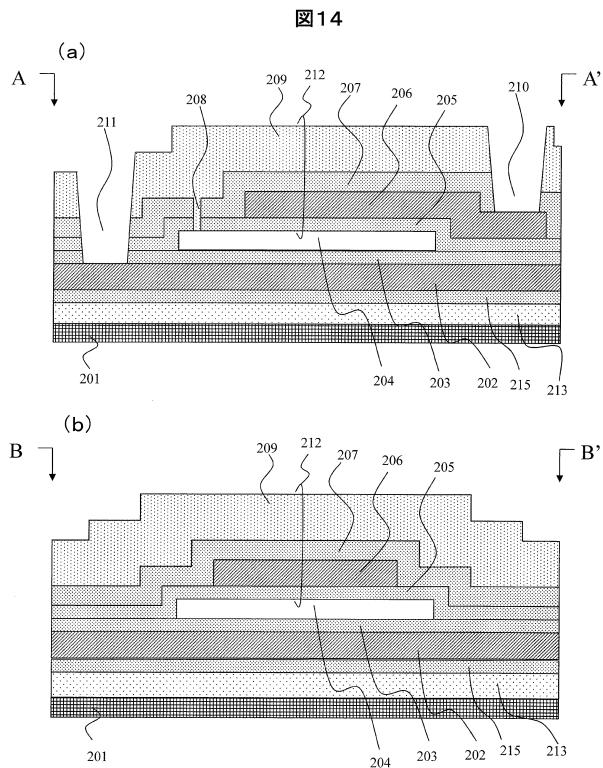

**【図15】第一の実施形態（第二実施例）における反り防止層の膜厚と反り量との関係を示す図**

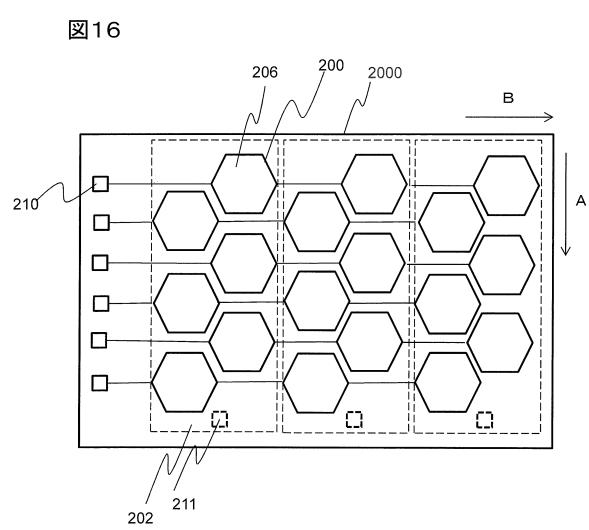

**【図16】第一の実施形態（第三実施例）の超音波トランスデューサアレイの上面図**

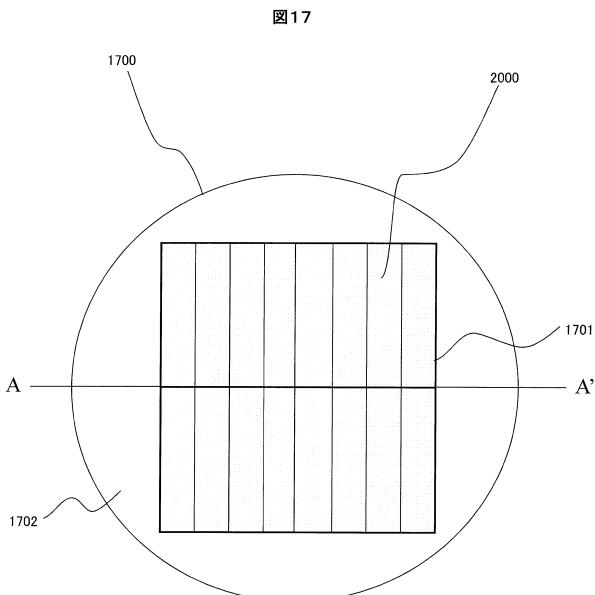

**【図17】第二の実施形態の超音波トランスデューサアレイの製造方法を説明する図で、基板の上面から見た図**

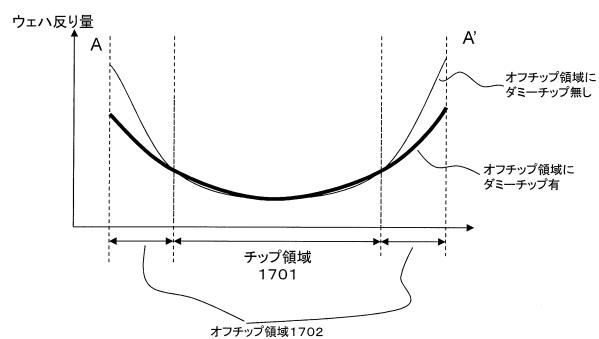

**【図18】基板の反りを説明する図**

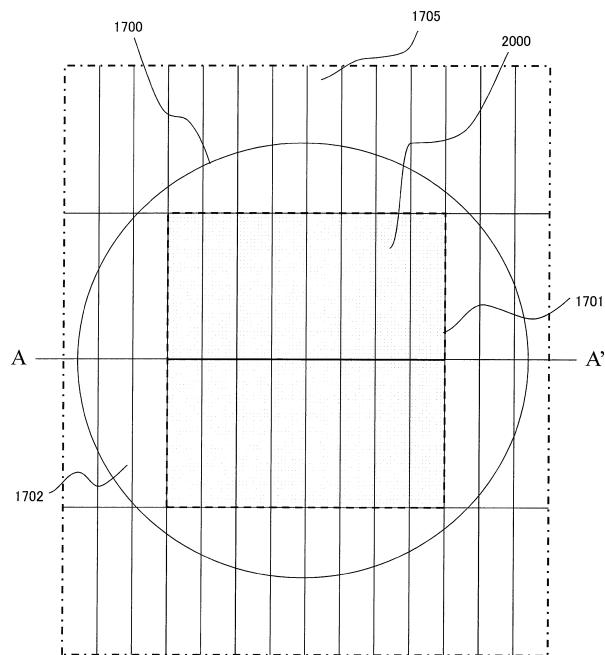

**【図19】第二の実施形態のCMUT及びオフチップ領域のパターン例（第四実施例）を示す図**

**【図20】第二の実施形態のCMUT及びオフチップ領域のパターン例（第五実施例）を示す図**

**【図21】第二の実施形態のCMUT及びオフチップ領域のパターン例（第六実施例）を示す図**

**【図22】図21のパターンの一部の拡大上面図**

**【図23】図21のパターンの一部の拡大断面図**

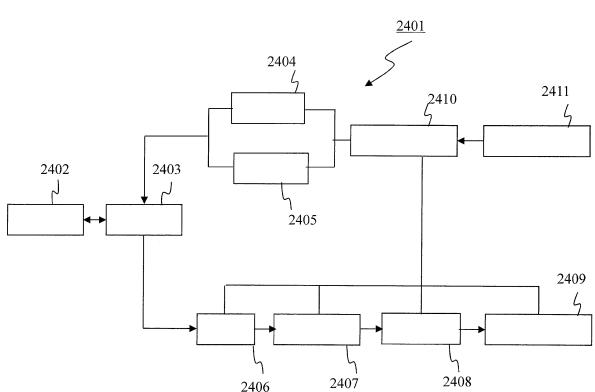

**【図24】超音波検査装置の一実施形態を示す全体ブロック図**

**【発明を実施するための形態】**

**【0017】**

以下、本発明の超音波トランスデューサ、超音波トランスデューサの製造方法、及び超音波検査装置の各実施形態を、図面を参照して説明する。

**【0018】**

なお、以下の実施形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施形態においては、便宜上、その必要があるときは、複数のセクションまたは実施例に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

10

20

30

40

50

**【 0 0 1 9 】**

また、以下の実施形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。更に、以下の実施形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

**【 0 0 2 0 】**

同様に、以下の実施形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。なお、平面図であっても理解を容易にするため、ハッチングを付す場合がある。

10

**【 0 0 2 1 】**

## &lt; 第一の実施形態 &gt;

最初に、本発明の超音波トランスデューサの実施形態を参照して説明する。

本実施形態の超音波トランスデューサは、基板と、前記基板の上に形成された第一導電膜と、前記第一導電膜の上に形成された第一絶縁膜及び第二絶縁膜と、前記第一絶縁膜と第二絶縁膜との間に設けられた空洞部と、前記第二絶縁膜の上に形成された第二導電膜と、前記第二導電膜を覆う第三絶縁膜と、を備え、前記基板と前記第一導電膜との間に、前記基板の反りを防止する反り防止層を設けたものである。

20

**【 0 0 2 2 】**

また本実施形態の超音波トランスデューサは、前記基板側を下側、前記第三絶縁膜側を上側とするとき、前記反り防止層は、前記第一絶縁膜より上側にある層で構成されるメンブレンの残留応力を打ち消す方向の応力を発生する材料からなる膜を含む。

**【 0 0 2 3 】**

本実施形態の超音波トランスデューサは、基板上にMEMS技術によって形成された所謂CMUTであり、単独の素子であってもよいし、CMUT素子を多数配置したCMUTアレイ或いはCMUTチップ（以下、総称してCMUTチップという）であってもよい。

以下、単独のCMUT素子を例に、本実施形態の超音波トランスデューサを詳述する。

30

**【 0 0 2 4 】**

## &lt;&lt; 第一実施例 &gt;&gt;

本実施例の超音波トランスデューサは、基板と、CMUTを構成する第一導電膜との間に、引張応力を持つ層を反り防止層として設けたことが特徴である。

**【 0 0 2 5 】**

まず一般的なCMUTの構造を説明する。CMUTは、図1の断面図に示すように、基板101の上層に絶縁膜104を介して下部電極102が形成され、その上層に絶縁膜104に囲まれた空洞部103が形成されている。また空洞部103の上方の、空洞部103に重なる位置に上部電極105が形成されている。空洞部103の上層の絶縁膜104と上部電極105により、振動するメンブレン106が構成されている。上部電極105と下部電極102の間に直流電圧と交流電圧を重畠すると、静電気力が上部電極105と下部電極102の間に働き、メンブレン106が印加した交流電圧の周波数で振動することで、超音波を発信する。逆に、受信の場合は、メンブレン106の表面に到達した超音波の圧力により、メンブレン106が振動する。すると、上部電極105と下部電極102との間の距離が変化するため、静電容量の変化として超音波を検出できる。

40

**【 0 0 2 6 】**

本実施例の超音波トランスデューサも、基本的な構造は上述したCMUTと同様であるが、本実施例の超音波トランスデューサは、基板101と下部電極（第一導電膜）102との間の絶縁膜104が、下部電極102から上の層の残留応力によって基板101に発生する反りを防止する膜（反り防止層）である点が特徴である。

50

**【0027】**

以下、図2及び図3を参照して、本実施例の超音波トランスデューサの詳細を説明する。

図2は、本実施例の超音波トランスデューサを上面（基板と反対側）から見た図であり、下部電極（第一導電膜）202、空洞部204及び上部電極（第二導電膜）203の位置関係を示している。上部電極206は、上面から見た形状が空洞部204とほぼ同じ形状を有し、空洞部204によって下部電極202と離間して下部電極202と対向している。空洞部204の下側に位置する下部電極202と、空洞部204の上側に位置する上部電極206の重なる面積によって、このトランスデューサの静電容量が決まる。

**【0028】**

10

なお、図2において、空洞部204と上部電極206は、基板の上面からみて六角形の形状をしているが、形状はこれに限らず、例えば、円形でも矩形形状をしていてもよい。

**【0029】**

下部電極202は、図2のA-A'断面図及びB-B'断面図である図3(a)、(b)に示すように、基板201の上に反り防止膜213を介して設けられており、その上に第一絶縁膜203、第二絶縁膜205、上部電極206、第三絶縁膜207及び保護絶縁膜209が積層されている。これら絶縁膜203、205、207及び209の一部又は全部を適宜包括的に絶縁膜という。また絶縁膜を貫通して、下部電極202及び上部電極206へ外部から電圧を供給するためのパッド開口211、210が設けられている。

**【0030】**

20

空洞部204は、絶縁膜（第一絶縁膜203及び第二絶縁膜205）に囲まれており、空洞部204の上側に位置する層、即ち第二絶縁層205、上部電極206、第三絶縁膜207及び保護絶縁膜209は、下部電極202と上部電極206との間に交流電圧を印加したときに振動するメンブレン212を構成する。

**【0031】**

上下電極間の距離を決定する、電極間に挟まれる絶縁膜203、205の厚さと、空洞部204の厚さは、CMUTの駆動電圧やサイズに応じて決められ、CMUTの安定した動作を確保するために適切に制御される。絶縁膜の厚さについては、CMUTを製造する際の絶縁膜の成膜工程において制御することで、十分な精度を実現できる。空洞部204の厚さは、初期的には、後述するCMUT製造工程において、空洞部204を形成するために設けられる犠牲層の厚みで決まるが、さらにメンブレン212の変形を抑制するために、空洞部212より上層の絶縁膜205、207、209及び上部電極105の、それぞれの残留応力と厚さを調整してメンブレンの形状を平坦に保つよう設計する。例えば、絶縁膜205、207、209として残留応力の異なる材料を組み合わせて、その応力を調整する。

30

**【0032】**

また電極に接する絶縁膜203、205、207としては、膜中に電荷トラップサイトが極力少ない材料を選択することが好ましい。その理由は、電荷トラップサイトが多い場合、電荷トラップサイトを介したリーク電流が増え、印加電圧が低下し安定した動作が確保できなくなるためである。

40

**【0033】**

上述したCMUTの特性を考慮した材料と膜厚の例を示す。

まず電極の材料としては、チタン、チタンタングステンや窒化チタン等の合金、アルミニウム合金などが挙げられ、これらの単層膜或いは積層膜を用いることができる。積層膜として、例えば、窒化チタン膜の間にアルミニウム合金膜を挟んだ積層膜が好適である。上部電極206と下部電極202の材料は、同じでも異なっていてもよい。

**【0034】**

上部電極206の厚みは、その両側に設けられる絶縁膜の厚みや材料にも依存するが、例えば500nm程度である。下部電極202は、メンブレン212を構成する膜ではないので、厚みの自由度は上部電極206よりも大きく、特に限定されるものではないが、

50

例えば厚み 500 nm ~ 1000 nm 程度である。

#### 【0035】

絶縁膜の材料として、窒化シリコン、酸化シリコンが挙げられる。このうち、下部電極 202 及び上部電極 206 に接する絶縁膜 203、205、207 としては、電荷トラップサイトの少ない酸化シリコンが好適である。シリコン酸化膜は圧縮応力を発生するが、電荷トラップサイトが少ないと、比較的薄い膜厚でもリーク電流を抑制し、電極間に印加した電圧の低下とそれによる動作の不安定化を防止することができる。

#### 【0036】

絶縁膜 203、205 の厚みは、特に限定されないが、100 nm ~ 300 nm 程度、絶縁膜 207 の厚みは、300 nm ~ 1000 nm 程度とすることができる。

10

#### 【0037】

絶縁膜 207 の上に設けられる保護絶縁膜 209 は、空洞部 104 となる犠牲層をエッティングするためのエッティング孔 208 を埋めて空洞部 104 を密封するとともに、CMUT の保護膜として設けられる。絶縁膜 209 は、また、絶縁膜 205、207 とともにメンブレン 212 を構成し、メンブレン 212 の残留応力を決定する。従って、絶縁膜 205、207 が圧縮応力を発生するシリコン酸化膜の場合には、引張応力を有する膜であることが好ましい。具体的にはシリコン窒化膜が好適に用いられる。保護絶縁膜 209 の厚みは、エッティング孔 208 を埋め込み、空洞部 104 を密封するのに十分な膜厚であり、かつメンブレン 212 の平坦性を確保する必要があり、例えば、500 nm ~ 1500 nm 程度とすることができる。

20

#### 【0038】

次に下部電極 202 から下側の材料について説明する。

基板 201 は、シリコン、ガラス等からなる半導体基板で、特に限定されないが、CMUT 素子の支持板として十分な厚みがあればよく、例えば 8 インチのシリコン基板の場合は 725 μm を有する。

#### 【0039】

反り防止膜 213 は、上述した下部電極 202 から上の層の応力に起因して基板 201 が変形するのを防止するための層であり、下部電極 202 から上の層の残留応力を考慮して適切な材料が選択される。前掲のようにメンブレン 212 を構成する絶縁層 205、207 としてシリコン酸化膜を用いた場合、一般にシリコン酸化膜は圧縮応力を有し、図 4 に示すように、基板 201 の両端が上側に反るような変形応力となる。このような変形応力に対しては、引張応力のある材料が好ましく、具体的にはシリコン窒化膜が好適である。逆に下部電極 202 より上の膜の残留応力が、基板に図 4 示す変形と逆の変形を生じるような応力の場合には、圧縮応力のある材料、例えばシリコン酸化膜を用いる場合もあり得る。但し、CMUT におけるリーク電流を抑制し、動作の安定性を確保する観点からは、絶縁膜 203、205、207 としてシリコン酸化膜を用い、反り防止膜 213 としてシリコン窒化膜を用いる組み合わせが最も好ましい。

30

#### 【0040】

なお特許文献 3 に開示される CMUT では、基板と下部電極の間にシリコン窒化膜を設けているが、この CMUT ではその他の絶縁層も同じ材料であり、基板と下部電極の間に設けられたシリコン窒化膜は、基板の反り防止層として機能するものではない。

40

#### 【0041】

ここで基板 201 上に形成した薄膜の応力は、次の式(1)で記述することができる。

#### 【数 1】

$$\sigma_f = \frac{E_s t_s^2}{(1-\nu_s)6t_f} \left( \frac{1}{R_1} - \frac{1}{R_0} \right) \quad (1)$$

式中、 $\sigma_f$  は薄膜の応力、 $t_f$  は薄膜の厚み、 $E_s$  は基板の弾性率、 $t_s$  は基板の厚み

50

、  $\nu_s$  は基板のポワソン比、  $R_1$  は薄膜を形成したときの基板の曲率半径、  $R_0$  は薄膜を形成する前の基板の曲率半径である。ここで、反りの向きを考慮せずに  $R_1$  を正の値とした場合には、薄膜の応力  $\sigma_f$  は、引張応力か圧縮応力かによって符号が異なる値となる。

#### 【0042】

薄膜を形成したときの基板の曲率半径  $R_1$  は、式(1)より、式(2)で表される。

#### 【数2】

$$\frac{1}{R_1} = \frac{6t_f(1-\nu_s)\sigma_f}{E_st_s^2} + \frac{1}{R_0} \quad (2)$$

10

#### 【0043】

今、薄膜形成前の基板の反りが非常に小さく、曲率半径が無限大であると仮定すると、式(2)は式(3)となる。

#### 【数3】

$$R_1 = \frac{E_st_s^2}{6t_f\sigma_f(1-\nu_s)} \quad (3)$$

#### 【0044】

20

式(3)において、基板の弾性率及び厚み、薄膜の厚み、応力は別途測定することで求められるので、基板の曲率半径  $R$  と基板の半径  $r$  (円形の場合) とから、図4に示すように、薄膜形成後の基板の反り量  $C$  を算出することができる。即ち、反り量  $C$  は、  $C = R(1 - \cos(r/R))$  である。なお図4は、説明をわかりやすくするために、反りを強調して示したものであり、現実的な基板の反り量を表すものではない。

#### 【0045】

基板に複数の薄膜を積層する場合には、一次近似として、式(4)に示すように、基板上にそれぞれの膜を形成した際の曲率半径の逆数の和が、薄膜が積層された基板の曲率半径の逆数の和となる。

#### 【数4】

30

$$\frac{1}{R_{multi-layer}} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} + \dots \quad (4)$$

#### 【0046】

このように薄膜或いは積層した薄膜によって生じた基板の反り量が求められるので、式(1)の応力の符号が逆で、発生する反り量が同じになる材料を組み合わせることにより、反り量を抑制できることがわかる。

#### 【0047】

次に、上記超音波トランステューサの構造を踏まえ、図5～図13を参照して、CMTの製造方法の一例を説明する。図5～図13の(a)は、図2のA-A'方向の断面を示しており、図5～図13の(b)は、図2のB-B'方向の断面を示している。

40

#### 【0048】

まず、図5(a)、(b)に示すように、半導体基板201上に、低圧CVD(Chemical Vapour Deposition)法でシリコン窒化膜による反り防止膜213を200nm堆積する。このとき、シリコン窒化膜の応力は2GPa程度の引っ張り応力となる。次に、反り防止膜213上に、スパッタリング法で窒化チタン膜とアルミニウム合金膜と窒化チタン膜をそれぞれ100nm、600nm、100nm積層した後に、フォトリソグラフィ技術とドライエッチング技術によりパターニングすることで、下部電極202を形成する(図6(a)、(b))。

50

**【0049】**

続いて、図7(a)、(b)に示すように、下部電極202上にプラズマCVD法でシリコン酸化膜による絶縁膜203を100nm堆積し、その後、絶縁膜203の上面に、プラズマCVD法で多結晶シリコン膜を100nm堆積し、フォトリソグラフィ技術とドライエッチング技術により、多結晶シリコン膜をパターニングすることで、絶縁膜203上に多結晶シリコン膜からなる犠牲層601を形成する。犠牲層601は、その後の工程で空洞部となる。

**【0050】**

続いて、犠牲層601と絶縁膜203を覆うように、プラズマCVD法によりシリコン酸化膜による絶縁膜205を100nm堆積する(図8(a)、(b))。引き続き、CMUTの上部電極206を形成するため、スパッタリング法により窒化チタン膜とアルミニウム合金膜と窒化チタン膜の積層膜をそれぞれ50nm、300nm、50nm堆積する。そして、フォトリソグラフィ技術とドライエッチング技術により、上部電極206を形成する(図9(a)、(b))。

10

**【0051】**

次にプラズマCVD法により、シリコン酸化膜による絶縁膜207を絶縁膜205、上部電極206を覆うように500nm堆積する(図10(a)、(b))。続いて、絶縁膜207および205に、フォトリソグラフィ技術とドライエッチング技術を使用して犠牲層601に到達するエッチング孔208を形成する(図11(a)、(b))。その後、エッチング孔208を介して、犠牲層601をフッ化キセノン(XeF<sub>2</sub>)ガスで等方性エッチングすることにより空洞部204を形成する(図12(a)、(b))。

20

**【0052】**

次に、エッチング孔208を埋め込むために、プラズマCVD法によりシリコン窒化膜による絶縁膜209を800nm堆積する(図13(a)、(b))。この工程により、絶縁膜205、207、209と上部電極206からなるメンブレン212が形成される。次に、下部電極202へ電気接続するためのパッド開口部211、上部電極206へ電気接続するためのパッド開口部210を、フォトリソグラフィ技術とドライエッチング技術を使用して形成し、図3(a)、(b)で示した本実施例1におけるCMUTを形成することができる。

**【0053】**

30

図5～図13では、単一のCMUT素子のみを示しているが、実際の製造工程では、径が数インチ以上の基板上に、複数のCMUT或いはCMUTチップが同時に製造される。このとき基板には、図4に示すような反り(変形)を生じさせる応力がかかるが、本実施形態のCMUTは、基板201と下部電極202との間に、他の膜に対し応力を調整された反り防止膜213が設けられているので、基板の変形を効果的に抑制することができる。

**【0054】**

&lt;&lt; 第二実施例 &gt;&gt;

本実施例の超音波トランステューサ(CMUT)は、第一実施例の構造を基礎として、下部電極(第一導電膜)202と反り防止膜213との間に、第四絶縁膜を設けたものである。本実施形態において、例えば、反り防止膜213はシリコン窒化膜であり、第四絶縁膜はシリコン酸化膜である。

40

**【0055】**

本実施形態のCMUTの構造を図14(a)、(b)に示す。図14においても、(a)は図2のA-A'方向の断面を示しており、(b)は、図2のB-B'方向の断面を示している。図示するように、このCMUTは、基板201と下部電極202の間に、反り防止層であるシリコン窒化膜213と、第四絶縁膜であるシリコン酸化膜215を積層した構造を有している。その他の膜は、実施例1と同様であり説明を省略する。

**【0056】**

シリコン窒化膜は、上述したように、膜中に電荷トラップサイトが多数存在する。その

50

ため、電荷トラップサイトを介したリーク電流も多く、基板と下部電極の間に電流が流れることによる印加電圧低下の可能性がある。本実施例では、シリコン窒化膜よりも電荷トラップサイトが少なく、リーク電流が小さいシリコン酸化膜をシリコン窒化膜と積層して挿入することで、リーク電流を抑制し、電極に印加した電圧の低下を抑制できる。

#### 【0057】

シリコン酸化膜の材料特性は、引っ張り応力にすることは困難であり、通常は圧縮応力をを持つため、基板を反らせる方向はシリコン窒化膜と反対方向であるが、シリコン窒化膜と一緒に挿入し、シリコン窒化膜の応力と膜厚を調整することで、基板の反り量を制御できる。反り量の制御方法は、第一実施例において式(1)～式(4)を用いて説明した方法と同様であり、引張応力を持つ膜によって生じる反り量と、圧縮応力を持つ膜によって生じる反り量の、絶対値が同じになるように、両者の膜厚を制御することにより、反りをなくすことが可能である。10

#### 【0058】

シリコン酸化膜とシリコン窒化膜によって基板(シリコン)に生じる反りを計算した例を図15に示す。図中、■でプロットしたグラフは、基板にシリコン酸化膜の厚みを変えて積層した場合(ケース1)、□でプロットしたグラフは、ケース1の基板にさらにシリコン窒化膜を厚み0.1μmで積層した場合(ケース2)、△でプロットしたグラフは、ケース1の基板にさらにシリコン窒化膜を厚み0.2μmで積層した場合(ケース3)を示している。また反り量は、基板の半径rを100mm、シリコン酸化膜の圧縮応力を150MPa、シリコン窒化膜の引張応力を1000MPaとして、図4に示す式から算出したものである。20

#### 【0059】

図15のグラフからわかるように、反り量はほぼ膜厚に比例して増加し、両者の厚みを適切にすることにより、反り量をほぼゼロにできる。例えば、グラフ中に矢印で示すように、シリコン酸化膜のみを積層したケース1で+30μm或いは+60μm程度基板が反っても、1000MPaの引張応力を持つシリコン窒化膜を、それぞれ、0.1μm、0.2μm形成することで、反り量をほぼゼロに抑制できる。またケース2でシリコン窒化膜のみ(シリコン酸化膜の厚み=0)で-40μm程度基板が反っても、150MPaのシリコン酸化膜を0.6μm形成することで反り量をほぼゼロに抑制することができる。30

#### 【0060】

このように本実施例によれば、下部電極202と基板201との間に、シリコン酸化膜215を挿入することで、下部電極202から基板201に向かうリーク電流を低減し、リーク電流による印加電圧の低下を防止できる。本実施例は、リーク電流による印加電圧の低下量が駆動電圧に対して大きい場合に有効である。

#### 【0061】

また本実施例における第四絶縁層215は、反り防止膜213と組み合わせることにより、基板の変形をより効果的に防止する反り防止層としても機能する。このように応力特性が異なる反り防止層を組み合わせることにより、反り防止効果を向上することができる。第四絶縁層215を、第二の反り防止層ととらえた場合、それが配置される位置は図14に示す位置、即ち反り防止膜213と下部電極202との間に限らず、反り防止膜213と基板201との間も採りえる。40

#### 【0062】

本実施例のCMUTの製造方法は、図5に示す反り防止膜213の形成工程と、図6に示す下部電極202の形成工程との間に、反り防止膜213を覆うようにシリコン酸化膜からなる絶縁膜215を形成する工程を追加すること以外は、実施例1の製造方法と同様である。なおシリコン酸化膜を基板上に直接形成し、その後、図5に示す反り防止膜213の形成工程を行う場合もある。

#### 【0063】

以上の説明では、反り防止膜213及び絶縁膜215が、それぞれ一層の場合を説明したが、いずれかが或いは両方が多層である構成や、例えば二層の絶縁膜215の間に反り50

防止膜 213 を挟んだ構成など、種々の変形があり得る。

**【0064】**

<<第三実施例>>

第一実施例及び第二実施例は、一つの CMUT を例に説明をしたが、CMUT の実施形態としては、単独の CMUT 素子に限らず、CMUT 素子を多数配列した CMUT チップにも適用できる。

**【0065】**

第一の実施形態を適用可能な CMUT チップの一例を図 16 に示す。図 16 において、図 3 と同じ要素は同じ符号で示し説明を省略する。この CMUT チップ 2000 は、二次元方向に多数の CMUT 素子 200 を配列した構造を有し、図 16 中、矢印 A で示す方向に配列した CMUT 素子は、その第一導電膜（下部電極）202 がパッド開口部 211 を介して共通の下部電極に電気的に接続され、矢印 B で示す方向に配列した CMUT 素子は、その第二導電膜（上部電極）206 がパッド開口部 210 を介して共通の上部電極に電気的に接続されている。通電する上部電極及び下部電極の組み合わせによって、個々の CMUT 素子を駆動し、超音波の送信、受信を行うことができる。なお図 16 では、簡略化して 18 個の CMUT 素子 200 が配列したものを見たが、CMUT チップにおける CMUT 素子の数は、これに限定されず、数 10 ~ 数百のものもある。もちろん少ないものもあり得る。

**【0066】**

この CMUT においても、基板から保護絶縁膜までの膜構成は、図 3 或いは図 14 に示す膜構成と同様であり、実施例 1、2 と同様の製造方法によって製造することができる。

**【0067】**

以上、CMUT の実施形態（第一の実施形態）について説明したように、本実施形態によれば、CMUT の特性に影響を与えることなく、効果的に基板の反りを抑制することができる。これにより、CMUT 製造時において基板の吸着不良やプロセス処理の不具合を解消するとともに、超音波装置への CMUT 組み立て時ににおけるチップ割れなどの問題を解消することができる。

**【0068】**

<第二の実施形態>

本発明の第二の実施形態は、上述したように、基板の、CMUT が設けられる領域以外の領域に、基板の反りを防止する層（構造）を設けるものであり、この構造が設けられる領域は、基板から個々の CMUT 或いは CMUT チップを切り出した後の CMUT には残留しない領域である。従ってこの特徴は、CMUT の製造方法に現れる。

**【0069】**

即ち、本実施形態の CMUT の製造方法は、基板上の所定の領域（以下、チップ領域という）に、第一導電膜、第一絶縁膜、第二絶縁膜、第二導電膜及び第三絶縁膜を含む複数の層をパターニングによって形成し、複数の超音波トランステューサアレイを製造する方法であって、前記パターニングと同じ工程において、前記基板上の、前記所定の領域を除く外側の領域（以下、オフチップ領域という）に、前記基板の反りを抑制する反り防止層を所定のパターンで形成することが特徴である。

**【0070】**

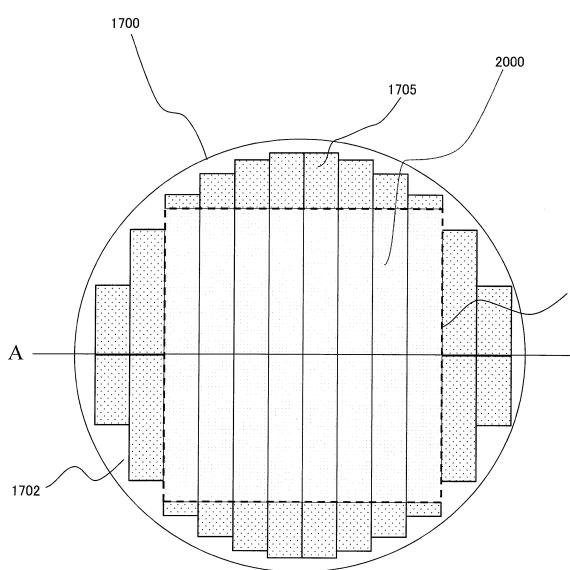

基板上のチップ領域とオフチップ領域の配置例を図 17 に示す。この配置例では、基板 1700 は円形であり、チップ領域 1701 は基板の円にほぼ内接する矩形の領域であり、この領域に複数の CMUT チップ 2000 が形成される。CMUT チップ 2000 は、例えば図 16 に示したような、CMUT 素子が二次元方向に多数配列したアレイと CMUT 素子に給電するパッド開口部などを備えている。各 CMUT は、図 1 や図 3 に示したような膜構成を持つ。オフチップ領域 1702 は、CMUT チップ 2000 を配列方向に増やした時に、CMUT チップ 2000 が完全な形で形成することができない領域であり、チップ領域 1701 の外側の領域である。

**【0071】**

10

20

30

40

50

基板 1700 のチップ領域 1701 に、CMUT チップを構成する各膜を形成した場合、基板 1700 は、図 18 において細線で示すように、チップ領域 1701 とオフチップ領域 1702 とで反りの曲率が異なり、オフチップ領域 1702 で局所的に基板の反りが増大する。このような局所的な基板の変形は、特に、基板を製造装置のステージへ吸着する際に吸着できなかったり破損を招く可能性がある。

#### 【0072】

本実施形態は、このオフチップ領域に反り防止構造を設けることにより、局所的に増大する反りを抑制する。反り防止構造は、例えば、CMUT と共に層構成を有する積層膜であることが好ましく、パターンは、CMUT のパターンと同一のパターン、大きさの異なる複数のパターン、互いに独立した複数の区分に分割されたパターンなど種々の形態が採りえる。10

#### 【0073】

反り防止構造を、CMUT と共に層構成を有するパターンで形成する場合には、オフチップ領域に所定のパターニングを行って成膜することを追加するだけで、第一実施例で説明した CMUT の製造工程で、CMUT の製造と反り防止構造の製造を同時にを行うことができる。従って製造方法の工程は図 5 ~ 図 13 に示した工程と同様であるので、その説明は省略し、以下、パターンの異なる各実施例を説明する。

#### 【0074】

<< 第四実施例 >>

本実施例は、チップ領域 1701 のパターンを、オフチップ領域 1702 にも延長して用いることが特徴である。20

#### 【0075】

本実施例において、CMUT チップが配列された基板の上面図を図 19 に示す。図示する例では、基板 1700 上のチップ領域 1701 に、横 8 列、縦 2 列の CMUT チップ 2000 が形成されている。基板 1700 上のその他の部分はオフチップ領域 1702 であり、このオフチップ領域 1702 を含む外側に、チップとしては基板からはみ出してしまうが、ダミーチップとして、CMUT チップと同じ構造のチップを作製する領域（ダミーチップ領域）1705 を設ける。ダミーチップ領域 1705（図中、一点鎖線で囲った領域）は、その領域内に基板 1700 が収まる最小限の大きさの領域であり、その中に CMUT チップのパターンと同じ配列を含む。30

#### 【0076】

ダミーチップとして作製されるチップは、基板を有しないか、基板があってもパターンの一部が欠けたチップである。しかし、基板 1700 上には連続したチップの層構造が形成されるため、図 18 に太線で示すように、チップ領域 1701 とオフチップ領域 1702 とで基板 1700 の反りは連続性があり、局所的な変形を防止することができる。

#### 【0077】

本実施例は、CMUT のパターンの領域を広げるだけで、通常の CMUT 製造工程に変更を加えることなく容易に基板の変形を防止することができる。

#### 【0078】

<< 第五実施例 >>40

本実施例は、CMUT チップと同じ構造のダミーチップ領域を設けて、ダミーチップを作製することは第四実施例と同じであるが、ダミーチップ領域を基板のオフチップ領域 1702 内に限定したことが特徴である。

#### 【0079】

即ち、図 20 に示すように、チップ領域 1701 の周囲に、基板 1700 の端部と重ならないように、大きさの異なるダミーチップを配置したダミーチップ領域 1705 を設ける。本実施例は、ダミーチップ領域を基板の内側にするために、オフチップ領域の形状に合わせてダミーチップの大きさを変える必要があるので、第四実施例に比べ、ダミーチップをパターニングする際のリソグラフィー工程が煩雑になるが、次のような利点がある。

#### 【0080】

すなわち、C M U Tと同じ構造を持つダミーチップは、C M U Tと同じ空洞部を有しているため、第四実施例のように基板の端部に重なる位置にダミーチップがあると、ダミーチップの空洞部が基板1700の端部と重なる可能性がある。C M U Tの製造工程において、基板を搬送するカセットやハンドリングするピンセットが基板端部に接触し、製造工程の途中で空洞上のメンブレンが剥がれる可能性がある。剥がれたメンブレンの破片は基板上に残留し、その後の製造工程で異物となり、C M U Tのチップの歩留まりを低下させる原因となる。本実施例は、ダミーチップ領域を基板の内側に限定したことにより、この問題を解消している。

#### 【0081】

本実施例によれば、基板端部でのメンブレンの剥がれを抑制できる。またオフチップ領域1702の中で、ダミーチップが配列されない領域は少ないため、その領域の基板の反りへの影響も最小限に留めることができる。10

#### 【0082】

なお第四実施例及び第五実施例においても、C M U Tの層構成として、第一実施形態の層構成即ち下部電極と基板の間に基板の反りを調整する反り防止膜（シリコン窒化膜）を挿入する構成を組み合わせることが可能であり、それによりさらに基板の反りを抑制できることは言うまでもない。

#### 【0083】

<<第六実施例>>

本実施例は、C M U Tチップが配置されていない基板上の領域において、絶縁膜にパターニングを行うことで、ウェハの反りの抑制を実現している。即ち、本実施例の反り防止構造は、絶縁膜を独立した複数の区分に分割したパターンで構成される。20

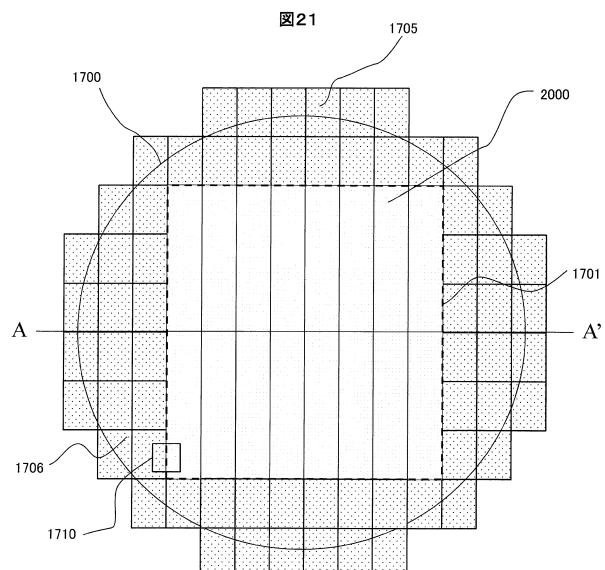

#### 【0084】

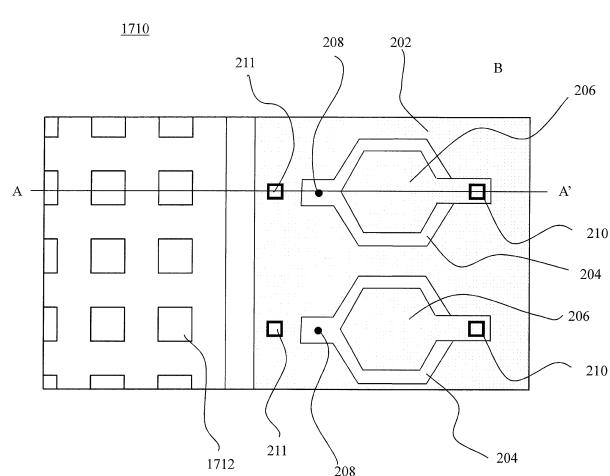

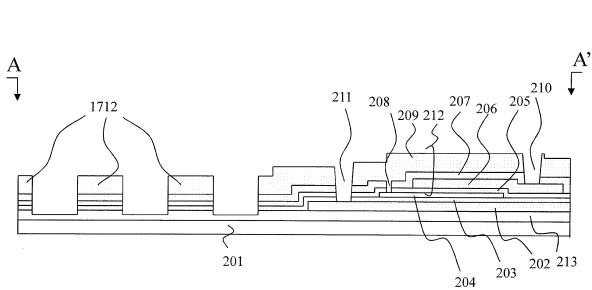

本実施例の、C M U Tチップが配列された基板の上面図を図21に示す。図21においても、図19と同じ要素は同じ符号で示し、重複する説明は省略する。また図21に示すC M U Tチップが配列された基板の一部1710について、上面図と断面図をそれぞれ図22、図23に示す。

#### 【0085】

図21に示すように、本実施例でもチップ領域1701の周囲に所定のパターンの反り防止構造が設けられる。所定のパターンが形成される領域（ここではダミーチップ領域という）1705は、基板の端部を含む外側の領域を含み、個々のダミーチップ1706は、部分1710の拡大図である図22及び図23に示すように、概ね四角形の区画1712を敷き詰めたパターンを持つ。概四角形の区画からなるパターンは、積層した絶縁膜をパターニングによって分割して形成されている。30

#### 【0086】

即ち、このパターンは、第一実施形態で説明したC M U Tの製造工程において、オフチップ領域には下部及び上部電極を形成せずに、第一絶縁膜から保護絶縁膜までを成膜した後（図13）、次のパッド開口部を形成するための工程（図14）で作製される。即ちパッド開口部を形成するリソグラフィーの際に、概四角形のパターンを持ったホトマスクを使用してリソグラフィーによりダミーチップ領域にパターンを形成し、パッド開口部を形成するドライエッチング工程の際に、ダミーチップ領域のパターンも同時にドライエッチングすることで分割された絶縁膜の構造を形成する。40

#### 【0087】

ダミーチップ領域の絶縁膜をパターニングにより分割することで、絶縁膜の応力を開放し、ダミーチップ領域の絶縁膜の応力による基板の反りを抑制することができる。パターンの間隔は、限定されるものではないが、パターンの寸法（四角形の構造と構造との間隔）を絶縁膜の厚さ（四角形の構造の高さ）の2倍以下にすることにより、より効果的に絶縁膜の応力を開放でき、基板の反りを抑制できる。また図では四角形のパターンを示したが、円形や六角形など任意の形状とすることができる、また個々の構造が独立したパターンではなく、線条のものや網目状のパターンもあり得る。50

## 【0088】

本実施例によれば、ダミーチップ領域にCMUTと共に通する膜構成のパターンを形成することにより、上述した第四実施例及び第五実施例と同様に、基板の局所的な変形を防止することができる。また共通する膜構成ではあるが、ダミーチップは空洞部を有していないので、空洞部と基板とが重なることによる空洞部の破損やダストの発生などの問題、空洞部と基板とが重ならないようにするため製造工程が煩雑になるという問題がなく、通常の製造工程を大幅に変更することなく、基板の反り防止を図ることができる。

## 【0089】

なおパターニングする絶縁膜は、CMUTと共に通する膜が含まれていればよく、必ずしも同一の膜構成とする必要はない。少なくとも上部電極より上層の膜、絶縁膜207、209をパターニングすることが好ましい。

10

## 【0090】

以上、本発明の第二の実施形態の各実施例（第四実施例～第六実施例）を説明したが、これら実施例においても、CMUTの層構成として、第一の実施形態の層構成即ち下部電極と基板の間に基板の反りを調整するシリコン窒化膜を挿入する構成を組み合わせることが可能であり、それによりさらに基板の反りを抑制できることは言うまでもない。

## 【0091】

## &lt;第三の実施形態&gt;

最後に、本発明の超音波検査装置の実施形態を説明する。

本実施形態の超音波検査装置は、超音波トランスデューサを内蔵する超音波探触子と、前記超音波探触子に超音波信号を送信するとともに前記超音波探触子が検出した超音波信号を受信する超音波送受信回路と、前記超音波送受信回路が受信した超音波信号を用いて画像を作成する画像作成部とを備え、前記超音波探触子として、基板と、前記基板の上に形成された第一導電膜と、前記第一導電膜の上に形成された第一絶縁膜及び第二絶縁膜と、前記第一絶縁膜と第二絶縁膜との間に設けられた空洞部と、前記第二絶縁膜の上に形成された第二導電膜と、前記第二導電膜を覆う第三絶縁膜と、前記基板と前記第一導電膜との間に配置され、前記基板の反りを防止する反り防止層と、を備えた超音波探触子を用いたものである。

20

## 【0092】

図24を参照して、本実施形態の超音波検査装置の一構成例と動作を説明する。

30

図24に示すように、超音波検査装置は、超音波検査装置本体2401と、超音波探触子2402で構成され、超音波検査装置本体2401は、送受分離部2403、送信部2404、バイアス部2405、受信部2406、整相加算部2407、画像処理部2408、表示部2409、制御部2410、操作部2411から構成される。

## 【0093】

超音波探触子2402は、被検体に接触させて被検体との間で超音波を送受波する装置であり、上述した各実施例の製法で製造されたCMUTを用いて作製される。超音波探触子2402の形態は、検査対象によって種々のものがあるが、基本的な構造として、振動子アレイ、それを支持するパッキング層、振動子アレイに電気的に接続されるフレキシブルプリント基板、振動子アレイの前面（被検体との接触面側）に配置される音響レンズなどを備えている。振動子アレイは、多数の振動子を二次元方向に配列したものであり、本実施形態では図16に示すようなCMUTチップが用いられる。

40

## 【0094】

超音波探触子2402に内蔵されるCMUTは、送受分離部2403と電気的に接続される。送受分離部2403は、超音波の送信時には送信部2404からの駆動信号を超音波探触子2402へ渡し、受信時には超音波探触子2402から受信信号を受信部2406へ渡すよう送信と受信とを切換、分離する。

## 【0095】

送信時には、送信部2404及びバイアス部2405が、超音波探触子2402に駆動信号を供給し、これにより超音波探触子2402から超音波が被検体に送波される。受信

50

時には、被検体からの反射エコー信号が超音波探触子 2402 により受波されると、受信部 2406 が、超音波探触子 2402 から出力される反射エコー信号を受信する。受信部 2406 は、さらに、受信した反射エコー信号に対してアナログデジタル変換等の処理を行う。整相加算部 2407 は、受信された反射エコー信号を整相加算し、画像処理部 2408 に渡す。画像処理部 2408 は、整相加算された反射エコー信号に基づいて検査画像を構成し、表示部 2409 が、画像処理された検査画像を表示する。

#### 【0096】

これら各部の動作は、制御部 2410 により制御され、超音波探触子 2402 による超音波の送受信が行われる。検査の条件やパラメータ、制御のための指令は、トラックボールやキーボードやマウス等の入力機器からなる操作部 2411 を介して制御部 2410 に入力される。

10

#### 【0097】

本実施形態の超音波検査装置は、超音波探触子に、基板の反りが抑制され且つ安定した動作が確保された CMUT を採用しているので、個々の振動子の動作が均一で安定した出力が得られ、これにより高品質の検査画像を得ることができる。

#### 【0098】

なお本実施形態の超音波検査装置としては、人や動物を対象とする超音波診断装置の他、構造物の内部検査装置など種々の検査装置に適用することができる。

#### 【符号の説明】

#### 【0099】

20

201、1700・・・基板、202・・・下部電極、203・・・第一絶縁膜、204

・・・空洞部、205・・・第二絶縁膜、206・・・上部電極、207・・・第三絶縁

膜、208・・・エッティング穴、209・・・保護絶縁膜、210、211・・・パッ

ド開口部、213・・・反り防止膜、215・・・第四絶縁膜、1701・・・チップ領

域、1702・・・オフチップ領域、1705・・・ダミーチップ領域、1706・・・

ダミーチップ、1710・・・CMUTチップが形成された基板の一部、1712・・・

ダミーチップのパターン、2000・・・CMUTチップ、2401・・・超音波検査装

置本体、2402・・・超音波探触子、2403・・・送受分離部、2404・・・送信

部、2405・・・バイアス部、2406・・・受信部、2407・・・整相加算部、2

408・・・画像処理部、2409・・・表示部、2410・・・制御部、2411・・・

操作部

30

【図1】

【図2】

図2

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

【図15】

【図16】

【図17】

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

---

フロントページの続き

(51)Int.Cl. F I

A 6 1 B 8/00 (2006.01) A 6 1 B 8/00

G 0 1 N 29/24 (2006.01) G 0 1 N 29/24

(72)発明者 山下 尚昭

東京都三鷹市牟礼六丁目22番1号 日立アロカメディカル株式会社内

(72)発明者 花岡 裕子

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72)発明者 吉村 保廣

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

審査官 菊池 充

(56)参考文献 特開2014-120874 (JP, A)

特開2012-099847 (JP, A)

特開2004-165193 (JP, A)

米国特許出願公開第2005/0230794 (US, A1)

特開2013-226391 (JP, A)

米国特許出願公開第2013/0255388 (US, A1)

特開2007-259165 (JP, A)

米国特許出願公開第2007/0222338 (US, A1)

特開2012-222516 (JP, A)

米国特許出願公開第2012/0256520 (US, A1)

特開2004-029403 (JP, A)

特表2001-502871 (JP, A)

米国特許第6320239 (US, B1)

特開2013-150198 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 04 R 19 / 00

H 04 R 31 / 00

H 01 L 29 / 84

B 8 1 B 1 / 00 - 7 / 04

B 8 1 C 1 / 00 - 99 / 00

A 6 1 B 8 / 00 - 8 / 15

G 0 1 N 29 / 00 - 29 / 52