(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6415602号

(P6415602)

(45) 発行日 平成30年10月31日(2018.10.31)

(24) 登録日 平成30年10月12日(2018.10.12)

(51) Int.Cl.

F 1

|      |         |           |      |       |      |

|------|---------|-----------|------|-------|------|

| G03F | 7/20    | (2006.01) | G03F | 7/20  | 521  |

| H01L | 21/027  | (2006.01) | G03F | 7/20  | 503  |

| H01L | 27/10   | (2006.01) | G03F | 7/20  | 504  |

| H01L | 21/8244 | (2006.01) | H01L | 21/30 | 502D |

| H01L | 27/11   | (2006.01) | H01L | 27/10 | 431  |

請求項の数 25 (全 17 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-567854 (P2016-567854)  |

| (86) (22) 出願日 | 平成26年6月25日 (2014.6.25)        |

| (65) 公表番号     | 特表2017-520786 (P2017-520786A) |

| (43) 公表日      | 平成29年7月27日 (2017.7.27)        |

| (86) 國際出願番号   | PCT/US2014/044105             |

| (87) 國際公開番号   | W02015/199682                 |

| (87) 國際公開日    | 平成27年12月30日 (2015.12.30)      |

| 審査請求日         | 平成29年6月20日 (2017.6.20)        |

|           |                                                                                       |

|-----------|---------------------------------------------------------------------------------------|

| (73) 特許権者 | 591003943<br>インテル・コーポレーション<br>アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200    |

| (74) 代理人  | 110000877<br>龍華国際特許業務法人                                                               |

| (72) 発明者  | エルセイド、ラニー、ティー。<br>アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200 インテル・コーポレーション内 |

最終頁に続く

(54) 【発明の名称】機能セルのコンパクトアレイを形成するための技術

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板上に形成された格子状の複数の拡散ライン及び複数のゲートラインであり、格子に含まれる前記複数の拡散ラインのうちの少なくとも3つはそれらの間に一貫する間隔を有する、複数の拡散ライン及び複数のゲートラインと、

格子状の前記複数の拡散ライン及び前記複数のゲートライン上に形成された複数の機能セルのアレイであり、前記複数の機能セルのアレイは、それらの間に一貫する間隔を有する前記少なくとも3つの拡散ライン上に少なくとも一部が形成された2つの隣接する機能セルである隣接セルを含み、各セルは、境界を有し、前記2つの隣接セルの前記境界の間には拡散ラインはなく、それにより、前記2つの隣接セルのうちの1つは、前記少なくとも3つの拡散ラインのうちの2つを含み、前記2つの隣接セルのうちのほかは、前記少なくとも3つの拡散ラインのうちの1又は複数を含む、複数の機能セルのアレイと、を備え、

前記アレイ内の前記2つの隣接セルの前記境界の間の距離は50nmより小さい、集積回路。

## 【請求項 2】

前記基板は、シリコン(Si)及びゲルマニウム(Ge)のうちの少なくとも一方を含む、請求項1に記載の集積回路。

## 【請求項 3】

10

20

前記アレイ内の前記 2 つの隣接セルの前記境界の間の前記距離は 20 nm より小さい、請求項 1 に記載の集積回路。

**【請求項 4】**

前記複数の機能セルは、複数のゲートアレイ論理セル及び複数のメモリビットセルのうちの少なくとも一方を含む、請求項 1 に記載の集積回路。

**【請求項 5】**

前記 2 つの隣接セルに含まれる前記複数のゲートラインは、更に、それらの間に一貫する間隔を有し、

前記 2 つの隣接セルの前記境界の間にはゲートラインは存在しない、請求項 1 に記載の集積回路。

10

**【請求項 6】**

複数の機能セルの前記アレイは、前記複数の機能セルの複数の前記境界を形成すべく 193 nm フォトリソグラフィを使用して形成され得る最も高い密度の実効構造より 10 パーセントから 50 パーセント高密度である、請求項 1 に記載の集積回路。

**【請求項 7】**

基板と、

前記基板から延びる格子状の複数の拡散ラインであり、格子に含まれる前記複数の拡散ラインのうちの少なくとも 3 つはそれらの間に一貫する間隔を有する、複数の拡散ラインと、

それらの間に一貫する間隔を有する格子に含まれる前記 3 つの拡散ライン上に少なくとも一部が形成される 2 つの隣接する機能セルである隣接セルを含む複数の機能セルのアレイであり、各セルは、境界を有し、前記 2 つの隣接セルの前記境界の間には拡散ラインはなく、それにより、前記 2 つの隣接セルのうちの 1 つは、前記少なくとも 3 つの拡散ラインのうちの 2 つを含み、前記 2 つの隣接セルのうちのほかは、前記少なくとも 3 つの拡散ラインのうちの 1 又は複数を含む、複数の機能セルのアレイと、

を備え、

20

前記アレイ内の前記 2 つの隣接セルの前記境界の間の距離は 50 nm より小さく、

前記アレイは、前記複数の機能セルの複数の前記境界を形成すべく 193 nm フォトリソグラフィを使用して形成され得る最も高い密度の実効構造より 10 パーセントから 50 パーセント高密度である、集積回路。

30

**【請求項 8】**

請求項 1 から 7 の何れか一項に記載の集積回路を備える、フィールドプログラマブルゲートアレイ (FPGA) デバイス。

**【請求項 9】**

請求項 1 から 7 の何れか一項に記載の集積回路を備える、スタティックランダムアクセスメモリ (SRAM) デバイス。

**【請求項 10】**

請求項 1 から 7 の何れか一項に記載の集積回路を備える、コンピューティングシステム。

**【請求項 11】**

基板を設ける段階と、

複数の拡散ラインを形成する段階と、

複数のゲートラインを形成する段階であって、前記複数の拡散ラインと前記複数のゲートラインは格子状構造で形成される、段階と、

前記格子状構造上にレジストを形成する段階と、

サブ 100 nm クリティカルディメンジョンを有する複数のレジストフィーチャを実現でき、1 又は 0 個のマスクを必要とするリソグラフィプロセスを使用して複数の機能セルの境界を形成すべく前記レジストをパターニングする段階であって、前記複数の機能セルはアレイ内に配置される、段階と、

パターンを前記格子状構造の中にエッチングして、前記複数の機能セルのアレイを前記

40

50

格子状構造の前記複数の拡散ラインと前記複数のゲートライン上に形成する段階であって、前記複数の機能セルのアレイは、それらの間に一貫する間隔を有する少なくとも3つの拡散ライン上に少なくとも一部が形成された2つの隣接する機能セルである隣接セルを含み、各セルは、境界を有し、前記2つの隣接セルの前記境界の間には拡散ラインはなく、それにより、前記2つの隣接セルのうちの1つは、前記少なくとも3つの拡散ラインのうちの2つを含み、前記2つの隣接セルのうちのほかは、前記少なくとも3つの拡散ラインのうちの1又は複数を含む、段階と、

を備える集積回路を形成する方法。

【請求項12】

前記複数の機能セルは、複数のゲートアレイ論理セル及び複数のメモリビットセルのうちの少なくとも一方を含む、請求項11に記載の方法。 10

【請求項13】

前記リソグラフィプロセスは電子ビームリソグラフィである、請求項11に記載の方法。

。

【請求項14】

前記電子ビームリソグラフィはマルチビームを含む、請求項13に記載の方法。

【請求項15】

前記リソグラフィプロセスはマスクレスである、請求項11に記載の方法。

【請求項16】

前記リソグラフィプロセスは極端紫外線リソグラフィ(EUVL)である、請求項11

に記載の方法。 20

【請求項17】

前記リソグラフィプロセスはナノインプリントリソグラフィである、請求項11に記載の方法。

【請求項18】

前記リソグラフィプロセスは、サブ30nmクリティカルディメンジョンを有する複数のレジストフィーチャを実現できる、請求項11から17の何れか一項に記載の方法。

【請求項19】

前記リソグラフィプロセスは、サブ10nmクリティカルディメンジョンを有する複数のレジストフィーチャを実現できる、請求項11から17の何れか一項に記載の方法。 30

【請求項20】

基板を設ける段階と、

前記基板上に複数の拡散ライン及び複数のゲートラインを格子状構造で形成する段階と

前記格子状構造上にレジストを形成する段階と、

複数の機能セルの境界を形成すべくリソグラフィプロセスを使用して前記レジストをパターニングする段階であって、2つの隣接する機能セルである隣接セルの前記境界の間の距離は50nmより小さい、段階と、

パターンを前記格子状構造の中にエッチングして、前記2つの隣接セルを含む複数の機能セルのアレイを前記格子状構造の前記複数の拡散ラインと前記複数のゲートライン上に形成する段階であって、前記2つの隣接セルは、それらの間に一貫する間隔を有する少なくとも3つの拡散ライン上に少なくとも一部が形成され、各セルは、境界を有し、前記2つの隣接セルの前記境界の間には拡散ラインはなく、それにより、前記2つの隣接セルのうちの1つは、前記少なくとも3つの拡散ラインのうちの2つを含み、前記2つの隣接セルのうちのほかは、前記少なくとも3つの拡散ラインのうちの1又は複数を含む、段階と 40

、を備える、複数の機能セルのアレイを形成する方法。

【請求項21】

前記複数の機能セルは、複数のゲートアレイ論理セル及び複数のメモリビットセルのうちの少なくとも一方を含む、請求項20に記載の方法。 50

**【請求項 2 2】**

前記リソグラフィプロセスは電子ビームリソグラフィである、請求項 2 0 に記載の方法。

。

**【請求項 2 3】**

前記電子ビームリソグラフィはマルチビームを含む、請求項 2 2 に記載の方法。

**【請求項 2 4】**

前記リソグラフィプロセスはマスクレスである、請求項 2 0 から 2 3 の何れか一項に記載の方法。

**【請求項 2 5】**

前記リソグラフィプロセスは極端紫外線リソグラフィ ( E U V L ) である、請求項 2 0 10

に記載の方法。

**【発明の詳細な説明】****【背景技術】****【0 0 0 1】**

フィールドプログラマブルゲートアレイ、( F P G A ) 、スタティックランダムアクセスメモリ ( S R A M ) 、並びに他のメモリ及び論理デバイスなどの規則正しい集積回路構造は通常、連続格子状の拡散ライン及びゲートラインを含む。次に、付随する光リソグラフィ設計ルール及びそれにより課される間隔制限などの要素を考慮して、当該拡散ライン及びゲートラインから複数の論理セル又は複数のブロックが形成される。そのような集積回路構造内の論理セル数は、例えば増大する性能要求を満たすべく、増加してきている。20

論理セル数の増加は必要な領域の増加につながり、それは、より大きいチップサイズの要求及び費用増加と言い換えられ得る。

**【図面の簡単な説明】****【0 0 0 2】**

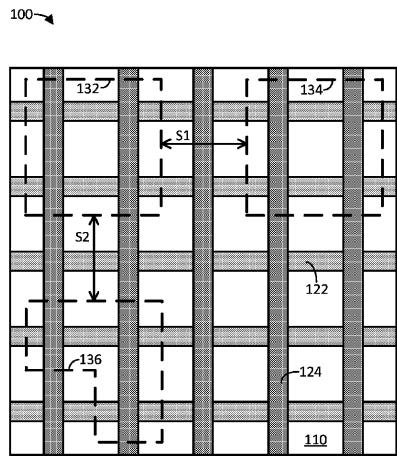

【図 1】格子状の複数の拡散ライン及び複数のゲートライン上に形成された 3 つの論理セルであって、それらの論理セルの境界は 1 9 3 n m フォトリソグラフィを使用して形成された、3 つの論理セルを含む集積回路 ( I C ) 構造を示す。

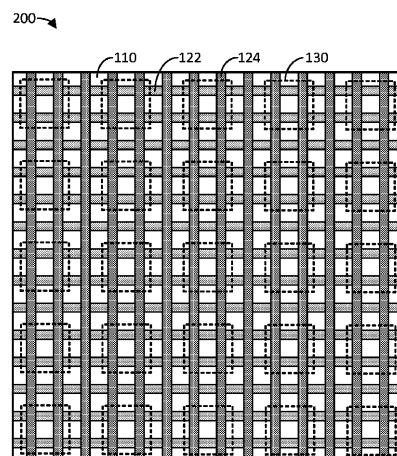

【図 2】格子状の複数の拡散ライン及び複数のゲートライン上に形成された論理セルのセットであって、それらの論理セルの境界は 1 9 3 n m フォトリソグラフィを使用して形成された、論理セルのセットを含む I C 構造を示す。

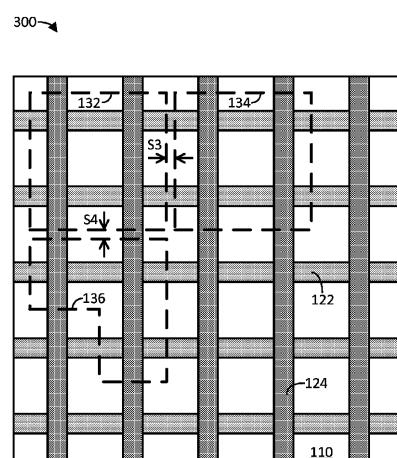

【図 3 A】本開示の一実施形態に係る、格子状の複数の拡散ライン及び複数のゲートライン上に形成された 3 つの機能セルを含む例示的な I C 構造を示す。

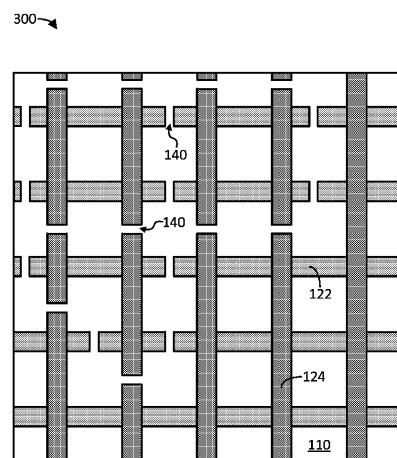

【図 3 B】図 3 A の 3 つの機能セルを形成すべく作られた、格子状の複数の拡散ライン及び複数のゲートラインにおける複数の切断を示す。

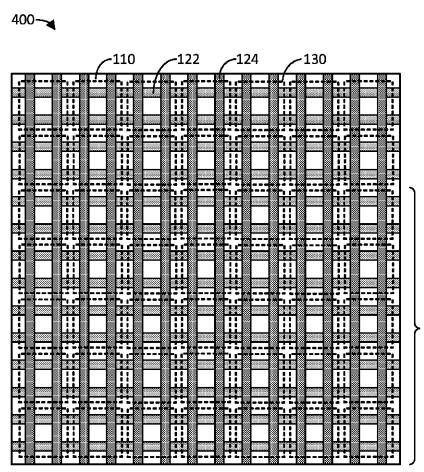

【図 4】本開示の一実施形態に係る、格子状の複数の拡散ライン及び複数のゲートライン上に形成された複数の機能セルのアレイを含む例示的な I C 構造を示す。

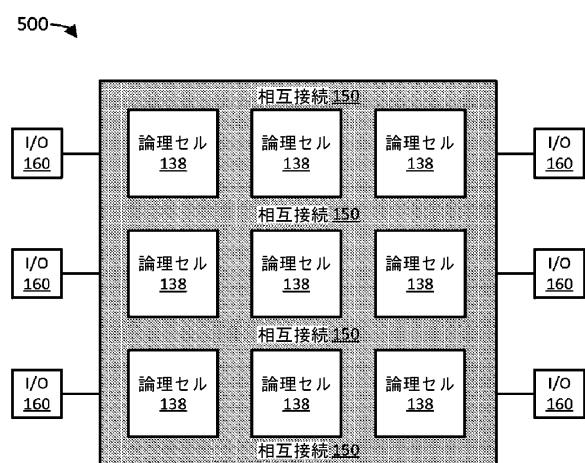

【図 5】一実施形態に従って構成された複数の機能セルのアレイを含む例示的なフィールドプログラマブルゲートアレイ ( F P G A ) 構造を示す。

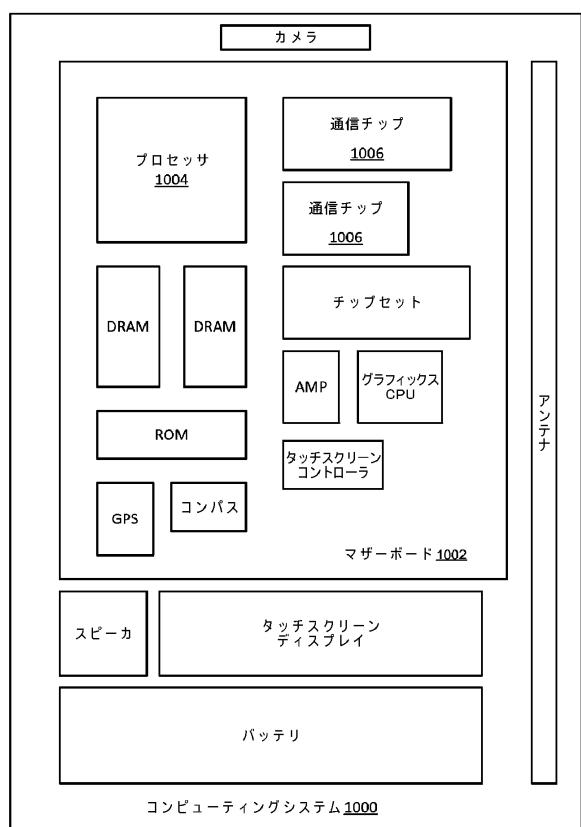

【図 6】一例示的実施形態に係る、本明細書において開示された複数の技術を使用して形成された集積回路の複数の構造又は複数のデバイスが実装されたコンピューティングシステムを示す。

**【発明を実施するための形態】****【0 0 0 3】**

電子ビーム直接描画 ( E B D W ) 及び極端紫外線リソグラフィ ( E U V L ) などの次世代リソグラフィ ( N G L ) プロセスを使用して複数の機能セルのコンパクトアレイを形成し、当該アレイ内の複数のセルの複数の境界を形成するための複数の技術が開示される。複数のセルのコンパクトアレイは、複数の論理セルで構成されたフィールドプログラマブルゲートアレイ ( F P G A ) 構造、複数のビットセルで構成されたスタティックランダムアクセスメモリ ( S R A M ) 構造、又は複数のセルベース構造を有する他の複数のメモリデバイス又は複数の論理デバイスに使用されてよい。当該複数の技術は、例えば複数の機50

能セルのアレイについては、10パーセントから50パーセントの面積削減を達成すべく使用され得る。なぜなら、従来の193nmフォトリソグラフィと比較して、複数のNGLプロセスは、複数のセル境界のためのより高い精度のより接近した切断を可能にするからである。加えて、複数のセルの複数の境界を形成すべく複数のNGLプロセスを使用することで、それらを使用せず従来の193nmフォトリソグラフィを使用した場合には存在するであろうリソグラフィ誘導変動(lithography induced variation)を低減することもできる。当該開示に照らし、多数の構成及び変更が明らかであろう。

#### 【発明の概要】

##### 【0004】

上記のように、フィールドプログラマブルゲートアレイ(FPGA)、スタティックランダムアクセスメモリ(SRAM)、及び他の論理デバイス及びメモリデバイスなどの集積回路(ASIC)構造での論理セル数の増加は必要な領域の増加につながり、それはより大きいチップサイズの要求及び費用増加と言い換えられ得る。従来、そのようなASIC構造上に複数の論理セル境界を形成すべく、拡散ライン及びゲートラインのエッティング／切断には193nmフォトリソグラフィが使用されてきた。しかしながら、193nmフォトリソグラフィは、特にサブ100nm解像度用途に関して特定の制限を有する。そのような制限には、いくつか例を挙げると、複数のリソグラフィプロセスを必要とすること、複数のマスクを必要とすること、追加の複数の材料を必要とすること、精度に欠けること、高密度のコンポーネントを形成する能力に欠けること、鋭い複数の角及び複数のエッジを形成する能力に欠けること、形成された複数の構造の全体にわたる整合性に欠けること、などが含まれる。例えば、図1は、基板110と、格子状の複数の拡散ライン122及び複数のゲートライン124上に形成された3つの論理セル132、134、136とを含むASIC構造100を示している。別の例では、図2は、基板110と、格子状の14本の拡散ライン122及び14本のゲートライン124上に形成された25個の論理セル130とを含むASIC構造200を示している。論理セル130、132、134、136の(破線で示された)境界は、従来の193nmフォトリソグラフィを使用して形成されたものである。図1及び図2から分かるように、隣接する複数の論理セルの複数の境界の間の間隔(例えば、論理セル132及び134の境界の間の間隔S1、並びに、論理セル132及び136の境界の間の間隔S2)は拡散ライン又はゲートラインの何れかを含み、その間隔は、特にサブ100nm解像度用途では、従来の193nmフォトリソグラフィによって制限される。より具体的には、従来の光リソグラフィ設計ルールは、複数のデバイスセルを形成すべく複数のゲートライン(又は場合によりポリシリコンなどの犠牲ゲート材料)が切断され得る場所に対して複数の制限を課す。ここで、S1及びS2は、複数のセルの間で維持されなければならない最小距離を表わす。

##### 【0005】

従って、本開示の1又は複数の実施形態に従って、電子ビーム直接描画(EBDW)及び極端紫外線リソグラフィ(EUVL)などの複数の次世代リソグラフィ(NGL)プロセスを使用して複数の機能セルのコンパクトアレイを形成し、当該アレイ内の複数のセルの複数の境界を形成するための複数の技術が開示される。本開示に照らし明らかであろうように、ナノインプリントリソグラフィ、並びに、他のマスクレスプロセス及び低減されたマスクでのプロセスなどの他の複数のNGLプロセスが、本明細書において記載される複数のセルのコンパクトアレイを形成すべく使用されてよい。これらの技術は、複数のFPGA、SRAM、及び、他のメモリ若しくは論理若しくはセルベースのデバイスのためのアレイなどの、複数の論理セル及び／又は複数のビットセルの様々なコンパクトアレイを形成すべく使用され得る。いくつかの実施形態において、本明細書において記載される複数の技術は、(例えば、193nmフォトリソグラフィを使用する場合と比較して)複数のセルの間のスペース、又は任意のセルのサブロックレベルを低減すべく使用され得る。それにより、特に、複数の論理セルのアレイがチップ面積の50、65、80、又は90パーセントより大きい面積を占めることがあるFPGAなどの複数のデバイスについ

10

20

30

40

50

て、複数のセルのアレイ全体に必要とされる面積を低減する。

#### 【0006】

いくつかの実施形態において、本明細書において記載される複数の技術を使用して（例えば、E B D W又はE U V Lを使用して）複数の機能セルの複数のコンパクトアレイを形成すると、例えば、4 nmを下回る又は2 nmを下回るラインエッジラフネス（L E R : line edge roughness）などの改良されたL E Rを有する複数の機能セル境界を得ることができる。更に、本明細書において記載される複数の技術は、30 nm若しくはそれより小さい（又は更には10 nm若しくはそれより小さい）クリティカルディメンジョンを有する複数のレジストフィーチャ（resist feature）を形成する場合でさえも、比較的正確なレジストが形成されることを可能にする。この精度の向上により、複数の機能セルがより高い密度で形成されることが可能となる。なぜなら、これらの機能セルの複数の境界はより高い精度で形成され得、それにより、リソグラフィ誘導変動を回避するか、又はそうでなければ低減し得る。本明細書において記載される複数の技術はまた、複数の機能セルの複数の境界について、正確度及び／又はクリティカルディメンジョン均一性（C D U）の向上を可能にし得る。本明細書において記載された複数の技術を使用して、不規則な形状の複数のセル境界が、（例えば、193 nmフォトリソグラフィを使用して実現され得るものと比較して）より効果的に形成されることもある。加えて、これらの改善された結果は、1つのリソグラフィプロセスと、（使用される特定のN G Lプロセスに応じて）1又は0個のマスクを使用することで実現され得る。193 nmフォトリソグラフィであれば、例えばサブ100 nm解像度に至るのに複数のリソグラフィプロセスと複数のマスクとを必要とするので、このことは193 nmフォトリソグラフィよりも優れたもう1つの利点である。10

20

#### 【0007】

（例えば、走査型／透過型電子顕微鏡（S E M / T E M）及び／又は組成マッピングを使用して）分析をすると、1又は複数の実施形態に従って構成された構造又はデバイスが、従来の193 nmフォトリソグラフィを使用して形成された構造と比較して、複数の機能セルのコンパクトアレイを有するI C構造を効果的に示すであろう。例えば、本明細書において様々に記載されるような複数の技術を使用して形成された複数の構造は、2つの隣接セルの境界の間の距離が100 nm、50 nm、30 nm、若しくは10 nmより小さい、又は何か他の適切な上限値である複数の機能セルのアレイを含んでよい。このことは当該開示に照らし明らかであろう。また、これらの機能セル境界は、たとえサブ100 nm解像度であっても、拡散ラインもゲートラインも隣接セルの境界間に存在しないように形成され得る。更に、そのようなコンパクトにされた構造は、1つのリソグラフィプロセス、及び1又は0個のマスクを使用して形成され得る。加えて、本明細書において記載される複数の技術は、複数の機能セルのアレイを形成する場合に、（例えば、従来の193 nmフォトリソグラフィを使用して複数のセルの複数の境界を形成する場合と比較して）、最低10、25、40、若しくは50パーセントの面積削減、又は、何か他の適切な最小面積削減を達成すべく使用され得る。面積の削減は、例えば、アレイ総面積、終端間の拡散距離、又は、終端間のゲート距離を使用して測定され得る。多数の構成及び変更が当該開示に照らし明らかであろう。30

40

#### 【0008】

##### [構造及び方法]

図3 Aは、本開示の一実施形態に係る、格子状の複数の拡散ライン122及び複数のゲートライン124上に形成された3つの機能セル132、134、136を含む例示的なI C構造300を示す。機能セル132、134、136は、例えば、F P G A若しくは他の論理デバイスの複数の論理セル、又は、S R A M若しくは他のメモリデバイスの複数のビットセルであってよい。格子状の拡散金属及びゲート金属、又は他の適切な格子の材料を使用して供給され得る他の複数の機能セルが当該開示に照らし明らかであろう。図から分かるように、複数の拡散ライン122及び複数のゲートライン124は基板110上に形成される。基板110は、半導体基板、又は絶縁体基板などの任意の適切な基板である50

ってよい。例えば、基板 300 としては、シリコン (Si)、ゲルマニウム (Ge)、シリコングルマニウム (SiGe)、1 又は複数の III-V 材料、ガラス、酸化物材料（例えば二酸化シリコン）、窒化物材料（例えば、窒化シリコン）、及び／又は任意の他の適切な半導体若しくは絶縁体材料が挙げられてよい。いくつかの実施形態において、基板 110 は、バルク基板、セミコンダクタ・オン・インシュレータ (SOI、ここで、X は、Si、Ge、若しくは SiGe などの半導体材料)、又は多層構造として構成されてよい。他の適切な基板材料及び／又は構成が、所与の目的用途又は最終用途に依存し、当該開示に照らし明らかであろう。

#### 【0009】

図 3A に示される例示的な IC 構造 300において、複数の拡散ライン 122 が、横方向に伸びてあり、説明の簡略化のために薄いグレーで示されている。複数の拡散ライン 122 は、様々なパターニングプロセス、エッチングプロセス、及び堆積プロセスを含む任意の適切な技術を使用して形成され得る。例えば、複数の拡散ライン 122 の材料は、（スパッタ堆積などの）物理気相成長法 (PVD) プロセス、化学気相成長法 (CVD) プロセス、原子層堆積 (ALD) プロセス、分子線エピタキシ (MBE) プロセス、及び／又は任意の他の適切な成長法又は堆積のプロセスを使用して基板 110 内及び／又は基板 110 上に堆積され得る。複数の拡散ライン 122 の材料としては、目的用途又は最終用途に応じて、Si、Ge、SiGe、及び／若しくは 1 又は複数の III-V 材料、又は、任意の他の適切な材料若しくは複数の材料の組み合わせが挙げられてよい。加えて、いくつかの実施形態において、複数の拡散ライン 122 は n 型ドープ及び／又は p 型ドープされてよい。複数の拡散ライン 122 は、互いに一貫した材料を有さなくてもよいことに留意されたい。例えば、複数の拡散ライン 122 は、ドープ型が交互になっていてよい（例えば、あるラインが n 型ドープを有し、隣接するラインが p 型ドープを有する状態）。また、複数の拡散ライン 122 は、説明の簡略化のために一貫した幅及び間隔で示されているが、本開示はそのように制限されるよう意図されていないことにも留意されたい。更に、（例えば、プレナトランジスタなどの、基板上に構築される複数のプレナデバイスについては）複数の拡散ライン 122 は基板 110 の上面と面一であってよい、又は、（例えば、フィン付きトランジスタなどの、基板上に構築される複数のフィン付きデバイスについては）複数の拡散ライン 122 は基板 110 の上面から突き出でてよい、又はそれらの何らかの組み合わせであってよいことにも留意されたい。

#### 【0010】

例示的な IC 構造 300について続けると、複数のゲートライン 124 が複数の拡散ライン 122 上に形成されるよう示されており、複数のゲートライン 124 は縦方向に伸び、説明の簡略化のために濃いグレーで示されている。複数のゲートライン 124 は、様々なパターニングプロセス、エッチングプロセス、及び堆積プロセスを含む任意の適切な技術を使用して形成され得る。例えば、複数のゲートライン 124 の材料は、限定はされないが、上記の堆積技術（例えば、PVD、CVD、ALD、MBE）を含む任意の適切なプロセスを使用して堆積され得る。複数のゲートライン 124 の材料としては、目的用途又は最終用途に応じて、1 又は複数の金属若しくは金属合金、ポリシリコン、及び／又は任意の他の適切な材料が挙げられてよい。複数のゲートライン 124 は、互いに一貫した材料を有さなくてもよいことに留意されたい。また、複数のゲートライン 124 は、説明の簡略化のために一貫した幅及び間隔で示されているが、本開示はそのように制限されるよう意図されていないことにも留意されたい。更に、複数のゲートライン 124 は、説明の簡略化のために複数の拡散ライン 122 の上に格子状に形成されているが、本開示はまた、そのように制限されるよう意図されていないことに留意されたい。複数の拡散ライン 122 及び複数のゲートライン 124 について、多数の変更及び構成が当該開示に照らし明らかであろう。

#### 【0011】

図 3A に示される例示的な実施形態において、機能セル 132、134、136 の境界は破線で示されている。これらの機能セルは、様々な論理要素若しくはブロック、RAM

10

20

30

40

50

ブロックなどの任意の適切な構造を含んでよく、本開示は、別段の指示のない限り、複数の機能セルに関して任意の特定の構造に制限されるよう意図されていない。この例示的な実施形態において、複数の機能セルの複数の境界は、例えば、電子ビームリソグラフィ若しくは電子ビーム直接描画（E B D W）、極端紫外線リソグラフィ（E U V L）、又はナノインプリントリソグラフィなどの次世代リソグラフィ（N G L プロセス）を使用して形成される。概して、複数のセル境界を形成するための複数の技術は、レジストの形成、N G L プロセスを使用したレジストのパターニング、及び、次に、複数の機能セルの間で複数の拡散ライン 122 及び / 又は複数のゲートライン 124 を切り離すためのエッチングを含み得る。このようにして、複数の機能セルのコンパクトアレイは実現され得る。なぜなら、本明細書においてより詳細に説明されるように、N G L プロセスが、（例えば 19 3 nm フォトリソグラフィと比較して、）複数の機能セルの複数の境界がより高い精度で形成されることを可能にし、更に、複数の隣接セルの複数の境界が互いにより近接して形成されることを可能にするからである。

#### 【 0 0 1 2 】

複数の機能セル境界の形成を助けるべく使用されるレジスト（図示せず）は、限定はされないが、有機フォトレジスト材料（例えばポリ（メタクリル酸メチル）、ポリ（ジメチルグルタルイミド）、フェノールホルムアルデヒド樹脂、S U 8、又は他のポリマー）、無機フォトレジスト材料（例えば、カルコゲニド）、分子フォトレジスト材料（例えば、トルキセン）、高解像度レジスト（例えば、水素シルセスキオキサン（H S Q））、前述のものの混合物、及び / 又は、導電性材料層上のレジストとしての使用に適した任意の他の材料を含む任意の適切な材料を含んでよい。レジスト材料は、限定はされないが、スピンドローティングを含む任意の適切なプロセスを使用して堆積されてよい。レジストは、当該開示に照らし明らかのように、複数の機能セル（例えばセル 132、134 及び 136）が形成される前、これらの形成が開始された後、又は、これらの形成が完了した後に、格子状の複数の拡散ライン 122 及び複数のゲートライン 124 上に堆積されてよい。いくつかの例では、レジストの材料及び厚さは、レジストをパターニングすべく使用されるリソグラフィプロセスに基づいて選択され得る。例えば、電子ビームリソグラフィ又は E B D W を使用する場合、レジストは、電子ビームでその溶解度を変更可能な電子感応性（e l e c t r o n s e n s i t i v e）膜であってよい。しかしながら、いくつかの例において、適切なフォトレジストが電子ビーム露光に使用されてよい。他の適切なレジストの複数の材料及び / 又は複数の構成は、所与の目的用途又は最終用途に依存し、当該開示に照らし明らかであろう。

#### 【 0 0 1 3 】

レジストは堆積後、1 又は複数のリソグラフィプロセスを使用してパターニングされ得る。いくつかの実施形態において、レジストは、電子ビームリソグラフィ若しくは E B D W、E U V L、ナノインプリントリソグラフィ、又は何か他の適切な N G L プロセスを使用してパターニングされる。いくつかの実施形態において、リソグラフィプロセスは、1 又は 0 個のマスクを必要としてよく、更に、1 つのリソグラフィプロセスしか必要としなくてもよい。例えば、E B D W は、ただ 1 つのリソグラフィプロセスでレジストをパターニングするのに 1 又は複数の集束電子ビームが使用され得る、マスクレスのリソグラフィプロセスである。別の例では、E U V L が、極端紫外波長（例えば 13.5 nm）とただ 1 つのマスクとを使用して、ただ 1 つのリソグラフィプロセスでレジストをパターニングする。いくつかのそのような実施形態において、リソグラフィプロセスは、たとえ 1 又は 0 個のマスクしか使用しない場合であっても高精度の複数のレジストフィーチャを実現可能であると考えられ、それは、例えば、サブ 100 nm、サブ 50 nm、サブ 30 nm、又はサブ 10 nm の解像度を実現可能であることを含む。換言すると、I C 構造 300 を形成すべく使用されるリソグラフィプロセスは、本明細書においてより詳細に説明されるように、サブ 100 nm、サブ 50 nm、サブ 30 nm、又はサブ 10 nm のクリティカルディメンジョンを有する複数のレジストフィーチャを実現可能であると考えられる。

#### 【 0 0 1 4 】

10

20

30

40

50

リソグラフィプロセスの実行後、レジストを適切にパターニングすべく、後のレジスト処理が必要であつてよい。例えば、そのような処理は、リソグラフィ処理中に露光された複数の領域を除去するための適切な溶媒の使用、又は他の適切な処理を含んでよい。レジストを適切にパターニングした後、下層の複数の拡散ライン 122、複数のゲートライン 124、及び／又は基板 110 がエッチングされて、パターンが転写され、複数の機能セルの複数の境界が形成され得る。当該開示に照らし明らかなように、複数の境界は、単に複数の拡散ライン 122 及び／又は複数のゲートライン 124 の断線／切断／等を行い、複数の機能セルを望みどおりに切り離すことによって形成されてよい。任意の適切なウェットエッチング又はドライエッチングが使用されてよく、いくつかの実施形態において、エッチャント及び／又はエッチングプロセスは、レジストの特性（例えば、レジストの材料及び／又は厚さ）及び／又は導電性層の特性（例えば、層の材料及び／又は厚さ）によって決定付けられてよい。レジストパターンが転写され次第、レジストは、レジスト剥離プロセス又は平坦化プロセスなどの任意の適切なプロセスを使用して除去されてよい。

#### 【0015】

図 3 A から分かるように、機能セル 132 及び 134 の境界間の距離はスペース S3 であり、機能セル 136 の境界とセル 132 及び 134 の境界との間の距離はスペース S4 である。スペース S3、S4 はそれぞれ、図 1 の IC 構造 100 上に示されたスペース S1、S2 と比較され得る。IC 構造 100 上のセル 132、134、136 の境界は従来の 193 nm フォトリソグラフィを使用して形成されたものであり、従って、隣接セルの境界間の達成可能な最小距離（例えば、S1 及び S2）は従来のリソグラフィプロセスに基づいて制限されることを思い出されたい。EBDW 及び EUVL などの複数の NGL プロセスを使用して、同じセル 132、134、136 は互いにより近接するように移動され得る。例えば、S3 及び S4 は、100 nm、50 nm、30 nm、若しくは 10 nm より小さい、又は何か他の適切な上限値であつてよい。このことは本開示に照らし明らかである。スペース S3 及び S4 はこの例示的な実施形態では等しいが、そうでなくてもよい。例えば、隣接セル間の横方向の間隔は、隣接セル間の縦方向の間隔に、（図 3 A の場合のように等しいこともあるが、）等しくなくてよい。更に、図 1 に示された従来の IC 構造 100 では、隣接セルの境界間に拡散ライン又はゲートラインが存在していることに留意されたい。例えば、スペース S1 においてセル 132 及び 134 の境界間にゲートラインが位置しており、スペース S2 においてセル 132 及び 136 の境界間に拡散ラインが位置している。しかしながら、複数のセル境界を形成すべく NGL プロセスを使用すると、図 3 A から分かるように、たとえサブ 100 nm の適用であつても、セル境界間には拡散ラインもゲートラインも存在しないようにできる。更に、そのような精密かつコンパクトなアレイは、上記のように、1 つのリソグラフィプロセス、及び 1 又は 0 個のマスクを使用して形成され得る。

#### 【0016】

図 3 A は論理セル 132、134、136 の境界を示しているが、説明の簡略化のために、複数の拡散ライン 122 及び複数のゲートライン 124 における複数の実際の切断は示されていない。図 3 B は、格子状の複数の拡散ライン 122 及び複数のゲートライン 124 内の複数の切断 140 を例示する、図 3 A の IC 構造 300 を示している。図から分かるように、複数の切断 140 は、それらがもはや物理的及び／又は電気的に接触しないように、複数の拡散ライン 122 及び複数のゲートライン 124 を切り離す、又はそうでなければ分割する。従って、複数の切断 140 により、複数の機能セル（例えば、セル 132、134、136）を互いに電気的に絶縁可能になる。レジストをパターニングし、複数の切断 140 が格子状の複数の拡散ライン 122 及び複数のゲートライン 124 の中にエッチングされることを可能にすべく NGL プロセス（例えば、EBDW、EUVL 等）を使用することなど、本明細書において記載された複数の技術を使用して複数の切断 140 は作られ得る。それにより、図 3 A に示された複数の機能セル境界を形成する。

#### 【0017】

図 4 は、本開示の一実施形態に係る、格子状の複数の拡散ライン 122 及び複数のゲー

10

20

30

40

50

トライン 124 上に形成された複数の機能セル 130 のアレイを含む例示的な I C 構造 400 を示している。図から分かるように、I C 構造 400 は、図 2 に示された構造と同様、基板 110 上に形成された 14 本の拡散ライン 122 及び 14 本のゲートライン 124 を含む四角形である。基板 110、複数の拡散ライン 122、及び複数のゲートライン 124 に関する前述の説明は、この例示的な実施形態において等しく適用可能である。図 2 に示された I C 構造 200 が、従来の 193 nm フォトリソグラフィを使用して形成された複数の境界を有する 25 個のセルのアレイを含むことを思い出されたい。図 4 に示された I C 構造 400 は、EBDW 又は EUVL などの NGL プロセスを使用して形成された複数の境界を有する複数の機能セル 130 を含む。I C 構造 200 を、図 4 に示された I C 構造と比較すると、図 4 に示された I C 構造 400 内の複数の機能セルのアレイは、より高密度である、又はよりコンパクトであることが分かる。更に図から分かるように、(図 2 の従来の I C 構造 200 上のアレイ内のセルの合計量である) 25 個の機能セル 130 は、I C 構造 400 の右下隅において括弧付きの線で示される、図 4 の方形領域内に収まる。この領域は、図 4 に示された I C 構造 400 の総面積のおよそ 51 パーセントに相当する。従って、本明細書において記載された複数の技術は、元の面積寸法のほんの 51 パーセントにすぎない面積に同数の機能セル(例えば、この例の場合では 25 個)を収容するアレイに收めるべく使用され得、それにより、49 パーセントの面積削減を達成する。いくつかの実施形態において、本明細書において様々に記載される複数の技術は、当該開示に照らし明らかのように、複数の機能セルのアレイについて、最低 10、25、40 又は 50 パーセントの面積削減、又は何か他の適切な最小面積削減を達成すべく使用され得る。

#### 【 0018 】

図 5 は、一実施形態に従って構成された、複数の論理セル 138 のアレイを含む、例示的なフィールドプログラマブルゲートアレイ(FPGA)構造 500 を示している。図から分かるように、FPGA 構造 500 は、本明細書において記載された複数の技術(例えば、NGL プロセスを使用した、複数の論理セルの複数の境界の切断)を使用して形成された 9 個の論理セル 138 のアレイを含む。複数の論理セル 138 は、複数の論理要素(LE)、又は複数の組み合わせ論理ブロック(CLB)として既知であつてよく、複数の論理セル 138 はいくつかの論理ゲートの機能を形成してよい。理解され得るように、複数の論理セル 138 は FPGA 構造 500 の複数の機能セルである。プログラム可能相互接続 150 を使用して論理セル 138 間に複数の相互接続が作られる。相互接続 150 は、例えば、複数のチャネル又は他の複数のユニットで論理的に構成されてよい。I/O ピンは I/O ブロック 160 と称されてよく、それらは概して複数の入力又は複数の出力となるようプログラム可能である。I/O ブロック 160 はまた、例えば、低電力又は高速の接続などの他の複数の特徴を提供できる。目的用途又は最終用途に応じて、メモリ(図示せず)もまた、他の典型的な又は適切な構成部品と共に FPGA 構造 500 に含まれてよい。多数の変更及び構成が当該開示に照らし明らかであろう。

#### 【 0019 】

##### [ 例示的システム ]

図 6 は、一例示的実施形態に係る、本明細書において開示された複数の技術を使用して形成された集積回路(I C)の複数の構造又は複数のデバイスが実装されたコンピューティングシステム 1000 を示している。図から分かるように、コンピューティングシステム 1000 はマザーボード 1002 を収容している。マザーボード 1002 は、限定はされないが、プロセッサ 1004 と少なくとも 1 つの通信チップ 1006 とを含むいくつのコンポーネントを含んでよい。それらの各々は、マザーボード 1002 に物理的かつ電気的に接続される、又はそうでなければマザーボード 1002 に統合され得る。理解され得るように、それがメインボード、メインボードに搭載されたデーターボード、又はシステム 1000 の唯一のボード等であるかないかに関わらず、マザーボード 1002 は、例えば任意のプリント回路基板であつてよい。

#### 【 0020 】

10

20

30

40

50

その用途に応じて、コンピューティングシステム 1000 は、マザーボード 1002 に物理的かつ電気的に接続されてもされなくてもよい 1 又は複数の他のコンポーネントを含んでよい。これらの他のコンポーネントは、限定はされないが、揮発性メモリ（例えば、DRAM）、不揮発性メモリ（例えば、ROM、STTM 等）、グラフィックスプロセッサ、デジタル信号プロセッサ、暗号プロセッサ、チップセット、アンテナ、ディスプレイ、タッチスクリーンディスプレイ、タッチスクリーンコントローラ、バッテリ、オーディオコーデック、ビデオコーデック、電力増幅器、全地球測位システム（GPS）デバイス、コンパス、加速度計、ジャイロスコープ、スピーカ、カメラ、及び（ハードディスクドライブ、コンパクトディスク（CD）、デジタル・バーサタイル・ディスク（DVD）等といった）大容量記憶装置を含んでよい。コンピューティングシステム 1000 に含まれる複数コンポーネントのうちの任意のものは、一例示的実施形態に係る複数の開示された技術を使用して形成された 1 又は複数の集積回路の構造又はデバイスを含んでよい。いくつかの実施形態において、複数の機能は 1 又は複数のチップの中に統合され得る（例えば、通信チップ 1006 がプロセッサ 1004 の一部であるか、又はそうでなければその中に統合され得ることに留意されたい）。 10

#### 【0021】

通信チップ 1006 は、コンピューティングシステム 1000 との間でのデータ転送のための無線通信を可能にする。「無線」という用語及びその派生語は、非固体媒体を通して変調電磁放射を使用することによりデータを通信し得る回路、デバイス、システム、方法、技術、通信チャネル等を説明すべく使用され得る。当該用語は、関連付けられたデバイスが有線を何も含まないことを暗示するものではないが、いくつかの実施形態においては有線を含まないこともある。通信チップ 1006 は、限定はされないが、Wi-Fi（登録商標）（IEEE802.11 ファミリ）、WiMAX（IEEE802.16 ファミリ）、IEEE802.20、ロングタームエボリューション（LTE）、EVDO、HSPA+、HSDPA+、HSUPA+、EDGE、GSM（登録商標）、GPRS、CDMA、TDMA、DECT、Bluetooth（登録商標）、それらの派生、並びに、3G、4G、5G、及びそれ以降として指定された任意の他の無線プロトコルを含むいくつかの無線規格又は無線プロトコルのうちの何れかを実装してよい。コンピューティングシステム 1000 は、複数の通信チップ 1006 を含んでよい。例えば、第 1 の通信チップ 1006 は Wi-Fi（登録商標）及び Bluetooth（登録商標）などの、短距離無線通信専用であってよく、第 2 の通信チップ 1006 は、GPS、EDGE、GPRS、CDMA、WiMAX、LTE、EVDO、及びその他のものなどの長距離無線通信専用であってよい。 20 30

#### 【0022】

コンピューティングシステム 1000 のプロセッサ 1004 は、プロセッサ 1004 内にパッケージングされた集積回路ダイを含む。いくつかの実施形態において、プロセッサの集積回路ダイは、本明細書において様々に記載されたような、開示された技術を使用して形成された 1 又は複数の集積回路の構造又はデバイスが実装されたオンボードの回路を含む。「プロセッサ」という用語は、例えば、レジスタ及び／又はメモリからの電子データを処理して、その電子データを、レジスタ及び／又はメモリに格納され得る他の電子データに変換する任意のデバイス又はデバイスの一部を指し得る。 40

#### 【0023】

通信チップ 1006 はまた、通信チップ 1006 内にパッケージングされた集積回路ダイを含んでよい。そのようないくつかの例示的な実施形態に従って、通信チップの集積回路ダイは、本明細書において様々に記載されたような、開示された技術を使用して形成された 1 又は複数の集積回路の構造又はデバイスを含む。当該開示に照らし理解されるよう、マルチスタンダードの無線機能が、（例えば、別個の複数の通信チップを有するのではなく、あらゆるチップ 1006 の機能がプロセッサ 1004 の中に統合されている）プロセッサ 1004 の中に直接統合されてよいことに留意されたい。更に、プロセッサ 1004 がそのような無線機能を有するチップセットであってよいことに留意されたい。要す 50

るに、任意の数のプロセッサ 1004 及び / 又は通信チップ 1006 が使用され得る。同様に、任意の 1 つのチップ又はチップセットは、その中に統合された複数の機能を有し得る。

#### 【 0024 】

いくつかの実施形態において、コンピューティングシステム 1000 は、フィールドプログラマブルゲートアレイ (FPGA)、スタティックランダムアクセスメモリ (SRAM)、及び / 又は、本明細書において記載された技術を使用して形成された複数の機能セルのコンパクトアレイを含む他の論理デバイス若しくはメモリデバイスを含んでよい。これらの機能セルは、( 例えは、FPGA の場合の ) 論理セル及び / 又は ( 例えは、SRAM の場合の ) ビットセル、又は、目的用途又は最終用途に基づいた任意の他の適切な機能セルであってよい。10

#### 【 0025 】

様々な実装において、コンピューティングデバイス 1000 は、ラップトップ、ネットブック、ノートブック、スマートフォン、タブレット、パーソナルデジタルアシスタント (PDA)、ウルトラモバイル PC、携帯電話、デスクトップコンピュータ、サーバ、プリンタ、スキヤナ、モニタ、セットトップボックス、エンターテインメント制御ユニット、デジタルカメラ、ポータブル音楽プレイヤ、デジタルビデオレコーダ、又は、データを処理する、若しくは本明細書において様々に記載されるような開示された技術を使用して形成された 1 又は複数の集積回路の構造又はデバイスを使用する任意の他の電子デバイスであってよい。20

#### 【 0026 】

##### [ 更なる例示的な実施形態 ]

以下の例は更なる複数の実施形態に関連し、それらから多数の変形及び構成が明らかであろう。

#### 【 0027 】

例 1 は、基板と、当該基板上に形成された複数の機能セルのアレイとを含む集積回路である。当該複数の機能セルの各々は、境界を有し、アレイ内の 2 つの隣接セルの境界間の距離は 50 nm より小さい。

#### 【 0028 】

例 2 は例 1 の主題を含み、当該基板はシリコン (Si) 及び / 又はゲルマニウム (Ge) を含む。30

#### 【 0029 】

例 3 は例 1 - 2 の何れかの主題を含み、アレイ内の 2 つの隣接セルの境界間の距離は 20 nm より小さい。

#### 【 0030 】

例 4 は例 1 - 3 の何れかの主題を含み、当該複数のセルは、複数のゲートアレイ論理セル及び / 又は複数のメモリビットセルを含む。

#### 【 0031 】

例 5 は例 1 - 4 の何れかの主題を含み、当該複数のセルは、格子状の複数の拡散ライン及び複数のゲートライン上に形成されている。40

#### 【 0032 】

例 6 は例 1 - 5 の何れかの主題を含み、2 つの隣接セルの境界間にはゲートラインも拡散ラインも存在しない。

#### 【 0033 】

例 7 は例 1 - 6 の何れかの主題を含み、複数のセルのアレイは、複数のセルの境界を形成すべく 193 nm フォトリソグラフィを使用して形成され得る最も高い密度の実効構造より、10 パーセントから 50 パーセント高密度である。

#### 【 0034 】

例 8 は、例 1 - 7 の何れかの主題を含むフィールドプログラマブルゲートアレイ (FPGA) デバイスである。50

**【 0 0 3 5 】**

例 9 は、例 1 - 7 の何れかの主題を含むスタティックランダムアクセスメモリ ( S R A M ) デバイスである。

**【 0 0 3 6 】**

例 10 は、例 1 - 7 の何れかの主題を含むコンピューティングシステムである。

**【 0 0 3 7 】**

例 11 は、集積回路を形成する方法である。当該方法は、基板を設ける段階と、複数の拡散ラインを形成する段階と、複数のゲートラインを形成する段階であって、複数の拡散ライン及び複数のゲートラインは格子状構造で形成される、段階と、当該格子状構造上にレジストを形成する段階と、サブ 100 nm クリティカルディメンジョンを有する複数のレジストフィーチャを実現でき、1 又は 0 個のマスクを必要とするリソグラフィプロセスを使用して複数の機能セル境界を形成すべくレジストをパターニングする段階であって、複数のセルはアレイ内に配置される、段階と、パターンを格子状構造にエッチングする段階とを備える。10

**【 0 0 3 8 】**

例 12 は例 11 の主題を含み、複数のセルは、ゲートアレイ論理セル及び / 又はメモリビットセルを含む。

**【 0 0 3 9 】**

例 13 は例 11 - 12 の何れかの主題を含み、当該リソグラフィプロセスは電子ビームリソグラフィである。20

**【 0 0 4 0 】**

例 14 は例 13 の主題を含み、電子ビームリソグラフィはマルチビームを含む。

**【 0 0 4 1 】**

例 15 は例 11 - 14 の何れかの主題を含み、当該リソグラフィプロセスはマスクレスである。

**【 0 0 4 2 】**

例 16 は例 11 - 12 の何れかの主題を含み、当該リソグラフィプロセスは極端紫外線リソグラフィ ( E U V L ) である。

**【 0 0 4 3 】**

例 17 は例 11 - 12 の何れかの主題を含み、当該リソグラフィプロセスはナノインプリントリソグラフィである。30

**【 0 0 4 4 】**

例 18 は例 11 - 17 の何れかの主題を含み、当該リソグラフィプロセスは、サブ 30 nm クリティカルディメンジョンを有する複数のレジストフィーチャを実現できる。

**【 0 0 4 5 】**

例 19 は例 11 - 18 の何れかの主題を含み、当該リソグラフィプロセスは、サブ 10 nm クリティカルディメンジョンを有する複数のレジストフィーチャを実現できる。

**【 0 0 4 6 】**

例 20 は例 11 - 19 の何れかの主題を含み、複数のセルのアレイを含むフィールドプログラマブルゲートアレイ ( F P G A ) デバイスを形成する段階を更に備える。40

**【 0 0 4 7 】**

例 21 は例 11 - 19 の何れかの主題を含み、複数のセルのアレイを含むスタティックランダムアクセスメモリ ( S R A M ) デバイスを形成する段階を更に備える。

**【 0 0 4 8 】**

例 22 は、複数の機能セルのアレイを形成する方法である。当該方法は、基板を設ける段階と、当該基板上にレジストを形成する段階と、複数の機能セル境界を形成すべくレジストをパターニングする段階であって、2 つの隣接セルの境界間の距離は 50 nm より小さい、段階と、パターンを基板の中にエッチングする段階とを備える。

**【 0 0 4 9 】**

例 23 は例 22 の主題を含み、複数のセルは複数のゲートアレイ論理セル及び / 又は複

50

数のメモリピットセルを含む。

【0050】

例24は例22-23の何れかの主題を含み、当該リソグラフィプロセスは電子ビームリソグラフィである。

【0051】

例25は例24の主題を含み、当該電子ビームリソグラフィはマルチビームを含む。

【0052】

例26は例22-25の何れかの主題を含み、当該リソグラフィプロセスはマスクレスである。

【0053】

例27は例22-23の何れかの主題を含み、当該リソグラフィプロセスは極端紫外線リソグラフィ(EUVL)である。

10

【0054】

例28は例22-23の何れかの主題を含み、当該リソグラフィプロセスはナノインプリントリソグラフィである。

【0055】

例29は例22-28の何れかの主題を含み、当該リソグラフィプロセスは、サブ30nmクリティカルディメンジョンを有する複数のレジストフィーチャを実現できる。

【0056】

例30は例22-29の何れかの主題を含み、当該リソグラフィプロセスは、サブ10nmクリティカルディメンジョンを有する複数のレジストフィーチャを実現できる。

20

【0057】

例31は例22-30の何れかの主題を含み、複数のセルのアレイを含むフィールドプログラマブルゲートアレイ(FPGA)デバイスを形成する段階を更に備える。

【0058】

例32は例22-30の何れかの主題を含み、複数のセルのアレイを含むスタティックランダムアクセスメモリ(SRAM)デバイスを形成する段階を更に備える。

【0059】

例示的な実施形態の前述の説明は、例示及び説明を目的として示してきた。当該説明は、包括的であること、又は、本開示を、開示された形態そのものに限定することは意図されていない。当該開示に照らし、多数の変形及び変更が可能である。本開示の範囲は、この詳細な説明によってではなく、むしろ、本明細書に添付された特許請求の範囲によって限定されることが意図されている。本出願に対する優先権を主張する今後なされる出願は、開示された主題を異なるやり方で特許請求してよく、概して、本明細書において様々に開示された、又はそうでなければ例示された1又は複数の限定の任意のセットを含んでよい。

30

【図1】

FIG. 1

【図2】

FIG. 2

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図4】

FIG. 4

【図5】

【図6】

---

フロントページの続き

|              |           |              |       |

|--------------|-----------|--------------|-------|

| (51)Int.Cl.  | F I       |              |       |

| H 01 L 21/82 | (2006.01) | H 01 L 27/10 | 4 6 1 |

|              |           | H 01 L 27/11 |       |

|              |           | H 01 L 21/82 | M     |

|              |           | H 01 L 21/82 | A     |

(72)発明者 ゴエル、ニティ

アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレ

バード・2200 インテル・コーポレーション内

(72)発明者 ボウ - グハザレ、シリビオ、イー。

アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレ

バード・2200 インテル・コーポレーション内

(72)発明者 アクサミット、ランディ、ジェイ。

アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレ

バード・2200 インテル・コーポレーション内

審査官 植木 隆和

(56)参考文献 特開2010-087194 (JP, A)

特開2013-157547 (JP, A)

特開2013-149928 (JP, A)

特開平05-298394 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 027

G 03 F 7 / 20

H 01 37 / 305