(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5180225号

(P5180225)

(45) 発行日 平成25年4月10日(2013.4.10)

(24) 登録日 平成25年1月18日(2013.1.18)

|                      |             |

|----------------------|-------------|

| (51) Int.Cl.         | F 1         |

| HO3L 7/089 (2006.01) | HO3L 7/08 D |

| HO3L 7/093 (2006.01) | HO3L 7/08 E |

| HO3L 7/197 (2006.01) | HO3L 7/18 A |

請求項の数 35 (全 21 頁)

|               |                               |           |                                                                                                                |

|---------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2009-539444 (P2009-539444)  | (73) 特許権者 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (86) (22) 出願日 | 平成19年11月27日(2007.11.27)       | (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (65) 公表番号     | 特表2010-512063 (P2010-512063A) | (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (43) 公表日      | 平成22年4月15日(2010.4.15)         | (74) 代理人  | 100088683<br>弁理士 中村 誠                                                                                          |

| (86) 國際出願番号   | PCT/US2007/085658             | (74) 代理人  | 100103034<br>弁理士 野河 信久                                                                                         |

| (87) 國際公開番号   | W02008/067324                 |           |                                                                                                                |

| (87) 國際公開日    | 平成20年6月5日(2008.6.5)           |           |                                                                                                                |

| 審査請求日         | 平成21年7月30日(2009.7.30)         |           |                                                                                                                |

| (31) 優先権主張番号  | 11/565,062                    |           |                                                                                                                |

| (32) 優先日      | 平成18年11月30日(2006.11.30)       |           |                                                                                                                |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                                                                |

| 前置審査          |                               |           |                                                                                                                |

最終頁に続く

(54) 【発明の名称】位相同期ループのための線形位相周波数検出器およびチャージポンプ

## (57) 【特許請求の範囲】

## 【請求項 1】

基準信号とクロック信号とを受け取るように、前記基準信号と前記クロック信号とに基づいて第1および第2の信号を生成するように、予め定められた量だけ前記第1の信号を遅らせるように、前記遅れた第1の信号に基づいてリセット信号を生成するように、そして、前記リセット信号に基づいて前記第1および第2の信号をリセットするように構成された位相周波数検出器と、

前記第1および第2の信号を受け取り、そして、前記基準信号と前記クロック信号との間の位相誤差を示す出力信号を生成するように構成されたチャージポンプと、

を備えるデバイスであって、

前記予め定められた量の遅れ  $T_D$  は、 $T_D > T_{ON} + d t_{MAX}$  で表され、前記チャージポンプのデッドゾーンの原因となる  $on$  時間  $T_{ON}$  と、周波数ロック達成後の前記クロック信号と前記基準信号との間の予期される最大時間差  $d t_{MAX}$  とを足したよりも大きい、デバイス。

## 【請求項 2】

前記第1の信号は、前記クロック信号に対して早い前記基準信号を示す  $up$  信号であり、そして、前記第2の信号は、前記クロック信号に対して遅い前記基準信号を示す  $down$  信号である、請求項1に記載のデバイス。

## 【請求項 3】

前記第1の信号は、前記クロック信号に対して遅い前記基準信号を示す  $down$  信号で

10

20

あり、そして、前記第2の信号は、前記クロック信号に対して早い前記基準信号を示すup信号である、請求項1に記載のデバイス。

【請求項4】

前記位相周波数検出器は、さらに前記第2の信号に基づいて前記リセット信号を生成するように構成されている、請求項1に記載のデバイス。

【請求項5】

前記位相周波数検出器は、

前記基準信号を受け取り、前記第1の信号を供給するように構成された第1のフリップフロップと、

前記クロック信号を受け取り、前記第2の信号を供給するように構成された第2のフリップフロップと、10

予め定められた量だけ前記第1の信号を遅らせるように構成された遅延ユニットと、

前記遅れた第1の信号および前記第2の信号に基づいて前記第1および第2のフリップフロップのためのリセット信号を生成するように構成された回路と、

を備える、

請求項1に記載のデバイス。

【請求項6】

前記位相周波数検出器は、

前記クロック信号を受け取り、前記第1の信号を供給するように構成された第1のフリップフロップと、20

前記基準信号を受け取り、前記第2の信号を供給するように構成された第2のフリップフロップと、

予め定められた量だけ前記第1の信号を遅らせるように構成された遅延ユニットと、

前記遅れた第1の信号および前記第2の信号に基づいて前記第1および第2のフリップフロップのためのリセット信号を生成するように構成された回路と、

を備える、

請求項1に記載のデバイス。

【請求項7】

前記チャージポンプは、

前記出力信号に第1の電流を供給するように構成された第1の電流ソースと；30

前記出力信号に第2の電流を供給するように構成された第2の電流ソースと、なお、前記第1および第2の電流は逆極性を有している；

前記第1の信号によってイネーブルにされたとき、前記第1の電流ソースを前記出力信号に結合するように構成された第1のスイッチと；

前記第2の信号によってイネーブルにされたとき、前記第2の電流ソースを前記出力信号に結合するように構成された第2のスイッチと；

を備える、

請求項1に記載のデバイス。

【請求項8】

前記クロック信号を生成するために、複数の整数素因数によって、発振器信号を分周するように構成された分周器、40

をさらに備える請求項1に記載のデバイス。

【請求項9】

前記分周器用の前記複数の整数素因数を選択するために、非整数分周比を受け取り、分周器制御を生成するように構成されたシグマ-デルタ変調器、

をさらに備える請求項8に記載のデバイス。

【請求項10】

前記予め定められた量の遅れはプログラム可能である、請求項1に記載のデバイス。

【請求項11】

基準信号とクロック信号とを受け取るように、前記基準信号と前記クロック信号とに基50

づいて第1および第2の信号を生成するように、予め定められた量だけ前記第1の信号を遅らせるように、前記遅れた第1の信号に基づいてリセット信号を生成するように、そして、前記リセット信号に基づいて前記第1および第2の信号をリセットするように構成された位相周波数検出器と、

前記第1および第2の信号を受け取り、そして、前記基準信号と前記クロック信号との間の位相誤差を示す出力信号を生成するように構成されたチャージポンプと、

を備える集積回路であって、

前記予め定められた量の遅れ  $T_D$  は、 $T_D > T_{ON} + dt_{MAX}$  で表され、前記チャージポンプのデッドゾーンの原因となる  $on$  時間  $T_{ON}$  と、周波数ロック達成後の前記クロック信号と前記基準信号との間の予期される最大時間差  $dt_{MAX}$  とを足したよりも大きい、集積回路。

#### 【請求項12】

前記第1の信号は、前記クロック信号に対して早い前記基準信号を示す  $up$  信号であり、そして、前記第2の信号は、前記クロック信号に対して遅い前記基準信号を示す  $down$  信号である、請求項11に記載の集積回路。

#### 【請求項13】

前記第1の信号は、前記クロック信号に対して遅い前記基準信号を示す  $down$  信号であり、そして、前記第2の信号は、前記クロック信号に対して早い前記基準信号を示す  $up$  信号である、請求項11に記載の集積回路。

#### 【請求項14】

前記位相周波数検出器は、さらに前記第2の信号に基づいて前記リセット信号を生成するように構成されている、請求項11に記載の集積回路。

#### 【請求項15】

前記位相周波数検出器は、

前記基準信号を受け取り、前記第1の信号を供給するように構成された第1のフリップフロップと、

前記クロック信号を受け取り、前記第2の信号を供給するように構成された第2のフリップフロップと、

予め定められた量だけ前記第1の信号を遅らせるように構成された遅延ユニットと、

前記遅れた第1の信号および前記第2の信号に基づいて前記第1および第2のフリップフロップのためのリセット信号を生成するように構成された回路と、

を備える、

請求項11に記載の集積回路。

#### 【請求項16】

前記位相周波数検出器は、

前記クロック信号を受け取り、前記第1の信号を供給するように構成された第1のフリップフロップと、

前記基準信号を受け取り、前記第2の信号を供給するように構成された第2のフリップフロップと、

予め定められた量だけ前記第1の信号を遅らせるように構成された遅延ユニットと、

前記遅れた第1の信号および前記第2の信号に基づいて前記第1および第2のフリップフロップのためのリセット信号を生成するように構成された回路と、

を備える、

請求項11に記載の集積回路。

#### 【請求項17】

前記チャージポンプは、

前記出力信号に第1の電流を供給するように構成された第1の電流ソースと、

前記出力信号に第2の電流を供給するように構成された第2の電流ソースと、なお、前記第1および第2の電流は逆極性を有している；

前記第1の信号によってイネーブルにされたとき、前記第1の電流ソースを前記出力信

10

20

30

40

50

号に結合するように構成された第1のスイッチと；

前記第2の信号によってイネーブルにされたとき、前記第2の電流ソースを前記出力信号に結合するように構成された第2のスイッチと；

を備える、

請求項11に記載の集積回路。

【請求項18】

前記クロック信号を生成するために、複数の整数素因数によって、発振器信号を分周するように構成された分周器、

をさらに備える請求項11に記載の集積回路。

【請求項19】

前記分周器用の前記複数の整数素因数を選択するために、非整数分周比を受け取り、分周器制御を生成するように構成されたシグマ-デルタ変調器、

をさらに備える請求項18に記載の集積回路。

【請求項20】

前記予め定められた量の遅れはプログラム可能である、請求項11に記載の集積回路。

【請求項21】

位相同期ループ(PLL)において位相周波数検出器およびチャージポンプの線形動作を達成するための方法であって：

基準信号とクロック信号とに基づいて前記位相周波数検出器において第1および第2の信号を生成することと；

予め定められた量だけ前記第1の信号を遅らせることと、なお、前記予め定められた量の遅れ $T_D$ は、 $T_D > T_{ON} + d t_{MAX}$ で表され、前記チャージポンプのデッドゾーンの原因となる $on$ 時間 $T_{ON}$ と、周波数ロック達成後の前記クロック信号と前記基準信号との間の予期される最大時間差 $d t_{MAX}$ とを足したよりも大きい；

前記遅れた第1の信号に基づいてリセット信号を生成することと；

前記生成されたリセット信号に基づいて前記第1および第2の信号をリセットすることと；

前記第1および第2の信号に基づいて前記チャージポンプにおいて出力信号を生成することと、なお、前記出力信号は前記基準信号と前記クロック信号との間の位相誤差を示す；

を備える方法。

【請求項22】

前記出力信号を前記生成することは、

前記第1の信号に基づいて、前記出力信号に第1の電流を供給することと；

前記第2の信号に基づいて、前記出力信号に第2の電流を供給することと、なお、前記第1および第2の電流は逆極性を有している；

を備える、

請求項21に記載の方法。

【請求項23】

前記クロック信号を生成するために、複数の整数素因数によって、発振器信号を分周することと、

非整数分周比を達成する前記複数の整数素因数を選択するために分周器制御を生成することと、

をさらに備える請求項21に記載の方法。

【請求項24】

基準信号とクロック信号とに基づいて第1および第2の信号を生成するための手段と；

予め定められた量だけ前記第1の信号を遅らせるための手段と、なお、前記予め定められた量の遅れ $T_D$ は、 $T_D > T_{ON} + d t_{MAX}$ で表され、前記チャージポンプのデッドゾーンの原因となる $on$ 時間 $T_{ON}$ と、周波数ロック達成後の前記クロック信号と前記基準信号との間の予期される最大時間差 $d t_{MAX}$ とを足したよりも大きい；

10

20

30

40

50

前記遅れた第1の信号に基づいてリセット信号を生成するための手段と、前記生成されたりセット信号に基づいて前記第1および第2の信号をリセットするための手段と；

前記第1および第2の信号に基づいて出力信号を生成するための手段と、なお、前記出力信号は前記基準信号と前記クロック信号との間の位相誤差を示す；

を備える装置。

【請求項25】

前記出力信号を生成するための前記手段は、

前記第1の信号に基づいて、前記出力信号に第1の電流を供給するための手段と；

前記第2の信号に基づいて、前記出力信号に第2の電流を供給するための手段と、なお

、前記第1および第2の電流は逆極性を有している；

を備える、

請求項24に記載の装置。

【請求項26】

前記クロック信号を生成するために、複数の整数素因数によって、発振器信号を分周するための手段と、

非整数分周比を達成する前記複数の整数素因数を選択するために分周器制御を生成するための手段と、

をさらに備える請求項24に記載の装置。

【請求項27】

基準信号とクロック信号とを受け取るように、前記基準信号と前記クロック信号とに基づいて第1および第2の信号を生成するように、予め定められた量だけ前記第1の信号を遅らせるように、前記遅れた第1の信号に基づいてリセット信号を生成するように、そして、前記リセット信号に基づいて前記第1および第2の信号をリセットするように構成された位相周波数検出器と、

前記第1および第2の信号を受け取り、そして、前記基準信号と前記クロック信号との間の位相誤差を示す出力信号を生成するように構成されたチャージポンプと、

を含む位相同期ループ、

を備える無線デバイスであって、

前記予め定められた量の遅れ $T_D$ は、 $T_D > T_{ON} + d t_{MAX}$ で表され、前記チャージポンプのデッドゾーンの原因となる $on$ 時間 $T_{ON}$ と、周波数ロック達成後の前記クロック信号と前記基準信号との間の予期される最大時間差 $d t_{MAX}$ とを足したよりも大きい、無線デバイス。

【請求項28】

前記位相同期ループは、

前記クロック信号を生成するために、複数の整数素因数によって、発振器信号を分周するように構成された分周器と、

前記分周器用の前記複数の整数素因数を選択するために、非整数分周比を受け取り、分周器制御を生成するように構成されたシグマ-デルタ変調器と、

をさらに含む、

請求項27に記載の無線デバイス。

【請求項29】

前記第1の信号は、前記クロック信号に対して早い前記基準信号を示す $up$ 信号であり、そして、前記第2の信号は、前記クロック信号に対して遅い前記基準信号を示す $down$ 信号である、請求項27に記載の無線デバイス。

【請求項30】

前記第1の信号は、前記クロック信号に対して遅い前記基準信号を示す $down$ 信号であり、そして、前記第2の信号は、前記クロック信号に対して早い前記基準信号を示す $up$ 信号である、請求項27に記載の無線デバイス。

【請求項31】

10

20

30

40

50

前記位相同期ループの前記位相周波数検出器は、前記第2の信号に基づいて前記リセット信号を生成するように構成されている、請求項27に記載の無線デバイス。

【請求項32】

前記位相同期ループの前記位相周波数検出器は、

前記基準信号を受け取り、前記第1の信号を供給するように構成された第1のフリップフロップと、

前記クロック信号を受け取り、前記第2の信号を供給するように構成された第2のフリップフロップと、

予め定められた量だけ前記第1の信号を遅らせるように構成された遅延ユニットと、

前記遅れた第1の信号および前記第2の信号に基づいて前記第1および第2のフリップフロップのためのリセット信号を生成するように構成された回路と、

を備える、

請求項27に記載の無線デバイス。

【請求項33】

前記位相同期ループの前記位相周波数検出器は、

前記クロック信号を受け取り、前記第1の信号を供給するように構成された第1のフリップフロップと、

前記基準信号を受け取り、前記第2の信号を供給するように構成された第2のフリップフロップと、

予め定められた量だけ前記第1の信号を遅らせるように構成された遅延ユニットと、

前記遅れた第1の信号および前記第2の信号に基づいて前記第1および第2のフリップフロップのためのリセット信号を生成するように構成された回路と、

を備える、

請求項27に記載の無線デバイス。

【請求項34】

前記位相同期ループの前記チャージポンプは、

前記出力信号に第1の電流を供給するように構成された第1の電流ソースと；

前記出力信号に第2の電流を供給するように構成された第2の電流ソースと、なお、前記第1および第2の電流は逆極性を有している；

前記第1の信号によってイネーブルにされたとき、前記第1の電流ソースを前記出力信号に結合するように構成された第1のスイッチと；

前記第2の信号によってイネーブルにされたとき、前記第2の電流ソースを前記出力信号に結合するように構成された第2のスイッチと；

を備える、

請求項27に記載の無線デバイス。

【請求項35】

前記予め定められた量の遅れはプログラム可能である、請求項27に記載の無線デバイス。

【発明の詳細な説明】

【背景】

【0001】

[I. 分野]

本開示は概して回路に関し、より具体的には、位相同期ループ(phase-locked loop)に関係する。

【0002】

[II. 背景]

位相同期ループ(PLL)は、多くのエレクトロニクス回路において一般に使用されており、そして、通信回路においては、特に重要である。例えば、デジタルシステムは、同期回路、例えばフリップフロップ、をトリガする(trigger)ためにクロック信号を使用する。送信器システムおよび受信器は、周波数アップコンバージョン(frequency upconversion)

10

20

30

40

50

ion) およびダウンコンバージョン(downconversion)のために局部発振器(local oscillator) (L O) 信号をそれぞれ使用する。無線通信システムにおける無線デバイス(wireless devices) (例えば携帯電話) は、典型的に、デジタル回路のためにクロック信号を、送信器および受信器の回路のために L O 信号に使用する。クロック信号と L O 信号は、PLL 内で動作する電圧制御発振器(voltage-controlled oscillators) (VCO) を用いて、多くの場合生成される。

#### 【0003】

PLL は、典型的に、位相周波数検出器(phase frequency detector)、チャージポンプ(charge pump)、ループフィルタ(loop filter)、および VCO、を含んでいる。位相周波数検出器、チャージポンプ、ループフィルタは、共同して、基準信号(reference signal) と VCO から導き出されるクロック信号との間の位相誤差(phase error)を検出し、VCO のための制御信号を生成する。クロック信号が基準信号にロックされる(locked)ように、制御信号は VCO の周波数を調整する。

#### 【0004】

位相周波数検出器は、典型的に、up 信号および down 信号(up and down signals) と一般に呼ばれる一対の信号を生成する。一方の信号は、クロック信号が基準信号に対して早いのか、あるいは遅いのかに応じて、各クロックサイクルにおいて典型的により長くなる(turn on longer)。up 信号および down 信号は、チャージポンプ内の電流ソースをアウトプット(output)に結合するために使用される。理想的には、位相周波数検出器およびチャージポンプは、出力チャージ対位相誤差(output charge versus phase error)の線形の伝達関数(linear transfer function)を有する。しかしながら、チャージポンプに使用された回路のミスマッチ(mismatch)により、この線形の伝達関数は典型的には達成されない。従って、同じ大きさであるが逆極性の位相誤差のために、up 信号からの出力チャージ(output charge)は、down 信号からの出力チャージ(output charge)とは、多くの場合等しくない。このチャージエラー(charge error)は、チャージポンプにおける up / down 電流ミスマッチ(up/down current mismatch)に起因するものであり、それは、トランジスタデバイスマスマッチ(transistor device mismatch)および他の要因で起こり得る。電流ミスマッチによるチャージポンプの非線形性は、性能を下げるさらなる位相ノイズを生じさせるかもしれない。

#### 【0005】

したがって、当技術分野においては、PLL についての良い性能を供給することができる位相周波数検出器およびチャージポンプに対しての必要性がある。

#### 【発明の概要】

#### 【0006】

PLL における位相周波数検出器およびチャージポンプのための線形動作(linear operation)を達成するための技術が、ここに説明される。一態様においては、位相周波数検出器は、チャージポンプにおける up / down 電流ミスマッチが、一次の非直線歪み(non-linear distortion in the first order)に寄与しないように、up 信号および down 信号を生成する新しいタイミング/クロッキングスキームを使用する。新しいタイミングスキームは、位相周波数検出器内のフリップフロップをリセットするために、up 信号をのみ、あるいは、down 信号のみ、を使用する。新しいタイミングスキームを用いることで、チャージポンプにおける up / down 電流ミスマッチは、チャージポンプのアウトプットに現われない。従って、トランジスタデバイスマスマッチが存在する状態さえ、良い性能が達成されることができる。

#### 【0007】

1つの設計においては、PLL は位相周波数検出器およびチャージポンプを含んでいる。位相周波数検出器は、基準信号とクロック信号を受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、そして、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、up 信号および down 信号であってもよい。あるいは、第1および第2の信号は、それぞれ、down 信号

10

20

30

40

50

およびup信号であってもよい。位相周波数検出器は、予め定められた量だけ(by a predetermined amount)、第1の信号を遅らせ、遅れた第1の信号(the delayed first signal)および第2の信号に基づいて、リセット信号を生成し、リセット信号で第1および第2の信号をリセットする。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。位相周波数検出器およびチャージポンプは、下記に説明されるようにインプリメントされる(implemented)ことができる。

#### 【0008】

本開示の種々な態様および特徴が、さらに詳細に下記に説明される。

#### 【図面の簡単な説明】

10

#### 【0009】

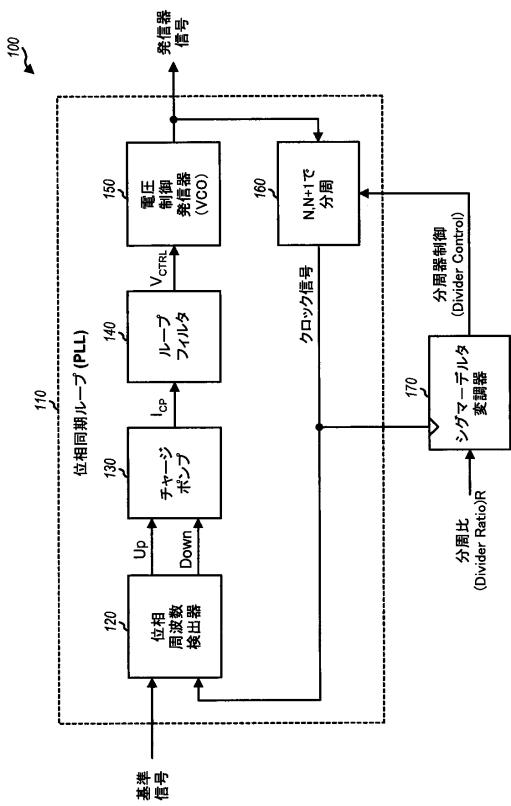

【図1】図1は、フラクショナルNPLL(fractional-N PLL)のブロック図を示す。

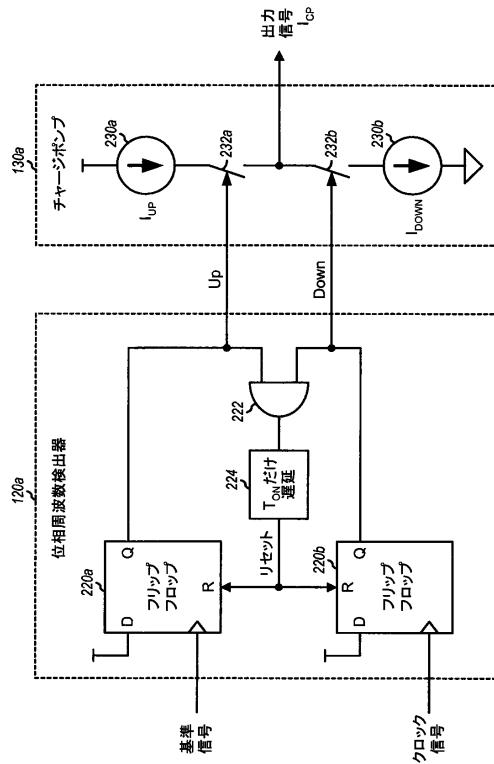

【図2】図2は、PLLのための位相周波数検出器およびチャージポンプを示す。

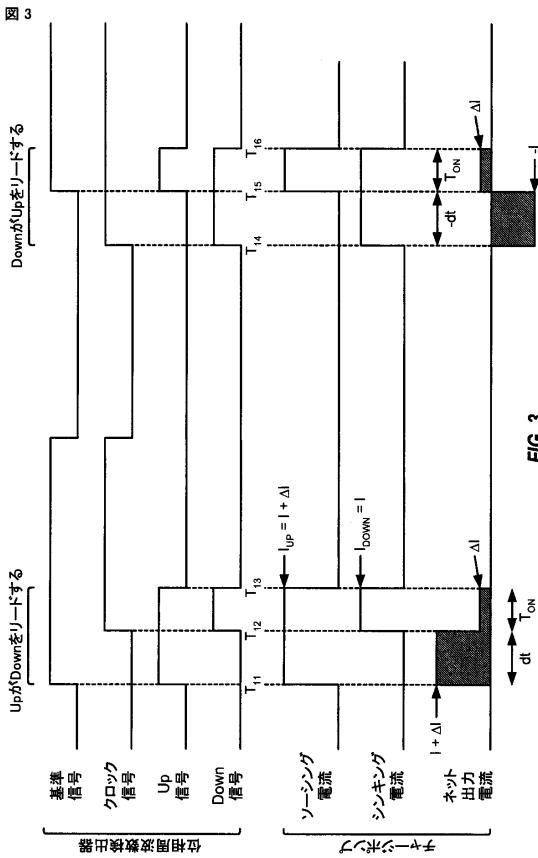

【図3】図3は、図2における位相周波数検出器のタイミング図を示す。

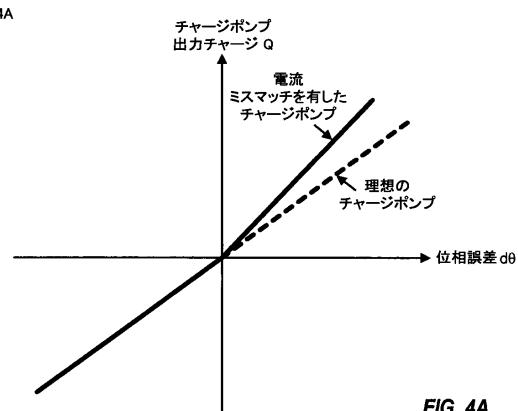

【図4A】図4Aは、図2におけるチャージポンプの電荷移動関数(charge transfer function)を示す。

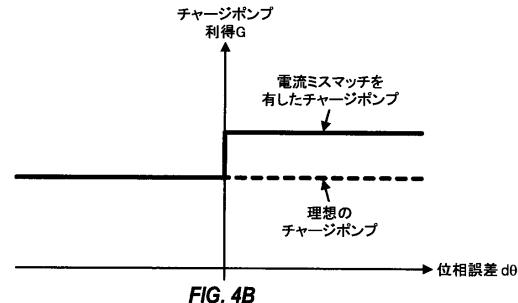

【図4B】図4Bは、図2におけるチャージポンプの利得関数(gain function)を示す。

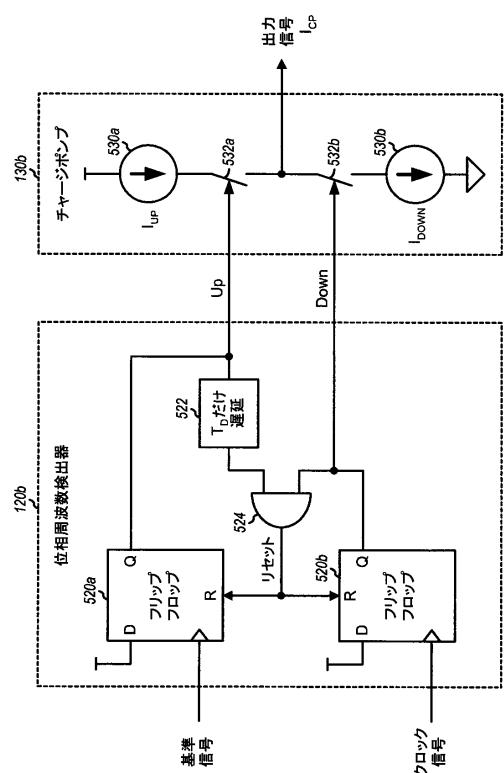

【図5A】図5Aは、線形位相周波数検出器(linear phase frequency detector)およびチャージポンプ(charge pump)を示す。

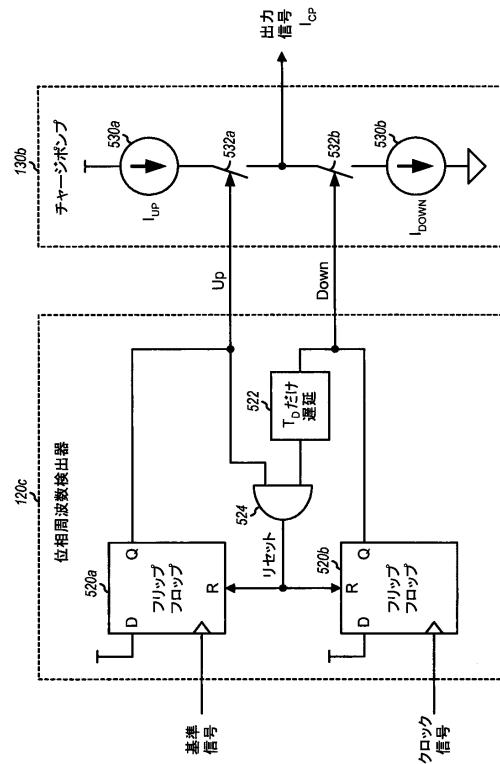

【図5B】図5Bは、別の線形位相周波数検出器およびチャージポンプを示す。

20

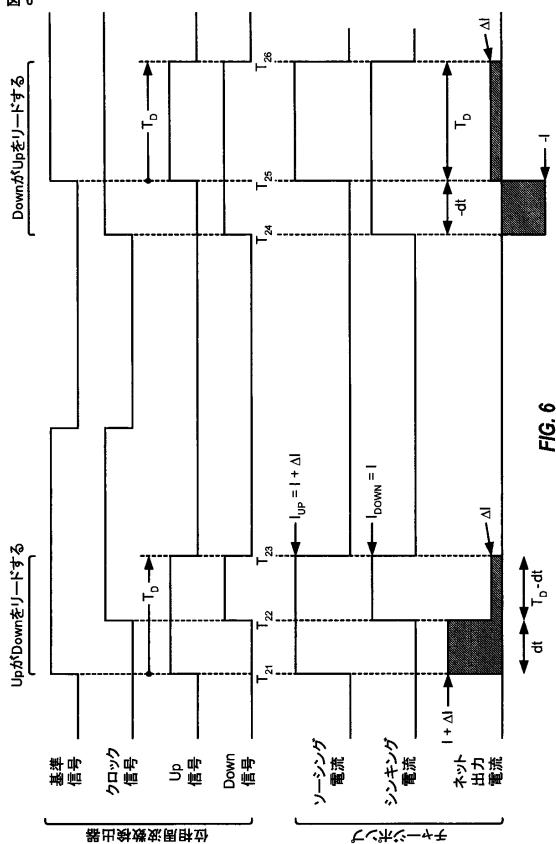

【図6】図6は、図5Aにおける位相周波数検出器用のタイミング図を示す。

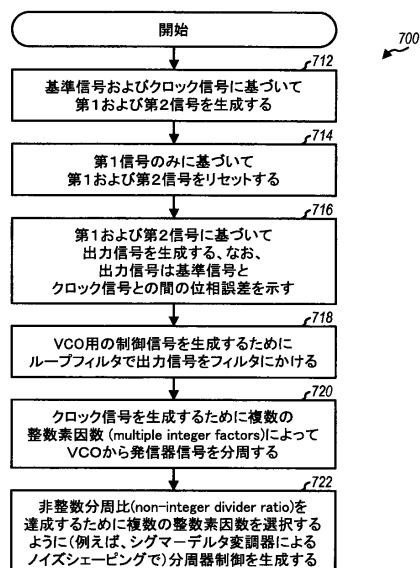

【図7】図7は、PLLを動作させるプロセスを示す。

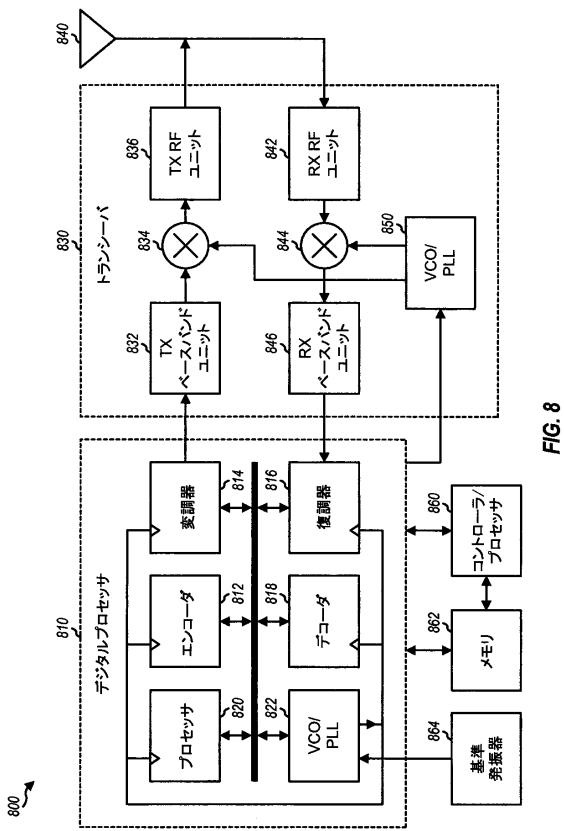

【図8】図8は、無線通信デバイスのブロック図を示す。

#### 【詳細な説明】

#### 【0010】

ここに説明される技術は、整数NPLL(integer-N PLLs)、フラクショナルNPLL(fractional-N PLLs)、マルチモジュラス分周器(multi-modulus dividers)(MMD)、シグマデルタ周波数シンセサイザ(sigma-delta frequency synthesizers sigma-delta frequency synthesizers)などの様々な様々なタイプの回路に使用されることができる。整数NPLLは、VCOからの発振器信号(oscillator signal)の周波数を、整数分周比N(integer divider ratio N)で、分周する(divides)、なお、この場合、N=1。フラクショナルNPLLは、発振器信号の周波数を、非整数分周比R(non-integer divider ratio R)で、例えば、あるときはNで、また、他のときはN+1で(by N some of the time and by N+1 some other time)、分周する、なお、この場合、N < R < N+1。シグマデルタ周波数シンセサイザは、フラクショナルNPLLの非整数分周比Rを生成するために、シグマ-デルタ変調器(sigma-delta modulator)を利用する。

30

#### 【0011】

図1は、フラクショナルNPLL110およびシグマ-デルタ変調器170を備えたシグマデルタ周波数シンセサイザ100の設計のブロック図を示す。PLL110は、位相周波数検出器120、チャージポンプ130、ループフィルタ(loop filter)140、電圧制御発振器(voltage-controlled oscillator)(VCO)150および分周器160を含んでいる。

40

#### 【0012】

位相周波数検出器120は、基準発振器(図1においては示されない)から基準信号を受け取り、分周器160からクロック信号を受け取り、2つの信号の位相を比較し、基準信号とクロック信号との間の位相誤差/相違(phase error/difference)を示すup信号およびdown信号を供給する。クロック信号はまた、分割されたクロック信号(divided clock signal)、フィードバック信号などと呼ばれてもよい。up信号およびdown信号はまた、early信号およびlate信号(early and late signals)、advance信号およびretard信号(advance and retard signals)などと、一般に呼ばれる。チ

50

チャージポンプ 130 は、up 信号およびdown 信号を受け取り、検出された位相誤差を示す電流  $I_{CP}$  である出力信号を生成する。

【0013】

ループフィルタ 140 は、チャージポンプ 130 からの出力信号をフィルタにかけ(filters)、VCO 150 のための制御信号  $V_{CTRL}$  を生成する。ループフィルタ 140 は、クロック信号の位相あるいは周波数が基準信号の位相あるいは周波数にロックされる(locked)ように、制御信号を調整する。ループフィルタ 140 は、PLL 110 の望ましい閉ループ応答(desired closed-loop response)を達成するために典型的に選択されている周波数応答(frequency response)を有している。例えば、ループフィルタ 140 の周波数応答は、獲得およびトラッキング性能(acquisition and tracking performance)と PLL ノイズ性能(PLL noise performance)との間のトレードオフに基づいて選択されることが可能である。

【0014】

VCO 150 は、ループフィルタ 140 からの制御信号によって決定される周波数を有している発振器信号を、生成する。分周器 160 は、N と N + 1 の整数素因数(integer factors of N and N+1)によって発振器信号を分周し、クロック信号を供給する。一般に、N は任意の正の整数値であってよい。シグマ - デルタ変調器 170 は分周比 R を受け取る、なお、R は次のように表されることができる：

【数1】

$$R = \frac{f_{vco}}{f_{ref}} \quad \text{式 (1)}$$

10

20

但し、 $f_{vco}$  は VCO 150 の望ましい周波数であり、

$f_{ref}$  は基準信号の周波数である。

シグマ - デルタ変調器 170 は、分周比 R を達成するために分周器 160 のための分周器制御を生成する。この分周器制御は、分周器 160 に N か N + 1 のいずれかによって分周するように命じる 1 ビットの制御(1-bit control)であってもよい。例えば、分周器制御上の論理 low(logic low) (「0」) は、N による分周に対応することができ、また、分周器制御上の論理 high(logic high) (「1」) は、N + 1 による分周に対応することができる。分周器制御上のゼロ(zeros)および 1 (ones) のパーセンテージは、分周比 R によって決定される。しかしながら、量子化雑音がより高い周波数へシフトされ、VCO 150 からの発振器信号について良好な位相ノイズ特性が達成される能够な方法で、ゼロは、分周器制御上で分布される。

30

【0015】

図 1 は、PLL および周波数シンセサイザの一例の設計を示す。一般に、PLL および周波数シンセサイザは、図 1 において示されるものよりは、より少ない回路ブロック、追加の回路ブロック、および / または、異なる回路ブロックで、インプリメントすることができる。例えば、VCO 150 は、電流デジタル / アナログ変換器 (iD/A) および電流制御発振器 (ICO) に取り替えられてもよい。分周器 160 は、固定整数 N 分周器 (fixed integer-N divider) であってもよい。ループフィルタ 140 は、変数ループ応答を有する適応ループフィルタであってもよく、それは、PLL ループ帯域幅および / またはダンピング(damping)を変更するために使用することができる。他の関心ある周波数(other frequencies of interest)で 1 つ以上のさらなるクロック信号を生成するために発振器信号を分周するのに、1 つ以上のさらなる分周器もまた使用することができる。

40

【0016】

図 2 は、位相周波数検出器 120a およびチャージポンプ 130a の一設計を示しており、それらは、それぞれ、図 1 における、位相周波数検出器 120 およびチャージポンプ 130 に使用されることができる。

50

## 【0017】

位相周波数検出器 120a 内では、基準信号とクロック信号とが、それぞれ、D フリップフロップ 220a および 220b のクロックインプットに、供給される。フリップフロップ 220a および 220b のデータ (D) インプットは、電源に結合され、論理  $h_{ig}$   $h$  を受け取る。フリップフロップ 220a および 220b のデータ (Q) アウトプットは、それぞれ、up 信号および down 信号 (up and down signals) を供給する。up 信号 (up signal) は、クロック信号に対して早い基準信号 (the reference signal being early with respect to the clock signal) を示す (indicative of)。down 信号 (down signal) は、クロック信号に対して遅い基準信号 (the reference signal being late with respect to the clock signal) を示す。AND ゲート 222 は、up 信号および down 信号を受け取り、2つの信号に関して論理 AND (logical AND) を行なう。遅延ユニット 224 は、AND ゲート 222 のアウトプットを、予め定められた量の時間  $T_{ON}$  だけ遅らせ、フリップフロップ 220a および 220b のリセット (R) インプットにリセット信号を供給する。

10

## 【0018】

チャージポンプ 130a 内では、電流ソース 230a および 230b とスイッチ 232a および 232b とが、電源と回路グラウンドとの間で、直列に結合される。電流ソース 230a は、 $I_{UP}$  の電流を供給し、電流ソース 230b は、 $I_{DOWN}$  の電流を供給する。スイッチ 232a は、up 信号を受け取り、up 信号上の論理  $h_{ig}$   $h$  によって on となるとき (when turned on)、電流ソース 230a をチャージポンプ 130a のアウトプットに結合する。スイッチ 232b は、down 信号を受け取り、down 信号上で論理  $h_{ig}$   $h$  によって on となるとき、電流ソース 230b をチャージポンプ 130a のアウトプットに結合する。

20

## 【0019】

ユニット 224 による  $T_{ON}$  遅延は、チャージポンプ中のデッドゾーン (dead zone) を抑制する (combat) ために使用される。電流ソース 230a および 230b は、on および off とするために、ある量の時間を必要とする。遷移時間 (transition time) の間、up 信号および down 信号においての位相情報が失われる所以、この遷移時間は、デッドゾーンと呼ばれる。 $T_{ON}$  遅延はデッドゾーンを抑制する。

30

## 【0020】

図 3 は、図 2 における位相周波数検出器 120a の動作を説明するタイミング図を示す。最初、up 信号および down 信号は、論理 low にある。時間  $T_{1,1}$  で、基準信号は、論理 low から論理  $h_{ig}$   $h$  へ遷移し、フリップフロップ 220a がトリガされ (triggered)、そして、up 信号が論理  $h_{ig}$   $h$  へ遷移する。時間  $T_{1,2}$  で、クロック信号が、論理 low から論理  $h_{ig}$   $h$  へ遷移し、フリップフロップ 220b がトリガされ、そして down 信号が論理  $h_{ig}$   $h$  へ遷移する。up 信号および down 信号が両方とも論理  $h_{ig}$   $h$  にあるとき、AND ゲート 222 のアウトプットは、論理  $h_{ig}$   $h$  へ遷移する。 $T_{1,2}$  よりほぼ  $T_{ON}$  遅延時間  $T_{1,3}$  で、リセット信号は、論理  $h_{ig}$   $h$  へ遷移し、フリップフロップ 220a および 220b は、両方ともリセットされ、そして、up 信号および down 信号は、論理 low へ遷移する。

40

## 【0021】

時間  $T_{1,4}$  で、クロック信号は、論理 low から論理  $h_{ig}$   $h$  へ遷移し、フリップフロップ 220b がトリガされ、そして、down 信号が論理  $h_{ig}$   $h$  へ遷移する。時間  $T_{1,5}$  で、基準信号が、論理 low から論理  $h_{ig}$   $h$  へ遷移し、フリップフロップ 220a がトリガされ、そして、up 信号が論理  $h_{ig}$   $h$  へ遷移する。up 信号および down 信号が、両方とも論理  $h_{ig}$   $h$  にあるとき、AND ゲート 222 のアウトプットは、論理  $h_{ig}$   $h$  へ遷移する。 $T_{1,5}$  よりほぼ  $T_{ON}$  遅延時間  $T_{1,6}$  で、リセット信号は、論理  $h_{ig}$   $h$  へ遷移し、フリップフロップ 220a および 220b は、両方ともリセットされ、そして、up 信号および down 信号は、論理 low へ遷移する。

50

## 【0022】

図3において示されるように、各クロックサイクルにおいて、*u p*信号および*d o w n*信号上で、2つのパルスが生成される。基準信号がクロック信号に対して早いとき、*u p*信号が、*d o w n*信号をリードし(leads)、より長いパルスを有する。反対に、基準信号がクロック信号に対して遅いとき、*d o w n*信号が、*u p*信号をリードし、より長いパルスを有する。各クロックサイクルにおいて、より早い立ち上がりエッジ(earlier rising edge)を備えた信号が、そのフリップフロップを最初にセットする(sets)。そして、より遅い立ち上がりエッジ(later rising edge)を備えた信号が、両方のフリップフロップをリセットする。このようにして、基準信号は、それがクロック信号より早いとき、両方のフリップフロップをリセットし、そして、クロック信号は、それが基準信号より遅いとき、両方のフリップフロップをリセットする。

10

## 【0023】

図3はまた、図2の中のチャージポンプ130aの動作を説明する。*u p*信号が*d o w n*信号をリードするとき、電流ソース230aは、時間T<sub>11</sub>から時間T<sub>13</sub>のI<sub>u p</sub>のソーシング電流(sourcing current)を供給し、そして、電流ソース230bは、時間T<sub>12</sub>から時間T<sub>13</sub>のI<sub>d o w n</sub>のシンキング電流(sinking current)を供給する。ネット出力電流(net output current)は、時間T<sub>11</sub>から時間T<sub>13</sub>のソーシング電流とシンキング電流との間の差である。

## 【0024】

*d o w n*信号が*u p*信号をリードするとき、電流ソース230bは、時間T<sub>14</sub>から時間T<sub>16</sub>のI<sub>d o w n</sub>のシンキング電流を供給し、そして、電流ソース230aは、時間T<sub>15</sub>から時間T<sub>16</sub>のI<sub>u p</sub>のソーシング電流を供給する。ネット出力電流は、時間T<sub>14</sub>から時間T<sub>16</sub>のソーシング電流とシンキング電流との間の差である。

20

## 【0025】

理想的には、電流ソース230aおよび230bは、I<sub>u p</sub> = I<sub>d o w n</sub>であるように同じ量の電流を供給するべきである。しかしながら、トランジスタデバイスマッチおよび他の要因により、I<sub>u p</sub>は、典型的に、I<sub>d o w n</sub>と等しくない。I<sub>u p</sub>とI<sub>d o w n</sub>の間のミスマッチは、I<sub>d o w n</sub> = I、I<sub>u p</sub> = I + Iとしてモデル化される(model ed)ことができる、ただし、Iは名目上の電流(nominal current)であり、Iは電流ミスマッチの量である。

## 【0026】

30

*u p*信号が*d o w n*信号をリードするとき、例えば、時間T<sub>11</sub>から時間T<sub>13</sub>まで、チャージポンプ130aからのネット出力チャージ(net output charge)は、次のように表されることができる。

$$Q(d t) = I * d t + I * d t + I * T_{o N} \quad \text{式 (2)}$$

但し、d tは、基準信号の立ち上がりエッジとクロック信号の立ち上がりエッジとの間の時間差であり、

Q(d t)は、*u p*信号が*d o w n*信号をリードする場合の出力チャージである。

## 【0027】

*d o w n*信号が*u p*信号をリードするとき、例えば、時間T<sub>14</sub>から時間T<sub>16</sub>まで、チャージポンプ130aからのネット出力チャージは次のように表されることができる。

40

$$Q(-d t) = -I * d t + I * T_{o N} \quad \text{式 (3)}$$

但し、d tは基準信号の立ち上がりエッジとクロック信号の立ち上がりエッジとの間の時間差であり、

Q(-d t)は、*d o w n*信号が*u p*信号をリードする場合のネットチャージである。

## 【0028】

式(2)および(3)において、「I \* d t」および「-I \* d t」の項は望ましい成分(desired component)に対応し、「I \* d t」の項は、非直線歪み成分(non-linear distortion component)に対応し、「I \* T<sub>o N</sub>」の項は、直流(DC)オフセットに対

50

応する。DCオフセットは、基準信号とクロック信号との間のスタティック位相オフセットの原因となり、一般には性能に影響を与えない(does not impact performance)。しかしながら、非線形の成分は、位相ノイズを劣化させ、他の悪影響(other deleterious effects)を生じさせうる。

【0029】

図4Aは、チャージポンプ130aからの出力チャージQ 対 位相誤差d の伝達関数(transfer function)を示す。位相誤差と時間差は関連づけられ、次のように与えられることができる:  $d = 2 * d t / T_{REF}$  但し、 $T_{REF}$  は基準信号の1サイクルの期間である。理想的には、伝達関数は、電流Iによって決定された傾斜(slope)を持った直線であるべきである。しかしながら、電流ミスマッチ I により、伝達関数は、負の位相誤差の場合の1つの直線および正の位相誤差の場合の別の直線からなる。正の位相誤差の場合の直線は、図3および4Aにおいて示されるように、もし  $I_{UP} > I_{DOWN}$  ならば、より急な傾斜を有する。

【0030】

図4Bは、チャージポンプ130a 対 位相誤差d の利得関数(gain function)を示す。チャージポンプ利得Gは、 $G = d Q / d$  として与えられることができる。理想的には、チャージポンプ利得は、すべての位相誤差に対して一定であるべきである。しかしながら、電流ミスマッチ I により、チャージポンプ利得は、負の位相誤差の場合は1つの値であり、正の位相誤差の場合は別の値である。正の位相誤差の場合のチャージポンプ利得は、図3および4Bにおいて示されるように、もし  $I_{UP} > I_{DOWN}$  ならば、より高い。

【0031】

電流ミスマッチ I は、電流ソース230aおよび230bをインプリメントするために使用されるトランジスタデバイスにおけるミスマッチ、チャージポンプの電源電圧における変化、および他の要因に起因し得る。デバイスマミスマッチは、大きなデバイスサイズを使用すること、および良い設計ガイドラインを使用することにより軽減されるかもしれない。しかしながら、大きなデバイスサイズは、より多くの回路エリアを占め、それは望ましくない。更に、デバイスマミスマッチは、大きなデバイスサイズを用いてさえ、完全には除去されない。従って、チャージポンプが、なんらかの電流ミスマッチを持つと予想されることができる。

【0032】

一態様では、チャージポンプにおけるup / down電流ミスマッチが一次の非直線歪みに寄与しないように、位相周波数検出器は、up信号およびdown信号を生成する新しいタイミング/クロッキングスキームを使用する。新しいタイミングスキームは、位相周波数検出器内でフリップフロップをリセットするために、up信号のみ、あるいはdown信号のみを使用する。これは、図2において示されるup信号およびdown信号が両方ともフリップフロップをリセットするタイミングスキームとは、異なる。新しいタイミングスキームを用いると、チャージポンプにおけるup / down電流ミスマッチは、チャージポンプのアウトプットで現われない。従って、良い性能が、チャージポンプにおいてトランジスタデバイスマミスマッチが存在する状態でさえ達成されることがある。

【0033】

図5Aは、位相周波数検出器120bおよびチャージポンプ130bの設計を示しており、それらは、それぞれ、図1における位相周波数検出器120およびチャージポンプ130に使用されることができる。位相周波数検出器120bは、単にup信号に基づいて、そのフリップフロップをリセットする。

【0034】

位相周波数検出器120b内では、基準信号とクロック信号が、Dフリップフロップ520aおよび520bのクロックインプットにそれぞれ供給される。フリップフロップ520aおよび520bのDインプットは、電源に結合される。フリップフロップ520aおよび520bのQアウトプットは、up信号およびdown信号をそれぞれ供給する。

10

20

30

40

50

遅延ユニット 522 は、*u p* 信号を予め定められた量の時間  $T_D$  だけ遅らせる。AND ゲート 524 は、遅れた *u p* 信号(*delayed up signal*)と *d own* 信号とを受け取り、2つの信号に関して論理 AND を行ない、フリップフロップ 520a および 520b の R インプットにリセット信号を供給する。

【0035】

チャージポンプ 130b は、電流ソース 530a および 530b と、スイッチ 532a および 532b とを含み、それらは、電源と回路グラウンドとの間で直列に結合される。スイッチ 532a は、*u p* 信号を受け取り、電流ソース 530a をチャージポンプアウトプットに結合する。スイッチ 532b は、*d own* 信号を受け取り、電流ソース 530b をチャージポンプアウトプットに結合する。

10

【0036】

図 5B は、位相周波数検出器 120c の設計を示し、それらはまた、図 1 における位相周波数検出器 120 に使用されることができる。位相周波数検出器 120c は、単に *d own* 信号に基づいて、そのフリップフロップをリセットする。位相周波数検出器 120c は、フリップフロップ 520a および 520b と、遅延ユニット 522 と、AND ゲート 524 とを含んでいる。しかしながら、図 5A とは違って、遅延ユニット 522 は、*d own* 信号を、予め定められた量の時間  $T_D$  だけ遅らせる。AND ゲート 524 は、遅れた *d own* 信号(*delayed down signal*)と *u p* 信号とを受け取り、リセット信号をフリップフロップ 520a および 520b に供給する。

【0037】

図 5A および 5B において示されるように、位相周波数検出器の新しいタイミングスキームは、小さな回路構成を用いてインプリメントされることができる。他の回路もまた、*u p* 信号のみ、あるいは *d own* 信号のみに基づいて、フリップフロップをリセットするように設計されることができる。

20

【0038】

図 6 は、図 5A の中の位相周波数検出器 120b の動作を説明するタイミング図を示す。最初に、*u p* 信号および *d own* 信号は、論理 *low* にある。時間  $T_{2,1}$  で、基準信号は論理 *high* へ遷移し、フリップフロップ 520a がトリガされ、そして、*u p* 信号が、論理 *high* へ遷移する。時間  $T_{2,2}$  で、クロック信号は論理 *high* へ遷移し、フリップフロップ 520b がトリガされ、そして、*d own* 信号が、論理 *high* へ遷移する。 $T_{2,1}$  よりほぼ  $T_D$  遅い時間  $T_{2,3}$  で、遅れた *u p* 信号と *d own* 信号とは、AND ゲート 522 のインプットにおいて、両方とも論理 *high* にあり、そして、AND ゲート 522 は論理 *high* をリセット信号上に供給する。フリップフロップ 520a および 520b は、その結果、両方ともリセットされ、そして、*u p* 信号および *d own* 信号は、論理 *low* へ遷移する。

30

【0039】

時間  $T_{2,4}$  で、クロック信号は論理 *high* へ遷移し、フリップフロップ 520b がトリガされ、そして、*d own* 信号は、論理 *high* へ遷移する。時間  $T_{2,5}$  で、基準信号は論理 *high* へ遷移すし、フリップフロップ 520a がトリガされ、そして、*u p* 信号が論理 *high* へ遷移する。 $T_{2,5}$  よりほぼ  $T_D$  遅い時間  $T_{2,6}$  で、遅れた *u p* 信号と *d own* 信号とは、AND ゲート 522 のインプットで、両方とも論理 *high* にあり、そして、AND ゲート 522 は、リセット信号上に論理 *high* を供給する。フリップフロップ 520a および 520b は、その結果、両方ともリセットされ、そして *u p* 信号および *d own* 信号は、論理 *low* へ遷移する。

40

【0040】

図 6 において示されるように、基準信号あるいはクロック信号がより早いかどうかにかかわらず、*u p* 信号のみが、フリップフロップをリセットする。各クロックサイクルにおいて、より早い立ち上がりエッジを備えた信号が、そのフリップフロップを最初にセットし、そして、*u p* 信号が両方のフリップフロップをリセットする。

【0041】

50

図6はまた、図5Aの中のチャージポンプ130bの動作を説明する。up信号がdown信号をリードするとき、例えば、時間T<sub>21</sub>から時間T<sub>23</sub>まで、チャージポンプ130bからの出力チャージは、次のように表されることができる：

$$\begin{aligned} Q(d_t) &= I^* d_t + I^* d_t + I^* (T_D - d_t) \\ &= I^* d_t + I^* T_D \end{aligned} \quad \text{式(4)}$$

down信号がup信号をリードするとき、例えば、時間T<sub>24</sub>から時間T<sub>26</sub>まで、チャージポンプ130bからの出力チャージは、次のように表されることができる：

$$Q(-d_t) = I^* d_t + I^* T_D \quad \text{式(5)}$$

式(2)および(3)において、「 $I^* d_t$ 」および「 $-I^* d_t$ 」の項は望ましい成分に対応し、そして、「 $I^* T_D$ 」の項はDCオフセットに対応する。その、電流ソース530aおよび530bにおけるup/down電流ミスマッチは、チャージポンプ130bのアウトプットにおいては現われない。非線形成分は、up信号の立ち上がりエッジの後に固定の遅れ $T_D$ を導入することにより取り消される(canceled)。非線形成分の取り消し(cancellation)は、(a)図4Aにおいて示される、理想的な伝達関数に似ている出力チャージQ対位相誤差dの伝達関数、および(b)図4Bにおいて示される理想的な利得関数に似ているチャージポンプ利得、をもたらす。

#### 【0042】

固定の遅れ $T_D$ は以下のように選択されることができる：

$$T_D > T_{ON} + d_{t_{MAX}} \quad \text{式(6)}$$

但し、 $T_{ON}$ は、チャージポンプのデッドゾーンを説明するために使用されるon時間であり(on time used to account for the dead zone of the charge pump)、

$d_{t_{MAX}}$ は、PLLがロックされる(locked)ときの、基準信号とクロック信号の立ち上がりエッジ間の予期される最大時間差である。

#### 【0043】

PLLがロックされるとき、位相周波数検出器およびチャージポンプによる線形動作が、典型的には、もっぱら必要とされる(only needed)。位相ノイズ、スブリアス信号レベル(spurious signal levels)および他の仕様(other specifications)は、ロックされたPLLに対して通常適用可能である。PLLがロックされるとき、位相周波数検出器のインプットでは、基準信号とクロック信号との間に時間/位相差の範囲がある。時間/位相差のこの範囲は、様々な要因、例えば、分周器160に使用される因数N、N+1、デルタ-シグマ変調器170分周器制御(それはデルタ-シグマ変調器のトポロジあるいは設計に依存し得る)など、に依存し得る。時間/位相差の範囲は、コンピュータシミュレーション、経験に基づく測定(empirical measurements)などによって決定されることができる。例えば、時間/位相差のヒストグラム(histogram)は、特定のPLLおよびデルタ-シグマ変調器の設計については、周波数ロック中の多くのクロックサイクルの間に得られるかもしれない。そのとき、 $d_{t_{MAX}}$ が、ヒストグラムに基づいて選択されることができ、例えば、クロックサイクルのターゲット割合(例えば99%)をカバーする時間/位相差に等しくセットされる。

#### 【0044】

例えば、式(6)において示されるような、十分に長い固定の遅れ $T_D$ を選択することは、すべてのインプット状態に対し(for all input conditions)、チャージポンプ内の電流ソースが十分にonになる(turned on)ことを確かなものとする。これはまた、PLLがロックされるとき、フリップフロップをリセットするように指定された信号(例えば図5Aの中のup信号)がT<sub>1</sub>の遅れの後にフリップフロップを実際にリセットするであろうということを確実にする。固定の遅れはまた、プログラム可能な値であることができる。

#### 【0045】

PLLがロックされないとき、時間/位相差 $d_t$ は、 $d_{t_{MAX}}$ より大きいかもしれない。up信号がdown信号をリードする(leads)とき、down信号の立ち上がりエッジ

10

20

30

40

50

ジが、 $T_{DN}$ の後に、フリップフロップをリセットする。 $down$ 信号が $up$ 信号をリードするとき、 $up$ 信号の立ち上がりエッジが、 $T_D$ の後に、フリップフロップをリセットする。位相周波数検出器およびチャージポンプは、PLLがロックされないときは、やはり適切に機能するが、線形化されていない(not linearized)、が、これは、通常受け入れることができる動作(behavior)である。

#### 【0046】

一般に、PLLは、基準信号とクロック信号とを受け取り、基準とクロック信号とに基づいて第1および第2の信号を生成し、そして、第1の信号のみに基づいて第1および第2の信号をリセットする位相周波数検出器、を含み得る。第1および第2の信号は、 $up$ 信号および $down$ 信号にそれぞれ対応することができ、また、例えば、図5Aにおいて示されるように、基準信号とクロック信号と基づいてそれぞれ生成されることがある。あるいは、第1および第2の信号は、 $down$ 信号および $up$ 信号にそれぞれ対応することができ、また、例えば、図5Bにおいて示されるように、クロック信号と基準信号とに基づいて、それぞれ生成されることがある。位相周波数検出器は、第1の信号を予め定められた量だけ遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、そして、リセット信号に基づいて、第1および第2の信号をリセットすることができる。予め定められた量の遅れは、例えば、式(6)において示されるように、選択されてもよいし、あるいはプログラム可能であってもよい。

#### 【0047】

チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。チャージポンプは、第1の信号に基づいて第1の電流を出力信号に供給することができ、第2の信号に基づいて第2の電流を出力信号に供給することができる、なお、第1の電流および第2の電流は逆の極性を有する。位相周波数検出器およびチャージポンプは、図5Aまたは5Bに示されるように、あるいはなんらかの他の設計で、インプリメントされることがある。

#### 【0048】

図7は、PLLを動作させるプロセス700を示す。第1および第2の信号は、基準信号およびクロック信号に基づいて生成される(ブロック712)。第1および第2の信号は、第1の信号のみに基づいてリセットされる(ブロック714)。基準信号とクロック信号との間の位相誤差を示す出力信号は、第1および第2の信号に基づいて生成される(ブロック716)。出力信号は、VCOのための制御信号を生成するために、ループフィルタでフィルタにかけられる(ブロック718)。VCOからの発振器信号は、クロック信号を生成するために、複数の整数素因数(multiple integer factors)(例えばNとN+1)で分周することができる(ブロック720)。非整数分周比(non-integer divider ratio)を達成するために、分周器制御(divider control)が、複数の整数素因数を選択するために(例えば、シグマ-デルタ変調器によってノイズシェーピングを用いて)生成される(ブロック722)。

#### 【0049】

ここに説明される線形位相周波数検出器およびチャージポンプは、上記に示されたように、様々なタイプのPLLに使用されてもよく、また、特に、信号-デルタ フラクショナルNPLL(signal-delta fractional-N PLLs)の場合には好都合である。信号-デルタ フラクショナルNPLLは、ループフィルタ140によってより容易にフィルタにかけられることができるより高い周波数へ量子化雑音(quantization noise)を押しあげる(push)ために、信号-デルタ変調器によるノイズシェーピングを使用する。チャージポンプ中の非線形は、より高い周波数ノイズをより低い周波数へ折り返す(fold back)原因となり、性能を低下させるかもしれない。上記に説明されるようなチャージポンプを線形化することは、ノイズフォールディング効果(noise folding effects)を低減させる。チャージポンプを線形化することは、また、非線形のミキシングおよび相互変調(non-linear mixing and inter-modulation)から生成されるフラクショナルスパー(fractional spurs)あるいは異質のトーン(extraneous tones)を低減させ得る。

10

20

30

40

50

## 【0050】

ここに説明される線形位相周波数検出器およびチャージポンプは、様々な利点を提供することができる。線形動作は、チャージポンプ中における電流ソースの有限出力インピーダンス(finite output impedance)およびトランジスタデバイスおよびにおけるミスマッチがある状態でさえ達成されることがある。したがって、電流ソースの電流整合要件(current matching requirements)は緩められる(relaxed)ことができ、チャージポンプの電圧適合要件(voltage compliance requirements)は改善されることができ、また、より小さなトランジスタのサイズがチャージポンプに使用されることがある。さらに、至近距離の位相ノイズ(close-in phase noise)が改善されることができ、フラクショナルスプリアス信号レベル(fractional spurious signal level)が下げられることができ、そして、全体的なPLL性能は改善されることができる。トランジスタデバイスミスマッチは、次に(now)、基準スパー(reference spurs)のみは引き起こすかもしれないが、それは、適切に設計されたフラクショナルNPLLにおけるノイズレベルよりも下に抑えられることがある。

10

## 【0051】

ここに説明された線形位相周波数検出器およびチャージポンプは、様々なエレクトロニクス回路に使用されることがある。無線通信デバイスのための線形位相周波数検出器およびチャージポンプの使用が下記に説明される。

## 【0052】

図8は、無線通信システムにおける無線デバイス800の一設計のブロック図を示す。無線デバイス800は、携帯電話、端末、携帯情報端末(personal digital assistant)(PDA)、ハンドセットあるいは他の何らかのデバイスであってよい。無線通信システムは、符号分割多元接続(CDMA)システム、時分割多元接続(TDMA)システム、周波数分割多元接続(FDMA)システム、グローバル移動体通信システム(Global System for Mobile Communications)(GSM)のシステム、直交FDMA(OFDMA)システム、無線ローカルエリアネットワーク(WLAN)などであってよい。

20

## 【0053】

無線デバイス800は、双方向通信をサポートするデジタルプロセッサ810およびトランシーバ830を含んでいる。デジタルプロセッサ810は、1つ以上の特定用途向け集積回路(ASIC)などでインプリメントされる(implemented)ことができる。トランシーバ830は、1つ以上のRF集積回路(RFIC)などでインプリメントされることができる。

30

## 【0054】

データ伝送の場合は、エンコーダ812が、送信されるべきデータを処理し(例えば、フォーマットし、符号化し、インタリーブし(interleaves))、そして、変調器814が、データチップを生成するために符号化データをさらに処理する(例えば、変調し、スクランブルする)。トランシーバ830内では、送信(transmit)(TX)ベースバンドユニット832が、デジタル/アナログ変換、フィルタリング、増幅などのような、ベースバンド処理を行なう。ミキサ(mixer)834は、ベースバンド信号を無線周波数(RF)へアップコンバートする(upconverts)。TX RFユニット836は、例えば、フィルタリングや電力増幅などの、信号調整(signal conditioning)を行ない、そして、アンテナ840を介して送信されるRF変調信号(RF modulated signal)を、生成する。

40

## 【0055】

データ受信の場合は、受信(receive)(RX)RFユニット842が、アンテナ840からインプットRF信号を受け取り、例えば、低ノイズ増幅やフィルタリングなどの、信号調整を行なう。ミキサ844は、調整されたRF信号を、RFからベースバンドにダウンコンバートする。RXベースバンドユニット846は、フィルタリング、増幅、アナログ/デジタル変換などのような、ベースバンド処理を行なう。復調器(Demod)816は、ユニット846からの入力サンプルを処理し(例えば、デスクランブルし(descremables)、復調し)、そして、シンボル評価(symbol estimates)を提供する。デコーダ81

50

8 は、シンボル評価を処理し（例えば、デインターリーブし(deinterleaves)、デコードし）、そして、デコードされたデータを提供する。一般に、データプロセッサ 810 およびトランシーバ 830 による処理は、無線システムの設計に依存する。

【0056】

プロセッサ 820 は、ビデオ、オーディオ、グラフィックスなどのような、様々なアプリケーションをサポートすることができる。コントローラ/プロセッサ 860 は、無線デバイス 800 内の様々な処理ユニット(processing units)の動作を指図する(directs)。メモリ 862 は、無線デバイス 800 のためのプログラムコードおよびデータを保存する。

【0057】

VCO/PLL 822 は、デジタルプロセッサ 810 内の処理ユニットのためのクロック信号を生成する。VCO/PLL 850 は、周波数アップコンバージョンのためにミキサ 834 によって使用される送信 LO 信号と、周波数ダウンコンバージョンのためにミキサ 844 によって使用される受信 LO 信号とを、生成する。VCO/PLL 822 および VCO/PLL 850 は、性能を改善するために、線形位相周波数検出器およびチャージポンプを各々が使用してもよい。基準発振器 864 は、VCO/PLL 822 および/または VCO/PLL 850 のための基準信号を生成する。基準発振器 864 は、水晶発振器 (XO)、電圧制御 XO (VCXO)、温度補償 XO (TCXO)、あるいは何らかの他のタイプの発振器であってもよい。

【0058】

ここに説明された位相周波数検出器、チャージポンプ、PLL は、アナログ IC、RF IC、ASIC、デジタル信号プロセッサ (DSP)、デジタル信号処理デバイス (DSPD)、プログラマブル論理回路 (PLD)、フィールドプログラマブルゲートアレイ (FPGA)、プロセッサ、コントローラ、マイクロコントローラ、マイクロプロセッサ、および他の電子ユニット、においてインプリメントされてもよい。位相周波数検出器、チャージポンプ、および PLL は、様々な IC プロセス技術、例えば、N-MOS、P-MOS、CMOS、BJT、GaAs、など、で製造ができる。位相周波数検出器、チャージポンプ、および PLL は、また、ディスクリートコンポーネントでインプリメントされてもよい。

【0059】

本開示の以上の説明は、いずれの当業者も本開示を作りまたは使用することを可能にするように提供されている。本開示に対する様々な修正は、当業者には容易に明らかであろう、また、ここに定義された総括的な原理は、本開示の精神あるいは範囲から逸脱することなく、他の変形に適用されることができる。したがって、本開示は、ここに説明された例に限定されるようには意図されておらず、ここに開示された原理と新規な特徴に整合する最も広いスコープを与えられるべきである。

10

20

30

### 【図1】

图 1

FIG. 1

【 図 2 】

图 2

FIG. 2

【 図 3 】

図 3

FIG. 3

### 【図4A】

图 4.

FIG. 4A

【図4B】

4

FIG. 4B

【図 5 A】

図 5A

FIG. 5A

【図 5 B】

図 5B

FIG. 5B

【図 6】

図 6

FIG. 6

【図 7】

図 7

FIG. 7

【図 8】

図 8

FIG. 8

---

フロントページの続き

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 シヤン、ガン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 畑中 博幸

(56)参考文献 米国特許第07092475(US, B1)

特開平11-330958(JP, A)

特開平11-225072(JP, A)

特表2003-526239(JP, A)

特開2003-179490(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03L 7/089

H03L 7/093

H03L 7/197