(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-99114

(P2016-99114A)

(43) 公開日 平成28年5月30日(2016.5.30)

(51) Int.Cl. F I テーマコード (参考)

**G01L** 9/00 (2006.01) G01L 9/00 303Z 2F055

**B81B** 3/00 (2006.01) B81B 3/00 3C081

**H01L** 29/84 (2006.01) H01L 29/84 A 4M112

H01L 29/84 B

審査請求 未請求 請求項の数 13 O.L. (全 20 頁)

|           |                              |            |                                              |

|-----------|------------------------------|------------|----------------------------------------------|

| (21) 出願番号 | 特願2014-233352 (P2014-233352) | (71) 出願人   | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区新宿四丁目1番6号 |

| (22) 出願日  | 平成26年11月18日 (2014.11.18)     | (74) 代理人   | 100116665<br>弁理士 渡辺 和昭                       |

|           |                              | (74) 代理人   | 100164633<br>弁理士 西田 圭介                       |

|           |                              | (72) 発明者   | 田中 信幸<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内       |

|           |                              | F ターム (参考) | 2F055 AA01 BB01 CC02 DD05 EE14<br>FF45 GG12  |

最終頁に続く

(54) 【発明の名称】電子デバイス、物理量センサー、圧力センサー、高度計、電子機器および移動体

(57) 【要約】

【課題】優れた信頼性を有する電子デバイスおよび物理量センサーを提供すること、また、かかる電子デバイスを備える圧力センサー、高度計、電子機器および移動体を提供すること。

【解決手段】本発明の物理量センサー1は、基板2と、基板2の一方の面側に配置されているピエゾ抵抗素子5と、基板2の一方の面側に基板2の平面視でピエゾ抵抗素子5を囲んで配置されている壁部と、壁部に対して基板とは反対側に配置されていて空洞部Sを壁部とともに構成している天井部と、を備え、壁部は、壁部を横断する断面で見たときに、絶縁層631と、絶縁層631を互いに協働して囲んでいて、絶縁層631をエッチング可能なエッチング液に対する耐性が絶縁層631よりも高い配線層62、64と、を有する。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

基板と、

前記基板の一方の面側に配置されている機能素子と、

前記基板の前記一方の面側に前記基板の平面視で前記機能素子を囲んで配置されている壁部と、

前記壁部に対して前記基板とは反対側に配置されていて、前記壁部とともに内部空間を構成している天井部と、

を備え、

前記壁部は、絶縁層と、前記絶縁層をエッチング可能なエッチング液に対する耐性が前記絶縁層よりも高い複数の耐蝕層と、を有し、

前記基板と交差する方向の断面視で、前記複数の耐蝕層が接続して前記絶縁層の周囲に配置されていることを特徴とする電子デバイス。

**【請求項 2】**

前記複数の耐蝕層は、前記断面視で、第1耐蝕層と、前記第1耐蝕層に対して2箇所で接続していて前記第1耐蝕層とともに前記絶縁層を囲んでいる第2耐蝕層と、を有する請求項1に記載の電子デバイス。

**【請求項 3】**

前記第1耐蝕層は、

前記基板に固定されている固定部と、

前記固定部から前記内部空間側に延びていて前記基板と離間している第1フランジ部と、

前記固定部から前記内部空間とは反対側に延びていて前記基板と離間している第2フランジ部と、

を有し、

前記第2耐蝕層は、

前記第1フランジ部に接続している第1接続部と、

前記第2フランジ部に接続している第2接続部と、

を有する請求項2に記載の電子デバイス。

**【請求項 4】**

前記耐蝕層は、金属を含んでいる請求項1ないし3のいずれか1項に記載の電子デバイス。

**【請求項 5】**

前記金属は、アルミニウムを含んでいる請求項4に記載の電子デバイス。

**【請求項 6】**

前記絶縁層は、酸化シリコンを含んでいる請求項1ないし5のいずれか1項に記載の電子デバイス。

**【請求項 7】**

前記基板は、平面視で前記天井部と重なる位置に設けられていて、受圧により撓み変形するダイヤフラム部を有する請求項1ないし6のいずれか1項に記載の電子デバイス。

**【請求項 8】**

前記機能素子は、歪みにより電気信号を出力するセンサー素子である請求項7に記載の電子デバイス。

**【請求項 9】**

前記機能素子が前記ダイヤフラム部の一方の面側に配置されているセンサー素子である請求項7に記載の電子デバイス、を備えることを特徴とする物理量センサー。

**【請求項 10】**

請求項1ないし8のいずれか1項に記載の電子デバイスを備えることを特徴とする圧力センサー。

**【請求項 11】**

10

20

30

40

50

請求項 1ないし 8のいずれか 1 項に記載の電子デバイスを備えることを特徴とする高度計。

【請求項 1 2】

請求項 1ないし 8のいずれか 1 項に記載の電子デバイスを備えることを特徴とする電子機器。

【請求項 1 3】

請求項 1ないし 8のいずれか 1 項に記載の電子デバイスを備えることを特徴とする移動体。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、電子デバイス、物理量センサー、圧力センサー、高度計、電子機器および移動体に関するものである。

【背景技術】

【0 0 0 2】

半導体製造プロセスを用いて形成された空洞部を有する電子デバイスが知られている（例えば、特許文献 1 参照）。このような電子デバイスの一例としては、例えば、特許文献 1 に係る電子装置が挙げられ、この電子装置は、基板と、基板に設けられた MEMS 構造体と、被覆構造体と、を含み、被覆構造体が、包囲壁と、第 1 被覆層と、第 2 被覆層と、を有し、包囲壁、第 1 被覆層、第 2 被覆層および基板によって、MEMS 構造体が配置された空洞部が形成されている。

【0 0 0 3】

しかし、特許文献 1 に係る電子装置では、ウェットエッティングを用いて空洞部を形成する際に、レジストで構成されたマスクとの隙間からエッティング液が侵入し、それによって不本意なエッティングが生じ、その結果、空洞部の気密性が低下するという問題があった。

【先行技術文献】

【特許文献】

【0 0 0 4】

【特許文献 1】特開 2012 - 96316 号公報

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 5】

本発明の目的は、優れた信頼性を有する電子デバイスおよび物理量センサーを提供すること、また、かかる電子デバイスを備える圧力センサー、高度計、電子機器および移動体を提供することにある。

【課題を解決するための手段】

【0 0 0 6】

このような目的は、下記の本発明により達成される。

【適用例 1】

本発明の電子デバイスは、基板と、

前記基板の一方の面側に配置されている機能素子と、

前記基板の前記一方の面側に前記基板の平面視で前記機能素子を囲んで配置されている壁部と、

前記壁部に対して前記基板とは反対側に配置されていて、前記壁部とともに内部空間を構成している天井部と、

を備え、

前記壁部は、絶縁層と、前記絶縁層をエッティング可能なエッティング液に対する耐性が前記絶縁層よりも高い複数の耐蝕層と、を有し、

前記基板と交差する方向の断面視で、前記複数の耐蝕層が接続して前記絶縁層の周囲に配置されていることを特徴とする。

10

20

30

40

50

**【 0 0 0 7 】**

このような電子デバイスによれば、複数の耐蝕層が互いに接続して絶縁層を囲んでいることにより、内部空間を形成する際に用いるエッティング液により壁部（特に絶縁層）がエッティングされてしまうのを低減することができる。よって、優れた信頼性を有する電子デバイスを提供することができる。

**【 0 0 0 8 】****[ 適用例 2 ]**

本発明の電子デバイスでは、前記複数の耐蝕層は、前記断面視で、第1耐蝕層と、前記第1耐蝕層に対して2箇所で接続していて前記第1耐蝕層とともに前記絶縁層を囲んでいる第2耐蝕層と、を有することが好ましい。10

これにより、第1耐蝕層および第2耐蝕層の2層により絶縁層を囲むことができる。

**【 0 0 0 9 】****[ 適用例 3 ]**

本発明の電子デバイスでは、前記第1耐蝕層は、

前記基板に固定されている固定部と、

前記固定部から前記内部空間側に延びていて前記基板と離間している第1フランジ部と20

、

前記固定部から前記内部空間とは反対側に延びていて前記基板と離間している第2フランジ部と、

を有し、

前記第2耐蝕層は、

前記第1フランジ部に接続している第1接続部と、

前記第2フランジ部に接続している第2接続部と、

を有することが好ましい。

**【 0 0 1 0 】**

これにより、壁部の基板とは反対側の段差を低減することができる。そのため、壁部および天井部を構成する各層の密着性を高めて、内部空間の気密性の低下を効果的に低減することができる。また、内部空間をエッティングにより形成する際に用いるマスクの密着性を高めることができ、その結果、不本意なエッティングを低減することができる。

**【 0 0 1 1 】****[ 適用例 4 ]**

本発明の電子デバイスでは、前記耐蝕層は、金属を含んでいることが好ましい。

金属は、高精度な成膜が可能であるとともに、シリコン酸化膜で構成された絶縁層のエッティングに用いるエッティングに対して高い耐性を有する。したがって、耐蝕層が金属を含んでいることにより、高精度な壁部を形成することができる。

**【 0 0 1 2 】****[ 適用例 5 ]**

本発明の電子デバイスでは、前記金属は、アルミニウムを含んでいることが好ましい。

アルミニウムは、金属の中でも、半導体製造プロセスとの親和性が高い。したがって、耐蝕層がアルミニウムを含んでいることにより、比較的簡単に、高精度な壁部を形成することができる。40

**【 0 0 1 3 】****[ 適用例 6 ]**

本発明の電子デバイスでは、前記絶縁層は、酸化シリコンを含んでいることが好ましい。

。

**【 0 0 1 4 】**

酸化シリコン（SiO<sub>2</sub>）は、絶縁性を有し、犠牲層の材料として適している。そのため、比較的簡単に、高精度な壁部および内部空間を形成することができる。

**【 0 0 1 5 】****[ 適用例 7 ]**

10

20

30

40

50

本発明の電子デバイスでは、前記基板は、平面視で前記天井部と重なる位置に設けられていて、受圧により撓み変形するダイヤフラム部を有することが好ましい。

【0016】

これにより、圧力を検出可能な電子デバイス（物理量センサー）を実現することができる。

【0017】

[適用例8]

本発明の電子デバイスでは、前記機能素子は、歪みにより電気信号を出力するセンサー素子であることが好ましい。

これにより、圧力の検出感度を向上させることができる。

10

【0018】

[適用例9]

本発明の物理量センサーは、前記機能素子が前記ダイヤフラム部の一方の面側に配置されているセンサー素子である本発明の電子デバイス、を備えることを特徴とする。

これにより、優れた信頼性を有する物理量センサーを提供することができる。

【0019】

[適用例10]

本発明の圧力センサーは、本発明の電子デバイスを備えることを特徴とする。

これにより、優れた信頼性を有する圧力センサーを提供することができる。

20

【0020】

[適用例11]

本発明の高度計は、本発明の電子デバイスを備えることを特徴とする。

これにより、優れた信頼性を有する高度計を提供することができる。

【0021】

[適用例12]

本発明の電子機器は、本発明の電子デバイスを備えることを特徴とする。

これにより、優れた信頼性を有する電子機器を提供することができる。

30

【0022】

[適用例13]

本発明の移動体は、本発明の電子デバイスを備えることを特徴とする。

これにより、優れた信頼性を有する移動体を提供することができる。

【図面の簡単な説明】

【0023】

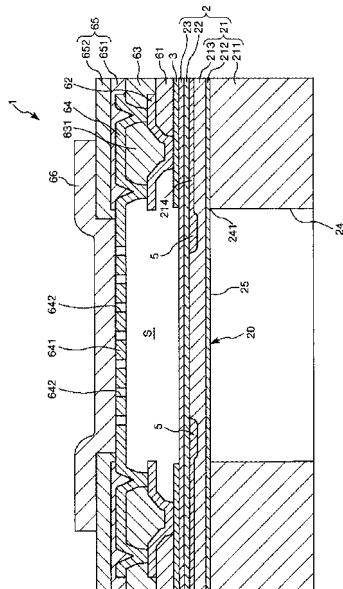

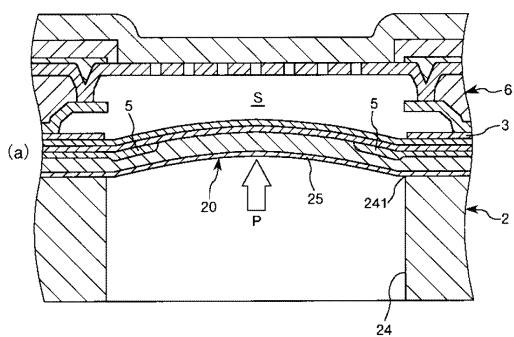

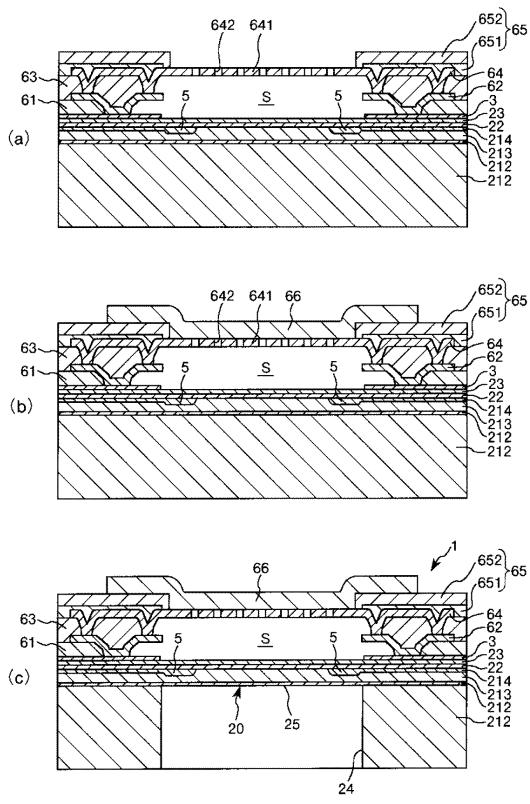

【図1】本発明の実施形態に係る物理量センサー（電子デバイス）を示す断面図である。

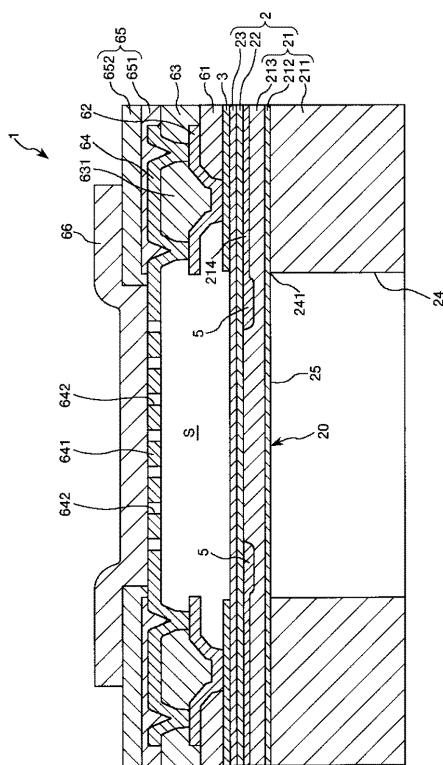

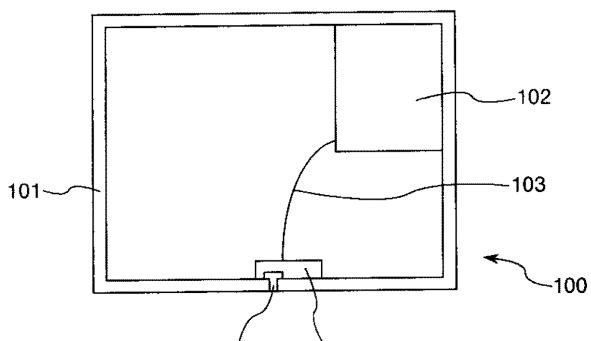

【図2】図1に示す物理量センサーのピエゾ抵抗素子（センサー素子）の配置を示す平面図である。

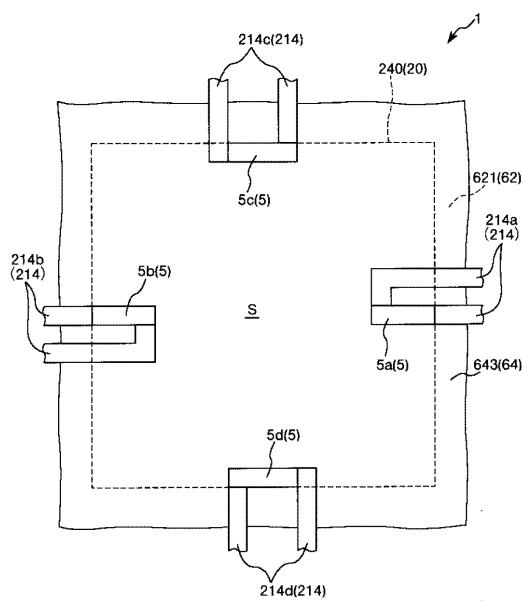

【図3】図1に示す物理量センサーの作用を説明するための図であって、（a）は加圧状態を示す断面図、（b）は加圧状態を示す平面図である。

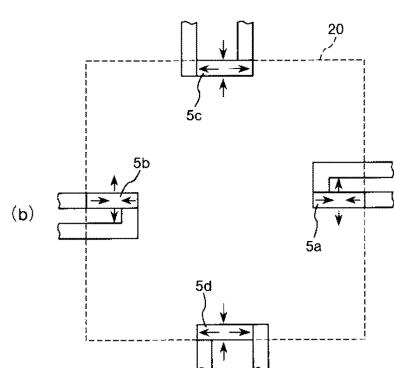

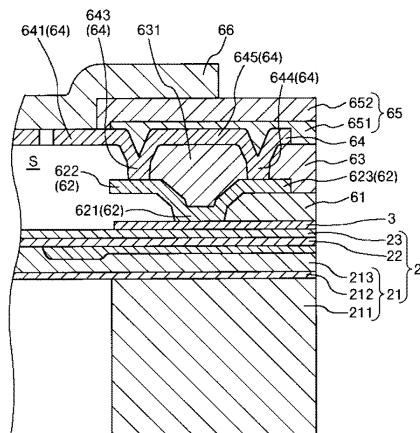

【図4】図1に示す物理量センサーの部分拡大断面図である。

40

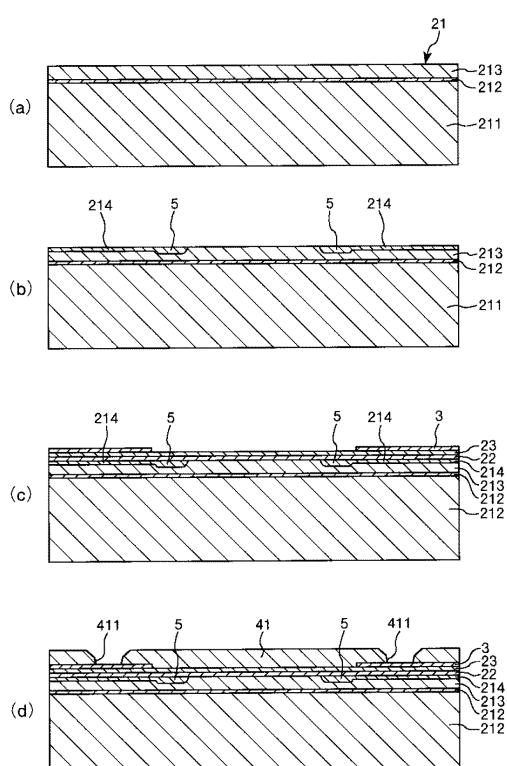

【図5】図1に示す物理量センサーの製造工程を示す図である。

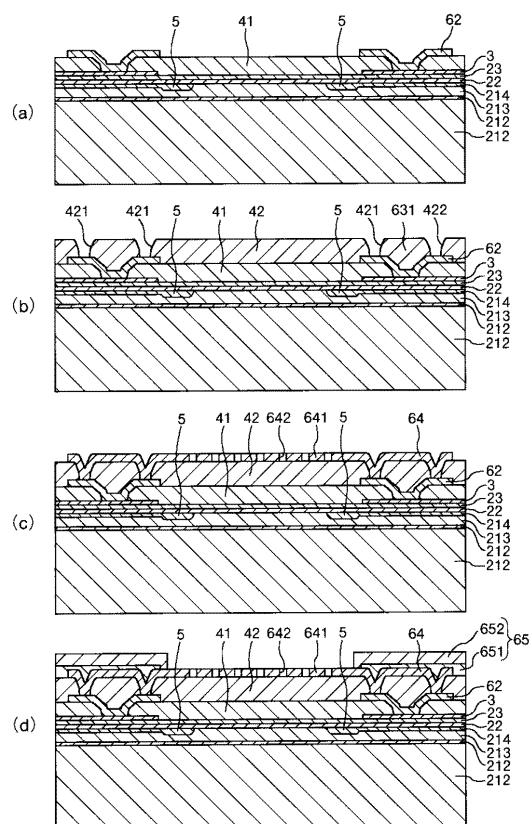

【図6】図1に示す物理量センサーの製造工程を示す図である。

【図7】図1に示す物理量センサーの製造工程を示す図である。

【図8】本発明の圧力センサーの一例を示す断面図である。

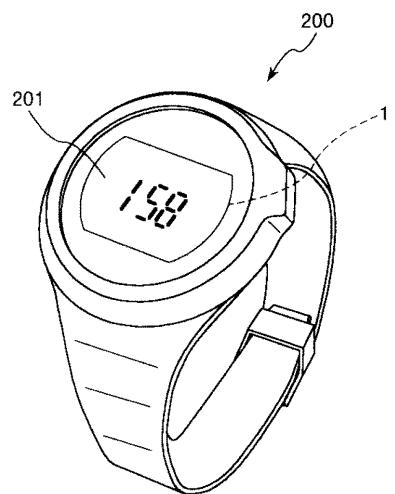

【図9】本発明の高度計の一例を示す斜視図である。

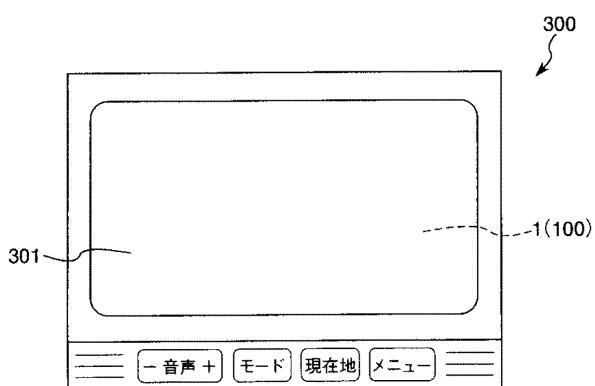

【図10】本発明の電子機器の一例を示す正面図である。

【図11】本発明の移動体の一例を示す斜視図である。

【発明を実施するための形態】

【0024】

以下、本発明の電子デバイス、物理量センサー、圧力センサー、高度計、電子機器および移動体を添付図面に示す各実施形態に基づいて詳細に説明する。

50

## 【0025】

## 1. 物理量センサー

図1は、本発明の実施形態に係る物理量センサーを示す断面図、図2は、図1に示す物理量センサーのピエゾ抵抗素子(センサー素子)の配置を示す平面図である。図3は、図1に示す物理量センサーの作用を説明するための図であって、図3(a)は加圧状態を示す断面図、図3(b)は加圧状態を示す平面図である。なお、以下では、説明の便宜上、図1中の上側を「上」、下側を「下」という。

## 【0026】

図1に示す物理量センサー1は、ダイヤフラム部20を有する基板2と、ダイヤフラム部20に配置されている機能素子である複数のピエゾ抵抗素子5(センサー素子)と、基板2とともに空洞部S(内部空間)を形成している積層構造体6と、基板2と積層構造体6との間に配置されている中間層3と、を備えている。10

## 【0027】

以下、物理量センサー1を構成する各部を順次説明する。

## - 基板 -

基板2は、半導体基板21と、半導体基板21の一方の面上に設けられた絶縁膜22と、絶縁膜22の半導体基板21とは反対側の面上に設けられた絶縁膜23と、を有している。

## 【0028】

半導体基板21は、単結晶シリコンで構成されているシリコン層211(ハンドル層)と、シリコン酸化膜で構成されている酸化シリコン層212(ボックス層)と、単結晶シリコンで構成されているシリコン層213(デバイス層)とがこの順で積層されたSOI基板である。なお、半導体基板21は、SOI基板に限定されず、例えば、単結晶シリコン基板等の他の半導体基板であってもよい。20

## 【0029】

絶縁膜22は、例えば、シリコン酸化膜であり、絶縁性を有する。また、絶縁膜23は、例えば、シリコン窒化膜であり、絶縁性を有するとともに、フッ酸を含むエッチング液に対する耐性をも有する。ここで、半導体基板21(シリコン層213)と絶縁膜23(シリコン窒化膜)との間に絶縁膜22(シリコン酸化膜)が介在していることにより、絶縁膜23の成膜時に生じた応力が半導体基板21に伝わるのを絶縁膜22により緩和することができる。また、絶縁膜22は、半導体基板21およびその上方に半導体回路を形成する場合、素子間分離膜として用いることもできる。なお、絶縁膜22、23は、前述した構成材料に限定されず、また、必要に応じて、絶縁膜22、23のうちのいずれか一方を省略してもよい。30

## 【0030】

このような基板2の絶縁膜23上には、パターニングされた中間層3が配置されている。この中間層3は、平面視でダイヤフラム部20の周囲を囲むように形成されており、中間層3の上面と基板2の上面との間であって、ダイヤフラム部20の中心側(内側)に中間層3の厚さ分の段差部を形成する。これにより、ダイヤフラム部20が受圧により撓み変形したとき、ダイヤフラム部20の段差部との間の境界部分に応力を集中させることができる。そのため、かかる境界部分(またはその付近)にピエゾ抵抗素子5を配置することにより、検出感度を向上させることができる。40

## 【0031】

この中間層3は、例えば、単結晶シリコン、多結晶シリコン(ポリシリコン)またはアモルファスシリコンで構成されている。また、中間層3は、例えば、単結晶シリコン、多結晶シリコン(ポリシリコン)またはアモルファスシリコンにリン、ボロン等の不純物をドープ(拡散または注入)して構成されていてもよい。この場合、中間層3は、導電性を有するため、例えば、空洞部Sの外側において基板2上にMOSトランジスタを形成する場合、中間層3の一部をMOSトランジスタのゲート電極として用いることができる。また、中間層3の一部を配線として用いることもできる。50

## 【0032】

このような基板2には、周囲の部分よりも薄肉であり、受圧によって撓み変形するダイヤフラム部20が設けられている。ダイヤフラム部20は、半導体基板21の下面に有底の凹部24を設けることで形成されている。すなわち、ダイヤフラム部20は、基板2の一方の面に開口している凹部24の底部を含んで構成されている。このダイヤフラム部20は、その下面が受圧面25となっている。本実施形態では、図2に示すように、ダイヤフラム部20は、正方形(矩形)の平面視形状である。

## 【0033】

本実施形態の基板2では、凹部24がシリコン層211を貫通しており、ダイヤフラム部20が酸化シリコン層212、シリコン層213、絶縁膜22および絶縁膜23の4層で構成されている。ここで、酸化シリコン層212は、後述するように、物理量センサー1の製造工程において凹部24をエッティングにより形成する際にエッティングストップ層として利用することができ、ダイヤフラム部20の厚さの製品ごとのバラツキを少なくすることができる。

10

## 【0034】

なお、凹部24がシリコン層211を貫通せず、ダイヤフラム部20がシリコン層211の薄肉部、酸化シリコン層212、シリコン層213、絶縁膜22および絶縁膜23の5層で構成されていてもよい。

## 【0035】

- ピエゾ抵抗素子(機能素子) -

20

複数のピエゾ抵抗素子5は、図1に示すように、それぞれ、ダイヤフラム部20の空洞部S側に形成されている。ここで、ピエゾ抵抗素子5は、半導体基板21のシリコン層213に形成されている。

## 【0036】

図2に示すように、複数のピエゾ抵抗素子5は、ダイヤフラム部20の外周部に配置されている複数のピエゾ抵抗素子5a、5b、5c、5dで構成されている。

## 【0037】

基板2の厚さ方向から見た平面視(以下、単に「平面視」という)で四角形をなすダイヤフラム部20の4つの辺にそれぞれ対応して、ピエゾ抵抗素子5a、ピエゾ抵抗素子5b、ピエゾ抵抗素子5c、ピエゾ抵抗素子5dが配置されている。

30

## 【0038】

ピエゾ抵抗素子5aは、ダイヤフラム部20の対応する辺に対して垂直な方向に沿って延びている。そして、ピエゾ抵抗素子5aの両端部には、1対の配線214aが電気的に接続されている。同様に、ピエゾ抵抗素子5bは、ダイヤフラム部20の対応する辺に対して垂直な方向に沿って延びている。そして、ピエゾ抵抗素子5bの両端部には、1対の配線214bが電気的に接続されている。

## 【0039】

一方、ピエゾ抵抗素子5cは、ダイヤフラム部20の対応する辺に対して平行な方向に沿って延びている。そして、ピエゾ抵抗素子5cの両端部には、1対の配線214cが電気的に接続されている。同様に、ピエゾ抵抗素子5dは、ダイヤフラム部20の対応する辺に対して平行な方向に沿って延びている。そして、ピエゾ抵抗素子5dの両端部には、1対の配線214dが電気的に接続されている。

40

## 【0040】

なお、以下では、配線214a、214b、214c、214dをまとめて「配線214」ともいう。

## 【0041】

このようなピエゾ抵抗素子5および配線214は、それぞれ、例えば、リン、ボロン等の不純物をドープ(拡散または注入)したシリコン(単結晶シリコン)で構成されている。ここで、配線214における不純物のドープ濃度は、ピエゾ抵抗素子5における不純物のドープ濃度よりも高い。なお、配線214は、金属で構成されていてもよい。

50

## 【0042】

また、複数のピエゾ抵抗素子5は、例えば、自然状態における抵抗値が互いに等しくなるように構成されている。

## 【0043】

以上説明したようなピエゾ抵抗素子5は、配線214等を介して、ブリッジ回路(ホイートストンブリッジ回路)を構成している。このブリッジ回路には、駆動電圧を供給する駆動回路(図示せず)が接続されている。そして、このブリッジ回路では、ピエゾ抵抗素子5の抵抗値に応じた信号(電圧)として出力される。

## 【0044】

- 積層構造体 -

積層構造体6は、前述した基板2との間に空洞部Sを画成するように形成されている。ここで、積層構造体6は、ダイヤフラム部20のピエゾ抵抗素子5側に配置されていてダイヤフラム部20(または基板2)とともに空洞部S(内部空間)を区画形成(構成)している。

## 【0045】

この積層構造体6は、基板2上に平面視でピエゾ抵抗素子5を取り囲むように形成された層間絶縁膜61と、層間絶縁膜61上に形成された配線層62と、配線層62および層間絶縁膜61上に形成された層間絶縁膜63と、層間絶縁膜63上に形成され、複数の細孔642(開孔)を備えた被覆層641を有する配線層64と、配線層64および層間絶縁膜63上に形成された表面保護膜65と、被覆層641上に設けられた封止層66とを有している。

## 【0046】

層間絶縁膜61、63は、それぞれ、例えば、シリコン酸化膜で構成されている。また、配線層62、64および封止層66は、それぞれ、アルミニウム等の金属で構成されている。また、封止層66は、被覆層641が有する複数の細孔642を封止している。また、表面保護膜65は、シリコン酸化膜であるSiO<sub>2</sub>層651と、シリコン窒化膜であるSiN層652とがこの順で積層されて構成されている。ここで、主としてSiN層652が表面保護の機能を有し、SiO<sub>2</sub>層651は、SiN層652との間の密着性や平坦性を高める機能を有する。

## 【0047】

このような積層構造体6において、被覆層641を除く配線層62および配線層64からなる構造体は、層間絶縁膜63の一部である絶縁層631とともに、基板2の一方の面側に平面視でピエゾ抵抗素子5を囲んで配置されている「壁部」(ガードリング)を構成している。また、被覆層641は、この壁部に対して基板2とは反対側に配置されていて空洞部S(内部空間)を壁部とともに構成している「天井部」を構成している。なお、壁部およびこれに関連する事項については、後に詳述する。

## 【0048】

また、このような積層構造体6は、CMOSプロセスのような半導体製造プロセスを用いて形成することができる。なお、シリコン層213上およびその上方には、半導体回路が作り込まれていてもよい。この半導体回路は、MOSトランジスタ等の能動素子、その他必要に応じて形成されたコンデンサ、インダクタ、抵抗、ダイオード、配線(ピエゾ抵抗素子5に接続されている配線を含む)等の回路要素を有している。

## 【0049】

基板2と積層構造体6とによって画成された空洞部Sは、密閉された空間である。この空洞部Sは、物理量センサー1が検出する圧力の基準値となる圧力基準室として機能する。本実施形態では、空洞部Sが真空状態(300Pa以下)となっている。空洞部Sを真空状態とすることによって、物理量センサー1を、真空状態を基準として圧力を検出する「絶対圧センサー」として用いることができ、その利便性が向上する。

## 【0050】

ただし、空洞部Sは、真空状態でなくてもよく、大気圧であってもよいし、大気圧より

10

20

30

40

50

も気圧が低い減圧状態であってもよいし、大気圧よりも気圧が高い加圧状態であってもよい。また、空洞部 S には、窒素ガス、希ガス等の不活性ガスが封入されていてもよい。

以上、物理量センサー 1 の構成について簡単に説明した。

#### 【0051】

このような構成の物理量センサー 1 は、図 3 (a) に示すように、ダイヤフラム部 20 の受圧面 25 が受ける圧力 P に応じて、ダイヤフラム部 20 が変形し、これにより、図 3 (b) に示すように、ピエゾ抵抗素子 5a、5b、5c、5d が歪み、ピエゾ抵抗素子 5a、5b、5c、5d の抵抗値が変化する。それに伴って、ピエゾ抵抗素子 5a、5b、5c、5d が構成するブリッジ回路の出力が変化し、その出力に基づいて、受圧面 25 で受けた圧力の大きさを求めることができる。

10

#### 【0052】

より具体的に説明すると、前述したようなダイヤフラム部 20 の変形が生じる前の自然状態では、例えば、ピエゾ抵抗素子 5a、5b、5c、5d の抵抗値が互いに等しい場合、ピエゾ抵抗素子 5a、5b の抵抗値の積とピエゾ抵抗素子 5c、5d の抵抗値の積とが等しく、ブリッジ回路の出力（電位差）はゼロとなる。

#### 【0053】

一方、前述したようなダイヤフラム部 20 の変形が生じると、図 3 (b) に示すように、ピエゾ抵抗素子 5a、5b にその長手方向に沿った圧縮歪みおよび幅方向に沿った引張歪みが生じるとともに、ピエゾ抵抗素子 5c、5d がその長手方向に沿った引張歪みおよびその幅方向に沿った圧縮歪みが生じる。したがって、前述したようなダイヤフラム部 20 の変形が生じたとき、ピエゾ抵抗素子 5a、5b の抵抗値とピエゾ抵抗素子 5c、5d の抵抗値とのうち、一方の抵抗値が増加し、他方の抵抗値が減少する。

20

#### 【0054】

このようなピエゾ抵抗素子 5a、5b、5c、5d の歪みにより、ピエゾ抵抗素子 5a、5b の抵抗値の積とピエゾ抵抗素子 5c、5d の抵抗値の積との差が生じ、その差に応じた出力（電位差）がブリッジ回路から出力される。このブリッジ回路からの出力に基づいて、受圧面 25 で受けた圧力の大きさ（絶対圧）を求めることができる。

#### 【0055】

ここで、前述したようなダイヤフラム部 20 の変形が生じたとき、ピエゾ抵抗素子 5a、5b の抵抗値とピエゾ抵抗素子 5c、5d の抵抗値とのうち、一方の抵抗値が増加し、他方の抵抗値が減少するため、ピエゾ抵抗素子 5a、5b の抵抗値の積とピエゾ抵抗素子 5c、5d の抵抗値の積との差の変化を大きくすることができ、それに伴って、ブリッジ回路からの出力を大きくすることができる。その結果、圧力の検出感度を高めることができる。

30

#### 【0056】

このように、物理量センサー 1 では、基板 2 が有するダイヤフラム部 20 が、平面視で被覆層 641 と重なる位置に設けられていて、受圧により撓み変形する。これにより、圧力を検出可能な物理量センサー 1 を実現することができる。また、ダイヤフラム部 20 に配置されているピエゾ抵抗素子 5 が歪みにより電気信号を出力するセンサー素子であるため、圧力の検出感度を向上させることができる。また、前述したように平面視でダイヤフラム部 20 の輪郭が矩形をなしているため、圧力の検出感度を向上させることができる。

40

#### 【0057】

(壁部)

以下、壁部について詳述する。

図 4 は、図 1 に示す物理量センサーの部分拡大断面図である。

#### 【0058】

前述したように、被覆層 641 を除く配線層 62 および配線層 64 からなる構造体は、層間絶縁膜 63 の一部である絶縁層 631 とともに、基板 2 の一方の面側に平面視でピエゾ抵抗素子 5 を囲んで配置されている「壁部」を構成している。この壁部は、図 4 に示すように、この壁部を横断する断面で見たときに、絶縁層 631 と、絶縁層 631 を互いに

50

協働して囲んでいている配線層 6 2、6 4 と、を有する。

【0059】

ここで、配線層 6 2、6 4 は、それぞれ、絶縁層 6 3 1 をエッティング可能なエッティング液に対する耐性が絶縁層 6 3 1 よりも高い「耐蝕層」である。このような耐蝕性を有する配線層 6 2、6 4 が互いに協働して絶縁層 6 3 1 を囲んでいるため、各配線層 6 2、6 4 が絶縁層 6 3 1 により効果的に補強される。そのため、各配線層 6 2、6 4 にクラックが生じ難く、空洞部 S の気密性の低下を低減することができる。しかも、複数の配線層 6 2、6 4 が互いに協働して絶縁層 6 3 1 を囲んでいることにより、後述するように空洞部 S を形成する際に用いるエッティング液により壁部（特に絶縁層 6 3 1）がエッティングされてしまうのを低減することができる。また、仮に絶縁層 6 3 1 がエッティングされてしまったとしても、壁部の外形形状を安定的に維持することができる。10

【0060】

ここで、図 4 に示す断面で見たとき、配線層 6 4（第 2 耐蝕層）は、配線層 6 2（第 1 耐蝕層）に対して 2箇所で接続していて配線層 6 2 との間に絶縁層 6 3 1 を挟んでいる。これにより、配線層 6 2 および配線層 6 4 の 2 層により絶縁層 6 3 1 を囲むことができる。。

【0061】

より具体的に説明すると、配線層 6 2 は、基板 2 に中間層 3 を介して固定されている固定部 6 2 1 と、固定部 6 2 1 から空洞部 S 側に延びていて基板 2 と離間している第 1 フランジ部 6 2 2 と、固定部 6 2 1 から空洞部 S とは反対側に延びていて基板 2 と離間している第 2 フランジ部 6 2 3 と、を有する。20

【0062】

一方、配線層 6 4 は、配線層 6 2 の第 1 フランジ部 6 2 2 に接続している第 1 接続部 6 4 3 と、配線層 6 2 の第 2 フランジ部に接続している第 2 接続部 6 4 4 と、第 1 接続部 6 4 3 と第 2 接続部 6 4 4 とを連結していて固定部 6 2 1 と離間している連結部 6 4 5 と、を有する。

【0063】

このように構成された配線層 6 2、6 4 によれば、壁部の基板 2 とは反対側の段差を低減して平坦性を高くすることができる。そのため、壁部および天井部を構成する各層の密着性を高めて、空洞部 S の気密性の低下を効果的に低減することができる。また、空洞部 S をエッティングにより形成する際に用いるマスクの密着性を高めることができ、その結果、不本意なエッティングを低減することができる。30

【0064】

これに対し、仮に配線層 6 4 が配線層 6 2 の固定部 6 2 1 で接続されていたとすると、配線層 6 4 の接続部と他の部分との間に形成される段差は、配線層 6 2 の固定部 6 2 1 と第 1 フランジ部 6 2 2 または第 2 フランジ部 6 2 3 との間に形成される段差の影響を受けて重畠的に大きく形成されてしまい、その結果、壁部の基板 2 とは反対側の段差が大きくなって平坦性が低くなってしまう。そのため、例えば、表面保護膜 6 5 と配線層 6 4 との密着性が低下し、配線層 6 4 に亀裂が生じたときに、空洞部 S の気密性が低下したり、空洞部 S をエッティングにより形成する際に用いるマスクの密着性が低下して、不本意なエッティングが生じる結果、空洞部 S の気密性の低下が生じやすくなったりする。40

【0065】

ここで、配線層 6 2、6 4 の構成材料としては、絶縁層 6 3 1 をエッティング可能なエッティング液に対する耐性が絶縁層 6 3 1 よりも高ければよいが、金属を用いることが好ましく、アルミニウムを用いることがより好ましい。金属は、高精度な成膜が可能であるとともに、シリコン酸化膜で構成された絶縁層 6 3 1 のエッティングに用いるエッティングに対して高い耐性を有する。したがって、配線層 6 2、6 4 が金属を含んでいることにより、高精度な壁部を形成することができる。特に、アルミニウムは、金属の中でも、半導体製造プロセスとの親和性が高い。したがって、配線層 6 2、6 4 がアルミニウムを含んでいることにより、比較的簡単に、高精度な壁部を形成することができる。50

## 【0066】

また、絶縁層631は、酸化シリコン(SiO<sub>2</sub>)を含んでいることが好ましい。酸化シリコンは、絶縁性を有し、犠牲層の材料として適している。そのため、比較的簡単に、高精度な壁部および空洞部Sを形成することができる。

## 【0067】

また、壁部の厚さ(第1接続部643と第2接続部644との間の距離)は、特に限定されないが、15μm以上20μm以下であることが好ましい。これにより、前述したような効果を発揮させつつ、壁部の占める容積を低減して物理量センサー1の小型化を図ることができる。

## 【0068】

## (物理量センサーの製造方法)

次に、物理量センサー1の製造方法を簡単に説明する。

## 【0069】

図5～図7は、図1に示す物理量センサーの製造工程を示す図である。以下、物理量センサー1の製造方法を、これらの図に基づいて説明する。

## 【0070】

## [素子形成工程]

まず、図5(a)に示すように、SOI基板である半導体基板21を用意する。

## 【0071】

そして、半導体基板21のシリコン層213にリン(n型)またはボロン(p型)等の不純物をドープ(イオン注入)することにより、図5(b)に示すように、複数のピエゾ抵抗素子5および配線214を形成する。

## 【0072】

例えば、ボロンを+80keVでイオン注入を行う場合、ピエゾ抵抗素子5へのイオン注入濃度を $1 \times 10^{14}$ atoms/cm<sup>2</sup>程度とする。また、配線214へのイオン注入濃度をピエゾ抵抗素子5よりも多くする。例えば、ボロンを10keVでイオン注入を行う場合、配線214へのイオン注入濃度を $5 \times 10^{15}$ atoms/cm<sup>2</sup>程度とする。また、前述したようなイオン注入の後、例えば、1000程度で20分程度のアニールを行う。

## 【0073】

## [絶縁膜等形成工程]

次に、図5(c)に示すように、シリコン層213上に絶縁膜22、絶縁膜23および中間層3をこの順で形成する。

## 【0074】

絶縁膜22、23の形成は、それぞれ、例えば、スパッタリング法、CVD法等により行うことができる。中間層3は、例えば、多結晶シリコンをスパッタリング法、CVD法等により成膜した後、その膜に必要に応じてリン、ボロン等の不純物をドープ(イオン注入)し、その後、エッチングによりパターニングすることで形成することができる。

## 【0075】

## [層間絶縁膜・配線層形成工程]

次に、図5(d)に示すように、絶縁膜23上に、犠牲層41を形成する。

## 【0076】

この犠牲層41は、後述する空洞部形成工程により一部が除去され、残部が層間絶縁膜61となるものであり、配線層62が貫通するための貫通孔411を有する。犠牲層41の形成は、シリコン酸化膜をスパッタリング法、CVD法等により形成し、そのシリコン酸化膜をエッチングによりパターニングすることにより行う。

## 【0077】

また、犠牲層41の厚さは、特に限定されないが、例えば、1500nm以上5000nm以下程度とされる。

## 【0078】

10

20

30

40

50

次に、図6(a)に示すように、犠牲層41に形成された貫通孔411を埋めるように、配線層62を形成する。

【0079】

配線層62の形成は、例えば、スパッタリング法、CVD法等により一様な導体膜を形成した後、この導体膜をパターニング処理することにより行うことができる。図示しないが、アルミニウムを用いて配線層62を形成する場合、アルミニウムの成膜に先立ち、貫通孔411の壁面に、例えばTi層およびTiN層からなるグルーレイヤーを形成してもよい。また、アルミニウムを一様に成膜した後に、その膜上に、例えばTiN層からなる反射防止層を形成してもよい。

【0080】

また、配線層62の厚さは、特に限定されないが、例えば、300nm以上900nm以下程度とされる。

【0081】

次に、図6(b)に示すように、犠牲層41上および配線層62上に、犠牲層42を形成する。

【0082】

この犠牲層42は、後述する空洞部形成工程により一部が除去され、残部が層間絶縁膜63となるものであり、配線層64が貫通するための貫通孔421、422を有する。犠牲層42の形成は、前述した犠牲層41の形成と同様、シリコン酸化膜をスパッタリング法、CVD法等により形成し、そのシリコン酸化膜をエッチングによりパターニングすることにより行う。

【0083】

また、犠牲層42の厚さは、特に限定されないが、例えば、1500nm以上5000nm以下程度とされる。

【0084】

次に、図6(c)に示すように、犠牲層42に形成された貫通孔421、422を埋めるように、配線層64を形成する。これにより、犠牲層42の一部が配線層62、64により囲まれて絶縁層631が形成される。

【0085】

配線層64の形成は、例えば、スパッタリング法、CVD法等により一様な導体膜を形成した後、この導体膜をパターニング処理することにより行うことができる。図示しないが、アルミニウムを用いて配線層64を形成する場合、アルミニウムの成膜に先立ち、貫通孔421、422の各壁面に、例えばTi層およびTiN層からなるグルーレイヤーを形成してもよい。また、アルミニウムを一様に成膜した後に、その膜上に、例えばTiN層からなる反射防止層を形成してもよい。

【0086】

また、配線層64の厚さは、特に限定されないが、例えば、300nm以上900nm以下程度とされる。

【0087】

以上のようにして犠牲層41、42および配線層62、64が形成される。なお、このような犠牲層41、42および配線層62、64からなる積層構造は、通常のCMOSプロセスを用いて形成され、その積層数は、必要に応じて適宜に設定される。すなわち、必要に応じてさらに多くの犠牲層や配線層が積層される場合もある。

【0088】

その後、図6(d)に示すように、スパッタリング法、CVD法等により表面保護膜65を形成する。これにより、後述する空洞部形成工程におけるエッチングの際、犠牲層41、42の層間絶縁膜61、62となる部分を保護することができる。

【0089】

ここで、前述したSiO<sub>2</sub>層651およびSiN層652を有する表面保護膜65を形成する際には、SiO<sub>2</sub>層およびSiN層をこの順で一様に形成した後にこれらの層をパ

ターニングすることにより SiO<sub>2</sub>層 651 および SiN 層 652 を形成する。

【0090】

なお、表面保護膜 65 の構成は、前述したものに限定されない。表面保護膜 65 の構成材料としては、例えば、シリコン酸化膜、シリコン窒化膜、ポリイミド膜、エポキシ樹脂膜など、素子を水分、ゴミ、傷などから保護するための耐性を有するものが挙げられ、特に、シリコン窒化膜が好適である。

【0091】

表面保護膜 65 の厚さは、特に限定されないが、例えば、500 nm 以上 2000 nm 以下程度とされる。

【0092】

10 [空洞部形成工程]

次に、犠牲層 41、42 の一部を除去することにより、図 7 (a) に示すように、絶縁膜 23 と被覆層 641 との間に空洞部 S (キャビティ) を形成する。これにより、層間絶縁膜 61、63 が形成される。

【0093】

空洞部 S の形成は、被覆層 641 に形成された複数の細孔 642 を通じたエッチングにより、犠牲層 41、42 の一部を除去することにより行う。ここで、かかるエッチングとしてウェットエッチングを用いる場合、複数の細孔 642 からフッ酸、緩衝フッ酸等のエッチング液を供給し、ドライエッチングを用いる場合、複数の細孔 642 からフッ化水素酸ガス等のエッチングガスを供給する。このようなエッチングの際、絶縁膜 23 がエッチングトップ層として機能する。また、絶縁膜 23 は、エッチング液に対する耐性を有することから、絶縁膜 23 に対して下側の構成部（例えば、絶縁膜 22、ピエゾ抵抗素子 5、配線 214 等）をエッチング液から保護する機能をも有する。

【0094】

20 [封止工程]

次に、図 7 (b) に示すように、被覆層 641 上に、シリコン酸化膜、シリコン窒化膜、Al、Cu、W、Ti、TiN 等の金属膜等からなる封止層 66 をスパッタリング法、CVD 法等により形成し、各細孔 642 を封止する。これより、空洞部 S が封止層 66 により封止され、積層構造体 6 を得る。

【0095】

30 ここで、封止層 66 の厚さは、特に限定されないが、例えば、1000 nm 以上 500 nm 以下程度とされる。

【0096】

[ダイヤフラム形成工程]

次に、シリコン層 211 の下面を必要に応じて研削した後、シリコン層 211 の下面の一部をエッチングにより除去（加工）することにより、図 7 (c) に示すように、凹部 24 を形成する。これにより、空洞部 S を介して被覆層 641 に対向するダイヤフラム部 20 が形成される。

【0097】

40 ここで、シリコン層 211 の下面の一部を除去する際、酸化シリコン層 212 がエッチングトップ層として機能する。これにより、ダイヤフラム部 20 の厚さを高精度に規定することができる。

【0098】

なお、シリコン層 211 の下面の一部を除去する方法としては、ドライエッチングであっても、ウェットエッチング等であってもよい。

以上のような工程により、物理量センサー 1 を製造することができる。

【0099】

2. 圧力センサー

次に、本発明の物理量センサーを備える圧力センサー（本発明の圧力センサー）について説明する。図 8 は、本発明の圧力センサーの一例を示す断面図である。

**【 0 1 0 0 】**

図8に示すように、本発明の圧力センサー100は、物理量センサー1と、物理量センサー1を収納する筐体101と、物理量センサー1から得た信号を圧力データに演算する演算部102とを備えている。物理量センサー1は、配線103を介して演算部102と電気的に接続されている。

**【 0 1 0 1 】**

物理量センサー1は、筐体101の内側に、図示しない固定手段により固定されている。また、筐体101には、物理量センサー1のダイヤフラム部20が、例えば大気(筐体101の外側)と連通するための貫通孔104を有している。

10

**【 0 1 0 2 】**

このような圧力センサー100によれば、貫通孔104を介してダイヤフラム部20が圧力を受ける。この受圧した信号を配線103を介して演算部に送信し、圧力データに演算する。この演算された圧力データは、図示しない表示部(例えば、パーソナルコンピューターのモニター等)を介して表示することができる。

**【 0 1 0 3 】****3 . 高度計**

次に、本発明の物理量センサーを備える高度計(本発明の高度計)の一例について説明する。図9は、本発明の高度計の一例を示す斜視図である。

**【 0 1 0 4 】**

高度計200は、腕時計のように、手首に装着することができる。また、高度計200の内部には、物理量センサー1(圧力センサー100)が搭載されており、表示部201に現在地の海拔からの高度、または、現在地の気圧等を表示することができる。

20

**【 0 1 0 5 】**

なお、この表示部201には、現在時刻、使用者の心拍数、天候等、様々な情報を表示することができる。

**【 0 1 0 6 】****4 . 電子機器**

次に、本発明の物理量センサーを備える電子機器を適用したナビゲーションシステムについて説明する。図10は、本発明の電子機器の一例を示す正面図である。

30

**【 0 1 0 7 】**

ナビゲーションシステム300には、図示しない地図情報と、GPS(全地球測位システム: Global Positioning System)からの位置情報取得手段と、ジャイロセンサーおよび加速度センサーと車速データとによる自立航法手段と、物理量センサー1と、所定の位置情報または進路情報を表示する表示部301とを備えている。

30

**【 0 1 0 8 】**

このナビゲーションシステムによれば、取得した位置情報に加えて高度情報を取得することができる。高度情報を得ることにより、例えば、一般道路と位置情報上は略同一の位置を示す高架道路を走行する場合、高度情報を持たない場合には、一般道路を走行しているのか高架道路を走行しているのかナビゲーションシステムでは判断できず、優先情報として一般道路の情報を使用者に提供してしまっていた。そこで、本実施形態に係るナビゲーションシステム300では、高度情報を物理量センサー1によって取得することができ、一般道路から高架道路へ進入することによる高度変化を検出し、高架道路の走行状態におけるナビゲーション情報を使用者に提供することができる。

40

**【 0 1 0 9 】**

なお、表示部301は、例えば液晶パネルディスプレイや、有機EL(Organic Electroluminescence)ディスプレイなど、小型かつ薄型化が可能な構成となっている。

**【 0 1 1 0 】**

なお、本発明の物理量センサーを備える電子機器は、上記のものに限定されず、例えば、パーソナルコンピューター、携帯電話、医療機器(例えば電子体温計、血圧計、血糖計

50

、心電図計測装置、超音波診断装置、電子内視鏡)、各種測定機器、計器類(例えば、車両、航空機、船舶の計器類)、ライトシミュレーター等に適用することができる。

【0111】

5. 移動体

次いで、本発明の物理量センサーを適用した移動体(本発明の移動体)について説明する。図11は、本発明の移動体の一例を示す斜視図である。

【0112】

図11に示すように、移動体400は、車体401と、4つの車輪402とを有しており、車体401に設けられた図示しない動力源(エンジン)によって車輪402を回転させるように構成されている。このような移動体400には、ナビゲーションシステム300(物理量センサー1)が内蔵されている。

10

【0113】

以上、本発明の電子デバイス、物理量センサー、圧力センサー、高度計、電子機器および移動体を図示の各実施形態に基づいて説明したが、本発明はこれらに限定されるものではなく、各部の構成は、同様の機能を有する任意の構成のものに置換することができる。また、他の任意の構成物が付加されていてもよい。

20

【0114】

また、1つのダイヤフラム部に設けられるピエゾ抵抗素子(機能素子)の数は、前述した実施形態では4つである場合を例に説明したが、これに限定されず、例えば、1つ以上3つ以下、または、5つ以上であってもよい。また、ピエゾ抵抗素子の配置や形状等も前述した実施形態に限定されず、例えば、前述した実施形態において、ダイヤフラム部の中央部にもピエゾ抵抗素子を配置してもよい。

20

【0115】

また、前述した実施形態では、ダイヤフラム部の撓みを検出するセンサー素子としてピエゾ抵抗素子を用いた場合を例に説明したが、かかる素子としては、これに限定されず、例えば、共振子であってもよい。

30

【0116】

また、前述した実施形態では、本発明の電子デバイスを物理量センサーに適用した場合を例に説明したが、これに限定されず、前述したように半導体製造プロセスを用いて基板上に壁部および天井部を形成し、基板、壁部および天井部により内部空間を形成する各種電子デバイスに本発明を適用することができ、その場合、ダイヤフラム部を省略することができる。

30

【0117】

また、前述した実施形態では、壁部の耐蝕層の数が2つの場合を例に説明したが、耐蝕層の数は、これに限定されず、3つ以上であってもよい。この場合、3つ以上の耐蝕層のうちの任意の互いに隣り合う2つの耐蝕層により絶縁層を囲んでもよいし、また、3つ以上の耐蝕層で絶縁層を囲んでもよいが、壁部の基板とは反対側の段差を低減する観点から、最も天井部側の耐蝕層を含む複数の耐蝕層で絶縁層を囲むことが好ましい。

【符号の説明】

【0118】

40

1 物理量センサー

2 基板

3 中間層

5 ピエゾ抵抗素子

5 a ピエゾ抵抗素子

5 b ピエゾ抵抗素子

5 c ピエゾ抵抗素子

5 d ピエゾ抵抗素子

6 積層構造体

20 ダイヤフラム部

50

|         |                    |    |

|---------|--------------------|----|

| 2 1     | 半導体基板              |    |

| 2 2     | 絶縁膜                |    |

| 2 3     | 絶縁膜                |    |

| 2 4     | 凹部                 |    |

| 2 5     | 受圧面                |    |

| 4 1     | 犠牲層                |    |

| 4 2     | 犠牲層                |    |

| 6 1     | 層間絶縁膜              |    |

| 6 2     | 配線層                |    |

| 6 3     | 層間絶縁膜              | 10 |

| 6 4     | 配線層                |    |

| 6 5     | 表面保護膜              |    |

| 6 6     | 封止層                |    |

| 1 0 0   | 圧力センサー             |    |

| 1 0 1   | 筐体                 |    |

| 1 0 2   | 演算部                |    |

| 1 0 3   | 配線                 |    |

| 1 0 4   | 貫通孔                |    |

| 2 0 0   | 高度計                |    |

| 2 0 1   | 表示部                | 20 |

| 2 1 1   | シリコン層              |    |

| 2 1 2   | 酸化シリコン層            |    |

| 2 1 3   | シリコン層              |    |

| 2 1 4   | 配線                 |    |

| 2 1 4 a | 配線                 |    |

| 2 1 4 b | 配線                 |    |

| 2 1 4 c | 配線                 |    |

| 2 1 4 d | 配線                 |    |

| 3 0 0   | ナビゲーションシステム        |    |

| 3 0 1   | 表示部                | 30 |

| 4 0 0   | 移動体                |    |

| 4 0 1   | 車体                 |    |

| 4 0 2   | 車輪                 |    |

| 4 1 1   | 貫通孔                |    |

| 4 2 1   | 貫通孔                |    |

| 6 2 1   | 固定部                |    |

| 6 2 2   | 第1フランジ部            |    |

| 6 2 3   | 第2フランジ部            |    |

| 6 3 1   | 絶縁層                |    |

| 6 4 1   | 被覆層                | 40 |

| 6 4 2   | 細孔                 |    |

| 6 4 3   | 第1接続部              |    |

| 6 4 4   | 第2接続部              |    |

| 6 4 5   | 連結部                |    |

| 6 5 1   | SiO <sub>2</sub> 層 |    |

| 6 5 2   | SiN層               |    |

| P       | 圧力                 |    |

| S       | 空洞部                |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

F ターム(参考) 3C081 AA01 BA22 BA30 BA45 BA48 BA56 CA03 CA14 CA15 CA16

CA28 CA29 DA04 DA29 DA30 EA01 EA03

4M112 AA01 BA01 CA01 CA03 CA04 CA09 CA12 CA13 CA14 DA03

DA04 DA05 DA06 DA09 DA10 DA12 DA14 DA15 DA18 EA03

EA04 EA05 EA06 EA07 EA10 EA11 EA12 EA14 EA18 FA01

FA09 FA11 FA20 GA01 GA03