(19)日本国特許庁(JP)

(12)特許公報(B2)

(11)特許番号

特許第7522548号

(P7522548)

(45)発行日 令和6年7月25日(2024.7.25)

(24)登録日 令和6年7月17日(2024.7.17)

(51) 國際特許分類

H 0 4 N 25/78 (2023.01) H 0 4 N 25/78

H 0 4 N 25/76 (2023.01) H 0 4 N 25/76

FI

H 0 4 N 25/78

請求項の数 12 (全22頁)

|          |                             |          |                                            |

|----------|-----------------------------|----------|--------------------------------------------|

| (21)出願番号 | 特願2019-223001(P2019-223001) | (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22)出願日  | 令和1年12月10日(2019.12.10)      |          |                                            |

| (65)公開番号 | 特開2021-93623(P2021-93623A)  |          |                                            |

| (43)公開日  | 令和3年6月17日(2021.6.17)        | (74)代理人  | 110003281<br>弁理士法人大塚国際特許事務所                |

| 審査請求日    | 令和4年12月12日(2022.12.12)      | (72)発明者  | 誠名 紀之<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

|          |                             | (72)発明者  | 鶴谷 美子<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

|          |                             | (72)発明者  | 竹中 真太郎<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内   |

|          |                             | 審査官      | 鈴木 肇                                       |

(54)【発明の名称】 光電変換装置および撮像装置

### (57) 【特許請求の範囲】

### 【請求項 1】

複数の行および複数の列を構成するように配置された複数の画素、および、前記複数の画素のノイズ信号および光信号を出力するための複数の列信号線を有する画素アレイと、各画素からノイズ信号の次に光信号が出力されるように前記複数の画素を駆動する駆動部と、

前記複数の行のうち第1数の行から前記複数の列信号線に出力されるノイズ信号をノイズデータにA/D変換する動作を前記第1数の行を単位として繰り返し、次いで、前記複数の行のうち前記第1数の行から前記複数の列信号線に出力される光信号を光データにA/D変換する動作を前記第1数の行を単位として繰り返す複数のA/D変換器を含むA/D変換部と、

データ保持部と、

第1期間において前記第1数の行の前記ノイズデータを前記第1数のチャネルを構成する複数の水平転送線を介して前記A/D変換部から前記データ保持部に並列に転送して前記データ保持部に保持させる動作を前記第1数の行を単位として繰り返し、次いで、前記第1期間とは異なる第2期間において前記第1数の行の前記光データを前記複数の水平転送線を介して前記A/D変換部から前記データ保持部に並列に転送して前記データ保持部に保持させる動作を前記第1数の行を単位として繰り返す転送部と、

前記データ保持部によって保持され前記データ保持部から出力される前記光データと前記ノイズデータとの差分を演算する演算部と、を備え、

前記データ保持部は、並列に設けられた第2数のチャネルを通して、前記データ保持部によって保持されたノイズデータを前記第2数のノイズデータごとに並列に前記データ保持部から前記演算部に出力するとともに前記データ保持部によって保持された光データを前記第2数の光データごとに並列に前記データ保持部から前記演算部に出力し、

前記転送部が前記ノイズデータおよび前記光データを前記データ保持部に転送し保持させる動作と、前記データ保持部によって保持されたノイズデータおよび光データを前記データ保持部から前記演算部に出力する動作とは並行して行われ、

前記第2数は、前記第1数よりも小さい2以上の自然数である、

ことを特徴とする光電変換装置。

**【請求項2】**

10

前記データ保持部は、前記第1数の行の画素のノイズデータを保持するノイズデータ記憶部と、前記第1数の行の画素の光データを保持する光データ記憶部とを含む、

ことを特徴とする請求項1に記載の光電変換装置。

**【請求項3】**

前記ノイズデータ記憶部は、互いに独立してアクセス可能な第1記憶部および第2記憶部を含み、

前記光データ記憶部は、互いに独立してアクセス可能な第3記憶部および第4記憶部を含む、

ことを特徴とする請求項2に記載の光電変換装置。

**【請求項4】**

20

前記データ保持部は、前記第1数の行の画素のノイズデータを保持する第1ノイズデータ記憶部と、前記第1数の行の画素のノイズデータを保持する第2ノイズデータ記憶部と、前記第1数の行の画素の光データを保持する第1光データ記憶部と、前記第1数の行の画素の光データを保持する第2光データ記憶部とを含む、

ことを特徴とする請求項1に記載の光電変換装置。

**【請求項5】**

前記第1ノイズデータ記憶部、前記第2ノイズデータ記憶部、前記第1光データ記憶部および前記第2光データ記憶部のそれぞれは、互いに独立してアクセス可能な2つの記憶部を含む、

ことを特徴とする請求項4に記載の光電変換装置。

30

**【請求項6】**

前記第1ノイズデータ記憶部、前記第2ノイズデータ記憶部、前記第1光データ記憶部および前記第2光データ記憶部のそれぞれは、前記第1数の半分のデータを2回受けて前記第1数のデータとして出力するバス幅変換部と、前記バス幅変換部から出力される前記第1数の行の画素のデータを保持する記憶部とを含む、

ことを特徴とする請求項4に記載の光電変換装置。

**【請求項7】**

前記第1ノイズデータ記憶部は、前記第1数の半分のノイズデータを2回受けて前記第1数のノイズデータとして出力する第1バス幅変換部と、前記第1バス幅変換部から出力される前記第1数の行の画素のノイズデータを保持する第1記憶部とを含み、

前記第2ノイズデータ記憶部は、前記第1数の半分のノイズデータを2回受けて前記第1数のノイズデータとして出力する第2バス幅変換部と、前記第2バス幅変換部から出力される前記第1数の行の画素のノイズデータを保持する第2記憶部とを含み、

前記第1光データ記憶部は、前記第1数の半分の光データを2回受けて前記第1数の光データとして出力する第3バス幅変換部と、前記第3バス幅変換部から出力される前記第1数の行の画素の光データを保持する第3記憶部とを含み、

前記第2光データ記憶部は、前記第1数の半分の光データを2回受けて前記第1数の光データとして出力する第4バス幅変換部と、前記第4バス幅変換部から出力される前記第1数の行の画素の光データを保持する第4記憶部とを含む、

ことを特徴とする請求項4に記載の光電変換装置。

40

50

**【請求項 8】**

水平同期信号によって規定される水平走査期間において前記転送部が前記データ保持部に転送し前記データ保持部に保持させた前記ノイズデータおよび前記光データは、次の水平走査期間において前記データ保持部から前記演算部に出力される、

ことを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の光電変換装置。

**【請求項 9】**

前記次の水平走査期間において、前記データ保持部が前記演算部に前記ノイズデータおよび前記光データを出力する動作と並行して、前記転送部は、新たなノイズデータおよび光データを前記データ保持部に転送し保持させる、

ことを特徴とする請求項 8 に記載の光電変換装置。

10

**【請求項 10】**

前記画素アレイが配された第 1 の半導体基板と、

前記データ保持部が配された第 2 の半導体基板と、

を備えることを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の光電変換装置。

**【請求項 11】**

前記駆動部と前記複数の A/D 変換器とが、前記第 2 の半導体基板に配される、

ことを特徴とする請求項 10 に記載の光電変換装置。

**【請求項 12】**

請求項 1 乃至 1 1 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置からのデータを処理するプロセッサと、

を備えることを特徴とする撮像装置。

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、光電変換装置および撮像装置に関する。

**【背景技術】****【0002】**

特許文献 1 には、画素アレイ部と、複数の A/D 変換器と、データラッチ部と、パラシリ変換部と、列デコーダ/センサアンプと、メモリ部と、データ処理部と、IF 部とを備える固体撮像素子が記載されている。各 A/D 変換器は、画素アレイの各画素から信号線を通して読み出されるアナログ信号を A/D 変換して画素データを生成する。この際に、各 A/D 変換器は、画素からの信号レベルと該画素からのリセットレベルとの差分に相当する画素データを生成する。複数の A/D 変換器によって生成された複数の画素データは、データラッチ部に転送され、パラシリ変換部および列デコーダ/センサアンプを介してメモリ部に転送される。また、列デコーダ/センサアンプは、メモリ部からビット線を通して読み出される微弱な電圧をデジタルレベルとして取り扱いが可能なレベルまで増幅し画素データとして出力する。画素データは、データ処理部に提供され、データ処理部によって処理される。

30

**【先行技術文献】****【特許文献】**

40

**【0003】**

【文献】特開 2017-183659 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

特許文献 1 に記載された固体撮像素子では、各 A/D 変換器は、画素からの信号レベルと該画素からのリセットレベルとの差分に相当する画素データを生成する。よって、A/D 変換器の機能が複雑化しうる。

**【0005】**

本発明は、A/D 変換器の機能を単純化するために有利な光電変換装置の構成を提供する

50

ことを目的とする。

【課題を解決するための手段】

【0006】

本発明の1つの側面は、光電変換装置に係り、前記光電変換装置は、複数の行および複数の列を構成するように配置された複数の画素、および、前記複数の画素のノイズ信号および光信号を出力するための複数の列信号線を有する画素アレイと、各画素からノイズ信号の次に光信号が出力されるように前記複数の画素を駆動する駆動部と、前記複数の行のうち第1数の行から前記複数の列信号線に出力されるノイズ信号をノイズデータにAD変換する動作を前記第1数の行を単位として繰り返し、次いで、前記複数の行のうち前記第1数の行から前記複数の列信号線に出力される光信号を光データにAD変換する動作を前記第1数の行を単位として繰り返す複数のAD変換器を含むAD変換部と、データ保持部と、第1期間において前記第1数の行の前記ノイズデータを前記第1数のチャネルを構成する複数の水平転送線を介して前記AD変換部から前記データ保持部に並列に転送して前記データ保持部に保持させる動作を前記第1数の行を単位として繰り返し、次いで、前記第1期間とは異なる第2期間において前記第1数の行の前記光データを前記複数の水平転送線を介して前記AD変換部から前記データ保持部に並列に転送して前記データ保持部に保持させる動作を前記第1数の行を単位として繰り返す転送部と、前記データ保持部によって保持され前記データ保持部から出力される前記光データと前記ノイズデータとの差分を演算する演算部と、を備え、前記データ保持部は、並列に設けられた第2数のチャネルを通して、前記データ保持部によって保持されたノイズデータを前記第2数のノイズデータごとに並列に前記データ保持部から前記演算部に出力するとともに前記データ保持部によって保持された光データを前記第2数の光データごとに並列に前記データ保持部から前記演算部に出力し、前記転送部が前記ノイズデータおよび前記光データを前記データ保持部に転送し保持させる動作と、前記データ保持部によって保持されたノイズデータおよび光データを前記データ保持部から前記演算部に出力する動作とは並行して行われ、前記第2数は、前記第1数よりも小さい2以上の自然数である。

10

20

30

【発明の効果】

【0007】

本発明によれば、AD変換器の機能を単純化するために有利な光電変換装置の構成が提供される。

30

【図面の簡単な説明】

【0008】

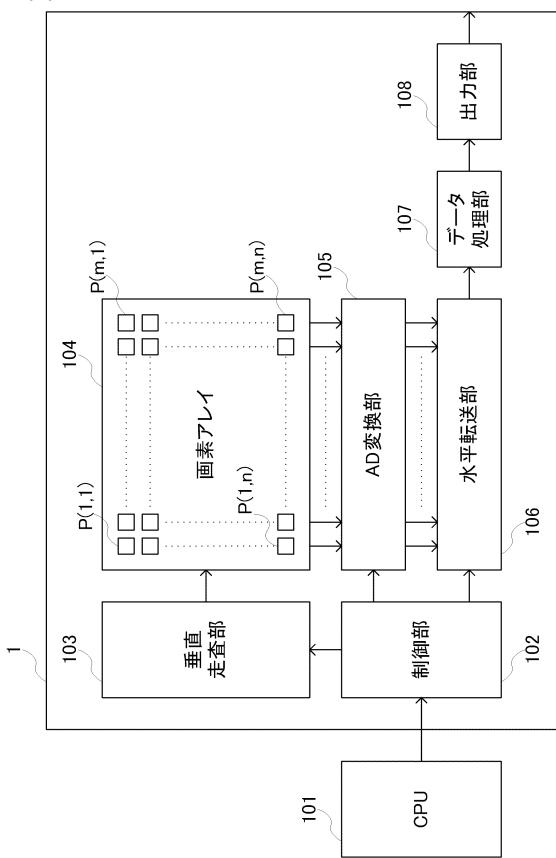

【図1】第1実施形態の光電変換装置の構成例を示すブロック図。

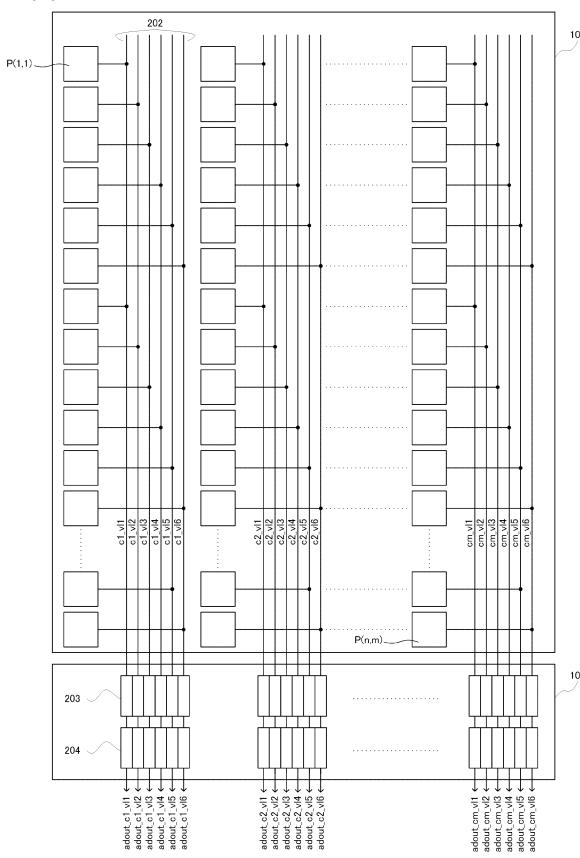

【図2】第1実施形態の光電変換装置の画素アレイおよびAD変換部の構成例を示す図。

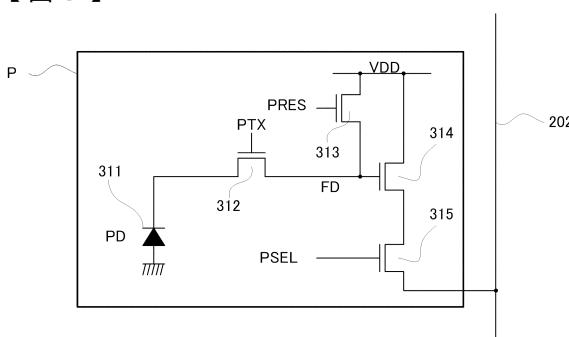

【図3】第1実施形態の光電変換装置の画素の構成例を示す図。

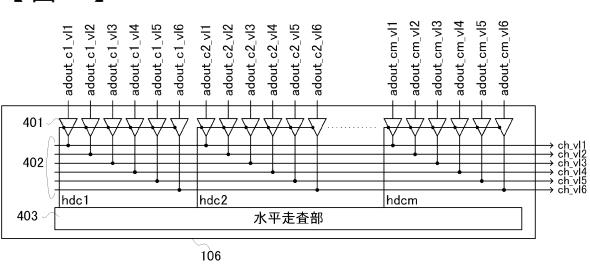

【図4】第1実施形態の光電変換装置の水平転送部の構成例を示す図。

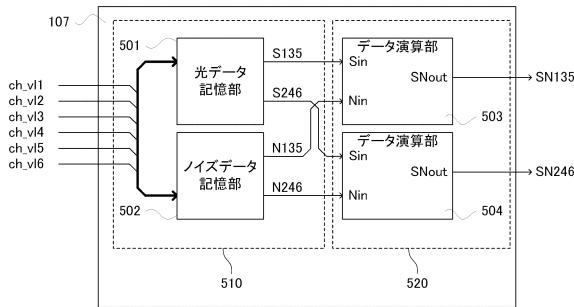

【図5】第1実施形態の光電変換装置のデータ処理部の構成例を示す図。

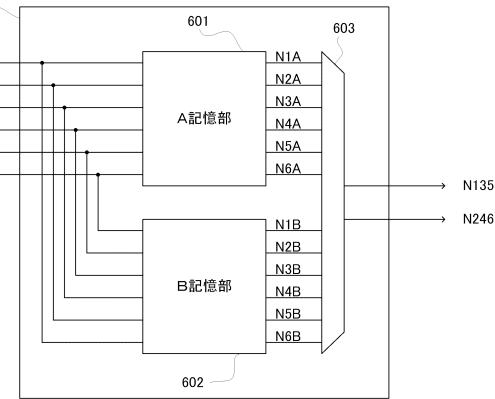

【図6】第1実施形態の光電変換装置のノイズデータ記憶部の構成例を示す図。

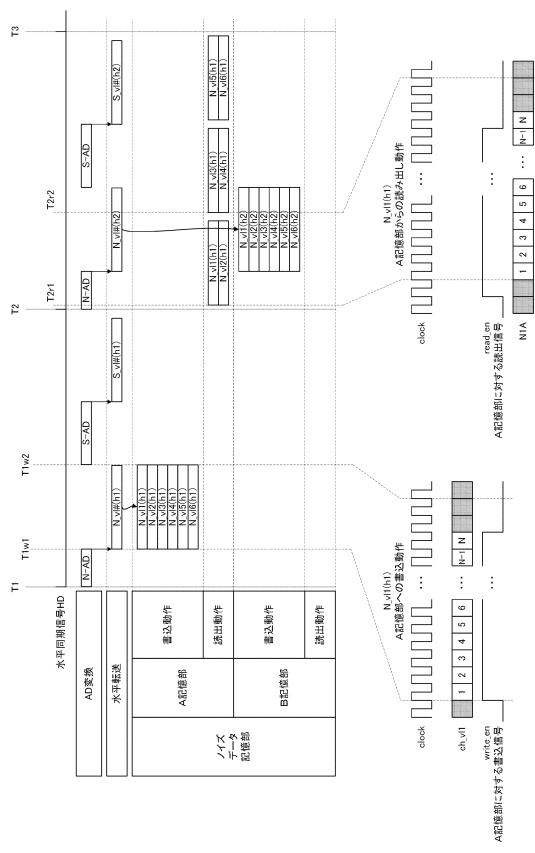

【図7】第1実施形態の光電変換装置の動作例を示すタイミングチャート。

【図8】第1実施形態の光電変換装置の動作例を示すタイミングチャート。

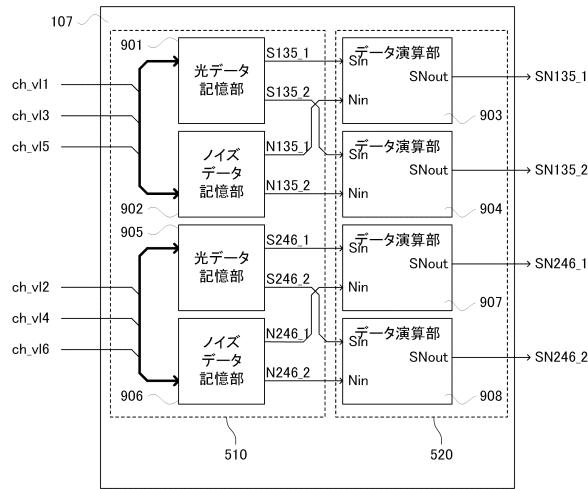

【図9】第2実施形態の光電変換装置のデータ処理部の構成例を示す図。

40

【図10】第2実施形態の光電変換装置のノイズデータ記憶部の構成例を示す図。

【図11】第1実施形態の光電変換装置の動作例を示すタイミングチャート。

【図12】第1実施形態の光電変換装置の動作例を示すタイミングチャート。

【図13】実施形態の撮像装置の構成例を示す図。

【発明を実施するための形態】

【0009】

以下、添付図面を参照して実施形態を詳しく説明する。尚、以下の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に

50

組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。

#### 【 0 0 1 0 】

図 1 には、第 1 実施形態の光電変換装置 1 の構成が示されている。光電変換装置 1 は、例えば、固体撮像装置として構成されうる。光電変換装置 1 は、C P U 1 0 1 によって制御されうる。光電変換装置 1 は、例えば、制御部 1 0 2 と、垂直走査部（駆動部）1 0 3 と、画素アレイ 1 0 4 と、A D 変換部 1 0 5 と、水平転送部（転送部）1 0 6 と、データ処理部 1 0 7 と、信号出力部 1 0 8 とを備えうる。制御部 1 0 2 は、C P U 1 0 1 から同期信号等の制御信号を受けて、該制御信号に従って動作しうる。画素アレイ 1 0 4 は、複数の行（n 行）および複数の列（m 列）を構成するように配置された複数の画素 P、および、複数の画素 P からのノイズ信号および光信号を出力するための複数の列信号線を有する。ここで、n、m は、任意の自然数である。画素 P ( x, y ) は、第 x 行、第 y 列に配置された画素 P を意味する。垂直走査部（駆動部）1 0 3 は、制御部 1 0 2 から提供される制御信号を受けて画素アレイ 1 0 4 を駆動しうる。より具体的には、垂直走査部 1 0 3 は、各画素 P からノイズ信号の次に光信号が出力されるように複数の画素 P を駆動しうる。光電変換装置 1 は、1 つの半導体基板に形成されうる。あるいは、光電変換装置 1 は積層された複数の半導体基板によって構成されうる。例えば、画素アレイ 1 0 4 が第 1 の半導体基板に配置されうる。そして、制御部 1 0 2 と、垂直走査部（駆動部）1 0 3 と、A D 変換部 1 0 5 と、水平転送部（転送部）1 0 6 と、データ処理部 1 0 7 と、信号出力部 1 0 8 とが第 2 の半導体基板に配置されうる。また、C P U 1 0 1 の一部または全部が光電変換装置 1 に搭載されてもよい。

#### 【 0 0 1 1 】

A D 変換部 1 0 5 は、画素アレイ 1 0 4 の複数の列信号線に出力されるノイズ信号をノイズデータに A D 変換し、次いで、該複数の列信号線に出力される光信号を光データに A D 変換する複数の A D 変換器を含みうる。水平転送部（転送部）1 0 6 は、A D 変換部 1 0 5 によって変換されたノイズデータをデータ処理部 1 0 7 に転送し、次いで、A D 変換部 1 0 5 によって変換された光データをデータ処理部 1 0 7 に転送しうる。データ処理部 1 0 7 は、データ保持部および演算部を含みうる。信号出力部 1 0 8 は、データ処理部 1 0 7 によって処理されたデータを出力しうる。

#### 【 0 0 1 2 】

図 2 には、画素アレイ 1 0 4 および A D 変換部 1 0 5 の構成例が示されている。図 2 に示された例では、画素アレイ 1 0 4 は、n 行および m 列の行列を構成するように配置された複数の画素 P ( 1, 1 ) ~ P ( n, m ) と、複数 ( m × I ) の列信号線 2 0 2 とを有する。ここで、I（第 1 数）は、2 以上の任意の自然数であり、第 1 実施形態では I = 6 である。第 1 実施形態において、1 つの列には、6 本の列信号線 2 0 2 が配置されている。具体的には、第 y 列の第 1 の列信号線 2 0 2 には画素 P ( 1 + 6 k, y ) が接続され、第 y 列の第 2 の列信号線 2 0 2 には画素 P ( 2 + 6 k, y ) が接続され、第 y 列の第 3 の列信号線 2 0 2 には画素 P ( 3 + 6 k, y ) が接続されている。また、第 y 列の第 4 の列信号線 2 0 2 には画素 P ( 4 + 6 k, y ) が接続され、第 y 列の第 5 の列信号線 2 0 2 には画素 P ( 5 + 6 k, y ) が接続され、第 y 列の第 6 の列信号線 2 0 2 には画素 P ( 6 + 6 k, y ) が接続されている。ここで、k は、0 ≤ k < n / 6 を満たす全ての自然数でありうる。

#### 【 0 0 1 3 】

A D 変換部 1 0 5 は、複数の A D 変換器 2 0 3 を含み、複数の A D 変換器 2 0 3 の数は、複数の列信号線 2 0 2 の数と同数でありうる。また、A D 変換部 1 0 5 は、複数の A D 変換器 2 0 3 の数と同数の保持部 2 0 4 を含みうる。複数の列信号線 2 0 2 には、定電流源（不図示）が接続されうる。また、1 つの列信号線 2 0 2 は、複数の A D 変換器 2 0 3 のうちの 1 つの A D 変換器 2 0 3 に接続される。各 A D 変換器 2 0 3 の出力は、対応する保持部 2 0 4 に提供され、該保持部 2 0 4 によって保持される。第 1 実施形態では、画素アレイ 1 0 4 の各列に対して、6 個の A D 変換器 2 0 3 と 6 個の保持部 2 0 4 が割り当て

られる。

【0014】

複数の列信号線 202 を相互に識別するために、第1列の6本の列信号線 202 は、 $c_1\_v1\#$  ( $\# : 1 \sim 6$ ) として示され、第m列の6本の列信号線 202 は、 $c_m\_v1\#$  と表して示されている。また、列信号線  $c_1\_v1\#$  に接続された画素 P の信号 (ノイズ信号、光信号) を A/D 変換器 203 によって A/D 変換したデータ (ノイズデータ、光データ) は、保持部 204 から  $adout\_c1\_v1\#$  として出力される。ここで、 $adout\_c1\_v1\#$  は、デジタルデータであり、複数  $bit$  で構成される。第1列の第1行の画素 P は、 $c_1\_v1_1$  に接続され、第1列の第2行の画素 P は、 $c_1\_v1_2$  に接続される。同様にして、各列において、画素 P は、6行周期で6本の列信号線 202 のいずれかに接続される。

【0015】

図3には、画素 P の構成例が示されている。画素 201 は、光電変換素子 (P D) 311 と、電荷転送部 312 と、フローティングディフュージョン FD と、リセット部 313 と、増幅部 314 と、行選択部 315 とを含みうる。光電変換素子 311 は、光電変換素子 311 に入射した光の量に応じた電荷を生成する素子であり、例えば、フォトダイオードでありうる。電荷転送部 312 は、光電変換素子 311 とフローティングディフュージョン FD との間に配置される。電荷転送部 312 は、垂直走査部 103 によって転送信号 P TX がアクティブル (ハイレベル) に駆動されることに応じて導通し、光電変換素子 311 の電荷をフローティングディフュージョン FD に転送する。

【0016】

リセット部 313 は、電源電圧 VDD とフローティングディフュージョン FD との間に配置される。リセット部 313 は、フローティングディフュージョン FD に電源電圧 VDD に応じた電圧を供給してフローティングディフュージョン FD の電圧をリセットする。リセット部 313 は、垂直走査部 103 によってリセット信号 P RES がアクティブル (ハイレベル) に駆動されることに応じて導通し、フローティングディフュージョン FD の電圧をリセットする。

【0017】

増幅部 314 のゲート端子にはフローティングディフュージョン FD が接続され、増幅部 314 のドレインおよびソースには、電源電圧 VDD および行選択部 315 がそれぞれ接続される。増幅部 314 は、前述の定電流源とともにソースフォロア回路を構成し、フローティングディフュージョン FD に転送された電荷に対応する電圧を列信号線 202 に出力する。行選択部 315 は、増幅部 314 の出力と列信号線 202 との間に配置される。行選択部 315 は、垂直走査部 103 によって選択された行の画素 P を選択状態にするためのトランジスタである。行選択部 315 は、垂直走査部 103 によって選択信号 P SEL がアクティブル (ハイレベル) に駆動されることによって導通し、増幅部 314 による列信号線 202 の駆動を可能にする。

【0018】

垂直走査部 103 は、選択された画像 P がノイズ信号を列信号線 202 に出力し、次いで、光信号を列信号線 202 に出力するように、該選択された画像 P を駆動する。ノイズ信号は、リセット部 313 によるフローティングディフュージョン FD の電圧のリセットが解除された後、電荷転送部 312 が導通される前に増幅部 314 によって列信号線 202 に出力される信号である。光信号は、光電変換素子 311 において光電変換によって発生した電荷が電荷転送部 312 によってフローティングディフュージョン FD に転送された状態で、増幅部 314 によって列信号線 202 に出力される信号である。光信号とノイズ信号との差分に相当する信号を得る関数サンプリング (CDS) によってフローティングディフュージョン FD のリセットノイズに相当するノイズを除去することができる。

【0019】

図4には、水平転送部 106 の構成例が示されている。水平転送部 106 は、例えば、複数のスリーステートバッファ 401 と、複数 (I本) の水平転送線 402 と、水平走査

10

20

30

40

50

部 4 0 3 を含みうる。A D 変換部 1 0 5 の複数の保持部 2 0 4 の出力 `a d o u t _ c M _ v 1 #` ( $M : 1 \sim m$ ) ( $# : 1 \sim 6$ ) は、対応するスリーステートバッファ 4 0 1 の入力端子に提供される。複数のスリーステートバッファ 4 0 1 のそれぞれの出力端子は、複数の水平転送線 4 0 2 のうち対応する水平転送線 4 0 2 に接続される。複数のスリーステートバッファ 4 0 1 の出力は、水平走査部 4 0 3 によって制御される。スリーステートバッファ 4 0 1 は、制御端子を有し、ハイまたはローレベルの入力信号と同一論理レベルの出力信号を出力する状態と、出力端子をハイインピーダンスに維持する状態とが該制御端子に与えられる制御信号によって切り替えられる。

#### 【 0 0 2 0 】

複数の水平転送線 4 0 2 は、水平転送線 `c h _ v 1 1`、`c h _ v 1 2`、`c h _ v 1 3`、`c h _ v 1 4`、`c h _ v 1 5`、`c h _ v 1 6` として相互に区別される。出力 `a d o u t _ c M _ v 1 1` は、対応するスリーステートバッファ 4 0 1 を介して水平転送線 `c h _ v 1 1` に伝達され、出力 `a d o u t _ c M _ v 1 2` は、対応するスリーステートバッファ 4 0 1 を介して `c h _ v 1 2` に伝達される。出力 `a d o u t _ c M _ v 1 3`、`a d o u t _ c M _ v 1 4`、`a d o u t _ c M _ v 1 5`、`a d o u t _ c M _ v 1 6` も、対応するスリーステートバッファ 4 0 1 を介して `c h _ v 1 3`、`c h _ v 1 4`、`c h _ v 1 5`、`c h _ v 1 6` に伝達される。

#### 【 0 0 2 1 】

図 5 には、データ処理部 1 0 7 の構成例が示されている。データ処理部 1 0 7 は、データ保持部 5 1 0 および演算部 5 2 0 を含みうる。データ保持部 5 1 0 の入力端子には、I 本 (即ち I チャネル) の水平転送線 `c h _ v 1 1`、`c h _ v 1 2`、`c h _ v 1 3`、`c h _ v 1 4`、`c h _ v 1 5`、`c h _ v 1 6` が接続されている。したがって、水平転送部 1 0 6 は、複数の A D 変換器 2 0 3 によって変換されたデータをデータ保持部 5 1 0 に転送するように動作しうる。より具体的には、水平転送部 1 0 6 は、複数の A D 変換器 2 0 3 によって変換されたノイズデータをデータ保持部 5 1 0 に転送し、次いで、複数の A D 変換器 2 0 3 によって変換された光データをデータ保持部 5 1 0 に転送するように動作しうる。

#### 【 0 0 2 2 】

データ保持部 5 1 0 は、I 行分の画素のデータ (ノイズデータまたは光データ) を順次に取り込んで保持する。また、データ保持部 5 1 0 は、J (第 2 数) 個のノイズデータと J (第 2 数) 個の光データとを並列に設けられた J 本のチャネルを通して出力する。ここで、J (第 2 数) は、I (第 1 数) と同じか、I (第 1 数) より小さい自然数であり、第 1 実施形態では  $J = 2$  である。データ保持部 5 1 0 は、I (6) 個のノイズデータを取り込んで保持するノイズデータ記憶部 5 0 2 と、I (6) 個の光データを取り込んで保持する光データ記憶部 5 0 1 とを含みうる。ノイズデータ記憶部 5 0 2 は、J (2) 個のノイズデータを出力し、これと並行して、光データ記憶部 5 0 1 は、J (2) 個の光データを出力する。

#### 【 0 0 2 3 】

ここで、あるデバイス (例えば、ノイズデータ記憶部 5 0 2) がデータを取り込んで保持する動作は、該デバイスに対するデータの書込動作として理解することができる。また、あるデバイス (例えば、ノイズデータ記憶部 5 0 2) がデータを出力する動作は、該デバイスからのデータの読出動作として理解することができる。データの書込動作および読出動作は、制御部 1 0 2 が発生する書込信号 (`w r i t e _ e n`) および読出信号 (`r e a d _ e n`) によって制御されうる。

#### 【 0 0 2 4 】

演算部 5 2 0 は、第 1 データ演算部 5 0 3 と、第 2 データ演算部 5 0 4 とを含みうる。第 1 データ演算部 5 0 3 および第 2 データ演算部 5 0 4 は、光データとノイズデータとの差分を演算しうる。ノイズデータ記憶部 5 0 2 は、2 つの出力ポート N 1 3 5、N 2 4 6 を有し、出力ポート N 1 3 5 は、第 1 データ演算部 5 0 3 の入力ポート N i n に接続され、出力ポート N 2 4 6 は、第 2 データ演算部 5 0 4 の入力ポート N i n に接続されている。光データ記憶部 5 0 1 は、2 つの出力ポート S 1 3 5、S 2 4 6 を有し、出力ポート S

10

20

30

40

50

135は、第1データ演算部503の入力ポートS<sub>in</sub>に接続され、出力ポートS246は、第2データ演算部504の入力ポートS<sub>in</sub>に接続されている。

【0025】

出力ポートN135には、第1、第3、第5チャネルの水平転送線c<sub>h</sub>\_v11、c<sub>h</sub>\_v13、c<sub>h</sub>\_v15を介してノイズデータ記憶部502に提供された第1、第3、第5チャネルのノイズデータが出力される。出力ポートN246には、第2、第4、第6チャネルの水平転送線c<sub>h</sub>\_v12、c<sub>h</sub>\_v14、c<sub>h</sub>\_v16を介してノイズデータ記憶部502に提供された第2、第4、第6ノイズデータが出力される。出力ポートS135には、第1、第3、第5チャネルの水平転送線c<sub>h</sub>\_v11、c<sub>h</sub>\_v13、c<sub>h</sub>\_v15を介して光データ記憶部501に提供された第1、第3、第5チャネルの光データが出力される。出力ポートS246には、第2、第4、第6チャネルの水平転送線c<sub>h</sub>\_v12、c<sub>h</sub>\_v14、c<sub>h</sub>\_v16を介して光データ記憶部501に提供された第2、第4、第6チャネルの光データが出力される。

【0026】

I本の水平転送線c<sub>h</sub>\_v1# (# : 1 ~ 6)は、ノイズデータ記憶部502および光データ記憶部501の双方に供給されうる。第1データ演算部503は、入力ポートS<sub>in</sub>に提供された第1、第3、第5チャネルの光データと入力ポートN<sub>in</sub>に提供された第1、第3、第5チャネルのノイズデータとのそれぞれの差分を演算する。そして、第1データ演算部503は、第1、第3、第5チャネルの演算結果を出力ポートS<sub>Noout</sub>に出力する。第2データ演算部504は、入力ポートS<sub>in</sub>に入力された第2、第4、第6チャネルの光データと入力ポートN<sub>in</sub>に入力された第2、第4、第6チャネルのノイズデータとのそれぞれの差分を演算する。そして、第2データ演算部504は、第2、第4、第6チャネルの演算結果を出力ポートS<sub>Noout</sub>に出力する。

【0027】

データ演算部503、504は、例えば、式1に示す演算を行うように構成されるが、他の演算を行うように構成されてもよい。

【0028】

$$S_{Noout} = S_{in} - N_{in} \quad \dots \text{式1}$$

図6には、図5に示されたノイズデータ記憶部502の構成例が示されている。ノイズデータ記憶部502は、例えば、A記憶部(第1記憶部)601と、B記憶部(第2記憶部)602と、セレクタ603とを含みうる。A記憶部601およびB記憶部602は、それぞれ、I行分の画素(第1数の行の画素)、つまり、(I × m)個の画素のデータを保持することができる。ノイズデータ記憶部502の入力端子には、水平転送線c<sub>h</sub>\_v1# (# : 1 ~ 6)が接続されていて、水平転送線c<sub>h</sub>\_v1# (# : 1 ~ 6)は、A記憶部601およびB記憶部602の双方の入力端子に接続されている。A記憶部601の出力端子から出力される出力信号N#A (# : 1 ~ 6)およびB記憶部602の出力端子から出力される出力信号N#B (# : 1 ~ 6)は、セレクタ603に供給される。

【0029】

セレクタ603は、出力ポートN135、N246を有する。セレクタ603は、出力ポートN135に対しては、N1A、N3A、N5A、N1B、N3B、N5Bのいずれかを選択して出力し、出力ポートN246に対しては、N2A、N4A、N6A、N2B、N4B、N6Bのいずれかを選択して出力する。

【0030】

A記憶部601およびB記憶部602は、例えば、互いに独立してアクセス可能な別個のSRAMで構成されうる。A記憶部601およびB記憶部602は、例えば、フリップフロップのような記憶素子の集合体で構成されてもよいし、他の記憶素子の集合体で構成されてもよい。光データ記憶部501は、ノイズデータ記憶部502と同様の構成を有しうる。光データ記憶部501は、例えば、A記憶部601と同様のA記憶部と、B記憶部602と同様のB記憶部と、セレクタ603とを同様のセレクタとを含みうる。

【0031】

10

20

30

40

50

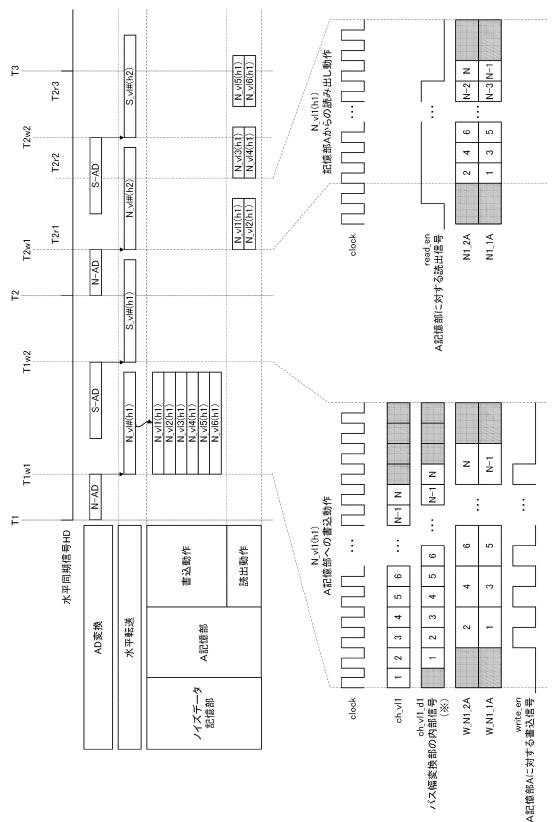

以下、第1実施形態の光電変換装置1の動作方法を説明する。図7には、第1実施形態の光電変換装置1の動作方法が示されている。図7において、「A D変換」はA D変換部105の動作、「水平転送」は水平転送部106の動作、「ノイズデータ記憶部」はノイズデータ記憶部502の動作、「光データ記憶部」は光データ記憶部501の動作を示している。第1実施形態の光電変換装置1は、6行分の画素のノイズ信号を同時にA D変換し、次いで、該6行分の画素の光信号を同時にA D変換する。また、第1実施形態の光電変換装置1は、2行の画素のデータ(光データとノイズデータとの差分)を並列に、かつ、各行の画素のデータについては1画素ずつ順次に出力する。

#### 【0032】

まず、第1行から第6行かつ第1列から第m列の画素Pのノイズ信号がA D変換部105でA D変換されてノイズデータが生成され、そのノイズデータがデータ処理部107のノイズデータ記憶部502のA記憶部601に書き込まれる動作について説明する。時刻T1において、C P U 1 0 1は、制御部102に対して水平同期信号H Dを出力する。時刻T1から時刻T1w1において、A D変換部105の複数( $m \times I$ )のA D変換器203は、制御部102による制御の下で、第1行から第6行かつ第1列から第m列の画素Pのノイズ信号を同時にA D変換してノイズデータを生成する。時刻T1w1において、複数( $m \times I$ )のA D変換器203によって生成された複数( $m \times I$ )のノイズデータが複数( $m \times I$ )の保持部204に一括転送される。ここで、第1行のノイズデータ群をN\_v11(h1)、第2行のノイズデータ群をN\_v12(h1)、・・・、第6行のノイズデータ群をN\_v16(h1)とする。

#### 【0033】

時刻T1w1から時刻T1w2において、複数の保持部204によって保持されているノイズデータ群N\_v1#(h1)(# : 1 ~ 6)は、水平転送部106を介してデータ処理部107に転送される。ここで、6行のノイズデータ群は、並列に、かつ、各行の画素のノイズデータ群が1画素ずつ順次に、データ処理部107に転送される。データ処理部107に転送されたノイズデータ群N\_v11(h1)は、制御部102が発生する書込信号w r i t e \_ e nおよび書込クロックc l o c kに従ってノイズデータ記憶部502のA記憶部601に順次に書き込まれる。A記憶部601に対するノイズデータ群N\_v11(h1)の書込動作については、図8の左下のタイミングチャートに示されている。

#### 【0034】

以下、第1行から第6行かつ第1列から第m列の画素Pの光信号がA D変換部105でA D変換されて光データが生成され、その光データがデータ処理部107の光データ記憶部501のA記憶部に書き込まれる動作について説明する。時刻T1w2から時刻T1w3において、A D変換部105の複数( $m \times I$ )のA D変換器203は、制御部102による制御の下で、第1行から第6行かつ第1列から第m列の画素Pの光信号を同時にA D変換して光データを生成する。時刻T1w3において、複数( $m \times I$ )のA D変換器203によって生成された複数( $m \times I$ )のノイズデータが複数( $m \times I$ )の保持部204に一括転送される。ここで、第1行の光データ群をS\_v11(h1)、第2行の光データ群をS\_v12(h1)、・・・、第6行の光データ群をS\_v16(h1)とする。

#### 【0035】

時刻T1w3から時刻T1w4において、複数の保持部204によって保持されている光データ群S\_v1#(h1)(# : 1 ~ 6)は、水平転送部106を介してデータ処理部107に転送される。ここで、6行の光データ群は、並列に、かつ、各行の画素のノイズデータ群が1画素ずつ順次に、データ処理部107に転送される。データ処理部107に転送された光データ群は、制御部102が発生する書込信号w r i t e \_ e nおよび書込クロックc l o c kに従って光データ記憶部501のA記憶部に順次に書き込まれる。

#### 【0036】

以下、第1行から第6行かつ第1列から第m列の画素Pのノイズデータ、光データをデータ処理部107のノイズデータ記憶部502(A記憶部601)、光データ記憶部501(A記憶部)から読み出す動作について説明する。時刻T2において、C P U 1 0 1は

10

20

30

40

50

、制御部 102 に対して水平同期信号 H D を出力する。時刻 T 2 r 1 から時刻 T 2 r 2 において、ノイズデータ記憶部 502 の A 記憶部 601 から第 1 行のノイズデータ群 N\_v11 (h1) と第 2 行のノイズデータ群 N\_v12 (h1) が並行して、各行について 1 画素ずつ順次に、読み出される。また、これと並行して、時刻 T 2 r 1 から時刻 T 2 r 2 において、光データ記憶部 501 の A 記憶部から第 1 行の光データ群 S\_v11 (h1) と第 2 行の光データ群 S\_v12 (h1) が並行して、各行について 1 画素ずつ順次に、読み出される。また、時刻 T 2 r 1 から時刻 T 2 r 2 において、第 1 行および第 2 行のそれについて、1 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。A 記憶部 601 からのノイズデータ群 N\_v11 (h1) の読み出動作については、図 8 の右下のタイミングチャートに示されている。

#### 【0037】

上記の動作と同様にして、時刻 T 2 r 2 から時刻 T 2 r 3 において、第 3 行と第 4 行のそれについて、1 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。また、時刻 T 2 r 3 から時刻 T 3 r 1 において、第 5 行と第 6 行のそれについて、1 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。

#### 【0038】

以上のようにして、第 1 行から第 6 行の画素のノイズ信号が同時に A D 変換され、次いで、第 1 行から第 6 行の画素の光信号が同時に A D 変換される。また、2 つの行の画素のデータ（光データとノイズデータとの差分）は、並列に、かつ、各行の画素のデータについては 1 画素ずつ順次に出力される。

#### 【0039】

以下、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P のノイズ信号が A D 変換部 105 で A D 変換されてノイズデータが生成され、そのノイズデータがデータ処理部 107 のノイズデータ記憶部 502 の B 記憶部 602 に書き込まれる動作について説明する。時刻 T 2 から時刻 T 2 w 1 において、A D 変換部 105 の複数 (m × I) の A D 変換器 203 は、制御部 102 による制御の下で、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P のノイズ信号を同時に A D 変換してノイズデータを生成する。時刻 T 2 w 1 において、複数 (m × I) の A D 変換器 203 によって生成された複数 (m × I) のノイズデータが複数 (m × I) の保持部 204 に一括転送される。ここで、第 7 行のノイズデータ群を N\_v11 (h2) 、第 8 行のノイズデータ群を N\_v12 (h2) 、 … 、第 12 行のノイズデータ群を N\_v16 (h2) とする。

#### 【0040】

時刻 T 2 w 1 から時刻 T 2 w 2 において、複数の保持部 204 によって保持されているノイズデータ群 N\_v1# (h2) (# : 1 ~ 6) は、水平転送部 106 を介してデータ処理部 107 に転送される。ここで、6 行のノイズデータ群は、並列に、かつ、各行の画素のノイズデータ群が 1 画素ずつ順次に、データ処理部 107 に転送される。データ処理部 107 に転送されたノイズデータ群 N\_v1# (h2) (# : 1 ~ 6) は、制御部 102 が発生する書込信号 w\_r\_i\_t\_e\_e\_n および書込クロック c\_l\_o\_c\_k に従ってノイズデータ記憶部 502 の B 記憶部 602 に書き込まれる。

#### 【0041】

以下、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P の光信号が A D 変換部 105 で A D 変換されて光データが生成され、その光データがデータ処理部 107 の光データ記憶部 501 の B 記憶部に書き込まれる動作について説明する。時刻 T 2 w 2 から時刻 T 2 w 3 において、A D 変換部 105 の複数 (m × I) の A D 変換器 203 は、制御部 102 による制御の下で、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P の光信号を同時に A D 変換して光データを生成する。時刻 T 2 w 3 において、複数 (m × I) の A D 変換器 203 によって生成された複数 (m × I) のノイズデータが複数 (m × I) の保持部 204 に一括転送される。ここで、第 7 行のデータ群を S\_v11 (h2) 、8 行目のデータ群を S\_v12 (h2) 、 … 、第 12 行のデータ群を S\_v16 (h2) とする。

10

20

30

40

50

## 【0042】

時刻 T<sub>2w3</sub> から時刻 T<sub>2w4</sub> において、複数の保持部 204 によって保持されている光データ群 S\_v1#(h2) (#: 1 ~ 6) は、水平転送部 106 を介してデータ処理部 107 に転送される。ここで、6 行の光データ群は、並列に、かつ、各行の画素の光データ群が 1 画素ずつ順次に、データ処理部 107 に転送される。データ処理部 107 に転送された光データ群 S\_v1#(h2) (#: 1 ~ 6) は、制御部 102 が発生する書込信号 write\_en および書込クロック clock に従って光データ記憶部 501 の B 記憶部に書き込まれる。

## 【0043】

以下、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P のノイズデータ、光データを、データ処理部 107 のノイズデータ記憶部 502 (B 記憶部 602)、光データ記憶部 501 (B 記憶部) から読み出す動作について説明する。時刻 T<sub>3</sub> において、CPU 101 は、制御部 102 に対して水平同期信号 HD を出力する。時刻 T<sub>3r1</sub> から時刻 T<sub>3r2</sub> において、ノイズデータ記憶部 502 の B 記憶部 602 から第 7 行のノイズデータ群 N\_v11(h2) と第 8 行のノイズデータ群 N\_v12(h2) が並行して、各行について 1 画素ずつ順次に、読み出される。また、これと並行して、時刻 T<sub>3r1</sub> から時刻 T<sub>3r2</sub> において、光データ記憶部 501 の B 記憶部から第 7 行の光データ群 S\_v11(h2) と第 8 行の光データ群 S\_v12(h2) が並行して、各行について 1 画素ずつ順次に、読み出される。また、時刻 T<sub>3r1</sub> から時刻 T<sub>3r2</sub> において、第 7 行および第 8 行のそれについて、1 画素ずつ行 1 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。

10

20

## 【0044】

上記の動作と同様にして、時刻 T<sub>3r2</sub> から時刻 T<sub>3r3</sub> において、第 9 行と第 10 行のそれについて、1 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。また、時刻 T<sub>3r3</sub> から時刻 T<sub>3r1</sub> において、第 11 行と第 12 行のそれについて、1 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。以降は、A 記憶部を用いた動作と B 記憶部を用いた動作とが交互かつ並行して実施される。

## 【0045】

以上のように、第 1 実施形態の光電変換装置 1 では、I 行分の画素のノイズ信号を同時に A/D 変換し、次いで、該 I 行分の画素の光信号を同時に A/D 変換する。これにより、A/D 変換部 105 に要求される機能を単純化することができる。また、第 1 実施形態の光電変換装置 1 では、J 行の画素のデータ (光データとノイズデータとの差分) を並列に設けられた J 本のチャネルを通して並列に、かつ、各行の画素のデータについては 1 画素ずつ順次に出力してもよい。このような構成は、データ処理部 107 の回路規模を削減するために有利である。ここでは、I = J である。

30

## 【0046】

第 1 実施形態では、各行の画素データは 1 画素 / 1 clock のレートで水平転送されてデータ処理部 107 に供給され、各行の画素データは 1 画素 / 1 clock のレートでデータ処理部 107 から出力される。第 1 実施形態では、データ処理部 107 の記憶部へのアクセスが単純である。

40

## 【0047】

第 2 実施形態では、各行の画素データは 1 画素 / 1 clock のレートで水平転送されてデータ処理部 107 に供給され、2 画素 / 1 clock のレートでデータ処理部 107 から出力される。以下、図 9、図 10、図 11、図 12 を参照しながら第 2 実施形態の光電変換装置 1 について説明する。第 2 実施形態として言及しない事項は、第 1 実施形態に従う。第 2 実施形態の光電変換装置 1 は、画素アレイ 104、A/D 変換部 105 の構成 (図 2)、画素 201 の構成 (図 3)、水平転送部 106 の構成 (図 4) は、第 1 実施形態と同様でありうる。

## 【0048】

50

図9には、第2実施形態のデータ処理部107の構成例が示されている。データ処理部107は、データ保持部510および演算部520を含みうる。データ保持部510の入力端子には、I本(即ちIチャネル)の水平転送線ch\_v11、ch\_v12、ch\_v13、ch\_v14、ch\_v15、ch\_v16が接続されている。より具体的には、水平転送部106は、複数のAD変換器203によって変換されたノイズデータをデータ保持部510に転送し、次いで、複数のAD変換器203によって変換された光データをデータ保持部510に転送するように動作しうる。

#### 【0049】

データ保持部510は、I行分のデータ(ノイズデータまたは光データ)を取り込んで保持する。また、データ保持部510は、J(第2数)個のノイズデータとJ(第2数)個の光データとを出力する。ここで、J(第2数)は、I(第1数)と同じか、I(第1数)より小さい自然数である。第2実施形態においても、I=6、J=2である。データ保持部510は、I行分の画素と同数のノイズデータを取り込んで保持するノイズデータ記憶部902と、I行分の画素と同数のノイズデータを取り込んで保持するノイズデータ記憶部906とを含む。また、データ保持部510は、I行分の画素と同数の光データを取り込んで保持する光データ記憶部901と、I行分の画素と同数の光データを取り込んで保持する光データ記憶部905とを含む。演算部520は、第1データ演算部903と、第2データ演算部904と、第3データ演算部907と、第4データ演算部908とを含みうる。第1データ演算部903、第2データ演算部904、第3データ演算部907および第4データ演算部908は、光データとノイズデータとの差分を演算する。

#### 【0050】

データ処理部107は、第1、第2、第3、第4、第5、第6チャネルの水平転送線ch\_v11、ch\_v12、ch\_v13、ch\_v14、ch\_v15、ch\_v16が接続される入力端子を有する。第1、第3、第5チャネルの水平転送線ch\_v11、ch\_v13、ch\_v15は、光データ記憶部901およびノイズデータ記憶部902の入力端子に接続されている。

#### 【0051】

光データ記憶部901は、出力ポートS135\_1、S135\_2を有し、出力ポートS135\_1は、第1データ演算部903の入力ポートSinに接続され、出力ポートS135\_2は、第2データ演算部904の入力ポートSinに接続されている。出力ポートS135\_1、S135\_2には、第1、第3、第5チャネルの水平転送線ch\_v11、ch\_v13、ch\_v15を介して光データ記憶部901に提供された第1、第3、第5チャネルの光データが出力される。ノイズデータ記憶部902は、出力ポートN135\_1、N135\_2を有し、出力ポートN135\_1は、第1データ演算部903の入力ポートSinに接続され、出力ポートN135\_2は、第2データ演算部904の入力ポートSinに接続されている。出力ポートN135\_1、N135\_2には、第1、第3、第5チャネルの水平転送線ch\_v11、ch\_v13、ch\_v15を介してノイズデータ記憶部902に提供された第1、第3、第5チャネルのノイズデータが出力される。

#### 【0052】

第1データ演算部903は、入力ポートSinに出力ポートS135\_1から供給される光データと入力ポートNinに出力ポートN135\_1から供給されるノイズデータとの差分を演算し、演算結果を出力ポートSN135\_1に出力する。第2データ演算部904は、入力ポートSinに出力ポートS135\_2から供給される光データと入力ポートNinに出力ポートN135\_2から供給されるノイズデータとの差分を演算し、演算結果を出力ポートSN135\_2に出力する。

#### 【0053】

光データ記憶部905は、出力ポートS246\_1、S246\_2を有し、出力ポートS246\_1は、第3データ演算部907の入力ポートSinに接続され、出力ポートS246\_2は、第2データ演算部908の入力ポートSinに接続されている。出力ポートS246\_1は、第3データ演算部907の入力ポートSinに接続され、出力ポートS246\_2は、第2データ演算部908の入力ポートSinに接続されている。

10

20

30

40

50

ト S 2 4 6 \_ 1、S 2 4 6 \_ 2 には、第 2、第 4、第 6 チャネルの水平転送線 c h \_ v 1 2、c h \_ v 1 4、c h \_ v 1 6 を介して光データ記憶部 9 0 5 に提供された第 2、第 4、第 6 チャネルの光データが出力される。ノイズデータ記憶部 9 0 6 は、出力ポート N 2 4 6 \_ 1、N 2 4 6 \_ 2 を有し、出力ポート N 2 4 6 \_ 1 は、第 3 データ演算部 9 0 7 の入力ポート S i n に接続され、出力ポート N 2 4 6 \_ 2 は、第 4 データ演算部 9 0 8 の入力ポート S i n に接続されている。出力ポート N 2 4 6 \_ 1、N 2 4 6 \_ 2 には、第 2、第 4、第 6 チャネルの水平転送線 c h \_ v 1 2、c h \_ v 1 4、c h \_ v 1 6 を介してノイズデータ記憶部 9 0 6 に提供された第 2、第 4、第 6 チャネルのノイズデータが出力される。

#### 【 0 0 5 4 】

第 1 データ演算部 9 0 3 は、入力ポート S i n に出力ポート S 1 3 5 \_ 1 から供給される光データと入力ポート N i n に出力ポート N 1 3 5 \_ 1 から供給されるノイズデータとの差分を演算し、演算結果を出力ポート S N 1 3 5 \_ 1 に出力する。第 2 データ演算部 9 0 4 は、入力ポート S i n に出力ポート S 1 3 5 \_ 2 から供給される光データと入力ポート N i n に出力ポート N 1 3 5 \_ 2 から供給されるノイズデータとの差分を演算し、演算結果を出力ポート S N 1 3 5 \_ 2 に出力する。

#### 【 0 0 5 5 】

第 3 データ演算部 9 0 7 は、入力ポート S i n に出力ポート S 2 4 6 \_ 1 から供給される光データと入力ポート N i n に出力ポート N 2 4 6 \_ 1 から供給されるノイズデータとの差分を演算し、演算結果を出力ポート S N 2 4 6 \_ 1 に出力する。第 4 データ演算部 9 0 8 は入力ポート S i n に出力ポート S 2 4 6 \_ 2 から供給される光データと入力ポート N i n に出力ポート N 2 4 6 \_ 2 から供給されるノイズデータとの差分を演算し、演算結果を出力ポート S N 4 6 \_ 2 に出力する。

#### 【 0 0 5 6 】

データ演算部 9 0 3、9 0 4、9 0 5、9 0 6 は、例えば、式 1 に示す演算を行うように構成されるが、他の演算を行うように構成されてもよい。

#### 【 0 0 5 7 】

$$S N o u t = S i n - N i n \quad \dots \text{式 1}$$

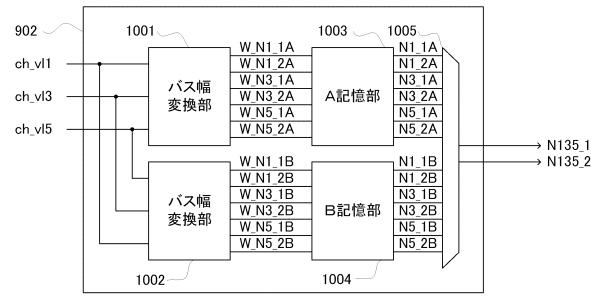

図 10 は、図 9 に示されたノイズデータ記憶部 9 0 2 の構成例が示されている。ノイズデータ記憶部 9 0 2 は、バス幅変換部 1 0 0 1、1 0 0 2 と、A 記憶部 1 0 0 3 と、B 記憶部 1 0 0 4 と、セレクタ 1 0 0 5 とを含みうる。ノイズデータ記憶部 9 0 2 の入力端子には、水平転送線 c h \_ v 1 # (# : 1、3、5) が接続されていて、水平転送線 c h \_ v 1 # (# : 1、3、5) は、バス幅変換部 1 0 0 1、1 0 0 2 の双方の入力端子に接続されている。

#### 【 0 0 5 8 】

バス幅変換部 1 0 0 1 は、I (第 1 数) の半分のノイズデータを 2 回受けて I (第 1 数) のノイズデータとして出力する。同様に、バス幅変換部 1 0 0 2 は、I (第 1 数) の半分のノイズデータを 2 回受けて I (第 1 数) のノイズデータとして出力する。バス幅変換部 1 0 0 1 の出力端子から出力される出力信号 W\_N # \_ 1 A、W\_N # \_ 2 A (# : 1、3、5) は、A 記憶部 1 0 0 3 に供給される。バス幅変換部 1 0 0 2 の出力端子から出力される出力信号 W\_N # \_ 1 B、W\_N # \_ 2 B (# : 1、3、5) は、B 記憶部 1 0 0 4 に供給される。

#### 【 0 0 5 9 】

A 記憶部 1 0 0 3 の出力端子から出力される出力信号 N # \_ 1 A、N # \_ 2 A (# : 1、3、5) と、B 記憶部 1 0 0 4 の出力端子から出力される出力信号 N # \_ 1 B、N # \_ 2 B (# : 1、3、5) は、セレクタ 1 0 0 5 に供給される。セレクタ 1 0 0 5 は、出力ポート N 1 3 5 \_ 1、N 1 3 5 \_ 2 を有する。セレクタ 1 0 0 5 は、出力ポート N 1 3 5 \_ 1 に対しては、N 1 \_ 1 A、N 3 \_ 1 A、N 5 \_ 1 A、N 1 \_ 1 B、N 3 \_ 1 B、N 5 \_ 1 B のいずれかを選択して出力する。また、セレクタ 1 0 0 5 は、出力ポート N 1 3 5 \_ 2 に対しては、N 1 \_ 2 A、N 3 \_ 2 A、N 5 \_ 2 A、N 1 \_ 2 B、N 3 \_ 2 B、N 5 \_ 2 B のいずれかを選択して出力する。

10

20

30

40

50

—2Bのいずれかを選択して出力する。

【0060】

A記憶部1003およびB記憶部1004は、例えば、互いに独立してアクセス可能別個のSRAMで構成されうる。A記憶部1003およびB記憶部1004は、例えば、フリップフロップのような記憶素子の集合体で構成されてもよいし、他の記憶素子の集合体で構成されてもよい。光データ記憶部901、905、ノイズデータ記憶部906は、ノイズデータ記憶部902と同様の構成を含みうる。ここで、光データ記憶部901、905に適用されるバス幅変換部は、I(第1数)の半分の光データを2回受けてI(第1数)の光データとして出力する。

【0061】

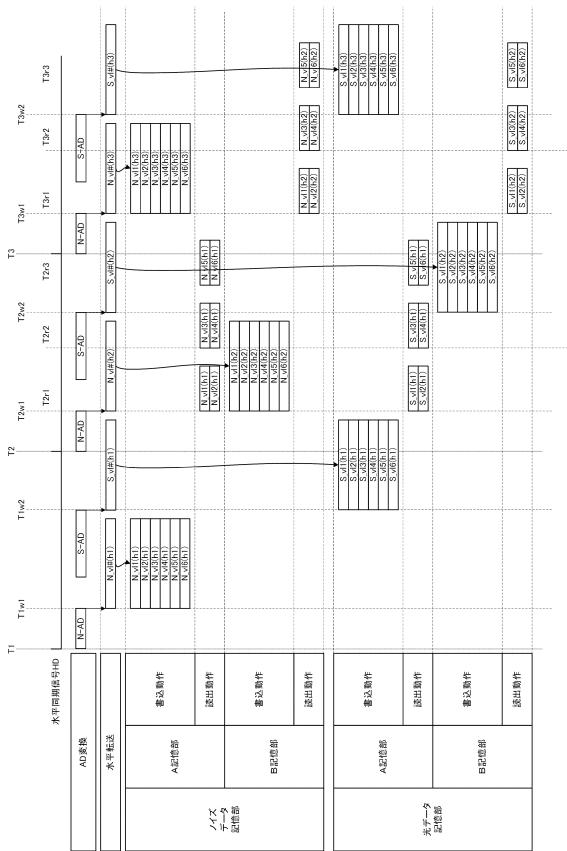

以下、第2実施形態の光電変換装置1の動作方法を説明する。図11には、第2実施形態の光電変換装置1の動作方法が示されている。図11において、「AD変換」はAD変換部105の動作、「水平転送」は水平転送部106の動作、「ノイズデータ記憶部」はノイズデータ記憶部902、906の動作、「光データ記憶部」は光データ記憶部901、905の動作を示している。図11において、「ノイズデータ記憶部」の「A記憶部」は、ノイズデータ記憶部902、906のA記憶部の動作をまとめて示し、「ノイズデータ記憶部」の「B記憶部」は、ノイズデータ記憶部902、906のB記憶部の動作をまとめて示している。図11において、「光データ記憶部」の「A記憶部」は、光データ記憶部901、905のA記憶部の動作をまとめて示し、「光データ記憶部」の「B記憶部」は、光データ記憶部901、905のB記憶部の動作をまとめて示している。第2実施形態の光電変換装置1は、6行分の画素のノイズ信号を同時にAD変換し、次いで、該6行分の画素の光信号を同時にAD変換する。また、第2実施形態の光電変換装置1は、2行の画素のデータ(光データとノイズデータとの差分)を並列に設けられた2本のチャネルを通して並列に、かつ、各行の画素のデータについては2画素ずつ順次に出力する。

10

【0062】

まず、第1行目から第6行目まで第1列から第m列の画素Pのノイズ信号がAD変換されてノイズデータが生成され、そのノイズデータがタータ処理部107のA記憶部に書き込まれる動作について説明する。時刻T1において、CPU101は、制御部102に対して水平同期信号HDを出力する。時刻T1から時刻T1w1において、AD変換部105の複数( $m \times I$ )のAD変換器203は、制御部102による制御の下で、第1行目から第6行目まで第1列から第m列の画素Pのノイズ信号を同時にAD変換してノイズデータを生成する。時刻T1w1において、複数( $m \times I$ )のAD変換器203によって生成された複数( $m \times I$ )のノイズデータが複数( $m \times I$ )の保持部204に一括転送される。ここで、第1行のノイズデータ群をN\_v11(h1)、第2行のノイズデータ群をN\_v12(h1)、・・・、第6行のノイズデータ群をN\_v16(h1)とする。

20

【0063】

時刻T1w1から時刻T1w2において、複数の保持部204によって保持されているノイズデータ群N\_v1#(h1)(# : 1 ~ 6)は、水平転送部106を介してデータ処理部107に転送される。ノイズデータ群N\_v1#(h1)(# : 1 ~ 6)は、ノイズデータ記憶部902、906のA記憶部Aに書き込まれる。ノイズデータ記憶部902のA記憶部に対するノイズデータ群N\_v11(h1)の書き込み動作については、図12左下のタイミングチャートに示されている。ch\_v1は、バス幅変換部内で1段分のバッファリング(ch\_v11\_d1)がされた後、クロックclockの2サイクルに1回のレートで2画素ずつA記憶部に書き込まれる。

30

【0064】

以下、第1行から第6行目まで第1列から第m列の画素Pの光信号がAD変換部105でAD変換されて光データが生成され、その光データがデータ処理部107の光データ記憶部901、905のA記憶部に書き込まれる動作について説明する。時刻T1w1から時刻T1w2において、AD変換部105の複数( $m \times I$ )のAD変換器203は、制御部102による制御の下で、第1行から第6行目まで第1列から第m列の画素Pの光信号を同

40

50

時に A/D 变換して光データを生成する。時刻 T<sub>1 w 2</sub>において、複数 (m × I) の A/D 变換器 203 によって生成された複数 (m × I) のノイズデータが複数 (m × I) の保持部 204 に一括転送される。ここで、第 1 行の光データ群を S\_v11 (h1)、第 2 行の光データ群を S\_v12 (h1)、…、第 6 行の光データ群を S\_v16 (h1) とする。

#### 【0065】

時刻 T<sub>1 w 2</sub> から時刻 T<sub>2 w 1</sub> において、複数の保持部 204 によって保持されている光データ群 S\_v1# (h1) (# : 1 ~ 6) は、水平転送部 106 を介してデータ処理部 107 に転送される。光データ群 S\_v1# (h1) (# : 1 ~ 6) は、光データ記憶部 901、905 の A 記憶部に書き込まれる。光データ記憶部 901、905 の A 記憶部に対する光データ群 S\_v1# (h1) (# : 1 ~ 6) の書き込み動作は、クロック cloc の 2 サイクルに 1 回のレートで行われる。

10

#### 【0066】

以下、第 1 行から第 6 行かつ第 1 列から第 m 列の画素 P のノイズデータ、光データをデータ処理部 107 のノイズデータ記憶部 902、906 の A 記憶部、光データ記憶部 901、905 の A 記憶部から読み出す動作について説明する。時刻 T<sub>2</sub> において、CPU101 は、制御部 102 に対して水平同期信号 HD を出力する。時刻 T<sub>2 r 1</sub> から時刻 T<sub>2 r 2</sub> において、ノイズデータ記憶部 902、906 の A 記憶部から第 1 行のノイズデータ群 N\_v11 (h1) と第 2 行のノイズデータ群 N\_v12 (h1) が並列して、各行について 2 画素ずつ読み出される。また、これと並行して、時刻 T<sub>2 r 1</sub> から時刻 T<sub>2 r 2</sub> において、光データ記憶部 901、905 の A 記憶部から第 1 行の光データ群 S\_v11 (h1) と第 2 行の光データ群 S\_v12 (h1) が並列して、各行について 2 画素ずつ読み出される。また、時刻 T<sub>2 r 1</sub> から時刻 T<sub>2 r 2</sub> において、第 1 行および第 2 行のそれぞれについて、各行について 2 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。ノイズデータ記憶部 902、906 の A 記憶部からのノイズデータ群 N\_v11 (h1) の読み出動作については、図 12 の右下のタイミングチャートに示されている。

20

#### 【0067】

上記の動作と同様にして、時刻 T<sub>2 r 2</sub> から時刻 T<sub>2 r 3</sub> において、第 3 行と第 4 行のそれぞれについて、2 行のそれぞれについて、2 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。また、時刻 T<sub>2 r 3</sub> から時刻 T<sub>3 r 1</sub> において、第 5 行と第 6 行のそれぞれについて、2 行のそれぞれについて、2 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。

30

#### 【0068】

以上のようにして、第 1 行から第 6 行の画素のノイズ信号が同時に A/D 变換され、次いで、第 1 行から第 6 行の画素の光信号が同時に A/D 变換される。また、2 つの行の画素のデータ (光データとノイズデータとの差分) は並列に、かつ、各行の画素のデータについては 2 画素ずつ順次に出力される。

#### 【0069】

以下、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P のノイズ信号が A/D 变換部 105 で A/D 变換されてノイズデータが生成され、そのノイズデータがデータ処理部 107 のノイズデータ記憶部 902、906 の B 記憶部に書き込まれる動作について説明する。時刻 T<sub>2</sub> から時刻 T<sub>2 w 1</sub> において、A/D 变換部 105 の複数 (m × I) の A/D 变換器 203 は、制御部 102 による制御の下で、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P のノイズ信号を同時に A/D 变換してノイズデータを生成する。時刻 T<sub>2 w 1</sub> において、複数 (m × I) の A/D 变換器 203 によって生成された複数 (m × I) のノイズデータが複数 (m × I) の保持部 204 に一括転送される。ここで、第 7 行のノイズデータ群を N\_v11 (h2)、第 8 行のノイズデータ群を N\_v12 (h2)、…、第 12 行のノイズデータ群を N\_v16 (h2) とする。

40

50

## 【0070】

時刻 T<sub>2w1</sub> から時刻 T<sub>2w2</sub> において、複数の保持部 204 によって保持されているノイズデータ群 N\_v1#(h2) (# : 1 ~ 6) は、水平転送部 106 を介してデータ処理部 107 に 6 行並列で順次に転送される。データ処理部 107 に転送されたノイズデータ群 N\_v1#(h2) (# : 1 ~ 6) は、制御部 102 が発生する書込信号 w\_r\_i\_t\_e\_e\_n および書込クロック c10ck に従ってノイズデータ記憶部 902、906 の B 記憶部に書き込まれる。ノイズデータ記憶部 902、906 の B 記憶部に対するノイズデータ群 N\_v1#(h2) (# : 1 ~ 6) の書込動作は、クロック c10ck の 2 サイクルに 1 回のレートで行われる。

## 【0071】

以下、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P の光信号が A/D 変換部 105 で A/D 変換されて光データが生成され、その光データがデータ処理部 107 の光データ記憶部 901、905 の B 記憶部に書き込まれる動作について説明する。時刻 T<sub>2w1</sub> から時刻 T<sub>2w2</sub> において、A/D 変換部 105 の複数 (m × I) の A/D 変換器 203 は、制御部 102 による制御の下で、第 1 行から第 6 行かつ第 1 列から第 m 列の画素 P の光信号を同時に A/D 変換して光データを生成する。時刻 T<sub>2w2</sub> において、複数 (m × I) の A/D 変換器 203 によって生成された複数 (m × I) のノイズデータが複数 (m × I) の保持部 204 に一括転送される。ここで、第 7 行の光データ群を S\_v11(h2)、第 8 行の光データ群を S\_v12(h2)、…、12 行の光データ群を S\_v16(h2) とする。

10

## 【0072】

時刻 T<sub>2w2</sub> から時刻 T<sub>3w1</sub> において、複数の保持部 204 によって保持されている光データ群 S\_v1#(h2) (# : 1 ~ 6) は、水平転送部 106 を介してデータ処理部 107 に転送される。光データ群 S\_v1#(h2) (# : 1 ~ 6) は、光データ記憶部 901、905 の A 記憶部に書き込まれる。光データ記憶部 901、905 の B 記憶部に書き込まれる。光データ記憶部 901、905 の B 記憶部に対する光データ群 S\_v1#(h2) (# : 1 ~ 6) の書込動作は、クロック c10ck の 2 サイクルに 1 回のレートで行われる。

20

## 【0073】

以下、第 7 行から第 12 行かつ第 1 列から第 m 列の画素 P のノイズデータ、光データをデータ処理部 107 のノイズデータ記憶部 902、906 の B 記憶部、光データ記憶部 901、905 の B 記憶部から読み出す動作について説明する。時刻 T<sub>3</sub> において、CPU 101 は、制御部 102 に対して水平同期信号 HD を出力する。時刻 T<sub>3r1</sub> から時刻 T<sub>3r2</sub> において、ノイズデータ記憶部 902、906 の B 記憶部 B から第 7 行のノイズデータ群 N\_v11(h2) と第 8 行のノイズデータ群 N\_v12(h2) が並列して、各行について 2 画素ずつ読み出される。また、これと並行して、時刻 T<sub>3r1</sub> から時刻 T<sub>3r2</sub> において、光データ記憶部 901、905 の B 記憶部からは第 7 行の光データ群 S\_v11(h2) と第 8 行の光データ群 S\_v12(h2) が並列して、各行について 2 画素ずつ読み出される。また、時刻 T<sub>3r1</sub> から時刻 T<sub>3r2</sub> において、第 7 行および第 8 行のそれぞれについて、各行について 2 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。

30

## 【0074】

上記と同様にして、時刻 T<sub>3r2</sub> から時刻 T<sub>3r3</sub> において、第 9 行と第 10 行のそれぞれについて、各行について 2 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。また、時刻 T<sub>3r3</sub> から時刻 T<sub>3r1</sub> において、第 11 と第 12 行のそれぞれについて、各行について 2 画素ずつ光データとノイズデータとの差分が演算部 520 によって演算され、信号出力部 108 から出力される。

40

## 【0075】

以上のようにして、第 7 行から第 12 行の画素のノイズ信号が同時に A/D 変換され、次

50

いで、第7行から第12行の画素の光信号が同時にA/D変換される。また、2つの行の画素のデータ（光データとノイズデータとの差分）は並列に、かつ、各行の画素のデータについては2画素ずつ順次に出力される。以降は、A記憶部を用いた動作とB記憶部を用いた動作とが交互かつ並行して実施される。

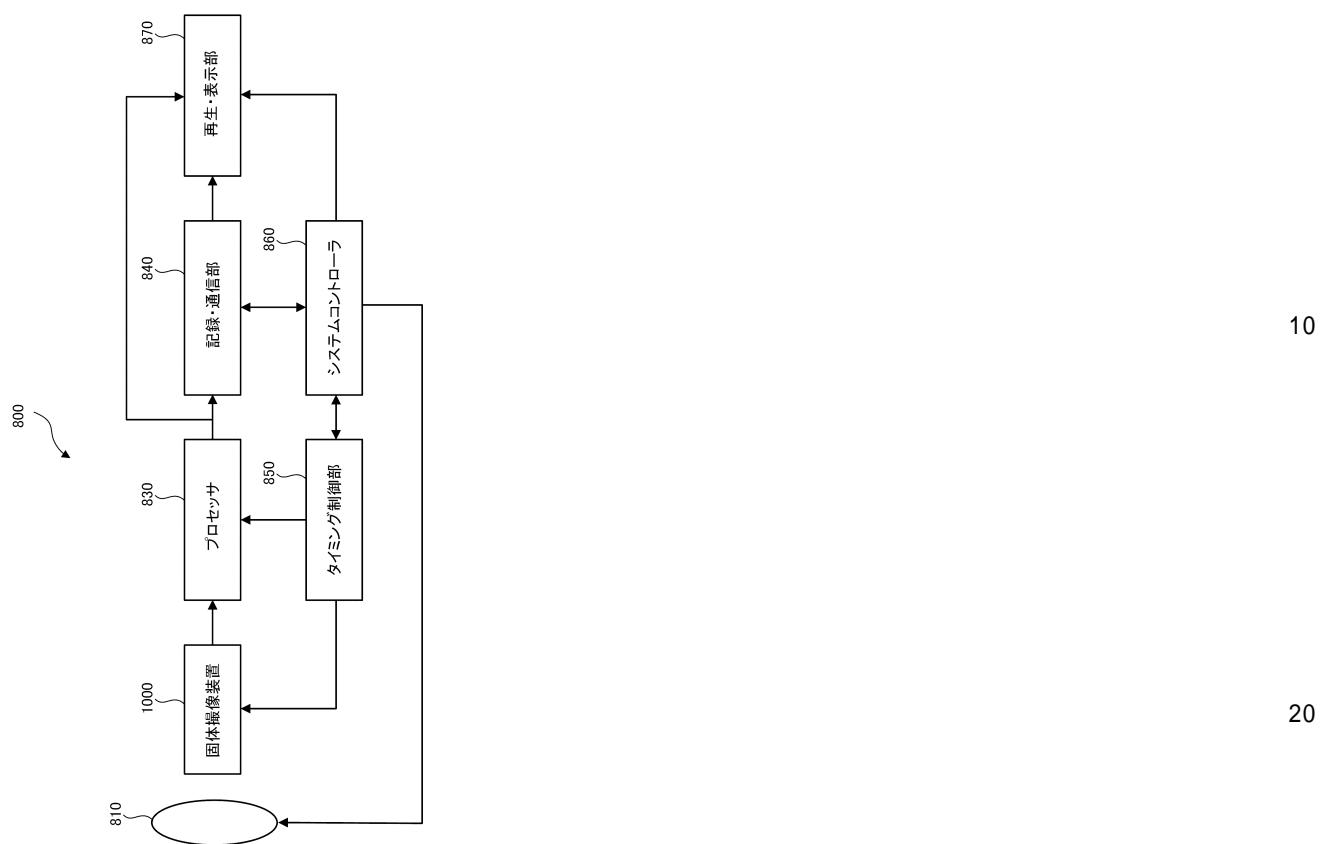

【0076】

以下、図13を参照しながら本発明の1つの実施形態の撮像装置800について説明する。撮像装置の概念には、撮像を主目的とする装置のみならず、撮像機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末）も含まれる。撮像装置800は、固体撮像装置1000として構成された光電変換装置1と、固体撮像装置1000から出力されるデータを処理するプロセッサ830とを備えうる。

10

【0077】

撮像装置800は、例えば、光学系810、記録・通信部840、タイミング制御部850、システムコントローラ860および再生・表示部870を更に備えてもよい。光学系810、被写体の像を固体撮像装置1000の画素アレイ（撮像面）に形成する。固体撮像装置1000は、タイミング制御部850からの信号に従って撮像動作を行って画像を出力する。固体撮像装置1000から出力されたデータは、プロセッサ830に提供される。

【0078】

プロセッサ830は、固体撮像装置1000から提供されるデータを処理して記録・通信部840に提供する。記録・通信部840は、画像を再生・表示部870に送り、再生・表示部870に画像を再生し表示させる。記録・通信部840はまた、不図示の記録媒体に画像を記録する。

20

【0079】

タイミング制御部850は、システムコントローラ860による制御に基づいて固体撮像装置1000およびプロセッサ830の駆動タイミングを制御する。システムコントローラ860は、撮像装置800の動作を統括的に制御するものであり、光学系810、タイミング制御部850、記録・通信部840および再生・表示部870の駆動を制御する。システムコントローラ860は、例えば、不図示の記憶装置を備え、ここに撮像装置800の動作を制御するのに必要なプログラムなどが記録される。また、システムコントローラ860は、例えば、ユーザによる操作に応じてモードを設定する。

30

【0080】

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

【符号の説明】

【0081】

103：垂直走査部（駆動部）、104：画素アレイ、105：A/D変換部、106：水平転送部（転送部）、107：データ処理部、510：データ保持部

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【図5】

【図6】

10

【図7】

【図8】

20

30

40

50

【図9】

【図10】

10

【図11】

【図12】

20

30

40

※: 図9には不図示

50

【図 1 3】

---

フロントページの続き

(56)参考文献      特開2017-184185 (JP, A)

特開2003-110798 (JP, A)

特開2017-183659 (JP, A)

特開2014-060697 (JP, A)

特開2015-167343 (JP, A)

特開2016-225972 (JP, A)

特開2015-156525 (JP, A)

特開2007-202035 (JP, A)

特開2012-134756 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04N 5/30 - 5/33

H04N 23/11

H04N 23/20 - 23/30

H04N 25/00

H04N 25/20 - 25/61

H04N 25/615 - 25/79