### PCT

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification  $^6$ :

H01L 27/02, G05F 3/20, H01L 29/94

(11) International Publication Number:

WO 97/18588

(43) International Publication Date:

22 May 1997 (22.05.97)

(21) International Application Number:

PCT/US96/12122

**A1**

(22) International Filing Date:

23 July 1996 (23.07.96)

(30) Priority Data:

08/558,119

13 November 1995 (13.11.95) U

Published

With international search report.

(81) Designated States: JP, KR, European patent (AT, BE, CH, DE,

DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

(71) Applicant: ADVANCED MICRO DEVICES, INC. [US/US]; One AMD Place, Mail Stop 68, Sunnyvale, CA 94088-3453 (US).

(72) Inventors: CLEVELAND, Lee, E.; 3428 St. Marys Place, Santa Clara, CA 95051 (US). KIM, Yong, K.; 3560 Flora Vista Avenue #215, Santa Clara, CA 95051 (US). CHANG, Chung, K.; 627 San Juan Drive #4, Sunnyvale, CA 94086 (US).

(74) Agent: PITRUZZELLA, Vincenzo, D.; Advanced Micro Devices, Inc., One AMD Place, Mail Stop 68, Sunnyvale, CA 94088-3453 (US).

(54) Title: IMPROVED CHARGE PUMPS USING ACCUMULATION CAPACITORS

(57) Abstract

A charge pump circuit utilizing accumulation capacitors for use in EEPROM devices so as to internally pump up an external power source voltage includes a plurality of MOS transistors (T101, T102; T201, T202) and accumulation capacitors (N2, P2). The plurality of MOS transistors are connected in series between a first input voltage terminal and a higher voltage output terminal. The first input voltage terminal receives the external power source voltage. The accumulation capacitor has a first plate and a second plate. Each of the first plates of the accumulation capacitors is connected between adjacent ones of the plurality of MOS transistors. Each of the second plates of the accumulation capacitors is connected to a second input terminal for receiving a clock signal. As a result, the pump circuit can be operated effectively so as to produce a significant reduction in power consumption.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM | Armenia                  | GB | United Kingdom               | MW | Malawi                   |

|----|--------------------------|----|------------------------------|----|--------------------------|

| AT | Austria                  | GE | Georgia                      | MX | Mexico                   |

| ΑU | Australia                | GN | Guinea                       | NE | Niger                    |

| BB | Barbados                 | GR | Greece                       | NL | Netherlands              |

| BE | Belgium                  | HU | Hungary                      | NO | Norway                   |

| BF | Burkina Faso             | IE | Ireland                      | NZ | New Zealand              |

| BG | Bulgaria                 | IT | Italy                        | PL | Poland                   |

| ВJ | Benin                    | JP | Japan                        | PT | Portugal                 |

| BR | Brazil                   | KE | Kenya                        | RO | Romania                  |

| BY | Belarus                  | KG | Kyrgystan                    | RU | Russian Federation       |

| CA | Canada                   | KP | Democratic People's Republic | SD | Sudan                    |

| CF | Central African Republic |    | of Korea                     | SE | Sweden                   |

| CG | Congo                    | KR | Republic of Korea            | SG | Singapore                |

| CH | Switzerland              | KZ | Kazakhstan                   | SI | Slovenia                 |

| CI | Côte d'Ivoire            | LI | Liechtenstein                | SK | Slovakia                 |

| CM | Cameroon                 | LK | Sri Lanka                    | SN | Senegal                  |

| CN | China                    | LR | Liberia                      | SZ | Swaziland                |

| CS | Czechoslovakia           | LT | Lithuania                    | TD | Chad                     |

| CZ | Czech Republic           | LU | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | LV | Latvia                       | TJ | Tajikistan               |

| DK | Denmark                  | MC | Monaco                       | TT | Trinidad and Tobago      |

| EE | Estonia                  | MD | Republic of Moldova          | UA | Ukraine                  |

| ES | Spain                    | MG | Madagascar                   | UG | Uganda                   |

| F1 | Finland                  | ML | Mali                         | US | United States of America |

| FR | France                   | MN | Mongolia                     | UZ | Uzbekistan               |

| GA | Gabon                    | MR | Mauritania                   | VN | Viet Nam                 |

#### DESCRIPTION

# IMPROVED CHARGE PUMPS USING ACCUMULATION CAPACITORS

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention:

5

10

15

20

25

30

35

This invention relates generally to semiconductor integrated circuit memory devices, such as flash electrically erasable programmable read-only memory (EEPROM) devices and more particularly, it relates to an improved charge pump utilizing an accumulation capacitor for use in EEPROM devices so as to internally pump up a power source voltage as supplied from an external or off-chip power supply on a more effective and efficient basis.

2. Description of the Prior Art:

As is generally known, in the area of memory devices and other semiconductor integrated circuits there is often required a voltage to be internally generated that is greater than an external or off-chip power supply potential which is supplied to it. For instance, in flash electrically erasable, programmable read-only memories (EEPROM's) high voltages such as ±12 V is needed to be produced for the programming and erasing modes of operation of memory cells. As a result, the semiconductor memory devices generally also include an internal booster circuit of some type for internally boosting up the external power supply voltage. One type of internal booster circuit commonly used in flash EEPROM's is referred to as a "charge pump."

While the user of such memory devices are not required to provide a high voltage source for its operation, these memory devices do suffer from the disadvantage that the charge pumps often account for a significant percentage of the total power dissipation of such memory devices. Further, as the demand for higher and higher densities of the semiconductor memory devices

5

10

15

20

25

30

35

increases, there exists a general miniaturization of all of the circuit elements forming the memory devices. Thus, there has been necessitated the use of lower power supply voltages not only as a way of reducing power dissipation, but also in order to prevent danger to the miniaturized circuit elements. There exists likewise a trend of decreasing the voltage for a battery power source for portable electronic applications to about 3 V or below. However, as the battery power source is reduced the conventional charge pumps utilizing inversion capacitors fail to provide an adequate degree of operation.

- 2 -

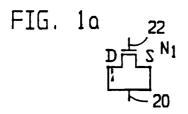

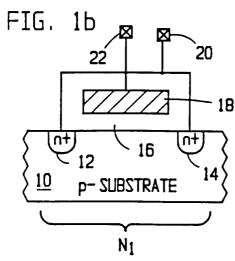

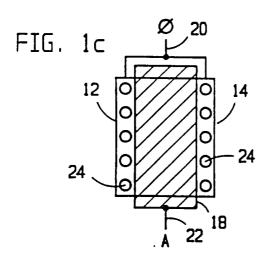

In Figure 1a, there is shown the electrical symbol for a capacitor-connected N-channel MOS transistor N1. Figures 1b and 1c show the cross-section and top plan views of the N-channel MOS transistor N1, respectively. As can be seen, the reference numeral 10 designates a p-type substrate. An n-type drain region 12 and an n-type source region 14 are diffused in the surface of the substrate 10. A thin gate oxide layer 16 is interposed between the top surface of the substrate and a conductive polysilicon gate 18. The drain and source regions 12 and 14 are connected together and to a metal contact connection 20 defining one plate of the capacitor N1. The gate 18 is also joined to a metal contact connection 22 defining the other plate of the capacitor N1.

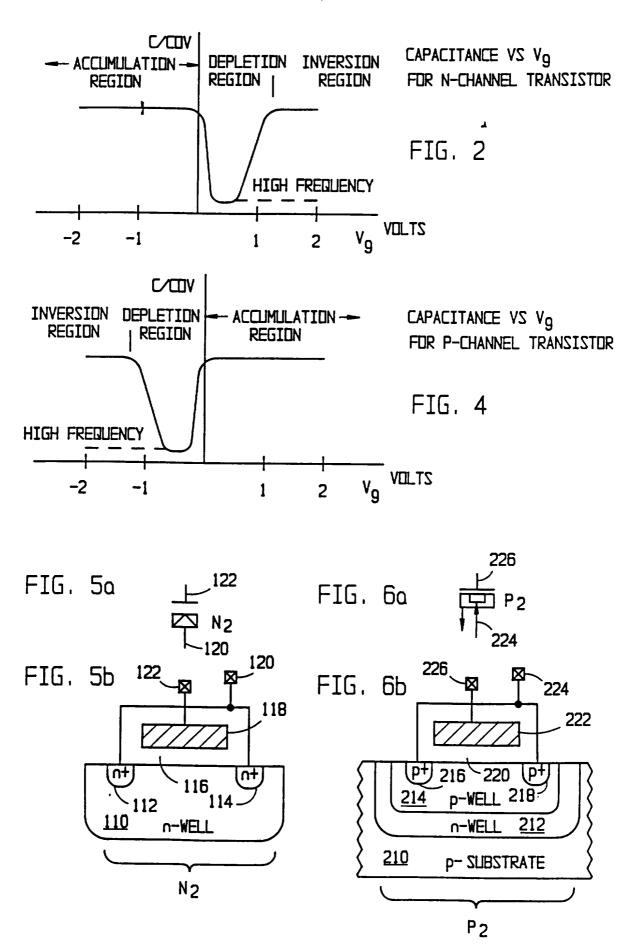

In Figure 2, there is illustrated a plot of the amount of capacitance value for the three operating regions (accumulation, depletion, and inversion) of the capacitor-connected MOS transistor N1 of Figure 1b as a function of the voltage  $\mathbf{V_g}$  applied to the polysilicon gate. As will be noted, when the capacitor is being operated in the inversion region there is the disadvantage of having the capacitance value drop off at the higher frequencies. The current output supplied from a charge pump becomes very small when the power source

- 3 -

voltage is made small. The output current of a charge pump is given by the following expression:

$I \propto C \times V \times F$

#### where:

5

10

15

20

25

30

C = value of pump capacitance

V = magnitude of switching power supply

F = frequency at which the voltage V

is being switched

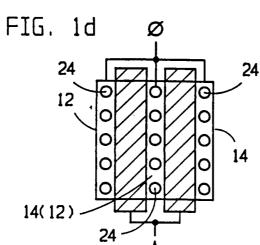

Thus, the output current of the charge pump can be made high by operating at higher frequencies. possible to increase the operating frequency of the capacitor operating in the inversion region by the adding of diffusion contacts 24 in the middle of the capacitor structure, as shown in Figure 1d. The diffusion contacts serve to generate a nearby supply of minority carriers thus improves the frequency response Therefore, it would be possible to further capacitor. subdivide the capacitor structure so as to add more diffusion contacts 24 and further improve the frequency response. However, this approach suffers from the drawback that it also adds parasitic capacitance which reduces the efficiency of the charge pump. Moreover, there is another disadvantage that the amount of area occupied by the capacitor on a semiconductor chip is significantly increased.

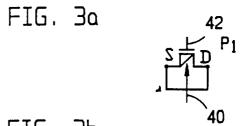

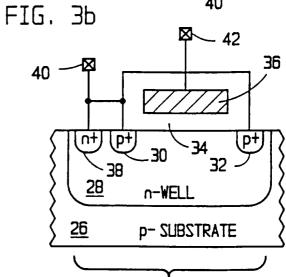

Similarly, there is shown in Figure 3a the electrical symbol for a capacitor-connected P-channel MOS transistor P1. Figure 3b shows the cross-sectional view of the P-channel MOS transistor P1. The capacitor is formed of a p-type substrate 26. An n-well region 28 is formed in the substrate 26. A p-type source region 30 and a p-type drain region 32 are diffused in the surface

-4-

of the n-well region 28. A thin gate oxide layer 34 is interposed between the top surface of the n-well region 28 and a conductive polysilicon gate 36. Further, an n-well contact region 38 is formed in the n-well region 28. The contact region 38, source region 30, and drain region 32 are all connected together and to a metal contact connection 40 defining one plate of the capacitor P1. The gate 36 is also connected to a metal contact connection 42 defining the other plate of the capacitor P1.

5

10

15

20

25

30

35

In Figure 4, there is illustrated a plot of the capacitance value for the three operating regions (accumulation, depletion, and inversion) of the capacitor-connected MOS transistor P1 of Figure 3b as a function of the voltage  $\mathbf{V_g}$  applied to the polysilicon gate. It will be noted again that when the capacitor P1 is being operated in the inversion region there is the disadvantage of having the capacitance value fall off at the higher frequencies.

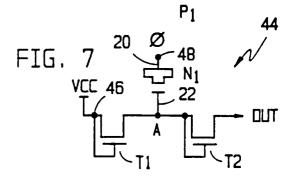

In Figure 7, there is depicted a schematic circuit diagram of a single stage positive voltage charge pump 44 of the prior art. The charge pump 44 includes a pair of N-channel MOS transistors T1, T2 and the inversion capacitor N1 (similar to Figure 1b). The drain and gate of the transistor T1 are connected together and to an input voltage terminal 46 for receiving a power supply voltage source VCC. The gate and drain of the transistor T2 are also connected together and to the source of the transistor T1 and to one plate of the capacitor N1 at node A. The other plate of the capacitor N1 is connected to an input node 48 for receiving a clock signal  $\phi$ . The source of the transistor T2 is connected to the output terminal OUT of the charge pump 44.

Referring again to the graph of Figure 2, it will be noted that for a full capacitance value in the inversion region the initial condition of the node A must be

- 5 -

greater than the threshold voltage of the capacitor-connected MOS transistor N1, which is approximately 1 volt. Thus, the operating voltage of the inversion capacitor cannot be reduced or lowered below 1 volt. On the other hand, the accumulation capacitor can be initialized at 0 volts as depicted in Figure 2. Another disadvantage of the inversion capacitor is that its effective threshold is increased due to the "body effect," which is caused by the differential potential applied between the source and the substrate of the transistor N1.

5

10

15

20

25

30

35

Accordingly, it would be desirable to provide an improved charge pump which overcomes the disadvantages of the prior art so as to be capable of operating reliably and effectively at lower power supply voltages (i.e., at 3 V or lower). It would be expedient that the charge pump be operated effectively so as to produce a significant reduction in power consumption. The present invention provides an improved charge pump by utilizing accumulation capacitors which is able to operate at lower voltages and with higher efficiency.

#### SUMMARY OF THE INVENTION

It is a general object of the present invention to provide an improved charge pump which overcomes all of the disadvantages of the prior art charge pumps.

It is an object of the present invention to provide an improved charge pump circuit utilizing accumulation capacitors for use in EEPROM devices so as to internally pump up a power source voltage on a more efficient and effective basis.

It is another object of the present invention to provide an improved charge pump circuit which is capable of operating reliably and effectively at lower power supply voltages.

It is still another object of the present invention to provide an improved charge pump which can be operated 5

10

15

20

25

30

35

efficiently so as to produce a significant reduction in power consumption.

In accordance with these aims and objectives, the present invention is concerned with the provision of a charge pump circuit utilizing accumulation capacitors for use in EEPROM devices so as to internally pump up an external power supply voltage. The charge pump circuit includes a plurality of MOS transistors connected in series between a first input voltage terminal and a higher voltage output terminal. The first input voltage terminal receives an external power supply voltage.

An accumulation capacitor has a first plate and a second plate. The first plate of the accumulation capacitor is connected between adjacent ones of the plurality of MOS transistors. The second plate of the accumulation capacitor is connected to a second input terminal for receiving a clock signal.

#### BRIEF DESCRIPTION OF THE DRAWINGS

These and other objects and advantages of the present invention will become more fully apparent from the following detailed description when read in conjunction with the accompanying drawings with like reference numerals indicating corresponding parts throughout, wherein:

Figure 1a shows the electrical symbol for an N-channel MOS transistor N1 connected so as to form an inversion capacitor for use in positive charge pumps;

Figure 1b is a cross-sectional view of the capacitor-connected N-channel MOS transistor N1 of Figure 1a;

Figure 1c is top plan view of the capacitor-connected N-channel MOS transistor N1 of Figure 1b;

Figure 1d is a top plan view of a capacitor-connected N-channel MOS transistor, similar to Figure 1c, which has an improved frequency response;

Figure 2 is a graph illustrating the capacitance value for the three operating regions of the capacitor-

5

10

15

20

25

30

35

-7-

connected N-channel MOS transistor N1 of Figure 1b as a function of the gate voltage  $V_{\alpha}$ ;

Figure 3a shows the electrical symbol for a P-channel MOS transistor P1 connected so as to form an inversion capacitor for use in negative charge pumps;

Figure 3b is a cross-sectional view of the capacitor-connected P-channel MOS transistor P1 of Figure 3a;

Figure 4 is a graph illustrating the capacitance value for the three operating regions of the capacitor-connected P-channel MOS transistor P1 of Figure 3b as a function of the gate voltage  $V_a$ ;

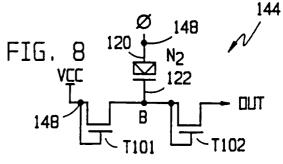

Figure 5a shows the electric symbol for an n-well capacitor for use as an accumulation capacitor in positive charge pumps;

Figure 5b is a cross-sectional view of the n-well capacitor of Figure 5a, constructed in accordance with the principles of the present invention;

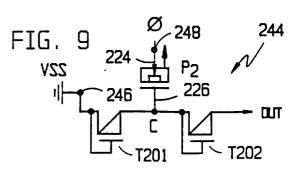

Figure 6a shows the electrical symbol for a p-well capacitor for use as an accumulation capacitor in negative charge pumps;

Figures 6b is a cross-sectional view of the p-well capacitor of Figure 6a, constructed in accordance with the principles of the present invention;

Figure 7 is a schematic circuit diagram of a single stage positive voltage charge pump of the prior art, utilizing an inversion capacitor similar to Figure 1b;

Figure 8 is a schematic circuit diagram of a single stage positive voltage charge pump of the present invention, utilizing an accumulation capacitor similar to Figure 5b; and

Figure 9 is a schematic circuit diagram of a single stage negative voltage charge pump of the present invention, utilizing an accumulation capacitor similar to Figure 6b.

5

10

15

20

25

30

35

## DESCRIPTION OF THE PREFERRED EMBODIMENTS

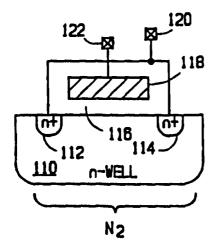

In the following, there will be described the preferred embodiments of the present invention with reference to the drawings. In Figure 5a, there is shown an electrical symbol for an n-well capacitor N2 for use as an accumulation capacitor in positive voltage charge There is illustrated in Figure 5b a crosssectional view of the n-well capacitor of Figure 5a, which is constructed with the principles of the present invention. As can be seen, the reference numeral 110 denotes an N-well region. There are formed n-type well electrode regions 112 and 114 in the n-well region 110. A thin gate oxide layer 116 is interposed between the top surface of the n-well region and a conductive polysilicon gate 118. The n-type well electrode regions 112 and 114 are connected together and to a metal contact connection 120 defining one plate of the n-well capacitor N2. The gate 118 is also joined to a metal contact connection 122 defining the other plate of n-well capacitor N2.

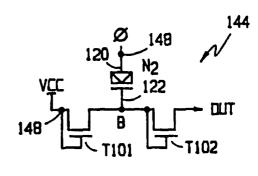

In Figure 8, there is illustrated a schematic circuit diagram of a single stage positive charge voltage pump 144 utilizing an accumulation capacitor, constructed accordance with the principles of the present The charge pump 144 includes a pair of invention. N-channel MOS transistor T101, T102 and the accumulation capacitor N2 (similar to Figure 5b). The gate and drain of the transistor T101 are connected together and to an input voltage terminal 146 for receiving a power supply voltage source VCC. The gate and drain of the transistor T102 are also connected together and to the source of the transistor T101 and to one plate 122 of the n-well capacitor N2 at an internal node B. The other plate 120 of the capacitor N2 is connected to an input terminal 148 for receiving a clock signal φ. The source of the transistor T102 is connected to the output node OUT of the charge pump 144. With reference to the graph of

5

10

15

20

25

30

35

-9-

Figure 2, it should be clear, as previously pointed out, that since the n-well capacitor N2 is operating in the accumulation region it can be initialized at zero volts.

Further, the power supply voltage source VCC, which is typically at +3.0 volts, can be reduced to approximately 2 volts so as to operate adequately in battery powered applications, thereby reducing significantly the power dissipation. As a result, the efficiency of the charge pump 144 can be increased by about 20% over the prior art charge pump 44 using the inversion capacitor. Moreover, the present charge pump 144 can be operated at a higher frequency of the switching voltage supply since the capacitance value in the accumulation region, unlike the inversion region, does not fall off at higher frequencies. In addition, the accumulation capacitors do not suffer from the "body effect" since there is no source-substrate voltage differential.

With reference to Figure 6a of the drawings, there is depicted an electrical symbol for a p-well capacitor P2 for use as an accumulation capacitor in negative voltage charge pumps. There is shown in Figure 6b a cross-sectional structural view of the p-well capacitor of Figure 6a, which is constructed in accordance with the principles of the present invention. As can be seen, the reference numeral 210 designates a p-type substrate which has formed therein an n-well region 212. A p-well region 214 is, in turn, formed in the n-well region 212. are formed a pair of p-well electrode regions 216 and 218 in the p-well region 214. A thin gate oxide region 220 is interposed between the top surface of the p-well region and a conductive polysilicon gate 222. Thus, the p-well region 214 is electrically insulated from the p-type substrate 210. The p-type well electrode regions 216 and 218 are connected together and to a metal contact connection 224 defining one plate of the p-well capacitor

5

10

15

20

25

30

-10-

P2. The gate 222 is also joined to a metal contact connection 226 defining the other plate of the capacitor P2.

In Figure 9, there is illustrated a schematic circuit diagram of a single stage negative voltage charge pump 244 utilizing an accumulation capacitor, constructed accordance with the principles of the present The charge pump 244 includes a pair of Pchannel MOS transistors T201, T202 and the accumulation capacitor P2 (similar to Figure 6b). The gate and source of the transistor T201 are connected together and to an input voltage terminal 246 for receiving a power supply voltage source VSS, which is typically at ground The gate and source of the transistor T202 potential. are connected together and to the drain of the transistor T201 and to one plate 226 of the p-well capacitor P2 at an internal node C. The other plate 224 of the capacitor P2 is connected to an input node 248 for receiving a clock signal  $\phi$ . The drain of the transistor T202 is also connected to the output terminal OUT of the charge pump. With reference to the graph of Figure 4, it will again be noted that since the p-well capacitor P2 is being operated in the accumulation region, it can be likewise initialized at zero volts and has all the advantages similar to that described with respect the n-well capacitor N2.

While Figures 8 and 9 show only single stage charge pumps, it should be apparent to those skilled in the art that they could be formed as multi-stage charge pumps. In this case, a plurality of MOS transistors would be cascade-connected between the input voltage terminal and the output voltage terminal. A corresponding plurality of capacitors would have their one end connected to respective internal nodes between adjacent transistors. Further, the other ends of the adjacent capacitors would

-11-

be driven by non-overlapping two-phase clock signals  $\phi 1$  and  $\phi 2$ .

From the foregoing detailed description, it can thus be seen that the present invention provides improved charge pumps utilizing accumulation capacitors for use in EEPROM devices so as to internally pump up a power supply voltage. The present charge pump overcomes the disadvantages of the prior art so as to be capable of operating reliably and effectively at lower power supply voltage. As a result, the charge pump of the present invention has improved efficiency since there is achieved a significant reduction in power consumption.

5

10

15

20

25

While there has been illustrated and described what are at present considered to be preferred embodiments of the present invention, it will be understood by those skilled in the art that various changes and modifications may be made, and equivalents may be substituted for elements thereof without departing from the true scope of the invention. In addition, many modifications may be made to adapt a particular situation or material to the teachings of the invention without departing from the central scope thereof. Therefore, it is intended that this invention not be limited to the particular embodiments disclosed as the best modes contemplated for carrying out the invention, but that the invention will include all embodiments falling within the scope of the appended claims.

5

15

20

25

#### **CLAIMS**

#### WHAT IS CLAIMED IS:

- 1. A charge pump circuit utilizing accumulation capacitors for use in EEPROM devices so as to internally pump up an external power supply voltage, comprising:

- a plurality of MOS transistors (T101, T102; T201, T202) connected in series between a first input voltage terminal, and a higher voltage output terminal, said first input voltage terminal receiving the external power source voltage;

- 10 accumulation capacitors (N2, P2) each having a first plate and a second plate;

- each of said first plates of said accumulation capacitors being connected between adjacent ones of said plurality of MOS transistors; and

- each of said second plates of said accumulation capacitors being connected to a second input terminal for receiving a clock signal.

- A charge pump circuit as claimed in Claim 1, wherein said plurality of MOS transistors is comprised of N-channel transistors (T101, T102).

- 3. A charge pump circuit as claimed in Claim 1, wherein said plurality of MOS transistors is comprised of P-channel transistors (T201, T202).

- 4. A charge pump circuit as claimed in Claim 2, wherein said external power source voltage is comprised of a positive potential (VCC), which is typically at +3.0 volts or lower.

- 5. A charge pump circuit as claimed in Claim 3, wherein said external power source voltage is comprised of a ground potential (VSS), which is typically at zero volts.

PCT/US96/12122

-13-

A charge pump circuit as claimed in Claim 4, 35 wherein each of said accumulation capacitors is comprised of an n-well capacitor (N2).

- A charge pump circuit as claimed in Claim 5, wherein each of said accumulation capacitors is comprised of a p-well capacitor (P2).

- 40 A charge pump circuit as claimed in Claim 6, wherein said n-well capacitor includes a pair of n+ electrode regions (112, 114) formed in an n-well region (110) and a gate oxide layer (116) disposed between the top surface of said n-well region and a polysilicon gate 45 (118).

- A charge pump circuit as claimed in Claim 7, 9. wherein said p-well capacitor includes a pair of p+ electrode regions (216, 218) formed in a p-well region (214) within an n-well region (212) and a gate oxide layer (220) disposed between the top surface of said pwell region and a polysilicon gate (222), said n-well region being disposed in a p-type substrate (210).

- 10. A positive voltage charge pump circuit for use in semiconductor memory devices, comprising:

a pair of N-channel MOS transistors (T101, T102) connected in series between a first input voltage terminal and a higher voltage output terminal, each of said pair of N-channel MOS transistors having its gate and drain connected together, said first input voltage terminal receiving an external power source voltage;

an n-well capacitor (N2) functioning as an accumulation capacitor having a first plate and a second plate;

said first plate of said n-well capacitor being connected between junction of said pair of MOS transistors; and

50

55

60

65

said second plate of said n-well capacitor being connected to a second input terminal for receiving a clock signal.

75

80

85

90

95

100

105

- 11. A charge pump circuit as claimed in Claim 10, wherein said external power source voltage is comprised of a positive potential (VCC), which is typically at +3.0 volts or lower.

- 12. A charge pump circuit as claimed in Claim 11, wherein said n-well capacitor includes a pair of n+ electrode regions (112, 114) formed in an n-well region (110) and a gate oxide layer (116) disposed between the top surface of said n-well region and a polysilicon gate (118).

- 13. A charge pump circuit for use in a semiconductor integrated circuit device for generating at an output terminal a voltage which is pumped higher than an external power source voltage, comprising:

transistor charging means connected between the external power source voltage and said output terminal for generating the higher voltage at said output terminal; and

accumulation capacitor means connected to said transistor charging means and being responsive to clock signals for generating the higher voltage at said output terminal.

- 14. A charge pump circuit as claimed in Claim 13, wherein said transistor charging means is comprised of a plurality of N-channel transistors (T101, T102).

- 15. A charge pump circuit as claimed in Claim 13, wherein said transistor charging means is comprised of a plurality of P-channel MOS transistors (T201, T202).

- 16. A charge pump circuit as claimed in Claim 14, wherein said accumulation capacitor means is comprised of an n-well capacitor (N2).

- 17. A charge pump circuit as claimed in Claim 15, wherein said accumulation capacitor means is comprised of a p-well capacitor (P2).

-15-

18. A charge pump circuit as claimed in Claim 16, wherein said n-well capacitor includes a pair of n+ electrode regions (112, 114) formed in an n-well region (110) and a gate oxide layer (116) disposed between the top surface of said n-well region and a polysilicon gate (118).

110

19. A charge pump circuit as claimed in Claim 17, wherein said p-well capacitor includes a pair of p+ electrode regions (216, 218) formed in a p-well region (214) within an n-well region (212) and a gate oxide layer (220) disposed between the top surface of said p-well region and a polysilicon gate (222), said n-well region being disposed in a p-type substrate (210).

## INTERNATIONAL SEARCH REPORT

Inte 2 nal Application No PCT/US 96/12122

| A. CLASS<br>IPC 6                                                          | H01L27/02 G05F3/20 H01L29/                                                                                                                                    | /94                                                                                                                                                                                                                                      |                        |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| According                                                                  | to International Patent Classification (IPC) or to both national class                                                                                        | safication and IPC                                                                                                                                                                                                                       |                        |  |

| <u> </u>                                                                   | S SEARCHED                                                                                                                                                    |                                                                                                                                                                                                                                          |                        |  |

| Minimum of IPC 6                                                           | documentation searched (classification system followed by classific<br>HO1L G05F                                                                              | ation symbols)                                                                                                                                                                                                                           |                        |  |

| Documenta                                                                  | tion searched other than minimum documentation to the extent tha                                                                                              | it such documents are included in the fields s                                                                                                                                                                                           | earched                |  |

| Electronic o                                                               | data base consulted during the international search (name of data b                                                                                           | ase and, where practical, search terms used)                                                                                                                                                                                             |                        |  |

| C. DOCUM                                                                   | MENTS CONSIDERED TO BE RELEVANT                                                                                                                               |                                                                                                                                                                                                                                          |                        |  |

| Category *                                                                 | Citation of document, with indication, where appropriate, of the                                                                                              | relevant passages                                                                                                                                                                                                                        | Relevant to claim No.  |  |

| Υ                                                                          | EP,A,O 638 984 (ADVANCED MICRO DINC) 15 February 1995 see the whole document                                                                                  | DEVICES                                                                                                                                                                                                                                  | 1-19                   |  |

| Y                                                                          | EP,A,O 581 702 (SGS THOMSON<br>MICROELECTRONICS) 2 February 199<br>see the whole document                                                                     | 14                                                                                                                                                                                                                                       | 1-19                   |  |

| A                                                                          | EP,A,O 062 894 (TOKYO SHIBAURA E<br>CO) 20 October 1982<br>see page 5, line 7 - page 8, lin<br>figures 3,4                                                    |                                                                                                                                                                                                                                          | 1-3,5,<br>10,13-15     |  |

|                                                                            |                                                                                                                                                               |                                                                                                                                                                                                                                          |                        |  |

|                                                                            |                                                                                                                                                               |                                                                                                                                                                                                                                          |                        |  |

| Furti                                                                      | her documents are listed in the continuation of box C.                                                                                                        | Patent family members are listed in                                                                                                                                                                                                      | n annex.               |  |

| "A" docum                                                                  | tegories of cited documents:  ent defining the general state of the art which is not cred to be of particular relevance                                       | "T" later document published after the inte<br>or priority date and not in conflict wi<br>cited to understand the principle or th<br>invention                                                                                           | th the application but |  |

|                                                                            | document but published on or after the international                                                                                                          | "X" document of particular relevance; the                                                                                                                                                                                                |                        |  |

| "L" document which may throw doubts on priority claim(s) or                |                                                                                                                                                               | cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the |                        |  |

| other r<br>'P' docume                                                      | ent referring to an oral disclosure, use, exhibition or<br>neans<br>ent published prior to the international filing date but<br>nan the priority date claimed | document is combined with one or ments, such combination being obvious in the art.  '&' document member of the same patent                                                                                                               | us to a person skilled |  |

|                                                                            |                                                                                                                                                               | Date of mailing of the international se                                                                                                                                                                                                  |                        |  |

| Date of the actual completion of the international search  29 October 1996 |                                                                                                                                                               | 2 1. 11. 96                                                                                                                                                                                                                              |                        |  |

| Name and n                                                                 | nailing address of the ISA  European Patent Office, P.B. 5818 Patentiaan 2                                                                                    | Authorized officer                                                                                                                                                                                                                       |                        |  |

|                                                                            | NL - 2280 HV Rijsmijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                 | Albrecht, C                                                                                                                                                                                                                              |                        |  |

1

## INTERNATIONAL SEARCH REPORT

Information on patent family members

Inter onal Application No PCT/US 96/12122

| Patent document cited in search report | Publication<br>date | Patent family member(s)                            |                                                                             | Publication<br>date                                                              |

|----------------------------------------|---------------------|----------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| EP-A-0638984                           | 15-02-95            | US-A-<br>JP-A-                                     | 5386151<br>7154964                                                          | 31-01-95<br>16-06-95                                                             |

| EP-A-0581702                           | 02-02-94            | FR-A-<br>JP-A-                                     | 2694450<br>6188364                                                          | 04-02-94<br>08-07-94                                                             |

| EP-A-0062894                           | 20-10-82            | JP-C-<br>JP-B-<br>JP-C-<br>JP-B-<br>JP-A-<br>US-A- | 1601288<br>2024027<br>57166066<br>1598174<br>2019979<br>57166067<br>4559548 | 18-02-91<br>28-05-90<br>13-10-82<br>28-01-91<br>07-05-90<br>13-10-82<br>17-12-85 |