(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4657602号

(P4657602)

(45) 発行日 平成23年3月23日(2011.3.23)

(24) 登録日 平成23年1月7日(2011.1.7)

(51) Int.Cl.

F 1

G06F 13/14 (2006.01)

G06F 13/36 (2006.01)G06F 13/14 320H

G06F 13/36 310E

請求項の数 30 (全 19 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2003-509332 (P2003-509332)  |

| (86) (22) 出願日 | 平成14年6月20日 (2002.6.20)        |

| (65) 公表番号     | 特表2004-531838 (P2004-531838A) |

| (43) 公表日      | 平成16年10月14日 (2004.10.14)      |

| (86) 國際出願番号   | PCT/US2002/019720             |

| (87) 國際公開番号   | W02003/003225                 |

| (87) 國際公開日    | 平成15年1月9日 (2003.1.9)          |

| 審査請求日         | 平成17年6月17日 (2005.6.17)        |

| 審判番号          | 不服2008-12766 (P2008-12766/J1) |

| 審判請求日         | 平成20年5月19日 (2008.5.19)        |

| (31) 優先権主張番号  | 09/896,395                    |

| (32) 優先日      | 平成13年6月29日 (2001.6.29)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 593096712<br>インテル コーポレイション<br>アメリカ合衆国 95052 カリフォルニア州 サンタクララ ミッション カレッジ ブールバード 2200 |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                                                             |

| (74) 代理人  | 100091214<br>弁理士 大貫 進介                                                             |

| (74) 代理人  | 100107766<br>弁理士 伊東 忠重                                                             |

| (72) 発明者  | ジョージ, ヴァルゲーゼ<br>アメリカ合衆国 95630 カリフォルニア州 フォルソム ハリドン ウェイ<br>1113                      |

最終頁に続く

(54) 【発明の名称】仮想PCIデバイス装置及び方法

## (57) 【特許請求の範囲】

## 【請求項1】

host-to-PCIブリッジと共有されることなく1以上のプロセッサを有するホストバスとに直接接続するためのインターフェースと、

1以上の機能を実行するよう前記インターフェースと接続され、仮想PCIデバイスとして出現し、前記host-to-PCIブリッジを介し前記ホストバスに接続されるPCIバス上に論理的に設けられるデバイスと、

前記ホストバスに接続される前記プロセッサの少なくとも1つにより開始されるホストバスサイクルを追跡するよう前記デバイスと前記インターフェースに接続され、前記仮想PCIデバイスを対象とするプロセッサにより開始されたホストバスサイクルを特定し、前記仮想PCIデバイスとして前記デバイスが前記host-to-PCIブリッジにアクセスする必要なく、前記仮想PCIデバイスを対象とする特定されたホストバスサイクルの1以上に応答することを可能にするよう1以上の制御信号を生成するモニタ回路と、から構成される装置であって、

前記デバイスによる前記host-to-PCIブリッジへのアクセスは、前記ホストバスを介してのみ行われることを特徴とする装置。

## 【請求項2】

請求項1記載の装置であって、さらに、

前記インターフェースと前記モニタ回路に接続され、前記仮想PCIデバイスにアドレス指定されたホストバスリードサイクルに係るデータを格納する第1ストレージを有し、

10

20

前記データは、前記host-to-PCIブリッジのホストインターフェースにアクセスすることなく、前記ホストバスリードサイクル中に前記第1ストレージから前記ホストバスに転送されることを特徴とする装置。

**【請求項3】**

請求項2記載の装置であって、さらに、

前記インターフェースと前記モニタ回路に接続され、前記仮想PCIデバイスにアドレス指定されたホストバスライトサイクルに係るデータを格納する第2ストレージを有し、

前記データは、前記host-to-PCIブリッジのホストインターフェースにアクセスすることなく、前記ホストバスライトサイクル中に前記ホストバスから前記第2ストレージに転送されることを特徴とする装置。 10

**【請求項4】**

請求項1記載の装置であって、さらに、

前記インターフェースに接続され、該インターフェースを介し前記ホストバス上で1以上のホストバスサイクルを開始可能なプロセッサを有することを特徴とする装置。

**【請求項5】**

請求項3記載の装置であって、さらに、

前記デバイス、前記モニタ回路、前記第1ストレージ及び前記第2ストレージを前記インターフェースに接続する内部バスを有することを特徴とする装置。

**【請求項6】**

請求項1記載の装置であって、

前記デバイスは、1以上の他のデバイスに接続されるブリッジデバイスであり、前記host-to-PCIブリッジに接続されるPCIバスに論理的に設けられる仮想PCI-PICIブリッジとして出現することを特徴とする装置。 20

**【請求項7】**

請求項1記載の装置であって、

前記仮想PCIデバイスを対象とする前記特定されたホストバスサイクルは、前記仮想PCIデバイスに割当てられたメモリアドレス空間を対象とするホストバスサイクルを有することを特徴とする装置。

**【請求項8】**

請求項1記載の装置であって、さらに、

前記ホストバスに接続され、前記ホストバスからデータを受信するための前記制御信号の1以上に応答するミラーレジスタを有し、

前記モニタ回路は、設定アドレスレジスタを対象とするホストバスライトサイクルをさらに特定し、前記設定アドレスレジスタを対象とするものとして特定された前記ホストバスサイクルの期間中に前記ミラーレジスタに格納するため、前記ホストバスからデータを受信するための前記制御信号を生成する、

ことを特徴とする装置。 30

**【請求項9】**

請求項1記載の装置であって、

前記仮想PCIデバイスを対象とする前記特定されたホストバスサイクルは、前記仮想PCIデバイスに割当てられたI/Oアドレス空間に対するホストバスサイクルを有することを特徴とする装置。 40

**【請求項10】**

請求項2記載の装置であって、

前記第1ストレージは、複数の第1設定レジスタを有し、

前記特定されたホストバスサイクルは、前記仮想PCIデバイスに対し確保されている設定空間を対象とするホストバスサイクルを有することを特徴とする装置。

**【請求項11】**

請求項10記載の装置であって、

前記仮想PCIデバイスは、仮想PCI-to-PCIブリッジの後方に配置され、 50

- 前記第1ストレージは、複数の第2設定レジスタを有し、

前記モニタ回路は、前記仮想PCI-t o - PCIブリッジに割当てられた設定空間を

対象とするホストバスサイクルをさらに特定し、

前記モニタ回路は、前記仮想PCI-t o - PCIブリッジに割当てられた設定空間を

対象とする前記特定されたホストバスリードサイクルの1以上において、1以上の前記デ

ータを前記ホストバスに伝送する複数の制御信号を生成する、

ことを特徴とする装置。

- 【請求項12】**

- host-t o - PCIブリッジと共有されることなくホストバスに直接接続するため

のインターフェースと、

プライマリPCIバスに割当てられた第1アドレス空間を指定するコンテンツを有する

第1ストレージと、

1以上の機能を実行するよう前記インターフェースに接続され、仮想PCIデバイスとし

出現し、前記プライマリPCIバスに接続されるPCIバス上に論理的に配置され、前記

host-t o - PCIブリッジへのアクセスが前記ホストバスを介してのみなされるデ

バイスと、

前記仮想PCIデバイスに割当てられる第2アドレス空間を指定するコンテンツを有する

第2ストレージと、

前記第1ストレージと前記第2ストレージに接続され、プロセッサにより開始されたホ

ストバスサイクルを追跡し、前記プライマリPCIバスにルーティングするホストバスサ

イクルを選択するようホストバスに接続する制御回路と、

から構成される装置であって、

前記ルーティングされたサイクルは、前記第2アドレス空間を対象とするホストバスサ

イクルを排除するため、前記第1ストレージと前記第2ストレージのコンテンツに基づき

選択されることを特徴とする装置。

- 【請求項13】**

- 請求項12記載の装置であって、

前記第1及び第2アドレス空間は、メモリホストバスアドレス空間を含むことを特徴と

する装置。

- 【請求項14】**

- 請求項12記載の装置であって、

前記第1及び第2アドレス空間は、ホストバスI/O空間を含むことを特徴とする装置

。

- 【請求項15】**

- 請求項12記載の装置であって、

前記第1及び第2アドレス空間は、PCIに準拠した設定アドレス空間を含むことを特

徴とする装置。

- 【請求項16】**

- 請求項12記載の装置であって、

前記仮想PCIデバイスは、仮想PCI-t o - PCIブリッジであることを特徴とす

る装置。

- 【請求項17】**

- 請求項16記載の装置であって、さらに、

複数の設定レジスタと、

前記制御回路に接続され、前記仮想PCI-t o - PCIブリッジが論理的に配備され

るデバイス番号とバスを示すコンテンツを有する第3ストレージと、

を有し、

前記制御回路はさらに、前記バス及びデバイス番号に基づき、前記host-t o - P

CIブリッジのホストインターフェースにアクセスする必要なく前記複数の設定レジスタに

ルーティングするよう前記仮想PCI-t o - PCIブリッジの設定アドレス空間を対象

10

20

30

40

50

とするホストバスサイクルを選択することを特徴とする装置。

**【請求項 18】**

ホストバスに接続された 1 以上のプロセッサと、

前記ホストバスにプライマリ PCI バスを接続する host - to - PCI ブリッジと

、

前記ホストバスに接続され、前記プライマリ PCI バスに接続された PCI バス上に論理的に配備される第 1 仮想 PCI デバイスとして出現し、前記ホストバスをモニタし、前記第 1 仮想 PCI デバイスを対象とするプロセッサにより開始されたホストバスサイクルを特定し、前記 host - to - PCI ブリッジにアクセスすることなく前記第 1 仮想 PCI デバイスを対象とする特定されたサイクルを傍受し、前記 host - to - PCI ブリッジへの前記デバイスによるアクセスが前記ホストバスのみを介する第 1 ホストバスデバイスと、

10

から構成されるシステムであって、

前記 host - to - PCI ブリッジは、前記第 1 仮想 PCI デバイスを対象とする前記 host - to - PCI ブリッジを介し接続される前記 PCI バスに前記特定されたサイクルを転送しないことを特徴とするシステム。

**【請求項 19】**

請求項 18 記載のシステムであって、

前記第 1 ホストバスデバイスは、複数の設定レジスタを有し、

前記傍受されたサイクルは、前記第 1 仮想 PCI デバイスのため確保された設定空間を対象とするホストバスサイクルを有し、前記複数の設定レジスタにアクセスするようルーティングされる、

20

ことを特徴とするシステム。

**【請求項 20】**

請求項 18 記載のシステムであって、

前記第 1 ホストバスデバイスは、メモリ装置アレイを有し、

前記傍受されたサイクルは、前記第 1 仮想 PCI デバイスに割当てられたメモリ空間を対象とするホストバスサイクルを有し、前記メモリ装置アレイにアクセスするようルーティングされる、

30

ことを特徴とするシステム。

**【請求項 21】**

請求項 18 記載のシステムであって、さらに、

前記ホストバスに接続され、前記プライマリ PCI バスに接続される PCI バス上に論理的に配備される第 2 仮想 PCI デバイスとして出現する第 2 ホストバスデバイスを有し、

30

前記第 1 及び第 2 仮想 PCI デバイスは、PCI バス番号とデバイス番号の一意的な組み合わせを有することを特徴とするシステム。

**【請求項 22】**

請求項 18 記載のシステムであって、

前記第 1 仮想 PCI デバイスは、プライマリ仮想 PCI - to - PCI ブリッジの後方に論理的に配置され、

40

前記プライマリ仮想 PCI - to - PCI ブリッジは、前記プライマリ PCI バスの後方に論理的に配置され、

前記第 1 ホストバスデバイスは、前記プライマリ仮想 PCI - to - PCI バスに割当てられたバス番号を決定するため、前記ホストバスを検索する、

40

ことを特徴とするシステム。

**【請求項 23】**

請求項 22 記載のシステムであって、

前記第 1 仮想 PCI デバイスは、プライマリ仮想 PCI - to - PCI ブリッジの後方に論理的に配置される補助仮想 PCI - to - PCI ブリッジの後方に論理的に配置され

50

、

前記第1ホストバスデバイスは、複数のブリッジ設定レジスタを有し、

前記傍受されたサイクルは、前記補助仮想PCI-to-PCIブリッジのために確保

された設定空間を対象とするホストバスサイクルを有し、前記複数のブリッジ設定レジス

タにアクセスするようルーティングされる、

ことを特徴とするシステム。

【請求項24】

ホストバスに接続されるプロセッサにより開始される現在のホストバスサイクルをキャ

プチャするステップと、

前記キャプチャされたサイクルが、プライマリPCIバスの後方のPCIバスに論理的

に配置され、前記ホストバスにアクセスするため、host-to-PCIブリッジとイ

ンタフェースを共有し、前記host-to-PCIブリッジのホストインターフェースに

アクセスする必要なく、前記ホストバスに直接接続されたホストバスデバイスを表す仮想

PCIデバイスを対象としているか判断するステップと、

10

前記現在のサイクルが前記仮想PCIデバイスを対象としていると判断されると、前記

host-to-PCIブリッジのホストインターフェースを介し前記プライマリPCIバ

スに前記サイクルをルーティングすることなく、前記現在のホストバスサイクルを傍受す

るステップと、

前記ホストバスデバイスが前記仮想PCIデバイスとして前記ホストバスサイクルに応

答することを可能にするため、前記host-to-PCIブリッジのホストインターフェ

ースを用いることなく前記傍受されたホストバスサイクルを前記ホストバスデバイスにル

ーティングするステップと、

20

から構成されることを特徴とする方法。

【請求項25】

請求項24記載の方法であって、

前記傍受は、前記ホストバスに接続されたストレージにアクセスするためのルーティン

グを含むことを特徴とする方法。

【請求項26】

請求項24記載の方法であって、

前記傍受は、複数の設定レジスタ内のある位置にアクセスするためのルーティングを含

むことを特徴とする方法。

30

【請求項27】

請求項24記載の方法であって、

前記判断は、前記現在のサイクルが設定アドレスレジスタを対象とするライトサイクル

であるか判断し、前記現在のサイクルが前記設定アドレスレジスタを対象とするライトサ

イクルである場合、前記ホストバスからデータを受信するよう前記現在のホストバスサイ

クルを検索し、前記データの一部またはすべてをミラーレジスタに書き込むことからなる

ことを特徴とする方法。

【請求項28】

請求項24記載の方法であって、

前記判断は、前記現在のサイクルが、バス番号が指定される仮想プライマリPCI-to-

PCIブリッジの設定レジスタ内のある位置を対象とするライトサイクルであるか判

断し、前記現在のサイクルが、バス番号が指定される仮想プライマリPCI-to-PCI

ブリッジの設定レジスタ内のある位置を対象とするライトサイクルである場合、前記ホ

ストバスからデータを受信するよう前記現在のホストバスサイクルを検索し、前記データ

をストレージに書き込むことからなることを特徴とする方法。

40

【請求項29】

請求項24記載の方法であって、

前記判断は、前記サイクルが仮想PCI-to-PCIブリッジの設定レジスタ内のある

位置に対するものであるか判断し、前記サイクルが仮想PCI-to-PCIブリッジ

50

の設定レジスタ内のある位置に対するものである場合、複数のブリッジ設定レジスタ内のある位置にアクセスするようルーティングするため、前記現在のホストバスを傍受することからなることを特徴とする方法。

**【請求項 30】**

請求項 24 記載の方法であって、

前記仮想 PCI デバイスは、仮想 PCI - to - PCI ブリッジであることを特徴とする方法。

**【発明の詳細な説明】**

**【発明の詳細な説明】**

**【0001】**

10

**[発明の背景]**

**発明の技術分野**

本発明は、一般にコンピュータに関する。より詳細には、本発明は、データ転送バスに関する。

**従来技術の説明**

PCI - SIG ( Peripheral Component Interconnect - Special Interest Group ) により公開された PCI ローカルバス仕様 ( PCI Local Bus Specification ) Rev. 2.2 と PCI - PCI ブリッジアーキテクチャ仕様 ( PCI to PCI Bridge Architecture Specification ) Rev. 1.1 は、ネットワークコントローラ、大容量記憶装置コントローラ、ディスプレイコントローラ、マルチメディア装置、通信装置及び他の装置をシステムに統合するための PCI バスプロトコルを規定するものである。 PCI バスプロトコルは、ソフトウェアが PCI デバイスと協調するための電気特性及び方法に関する仕様を含み、一般的に、ホストバス、プロセッサまたはメモリのような他のシステム構成要素に利用されるプロトコルとは独立な方法により周辺デバイスの統合を行う。

20

**【0002】**

PCI プロトコルは、コンピュータプログラムによる PCI デバイスへの直接的なアクセス及び PCI デバイスの設定を可能にする「フック ( hook ) 」を提供する。このフックには、各 PCI デバイスに関連付けされた 256 個の 8 ビット設定レジスタにアクセスするための設定アドレス空間が含まれる。これにより、ユーザによる操作なく、システムアドレスマップの構築のため、システムにインストールされている各 PCI デバイスの選択的な検出、ベンダーとデバイスタイプの特定、各 PCI デバイスのシステムリソース要件についての判断、システムアドレス空間内の各デバイスの再配置、バインディング ( binding ) の中断、インストール、設定及び起動を、コンピュータプログラムは実行することができる。設定レジスタには、所定のヘッダー領域とデバイス依存領域が含まれるが、各領域の必要性かつ関連性のあるレジスタのみが実現される必要がある。 PCI - PCI ブリッジは、レンジバス番号を当該 PCI - PCI ブリッジから後ろの PCI バスに割り当てるコンピュータプログラムにアクセス可能である設定レジスタを有する PCI 装置である。

30

**【0003】**

設定空間は、ホストコンピュータにおいて実行されるコンピュータプログラムにより始動される設定サイクルを介しアクセスされる。 PCI プロトコルは、異なる 2 つの機構の一方を通じ設定サイクルのルーティングが実行されると予想する。これらの機構で、ホスト - PCI ブリッジは、ターゲット PCI デバイスにより受信される当該 PCI デバイスが現在の設定サイクルでのターゲットであると通知する PCI バス信号に関し、ソフトウェアコマンドをターゲット PCI バスにおける 1 つの設定サイクルに解釈する。

40

**【0004】**

あるシステムにおける PCI デバイスの検出及び初期化は、設定空間を利用し、デバイスに依存しないプログラムにより実行される。プログラムは、 PCI バス 0 における各ス

50

ロットに割り当てられた設定空間をポーリングし、バス0上のPCIデバイス及びPCI-PCIブリッジを検出する。当該プログラムは、設定レジスタに書き込むことにより、検出されたPCI-PCIブリッジのそれぞれに一意的なバス番号を割り当て、割り当てられたバスそれぞれにおける各スロットをポーリングし、PCIデバイス及びPCI-PCIブリッジを検出するようにしてよい。検出されたPCIバスそれぞれの各スロットがポーリングされ、すべてのPCIデバイスが検出されるまで、上記処理は続けられる。システムにインストールされていると検出された各PCIデバイスに対し、リソース要件を判断するため、デバイスの設定レジスタが読み出される。システム及び様々なPCIデバイス間のコンフリクトを回避するようシステムアドレスマップが構成され、各PCIデバイスの適切な設定レジスタに書き込むことにより、システムリソースが各PCIデバイスに割り当てられるようにしてよい。さらに、自己診断テストや他の初期化処理をサポートするデバイス上に自己診断テストが呼び出され、各PCIデバイスに対し、インストールと設定がユーザ操作により、あるいはユーザ操作なしに実行されるようにしてよい。

。

#### 【0005】

PCIプロトコルに厳格に従うことによる短所として、データ転送速度、データバス幅、待ち時間(*latency*)及び帯域幅を限定してしまい、PCIデバイスのパフォーマンスの上限を設けてしまうという問題点がある。また、ホスト-PCIブリッジに特有の遅延と、共有PCIバス上の複数のPCIデバイスに特有の帯域幅に関する制約により、パフォーマンスは制限される。現在の傾向としては、より高いパフォーマンスのプロセッサ、メモリ及びホストバスを求めるというものであり、そこでは、効率的に接続されたデバイスが、実際のPCIバスへの接続を通じてよりも、より低い待ち時間、より高いスループット及びより良いシステム全体のパフォーマンスのようなパフォーマンス効果を達成することができる。

20

#### 【0006】

PCIブリッジ仕様により要求されているプラグ・アンド・プレイ(登録商標)リソース配分プログラムは、典型的には、あるPCIバスに割り当てられたアドレス空間が当該PCIバスより後方のPCIバスに割り当てられるアドレス空間を含むことを予期する。従って、PCIプロトコルへの完全な準拠は、PCIデバイスをホスト-PCIブリッジのホストプロセッサ側に配置することをより困難にし、この場合、PCIデバイスは、(恐らく互換性に関する理由のため)物理的なPCIバスに割り当てられたアドレス空間の一部であるアドレス空間を要求する。

30

#### [詳細な説明]

ネットワークコントローラ、大容量記憶装置コントローラ、ディスプレイコントローラ、マルチメディアデバイス、通信デバイス及びその他のデバイスのホストバスプロセッサへの統合、及びデバイスのプロセッサホストバスへの効率的な接続のための実施例が提供される。PCIプロトコルの選択された特徴が順守され、PCIに準拠したデバイスにのみ利用可能なデバイスのためのソフトウェアサポートを可能にする。本発明は、いくつかのシステムにおいて、システムパフォーマンスの向上、デバイスパフォーマンスの向上、システム内のすべてのデバイスのよりシンプルな初期化及び設定、システムリソース配分処理における頑健性の向上、全体コストの低下、及び物理的なボード/チップスペースの減少、さらに、物理的PCIバスに割り当てられたアドレス空間の一部のホストバス上のデバイスへの配分を可能にすることを含む従来方法に対する多くの優位点の少なくとも1つを提供する。さらに、本発明は、PCIに準拠するデバイスの特性の多くを有するものとしてコンピュータプログラムに現れるデバイスの統合を可能にし、それによって、システム全体のコスト低下、より少ないスペース、プロセッサチップのピン数の減少、PCIバスにおける帯域幅の増加、システムパフォーマンスの向上あるいはデバイスパフォーマンスの向上のような多くの効果をもたらす。

40

#### 【0007】

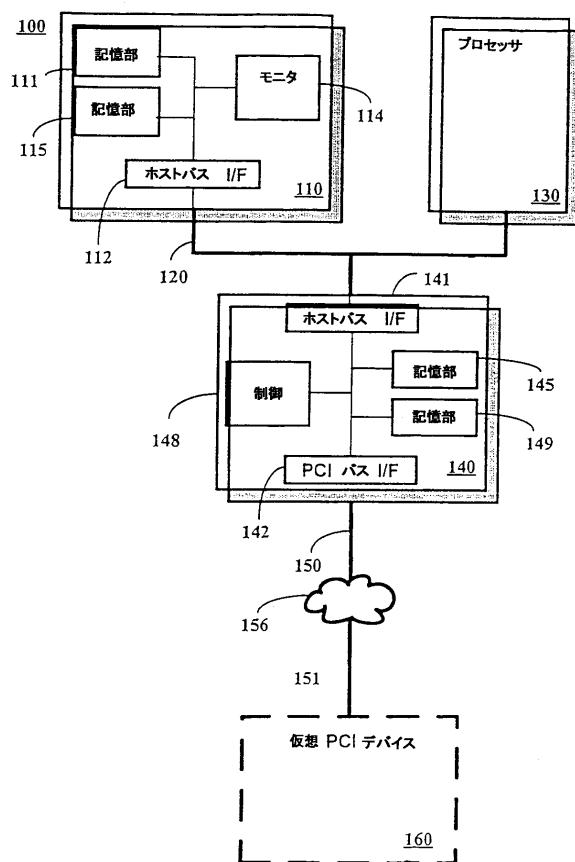

図1a、1b、2、3及び4は、本発明の様々な実施例を説明するためのシステム

10

0、200、300及び400のブロック図を示す。プロセッサ130は、ホストバス120に接続される任意のプロセッサは表しているかもしれない。あるいは、プロセッサ130は、ホストバス120に接続される2つ以上のプロセッサを表しているかもしれない。

#### 【0008】

システム100、200、300及び400は、例えば、ネットワークコントローラ、大容量記憶装置コントローラ、ディスプレイコントローラ、マルチメディアデバイス、通信デバイス、あるいはその他のデバイスとしてのホストバスデバイス110、210及び410を備える。ホストバスデバイス110、210及び410は、ホストバス120をモニタすることを可能にし、存在しない仮想PCIデバイス160を対象としたプロセッサ始動ホストバスサイクルをホストバスデバイス110が遮断できるよう、インターフェース112を介しホストバス120に接続されてもよい。10

#### 【0009】

ホストバスデバイス110、210及び410は、ホストバスサイクルの追跡のためホストバス120に接続されたモニタ回路114を備えてもよい。モニタ回路114は、各ホストバスサイクルにおいて選択された情報を取得し、監視(snoop)あるいは遮断(interccept)される選択されたホストバスサイクルを特定する。リードサイクル(read cycle)は、データをホストバス120に転送するため選択されたホストバスデータ信号を駆動し、そして当該サイクルを終了させることにより遮断される。プロセッサ130により始動されたサイクルは、アクティブなプロセッサ130にホストバス120により利用されているプロトコルに従って、いつ当該サイクルを終了すべきかを通知することにより終了される。ライトサイクル(write cycle)は、ホストバス120のライトサイクルにおける選択されたホストバス120のデータ信号の値をラッチし、その後当該サイクルを終了させることにより遮断される。ホストバス120のサイクルは、選択されたホストバスサイクルの情報を読み出し、それを記憶装置115に保存することにより監視される。ここで、当該サイクルは典型的にはホストバス120に接続された他のデバイスにより終了させられる。20

#### 【0010】

ホストバスデバイス110、210及び410は、記憶装置111のコンテンツがホストバス120を介しアクセス可能となるようホストバス120に接続される記憶装置111を備えてもよい。記憶装置111の様々な実施形態として、システム設定空間またはRAM(Random Access Memory)に備えられたレジスタ216、218及び417、あるいはシステムI/Oまたはメモリアドレス空間に備えられたレジスタやデータポートが含まれてもよい。30

#### 【0011】

PCIプロトコルは、PCIデバイスが備えられる各PCIバスのある個数のアドレス可能なスロットを提供する。PCI-PCIブリッジは、2つのPCIバス間の転送バスを提供するPCIデバイスである。コンピュータプログラムは、典型的に、検出されたPCI-PCIブリッジの直後にある各PCIバスに一意的なバス番号を割り当てる。PCIバス番号とスロット番号の組み合わせは、設定空間を通じシステムにインストールされる任意のPCIデバイスの選択のため、コンピュータプログラムにより利用されるユニークな識別子を提供する。PCIアドレッシング及びルーティングプロトコルは、一般に、あるPCIデバイスがホスト-PCIブリッジと恐らく1つ以上のPCI-PCIブリッジを介し物理的にルーティングされ、ターゲットPCIデバイスが備えられるPCIバスにおけるサイクルを生成する物理階層バス構造を想定している。各PCIバスは、当該PCIバスとホストバスの間の物理的/仮想的データ転送バスにおける任意のPCIバスの後方にあると定義される。40

#### 【0012】

本明細書において、主(primary)PCIバス150は、バス番号が0で、ホスト-PCIブリッジの直後のバスであるかもしれない。しかし、PCIバス150はまた50

、仮想 PCI 装置 150 が後方に現れ、システムに複数の主 PCI バスが存在するため、本発明による方法と適合したバス番号 0 の後方にある任意の PCI バスであってもよい。さらに、主 PCI バス 160 は実際の PCI バスでもよいし、あるいは仮想的なものであってもよい。本明細書において、仮想的と論理的という 2 つの単語は、実際の物理的デバイスや構造を反映しない効果を有する 1 つ以上のプロセッサ 130 上で実行されるコンピュータプログラムの一面を指すものである。仮想 PCI デバイス 160 は、論理的には PCI バス 151 にあり、主 PCI バス 150 を拡張したもの、あるいはそれの下位のものの 1 つ（すなわち、主 PCI バス 150 の後方にあるバス）である。

#### 【0013】

ホスト - PCI ブリッジ 140、240 及び 340 は、選択されたホストバス 120 のサイクルの主 PCI バス 150 及びその下位バス (subordinate bus) への解釈及びルーティングを容易にするかもしれない。ホスト - PCI ブリッジ 140、240 及び 340 は、ホストバスインターフェース 141、PCI バスインターフェース 142、記憶装置 145 及び 149、ホストバス 120 のサイクルを追跡する制御回路 148 を備え、各ホストバスサイクルに対し、当該ホストバスサイクルを実際の主 PCI バス 150 にルーティングすべきかどうか判断するようにしてよい。この判断のため、制御回路 148 は記憶装置 145 を参照し、主 PCI バス 150 とその下位バスに割り当てられているアドレス空間を特定し、記憶装置 149 を参照し、仮想 PCI デバイス 160 あるいは恐らく他の仮想デバイスに割り当てられているアドレス空間を特定する。記憶装置 145 と 149 は、バス番号、メモリアドレスレンジ、I/O アドレスレンジあるいは他の同様の情報の形式で情報を保持している。記憶装置 149 における情報は、仮想 PCI デバイス 160 (より複雑な設定では、仮想デバイスまたはバスのすべてあるいはその一部) に割り当てられているアドレスレンジを示すものであり、一般に、主 PCI バス 150 及びその下位バスに割り当てられる記憶装置 145 におけるアドレス空間の一部であるかもしれない。仮想 PCI デバイスを対象としたホストバスサイクルは、ホストバスデバイス 110、210 及び 310 による遮断が許されている。

#### 【0014】

ホストバス 120 が Pentium 3 または 4 (登録商標) プロセッサを利用しているシステムでは、ホスト - PCI ブリッジ 140、240 及び 340 は、すべてのホストバスサイクルに対し、ホストバスプロトコルに従いすべてのホストバスサイクルが完了したということを保証する応答装置であってもよく、ホストバスデバイス 110 は遮断を行う選択されたホストバスサイクルを要求してもよい。

#### 【0015】

仮想 PCI デバイス 160 を対象とするホストバスサイクルの特定に必要な情報と、この情報の取得方法は、システムのバス構造に依存する。仮想 PCI デバイス 160 の一意的なバスデバイス番号の組み合わせは、仮想 PCI デバイス 160 が主 PCI バス 150 上に論理的に設置されているシステム 100 のホストバスデバイス 110 とホスト - PCI ブリッジの両方に、ハードウェア的に組み込まれるか、あるいはソフトウェア的に予めプログラムされる。

#### 【0016】

システム 100、200、300 及び 400 が、複数のホストバスデバイス 110、210 及び 410 を備えること、あるいは各自がそこに統合された複数のホストバスデバイス 110、210 及び 410 を有する複数のプロセッサ 130 を備えることは、本発明による方法と適合している。本発明による方法は、各自が複数の仮想 PCI デバイス 160 の 1 つと関連付けされる複数のホストバスデバイス 110 からなるシステム 100 に適用することができる。複数の仮想 PCI デバイス 160 の 1 つを対象としたホストバス 120 のサイクルは、ホスト - PCI ブリッジ 140 により主 PCI バス 150 に転送されず、ホストバスデバイス 110 の 1 つが当該サイクルの遮断を許される。複数のホストバスデバイス 110 が、仮想 PCI デバイスに割り当てられているシステムリソースを利用できるよう当該仮想 PCI デバイス 160 に関連付けされる。その反対に、1 つのホストバ

10

20

30

40

50

ステバイス 110 が複数の仮想 PCI デバイス 160 に関連付けされてもよい。さらに、ホストバスデバイス 110 は PCI プロトコルに従い複数の昨日をサポートするよう構成されてもよい。複数のホストバスデバイス 110 が同一の仮想 PCI デバイス 160 に対する遮断を行うことを防ぐための方策は、それに関連付けされた仮想 PCI デバイス 160 を特定する一意的なバスデバイス番号の組み合わせにより、各ホストバスデバイス 110 をハードウェア的に組み込んだり、あるいはソフトウェア的に予めプログラムすることにより実行される。

#### 【 0017 】

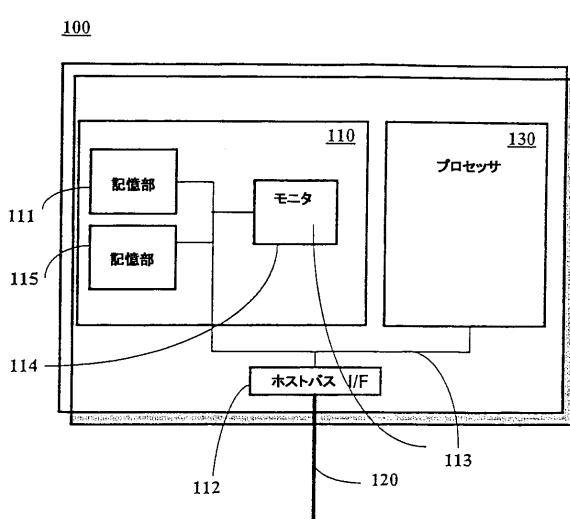

図 1 a は、プロセッサ 130 とのホストバスインターフェースとは異なるインタフェース 112 を介しホストバスに接続されるホストバスデバイス 110 を示す。図 1 b は、プロセッサ 130 とホストバスデバイス 110 が、内部バス 113 及び共有ホストバスインターフェース 112 を介しホストバス 120 に接続されている本発明による方法と適合した他の構成を示す。図 1 b のシステムは、ホストバスデバイス 110 とプロセッサ 130 を 1 つの回路パッケージに統合することにより構成されうる。

#### 【 0018 】

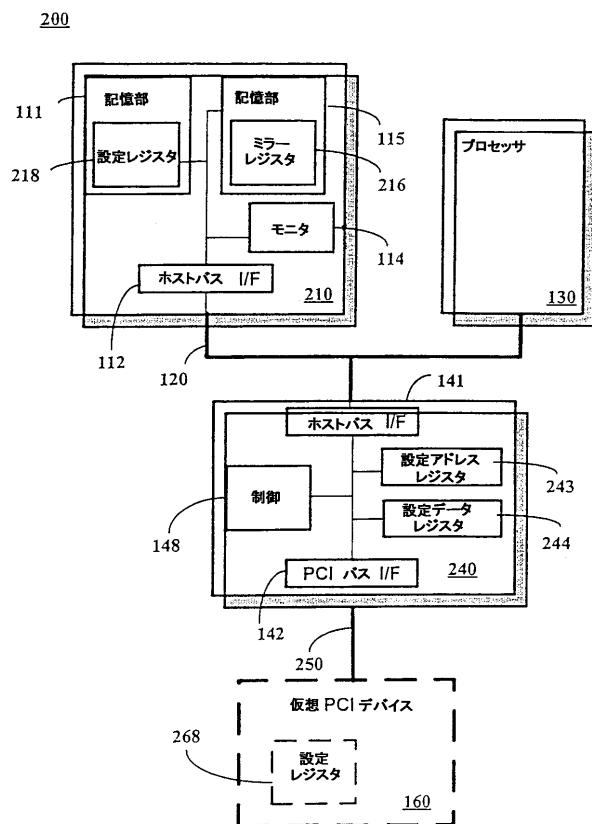

図 2 は、図 1 に示されたシステム 100 の教示に従う本発明の一実施例を説明するシステム 200 を示す。システム 200 は、設定空間を介しアクセス可能な 256 の 8 ビット設定レジスタ 268 を有する、1 つ以上のプロセッサ 130 において実行されるコンピュータプログラムの関し利用される仮想 PCI デバイス 160 を備える。必要かつ関連性のある設定レジスタ 268 のみが実現される。PCI プロトコルによると、ユーザによる操作を必要とせず、システムマップ構成における仮想 PCI デバイスを含む、コンピュータプログラムは仮想 PCI デバイス 160 の検出、仮想デバイス 160 のシステムリソース要件を判断するためのベンダーとデバイスタイプの特定、完全なデバイス再配置の提供、バインディングの中断、インストール、設定及び起動を含む 1 つ以上の機能を達成するため、仮想設定レジスタ 268 へのアクセスを開始してもよい。

#### 【 0019 】

ホストバスデバイス 210 は、本実施例において、PCI に準拠する設定レジスタ 218 からなるホストバス記憶装置 111 を備えてもよい。必要かつ関連性のあるレジスタ 218 のみが実現される。モニタ回路 114 は、ホストバスサイクルを追跡し、ホストバスデバイス設定レジスタ 218 にアクセスするため遮断及びリダイレクトを行う仮想設定レジスタ 268 を対象とするホストバスサイクルを特定する。この結果、プロセッサ 130 上で実行されるコンピュータプログラムは、仮想 PCI デバイス 160 の設定レジスタ 268 を対象とするホストバスサイクルを始動させることにより、ホストバスデバイス設定レジスタ 218 にアクセスすることができる。このように、ホストバスデバイス 210 は、一般に利用可能なシステムリソースに PCI デバイスを割り当てる初期化及び設定処理に入る。

#### 【 0020 】

設定サイクルは、PCI プロトコルにより与えられた 2 つのマッピング機構の 1 つを通じ、システム 200 において生成される。第 1 の機構は、典型的には、ホスト - PCI ブリッジ 240 に含まれる設定アドレスレジスタ 243 と設定データレジスタ 244 のためにプロセッサ I/O スペースの 2 つの固定された場所が予約されるインデックス方式である。設定アドレスレジスタ 243 は、設定空間をイネーブルあるいはディスイネーブルにし、以降の設定サイクルが対象とするバス番号、デバイス番号、機能番号及びレジスタ番号を指定することにより、PCI デバイスと設定レジスタを特定するコンピュータプログラムにより書き込まれる。設定データレジスタ 244 を対象とした以降の D W O R D リード・ライトホストバスサイクルは、典型的には、ホスト - PCI ブリッジ 240 により、PCI に準拠した設定サイクルに変換およびルーティングされる。しかしながら、仮想 PCI デバイス 160 の設置レジスタ 268 を対象としたホストバスサイクルは、PCI プロトコルにより予期されるように、ホスト - PCI ブリッジ 240 によりルーティングされるよりも、ホストバスデバイス 210 により遮断される。

10

20

30

40

50

## 【0021】

第1機構をサポートするシステム200は、監視により取得された選択情報を保持する記憶装置115に含まれるミラーレジスタ216を備えててもよい。設定アドレスレジスタ243を対象としたホストバス120のライトサイクルは、ホストバスデバイス210により監視されてもよいし、監視されたサイクルで転送されるデータは設定アドレスレジスタ243のコンテンツを反映するミラーレジスタ216に格納されてもよい。モニタ回路114は、仮想設定レジスタ268にアクセスする設定データレジスタ244を対象とした以降のD W O R D ホストバス120のサイクルを特定するため、ミラーレジスタ216を参照してもよい。これらの特定されたサイクルは、ホストバスデバイス210により遮断され、ホストバスデバイス210の対応する設定レジスタ218にアクセスするためリダイレクトされる。

10

## 【0022】

また、システム200は、第2の機構をサポートするものであってもよい。この第2の機構では、典型的には、ホスト - P C I ブリッジ240に配置される設定空間イネーブルレジスタ(図示せず)と転送レジスタ(図示せず)が、プロセッサI/Oアドレス空間における固定された場所にマップされる設定空間の4kバイトを指定するコンピュータプログラムにより書き込みされる。第2機構をサポートするよう設計されたシステム200は、設定空間イネーブルレジスタ(図示せず)と転送レジスタ(図示せず)を対象とした検索されたホストバスライトサイクルを格納するミラーレジスタ216を備えててもよい。仮想デバイスの設定レジスタ268を対象としたホストバスサイクルを特定するため、ミラーレジスタ216がモニタ回路114により参照されてもよい。特定されたサイクルは、ホストバスデバイス210により遮断され、ホストバスデバイス210の対応する設定レジスタ218にアクセスするようリダイレクトされる。

20

## 【0023】

P C I プロトコルに従って、設定レジスタは、割り込み、プロセッサメモリアドレス空間、プロセッサI/Oアドレス空間、及びR O M ( R e a d O n l y M e m o r y )に予約されたプロセッサメモリアドレス空間のレンジであるR O Mアドレス空間を含むシステムリソースの割当を実行するコンピュータプログラムにより利用されてもよい。コンピュータプログラムは、仮想P C I デバイス160のシステム要件を判断し、選択された設定レジスタ268への書き込みにより仮想P C I デバイス160にリソースを割り当てるため、存在しない仮想設定レジスタ268へのアクセスを開始してもよい。コンピュータプログラムはまた、致命的なエラーを処理すると共に、内蔵されている自己診断テスト(B I S T)の実行及びその状態の取得を行う仮想デバイスの設定レジスタ268にアクセスするようにしてよい。

30

## 【0024】

選択的には、ホストバスデバイス設定レジスタ218は、例えば、仮想P C I デバイス260に割り当てられるメモリ空間またはI/O空間の1つ以上のレンジである特定のシステムリソースのリクエストを示すよう実現されてもよい。内部記憶装置111の一部は、コンピュータプログラムにより、ホストバス120を介したアクセスのため当該アドレス空間にマップされてもよい。コンピュータプログラムによるアドレス空間の仮想P C I デバイス160への割当後、この選択的実施例において、モニタ回路114は、ホストバスサイクルが仮想P C I デバイス160に割り当てられるメモリあるいはI/O空間を対象としているかどうか特定するため、適当な設定レジスタ218を参照するようにしてよい。これら特定されたサイクルは、ホストバスデバイス210により遮断され、ホストバス記憶装置111にアクセスするようリダイレクトされてもよい。

40

## 【0025】

ホストバスデバイス210とホスト - P C I ブリッジ240は、仮想P C I デバイス160のバス番号とデバイス番号を把握するようにしてよい。このような情報は、ハードウェア的に組み込まれてもよいし、ソフトウェア的に予めプログラムされてもよいし、あるいはシステムの初期化においてプログラムにより提供されるようにしてよく、仮想P

50

C I デバイス 160 の設定空間を対象としたホストバスサイクルの特定に利用される。ホスト - P C I ブリッジ 240 は、仮想 P C I デバイス 160 に割り当てられたアドレス空間を指定する仮想設定レジスタ 268 を対象とする選択されたホストナスライトサイクルを監視することにより、仮想 P C I デバイス 160 に割り当てられたアドレス空間を把握ようにしてもよい。

#### 【 0 0 2 6 】

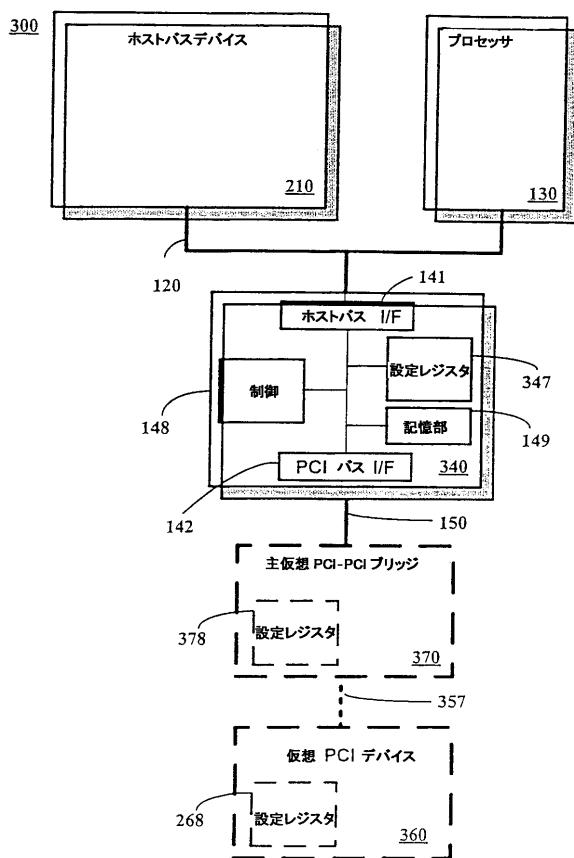

図 3 は、システム 100 及び 200 の教示に従う本発明の一実施例を説明するシステム 300 を示す。システム 300 は、設定空間にアクセスする第 1 機構を実現したものである。システム 300 は、プロセッサ 130 上で実行されるコンピュータプログラムに対し、主 P C I バス 150 上の配置として、そして主仮想 P C I バス 357 へのブリッジとして利用される主仮想 P C I - P C I ( P - P ) ブリッジ 370 から構成されてもよい。仮想 P C I デバイス 360 は、プロセッサ 130 上で実行されるコンピュータプログラムに対して、主仮想バス 357 上の配置として利用されてもよい。

10

#### 【 0 0 2 7 】

本実施例において、ホストバスデバイス 210 とホスト - P C I ブリッジ 340 は共に、主仮想 P C I - P C I ブリッジ 370 配置されているバス番号とデバイス番号を把握し、ホストバスデバイス 210 は仮想 P C I デバイス 360 のデバイス番号を把握している。この情報は、初期化プログラムにより与えられてもよいし、ハードウェア的に組み込まれても、ソフトウェア的に予めプログラムされていてもよい。

20

#### 【 0 0 2 8 】

ホスト - P C I ブリッジ 340 は、本実施例において、例えば、プラグ・アンド・プレイ（登録商標）リソース割当プログラムのような、主 P C I バス 150 にアドレス空間を割り当てるため、コンピュータプログラムにより書き込まれる、仮想デバイス 160 に割り当たるすべてのアドレス空間を網羅する記憶装置 149 を備えてよい。記憶装置 149 に格納される情報は、主 P C I バス 357 の後方にある仮想バス（図示せず）のバス番号を含むものであってもよい。通常、バス番号は、主 P C I バス 357 やその下位バスに割り当たる設定空間を決定するのに十分な情報である。選択的に、記憶装置 149 には、主 P C I バス 357 と下位バスに割り当たるメモリ空間または I / O 空間が含まれてもよい。本実施例では、プラグ・アンド・プレイ（登録商標）プロトコルに従つて、主 P C I バス 357 に割り当たったアドレス空間は、典型的には、選択的な下位バス（図示せず）と仮想 P C I デバイス 160 に割り当たったアドレス空間を網羅し、これにより、仮想 P C I バス 357 と選択的な下位仮想バスを対象としたホストバスサイクルの特定のため、ホスト - P C I ブリッジ 340 による容易かつ効率的復号化が可能となる。

30

#### 【 0 0 2 9 】

ホスト - P C I ブリッジ 340 は、主仮想 P C I - P C I ブリッジ 370 の仮想設定レジスタ 378 を対象としたホストバスサイクルの特定、及びこれら特定されたサイクルのホスト - P C I ブリッジ設定レジスタ 347 へのルーティングを実行するため、制御回路 148 により参照されるブリッジ設定レジスタ 347 を備えてよい。本実施例において、制御回路 148 は、ホストバスサイクルを主 P C I バス 150 にルーティングすべきか判断するため、ブリッジ設定レジスタ 347 及び記憶装置 145 と 149 を参照するようにしてよい。

40

#### 【 0 0 3 0 】

ホストバスデバイス 210 は、主仮想 P C I - P C I ブリッジ 370 の設定レジスタ 378 を対象としたホストバスサイクルを生成し、コンピュータプログラムにより主仮想 P C I バス 357 に割り当たったバス番号を取得し、この情報を監視により取得される選択された情報を保持する記憶装置 115 に格納するようにしてよい。1 つのホストバスデバイス 210 のみを有するシステムは、デバイス番号を仮想 P C I デバイス 160 に任意に割り当てもよい。複数のホストバスデバイス 210 を有するシステムは、ハードウェア的に組み込まれてもよいし、ソフトウェア的に予めプログラムされてもよいし、初

50

期化プログラムにより格納されてもよい一意的なデバイス番号（すなわち、スロット番号）を各ホストバスデバイス210に与えるなど、各ホストバスデバイス210を相異なる仮想PCIデバイス360に関連付けるための機構を要するかもしれない。

#### 【0031】

図4は、図3に示されるシステム300の教示に従う本発明の一実施例を説明するためのシステム400を示す。ホストバスデバイス410は、ホストバスデバイス210と310に対し与えられた説明に従うものであってもよい。システム400は、設定空間にアクセスする第1機構を実現するものである。システム400はさらに、副(secondary)仮想PCIバス451に直接接する副仮想PCI-PCIブリッジ490を備える。副仮想PCI-PCIブリッジ490は、プロセッサ130上で実行されるコンピュータプログラムの観点から、主仮想PCIバス上の配置に利用され、仮想PCIデバイス160は副仮想PCIバス451に論理的に配置されてもよい。10

#### 【0032】

副仮想バス451は、主仮想PCIバス357に従属し、本実施例では、副仮想バス451と仮想PCIデバイス160に割り当てられるアドレス空間は、主仮想PCIバス357に割り当てられるアドレス空間内にある。ホスト-PCIブリッジ340は、主PCIバス150とその下位バスを対象とするホストバスサイクルの特定及びルーティングのため記憶装置145を参照し、主仮想バス357とその下位バスを対象とするホストバスサイクルの特定のため記憶装置149を参照する。主仮想バス357とその下位バスを対象とするホストバスサイクルは、主PCIバス450に転送されず、ホストバスデバイス410による遮断が許可される。ホスト-PCIブリッジ340は、ホストバスプロトコルに従い、遮断したホストバス430のサイクルを完了（すなわち終了）させることができる。20

#### 【0033】

ホストバスデバイス410は、ホストバスに接続され、プロセッサ130にアクセス可能な記憶装置111を備えてよい。記憶装置111は、仮想PCIデバイス160の設定レジスタ268を対象とするホストバスサイクルによりアクセスされるデバイス設置レジスタ218を備えてよい。さらに、記憶装置111は、仮想副PCI-PCIブリッジ490の仮想設定レジスタ497を対象としたホストバスサイクルによりアクセスされるブリッジ設定レジスタ417を備えてよい。30

#### 【0034】

本実施例では、システム300と同様に、ホストバスデバイス410とホスト-PCIブリッジ340は、主仮想PCI-PCIブリッジ370が配置されるバス番号とデバイス番号を把握している。この情報は、初期化プログラムにより提供されてもよいし、ハードウェア的に組み込まれていてもよいし、ソフトウェア的に予めプログラムされていてもよい。さらに、本実施例において、ホストバスデバイス410は、主仮想PCI-PCIブリッジ370の設定レジスタ378を対象としたホストバスサイクルを監視することによって、主仮想PCIバス357とその下位バスに割り当てられたバス番号を取得してもよい。単一のホストバスデバイス410からなるシステム400では、副仮想PCI-PCIブリッジ490のデバイス番号は任意に割り当てることができる。40

#### 【0035】

複数のホストバスデバイス410からなるシステムでは、例えば、関連付けされた副仮想PCI-PCIブリッジ490の一意的なデバイス番号を各ホストバスデバイス410に割り当てるような、各ホストバスデバイスを相異なる副仮想PCI-PCIブリッジ490に関連付けるための機構が必要となり、この割り当ては、ハードウェア的に組み込まれてもよいし、ソフトウェア的に予めプログラムされてもよいし、あるいは初期化プログラムにより実行されてもよい。各ホストバスデバイス410は、コンピュータプログラムによる書き込み後、関連付けされている副仮想PCI-PCIブリッジの直後の副仮想バス451に割り当てられているバス番号を決定するため、その内部設定レジスタ417を参照し、各仮想PCIデバイス460にデバイス番号を任意に割り当てる。この情報は、50

システム 100 に関して説明された方法と同様にして、仮想 PCI デバイス 160 を対象としたホストバスサイクルの特定のため、モニタ回路 114 により参照されてもよい。各ホストバスデバイス 410 は、各々がそれに関連付けされた副仮想 PCI バス 451 に論理的に配置される相異なる仮想デバイス 160 と関連付けされている複数の物理的なデバイスを備えてもよい。プラグ・アンド・プレイ（登録商標）プログラムは、典型的には、各副仮想 PCI - PCI ブリッジ 490 の後方に配置されたすべての仮想デバイス 160 に割り当てられるリソースを分類し、その結果、遮断されるサイクルの特定のため各ホストバスデバイス 410 によるホストバスサイクルの復号化が容易になる。例えば、単一のメモリアドレスレンジが、各デバイスに割り当てられた複数のレンジを網羅する副仮想 PCI - PCI ブリッジ 490 に割り当てられてもよい。

10

#### 【0036】

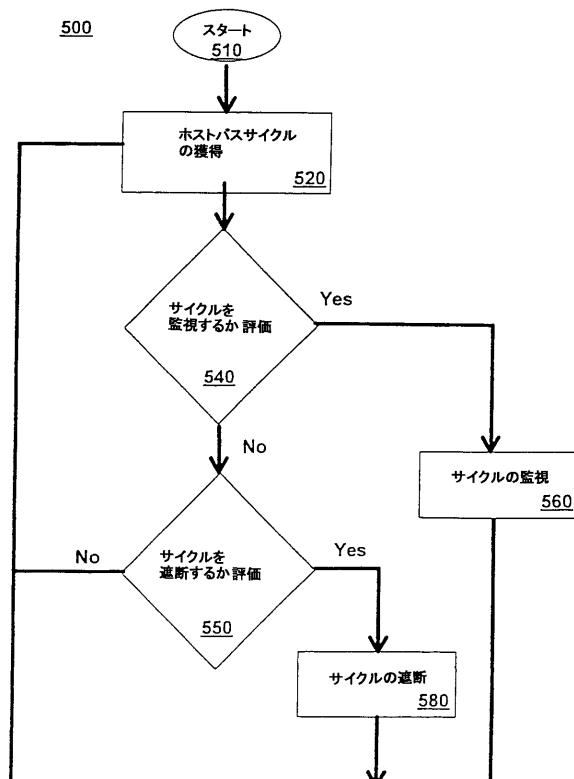

図 5 は、システム 100、200、300 及び 400 により利用され、モニタ回路 114 により実行される本発明による方法 500 を説明するフロー図を示す。スタートステップ 510 は、記憶装置とレジスタにデフォルト値を設定するホストバスのリセットである。各ホストバスサイクルに対し、以下の各ステップが実行される。獲得ステップ 520 は、ホストバスサイクルを待機し、カレントホストバスサイクルの対象を示す選択されたホストバスアドレスと制御信号の受信及びラッチングに関する処理である。次の評価ステップ 540 は、獲得した各サイクルを評価し、遮断ステップ 550 に進むか、監視ステップ 560 に進むか判断する。監視ステップ 560 は、選択されたホストバスデータ信号の受信及び格納に関する処理である。評価ステップ 550 は、獲得した各サイクルを評価し、カレントサイクルに対し処理を行わず、ステップ 520 に進み、次のホストバスサイクルを獲得するか、あるいはサイクルの遮断ステップ 580 に進み、ホストバス記憶装置 111 内の適当な場所にアクセス（すなわち、読み出し、または書き込み）するため、カレントホストバスサイクルをルーティングさせるかどうか判断する。ステップ 540 と 550 はパラレルに実行されてもよいし、何れか一方が先行して実行されてもよい。

20

#### 【0037】

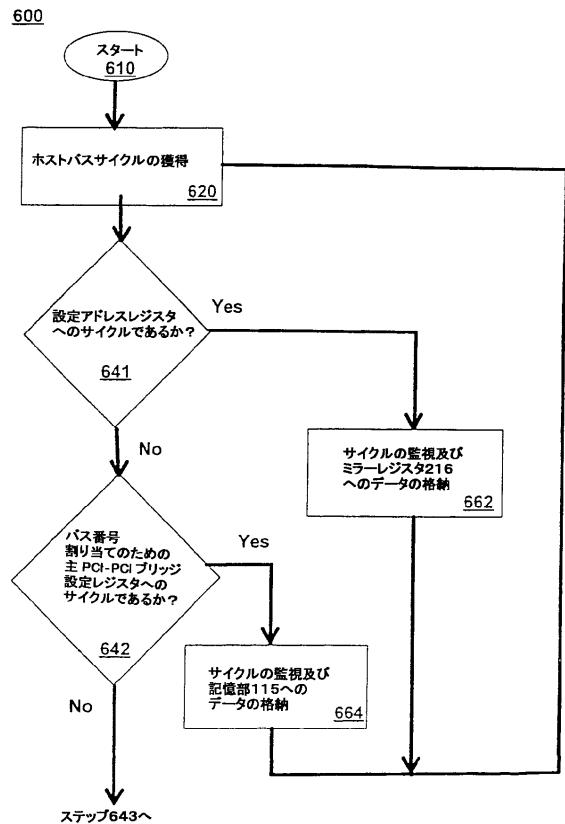

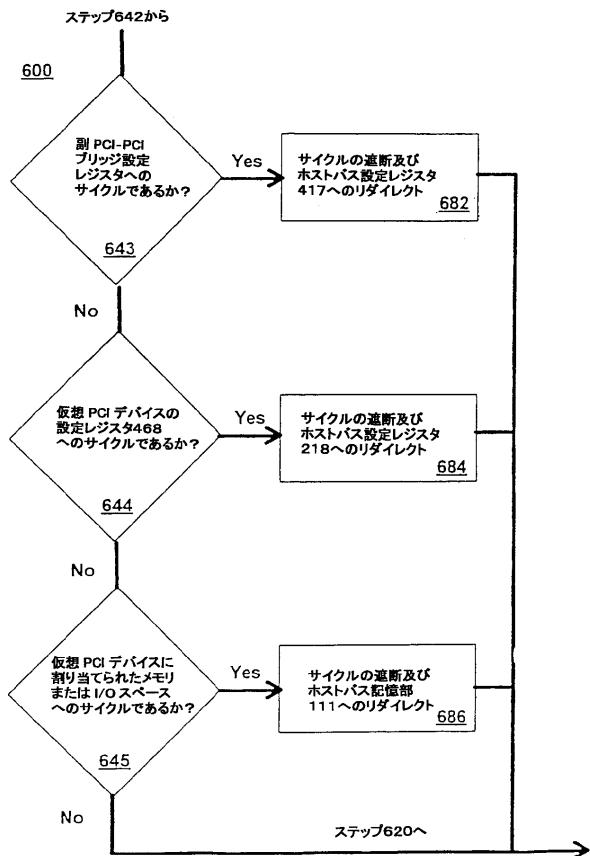

図 6 a 及び図 6 b は、図 4 に示されたシステム 400 のモニタ回路 114 により実行される方法 600 を説明するフロー図を示す。スタートステップ 610 及び獲得ステップ 620 は、それぞれステップ 510 と 520 に関する説明と同様である。評価ステップ 540 及び監視ステップ 560 は、ステップ 641、642、662 及び 664 によりなされる。同様に、評価ステップ 550 及び遮断ステップ 580 は、ステップ 643、644、645、682、684 及び 686 によりなされる。評価ステップ 641 ~ 645 はホストバスサイクルのアドレス段階において実質的にパラレルに実行され、監視ステップ 662 及び 664、あるいは遮断ステップ 682、684 及び 686 が実行される場合、当該監視あるいは遮断ステップはホストバスサイクルのデータ段階において実行される。監視されたサイクルは、ホストバスデバイス 410 以外のデバイスにより完了させられ（例えば、終了させられ）、遮断されたサイクルはホストバスデバイス 410 により完了させられる。

30

#### 【0038】

評価ステップ 641 では、獲得されたカレントホストバスサイクルが設定アドレスレジスタ 243 を対象としているか評価される。肯定的に評価されると、ステップ 662 に進み、獲得されたカレントサイクルにより転送されるデータが監視され、このデータの一部あるいは前部がミラーレジスタ 216 に格納される。否定的に評価されると、ステップ 642 に進む。

40

#### 【0039】

評価ステップ 642 では、獲得されたホストバスサイクルが、主仮想 PCI - PCI ブリッジ 370 にバス番号を割り当てるため、特定の仮想設定レジスタ 378 を対象としているかどうか評価される。この評価が肯定されるには、（ミラーレジスタ 216 のコンテンツにより反映されるような）設定アドレスレジスタ 243 が、設定空間がイネーブルであることを示す値と、主仮想バス 357 に割り当てるバス番号を指定する主仮想 PCI

50

I - PCI ブリッジ 370 の設定レジスタ 378 を現在指定している値を有することが要求される。また、肯定的な評価には、獲得されたサイクルが設定データレジスタ 244 を対象にしたリード / ライトホストバスサイクルであることが要求される。ステップ 642において肯定的な評価がなされると、監視ステップ 664 に進み、カレントサイクルで転送される一部あるいはすべてのホストバス 120 のデータが記憶装置 115 にラッチ及び格納される。

#### 【 0040 】

評価ステップ 643 では、カレントサイクルが副 PCI - PCI ブリッジ 490 の設定空間を対象としているかどうか評価される。この評価が肯定されるには、(ミラーレジスタ 216 のコンテンツにより反映されるような) 設定アドレスレジスタ 243 が、設定空間がイネーブルであることを示す値と、副 PCI - PCI ブリッジ 490 の設定レジスタ 497 を現在指定している値を有することが要求される。また、肯定的な評価には、獲得されたサイクルが設定データレジスタ 244 を対象としたリード / ライトホストバスサイクルであることが要求される。ステップ 643 において肯定的な評価がなされると、遮断ステップ 682 に進み、カレントホストバスサイクルが副仮想 PCI - PCI ブリッジ 490 の設定レジスタ 417 にルーティングされる。ここで、評価される設定レジスタ 417 は、ミラーレジスタ 216 の現在のコンテンツにより決定される。

#### 【 0041 】

評価ステップ 644 では、獲得したホストバスサイクルが仮想 PCI デバイス 160 の設定空間を対象としているかどうか評価される。この評価が肯定されるには、(ミラーレジスタ 216 のコンテンツにより反映されるような) 設定アドレスレジスタ 243 が、設定空間がイネーブルであることを示す値と、仮想 PCI デバイス 160 の設定レジスタ 268 を現在指定している値を有することが要求される。また、獲得されたサイクルが設定データレジスタ 244 を対象にしたリード / ライトホストバスサイクルであることが要求される。ステップ 644 において肯定的な評価がなされると、遮断ステップ 684 に進み、ミラーレジスタ 216 のコンテンツにより示されるように、ホストバス設定レジスタ 218 にアクセスするようカレントホストバスサイクルはルーティングされる。

#### 【 0042 】

評価ステップ 645 では、獲得されたホストバスサイクルが、コンピュータプログラムにより仮想 PCI デバイス 160 に割り当てられたメモリまたは I/O アドレス空間を対象としているどうかが評価される。仮想 PCI デバイス 460 に割り当てられたメモリあるいは I/O 空間を特定する設定レジスタ 218 が以前に設定されていない場合、評価結果は常に否定的なものとなる。PCI 設定レジスタ 218 の現在のコンテンツにより決定されるように、仮想 PCI デバイス 160 に割り当てられたアドレス空間が、獲得されたホストバスサイクル情報と比較される。カレントホストバスサイクルの対象が仮想 PCI デバイス 160 に割り当てられたアドレス空間内のものである場合、ステップ 686 に進み、獲得されたホストバスサイクルのアドレス及び制御信号により示されるように、カレントホストバス 420 のサイクルが適当な内部記憶装置 111 にルーティングされる。

#### 【 0043 】

ここで説明された機能が、本発明の意図を留める限り、説明された以外の物理的デバイスにおいて実現されうるということは当業者には理解されるであろう。

#### 【 0044 】

本発明は PCI システムに適用したものとして説明されてきたが、ここで教示された方法は、ホストバス及び (PCI に準拠したバスに類似の) 周辺バスを有する任意のシステムにより利用可能であり、システムのプロセッサ上で実行されるコンピュータプログラムに対し、周辺バスにおける配置として利用されるホストバスに接続されたデバイスを備えることにより効果が得られるということは当業者には理解されるであろう。

#### 【 図面の簡単な説明 】

#### 【 0045 】

【図 1a】図 1a は、本発明によるシステム構成を示す。

10

20

30

40

50

【図1b】図1bは、本発明によるシステム構成を示す。

【図2】図2は、さらなる詳細なシステム構成を示す。

【図3】図3は、主仮想ブリッジを備えたシステムを示す。

【図4】図4は、主仮想ブリッジと副仮想ブリッジを備えたシステムを示す。

【図5】図5は、本発明の一例となる方法のフロー図を示す。

【図6a】図6aは、本発明の一例となる方法のフロー図を示す。

【図6b】図6bは、本発明の一例となる方法のフロー図を示す。

【図1a】

【図1b】

【図2】

【図3】

【図4】

【図5】

【図 6 a】

【図 6 b】

---

フロントページの続き

(72)発明者 ランゲンドルフ, ブライアン

アメリカ合衆国 94510 カリフォルニア州 ベニーシャ センブルズ クロッシング 27

2

合議体

審判長 江口 能弘

審判官 清水 稔

審判官 鈴木 重幸

(56)参考文献 米国特許6629157第(US, B1)

特開平11-167523(JP, A)

米国特許第6108719(US, A)

(58)調査した分野(Int.Cl., DB名)

G06F 13/14, G06F 13/36