(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2018-511234

(P2018-511234A)

(43) 公表日 平成30年4月19日(2018.4.19)

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>HO4N 19/85 (2014.01)</b>  | HO4N 19/85  | 5C159       |

| <b>HO4N 19/13 (2014.01)</b>  | HO4N 19/13  |             |

| <b>HO4N 19/176 (2014.01)</b> | HO4N 19/176 |             |

| <b>HO4N 19/136 (2014.01)</b> | HO4N 19/136 |             |

| <b>HO4N 19/159 (2014.01)</b> | HO4N 19/159 |             |

審査請求 未請求 予備審査請求 有 (全 45 頁) 最終頁に続く

|               |                              |          |                                                                                                                |

|---------------|------------------------------|----------|----------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2017-546593 (P2017-546593) | (71) 出願人 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (86) (22) 出願日 | 平成28年1月4日 (2016.1.4)         | (74) 代理人 | 100108855<br>弁理士 蔡田 昌俊                                                                                         |

| (85) 翻訳文提出日   | 平成29年10月19日 (2017.10.19)     | (74) 代理人 | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (86) 國際出願番号   | PCT/US2016/012064            | (74) 代理人 | 100158805<br>弁理士 井関 守三                                                                                         |

| (87) 國際公開番号   | W02016/144418                | (74) 代理人 | 100112807<br>弁理士 岡田 貴志                                                                                         |

| (87) 國際公開日    | 平成28年9月15日 (2016.9.15)       |          |                                                                                                                |

| (31) 優先権主張番号  | 62/129,290                   |          |                                                                                                                |

| (32) 優先日      | 平成27年3月6日 (2015.3.6)         |          |                                                                                                                |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                                |

| (31) 優先権主張番号  | 14/724,108                   |          |                                                                                                                |

| (32) 優先日      | 平成27年5月28日 (2015.5.28)       |          |                                                                                                                |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                                |

最終頁に続く

(54) 【発明の名称】コード化パラメータのHEVC予測についての利用可能性検査を低減するためのパディング

## (57) 【要約】

本開示は、ビデオデータを符号化するためのシステム及び方法を提供する。本方法は、メモリにデータ構造を記憶することを含むことができ、データ構造が、第1のビデオデータブロックの第2の複数のデータ要素に対応する、及び外周を画定する、配置された第1の複数のデータ要素を有し、データ構造が、第1のビデオデータブロックのための最小予測単位(PU)の全てに関係するデータを更に含む。本方法はまた、第1の複数のデータ要素の外周に沿って複数の拡張単位を追加することによって、メモリ中のデータ構造のサイズを増加することを含むことができ、各拡張単位が、第1のビデオデータブロックの最小データ要素に関係するデータを有し、拡張単位がデフォルト値に設定される。本方法はまた、データ構造に基づいて第1のビデオデータブロックを符号化することを備えることができる。

FIG. 6A

**【特許請求の範囲】****【請求項 1】**

ビデオデータを符号化する方法であって、

メモリにデータ構造を記憶することと、前記データ構造が第1の複数のデータ要素を有し、外周を画定し、前記第1の複数のデータ要素がピクチャの第1の部分の第2の複数のデータ要素に対応して配置され、前記データ構造が、ピクチャの前記第1の部分のための最小予測単位( P U )の全てに関係するデータを更に含む、

前記第1の複数のデータ要素の前記外周に沿って複数の拡張単位を追加することを備えることによって、前記メモリ中の前記データ構造のサイズを増加することと、前記複数の拡張単位の各拡張単位が、ピクチャの前記第1の部分の最小データ要素に関係するデータを有する、

前記複数の拡張単位の各拡張単位と前記第1の複数のデータ要素とをデフォルト値に設定することと、

前記データ構造に基づいてピクチャの前記第1の部分を符号化することとを備える、方法。

**【請求項 2】**

前記データ構造に基づいて前記第2の複数のデータ要素の各データ要素に対して利用不可能性検査を実行することを更に備える、請求項1に記載の方法。

**【請求項 3】**

ピクチャの前記第1の部分の現在 C U の C U 深度と少なくとも1つの隣接 C U の C U 深度とに基づいて、前記現在 C U のためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化( C A B A C )コンテキストを決定することを更に備え、前記現在 C U が前記第2の複数のデータ要素のうちのデータ要素であり、前記少なくとも1つの隣接 C U が前記第1の複数のデータ要素のうちのデータ要素である、請求項2に記載の方法。

**【請求項 4】**

少なくとも1つの隣接コード化単位( C U )がスキップモードに設定されるかどうかに基づいて、ピクチャの前記第1の部分の現在 C U のためのスキップフラグのためのコンテキスト適応型バイナリ算術コード化( C A B A C )コンテキストを決定することを更に備え、前記現在 C U が前記第2の複数のデータ要素のうちのデータ要素であり、前記少なくとも1つの隣接 C U が前記第1の複数のデータ要素のうちのデータ要素である、請求項2に記載の方法。

**【請求項 5】**

ピクチャの前記第1の部分の現在 P U の隣接 P U がインター モード予測に設定されると決定することと、

前記隣接 P U に基づいて前記現在 P U のためのマージ候補を決定することと、前記隣接 P U が前記第1の複数のデータ要素のうちのデータ要素である、を更に備える、請求項2に記載の方法。

**【請求項 6】**

ピクチャの前記第1の部分の現在 P U の隣接 P U がインター モード予測に設定されると決定することと、

前記隣接 P U に基づいて前記現在 P U の動き予測子を決定することと、前記隣接 P U が前記第1の複数のデータ要素のうちのデータ要素である、を更に備える、請求項2に記載の方法。

**【請求項 7】**

隣接 P U に基づいて、ピクチャの前記第1の部分の現在 P U のためのイントラ予測モードを予測することを更に備え、前記隣接 P U が前記第1の複数のデータ要素のうちのデータ要素である、請求項2に記載の方法。

**【請求項 8】**

更新されたデータ構造を形成するためにピクチャの第2の部分のサイズ及び形状に基づいて前記データ構造の前記複数の拡張単位を更新することと、

10

20

30

40

50

更新された前記データ構造に基づいてピクチャの前記第2の部分を符号化することとを更に備える、請求項1に記載の方法。

#### 【請求項9】

前記データ構造に基づいてピクチャの前記第1の部分を符号化することが、ピクチャの前記第1の部分を符号化するために空間予測のための参照として前記複数の拡張単位を使用することを備える、請求項1に記載の方法。

#### 【請求項10】

ピクチャの前記第1の部分の前記最小データ要素が、予測単位又はコード化単位を備える、請求項1に記載の方法。

#### 【請求項11】

ビデオデータを符号化するための装置であって、

第1の複数のデータ要素を有し、外周を画定するデータ構造を記憶するように構成されたメモリと、前記第1の複数のデータ要素はピクチャの第1の部分の第2の複数のデータ要素に対応して配置され、前記データ構造がピクチャの前記第1の部分のための最小予測単位(PU)の全てに関係するデータを更に含む、

前記メモリに動作可能に結合され、

前記第1の複数のデータ要素の前記外周に沿って複数の拡張単位を追加することを備えることによって、前記メモリ中の前記データ構造のサイズを増加することと、前記複数の拡張単位の各拡張単位が、ピクチャの前記第1の部分の最小データ要素に関係するデータを有する、

前記複数の拡張単位の各拡張単位と前記第1の複数のデータ要素とをデフォルト値に設定することと、

前記データ構造に基づいてピクチャの前記第1の部分を符号化することとを行うように構成されたプロセッサとを備える、装置。

#### 【請求項12】

前記プロセッサが、前記データ構造に基づいて前記第2の複数のデータ要素の各データ要素に対して利用不可能性検査を実行するように更に構成された、請求項11に記載の装置。

#### 【請求項13】

ピクチャの前記第1の部分の現在CUと少なくとも1つの隣接CUのCU深度に基づいて、スプリットフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することと、前記現在CUが前記第2の複数のデータ要素のうちのデータ要素であり、前記少なくとも1つの隣接CUが前記第1の複数のデータ要素のうちのデータ要素である、

前記少なくとも1つの隣接CUがスキップモードに設定されるかどうかに基づいて、ピクチャの前記第1の部分の前記現在CUのためのスキップフラグのためのCABACコンテキストを決定することと、

ピクチャの前記第1の部分の現在PUの隣接PUがインター モード予測に設定されると決定することと、前記隣接PUに基づいて前記現在PUのためのマージ候補を決定することと、前記隣接PUが前記第1の複数のデータ要素のうちのデータ要素である、

前記現在PUの前記隣接PUがインター モード予測に設定されると決定することと、前記隣接PUに基づいて前記現在PUの動き予測子を決定することと、

前記隣接PUに基づいて、ピクチャの前記第1の部分の前記現在PUのためのイントラ予測モードを予測することとのうちの少なくとも1つを完了するように更に構成された前記プロセッサ、請求項11に記載の装置。

#### 【請求項14】

前記プロセッサが、

更新されたデータ構造を形成するためにピクチャの第2の部分のサイズ及び形状に基づ

10

20

30

40

50

いて前記データ構造の前記複数の拡張単位を更新することと、

前記更新されたデータ構造に基づいてピクチャの前記第2の部分を符号化することとを行うように更に構成された、請求項11に記載の装置。

**【請求項15】**

前記プロセッサが、ピクチャの前記第1の部分を符号化するために空間予測のための前記複数の拡張単位を参照するように更に構成された、請求項11に記載の装置。

**【請求項16】**

前記プロセッサが、前記デフォルト値を、

コード化単位深度が0に等しい、

予測モードがイントラ予測に設定される、及び

イントラ予測モードがDC予測に設定される、

に設定するように更に構成された、請求項11に記載の装置。

10

**【請求項17】**

ピクチャの前記第1の部分の前記最小データ要素が、予測単位又はコード化単位を備える、請求項11に記載の装置。

**【請求項18】**

ピクチャの前記第1の部分が、スライス又はタイルを備える、請求項11に記載の装置。

**【請求項19】**

ピクチャの部分中のビデオデータを符号化する方法であって、

データ構造中の第1の複数の予測単位(PU)の各PUに關係するデータを記憶することと、前記データ構造がコード化ツリー単位(CTU)のサイズを有する、

20

前記データ構造中の前記第1の複数のPUの外周に沿って配設された複数の拡張単位の各拡張単位毎に拡張データを記憶することと、

前記データ構造に基づいて第1のCTUを符号化することと、

第1の更新されたデータ構造を形成するために前記第1のCTUのPUの最右列に關係するデータを用いて前記データ構造中の前記複数の拡張単位の最左列を更新することと、

前記第1の更新されたデータ構造に基づいて第2のCTUを符号化することと

を備える、方法。

30

**【請求項20】**

要素ラインバッファに前記第1のCTUのPUの最下行に關係するデータを記憶することと、前記要素ラインバッファが、ピクチャの部分の幅に等しい第2の複数のPUに關係するデータを記憶するように構成された、

前記要素ラインバッファに前記第2のCTUのPUの最下行に關係するデータを記憶することと、

ピクチャの前記部分中のCTUの第1の行を符号化した後に、デフォルト値を用いて、前記データ構造中の前記複数の拡張単位の前記最左列と前記データ構造中の前記第1の複数のPUとを更新することと、CTUの前記第1の行が前記第1のCTUと前記第2のCTUとを含む、

40

第2の更新されたデータ構造を形成するために前記要素ラインバッファからのデータを用いて前記第1の更新されたデータ構造中の前記複数の拡張単位の最上行を更新することと、

前記第2の更新されたデータ構造に基づいてCTUの第2の行上の第3のCTUを符号化することと

を更に備える、請求項19に記載の方法。

**【請求項21】**

前記データ構造に基づいて前記第1のCTUを符号化することが、前記第1のCTUを符号化するために空間予測のための参照として前記複数の拡張単位を使用することを備える、請求項19に記載の方法。

50

**【請求項22】**

前記第1の複数のPUの各PUが、前記第1のCTUのための最小PUを含み、前記第1の複数のPUの各PUに関係する前記データが、少なくとも、コード化単位深度、予測モード及びインター予測モードを備える、請求項19に記載の方法。

【請求項23】

前記複数の拡張単位の各拡張単位がデフォルト値を有するように設定され、前記デフォルト値は、

コード化単位深度が0に等しい、

予測モードがイントラ予測に設定される、及び

イントラ予測モードがDC予測に設定される、

を備える、請求項19に記載の方法。

10

【請求項24】

前記データ構造に基づいて前記CTUの複数のコード化単位(CU)の各CUに対して利用不可能性検査を実行することを更に備える、請求項19に記載の方法。

【請求項25】

前記第1のCTUの現在CUのCU深度と前記データ構造の少なくとも1つの隣接PUのCU深度とに基づいて、前記現在CUのためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することを更に備え、前記現在CUが前記複数のCUのうちのCUであり、前記少なくとも1つの隣接PUが前記第1の複数のPUのうちのPUである、請求項24に記載の方法。

20

【請求項26】

少なくとも1つの隣接PUがスキップモードに設定されるかどうかに基づいて、前記CTUの現在CUのためのスキップフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することを更に備え、前記現在CUが前記複数のCUのうちのCUであり、前記少なくとも1つの隣接PUが前記第1の複数のPUのうちのPUである、請求項24に記載の方法。

【請求項27】

前記第1のCTUの現在CUの隣接PUがインターモード予測に設定されると決定することと、

前記隣接PUに基づいて前記現在CUのためのマージ候補を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、

を更に備える、請求項24に記載の方法。

30

【請求項28】

前記第1のCTUの現在PUの隣接PUがインターモード予測に設定されると決定することと、

前記隣接PUに基づいて前記現在PUの動き予測子を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、

を更に備える、請求項24に記載の方法。

【請求項29】

隣接PUに基づいて、前記第1のCTUの現在PUのためのイントラ予測モードを予測することを更に備え、前記隣接PUが前記第1の複数のPUのうちのPUである、請求項24に記載の方法。

40

【請求項30】

ビデオデータを符号化するための装置であって、

データ構造を記憶することと、前記データ構造が、第1の複数の予測単位(PU)の各PUに関係するデータを有し、前記データ構造がコード化ツリー単位(CTU)のサイズを更に有する、

前記データ構造中の前記第1の複数のPUの外周に沿って配設された複数の拡張単位の各拡張単位毎に拡張データを記憶することと

を行うように構成されたメモリと、

前記メモリに動作可能に結合され、

50

前記データ構造に基づいて第1のCTUを符号化することと、

第1の更新されたデータ構造を形成するために前記第1のCTUのPUの最右列に関係するデータを用いて前記データ構造中の前記複数の拡張単位の最左列を更新することと、

前記第1の更新されたデータ構造に基づいて第2のCTUを符号化することとを行うように構成されたプロセッサとを備える、装置。

【請求項31】

前記プロセッサは、

要素ラインバッファに前記第1のCTUのPUの最下行に関係するデータを記憶することと、前記要素ラインバッファが、ピクチャ幅の部分に等しい第2の複数のPUに関係するデータを記憶するように構成される、

前記要素ラインバッファに前記第2のCTUのPUの最下行に関係するデータを記憶することと、

ピクチャの前記部分中のCTUの第1の行を符号化した後に、デフォルト値を用いて、前記データ構造中の前記複数の拡張単位の前記最左列と前記データ構造中の前記第1の複数のPUとを更新することと、CTUの前記第1の行が前記第1のCTUと前記第2のCTUとを含む、

第2の更新されたデータ構造を形成するために前記要素ラインバッファからのデータを用いて前記第1の更新されたデータ構造中の前記複数の拡張単位の最上行を更新することと、

前記第2の更新されたデータ構造に基づいてCTUの第2の行上の第3のCTUを符号化することと

を行うように更に構成された、請求項30に記載の装置。

【請求項32】

前記第1のCTUの現在CUのCU深度と前記第1の複数のPUの少なくとも1つの隣接PUのCU深度とに基づいて、前記現在CUのためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することと、

前記少なくとも1つの隣接PUがスキップモードに設定されるかどうかに基づいて、前記第1のCTUの前記現在CUのためのスキップフラグのためのCABACコンテキストを決定することと、

前記第1のCTUの現在CUの隣接PUがインターモード予測に設定されると決定することと、前記隣接PUに基づいて前記現在CUのためのマージ候補を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、

現在PUの前記隣接PUがインターモード予測に設定されると決定することと、前記隣接PUに基づいて前記現在PUの動き予測子を決定することと、

前記隣接PUに基づいての前記第1のCTUの前記現在PUのためのイントラ予測モードを予測することと

のうちの少なくとも1つを完了するように更に構成された前記プロセッサ、請求項30に記載の装置。

【請求項33】

前記プロセッサが、空間予測のための参照として前記データ構造を使用して前記第1のCTUを符号化するように更に構成された、請求項30に記載の装置。

【請求項34】

前記第1の複数のPUの各PUが、前記第1のCTUのための最小PUを含み、前記データが、少なくとも、コード化単位深度、予測モード、及びインター予測モードを備える、請求項30に記載の装置。

【発明の詳細な説明】

【技術分野】

【0001】

10

20

30

40

50

[0001]本開示は、ビデオコード化及び圧縮の分野に関する。特に、本開示は、高効率ビデオコード化（H E V C : High Efficiency Video Coding）のための適応タイルサイジング（adaptive tile sizing）に関する。本開示はまた、M V - H E V C と呼ばれる、H E V C のマルチビュー拡張などの3Dビデオコード化に関する。

【背景技術】

【0 0 0 2】

[0002]デジタルビデオ能力は、デジタルテレビジョン、デジタルダイレクトブロードキャストシステム、ワイヤレスブロードキャストシステム、携帯情報端末（P D A）、ラップトップ又はデスクトップコンピュータ、タブレットコンピュータ、電子ブックリーダー、デジタルカメラ、デジタル記録機器、デジタルメディアプレーヤ、ビデオゲーム機器、ビデオゲームコンソール、セルラー電話又は衛星無線電話、所謂「スマートフォン」、ビデオ遠隔会議機器、ビデオストリーミング機器などを含む、広範囲にわたる機器に組み込まれ得る。デジタルビデオ機器は、M P E G - 2、M P E G - 4、I T U - T H . 2 6 3、I T U - T H . 2 6 4 / M P E G - 4，P a r t 1 0，高度ビデオコード化（A V C : Advanced Video Coding）、現在開発中の（H E V C 規格によって定義された規格、及びそのような規格の拡張に記載されているビデオコード化プロセスなど、ビデオコード化プロセスを実装する。ビデオ機器は、そのようなタイプのビデオコード化を実装することによって、デジタルビデオ情報をより効率的に送信、受信、符号化、復号、及び／又は記憶し得る。

10

【0 0 0 3】

[0003]ビデオコード化方法は、ビデオシーケンスに固有の冗長性を低減又は除去するための空間（イントラピクチャ）予測及び／又は時間（インターピクチャ）予測を含む。ブロックベースビデオコード化の場合、ビデオスライス（例えば、ビデオフレーム又はビデオフレームの一部分）が、ツリーブロック、コード化単位（C U : coding unit）及び／又はコード化ノードと呼ばれることがあるビデオブロックに区分され得る。ピクチャのイントラコード化（I）スライス中のビデオブロックは、同じピクチャ中の隣接ブロック中の参照サンプルに対する空間予測を使用して符号化される。ピクチャのインターフレームコード化（P又はB）スライス中のビデオブロックは、同じピクチャ中の隣接ブロック中の参照サンプルに対する空間予測、又は他の参照ピクチャ中の参照サンプルに対する時間予測を使用し得る。ピクチャはフレームと呼ばれることがあり、参照ピクチャは参照フレームと呼ばれることがある。

20

【0 0 0 4】

[0004]空間予測又は時間予測は、コード化されるべきブロックのための予測ブロックを生じる。残差データは、コード化されるべき元のブロックと予測ブロックとの間の画素差分を表す。インターフレームコード化ブロックは、予測ブロックを形成する参照サンプルのブロックを指す動きベクトルと、コード化ブロックと予測ブロックとの間の差分を示す残差データとに従って符号化される。イントラコード化ブロックは、イントラコード化モードと残差データとに従って符号化される。更なる圧縮のために、残差データは、画素領域から変換領域に変換され、残差変換係数が生じ得、その残差変換係数は、次いで量子化され得る。最初は2次元アレイで構成される量子化変換係数は、変換係数の1次元ベクトルを生成するために走査され得、なお一層の圧縮を達成するために、エントロピーコード化が適用され得る。

30

【発明の概要】

【0 0 0 5】

[0005]概して、本開示は、ビデオコード化に関するシステム及び方法について説明する。本開示のシステム、方法及び機器は、それぞれ幾つかの発明的態様を有し、それらのうちの単一の態様が、本明細書で開示される望ましい属性を単独で担当するとは限らない。

40

【0 0 0 6】

[0006]本開示の一態様は、ビデオデータを符号化する方法を提供する。本方法は、メモ

50

リにデータ構造を記憶することを含むことができる。データ構造は、ピクチャの第1の部分の第2の複数のデータ要素に対応する、及び外周を画定する、配置された第1の複数のデータ要素を有することができ、データ構造は、ピクチャの第1の部分のための最小予測単位( P U )の全てに関係するデータを更に含む。本方法は、第1の複数のデータ要素の外周に沿って複数の拡張単位を追加することを備える、メモリ中のデータ構造のサイズを増加させることを更に含むことができ、複数の拡張単位の各拡張単位は、ピクチャの第1の部分の最小データ要素に関係するデータを有する。本方法は、複数の拡張単位の各拡張単位と第1の複数のデータ要素とをデフォルト値に設定することを更に含むことができる。本方法は、データ構造に基づいてピクチャの第1の部分を符号化することを更に含むことができる。

10

## 【0007】

[0007]本開示の別の態様は、ビデオデータを符号化するための機器を提供する。本機器は、ピクチャの第1の部分の第2の複数のデータ要素に対応する、及び外周を画定する、配置された第1の複数のデータ要素を有し、データ構造を記憶するように構成されたメモリを有することができ、データ構造は、ピクチャの第1の部分のための最小予測単位( P U )の全てに関係するデータを更に含む。本機器はまた、メモリに動作可能に結合されたプロセッサを有することができる。プロセッサは、第1の複数のデータ要素の外周に沿って複数の拡張単位を追加することを備える、メモリ中のデータ構造のサイズを増加させることができ、複数の拡張単位の各拡張単位は、ピクチャの第1の部分の最小データ要素に関係するデータを有する。プロセッサはまた、複数の拡張単位の各拡張単位と第1の複数のデータ要素とをデフォルト値に設定することができる。プロセッサはまた、データ構造に基づいてピクチャの第1の部分を符号化することができる。

20

## 【0008】

[0008]本開示の別の態様は、ビデオデータブロック中のビデオデータを符号化する方法を提供する。本方法は、データ構造中の第1の複数の予測単位の各予測単位に関係するデータを記憶することを含むことができ、データ構造はコード化ツリー単位( C T U )のサイズを有する。本方法はまた、データ構造中の複数の予測単位の外周に沿って配設された複数の拡張単位の各拡張単位についての拡張データを記憶することを含むことができる。本方法はまた、データ構造に基づいて第1の C T U を符号化することを含むことができる。本方法はまた、第1の更新されたデータ構造を形成するために第1の C T U の予測単位の最右列に関係するデータを用いてデータ構造中の複数の拡張単位の最左列を更新することを含むことができる。本方法はまた、第1の更新されたデータ構造に基づいて第2の C T U を符号化することを含むことができる。

30

## 【0009】

[0009]本開示の別の態様は、ビデオデータを符号化するための機器を提供する。本機器はメモリを有することができる。メモリは、データ構造を記憶することができ、データ構造は、第1の複数の予測単位の各予測単位に関係するデータを有し、データ構造はコード化ツリー単位( C T U )のサイズを更に有する。メモリはまた、データ構造中の複数の予測単位の外周に沿って配設された複数の拡張単位の各拡張単位についての拡張データを記憶することができる。本機器はまた、メモリに動作可能に結合されたプロセッサを有することができる。プロセッサは、データ構造に基づいて第1の C T U を符号化することができる。プロセッサはまた、第1の更新されたデータ構造を形成するために第1の C T U の予測単位の最右列に関係するデータを用いてデータ構造中の複数の拡張単位の最左列を更新することができる。プロセッサはまた、第1の更新されたデータ構造に基づいて第2の C T U を符号化することができる。

40

## 【0010】

[0010]本開示の他の特徴及び利点は、例として、本開示の態様を示す以下の説明から明らかであろう。

## 【0011】

[0011]本開示の実施形態の詳細は、それらの構造と動作の両方について、添付の図面の

50

検討によって部分的に収集され得、同様の参照番号は同様の部分を指す。

【図面の簡単な説明】

【0012】

【図1】[0012]ビデオコード化システムのブロック図。

【図2】[0013]図1のビデオエンコーダのブロック図。

【図3】[0014]図1のビデオデコーダのブロック図。

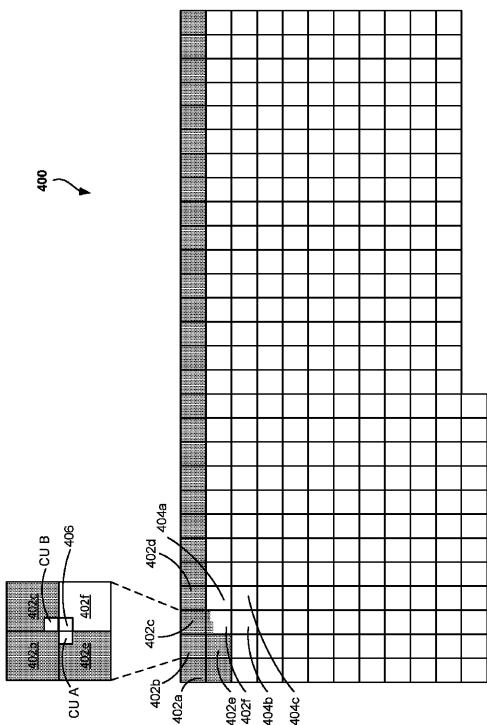

【図4】[0015]ビデオデータブロックのグラフィカル表現。

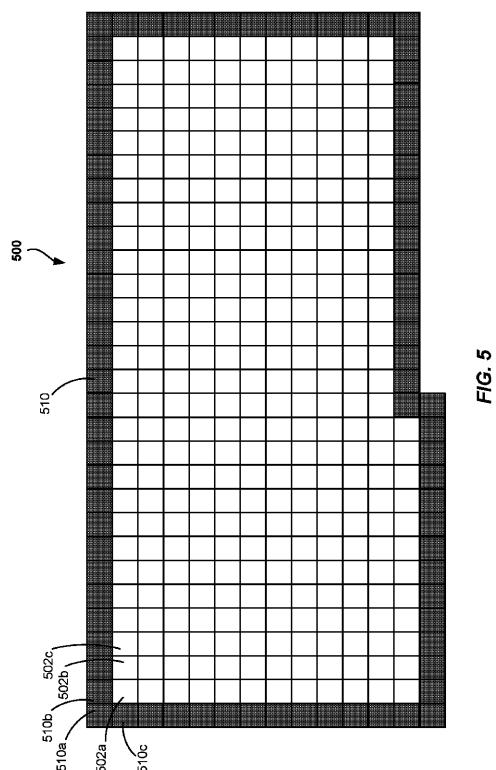

【図5】[0016]拡張単位を使用するデフォルトデータブロックのグラフィカル表現。

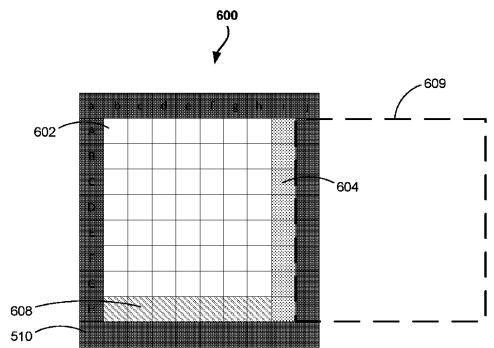

【図6A】[0017]ビデオデータをコード化するために使用されるデータ構造のグラフィカル表現。 10

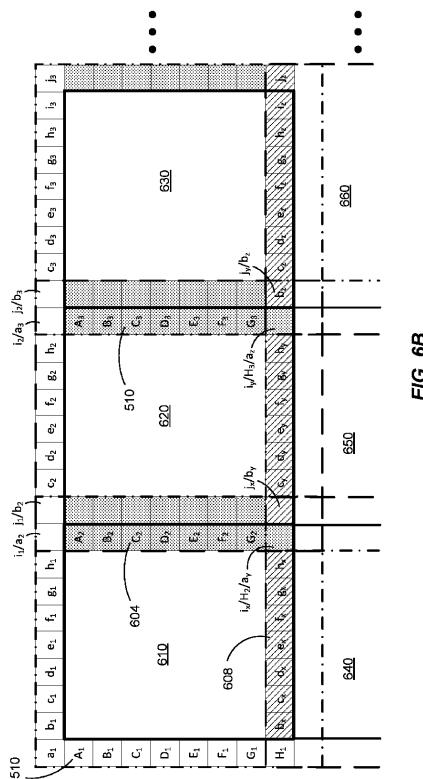

【図6B】[0018]図6Aのデータ構造を使用する符号化ビデオデータである複数のコード化ツリー単位(CTU)のグラフィカル表現。

【図7】[0019]図5のデータ構造を使用してビデオデータを符号化するためのフローチャート。

【図8】[0020]図6Aのデータ構造を使用してビデオデータを符号化するためのフローチャート。

【発明を実施するための形態】

【0013】

[0021]本出願は、ビデオコード化における空間予測に関する。ビデオデータの連続ブロック又はフレームをコード化する際に、ビデオエンコーダは、例えば、ベクトルの観点から画素動きについて説明するために隣接画素情報を活用することができる。これは、一連のビデオフレーム又はブロック中の画素動きについて説明するために必要とされる情報の量を劇的に低減することができる。幾つかの事例では、この原理は、画素信号伝達と予測モード信号伝達とに適用され得る。但し、全ての画素が、コード化中に参照として使用するために常に利用可能であるとは限らない。従って、例えば、そのような空間参照としての画素又はブロックの利用可能性に課される複数の制限がある。符号化が進むにつれて、これらの制限は、隣接ビデオデータの利用可能性(又は利用不可能性)を検証するために検査されなければならない。そのような「利用不可能性」検査に必要な処理オーバーヘッドを低減するために、あるデフォルトデータが、コード化プロセスのための参照を与えるために実装され、それにより、検査の少なくとも一部分を避けることができる。これらのデフォルトデータは、利用不可能性検査を行う必要を緩和するために符号化プロセス全体にわたって参照される、一時的に記憶され連続的に又は周期的に更新されたデータ構造として実装され得る。これは、コード化効率の増加をもたらすことができる。 20

【0014】

[0022]添付の図面に関して以下に記載される発明を実施するための形態は、様々な実施形態を説明するものであり、本開示が実施され得る実施形態のみを表すものではない。発明を実施するための形態は、実施形態の完全な理解を与えるための具体的な詳細を含む。但し、本開示はこれらの具体的な詳細なしにことが当業者には明らかであろう。幾つかの事例では、よく知られている構造及び構成要素は、説明の簡潔のために簡略化された形式で示される。 30

ビデオコード化

[0023]ビデオコード化規格は、ITU-T H.261、ISO/IEC MPEG-1 Visual、ITU-T H.262又はISO/IEC MPEG-2 Visual、ITU-T H.263、ISO/IEC MPEG-4 Visual、及びそのスケーラブルビデオコード化(SVC:Scalable Video Coding)拡張とマルチビュービデオコード化(MVC:Multiview Video Coding)拡張とを含む、(ISO/IEC MPEG-4 AVCとしても知られる)ITU-T H.264を含む。上記の規格のうちの1つ又は複数は、本明細書で説明される実施形態とともに使用され得る。 40

【0015】

[0024]更に、新しいビデオコード化規格、即ち、高効率ビデオコード化(HEVC)が 50

、 I T U - T ビデオコード化工キスパートグループ ( V C E G : Video Coding Experts Group ) と I S O / I E C モーションピクチャエキスパートグループ ( M P E G : Motion Picture Experts Group ) とのジョイントコラボレーションチームオンビデオコード化 ( J C T - V C : Joint Collaboration Team on Video Coding ) によって開発されている。以下で「 H E V C W D 」と呼ばれる、最新の H E V C ドラフト仕様は、 [http://phenix.it-evry.fr/jct/doc\\_end\\_user/documents/15\\_Geneva/wg11/JCTVC-01003-v1.zip](http://phenix.it-evry.fr/jct/doc_end_user/documents/15_Geneva/wg11/JCTVC-01003-v1.zip) から入手可能である。 H E V C のマルチビュー拡張、即ち、 M V - H E V C と、より高度な 3 D ビデオコード化のための別の H E V C 拡張 ( 3 D - H E V C ) とは、 J C T - 3 V によって開発されており、一方、 H E V C のスケーラブルビデオコード化拡張、即ち、 S H V C は、 J C T - V C によって開発されている。以下で M V - H E V C W D 5 と呼ばれる、 M V - H E V C の最近のワーキングドラフト ( W D ) は、 [http://phenix.it-sudparis.eu/jct2/doc\\_end\\_user/documents/6\\_Geneva/wg11/JCT3V-F1004-v6.zip](http://phenix.it-sudparis.eu/jct2/doc_end_user/documents/6_Geneva/wg11/JCT3V-F1004-v6.zip) から入手可能である。以下で 3 D - H E V C W D 1 と呼ばれる、 3 D - H E V C の最新の W D は、 [http://phenix.it-sudparis.eu/jct2/doc\\_end\\_user/documents/6\\_Geneva/wg11/JCT3V-F1001-v3.zip](http://phenix.it-sudparis.eu/jct2/doc_end_user/documents/6_Geneva/wg11/JCT3V-F1001-v3.zip) から入手可能である。以下で S H V C W D 3 と呼ばれる、 S H V C の最近のワーキングドラフト ( W D ) は、 [http://phenix.it-sudparis.eu/jct/doc\\_end\\_user/documents/15\\_Geneva/wg11/JCTVC-01008-v3.zip](http://phenix.it-sudparis.eu/jct/doc_end_user/documents/15_Geneva/wg11/JCTVC-01008-v3.zip) から入手可能である。

10

#### 【 0 0 1 6 】

[0025] H E V C は、概して、増加した計算複雑さという犠牲を払って、同等の画像品質で、ビットレート要件を 1 / 2 だけ低減することができる。幾つかの実施形態では、 H E V C エンコーダは、計算複雑さ、圧縮レート、エラーに対するロバストネス及び符号化遅延時間のトレードオフを図ることができる。従って、 H E V C は、概して、より高い解像度のビデオ及び改善された並列処理方法をサポートすることができる。

20

#### 【 0 0 1 7 】

[0026] H E V C ビデオコード化レイヤは、インターピクチャ及びイントラピクチャ予測と 2 次元 ( 2 D ) 変換コード化とを実装する、「ハイブリッド」手法を使用する。 H E V C エンコーダは、最初に、ピクチャを、第 1 のピクチャ又はランダムアクセスポイントの第 1 のピクチャのためにロック形状の領域にスプリットすることができ、これは、イントラピクチャ予測を使用する。本明細書で使用されるイントラピクチャ予測は、概して、ピクチャ中の情報のみに基づくそのピクチャ中のロックの予測を指すことができる。全ての他のピクチャについて、インターピクチャ予測が使用される。インターピクチャ予測は、概して、現在ピクチャを生成するために他のピクチャからの予測情報がいつ使用されるかを指すことができる。予測方法が終了され、ピクチャがループフィルタを通った後に、最終ピクチャ表現が復号ピクチャバッファに記憶される。復号ピクチャバッファに記憶されたピクチャは、他のピクチャの予測のために使用され得る。

30

#### 【 0 0 1 8 】

[0027] H E V C はまた、幾つかの並列処理ツールを実装することができる。幾つかの実施形態では、ピクチャを、独立して符号化及び復号され得る矩形領域のグリッドに分割するために、タイルが使用され得る。

40

#### 【 0 0 1 9 】

[0028] H E V C 規格はパラメータセット概念を採用する。 H E V C におけるシーケンスパラメータセット ( S P S ) 、ピクチャパラメータセット ( P P S ) 及びビデオパラメータセット ( V P S ) 機構は、まれに変化する情報の送信を、コード化ビデオブロックデータの送信から分離し得る。

#### 【 0 0 2 0 】

[0029] H E V C では、 S P S ピクチャ、 P P S 又は V P S の識別子は、「 u e ( v ) 」と称する可変長符号化コード化方法を使用してコード化される。 H E V C ワーキングドラフトは、「 u e ( v ) 」コード化シンタックス要素を、左ビット第一の、符号なし整数指数ゴロムコード化 ( unsigned integer Exp-Golomb-coded ) シンタックス要素として定義する。各 S P S は S P S 識別子 ( I D ) を含み、各 P P S は P P S I D 及び S P S I

50

Dを含み、各スライスヘッダはPPS\_IDを含む。同じく、各バッファリング期間補足拡張情報(SEI: supplemental enhancement information)メッセージがSPS\_IDを含む。概して、ビデオコード化機器又はビデオ処理機器は、ネットワーク抽象化レイヤ(NAL)単位内にビットストリームのデータをカプセル化し得る。NAL単位は、ビデオコード化レイヤ(VCL)NAL単位と非VCL\_NAL単位とを含む。VCL\_NAL単位は、概して、コード化ビデオデータ及びパラメータセット、例えば、SPS、PPS及びVPSなど、ビデオコーダによって使用される情報を含む。非VCL\_NAL単位は、SEIメッセージを定義する情報を含み、その情報は、VCL\_NAL単位からのコード化ピクチャサンプルを復号するためには必要でないが、復号と、表示と、誤り耐性と、他の目的とに関係するプロセスを支援し得る情報を含んでいることがある。

10

### ビデオコード化システム

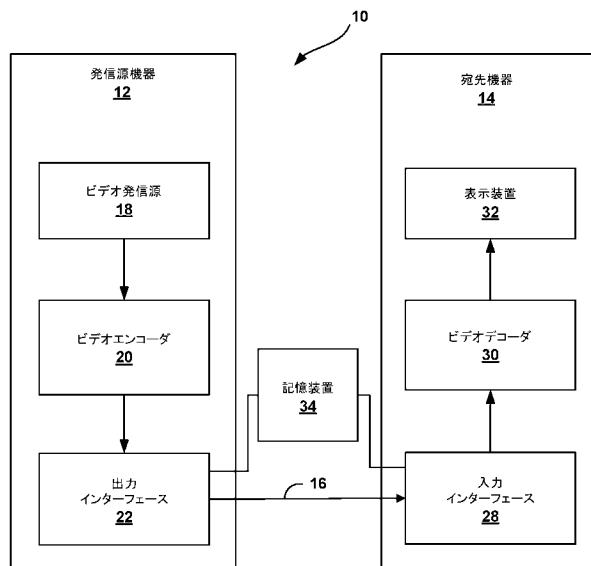

[0030]図1は、ビデオコード化システムのブロック図である。本開示で説明される様による方法を利用し得るビデオコード化システム(「システム」)10。本明細書で使用され説明される「ビデオコーダ」という用語は、総称的にビデオエンコーダとビデオデコーダの両方を指す。本開示では、「ビデオコード化」又は「コード化」という用語は、ビデオ符号化とビデオ復号とを総称的に指すことがある。

20

#### 【0021】

[0031]図1に示されているように、システム10は、宛先機器14によって後で復号されるべき符号化ビデオデータを生成することができる発信源機器12を含む。発信源機器12及び宛先機器14は、デスクトップコンピュータ、ノートブック(即ち、ラップトップ)コンピュータ、タブレットコンピュータ、セットトップボックス、所謂「スマート」フォンなどの電話ハンドセット、所謂「スマート」パッド、テレビジョン、カメラ、表示装置、デジタルメディアプレーヤ、ビデオゲームコンソール、ビデオストリーミング機器などを含む、広範囲にわたる機器のいずれかを備えることができる。幾つかの場合には、発信源機器12及び宛先機器14は、ワイヤレス通信のために装備され得る。

20

#### 【0022】

[0032]宛先機器14は、リンク16を介して復号されるべき符号化ビデオデータを受信し得る。リンク16は、発信源機器12から宛先機器14に符号化ビデオデータを移動することが可能な任意のタイプの媒体又は機器を備え得る。一例では、リンク16は、発信源機器12が、符号化ビデオデータをリアルタイムで宛先機器14に直接送信することを可能にするための通信媒体を備え得る。発信源機器12は、ワイヤレス通信プロトコルなどの通信規格に従って符号化ビデオデータを変調し得、宛先機器14に送信した。通信媒体は、無線周波数(RF)スペクトル又は1つ以上の物理伝送線路など、任意のワイヤレス又はワイヤード通信媒体を備え得る。通信媒体は、ローカルエリアネットワーク、ワイドエリアネットワークなどのパケットベースネットワーク又はインターネットなどのグローバルネットワークの一部を形成し得る。通信媒体は、ルータ、スイッチ、基地局又は発信源機器12から宛先機器14への通信を可能にするために有用であり得る任意の他の機器を含み得る。

30

#### 【0023】

[0033]符号化データは出力インターフェース22から記憶装置34に出力され得る。同様に、入力インターフェース28は、記憶装置34に記憶された符号化データにアクセスすることができる。記憶装置34は、ハードドライブ、Blu-ray(登録商標)ディスク、DVD、CD-ROM、フラッシュメモリ、揮発性又は不揮発性メモリ、あるいは符号化ビデオデータを記憶するための任意の他の好適なデジタル記憶媒体など、様々な分散された又はローカルにアクセスされるデータ記憶媒体のいずれかを含むことができる。更なる一例では、記憶装置34は、発信源機器12によって生成された符号化ビデオを保持することができるファイルサーバ又は別の中間記憶装置に対応することができる。宛先機器14は、ストリーミング又はダウンロードを介して記憶装置34から記憶されたビデオデータにアクセスすることができる。ファイルサーバは、符号化ビデオデータを記憶することと、その符号化ビデオデータを宛先機器14に送信することが可能な任意のタイ

40

50

プのサーバであり得る。例示的なファイルサーバとしては、(例えば、ウェブサイトのための)ウェブサーバ、FTPサーバ、ネットワーク接続記憶(NAS)装置又はローカルディスクドライブがある。宛先機器14は、インターネット接続を含む、任意の標準のデータ接続を通して符号化ビデオデータにアクセスすることができる。これは、ファイルサーバに記憶された符号化ビデオデータにアクセスするのに好適であるワイヤレスチャネル(例えば、Wi-Fi(登録商標)接続)、ワイヤード接続(例えば、DSL、ケーブルモデルなど)、又はその両方の組合せを含むことができる。記憶装置34からの符号化ビデオデータの送信は、ストリーミング送信、ダウンロード送信、又はその両方の組合せであり得る。

## 【0024】

10

[0034]本開示の方法は、必ずしもワイヤレス適用例又は設定に限定されるとは限らない。本方法は、無線テレビジョン放送、ケーブルテレビジョン送信、衛星テレビジョン送信、例えばインターネットを介したストリーミングビデオ送信、データ記憶媒体に記憶するためのデジタルビデオの符号化、データ記憶媒体に記憶されたデジタルビデオの復号、又は他の適用例など、様々なマルチメディア適用例のいずれかをサポートするビデオコード化に適用され得る。幾つかの例では、システム10は、ビデオストリーミング、ビデオ再生、ビデオプロードキャスティング、及び/又はビデオテレフォニーなどの適用例をサポートするために、一方向又は双方向のビデオ送信をサポートするように構成され得る。

## 【0025】

20

[0035]図1の例では、発信源機器12は、ビデオ発信源18と、ビデオエンコーダ20と、出力インターフェース22とを含む。幾つかの場合には、出力インターフェース22は、変調器/復調器(モデル)及び/又は送信機を含み得る。発信源機器12において、ビデオ発信源18は、撮像装置、例えばビデオカメラ、以前に撮られたビデオを含んでいるビデオアーカイブ、ビデオコンテンツプロバイダからビデオを受信するためのビデオフィードインターフェース及び/又は発信源ビデオとしてコンピュータグラフィックスデータを生成するためのコンピュータグラフィックスシステムなどの発信源、若しくはそのような発信源の組合せを含み得る。一例として、ビデオ発信源18がビデオカメラである場合、発信源機器12及び宛先機器14は、所謂カメラフォン又はビデオフォンを形成し得る。但し、本開示で説明される方法は、概してビデオコード化に適用可能であり得、ワイヤレス及び/又はワイヤード適用例に適用され得る。

30

## 【0026】

[0036]ビデオエンコーダ20は、撮られたビデオ、以前に撮られたビデオ又はコンピュータ生成されたビデオを符号化し得る。幾つかの例では、発信源機器12の出力インターフェース22は、介して符号化ビデオデータを宛先機器14に直接送信することができる。符号化ビデオデータは更に(又は代替的に)、復号及び/又は再生のための宛先機器14又は他の機器による後のアクセスのために記憶装置34上に記憶され得る。

## 【0027】

40

[0037]宛先機器14は、入力インターフェース28と、ビデオデコーダ30と、表示装置32とを含む。幾つかの場合には、入力インターフェース28は受信機及び/又はモデルを含み得る。宛先機器14の入力インターフェース28は、リンク16を介して符号化ビデオデータを受信する。リンク16を介して通信された、又は記憶装置34上に与えられた符号化ビデオデータは、ビデオデータを復号する際に、ビデオデコーダ30などのビデオデコーダが使用するための、ビデオエンコーダ20によって生成された様々なシンタックス要素を含むことができる。そのようなシンタックス要素は、通信媒体上で送信された、記憶媒体に記憶された、又はファイルサーバ記憶された符号化ビデオデータとともに含まれ得る。

## 【0028】

50

[0038]表示装置32は、宛先機器14と一体化されるか、又はその外部にあり得る。幾つかの例では、宛先機器14は、一体型表示装置を含み、外部表示装置とインターフェースするように構成され得る。他の例では、宛先機器14は表示装置であり得る。概して、

表示装置 32 は、復号ビデオデータをユーザに表示し、液晶表示器（LCD）、プラズマ表示器、有機発光ダイオード（OLED）表示器又は別のタイプの表示装置など、様々な表示装置のいずれかを備え得る。

【0029】

[0039] ビデオエンコーダ 20 及びビデオデコーダ 30 はそれぞれ、1つ又は複数のマイクロプロセッサ、デジタル信号プロセッサ（DSP）、特定用途向け集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）、ディスクリート論理回路、ソフトウェア、ハードウェア、ファームウェアなど、様々な好適なエンコーダ回路のいずれか、又はそれらの任意の組合せとして実装され得る。本方法が部分的にソフトウェアで実装されるとき、機器は、ソフトウェアのための命令を好適な非一時的コンピュータ可読媒体に記憶し、本開示の方法を実行するために1つ又は複数のプロセッサを使用してハードウェアでその命令を実行し得る。ビデオエンコーダ 20 及びビデオデコーダ 30 の各々は1つ又は複数のエンコーダ又はデコーダ中に含まれ得、そのいずれも、それぞれの機器において複合エンコーダ／デコーダ（コーデック）の一部として一体化され得る。

10

【0030】

[0040] H E V C 規格化の取り組みは、H E V C テストモデル（HM）と呼ばれるビデオコード化機器の発展的モデルに基づく。HMは、例えば、ITU-T H.264 / AVC に従う既存の機器に対してビデオコード化機器の幾つかの追加の能力を仮定する。例えば、H.264 は9つのイントラ予測符号化モードを与えるが、HMは33個ものイントラ予測符号化モードを与え得る。

20

【0031】

[0041] 概して、HMのワーキングモデルは、ビデオフレーム又はピクチャが、ルーマサンプルとクロマサンプルの両方を含む一連のツリーブロック又は最大コード化単位（LCU : largest coding unit）に分割され得ることを記載している。LCUは、本明細書ではコード化ツリー単位（CTU）と呼ばれることがある。CTUはH E V C の基本単位である。ツリーブロックは、H.264 規格のマクロブロックと概念的に同様である。スライスは、コード化順序で幾つかの連続するツリーブロックを含む。ビデオフレーム又はピクチャは、1つ又は複数のスライスに区分され得る。各ツリーブロックは、4分木に従ってコード化単位（CU）にスプリットされ得る。例えば、4分木のルートノードとしてのツリーブロックは、4つの子ノードにスプリットされ得、各子ノードは、次に、親ノードとなり、別の4つの子ノードにスプリットされ得る。4分木のリーフノードとしての、最終的な、スプリットされていない子ノードは、コード化ノード、即ち、コード化ビデオブロックを備える。コード化ビットストリームに関連するシンタックステータは、ツリーブロックがスプリットされ得る最大回数を定義し得、また、コード化ノードの最小サイズを定義し得る。

30

【0032】

[0042] CU は、コード化ノードと、コード化ノードに関連する予測単位（PU）及び変換単位（TU : transform unit）とを含む。CU のサイズは、コード化ノードのサイズに対応し、形状が正方形でなければならない。CU のサイズは、8 × 8 画素から最大 64 × 64 画素以上をもつツリーブロックのサイズまでに及び得る。各 CU は、1つ又は複数の PU と、1つ又は複数の TU とを含んでいることがある。CU に関連するシンタックステータは、例えば、1つ又は複数の PU への CU の区分を記述し得る。区分モードは、CU が、スキップモード符号化又はダイレクトモード符号化されるか、イントラ予測モード符号化されるか、若しくはインター予測モード符号化されるかの間で異なり得る。PU は、形状が非正方形になるように区分され得る。CU に関連するシンタックステータは、例えば、4分木に従う1つ又は複数の TU への CU の区分をも記述し得る。TU は、形状が正方形又は非正方形であり得る。

40

【0033】

[0043] H E V C 規格は、CUごとに異なり得る TU に従う変換を可能にする。TU は、一般に、区分された LCU について定義された所与の CU 内の PU のサイズに基づいてサ

50

イズ決定されるが、これは常にそうであるとは限らない。TUは、一般に、PUと同じサイズであるか、又はPUよりも小さい。幾つかの例では、CUに対応する残差サンプルは、「残差4分木」(RQT : residual quad tree)として知られる4分木構造を使用してより小さい単位に再分割され得る。RQTのリーフノードは変換単位(TU)と呼ばれることがある。TUに関連する画素差分値は、変換係数を生成するために変換され得、その変換係数は量子化され得る。

#### 【0034】

[0044]概して、PUは、予測プロセスに関係するデータを含む。例えば、PUがインストラモード符号化されるとき、PUは、PUのためのインストラ予測モードを記述するデータを含み得る。別の例として、PUがインターモード符号化されるとき、PUは、PUのための動きベクトルを定義するデータを含み得る。PUのための動きベクトルを定義するデータは、例えば、動きベクトルの水平成分、動きベクトルの垂直成分、動きベクトルの解像度(例えば、1/4画素精度又は1/8画素精度)、動きベクトルが指す参照ピクチャ、及び/又は動きベクトルのための参照ピクチャリスト(例えば、リスト0、リスト1、又はリストC)を記述し得る。

#### 【0035】

[0045]概して、TUは、変換プロセスと量子化プロセスとのために使用される。1つ又は複数のPUを有する所与のCUは、1つ又は複数の変換単位(TU)をも含み得る。予測の後に、ビデオエンコーダ20は、PUに対応する残差値を計算し得る。残差値は画素差分値を備え、画素差分値は、エントロピーコード化のためのシリアル化変換係数(serialized transform coefficient)を生成するためにTUを使用して変換係数に変換され、量子化され、走査され得る。本開示は、一般に、CUのコード化ノードを指すために「ビデオブロック」という用語を使用する。幾つかの特定の場合には、本開示はまた、コード化ノード並びにPU及びTUを含む、ツリーブロック、即ち、CTU、LCU又はCUを指すために「ビデオブロック」という用語を使用し得る。

#### 【0036】

[0046]ビデオシーケンスは一連のビデオフレーム又はピクチャを含むことができる。グループオブピクチャ(GOP : group of pictures)は、概して、ビデオピクチャのうちの一連の1つ又は複数を備える。GOPは、GOP中に含まれる幾つかのピクチャを記述するシンタックスデータを、GOPのヘッダ中、ピクチャのうちの1つ又は複数のヘッダ中、又は他の場所に含み得る。ピクチャの各スライスは、それぞれのスライスのための符号化モードを記述するスライスシンタックスデータを含み得る。ビデオエンコーダ20は、一般に、ビデオデータを符号化するために個々のビデオスライス内のビデオブロックに對して動作する。ビデオブロックはCU内のコード化ノードに対応し得る。ビデオブロックは、固定サイズ又は可変サイズを有し得、指定されたコード化規格に応じてサイズが異なり得る。

#### 【0037】

[0047]一例として、HMは、様々なPUサイズでの予測をサポートする。特定のCUのサイズが $2N \times 2N$ であると仮定すると、HMは、 $2N \times 2N$ 又は $N \times N$ のPUサイズでのインストラ予測と、 $2N \times 2N$ 、 $2N \times N$ 、 $N \times 2N$ 、又は $N \times N$ の対称PUサイズでのインター予測とをサポートする。HMはまた、 $2N \times nU$ 、 $2N \times nD$ 、 $nL \times 2N$ 、及び $nR \times 2N$ のPUサイズでのインター予測のための非対称区分をサポートする。非対称区分では、CUの一方は区分されないが、他の方向は25%と75%とに区分される。25%の区分に対応するCUの部分は、「n」とその後ろに付く「Up」、「Down」、「Left」、又は「Right」という表示によって示される。従って、例えば、「 $2N \times nU$ 」は、上部の $2N \times 0.5N$ PUと下部の $2N \times 1.5N$ PUとで水平方向に区分された $2N \times 2N$ CUを指す。

#### 【0038】

[0048]本開示では、「 $N \times N$ (NxN)」及び「 $N \times N$ (N by N)」は、垂直寸法及び水平寸法に関するビデオブロックの画素寸法、例えば、 $16 \times 16$ (16x16)画素又は $16$

10

20

30

40

50

$\times 16$  (16 by 16) 画素を指すために互換的に使用され得る。概して、 $16 \times 16$  ブロックは、垂直方向に 16 画素を有し ( $y = 16$ )、水平方向に 16 画素を有する ( $x = 16$ )。同様に、 $N \times N$  ブロックは、概して、垂直方向に  $N$  画素を有し、水平方向に  $N$  画素を有し、ここで、 $N$  は非負整数値を表す。ブロック中の画素は行及び列に配置され得る。その上、ブロックは、必ずしも、水平方向において垂直方向と同じ数の画素を有する必要があるとは限らない。例えば、ブロックは  $N \times M$  画素を備え得、ここで、 $M$  は必ずしも  $N$  に等しいとは限らない。

#### 【0039】

[0049]  $C_U$  の  $P_U$  を使用したイントラ予測コード化又はインター予測コード化の後に、ビデオエンコーダ 20 は、 $C_U$  の  $T_U$  のための残差データを計算し得る。 $P_U$  は、(画素領域とも呼ばれる) 空間領域において画素データを含むことができ、 $T_U$  は、変換、例えば、残差ビデオデータへの離散コサイン変換 (DCT)、整数変換、ウェーブレット変換又は概念的に同様の変換の適用後に、変換領域において係数を備え得る。残差データは、符号化されていないピクチャの画素と、 $P_U$  に対応する予測値との間の画素差分に対応し得る。ビデオエンコーダ 20 は、 $C_U$  のための残差データを含む  $T_U$  を形成し、次いで、 $C_U$  のための変換係数を生成するために  $T_U$  を変換することができる。

10

#### 【0040】

[0050] 変換係数を生成するための任意の変換の後に、ビデオエンコーダ 20 は変換係数の量子化を実行することができる。量子化は、一般に、係数を表すために使用されるデータの量をできるだけ低減するために変換係数が量子化され、更なる圧縮を行うプロセスを指す。量子化プロセスは、係数の一部又は全部に関連するビット深度を低減し得る。

20

#### 【0041】

[0051] 幾つかの例では、ビデオエンコーダ 20 は、エントロピー符号化され得るシリアル化ベクトルを生成するために、量子化変換係数を走査するために予め定義された走査順序を利用することができる。他の例では、ビデオエンコーダ 20 は適応型走査を実行することができる。1 次元ベクトルを形成するために量子化変換係数を走査した後に、ビデオエンコーダ 20 は、例えば、コンテキスト適応型可変長コード化 (C A V L C : context-adaptive variable length coding)、コンテキスト適応型バイナリ算術コード化 (C A B A C : context-adaptive binary arithmetic coding)、シンタックスベースコンテキスト適応型バイナリ算術コード化 (S B A C : syntax-based context-adaptive binary arithmetic coding)、確率間隔区分エントロピー (P I P E : Probability Interval Partitioning Entropy) コード化、又は別のエントロピー符号化方法に従って 1 次元ベクトルをエントロピー符号化することができる。ビデオエンコーダ 20 はまた、ビデオデータを復号する際にビデオデコーダ 30 が使用するための符号化ビデオデータに関連するシンタックス要素をエントロピー符号化し得る。

30

#### 【0042】

[0052] C A B A C を実行するために、ビデオエンコーダ 20 は、コンテキストモデル内のコンテキストを、送信されるべきシンボルに割り当てることができる。コンテキストは、例えば、シンボルの隣接値が非 0 であるか否かに関係し得る。C A V L C を実行するために、ビデオエンコーダ 20 は、送信されるべきシンボルのための可変長コードを選択し得る。V L C 中のコードワードは、比較的より短いコードが優勢シンボルに対応し、より長いコードが劣勢シンボルに対応するように構成され得る。このようにして、V L C の使用は、例えば、送信されるべき各シンボルのための等長コードワードを使用することに勝るビット節約を達成し得る。確率決定は、シンボルに割り当てられたコンテキストに基づくことができる。

40

#### 【0043】

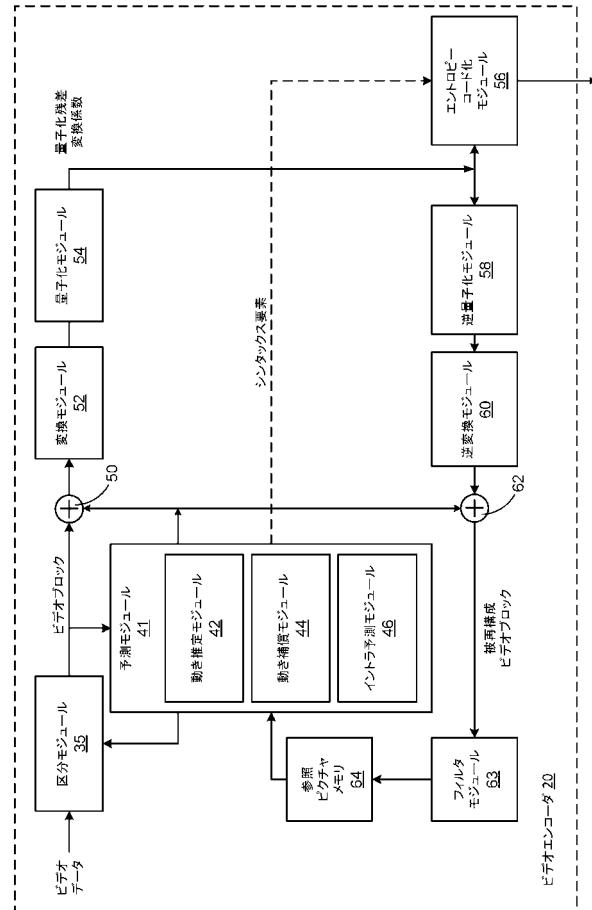

[0053] 図 2 は、図 1 のビデオエンコーダの機能ブロック図である。ビデオエンコーダ 20 は、撮られたビデオデータを受信し、ビデオデータをビデオブロックに区分するように構成された区分モジュール 35 を含むことができる。区分モジュール 35 は、ビデオデータを、スライス、タイル、又は他のより大きい単位に区分することができる。区分モジュ

50

ール 35 はまた、例えば、LCU と CU との 4 分木構造に従って、ビデオブロックを区分することができる。ビデオエンコーダ 20 は、スライスを複数のビデオブロックに（及び、場合によっては、タイルと呼ばれるビデオブロックのセットに）分割し得る。

#### 【0044】

[0054] ビデオエンコーダ 20 はまた、区分モジュール 35 に動作可能に結合され、区分されたビデオデータを受信するように構成された予測モジュール 41 を有することができる。予測モジュール 41 は、誤差結果（例えばコード化レート及び歪みレベル）に基づいて現在ビデオブロックについて、複数のイントラコード化モードのうちの 1 つ又は複数のインターフォーマット化モードのうちの 1 つなど、複数の可能なコード化モードのうちの 1 つを選択することができる。予測モジュール 41 は、ビデオエンコーダ 20 が、ビデオスライス内のビデオブロックのイントラコード化及びインターフォーマット化を実行することを可能にすることができます。イントラコード化は、所与のビデオフレーム又はピクチャ内のビデオの空間冗長性を低減又は除去するために空間予測に依拠する。インターフォーマット化は、ビデオシーケンスの隣接フレーム又はピクチャ内のビデオの時間冗長性を低減又は除去するために時間予測に依拠する。イントラモード（I モード）は、幾つかの空間ベース圧縮モードのいずれかを指すことがある。単方向予測（P モード）又は双方向予測（B モード）などのインターモードは、幾つかの時間ベース圧縮モードのいずれかを指すことがある。予測モジュール 41 は、以下で説明されるように、幾つかの制限内でインターフォーマット及びイントラ予測を実行することができる。

10

#### 【0045】

[0055] 予測モジュール 41 は、動き推定モジュール 42 と、動き補償モジュール 44 と、イントラ予測モジュール 46 とを含むことができる。これらの構成要素の各々は、ビデオエンコーダ 20 内で動作可能に接続されるか、又は 1 つ以上のプロセッサ中で一体化され得る。概念的な目的のために別々に説明されるが、動き推定モジュール 42 と、動き補償モジュール 44 と、イントラ予測モジュール 46 とは、高度に一体化され得る。

20

#### 【0046】

[0056] 動き推定モジュール 42 は、ビデオシーケンスのための所定のパターンに従ってビデオスライスのためのインター予測モードを決定するように構成され得る。1 つ又は複数の参照ピクチャ中の 1 つ又は複数の予測ブロックに対する現在ビデオブロックのそのようなインター予測又はインター予測コード化は、時間圧縮を行うことができる。所定のパターンは、シーケンス中のビデオスライスを、P スライス、B スライス又は GPB スライスに指定し得る。本明細書で使用される動き推定は、概して、ビデオブロックのための動きを推定する動きベクトルを生成するプロセスを指すことがある。動きベクトルは、例えば、参照フレーム又は参照ピクチャ内の予測ブロックに対する現在ビデオフレーム又はピクチャ内のビデオブロックの PU の変位を示し得る。参照フレームは、予測モジュール 41 に動作可能に結合された参照ピクチャメモリ 64 に記憶され得る。

30

#### 【0047】

[0057] 幾つかの実施形態では、動きベクトルは、サブ整数画素（「サブペル」）精度を有することができる。例えば、動きベクトルの水平成分と垂直成分の両方が、それぞれのフル整数又はフルペル成分及びサブペル成分を有し得る。そのようなサブペル精度は、参照フレーム内のフルペル位置から補間され得る。従って、分数画素動き推定、分数ペル動き推定、サブ整数動き推定及びサブ画素動き推定という用語は、互換的に使用され得る。幾つかの実施形態では、補間フィルタは補間された位置を与えることができる。補間フィルタは、動き推定及び / 又は動き補償の一部として補間を実行するために、動き推定モジュール 42 と動き補償モジュール 44 の一方又は両方によって呼び出され得る。

40

#### 【0048】

[0058] 予測ブロックは、絶対差分和（SAD : sum of absolute difference）、2 乗差分和（SSD : sum of square difference）、又は他の差分メトリックによって決定され得る画素差分に関して、コード化されるべきビデオブロックの PU にぴったり一致することがわかるブロックである。幾つかの例では、動き予測モジュール（「予測モジュール」

50

) 4 1 は、参照ピクチャメモリ 6 4 に記憶された参照ピクチャのサブ整数画素位置についての値を計算することができる。例えば、予測モジュール 4 1 は、参照ピクチャの 1 / 4 画素位置、1 / 8 画素位置又は他の分数画素位置の値を補間することができる。従って、動き推定モジュール 4 2 は、フル画素位置と分数画素位置とに対して動き探索を実行し、分数画素精度で動きベクトルを出力し得る。

#### 【 0 0 4 9 】

[0059]動き推定モジュール 4 2 は、PU の位置を参照ピクチャの予測ブロックの位置と比較することによって、インターフォード化スライス中のビデオブロックの PU のための動きベクトルを計算することができる。参照ピクチャは、第 1 の参照ピクチャリスト (リスト 0) 又は第 2 の参照ピクチャリスト (リスト 1) から選択され得、それらの各々が、参照ピクチャメモリ 6 4 に記憶された 1 つ又は複数の参照ピクチャを識別する。動き推定モジュール 4 2 は、計算された動きベクトルを動き補償モジュール 4 4 とエントロピー符号化モジュール 5 6 とに送ることができる。

10

#### 【 0 0 5 0 】

[0060]動き補償は、動き推定によって決定された動きベクトルに基づいて予測ブロックをフェッチ又は生成することを伴うことができる。これは、サブ画素精度への補間を含むことができる。現在ビデオブロックの PU のための動きベクトルを受信すると、動き補償モジュール 4 4 は、動きベクトルが参照ピクチャリストのうちの 1 つにおいて指す予測ブロックの位置を特定することができる。動き補償モジュール 4 4 はまた、ビデオスライスのビデオブロックを復号する際にビデオエンコーダ 3 0 が使用するための、ビデオブロックとビデオスライスとに関連するシンタックス要素を生成することができる。

20

#### 【 0 0 5 1 】

[0061]予測モジュール 4 1 内のイントラ予測モジュール 4 6 は、空間圧縮を行うために、同じフレーム又はスライス中の 1 つ又は複数の隣接ブロックに対して現在ビデオブロックのイントラ予測コード化を実行することができる。イントラ予測モジュール 4 6 は、上記で説明されたように、動き推定モジュール 4 2 と動き補償モジュール 4 4 とによって実行されるインター予測の代替として、現在ブロックをイントラ予測することができる。特に、イントラ予測モジュール 4 6 は、現在ブロックを符号化するために使用すべきイントラ予測モードを決定し得る。幾つかの例では、イントラ予測モジュール 4 6 は、例えば、別個の符号化パス中に、様々なイントラ予測モードを使用して現在ブロックを符号化し得る。例えば、イントラ予測モジュール 4 6 は、様々なテストされたイントラ予測モードのためのレート歪み分析を使用してレート歪み値を計算し、テストされたモードの中で最良のレート歪み特性を有するイントラ予測モードを選択し得る。レート歪み分析は、符号化ブロックと、符号化ブロックを生成するために符号化された元の符号化されていないブロックとの間の歪み (又は誤差) の量及び符号化ブロックを生成するために使用されるビットレート (即ち、ビット数) を決定することができる。イントラ予測モジュール 4 6 は、どのイントラ予測モードがブロックについて最良のレート歪み値を呈するかを決定するために、様々な符号化ブロックのための歪み及びレートから比を計算し得る。

30

#### 【 0 0 5 2 】

[0062]イントラ予測モジュール 4 6 は、ブロックのための選択されたイントラ予測モードを示す情報をエントロピー符号化モジュール 5 6 に与えることができる。エントロピー符号化モジュール 5 6 は、選択されたイントラ予測モードを示す情報を符号化することができる。ビデオエンコーダ 2 0 は、複数のイントラ予測モードインデックステーブル及び複数の変更されたイントラ予測モードインデックステーブル (コードワードマッピングテーブルとも呼ばれる) と、様々なブロックのための符号化コンテキストの定義と、コンテキストの各々について使用すべき、最確イントラ予測モード、イントラ予測モードインデックステーブル、及び変更されたイントラ予測モードインデックステーブルの指示とを含むことができる構成データを送信ビットストリーム中に含めることができる。

40

#### 【 0 0 5 3 】

[0063]予測モジュール 4 1 (及びその他の構成モジュール) が、上記で説明された様

50

々な動作を実行するとき、ビデオエンコーダ 20 は幾つかの制限によって抑制され得る。制限は、予測モジュール 41 が、空間的に相關するビデオデータを使用して予測ブロックを生成するとき、予測モジュール 41 によって観測される。例えば、空間又は時間予測のために使用される隣接 C U が、別のスライス中、別のタイル中、符号化されているビデオフレームの外側、又はまだ符号化されていない P U 中にある場合、それは利用不可能であり得る。制限は、幾つかの利用不可能性検査を実装することによって回避される。制限及び関連する利用不可能性検査は、図 4 に関して以下で説明される。

#### 【 0 0 5 4 】

[0064] 予測モジュール 41 が、インター予測又はイントラ予測のいずれかを介して現在ビデオブロックのための予測ブロックを生成した後に、ビデオエンコーダ 20 は、現在ビデオブロックから予測ブロックを減算することによって残差ビデオブロックを形成する。このプロセスは画素差分値を生じることができる。画素差分値は、ブロックのための残差データを形成し、ルーマ差分成分とクロマ差分成分の両方を含むことができる。予測モジュール 41 と区分モジュール 35 とに動作可能に結合された加算器 50 は、この減算演算を実行するように構成され得る 1 つ又は複数の構成要素を表す。

10

#### 【 0 0 5 5 】

[0065] 残差ブロック中の残差ビデオデータは、1 つ又は複数の T U 中に含まれ、加算器 50 に動作可能に結合された変換モジュール 52 に適用され得る。変換モジュール 52 は、離散コサイン変換 (DCT) 又は概念的に同様の変換などの変換を使用して、残差ビデオデータを残差変換係数に変換することができる。変換モジュール 52 は、残差ビデオデータを画素領域から周波数領域などの変換領域に変換することができる。予測モジュール 41 は、残差ブロックデータを生成するために、得られたイントラコード化ブロック又はインターフォーマット化ブロックを加算器 50 に与えることができる。得られたイントラコード化ブロック又はインターフォーマット化ブロックは、参照ピクチャとして使用するための符号化ブロックを再構成するために、更に加算器 62 に与えられ得る。

20

#### 【 0 0 5 6 】

[0066] ビデオエンコーダ 20 は、加算器 62 に動作可能に結合されたフィルタモジュール 63 をも含むことができる。フィルタモジュール 63 は、デブロッキングフィルタ、適応ループフィルタ (ALF : adaptive loop filter) 及びサンプル適応オフセット (SAO : sample adaptive offset) フィルタなど、1 つ又は複数のループフィルタを表すことができる。図 2 では、フィルタモジュール 63 はループ内フィルタであるとして示されているが、他の構成では、フィルタモジュール 63 はループ後フィルタとして実装され得る。フィルタモジュール 63 は、参照ピクチャを参照ピクチャメモリ 64 に与えることができる。

30

#### 【 0 0 5 7 】

[0067] 変換モジュール 52 は、得られた変換係数を量子化モジュール 54 に送ることができる。量子化モジュール 54 は、ビットレートを更に低減するために変換係数を量子化することができる。量子化プロセスは、係数の一部又は全部に関連するビット深度を低減し得る。量子化の程度は、量子化パラメータを調整することによって変更され得る。幾つかの例では、量子化モジュール 54 は、次いで、量子化変換係数を含む行列の走査を実行することができる。幾つかの実施形態では、エントロピー符号化モジュール 56 が走査を実行し得る。

40

#### 【 0 0 5 8 】

[0068] 量子化の後に、エントロピー符号化モジュール 56 は、量子化変換係数をエントロピー符号化することができる。例えば、エントロピー符号化モジュール 56 は、CABLC、CABAC、SBAC、及び / 又は PIPF、コード化、若しくは別のエントロピー符号化方法 (methodology) 又は方法 (method) を実行し得る。エントロピー符号化モジュール 56 によるエントロピー符号化の後に、符号化ビットストリームはビデオデコーダ 30 に送信され得る。ビットストリームはまた、ビデオデコーダ 30 による後の送信又は取り出しおためにアーカイブされ得る。エントロピー符号化モジュール 56 はまた、コ-

50

ド化されている現在ビデオスライスのための動きベクトルと他のシンタックス要素とをエントロピー符号化することができる。

【0059】

[0069]ビデオエンコーダ20は、エントロピー符号化モジュール56に動作可能に結合された逆量子化モジュール58をも含むことができる。また、逆変換モジュール60が、逆量子化モジュール58と加算器62とに動作可能に結合され得る。逆量子化モジュール58及び逆変換モジュール60は、参照ピクチャの参照ブロックとして後で使用するために画素領域において残差ブロックを再構成するために、それぞれ逆量子化及び逆変換を適用することができる。動き補償モジュール44は、残差ブロックを参照ピクチャリストのうちの1つ内の参照ピクチャのうちの1つの予測ブロックに加算することによって参照ブロックを計算することができる。動き補償モジュール44はまた、動き推定において使用するためのサブ整数画素値を計算するために、再構成された残差ブロックに補間フィルタのうちの1つ又は複数を適用することができる。加算器62は、参照ピクチャメモリ64に記憶するための参照ブロックを生成するために、再構成された残差ブロックを、動き補償モジュール44によって生成された動き補償予測ブロックに加算することができる。参照ブロックは、後続のビデオフレーム又はピクチャ中のブロックをインター予測するために、動き推定モジュール42と動き補償モジュール44とによって参照ブロックとして使用され得る。

10

【0060】

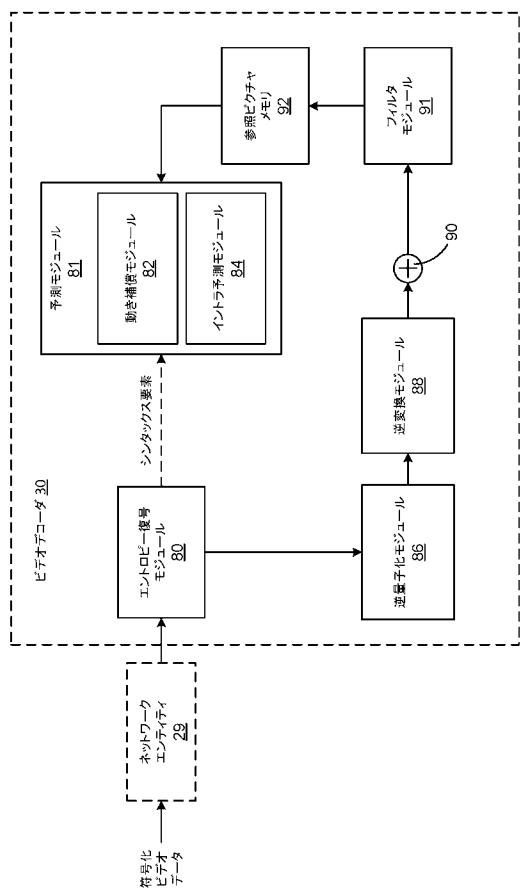

[0070]図3は、図1のビデオデコーダの機能ブロック図である。ビデオデコーダ30は、エントロピー復号モジュール80と、予測モジュール81と、逆量子化モジュール86と、逆変換モジュール88と、加算器90と、フィルタモジュール91と、参照ピクチャメモリ92とを含むことができる。予測モジュール81は、動き補償モジュール82とイントラ予測モジュール84とを含む。ビデオデコーダ30は、幾つかの例では、図2からのビデオエンコーダ20に関して説明された符号化パスとは概して逆の復号パスを実行することができる。

20

【0061】

[0071]復号プロセス中に、ビデオデコーダ30は、ビデオエンコーダ20から、符号化ビデオスライスのビデオブロックと、関連するシンタックス要素とを表す符号化ビデオビットストリームを受信する。ビデオデコーダ30は、ネットワークエンティティ29から符号化ビデオビットストリームを受信することができる。ネットワークエンティティ29は、例えば、上記で説明された方法のうちの1つ又は複数を実装するように構成されたサーバ、ビデオエディタ/スプライサ、又は他のそのような機器であり得る。上記で説明されたように、本開示で説明される方法のうちの幾つかは、ネットワークエンティティ29が符号化ビデオビットストリームをビデオデコーダ30に送信するより前に、ネットワークエンティティ29によって実装され得る。幾つかのビデオ復号システムでは、ネットワークエンティティ29及びビデオデコーダ30は別個の機器の部分であり得るが、他の事例では、ネットワークエンティティ29に関して説明される機能は、ビデオデコーダ30を備える同じ機器によって実行され得る。

30

【0062】

[0072]ビデオデコーダ30のエントロピー復号モジュール80は、量子化係数と、動きベクトルと、他のシンタックス要素とを生成するために、ビットストリームをエントロピー復号する。エントロピー復号モジュール80は、予測モジュール81に動きベクトルと他のシンタックス要素とを転送する。ビデオデコーダ30は、ビデオスライスレベル及び/又はビデオブロックレベルでシンタックス要素を受信することができる。

40

【0063】

[0073]ビデオスライスがイントラコード化(I)スライスとしてコード化されたとき、予測モジュール81のイントラ予測モジュール84は、信号伝達されたイントラ予測モードと、現在フレーム又はピクチャの前に復号されたブロックからのデータとに基づいて、現在ビデオスライスのビデオブロックのための予測データを生成することができる。ビデ

50

オフレームがインターフォード化（即ち、B、P又はGPB）スライスとしてコード化されたとき、予測モジュール81の動き補償モジュール82は、エントロピー復号モジュール80から受信された動きベクトル及び他のシンタックス要素に基づいて現在ビデオスライスのビデオブロックのための予測ブロックを生成する。予測ブロックは、参照ピクチャリストのうちの1つ内の参照ピクチャのうちの1つから生成され得る。ビデオデコーダ30は、参照ピクチャメモリ92に記憶された参照ピクチャに基づいて、デフォルトの構成方法を使用して、参照フレームリスト、即ち、リスト0及びリスト1を構成することができる。

#### 【0064】

[0074]動き補償モジュール82は、動きベクトルと他のシンタックス要素とを構文解析する（parsing）ことによって現在ビデオスライスのビデオブロックのための予測情報を決定し、復号されている現在ビデオブロックのための予測ブロックを生成するために、その予測情報を使用する。 10

#### 【0065】

[0075]動き補償モジュール82はまた、補間フィルタに基づいて補間を実行することができる。動き補償モジュール82は、参照ブロックのサブ整数画素についての補間値を計算するために、ビデオブロックの符号化中にビデオエンコーダ20によって使用された補間フィルタを使用することができる。この場合、動き補償モジュール82は、受信されたシンタックス要素からビデオエンコーダ20によって使用された補間フィルタを決定し、予測ブロックを生成するために、その補間フィルタを使用することができる。 20

#### 【0066】

[0076]逆量子化モジュール86は、ビットストリーム中で与えられ、エントロピー復号モジュール80によって復号された量子化変換係数を逆量子化（inverse quantize）、即ち、逆量子化（de-quantize）する。逆量子化プロセスは、量子化の程度を決定し、同様に、適用されるべき逆量子化の程度を決定するための、ビデオスライス中の各ビデオブロックについてビデオエンコーダ20によって計算される量子化パラメータの使用を含むことができる。逆変換モジュール88は、画素領域において残差ブロックを生成するために、逆変換、例えば、逆DCT、逆整数変換、又は概念的に同様の逆変換プロセスを変換係数に適用する。 30

#### 【0067】

[0077]動き補償モジュール82が、動きベクトルと他のシンタックス要素とにに基づいて現在ビデオブロックのための予測ブロックを生成した後、ビデオデコーダ30は、逆変換モジュール88からの残差ブロックを動き補償モジュール82によって生成された対応する予測ブロックと加算することによって、復号ビデオブロックを形成する。加算器90は、この加算演算を実行する1つ又は複数の構成要素を表す。所望される場合、（コード化ループ内又はコード化ループ後のいずれかの）ループフィルタも、画素遷移を平滑化するか、又はさもなければビデオ品質を改善するために使用され得る。フィルタモジュール91は、デブロッキングフィルタ、適応ループフィルタ（ALF）、及びサンプル適応オフセット（SAO）フィルタなど、1つ又は複数のループフィルタを表すものとする。図3では、フィルタモジュール91はループ内フィルタであるとして示されているが、他の構成では、フィルタモジュール91はループ後フィルタとして実装され得る。所与のフレーム又はピクチャ中の復号ビデオブロックは、次いで、その後の動き補償のために使用される参照ピクチャを記憶する参照ピクチャメモリ92に記憶される。参照ピクチャメモリ92はまた、図3の表示装置32などの表示装置上で後の提示のために、復号ビデオを記憶する。 40

#### 【0068】

[0078]図4は、ビデオデータブロックのグラフィカル表現である。ビデオデータブロック400は、ビデオデータを符号化するための、CTU、CU又はPUデータ構造を表すことができる。幾つかの実施形態では、ビデオデータブロック400は、ピクチャの一部分、ビデオスライス又はタイル、ツリーブロック若しくはより大きいビデオデータブロック

クの他の部分であり得る。ビデオデータブロック400は、CTU及び/又はPUを表す、一連の正方形として示される。灰色の正方形は、(以下でまとめてコード化CTU402と呼ばれる)コード化CTU402a~402eを表す。簡潔のために、本明細書では、コード化CTU402の全てが標示されるとは限らない。CTU402fが現在符号化されているが、部分的な灰色によって示されているように、それは、完全に符号化されているとは限らない。従って、CTU402fは、本明細書では、それが符号化されているCTUであることを示す、「現在CTU402f」と呼ばれることがある。本明細書で使用されるCTU、CU及び/又はPUは、総称的にデータ要素と呼ばれることがある。

#### 【0069】

[0079]白色の正方形は、非コード化CTU404a~404c(まとめて、非コード化CTU404)を表す。幾つかの実施形態では、白色のブロックはまた、コード化規格(例えば、HEVC)、予測モード及びビデオデータブロック400内のビデオデータに応じて、CTUを表すことができる。本明細書で説明されるように、それらは、一般に非コード化CTU404と呼ばれることがある。ビデオエンコーダ20が、非コード化CTU404の各々中に含まれているビデオデータを符号化するとき、コード化は、ビデオデータブロック400全体が符号化されるまで、左から右に、上から下に進む。図示のように、ビデオエンコーダ20は、コード化CTU402を表す、灰色の正方形を処理した。白色の正方形は、まだ符号化されていない非コード化CTU404を表す。

#### 【0070】

[0080]ビデオエンコーダ20は、現在ビデオデータをコード化するために隣接ビデオ情報を活用することができる。例えば、ビデオエンコーダ20が現在CTU402fを符号化するとき、ビデオエンコーダ20は、空間的に接続された情報がしばしば相關されるので、コード化CTU402b、402c、402d及び402eのために符号化されたデータを参照することができる。ある空間予測の場合、ビデオデータブロック400のための現在データは、例えば、ベクトルを用いて、参照ピクチャとの差分として表され得る。予測が正確になるほど、得られたエントロピーは多く低減され得る。

#### 【0071】

[0081]コード化CTU402b、402c、402d及び402eは、現在CTU402fに関して、本明細書では一般に隣接CTUと呼ばれることがある。幾つかの実施形態では、ちょうど、現在CTU402fが、符号化されているCTU402(又は符号化されるべき次のCTU402)であり、隣接CTUを参照するように、各非コード化CTU404は、各構成PU又はCUについて同様の符号化プロセスを有することができる。図4の挿入図は、隣接CU、即ち、CU A及びCU Bを参照する(現在CTU402f内の)現在CU406を示す。図4中の現在CTU402fは、図4の挿入図中のCTU402fと同じように着色されていないことに留意されたい。CTU402fの部分的な灰色は、CTU402fが部分的に符号化されることを示す。以下で説明される様々な制限の説明及び例示の目的で、挿入図中の現在CTU402fは、符号化プロセス中に隣接CUに対して行われる幾つかの参照を示すために着色されていない。

#### 【0072】

[0082]幾つかの実施形態では、ビデオエンコーダ20は、それらがまだコード化されておらず、場合によっては「利用不可能」であるので、CTU402fの下及び/又は右の非コード化CU/PU(例えば、非コード化CTU404中の非コード化CU)並びにCTU402f中のまだコード化されていないCU/PUのいずれをも参照することができない。

#### 【0073】

[0083]HEVCでは、例えば、上述のように、空間予測の使用に対する幾つかの制限がある。例えば、空間予測は、スライス境界又はタイル境界にわたって完了され得ない。更に、ビデオエンコーダ20は、イントラモードコード化のための予測においてインターフォーム化CUを使用することができない。

#### 【0074】

10

20

30

40

50

[0084]幾つかの実施形態では、CU（例えば、CTU402f中のCU）をコード化するより前にビデオエンコーダ20が各制限を検査するので、そのようなコード化制限は非効率的な符号化を生じることがある。制限による、複数の又は連続する利用不可能性検査が、遅延を追加し、符号化プロセスを遅くすることがある。そのような遅延は、例えば、4K超高精細度（UHD：ultra-high definition）リアルタイムエンコーダなど、例えば、超高速エンコーダに、特に有害であり得る。

#### 【0075】

[0085]隣接CU（例えば、コード化CU402又は非コード化CU404）は、様々な状況においてビデオエンコーダ20にとって利用不可能であり得る。例えば、隣接CU A、CU Bが、1)別のスライス中、2)別のタイル中、3)現在フレームの外側、4)異なるCTU行（例えば、非コード化CTU402c）中、又は5）（例えば、現在CTU402fの）まだ符号化されていないCU/PU中にある場合、そのようなビデオデータは、（例えば、現在CTU402f中の）CUをコード化するためのビデオエンコーダ20への参照として利用可能でないことがある。

#### 【0076】

[0086]例えば、幾つかの制限は、以下の行為を必要とし、関連するデフォルト設定を提示し得る。

#### 【0077】

[0087]スプリットフラグのためのCABACコンテキスト導出。ビデオエンコーダ20は、2つの隣接CU（例えば、CU A及びCU B）が利用可能であるかどうかを決定することができる。CU A及びCU Bは、例えば、CTU402f内の現在CU406を符号化することに関する説明される、CTU402e及びCTU402c内の隣接CUであり得る。隣接CU A（又はCU B）が利用可能でない場合、ビデオエンコーダ20はCU深度A（又はB）を0に設定することができる。次いで、CABACコンテキストは、現在CUのCU深度とCU A及びCU BのCU深度とから導出される。

#### 【0078】

[0088]スキップフラグのためのCABACコンテキスト導出。ビデオエンコーダ20は、2つの隣接CU（CU A及びCU B）が利用可能であるかどうかを決定することができる。隣接CU A（又はCU B）のうちの1つが利用可能でない場合、ビデオエンコーダ20はCU深度A（又はB）を非スキップ(not-skip)に設定することができる。CABACコンテキストは、CU A及びCU Bがスキップモードに設定されるかどうかに基づいて導出され得る。

#### 【0079】

[0089]マージ候補導出。マージ機能は、現在PUがそれの隣接PUのうちの1つと同等の動きベクトルを有し、従って互いにマージされ得ることを示す。ビデオエンコーダ20は、隣接PUが利用可能であるかどうかを検査することができる。隣接PUが利用可能でない場合、マージ候補は発見されない。隣接PUが利用可能である場合、ビデオエンコーダ20は、隣接PUがインター モード予測にあるかどうかを決定することができる。隣接PUがインター モード予測にない場合、マージ候補は利用可能でない。隣接PUがインター モード予測にある場合、ビデオエンコーダ20は、隣接PUからマージ候補を導出することができる。

#### 【0080】

[0090]動きベクトル予測子導出。ビデオエンコーダ20は、隣接PUが利用可能であるかどうかを決定することができる。隣接PUが利用可能でない場合、マージ候補は発見されない。隣接PUが利用可能である場合、ビデオエンコーダ20は、隣接PUがインター モード予測にあるかどうかを決定することができる。隣接PUがインター モード予測にない場合、動き予測子は発見されない。隣接PUがインター モード予測にある場合、動き予測子は、隣接PUから導出され得る。

#### 【0081】

[0091]イントラモード予測子導出。ビデオエンコーダ20は、2つの隣接PU、即ち、

10

20

30

40

50

P U A 及び P U B が利用可能であるかどうかを決定することができる。隣接 P U A (又は B ) が利用可能でない場合、ビデオエンコーダ 2 0 は、隣接 C U A (又は B ) のイントラ予測モードをイントラ D C 予測に設定することができる。ビデオエンコーダ 2 0 は、隣接 P U A (又は P U B ) がイントラ予測されるかどうかを更に決定することができる。隣接 P U A (又は B ) がイントラ予測されない場合、ビデオエンコーダ 2 0 は、隣接 P U A (又は P U B ) のイントラ予測モードをイントラ D C 予測に設定することができる。ビデオエンコーダ 2 0 はまた、現在 P U のイントラ予測モードを予測するために隣接 P U A 及び P U B のイントラ予測モードを使用することができる。

#### 【 0 0 8 2 】

[0092] 利用不可能性検査の数及び頻度は、ビデオエンコーダ 2 0 のシステムリ発信源に負担を課し、処理オーバーヘッドを増加させ、符号化効率を減少させことがある。従って、幾つかの実施形態では、オーバーヘッド及び処理時間を低減するために上記の検査を回避することが望ましい。従って、あるデフォルトデータが、そのような制限及び反復検査を回避するために、ビデオデータブロック 4 0 0 に挿入されるか、又はコード化中に参照され得る。

#### 【 0 0 8 3 】

[0093] 図 5 は、拡張デフォルトデータを使用するデータ構造のグラフィカル表現である。データ構造 5 0 0 は、ビデオデータを符号化するための、C T U 、 C U 又は P U データ構造を表すことができる。例えば、ビデオエンコーダ 2 0 は、ビデオデータブロック 4 0 0 を符号化するためにデータ構造 5 0 0 を使用することができる。データ構造 5 0 0 は、符号化されるべきビデオデータ又はデータ要素を表す、白色の正方形として示される複数の C T U 5 0 2 として示された、符号化されるべき、ピクチャの一部分、ビデオスライス又はタイトル若しくはビデオデータのより大きいブロックの一部分を含むことができる。H E V C に関連する実施形態では、白色の正方形は、 C U 又は P U をも表すことができる。これは、ビデオデータブロック 4 0 0 と同様のデータである。C T U 5 0 2 は、文字識別子 (例えば、5 0 2 a 、 5 0 2 b など) を使用して個々に標示され、表され得る。幾つかの実施形態では、C T U 5 0 2 は、C T U 4 0 2 及び C T U 4 0 4 (図 4 ) に対応することができる。幾つかの他の実施形態では、C T U 5 0 2 の数及び配置は、ビデオデータブロック 4 0 0 の C T U (例えば、コード化 C T U 4 0 2 及び非コード化 C T U 4 0 4 ) の数及び配置によって定義され得る。H E V C では、例えば、C T U 5 0 2 は、 C U 又は P U でもあり得る。例えば、C T U は、複数の C U を含むことができる。対応して、 C U は、複数の P U を含んでいることがある。

#### 【 0 0 8 4 】

[0094] データ構造 5 0 0 は、全ての方向において少なくとも 1 つの P U だけデータ構造 5 0 0 のサイズを増加させる拡張単位 5 1 0 をも有することができる。概念的に、拡張単位 5 1 0 は、符号化されるべきビデオデータの外周に沿って配設され得るデータを表す。従って、拡張単位 5 1 0 は、符号化されるべきビデオデータブロック (例えば、ビデオデータブロック 4 0 0 ) の外周を画定する C T U 5 0 2 との空間関係とともにメモリに記憶され得る。拡張単位 5 1 0 は、文字識別子 (例えば、5 1 0 a 、 5 1 0 b など) を使用して個々に標示され、表され得る。拡張単位 5 1 0 は、図 5 では暗い灰色の正方形によって表される。

#### 【 0 0 8 5 】

[0095] データ構造 5 0 0 全体が、 (例えば、記憶装置 3 4 中の) メモリにバッファ又は記憶され、例えば、ビデオデータブロック 4 0 0 など、第 1 のビデオブロックの符号化中に参照され得る。拡張単位 5 1 0 中の記憶されたデフォルトデータは、スライス又はタイトル (例えば、ビデオデータブロック 4 0 0 ) 符号化が開始するとき、参照され得る。幾つかの実施形態では、記憶装置 3 4 は、所与のデータ構造 5 0 0 についての最小 P U 情報の全てを記憶することができる。別の実施形態では、エンコーダ 2 0 は、メモリに拡張単位 5 1 0 中のデフォルトデータのみをバッファし得る。例えば H E V C では、あらゆる 4 × 4 画素ブロック (例えば、最小 P U ) に関係するデータが、メモリに記憶又はバッフ

10

20

30

40

50

アされ、符号化中に参照され得る。幾つかの実施形態では、データ構造 500 に記憶された PU 情報の全てが、メモリに記憶されたとき、符号化されている関連するスライス又はタイル（例えば、ビデオデータブロック 400）中の対応するデータと幾何学的に整合されたままである。例えば、データ構造 500 は、ビデオデータブロック中でコード化されている各要素が、データ構造 500 中に対応する要素を有するように、ビデオデータブロック 400 と同じ数及び配置の要素を有することができる。従って、ビデオデータブロック 400 がデータ構造 500 を使用して符号化されるとき、ビデオエンコーダ 20 は、CTU 402a（図 4）を符号化するときに空間参照として、（隣接 PU、CU 及び拡張単位 510 の中でも）拡張単位 510a、510b、510c を使用することができる。これは、例えば、CTU 404 を符号化するために必要とされる利用不可能性検査の数の低減をもたらすことができる。

10

## 【0086】

[0096] 従って、幾つかの実施形態では、エンコーダ 20 は、上記で説明された、利用不可能性検査を回避又は最小限に抑えるためにことができる拡張単位 510 を使用することができる。ビデオエンコーダ 20 は、スライス又はタイル（例えば、データ構造 500）コード化が開始する前に、データ構造 500 の境界上の各 PU に対して、拡張単位 510 からのデータを適用することができる。例えば、ビデオエンコーダ 20 が CTU 502a（例えば、スライスの最初のデータブロック）を符号化し始めるとき、エンコーダ 20 は基準値を必要とし得る。従って、ビデオエンコーダ 20 は、上記で説明された検査の全てを実行するとは限らずに、CTU 502a を符号化するために基準値として拡張単位 510a、510b、及び 510c に関係するデータを使用することができる。

20

## 【0087】

[0097] ビデオエンコーダ 20 がデータブロック 400 を符号化する準備をするとき、ビデオエンコーダ 20 は、拡張単位 510 中のデフォルトデータを適用し、利用不可能性検査の少なくとも一部分を先取りする（preempting）ことができる。幾つかの実施形態では、ビデオエンコーダ 20 は、拡張単位 510 について以下のデフォルト値を設定することができる。

30

## 【0088】

- 1) CU 深度が 0 に等しい

- 2) 予測モードがイントラ予測に設定される

- 3) イントラ予測モードが DC 予測に設定される

30

[0098] 上記のデフォルト値は、拡張単位 510 に関係するデフォルトデータの HEVC 実装について示される。但し、同様の検査を必要とするコーデックが、拡張単位 510 からのデータだけでなく、述べられたようなデフォルト値をも実装することができることに留意されたい。

## 【0089】

[0099] 幾つかの実施形態では、現在 PU の予測モードが決定されるとき、ビデオエンコーダ 20 は、それに応じてデフォルト値を更新することができる。しかしながら、イントラ予測モードは、現在 PU がイントラ予測モードにあるときにのみ更新され、他の場合、イントラ予測モードは DC 予測のままである。

40

## 【0090】

[00100] 拡張単位 510 中のそのようなデフォルトデータの使用は、ビデオエンコーダ 20 がデフォルト値に基づいてあるデータを仮定することができるので、簡略化された検査を生じ、利用不可能性検査を最小限に抑えることができる。その結果、ビデオエンコーダ 20 によって実行される検査は、以下のように簡略化され得る。

40

[00101] スプリットフラグのための CABAC コンテキスト導出。CABAC コンテキストは、現在 CU の CU 深度と CU\_A 及び CU\_B の CU 深度とから導出される。

## 【0091】

[00102] スキップフラグのための CABAC コンテキスト導出。CABAC コンテキストは、CU\_A 及び CU\_B がスキップモードに設定されるかどうかに基づいて導出され

50

る。

【0092】

[00103] マージ候補導出。ビデオエンコーダ20は、隣接PUがインターモード予測にあるかどうかを検査することができる。隣接PUがインターモード予測にない場合、マージ候補は発見されない。隣接PUがインターモード予測にある場合、マージ候補は、隣接PUから導出され得る。

【0093】

[00104] 動きベクトル予測子導出。ビデオエンコーダ20は、隣接PUがインターモード予測にあるかどうかを検査することができる。隣接PUがインターモード予測にない場合、動き予測子は発見されない。隣接PUがインターモード予測にある場合、動き予測子は、隣接PUから導出される。

【0094】

[00105] イントラモード予測子導出。エンコーダは、現在PUのイントラ予測モードを予測するために隣接PU A及びPU Bのイントラ予測モードを使用することができる。

【0095】

[00106] 幾つかの実施形態では、バッファ又はメモリサイズ（例えば、記憶装置34）は制限され得る。従って、メモリ使用を保存するためにデフォルトデータのより小さいブロックが実装され得る。幾つかの実施形態では、ビデオエンコーダ20は、スライス又はタイル（例えば、ビデオデータ構造500）全体を記憶することではなく、メモリ中の単一のCTUなど、より小さいデータ構造を記憶することによって、メモリ使用量を低減することができる。次いで、CTUは、符号化中に繰り返され、データ構造500全体を記憶することと同じ目的をはたすことができる。

【0096】

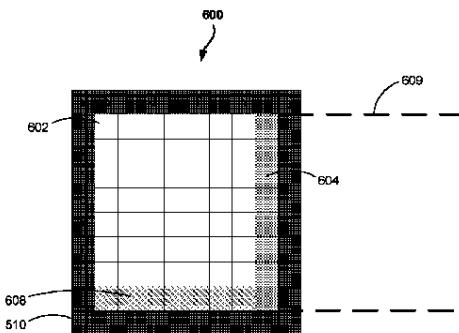

[00107] 図6Aは、ビデオデータを符号化するために使用されるデータ構造のグラフィカル表現である。データ構造600が、本明細書ではPU602と呼ばれる、複数の白色の正方形として示された、図5に示されているPUの一部分を有する。幾つかの実施形態では、データ構造600は、(M/N) × (M/N)要素として定義されるサイズを有し、ここで、データ構造600は、サイズM × Mと最小PUサイズN × NとをもつCTUを符号化するために使用され得る。例えば、M = 32及びN = 4であるデータ構造600が示される。ビデオエンコーダ20は、あらゆる方向において、1つの要素又は（灰色で着色された）拡張単位510によってデータ構造を拡張することができる。従って、メモリ中で、データ構造600は10 × 10要素として表され得る。これは、灰色の正方形として示される拡張単位510に加えて、例えば、CTUに対応する、8 × 8要素又はPU602を含むことができる。幾つかの実施形態では、PU602の8 × 8ブロックは、図4又は図5の単一の白色のブロック（例えば、非コード化CTU404、502）に対応することができる。

【0097】

[00108] 拡張単位510は、8 × 8PU602の外側に配置されるものとして記述され得る。代替的に、拡張単位510は、8 × 8PU602の外周に沿って配設されるものとして記述され得る。次いで、10 × 10データ構造600が行及び列に関して参照され得、ここで、行は水平方向に配置され、列は垂直方向に配置される。従って、データ構造600は10個の行及び10個の列を有する。

【0098】

[00109] 幾つかの実施形態では、ビデオエンコーダ20は、メモリ（例えば、記憶装置34）にデータ構造600を保存し、その後、非コード化PU（例えば、PU602）、又は符号化が進むにつれて隣接PUについてのデフォルト値を設定するためにデータ構造600を更新し、参照することができる。幾つかの実施形態では、後続のCTUが符号化されるとき、拡張単位510のみがバッファされ、更新される。

【0099】

10

20

30

40

50

[00110]幾つかの実施形態では、データ構造600は、新しいビデオブロック（例えば、CTU）が符号化されるとき、ビデオエンコーダ20が参照することができるデフォルトデータ構造を表すことができる。データ構造500の場合のようにスライス全体をバッファする代わりに、ビデオエンコーダ20は、 $10 \times 10$ 要素のはるかに小さい構造を占有するデータ構造600をバッファすることができる。述べられたように、データ構造600は、HEVCにおいてスライス又はタイルのためのベースデータユニットである、等価なサイズのCTUからのデータを含んでいる。

#### 【0100】

[00111]ビデオエンコーダ20がスライス又はタイル（例えば、ビデオデータブロック400）を符号化する前に、非コード化PU（例えば、白色の正方形又はPU602）中のデータの全てが、データ構造600によって示されたデフォルト値に設定され得る。データ構造600の上部に沿って小文字a～hで標示されたブロックと左側に沿って大文字A～Hで標示されたブロックとは、スライス又はタイル（例えば、データ構造500）が符号化されるとき、データ構造600中で周期的に更新される拡張単位510からのデータ（例えば、列及び行）を表すことができる。幾つかの実施形態では、データ構造600の一部分のみがバッファされる。例えば、拡張単位510、（淡い灰色で着色された）複数の最右PU604、及び複数の最下PU608（斜めストライプ）が、符号化の際に後で使用するためにバッファされ得、残りの白色のブロック（例えば、PU602）からのデータは廃棄され得る。最右PU604及び最下PU608は、コード化されているCTUの、それぞれ右端及び最下部における、PU602又はコード化要素を表す。

10

20

#### 【0101】

[00112]図示のように、CTU609は、コード化スライス（例えば、データブロック400）中の連続CTU間の関係を示す破線によって表される。データ構造600が、その後符号化されるCTU（例えば、CTU609）からのデータを用いて更新されるとき、最右PU604は、データ構造600に記憶され、CTU609を符号化するために参照されるデータ構造600の（A～Hと標示された）最左拡張単位510になる。これは以下でより詳細に説明される。

#### 【0102】

[00113]図6Bは、図6Aのデータ構造を使用する符号化ビデオデータである複数のCTUのグラフィカル表現である。3つのCTU610、620、630が、実線によって囲まれて示され、符号化されるべきデータを示す。破線及び一点鎖線は、CTU610、620、630の各々が符号化されるときのデータ構造600中のデータの相対位置を示す。従って、CTU610、620、630内に含まれている白色のスペースは、データ構造600の $8 \times 8$ PU、又は、幾つかの実施形態では、図4及び図5の単一のブロックに対応することができる。概して、CTU610、620、630の各々を符号化するために参照されるデータ構造600は、それぞれ、水平方向における2つの列によって重複される。重複は、ビデオエンコーダ20が、連続CTUを符号化するためにデータ構造600にバッファされたデータをどのように参照することができるかを表す。CTU610、620、630の各々は、拡張単位510を含むエリアを包含する、 $10 \times 10$ 要素の破線又は一点鎖線ボックスによって囲まれる。CTU610、620、630の各々の右側にある淡い灰色の要素とそれらの最下部に沿ったストライプの要素とは、それぞれ、最右PU604及び最下PU608（図6）を表し、それらは、連続CTUが符号化されるとき、連続CTUの拡張単位（例えば、A～H、a～j）を更新するために使用される。図の明快のために、図6B内の要素の全てが標示されるとは限らない。

30

40

#### 【0103】

[00114]CTU610はCTU620に隣接し、ここで、それぞれの破線ボックス及び一点鎖線ボックスは、CTU610のためのデータ構造600中のPU604の最右列と、CTU620を符号化するために使用されるデータ構造600内の拡張単位510の最左列とだけ重複する。同じことがCTU620とCTU630とについて当てはまる。更に、3つのCTU640、650、660より多くのために参照されるデータ構造600

50

の部分を含む、CTUの第2の行が、2つの行だけCTU610、620、620と重複する。特に、CTU640、650、660を符号化するためのデータ構造600は、交互の破線及び一点鎖線が最下PU608（斜めストライプ）と拡張単位の最下行とだけ垂直方向に重複して示される。

#### 【0104】

[00115]ビデオエンコーダ20がデータ構造600に従ってCTU610を符号化すると、（淡い灰色で示された）最右PU604は、バッファ中のデータ構造600の正方形A～Hにコピーされ、CTU620を符号化するために使用され得る。これは、次のCTU620を符号化する際に使用するために次に更新される、A<sub>2</sub>～H<sub>2</sub>、例えば、データ構造600中の拡張単位510についての値を置き換える。拡張単位A<sub>2</sub>～H<sub>2</sub>及びA<sub>3</sub>～H<sub>3</sub>は、後続のCTU620、630をコード化する際に使用するためのデータ構造600を更新するために最右CU604（図6A）からのデータが使用されることを示すために、淡い灰色で着色される。次いで、（斜めストライプ正方形として示される）最下CU608は、スライス又はタイル幅に等しいサイズをもつ要素の数を記憶することができるメモリ（例えば、記憶装置34）中のライン要素バッファにコピーされ得る。10

#### 【0105】

[00116]データ構造600は、スライス又はタイル（例えば、ビデオデータブロック400）の第1のCTU行中の最後の最後のCTUまでCTUによって連続的に更新されたCTUであり得る。例えば、CTU640をもつ第2のCTU行を開始する前に、データ構造600のA～H、aについての値と、CTU640内のPU602についての全てのデータとが、データ構造600に基づいてデフォルト値に初期化され得る。更に、H<sub>1</sub>についてのデータはデフォルト値に設定され得、（図6Aのa～jに対応する）ブロックb<sub>x～h<sub>x</sub></sub>、H<sub>2</sub>、b<sub>y</sub>についての値は、CTU640を符号化するより前に最下ブロック608からのラインバッファに記憶されたデータを用いて更新され得る。幾つかの実施形態では、垂直方向における参照CTUが利用可能でない状況では、関連するデータ要素は、データ構造600を使用してデータを更新する前にデフォルト値に初期化され得る。例えば、PU d<sub>x</sub>がイントラコード化PUである場合、イントラモードは、更新する前にDCモードにリセットされる。次いで、ビデオエンコーダ20は、CTU640、CTU650、CTU660などをもつ第2のCTU行上でプロセスを繰り返すことができる。20

#### 【0106】

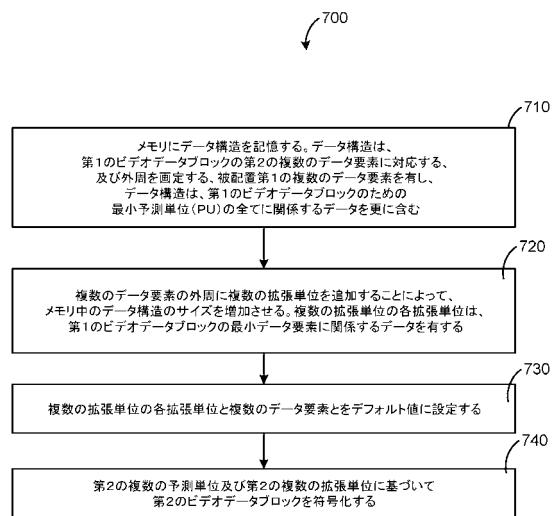

[00117]図7は、図5のデータ構造を使用してビデオデータを符号化するための方法のフローチャートである。方法700は、本明細書で説明されるように、ビデオデータブロック400、データ構造500及びデータ構造600を使用して実装され得る。30

#### 【0107】

[00118]ブロック710において、エンコーダはメモリにデータ構造を記憶する。データ構造（例えば、データ構造500）は、ビデオデータブロック400など、第1のビデオデータブロックのサイズに一致するように幾何学的に配置された複数のデータ要素を有することができる。データ構造500は、第1のビデオデータブロック400のための最小予測単位（PU）の全てに関係するデータを更に含むことができる。データは、ビデオデータブロックのための最小予測単位を含み、特性の中でも、コード化単位深度、予測モード、及びインター予測モードについてのデフォルト値に関係することができる。40

#### 【0108】

[00119]ブロック720において、エンコーダ20は、複数のデータ要素（例えば、ビデオデータブロック400）の外周に沿って複数の拡張単位510を追加することによって、記憶装置34中のデータ構造のサイズを増加させる。拡張単位510の各々は、第1のビデオデータブロック400の最小データ要素に関係するデータを有することができる。例えば、ビデオエンコーダ20は、ビデオデータブロック400のあらゆる側に拡張単位510を追加し、データ構造500を形成することができる。

#### 【0109】

[00120]ブロック730において、ビデオエンコーダ20は、各拡張単位510複数の

10

20

30

40

50

データ要素をデフォルト値に設定する。拡張単位 510 は、符号化されるべきビデオデータのための第 1 のデータ構造 500 ( 例えばスライス又はタイル ) についてのデフォルト値に設定されるデータ又は値を有することができる。

【 0110 】

[00121] ブロック 740 において、ビデオエンコーダ 20 は、データ構造 500 を使用してビデオデータブロック 400 を符号化する。拡張単位 510 は、C U 404 を符号化するためのデフォルト参照として働くことができる。その場合、データ構造 500 の使用が利用不可能性検査を低減することができる。

【 0111 】

[00122] 従って、方法 700 は、連続ビデオデータブロック 400 を符号化するために必要とされるバッファメモリ ( 例えば、記憶装置 34 ) の量を低減するために、ビデオエンコーダ 20 によって実装され得る。更に、方法 700 は、ビデオエンコーダ 20 の必要とされる利用不可能性検査に関係するオーバーヘッドを低減することができる。

【 0112 】

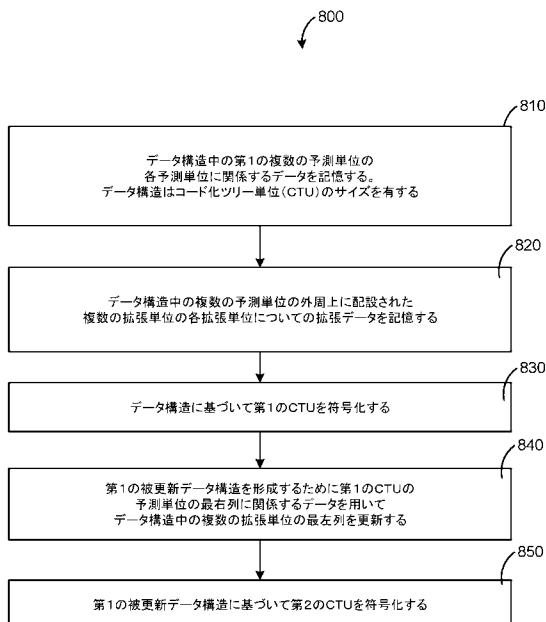

[00123] 図 8 は、図 6A のデータ構造を使用してビデオデータを符号化するための方法のフローチャートであるフローチャートである。方法 800 は、本明細書で説明されるように、ビデオデータブロック 400 及びデータ構造 600 を使用して実装され得る。

【 0113 】

[00124] ブロック 810 において、ビデオエンコーダ 20 は、データ構造 ( 例えば、データ構造 600 ) 中の第 1 の複数の予測単位の各予測単位に関係するデータを記憶する。データ構造 600 は、コード化ツリー単位 ( C T U ) のサイズを有することができる。

【 0114 】

[00125] ブロック 820 において、ビデオエンコーダ 20 は、データ構造中の複数の予測単位の外周に沿って配設された複数の拡張単位 510 の各拡張単位 510 についての拡張データを記憶する。

【 0115 】

[00126] ブロック 830 において、ビデオエンコーダ 20 は、データ構造 600 に基づいて第 1 の C T U ( 例えば、C T U 610 ) を符号化する。

【 0116 】

[00127] ブロック 840 において、ビデオエンコーダ 20 は、第 1 の更新されたデータ構造 600 を形成するために第 1 の C T U のコード化単位又は予測単位の最右列 ( 例えば、最右 C U 604 ) に関係するデータを用いてデータ構造中の複数の拡張単位 510 の最左列 ( 例えば、a 、 A ~ H と標示された拡張単位 510 ) を更新する。

【 0117 】

[00128] ブロック 850 において、ビデオエンコーダ 20 は、第 1 の更新されたデータ構造 600 に基づいて第 2 の C T U ( 例えば、C T U 620 ) を符号化する。

【 0118 】

[00129] 従って、方法 800 は、連続 C T U 620 、 630 、 640 、 650 、 660 、又はビデオデータブロック 400 のうちの 1 つ又は複数を符号化するために必要とされるバッファメモリ ( 例えば、記憶装置 34 ) の量を低減することができる。更に、方法 800 は、ビデオエンコーダ 20 の必要とされる利用不可能性検査に関係するオーバーヘッドを低減することができる。

【 0119 】

[00130] 本明細書で開示される情報及び信号は、多種多様な技術及び方法のいずれかを使用して表され得る。例えば、上記の説明全体にわたって言及され得るデータ、命令、コマンド、情報、信号、ビット、シンボル及びチップは、電圧、電流、電磁波、磁界又は磁性粒子、光場又は光学粒子若しくはそれらの任意の組合せによって表され得る。

【 0120 】

[00131] 本明細書で開示される実施形態に関して説明された様々な例示的な論理ブロック、モジュール、回路及びアルゴリズムステップは、電子ハードウェア、コンピュータソ

10

20

30

40

50

ソフトウェア又はその両方の組合せとして実装され得る。ハードウェアとソフトウェアとのこの互換性を明確に示すために、様々な例示的な構成要素、ブロック、モジュール及びステップが、概してそれらの機能に関して上記で説明された。そのような機能がハードウェアとして実装されるのかソフトウェアとして実装されるのかは、特定の適用例及び全体的なシステムに課される設計制約に依存する。当業者は、説明された機能を特定の適用例ごとに様々な方法で実装し得るが、そのような実装の決定は、本開示の範囲からの逸脱を生じるものと解釈されるべきではない。

#### 【0121】

[00132]本明細書で説明された実施形態は、ハードウェア、ソフトウェア、ファームウェア又はそれらの任意の組合せで実装され得る。そのような実施形態は、汎用コンピュータ、ワイヤレス通信機器ハンドセット、又はワイヤレス通信機器ハンドセット及び他の機器における適用例を含む複数の用途を有する集積回路機器など、様々な機器のいずれかにおいて実装され得る。モジュール又は構成要素として説明された特徴は、集積論理機器と一緒に、又は個別であるが相互運用可能な論理機器として別々に実装され得る。ソフトウェアで実装された場合、本方法は、実行されたとき、上記で説明された方法のうちの1つ又は複数を実行する命令を含むプログラムコードを備えるコンピュータ可読データ記憶媒体によって、少なくとも部分的に実現され得る。コンピュータ可読データ記憶媒体は、パッケージング材料を含むことができるコンピュータプログラム製品の一部を形成し得る。コンピュータ可読媒体は、同期型ダイナミックランダムアクセスメモリ(SDRAM)などのランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、不揮発性ランダムアクセスメモリ(NVRAM)、電気的消去可能プログラマブル読み取り専用メモリ(E PROM(登録商標))、フラッシュメモリ、磁気又は光学データ記憶媒体など、メモリ又はデータ記憶媒体を備えることができる。本方法は、追加又は代替として、伝搬信号又は電波など、命令又はデータ構造の形態でプログラムコードを搬送又は伝達し、コンピュータによってアクセスされ、読み取られ、及び/又は実行され得るコンピュータ可読通信媒体によって、少なくとも部分的に実現され得る。

10

20

30

40

#### 【0122】

[00133]プログラムコードは、1つ又は複数のデジタル信号プロセッサ(DSP)、汎用マイクロプロセッサ、特定用途向け集積回路(ASIC)、フィールドプログラマブル論理アレイ(FPGA)、あるいは他の等価の集積回路又はディスクリート論理回路など、1つ又は複数のプロセッサを含むことができるプロセッサによって実行され得る。そのようなプロセッサは、本開示で説明された方法及びプロセスのいずれかを実行するように構成され得る。汎用プロセッサはマイクロプロセッサであり得るが、代替として、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、又は状態機械であり得る。プロセッサはまた、コンピューティング機器の組合せ、例えば、DSPとマイクロプロセッサとの組合せ、複数のマイクロプロセッサ、DSPコアと連携する1つ又は複数のマイクロプロセッサ、あるいは任意の他のそのような構成として実装され得る。従って、本明細書で使用される「プロセッサ」という用語は、上記の構造、上記の構造の任意の組合せ、あるいは本明細書で説明された方法の実装に好適な他の構造又は装置のいずれかを指すことがある。更に、幾つかの態様では、本明細書で説明された機能は、符号化及び復号のために構成された専用のソフトウェアモジュール又はハードウェアモジュール内に提供され、あるいは複合ビデオエンコーダ/デコーダ(コーデック)に組み込まれ得る。

#### 【0123】

[00134]本開示の実施形態は、特定の実施形態について上記で説明されたが、本開示の多くの変形形態が可能である。例えば、様々な構成要素の数は増加又は減少され得、電源電圧を決定するモジュール及びステップは、周波数、別のシステムパラメータ、又はパラメータの組合せを決定するために変更され得る。更に、様々な実施形態の特徴は、上記で説明された組合せとは異なる組合せで組み合わせられ得る。

#### 【0124】

50

[00135]当業者は、本明細書で開示される実施形態に関して説明された様々な例示的なブロック及びモジュールが様々な形態で実装され得ることを諒解されよう。幾つかのブロック及びモジュールが、概してそれらの機能に関して上記で説明された。そのような機能がどのように実装されるかは、全体的なシステムに課される設計制約に依存する。当業者は、説明された機能を特定の適用例ごとに様々な方法で実装し得るが、そのような実装の決定は、本開示の範囲からの逸脱を生じるものと解釈されるべきではない。更に、モジュール、ブロック、又はステップ内の機能のグループ化は、説明を簡単にするためのものである。本開示から逸脱することなく、特定の機能又はステップが、1つのモジュール又はブロックから移されるか、あるいはモジュール又はブロックにわたって分散され得る。

【0125】

10

[00136]開示される実施形態の上記の説明は、当業者が本開示の主題を製作又は使用できるように提供されたものである。これらの実施形態への様々な変更は当業者には容易に明らかであり、本明細書で説明された一般原理は、本開示の趣旨又は範囲から逸脱することなく他の実施形態に適用され得る。従って、本明細書で提示される説明及び図面は、本開示の現在好ましい実装形態を表し、従って、本開示によって広く企図される主題を表すことを理解されたい。本開示の範囲は、当業者に明らかになり得る他の実施形態を完全に包含することと、従って、本開示の範囲は、添付の特許請求の範囲以外のものによって限定されないことを更に理解されたい。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

【図4】

FIG. 4

FIG. 3

【図5】

FIG. 5

【図6A】

FIG. 6A

【図 6 B】

FIG. 6B

【図 7】

FIG. 7

【図 8】

FIG. 8

**【手続補正書】**

【提出日】平成29年11月7日(2017.11.7)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

ビデオデータを符号化する方法であって、

メモリにデータ構造を記憶することと、前記データ構造が第1の複数のデータ要素を有し、外周を画定し、前記第1の複数のデータ要素がピクチャの第1の部分の第2の複数のデータ要素に対応して配置され、前記データ構造が、ピクチャの前記第1の部分のための最小予測単位( P U )の全てに關係するデータを更に含む、

前記メモリ中の前記データ構造のサイズを増加することと、前記増加することは、前記第1の複数のデータ要素の前記外周全体に沿って複数の拡張単位を追加することを備え、前記複数の拡張単位の各拡張単位が、ピクチャの前記第1の部分の最小データ要素に關係するデータを有する、

前記複数の拡張単位の各拡張単位と前記第1の複数のデータ要素とをデフォルト値に設定することと、

前記データ構造に基づいてピクチャの前記第1の部分を符号化することとを備える、方法。

**【請求項2】**

前記データ構造に基づいて前記第2の複数のデータ要素の各データ要素に対して利用不可能性検査を実行することと更に備える、請求項1に記載の方法。

**【請求項3】**

ピクチャの前記第1の部分の現在 C U の C U 深度と少なくとも1つの隣接 C U の C U 深度とに基づいて、前記現在 C U のためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化( C A B A C )コンテキストを決定することを更に備え、前記現在 C U が前記第2の複数のデータ要素のうちのデータ要素であり、前記少なくとも1つの隣接 C U が前記第1の複数のデータ要素のうちのデータ要素である、請求項2に記載の方法。

**【請求項4】**

少なくとも1つの隣接コード化単位( C U )がスキップモードに設定されるかどうかに基づいて、ピクチャの前記第1の部分の現在 C U のためのスキップフラグのためのコンテキスト適応型バイナリ算術コード化( C A B A C )コンテキストを決定することを更に備え、前記現在 C U が前記第2の複数のデータ要素のうちのデータ要素であり、前記少なくとも1つの隣接 C U が前記第1の複数のデータ要素のうちのデータ要素である、請求項2に記載の方法。

**【請求項5】**

ピクチャの前記第1の部分の現在 P U の隣接 P U がインター モード予測に設定されると決定することと、

前記隣接 P U に基づいて前記現在 P U のためのマージ候補を決定することと、前記隣接 P U が前記第1の複数のデータ要素のうちのデータ要素である、を更に備える、請求項2に記載の方法。

**【請求項6】**

ピクチャの前記第1の部分の現在 P U の隣接 P U がインター モード予測に設定されると決定することと、

前記隣接 P U に基づいて前記現在 P U の動き予測子を決定することと、前記隣接 P U が前記第1の複数のデータ要素のうちのデータ要素である、を更に備える、請求項2に記載の方法。

**【請求項 7】**

隣接 P U に基づいて、ピクチャの前記第 1 の部分の現在 P U のためのイントラ予測モードを予測することを更に備え、前記隣接 P U が前記第 1 の複数のデータ要素のうちのデータ要素である、請求項 2 に記載の方法。

**【請求項 8】**

更新されたデータ構造を形成するためにピクチャの第 2 の部分のサイズ及び形状に基づいて前記データ構造の前記複数の拡張単位を更新することと、

前記更新されたデータ構造に基づいてピクチャの前記第 2 の部分を符号化することとを更に備える、請求項 1 に記載の方法。

**【請求項 9】**

前記データ構造に基づいてピクチャの前記第 1 の部分を符号化することが、ピクチャの前記第 1 の部分を符号化するために空間予測のための参照として前記複数の拡張単位を使用することを備える、請求項 1 に記載の方法。

**【請求項 10】**

ピクチャの前記第 1 の部分の前記最小データ要素が、予測単位又はコード化単位を備える、請求項 1 に記載の方法。

**【請求項 11】**

ビデオデータを符号化するための装置であって、

第 1 の複数のデータ要素を有し、外周を画定するデータ構造を記憶するように構成されたメモリと、前記第 1 の複数のデータ要素はピクチャの第 1 の部分の第 2 の複数のデータ要素に対応して配置され、前記データ構造がピクチャの前記第 1 の部分のための最小予測単位 ( P U ) の全てに関係するデータを更に含む、

前記メモリに動作可能に結合され、

前記メモリ中の前記データ構造のサイズを増加することと、前記増加することは、前記第 1 の複数のデータ要素の前記外周全体に沿って複数の拡張単位を追加することを備え、前記複数の拡張単位の各拡張単位が、ピクチャの前記第 1 の部分の最小データ要素に関係するデータを有する、

前記複数の拡張単位の各拡張単位と前記第 1 の複数のデータ要素とをデフォルト値に設定することと、

前記データ構造に基づいてピクチャの前記第 1 の部分を符号化することとを行うように構成されたプロセッサとを備える、装置。

**【請求項 12】**

前記プロセッサが、前記データ構造に基づいて前記第 2 の複数のデータ要素の各データ要素に対して利用不可能性検査を実行するように更に構成された、請求項 1 に記載の装置。

**【請求項 13】**

ピクチャの前記第 1 の部分の現在 C U と少なくとも 1 つの隣接 C U の C U 深度とに基づいて、スプリットフラグのためのコンテキスト適応型バイナリ算術コード化 ( C A B A C ) コンテキストを決定することと、前記現在 C U が前記第 2 の複数のデータ要素のうちのデータ要素であり、前記少なくとも 1 つの隣接 C U が前記第 1 の複数のデータ要素のうちのデータ要素である、

前記少なくとも 1 つの隣接 C U がスキップモードに設定されるかどうかに基づいて、ピクチャの前記第 1 の部分の前記現在 C U のためのスキップフラグのための C A B A C コンテキストを決定することと、

ピクチャの前記第 1 の部分の現在 P U の隣接 P U がインター モード予測に設定されると決定することと、前記隣接 P U に基づいて前記現在 P U のためのマージ候補を決定することと、前記隣接 P U が前記第 1 の複数のデータ要素のうちのデータ要素である、

前記現在 P U の前記隣接 P U がインター モード予測に設定されると決定することと、前記隣接 P U に基づいて前記現在 P U の動き予測子を決定することと、

前記隣接 P U に基づいて、ピクチャの前記第 1 の部分の前記現在 P U のためのイントラ

予測モードを予測することとのうちの少なくとも1つを完了するように更に構成された前記プロセッサ、請求項11に記載の装置。

【請求項14】

前記プロセッサが、

更新されたデータ構造を形成するためにピクチャの第2の部分のサイズ及び形状に基づいて前記データ構造の前記複数の拡張単位を更新することと、

前記更新されたデータ構造に基づいてピクチャの前記第2の部分を符号化することを行いうように更に構成された、請求項11に記載の装置。

【請求項15】

前記プロセッサが、ピクチャの前記第1の部分を符号化するために空間予測のための前記複数の拡張単位を参照するように更に構成された、請求項11に記載の装置。

【請求項16】

前記プロセッサが、前記デフォルト値を、

コード化単位深度が0に等しい、

予測モードがイントラ予測に設定される、及び

イントラ予測モードがDC予測に設定される、に設定するように更に構成された、請求項11に記載の装置。

【請求項17】

ピクチャの前記第1の部分の前記最小データ要素が、予測単位又はコード化単位を備える、請求項11に記載の装置。

【請求項18】

ピクチャの前記第1の部分が、スライス又はタイルを備える、請求項11に記載の装置。

。

【請求項19】

ピクチャの部分中のビデオデータを符号化する方法であって、

データ構造中の第1の複数の予測単位(PU)の各PUに関係するデータを記憶することと、前記データ構造がコード化ツリー単位(CTU)のサイズを有する、

前記データ構造中の前記第1の複数のPUの外周全体に沿って配設された複数の拡張単位の拡張単位毎に拡張データを記憶することと、

前記データ構造に基づいて第1のCTUを符号化することと、

第1の更新されたデータ構造を形成するために前記第1のCTUのPUの最右列に関係するデータを用いて前記データ構造中の前記複数の拡張単位の最左列を更新することと、

前記第1の更新されたデータ構造に基づいて第2のCTUを符号化することとを備える、方法。

【請求項20】

要素ラインバッファに前記第1のCTUのPUの最下行に関係するデータを記憶することと、前記要素ラインバッファが、ピクチャの部分の幅に等しい第2の複数のPUに関係するデータを記憶するように構成された、

前記要素ラインバッファに前記第2のCTUのPUの最下行に関係するデータを記憶することと、

ピクチャの前記部分中のCTUの第1の行を符号化した後に、デフォルト値を用いて、前記データ構造中の前記複数の拡張単位の前記最左列と前記データ構造中の前記第1の複数のPUとを更新することと、CTUの前記第1の行が前記第1のCTUと前記第2のCTUとを含む、

第2の更新されたデータ構造を形成するために前記要素ラインバッファからのデータを用いて前記第1の更新されたデータ構造中の前記複数の拡張単位の最上行を更新することと、

前記第2の更新されたデータ構造に基づいてCTUの第2の行上の第3のCTUを符号化することとを更に備える、請求項19に記載の方法。

【請求項21】

前記データ構造に基づいて前記第1のCTUを符号化することが、前記第1のCTUを符号化するために空間予測のための参照として前記複数の拡張単位を使用することを備える、請求項19に記載の方法。

【請求項22】

前記第1の複数のPUの各PUが、前記第1のCTUのための最小PUを含み、前記第1の複数のPUの各PUに関係する前記データが、少なくとも、コード化単位深度、予測モード及びインター予測モードを備える、請求項19に記載の方法。

【請求項23】

前記複数の拡張単位の各拡張単位がデフォルト値を有するように設定され、前記デフォルト値は、

コード化単位深度が0に等しい、

予測モードがイントラ予測に設定される、及び

イントラ予測モードがDC予測に設定される、を備える、請求項19に記載の方法。

【請求項24】

前記データ構造に基づいて前記CTUの複数のコード化単位(CU)の各CUに対して利用不可能性検査を実行することを更に備える、請求項19に記載の方法。

【請求項25】

前記第1のCTUの現在CUのCU深度と前記データ構造の少なくとも1つの隣接PUのCU深度とに基づいて、前記現在CUのためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することを更に備え、前記現在CUが前記複数のCUのうちのCUであり、前記少なくとも1つの隣接PUが前記第1の複数のPUのうちのPUである、請求項24に記載の方法。

【請求項26】

少なくとも1つの隣接PUがスキップモードに設定されるかどうかに基づいて、前記CTUの現在CUのためのスキップフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することを更に備え、前記現在CUが前記複数のCUのうちのCUであり、前記少なくとも1つの隣接PUが前記第1の複数のPUのうちのPUである、請求項24に記載の方法。

【請求項27】

前記第1のCTUの現在CUの隣接PUがインターモード予測に設定されると決定することと、

前記隣接PUに基づいて前記現在CUのためのマージ候補を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、を更に備える、請求項24に記載の方法。

【請求項28】

前記第1のCTUの現在PUの隣接PUがインターモード予測に設定されると決定することと、

前記隣接PUに基づいて前記現在PUの動き予測子を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、を更に備える、請求項24に記載の方法。

【請求項29】

隣接PUに基づいて、前記第1のCTUの現在PUのためのイントラ予測モードを予測することを更に備え、前記隣接PUが前記第1の複数のPUのうちのPUである、請求項24に記載の方法。

【請求項30】

ビデオデータを符号化するための装置であって、

データ構造を記憶することと、前記データ構造が、第1の複数の予測単位(PU)の各PUに関係するデータを有し、前記データ構造がコード化ツリー単位(CTU)のサイズを更に有する、

前記データ構造中の前記第1の複数のPUの外周全体に沿って配設された複数の拡張単位の拡張単位毎に拡張データを記憶することとを行うように構成されたメモリと、

前記メモリに動作可能に結合され、

前記データ構造に基づいて第1のCTUを符号化することと、

第1の更新されたデータ構造を形成するために前記第1のCTUのPUの最右列に関係するデータを用いて前記データ構造中の前記複数の拡張単位の最左列を更新することと、

前記第1の更新されたデータ構造に基づいて第2のCTUを符号化することを行いうように構成されたプロセッサとを備える、装置。

#### 【請求項31】

前記プロセッサは、

要素ラインバッファに前記第1のCTUのPUの最下行に関係するデータを記憶することと、前記要素ラインバッファが、ピクチャ幅の部分に等しい第2の複数のPUに関係するデータを記憶するように構成される、

前記要素ラインバッファに前記第2のCTUのPUの最下行に関係するデータを記憶することと、

ピクチャの前記部分中のCTUの第1の行を符号化した後に、デフォルト値を用いて、前記データ構造中の前記複数の拡張単位の前記最左列と前記データ構造中の前記第1の複数のPUとを更新することと、CTUの前記第1の行が前記第1のCTUと前記第2のCTUとを含む、

第2の更新されたデータ構造を形成するために前記要素ラインバッファからのデータを用いて前記第1の更新されたデータ構造中の前記複数の拡張単位の最上行を更新することと、

前記第2の更新されたデータ構造に基づいてCTUの第2の行上の第3のCTUを符号化することとを行うように更に構成された、請求項30に記載の装置。

#### 【請求項32】

前記第1のCTUの現在CUのCU深度と前記第1の複数のPUの少なくとも1つの隣接PUのCU深度とに基づいて、前記現在CUのためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することと、

前記少なくとも1つの隣接PUがスキップモードに設定されるかどうかに基づいて、前記第1のCTUの前記現在CUのためのスキップフラグのためのCABACコンテキストを決定することと、

前記第1のCTUの現在CUの隣接PUがインターモード予測に設定されると決定することと、前記隣接PUに基づいて前記現在CUのためのマージ候補を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、

現在PUの前記隣接PUがインターモード予測に設定されると決定することと、前記隣接PUに基づいて前記現在PUの動き予測子を決定することと、

前記隣接PUに基づいての前記第1のCTUの前記現在PUのためのイントラ予測モードを予測することとのうちの少なくとも1つを完了するように更に構成された前記プロセッサ、請求項30に記載の装置。

#### 【請求項33】

前記プロセッサが、空間予測のための参照として前記データ構造を使用して前記第1のCTUを符号化するように更に構成された、請求項30に記載の装置。

#### 【請求項34】

前記第1の複数のPUの各PUが、前記第1のCTUのための最小PUを含み、前記データが、少なくとも、コード化単位深度、予測モード、及びインター予測モードを備える、請求項30に記載の装置。

#### 【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0125

【補正方法】変更

【補正の内容】

## 【 0 1 2 5 】

[00136] 開示される実施形態の上記の説明は、当業者が本開示の主題を製作又は使用できるように提供されたものである。これらの実施形態への様々な変更は当業者には容易に明らかであり、本明細書で説明された一般原理は、本開示の趣旨又は範囲から逸脱することなく他の実施形態に適用され得る。従って、本明細書で提示される説明及び図面は、本開示の現在好ましい実装形態を表し、従って、本開示によって広く企図される主題を表すことを理解されたい。本開示の範囲は、当業者に明らかになり得る他の実施形態を完全に包含することと、従って、本開示の範囲は、添付の特許請求の範囲以外のものによって限定されないことを更に理解されたい。

以下に本願の出願当初の特許請求の範囲に記載された発明を付記する。

## [ C 1 ]

ビデオデータを符号化する方法であって、

メモリにデータ構造を記憶することと、前記データ構造が第1の複数のデータ要素を有し、外周を画定し、前記第1の複数のデータ要素がピクチャの第1の部分の第2の複数のデータ要素に対応して配置され、前記データ構造が、ピクチャの前記第1の部分のための最小予測単位( P U )の全てに関係するデータを更に含む、

前記第1の複数のデータ要素の前記外周に沿って複数の拡張単位を追加することを備えることによって、前記メモリ中の前記データ構造のサイズを増加することと、前記複数の拡張単位の各拡張単位が、ピクチャの前記第1の部分の最小データ要素に関係するデータを有する、

前記複数の拡張単位の各拡張単位と前記第1の複数のデータ要素とをデフォルト値に設定することと、

前記データ構造に基づいてピクチャの前記第1の部分を符号化することとを備える、方法。

## [ C 2 ]

前記データ構造に基づいて前記第2の複数のデータ要素の各データ要素に対して利用不可能性検査を実行することとを更に備える、C 1 に記載の方法。

## [ C 3 ]

ピクチャの前記第1の部分の現在 C U の C U 深度と少なくとも 1 つの隣接 C U の C U 深度とに基づいて、前記現在 C U のためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化( C A B A C )コンテキストを決定することを更に備え、前記現在 C U が前記第2の複数のデータ要素のうちのデータ要素であり、前記少なくとも 1 つの隣接 C U が前記第1の複数のデータ要素のうちのデータ要素である、C 2 に記載の方法。

## [ C 4 ]

少なくとも 1 つの隣接コード化単位( C U )がスキップモードに設定されるかどうかに基づいて、ピクチャの前記第1の部分の現在 C U のためのスキップフラグのためのコンテキスト適応型バイナリ算術コード化( C A B A C )コンテキストを決定することを更に備え、前記現在 C U が前記第2の複数のデータ要素のうちのデータ要素であり、前記少なくとも 1 つの隣接 C U が前記第1の複数のデータ要素のうちのデータ要素である、C 2 に記載の方法。

## [ C 5 ]

ピクチャの前記第1の部分の現在 P U の隣接 P U がインター モード予測に設定されると決定することと、

前記隣接 P U に基づいて前記現在 P U のためのマージ候補を決定することと、前記隣接 P U が前記第1の複数のデータ要素のうちのデータ要素である、を更に備える、C 2 に記載の方法。

## [ C 6 ]

ピクチャの前記第1の部分の現在 P U の隣接 P U がインター モード予測に設定されると決定することと、

前記隣接 P U に基づいて前記現在 P U の動き予測子を決定することと、前記隣接 P U が

前記第1の複数のデータ要素のうちのデータ要素である、を更に備える、C2に記載の方法。

[ C 7 ]

隣接PUに基づいて、ピクチャの前記第1の部分の現在PUのためのイントラ予測モードを予測することを更に備え、前記隣接PUが前記第1の複数のデータ要素のうちのデータ要素である、C2に記載の方法。

[ C 8 ]

更新されたデータ構造を形成するためにピクチャの第2の部分のサイズ及び形状に基いて前記データ構造の前記複数の拡張単位を更新することと、

更新された前記データ構造に基づいてピクチャの前記第2の部分を符号化することを更に備える、C1に記載の方法。

[ C 9 ]

前記データ構造に基づいてピクチャの前記第1の部分を符号化することが、ピクチャの前記第1の部分を符号化するために空間予測のための参照として前記複数の拡張単位を使用することを備える、C1に記載の方法。

[ C 10 ]

ピクチャの前記第1の部分の前記最小データ要素が、予測単位又はコード化単位を備える、C1に記載の方法。

[ C 11 ]

ビデオデータを符号化するための装置であって、

第1の複数のデータ要素を有し、外周を画定するデータ構造を記憶するように構成されたメモリと、前記第1の複数のデータ要素はピクチャの第1の部分の第2の複数のデータ要素に対応して配置され、前記データ構造がピクチャの前記第1の部分のための最小予測単位(PU)の全てに関係するデータを更に含む、

前記メモリに動作可能に結合され、

前記第1の複数のデータ要素の前記外周に沿って複数の拡張単位を追加することを備えることによって、前記メモリ中の前記データ構造のサイズを増加することと、前記複数の拡張単位の各拡張単位が、ピクチャの前記第1の部分の最小データ要素に関係するデータを有する、

前記複数の拡張単位の各拡張単位と前記第1の複数のデータ要素とをデフォルト値に設定することと、

前記データ構造に基づいてピクチャの前記第1の部分を符号化することとを行うように構成されたプロセッサとを備える、装置。

[ C 12 ]

前記プロセッサが、前記データ構造に基づいて前記第2の複数のデータ要素の各データ要素に対して利用不可能性検査を実行するように更に構成された、C11に記載の装置。

[ C 13 ]

ピクチャの前記第1の部分の現在CUと少なくとも1つの隣接CUのCU深度とに基づいて、スプリットフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することと、前記現在CUが前記第2の複数のデータ要素のうちのデータ要素であり、前記少なくとも1つの隣接CUが前記第1の複数のデータ要素のうちのデータ要素である、

前記少なくとも1つの隣接CUがスキップモードに設定されるかどうかに基づいて、ピクチャの前記第1の部分の前記現在CUのためのスキップフラグのためのCABACコンテキストを決定することと、

ピクチャの前記第1の部分の現在PUの隣接PUがインター モード予測に設定されると決定することと、前記隣接PUに基づいて前記現在PUのためのマージ候補を決定することと、前記隣接PUが前記第1の複数のデータ要素のうちのデータ要素である、

前記現在PUの前記隣接PUがインター モード予測に設定されると決定することと、前記隣接PUに基づいて前記現在PUの動き予測子を決定することと、

前記隣接 P U に基づいて、ピクチャの前記第 1 の部分の前記現在 P U のためのイントラ予測モードを予測することとのうちの少なくとも 1 つを完了するように更に構成された前記プロセッサ、C 1 1 に記載の装置。

[ C 1 4 ]

前記プロセッサが、

更新されたデータ構造を形成するためにピクチャの第 2 の部分のサイズ及び形状に基づいて前記データ構造の前記複数の拡張単位を更新することと、

前記更新されたデータ構造に基づいてピクチャの前記第 2 の部分を符号化することを行いうように更に構成された、C 1 1 に記載の装置。

[ C 1 5 ]

前記プロセッサが、ピクチャの前記第 1 の部分を符号化するために空間予測のための前記複数の拡張単位を参照するように更に構成された、C 1 1 に記載の装置。

[ C 1 6 ]

前記プロセッサが、前記デフォルト値を、

コード化単位深度が 0 に等しい、

予測モードがイントラ予測に設定される、及び

イントラ予測モードが DC 予測に設定される、に設定するように更に構成された、C 1 1 に記載の装置。

[ C 1 7 ]

ピクチャの前記第 1 の部分の前記最小データ要素が、予測単位又はコード化単位を備える、C 1 1 に記載の装置。

[ C 1 8 ]

ピクチャの前記第 1 の部分が、スライス又はタイルを備える、C 1 1 に記載の装置。

[ C 1 9 ]

ピクチャの部分中のビデオデータを符号化する方法であって、

データ構造中の第 1 の複数の予測単位 ( P U ) の各 P U に関するデータを記憶することと、前記データ構造がコード化ツリー単位 ( C T U ) のサイズを有する、

前記データ構造中の前記第 1 の複数の P U の外周に沿って配設された複数の拡張単位の各拡張単位毎に拡張データを記憶することと、

前記データ構造に基づいて第 1 の C T U を符号化することと、

第 1 の更新されたデータ構造を形成するために前記第 1 の C T U の P U の最右列に関係するデータを用いて前記データ構造中の前記複数の拡張単位の最左列を更新することと、

前記第 1 の更新されたデータ構造に基づいて第 2 の C T U を符号化することとを備える方法。

[ C 2 0 ]

要素ラインバッファに前記第 1 の C T U の P U の最下行に関係するデータを記憶することと、前記要素ラインバッファが、ピクチャの部分の幅に等しい第 2 の複数の P U に関するデータを記憶するように構成された、

前記要素ラインバッファに前記第 2 の C T U の P U の最下行に関係するデータを記憶すること、

ピクチャの前記部分中の C T U の第 1 の行を符号化した後に、デフォルト値を用いて、前記データ構造中の前記複数の拡張単位の前記最左列と前記データ構造中の前記第 1 の複数の P U とを更新することと、C T U の前記第 1 の行が前記第 1 の C T U と前記第 2 の C T U とを含む、

第 2 の更新されたデータ構造を形成するために前記要素ラインバッファからのデータを用いて前記第 1 の更新されたデータ構造中の前記複数の拡張単位の最上行を更新すること、

前記第 2 の更新されたデータ構造に基づいて C T U の第 2 の行上の第 3 の C T U を符号化することとを更に備える、C 1 9 に記載の方法。

[ C 2 1 ]

前記データ構造に基づいて前記第1のCTUを符号化することが、前記第1のCTUを符号化するために空間予測のための参照として前記複数の拡張単位を使用することを備える、C19に記載の方法。

[C22]

前記第1の複数のPUの各PUが、前記第1のCTUのための最小PUを含み、前記第1の複数のPUの各PUに関係する前記データが、少なくとも、コード化単位深度、予測モード及びインター予測モードを備える、C19に記載の方法。

[C23]

前記複数の拡張単位の各拡張単位がデフォルト値を有するように設定され、前記デフォルト値は、

コード化単位深度が0に等しい、

予測モードがイントラ予測に設定される、及び

イントラ予測モードがDC予測に設定される、を備える、C19に記載の方法。

[C24]

前記データ構造に基づいて前記CTUの複数のコード化単位(CU)の各CUに対して利用不可能性検査を実行することを更に備える、C19に記載の方法。

[C25]

前記第1のCTUの現在CUのCU深度と前記データ構造の少なくとも1つの隣接PUのCU深度とに基づいて、前記現在CUのためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することを更に備え、前記現在CUが前記複数のCUのうちのCUであり、前記少なくとも1つの隣接PUが前記第1の複数のPUのうちのPUである、C24に記載の方法。

[C26]

少なくとも1つの隣接PUがスキップモードに設定されるかどうかに基づいて、前記CTUの現在CUのためのスキップフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することを更に備え、前記現在CUが前記複数のCUのうちのCUであり、前記少なくとも1つの隣接PUが前記第1の複数のPUのうちのPUである、C24に記載の方法。

[C27]

前記第1のCTUの現在CUの隣接PUがインターモード予測に設定されると決定することと、

前記隣接PUに基づいて前記現在CUのためのマージ候補を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、を更に備える、C24に記載の方法。

[C28]

前記第1のCTUの現在PUの隣接PUがインターモード予測に設定されると決定することと、

前記隣接PUに基づいて前記現在PUの動き予測子を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、を更に備える、C24に記載の方法。

[C29]

隣接PUに基づいて、前記第1のCTUの現在PUのためのイントラ予測モードを予測することを更に備え、前記隣接PUが前記第1の複数のPUのうちのPUである、C24に記載の方法。

[C30]

ビデオデータを符号化するための装置であって、

データ構造を記憶することと、前記データ構造が、第1の複数の予測単位(PU)の各PUに関係するデータを有し、前記データ構造がコード化ツリー単位(CTU)のサイズを更に有する、

前記データ構造中の前記第1の複数のPUの外周に沿って配設された複数の拡張単位の各拡張単位毎に拡張データを記憶することとを行うように構成されたメモリと、

前記メモリに動作可能に結合され、

前記データ構造に基づいて第1のCTUを符号化することと、

第1の更新されたデータ構造を形成するために前記第1のCTUのPUの最右列に関係するデータを用いて前記データ構造中の前記複数の拡張単位の最左列を更新することと、

前記第1の更新されたデータ構造に基づいて第2のCTUを符号化することとを行うように構成されたプロセッサとを備える、装置。

#### [ C 3 1 ]

前記プロセッサは、

要素ラインバッファに前記第1のCTUのPUの最下行に関係するデータを記憶することと、前記要素ラインバッファが、ピクチャ幅の部分に等しい第2の複数のPUに関係するデータを記憶するように構成される、

前記要素ラインバッファに前記第2のCTUのPUの最下行に関係するデータを記憶することと、

ピクチャの前記部分中のCTUの第1の行を符号化した後に、デフォルト値を用いて、前記データ構造中の前記複数の拡張単位の前記最左列と前記データ構造中の前記第1の複数のPUとを更新することと、CTUの前記第1の行が前記第1のCTUと前記第2のCTUとを含む、

第2の更新されたデータ構造を形成するために前記要素ラインバッファからのデータを用いて前記第1の更新されたデータ構造中の前記複数の拡張単位の最上行を更新することと、

前記第2の更新されたデータ構造に基づいてCTUの第2の行上の第3のCTUを符号化することとを行うように更に構成された、C 3 0に記載の装置。

#### [ C 3 2 ]

前記第1のCTUの現在CUのCU深度と前記第1の複数のPUの少なくとも1つの隣接PUのCU深度とに基づいて、前記現在CUのためのスプリットフラグのためのコンテキスト適応型バイナリ算術コード化(CABAC)コンテキストを決定することと、

前記少なくとも1つの隣接PUがスキップモードに設定されるかどうかに基づいて、前記第1のCTUの前記現在CUのためのスキップフラグのためのCABACコンテキストを決定することと、

前記第1のCTUの現在CUの隣接PUがインター モード予測に設定されると決定することと、前記隣接PUに基づいて前記現在CUのためのマージ候補を決定することと、前記隣接PUが前記第1の複数のPUのうちのPUである、

現在PUの前記隣接PUがインター モード予測に設定されると決定することと、前記隣接PUに基づいて前記現在PUの動き予測子を決定することと、

前記隣接PUに基づいての前記第1のCTUの前記現在PUのためのイントラ予測モードを予測することとのうちの少なくとも1つを完了するように更に構成された前記プロセッサ、C 3 0に記載の装置。

#### [ C 3 3 ]

前記プロセッサが、空間予測のための参照として前記データ構造を使用して前記第1のCTUを符号化することと、前記第1のCTUを符号化するように更に構成された、C 3 0に記載の装置。

#### [ C 3 4 ]

前記第1の複数のPUの各PUが、前記第1のCTUのための最小PUを含み、前記データが、少なくとも、コード化単位深度、予測モード、及びインター予測モードを備える、C 3 0に記載の装置。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2016/012064

A. CLASSIFICATION OF SUBJECT MATTER

INV. H04N19/70 H04N19/593 H04N19/463 H04N19/423

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H04N

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, COMPENDEX, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                             | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2015/010087 A1 (FUNNELL JOHN [GB])<br>8 January 2015 (2015-01-08)<br>paragraphs [0003], [0005], [0046],<br>[0047], [0052], [0055] - [0057]; figures<br>2,5<br>paragraph [0059] - paragraph [0074];<br>figures 6,7<br>-----                                                                                                                  | 1-34                  |

| A         | G.J. HAN ET AL: "Overview of the High Efficiency Video Coding (HEVC) Standard",<br>IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS<br>FOR VIDEO TECHNOLOGY,<br>1 January 2012 (2012-01-01), pages 1-19,<br>XP055045358,<br>ISSN: 1051-8215, DOI:<br>10.1109/TCSVT.2012.2221191<br>Sections II.A, IV.C and D, IV.H<br>sub-sections 3) and 4)<br>----- | 1-34                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

5 April 2016

12/04/2016

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Colesanti, Carlo

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2016/012064

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| US 2015010087                          | A1 08-01-2015    | NONE                    |                  |

## フロントページの続き

(51) Int.CI. F I テーマコード(参考)

H 0 4 N 19/52 (2014.01) H 0 4 N 19/52

(81) 指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,R0,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72) 発明者 チェン、ウェイ - ジュン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72) 発明者 トウ、チェンジエ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72) 発明者 ワン、シャンリン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72) 発明者 コバン、ムハンメド・ゼイド

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

F ターム(参考) 5C159 LA00 MA04 MA05 MA21 MC11 NN11 PP04 RC16 RC38 TA59

TB08 TC26 TC27 UA02