(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-285197

(P2005-285197A)

(43) 公開日 平成17年10月13日(2005.10.13)

(51) Int.CI.<sup>7</sup>**G 11 C 16/06****G 11 C 16/02**

F 1

G 11 C 17/00

テーマコード(参考)

5 B 125

審査請求 未請求 請求項の数 13 O L (全 41 頁)

(21) 出願番号

特願2004-95876 (P2004-95876)

(22) 出願日

平成16年3月29日 (2004.3.29)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【要約】

**【課題】** 低電源電圧下においても、高精度でセンス動作を行なって正確なデータの読み出を行なうことのできる不揮発性半導体記憶装置を提供する。

**【解決手段】** 読出回路(4)のセンスアンプに対し、電源電圧として、内部電圧発生回路(6)から内部電源電圧VCCよりも高い昇圧電圧Vbsを供給し、また内部データ線(DB)を介してのビット線プリチャージ電流は、内部電源電圧から供給する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数のメモリセル、および

前記複数のメモリセルの選択メモリセルのデータを検出するためのセンス増幅回路を備え、

前記センス増幅回路は、

内部電源電圧よりも高い電圧を受ける昇圧電源ノードと、

前記昇圧電源ノードに動作時結合され、前記選択メモリセルを流れる電流に応じて前記選択メモリセルの記憶データを読出す読出部と、

前記内部電源電圧を受けるノードに結合され、プリチャージ指示信号に応答して前記選択メモリセルへ前記内部電源ノードからの電流を供給して前記選択メモリセルが接続されるデータ線を所定電位にプリチャージするプリチャージ段とを備える、半導体記憶装置。10

**【請求項 2】**

外部から供給可能な外部電源電圧が前記昇圧電圧よりも高いときに動作可能とされ、活性化時、前記昇圧電圧を前記外部電源電圧の降圧により生成して前記昇圧電源ノードに供給する第1の電源と、

前記外部電源電圧が前記昇圧電圧よりも低いときに動作可能とされ、活性化時、前記外部電源電圧の昇圧動作により前記昇圧電圧を生成して前記昇圧電源ノードに供給する第2の電源とをさらに備える、請求項1記載の半導体記憶装置。20

**【請求項 3】**

前記読出部は、埋込チャネル方式のPチャネル絶縁ゲート型電界効果トランジスタを備える、請求項1記載の半導体記憶装置。

**【請求項 4】**

前記半導体記憶装置は、前記選択メモリセルのデータ読出基準の参照電流を生成する参照セルをさらに備え、30

前記センス増幅器は、

前記読出部として作用するカレントミラー段と、

基準バイアス電圧により伝達電圧レベルが制限され、前記プリチャージ段からの電流を前記選択メモリセルおよび前記参照セルに供給する電圧供給段と、

前記選択メモリセルおよび前記参照セルがそれぞれ結合されるデータ線を所定電位に初期設定する初期段と、30

前記カレントミラー段の出力ノードをイコライズするイコライズ段とを備える、請求項1記載の半導体記憶装置。

**【請求項 5】**

前記半導体記憶装置は、前記選択メモリセルのデータ読出基準の参照電流を生成する参照セルをさらに備え、40

前記センス増幅器は、

前記読出部として作用して、前記選択メモリセルに流れる電流を検出する第1のカレントミラー段と、

前記読出部として作用して、前記参照メモリセルに流れる電流を検出する第2のカレントミラー段と、

前記第1および第2のカレントミラー段をミラー結合して、前記選択メモリセルおよび前記参照セルの駆動電流の差に応じて前記選択メモリセルのデータを読出す第3のカレントミラー段と、

基準バイアス電圧により伝達電圧レベルが制限され、前記プリチャージ段からの電流を前記選択メモリセルおよび前記参照セルに供給する電圧供給段と、

前記選択メモリセルおよび前記参照セルがそれぞれ結合されるデータ線を所定電位に初期設定する初期段と、

前記プリチャージ段の出力ノードをイコライズする第1のイコライズ段と、

前記第3のカレントミラー段の出力ノードをイコライズする第2のイコライズ段を備え50

る、請求項 1 記載の半導体記憶装置。

**【請求項 6】**

各々がゲートを有し、そのしきい値電圧によりデータを記憶するトランジスタで構成される複数のメモリセル、

前記メモリセルと同一構造の参照セル、

前記複数のメモリセルの選択メモリセルの駆動電流と前記参照セルの駆動電流をセンスして前記選択メモリセルのデータを読出すセンス增幅回路、および

前記参照セルおよび前記選択メモリセルのゲートに印加する電圧を生成するゲート電圧発生回路を備え、前記ゲート電圧発生回路は、前記選択メモリセルの通常データ読出モード時には前記参照セルおよび前記選択メモリセルのゲートに対する電圧として同一レベルの電圧を生成し、前記選択メモリセルの書きまたは消去の検証モード時には、メモリセルの駆動電流分布範囲の上下端の位置のメモリセルの検証時には通常モード時とは異なるレベルの電圧を前記選択メモリセルのゲート電圧として生成する、半導体記憶装置。

10

**【請求項 7】**

複数のメモリセル、

参照メモリセル、および

前記複数のメモリセルのうちの選択メモリセルに接続される第 1 のノードと前記参照セルに接続される第 2 のノードとを有し、前記第 1 および第 2 のノードを流れる電流に従って前記選択メモリセルのデータを読出すセンス增幅器を備え、前記第 1 のノードの容量値は、前記第 2 のノードの容量値よりも大きくされている、半導体記憶装置。

20

**【請求項 8】**

選択メモリセルに接続される第 1 のノードと参照セルに接続される第 2 のノードとを有し、前記第 1 および第 2 のノードを流れる電流に従って前記選択メモリセルのデータを検出するセンス增幅回路、および

前記第 1 および第 2 のノードにそれぞれ結合されかつ個々に活性化され、活性化時、定電流を駆動する第 1 および第 2 の定電流源を備える、半導体記憶装置。

**【請求項 9】**

動作モード指示信号に従って前記第 1 および第 2 の定電流源を選択的に活性化する活性制御回路をさらに備える、請求項 8 記載の半導体記憶装置。

**【請求項 10】**

前記第 1 および第 2 の定電流源は、各々、活性化時、定電流発生回路の電流 / 電圧変換トランジスタとカレントミラー回路を構成するトランジスタを備える、請求項 8 記載の半導体記憶装置。

30

**【請求項 11】**

少なくとも 1 行に整列して配置され、各々がゲートを有しかつそのゲート電圧 / 電流特性が温度依存性を有するトランジスタを含み、該トランジスタのしきい値電圧に応じてデータを記憶するメモリセル、および

前記メモリセルのトランジスタのゲート電圧 - 駆動電流特性の温度依存性を補償する温度依存性を有するワード線駆動電圧を発生する電圧発生回路を備え、前記ワード線駆動電圧は、その温度依存性が制御信号に従って正および負の方向に変更可能であり、

40

前記行に整列して配置されるメモリセルに対応して配置され、前記メモリセルトランジスタのゲートが接続される少なくとも 1 本のワード線、および

前記 1 本のワード線の選択時、前記電圧発生回路の発生するワード線駆動電圧を前記 1 本のワード線に伝達するワード線選択回路を備える、半導体記憶装置。

**【請求項 12】**

前記電圧発生回路は、

活性化時、電荷ポンプ動作により前記ワード線駆動電圧を生成する電圧生成回路、

前記電圧生成回路の生成するワード線駆動電圧を分圧する分圧回路、

温度依存性を有する基準電圧を発生する基準電圧発生回路、

前記基準電圧発生回路の生成する基準電圧の温度依存性を調整しかつ前記分圧回路の分

50

圧比を調整する制御部と、

前記基準電圧発生回路からの基準電圧と前記分圧回路からの分圧電圧との比較に基づいて前記電圧生成回路を選択的に活性化するレベル判定回路とを備える、請求項11記載の半導体記憶装置。

#### 【請求項13】

前記基準電圧発生回路は、

定電流発生回路と、

ダイオード接続されるバイポーラトランジスタと、

前記定電流発生回路からの定電流を前記バイポーラトランジスタへ供給するその抵抗値が変更可能な抵抗素子とを備え、前記基準電圧は前記定電流発生回路と前記抵抗素子との間のノードに生成される、請求項12記載の半導体記憶装置。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この発明は、半導体記憶装置に関し、特に、メモリセルを流れる電流を参照セルを流れる電流と比較してその比較結果に基づいてメモリセルの記憶データを読出す半導体記憶装置に関する。より特定的には、この発明は、不揮発性半導体記憶装置のメモリセルの記憶データを正確に読出すための構成に関する。

##### 【背景技術】

##### 【0002】

消費電力および発熱量を低減するために、半導体集積回路装置においては、電源電圧が低くされてきている。半導体記憶装置においても、同様、電源電圧が低くされてきている。このような半導体記憶装置の1つの不揮発性半導体記憶装置においては、メモリセルデータの読出しあは、電流センス方式のセンスアンプ（電流センスアンプ）を用いて行われる。電流センスアンプは、定電流を供給するカレントミラー段を含み、選択メモリセルの駆動電流と参照セルの駆動電流とを比較し、その比較結果に基づいた内部データを出力し、これにより選択メモリセルのデータを読出す。

20

##### 【0003】

このような電流センスアンプにおいては、正確にセンス動作を行なうためには、カレントミラー段を構成するトランジスタは、飽和領域で動作させる必要がある。飽和領域においては、MOSトランジスタ（絶縁ゲート型電界効果トランジスタ）の場合、次式を満たすことが要求される。

30

##### 【0004】

$$V_{ds} = V_{gs} - V_{th}$$

ここで、 $V_{ds}$ はドレイン-ソース間電圧を示し、 $V_{gs}$ はゲート-ソース間電圧を示し、 $V_{th}$ はしきい値電圧を示す。

##### 【0005】

PチャネルMOSトランジスタでセンスアンプのカレントミラーを構成する場合、ソースに電源電圧が供給され、ドレインに比較結果に応じた電圧が生成される。したがって、上式から明らかなように、電源電圧が低くなる場合、MOSトランジスタを飽和領域で動作させるのが極めて困難となり、高精度でセンス動作を行なうのは困難となる。

40

##### 【0006】

PチャネルMOSトランジスタは、通常、ゲート電極がN型不純物を導入したポリシリコンで構成され、PチャネルMOSトランジスタの場合、ゲート電極と半導体基板の仕事関数の差により、しきい値電圧の絶対値が大きくなる（N型ゲート電極により電子が半導体基板表面に引き寄せられ、チャネル形成時、反転層ができにくくなる）。このPチャネルMOSトランジスタのしきい値電圧の絶対値を小さくするため、表面に、P型不純物を導入する。このため、半導体基板表面よりも内部にチャネルが形成される。このようなMOSトランジスタが、埋込チャネルMOSトランジスタと呼ばれる。

##### 【0007】

50

この埋込チャネルは、ソースおよびドレイン領域と同じ導電型の不純物が添加される領域である。このような埋込チャネル型MOSトランジスタにおいては、基板内部をキャリア（正孔）が通過するため、移動度が大きくなり、しきい値電圧の絶対値低下時のサブスレッショルド特性が劣化し、リーク電流が増加するという問題が生じる。このため、低しきい値化が困難であり、PチャネルMOSトランジスタは、導通状態とするためには、ある程度のゲート-ソース間電圧は必要とされ、低電圧化が、NチャネルMOSトランジスタに比べて困難である。したがって、このような電流センスアンプにおけるカレントミラ一段においてPチャネルMOSトランジスタを利用する場合、低電源電圧下では、正確なセンス動作を高精度で行なうことことができなくなるという問題が生じる。

## 【0008】

10

このセンス動作を高精度で行なうことを目的とする構成が、特許文献1（特開平4-216397号公報）に示されている。この特許文献1に示される構成においては、差動増幅器とオフセット手段とでセンス回路を構成し、メモリセルアレイのノーマルビット線と参照セルが接続される参照ビット線とに異なる大きさの電流を供給する。この特許文献1は、このオフセット電流を流すことにより、電流オフセット型センスアンプの静的特性および動的特性を、改良することを図る。

## 【0009】

20

また、このような半導体記憶装置においては、動作温度に従ってメモリセルを流れる電流が異なる。メモリセルデータを正確に読出すためには、このような温度特性を補償して、メモリセル電流を検出してデータを読出す必要がある。

## 【0010】

30

このような動作温度の相違に基づくメモリセル電流の温度依存性を補償するための構成が、特許文献2（特表2003-530656号パンフレット）に示されている。この特許文献2においては、プログラム（書き込みおよび消去）動作時においてビット線に所定値以上のリーク電流が生じていないかを検証する自動プログラム妨害消去検証（APDEV）動作時のワード線電圧を温度補償する構成が示されている。

## 【0011】

また、メモリセル電流の温度依存性を補償することを図る構成が、特許文献3（特開2003-217287号公報）において示されている。この特許文献3においては、メモリセル電流の温度依存性を、ワード線電圧の温度依存性およびビット線の放電時間の温度依存性とを制御して相殺し、温度依存性の少ないメモリセルのしきい値電圧分布を得ることを図る。

## 【0012】

また、同様、メモリセルのしきい値電圧分布の温度依存性を低減することを図る構成が、特許文献4（特開2001-35177号公報）に示されている。この特許文献4に示される構成においては、温度依存性を有する電流を発生する電流源と温度に依存しない一定の電流を生成する電流源とを用い、これらの電流源を選択的に用いて、温度特性を正および負両方ともに調整することを図っている。

## 【特許文献1】特開平4-216397号公報

40

【特許文献2】特表2003-530656号パンフレット

【特許文献3】特開2003-217287号公報

【特許文献4】特開2001-35177号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0013】

特許文献1に示される構成においては、ノーマルメモリセルが接続されるノーマルビット線と参照セルが接続される参照ビット線に対し、供給する電流をアンバランスとすることにより、負荷アンバランス型センス回路と同様の特性を実現し、また、この負荷アンバランス型センス回路の電源電圧に対する制限をなくすことを図る。

## 【0014】

50

しかしながら、この特許文献 1 に示される構成においては、常時、ノーマルビット線および参照ビット線にアンバランスな電流を供給しており、選択的に、ノーマルビット線のみまたは参照ビット線のみに負荷電流を供給して、メモリセル特性の検証を行なうことはできない。

#### 【 0 0 1 5 】

特許文献 2 に示される構成においては、P 型抵抗素子およびN 型抵抗素子の抵抗値の温度依存性の異なることを利用して、これらの P 型抵抗素子およびN 型抵抗素子を選択的に組合せて、動作温度に応じて抵抗値の予め定められた傾きを生成して、ワード線印加電圧の温度補償を行なっている。したがって、この特許文献 2 に示される構成においては、温度に応じて、P 型抵抗素子およびN 型抵抗素子の組合せを、適応的に調節する必要があり、その温度制御が困難であるという問題が生じる。10

#### 【 0 0 1 6 】

特許文献 3 に示される構成においても、ワード線電圧に温度依存性を持たせることにより、メモリセル電流の温度依存性を相殺している。しかしながら、この特許文献 3 に示される構成においては、ノーマルメモリセルおよび参照メモリセルの特性の温度依存性が異なる場合については何ら考慮していない。

#### 【 0 0 1 7 】

特許文献 4 に示される構成においても、同様、メモリセル電流の温度依存性を補償するために、ワード線電圧に、メモリセル電流の温度依存性を相殺するような温度依存性を持たせている。しかしながら、この特許文献 4 においても、ノーマルメモリセルと参照メモリセルの駆動電流の温度依存性が異なる場合については、何ら考察していない。20

#### 【 0 0 1 8 】

また、これらの特許文献 1 から 4 においては、内部電源電圧低下時においても、高精度でセンス動作を行なうためのセンスアンプの構成およびセンス動作については考察していない。

#### 【 0 0 1 9 】

それゆえ、この発明の目的は、低電源電圧下においても、正確にメモリセルデータを読出すことのできる半導体記憶装置を提供することである。

#### 【 0 0 2 0 】

この発明の他の目的は、多値データを高精度で読出すことのできる電流センスアンプを備える半導体記憶装置を提供することである。30

#### 【 0 0 2 1 】

この発明のさらに他の目的は、動作環境の影響を受けることなく正確にメモリセルデータの読み出を行うことのできる不揮発性半導体記憶装置を提供することである。

#### 【課題を解決するための手段】

#### 【 0 0 2 2 】

この発明の第 1 の観点に係る半導体記憶装置は、複数のメモリセルと、複数のメモリセルの選択メモリセルのデータを検出するセンス增幅回路を備える。このセンス增幅回路は、内部電源電圧よりも高い電圧を受ける昇圧電源ノードと、この昇圧電源ノードに動作時結合され、メモリセルを流れる電流に応じてメモリセルの記憶データを読み出す読み出部と、この内部電源電圧を受けるノードに結合され、プリチャージ指示信号に応答してメモリセルへ内部電源ノードからの電流を供給して選択メモリセルが接続されるデータ線を所定電位にプリチャージするプリチャージ段とを含む。40

#### 【 0 0 2 3 】

この発明の第 2 の観点に係る半導体記憶装置は、各々がゲートを有し、そのしきい値電圧によりデータを記憶するトランジスタで構成される複数のメモリセルと、これらのメモリセルと同一構造を有する参照セルと、複数のメモリセルの選択メモリセルの駆動電流と参照セルの駆動電流をセンスして選択メモリセルのデータを読み出すセンス增幅回路と、参照セルおよび選択メモリセルのゲートに印加する電圧を生成するゲート電圧発生回路を備える。このゲート電圧発生回路は、選択メモリセルの通常データ読み出モード時には参照セ50

ルおよび選択メモリセルのゲートに対する電圧として同一レベルの電圧を生成し、選択メモリセルの書込または消去の検証モード時には、メモリセルの駆動電流分布範囲の上下端の位置のメモリセルについては、通常モード時と異なるレベルの電圧を選択メモリセルのゲート電圧として生成する。

【0024】

この発明の第3の観点に係る半導体記憶装置は、複数のメモリセルと、参照メモリセルと、複数のメモリセルの選択メモリセルに接続される第1のノードと参照セルに接続される第2のノードとを有し、これらの第1および第2のノードを流れる電流に従って選択メモリセルのデータを読出すセンス増幅器を備える。この第1のノードの容量値は、第2のノードの容量値よりも大きくされる。

10

【0025】

この発明の第4の観点に係る半導体記憶装置は、選択メモリセルに接続される第1のノードと参照セルに接続される第2のノードとを有し、第1および第2のノードを流れる電流に従って選択メモリセルのデータを検出すセンス増幅回路と、これら第1および第2のノードにそれぞれ結合され、活性化時、定電流をこれらの第1および第2のノードから駆動する第1および第2の定電流源を備える。これらの第1および第2の定電流源は個別に活性化することができる。

【0026】

この発明の第5の観点に係る半導体記憶装置は、少なくとも1行に整列して配置され、各々がゲートを有しあつそのゲート電圧／駆動電流特性が温度依存性を有するトランジスタを含み、このトランジスタのしきい値電圧に応じてデータを記憶するメモリセルと、メモリセルのトランジスタのゲート電圧／駆動電流特性の温度依存性を補償する温度依存性を有するワード線駆動電圧を発生する電圧発生回路と、行に整列して配置されるメモリセルに対応して配置され、メモリセルトランジスタのゲートが接続される少なくとも1本のワード線と、この1本のワード線の選択時、電圧発生回路の発生するワード線駆動電圧を1本のワード線に伝達するワード線選択回路を備える。この電圧発生回路からのワード線駆動電圧は、制御信号に従って、正および負の温度依存性のいずれをも有することが可能である。

20

【発明の効果】

【0027】

第1の観点の半導体記憶装置においては、センス増幅回路の電源電圧として、内部電源電圧よりも高い電圧を供給している。したがって、内部電源電圧が低電圧化される場合においても、その読み出部を構成するトランジスタを飽和領域で動作させることができ、安定に、センス動作を行なうことができる。

30

【0028】

第2の観点に係る半導体記憶装置においては、メモリセルの駆動電流分布範囲の上下端の位置のメモリセルの検証時には、そのゲート電圧を通常動作モード時と異なる電圧レベルに設定しており、メモリセルのしきい値電圧分布を高精度に制御することができ、多値データ記憶時においても、正確に、データの読み出を行なうことができる。

40

【0029】

この発明の第3の観点に係る半導体記憶装置においては、参照セルが接続する第2のノードの容量値が、ノーマルメモリセルが接続される第1のノードよりも小さくされており、この容量値のアンバランスにより、センスノードの電圧を高速で所定電圧レベルに収束させることができ、アクセス時間を短縮することができる。

【0030】

この発明の第4の観点に係る半導体記憶装置においては、参照セルおよびノーマルセルに結合されるセンスノードそれぞれに、活性化時定電流を駆動する定電流源を接続しており、メモリセルおよび参照セルをそれぞれ独立に、電流特性を検証することができる。

【0031】

この発明の第5の観点に係る半導体記憶装置においては、メモリセルのトランジスタの

50

ゲート電圧とその駆動電流との間の特性の温度依存性を補償する温度依存性を有するワード線駆動電圧を発生し、このワード線駆動電圧は、制御信号により正および負の温度依存性を有することが可能である。したがって、最適な電圧レベルに、動作温度に応じてワード線駆動電圧を設定することができ、メモリセルトランジスタを流れる電流の温度依存性を補償することができる。これにより、参照メモリセルとメモリセルのしきい値電圧の温度依存性が異なる場合においても、正確に、メモリセル電流を、温度依存性を持たせることなく生成することができ、正確なセンス動作が保証される。

#### 【発明を実施するための最良の形態】

##### 【0032】

###### 〔実施の形態1〕

10

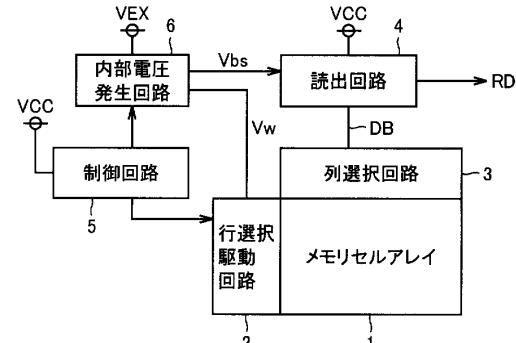

図1は、この発明の実施の形態1に従う不揮発性半導体記憶装置の要部の構成を概略的に示す図である。図1において、この発明の実施の形態1に従う不揮発性半導体記憶装置は、行列状に配列される不揮発性メモリセルを有するメモリセルアレイ1を含む。メモリセルアレイ1においては、メモリセル行に対応してワード線が配置され、また、メモリセル列に対応してビット線が配置される。しかしながら、図1においては、図面を簡略化するために、これらのワード線およびビット線は、示していない。

##### 【0033】

20

不揮発性半導体記憶装置は、さらに、メモリセルアレイ1のアドレス指定された行を選択しつつ選択行のワード線を所定の電圧レベルへ駆動する行選択駆動回路2と、メモリセルアレイ1の列(ビット線)を選択する列選択回路3と、データ読出時、列選択回路3により選択された列上のメモリセルのデータを読出す読出回路4と、この不揮発性半導体記憶装置の各種の内部動作を制御する制御回路5と、制御回路5の制御の下に、データの書込／消去および読出に必要な内部電圧Vwを生成しつつ読出回路4に対する昇圧電圧Vbを供給する内部電圧発生回路6を含む。

##### 【0034】

30

制御回路5は、内部電源電圧VCCを動作電源電圧として受け、また、内部電圧発生回路6は、外部からの電源電圧VEXを動作電源電圧として受ける。この外部電源電圧VEXは、内部電源電圧VCCと同一電圧レベルであってもよく、また、異なる電圧レベルであってもよい。読出回路4へは、また内部電源電圧VCCが与えられる。

##### 【0035】

メモリセルアレイ1においては、データを記憶するノーマルメモリセル(以下、単にメモリセルと称す)と選択メモリセルのデータ読出時の参照電流を供給する参照セルが配置される。読出回路4は、データ読出時、選択メモリセルと参照セルの駆動電流を比較し、その比較結果に基づいて読出データRDを生成する。

##### 【0036】

列選択回路3は、列アドレス信号をデコードする列アドレスデコーダと、列アドレスデコーダからの列選択信号(およびロック選択信号)とにしたがって選択列のビット線を読出回路4に接続する列選択ゲートを含む。

##### 【0037】

40

制御回路5は、たとえばコマンドデコーダで構成され、外部から与えられる動作モード指示に従って各種動作制御信号を生成する。図1においては、この制御回路5は内部電圧発生回路6および行選択駆動回路2の動作を制御するように示すが、この制御回路5は、また読出回路4におけるデータ読出動作をも制御し、また、列選択回路3に含まれる列アドレスデコード回路の動作および印加電圧レベルをも制御する。

##### 【0038】

50

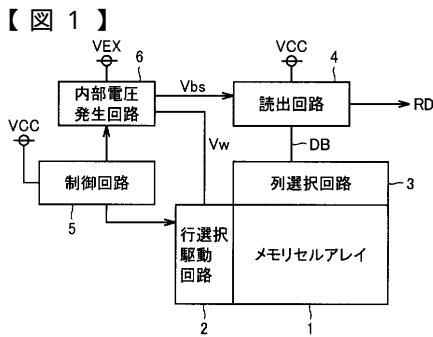

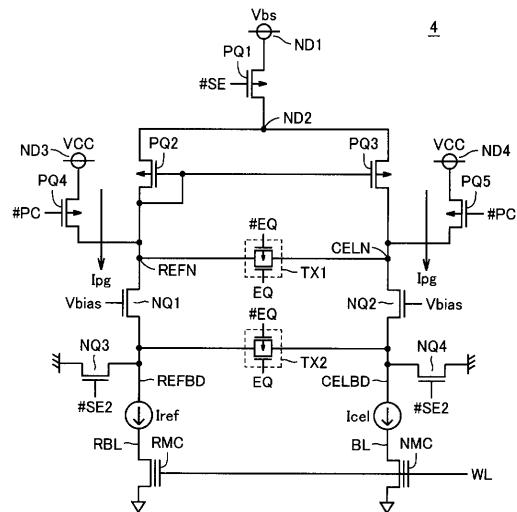

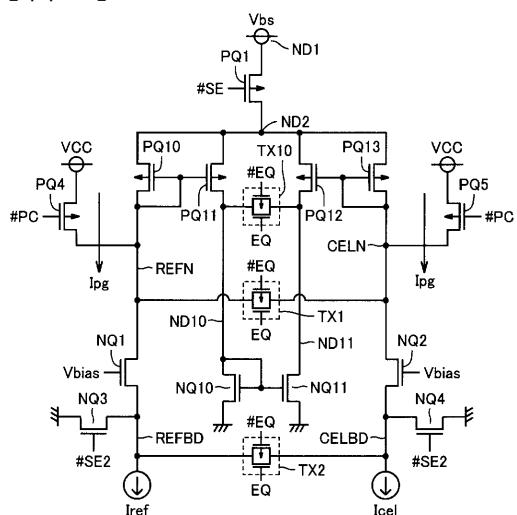

図2は、図1に示す読出回路4に含まれるセンスアンプ(センス増幅回路)の構成の一例を示す図である。図2において、センスアンプは、昇圧電源ノードND1と内部ノードND2の間に接続されかつそのゲートにセンス活性化信号SEを受けるPチャネルMOSトランジスタPQ1と、内部ノードND2と内部ノードREFNとの間に接続されかつそのゲートが内部ノードREFNに接続されるPチャネルMOSトランジスタPQ2と、

内部ノードN D 2と内部ノードC E L Nの間に接続されかつそのゲートが内部ノードR E F Nに接続されるPチャネルMOSトランジスタP Q 3と、プリチャージ指示信号P Cの活性化時導通し、内部ノードR E F Nへ内部電源ノードN D 3からプリチャージ電流I p gを供給するPチャネルMOSトランジスタP Q 4と、プリチャージ指示信号P Cの活性化時導通し、内部電源ノードN D 4から内部ノードC E L Nへプリチャージ電流I p gを供給するPチャネルMOSトランジスタP Q 5を含む。

#### 【0039】

電源ノードN D 3およびN D 4へは、内部電源電圧V C Cが供給される。一方、昇圧電源ノードN D 1へは、内部電源電圧V C Cよりも高い昇圧電圧V b sが供給される。プリチャージ電力I p gを、内部電源電圧V C Cから生成する。昇圧電圧V b sは、このセンスアンプのセンス動作においてのみ利用される。これにより、昇圧電圧V b sを発生する回路の消費電流を低減し、電流消費の増大を抑制する。10

#### 【0040】

これらのPチャネルMOSトランジスタP Q 1 - P Q 5は、その構成は後に説明するが、通常の埋込チャネル方式のPチャネルMOSトランジスタで構成される。

#### 【0041】

センスアンプは、さらに、内部ノードR E F Nと内部読出データ線R E F B Dの間に接続されかつそのゲートに一定のバイアス電圧V b i a sを受けるNチャネルMOSトランジスタN Q 1と、内部ノードC E L Nと内部読出データ線(センスノード)C E L B Dの間に接続されかつそのゲートにバイアス電圧V b i a sを受けるNチャネルMOSトランジスタN Q 2と、センスアンプ活性化信号S E 2の非活性化時導通し、参照データ線R E F B Dを接地電圧レベルに維持するNチャネルMOSトランジスタN Q 3と、センスアンプ活性化信号S E 2の非活性化時導通し、内部読出データ線C E L B Dを接地電圧レベルに維持するNチャネルMOSトランジスタN Q 4と、相補イコライズ指示信号E QおよびE Qの活性化時導通し、内部ノードR E F NおよびC E L Nを電気的に短絡するC MOSトランスマッショングートT X 1と、相補イコライズ指示信号E QおよびE Qの活性化時導通し、参照データ線R E F B Dおよび内部読出データ線C E L B Dを電気的に短絡するC MOSトランスマッショングートT X 2を含む。20

#### 【0042】

参照データ線R E F B Dは、データ読出時、参照セルR M Cに参照ビット線R B Lを介して接続され、また、内部読出データ線C E L B Dは、データ読出時、ビット線B Lを介してメモリセル(ノーマルメモリセル)N M Cに接続される。これらの参照セルR M CおよびメモリセルN M Cのゲートは、共通にワード線W Lに接続される。なお、図2においては、このメモリセルおよび参照セルを選択するためのコラム選択ゲート(列選択回路3内に含まれる)は示していない。30

#### 【0043】

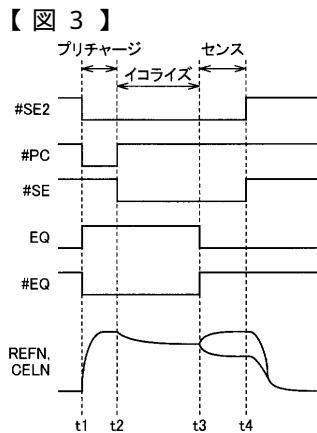

図3は、図2に示すセンスアンプの動作を示すタイミング図である。以下、図2に示すセンスアンプの動作を、図3に示すタイミング図を参照して説明する。

#### 【0044】

時刻t 1以前においては、センスアンプは非活性状態にあり、センスアンプ活性化信号S E 2、プリチャージ指示信号P C、センス活性化信号S Eおよびイコライズ指示信号E QはHレベルであり、イコライズ指示信号E QがLレベルである。この状態においては、PチャネルMOSトランジスタP Q 1が非導通状態にあり、内部ノードN D 2はフローティング状態にある。また、プリチャージ用のPチャネルMOSトランジスタP Q 4およびP Q 5もオフ状態にある。NチャネルMOSトランジスタN Q 3およびN Q 4がオン状態にあり、参照データ線R E F B Dおよび内部読出データ線C E L B Dは接地電圧レベルに維持される。またC MOSトランスマッショングートT X 1およびT X 2がオン状態であり、内部ノードR E F NおよびC E L Nが電気的に短絡され、また、参照データ線R E F B Dおよび内部読出データ線C E L B Dが電気的に短絡されて同一電位に維持される。40

10

20

30

40

50

## 【0045】

時刻  $t_1$  において、内部データの読み出動作が開始される。この時刻  $t_1$  においてイコライズ指示信号  $E_Q$  が H レベル、補のイコライズ指示信号  $E_Q$  が L レベルとなり、CMOS トランジションゲート  $TX_1$  および  $TX_2$  がオフ状態となり、内部ノードのイコライズが完了する。また、センスアンプ活性化信号  $SE_2$  が L レベルとなり、N チャネル MOS トランジスタ  $NQ_3$  および  $NQ_4$  がオフ状態となり、データ線  $REFBD$  および  $CELBD$  の接地電位レベルへのプリチャージが完了する。

## 【0046】

さらに、この時刻  $t_1$  において、プリチャージ指示信号  $PC$  が L レベルとなり、P チャネル MOS トランジスタ  $PQ_4$  および  $PQ_5$  がオン状態となり、プリチャージ電流  $I_{pg}$  が、それぞれ参照データ線  $REFBD$  および 内部読み出データ線  $CELBD$  へ供給される。これらの参照データ線  $REFBD$  および 内部読み出データ線  $CELBD$  は、それぞれ、図示しない列選択ゲートを介して参照セル  $RMC$  および 選択メモリセル  $NMC$  に結合され、これらのプリチャージ電流  $I_{pg}$  が、参照ビット線  $RBL$  および ビット線  $BBL$  に供給される。

10

## 【0047】

バイアス電圧  $Vbias$  をゲートに受ける N チャネル MOS トランジスタ  $NQ_1$  および  $NQ_2$  が、ソースフォロアモードで動作し、この参照データ線  $REFBD$  および 内部読み出データ線  $CELBD$  の電圧レベルが、一定電圧レベル ( $Vbias - VTHN$ :  $VTHN$  は、N チャネル MOS トランジスタのしきい値電圧) に維持される。一方、内部ノード  $REFN$  および  $CELN$  は、このプリチャージ電流  $I_{pg}$  により、内部電源電圧  $VCC$  レベルにまで充電される。これらの MOS トランジスタ  $NQ_1$  および  $NQ_2$  により、内部ノード  $REFN$  および  $CELN$  は、容量的にデータ線  $REFBD$  および  $CELBD$  から分離され、データ線  $REFBD$  および  $CELBD$  の電位レベルの変動の影響を受けない。

20

## 【0048】

時刻  $t_2$  において、プリチャージ指示信号  $PC$  が H レベルとなり、MOS トランジスタ  $PQ_4$  および  $PQ_5$  がオフ状態となり、内部ノード  $REFN$  および  $CELN$  のプリチャージならびに参照ビット線  $RBL$  および ビット線  $BBL$  の所定電位へのプリチャージが完了する。

30

## 【0049】

また、時刻  $t_2$  において、センス活性化信号  $SE$  が L レベルとなり、P チャネル MOS トランジスタ  $PQ_1$  がオン状態となり、センスアンプが活性化され、P チャネル MOS トランジスタ  $PQ_2$  および  $PQ_3$  が、昇圧ノード  $ND_1$  から電流を供給する。MOS トランジスタ  $PQ_2$  および  $PQ_3$  は、MOS トランジスタ  $PQ_2$  をマスターとするカレントミラーモードを構成し、同じ大きさの電流を供給する。

40

## 【0050】

このとき、まだイコライズ指示信号  $E_Q$  および  $E_Q$  はそれぞれ H レベルおよび L レベルであり、CMOS トランジションゲート  $TX_1$  および  $TX_2$  がオン状態である。したがって、内部ノード  $REFN$  および  $CELN$  が、参照セル  $RMC$  および メモリセル  $NMC$  の駆動電流  $I_{ref}$  および  $I_{cel}$  に応じて、同一電圧レベルでそれらの電圧レベルが低下する。

40

## 【0051】

時刻  $t_3$  において、イコライズ指示信号  $E_Q$  および  $E_Q$  がそれぞれ L レベルおよび H レベルとなり、CMOS トランジションゲート  $TX_1$  および  $TX_2$  がオフ状態となる。このときには、内部ノード  $REFN$  および  $CELN$  の電圧レベルは十分低下しており、MOS トランジスタ  $PQ_2$  および  $PQ_3$  は、十分に飽和領域で動作し、そのカレントミラーモードにより、参照セル  $RMC$  に対する参照電流  $I_{ref}$  と同じ大きさの電流が、内部ノード  $CELN$  へ供給される。この参照電流  $I_{ref}$  とメモリセル  $NMC$  の駆動電流  $I_{cel}$  の差に応じて、内部ノード  $CELN$  および  $REFN$  の間に電位差が高速で生じる。

50

## 【0052】

時刻  $t_4$ において、センス活性化信号  $S_E$  およびセンスアンプ活性化信号  $S_E 2$  がともに H レベルとなり、P チャネルMOSトランジスタ  $PQ_1$  がオフ状態、MOSトランジスタ  $NQ_3$  および  $NQ_4$  がオン状態となり、センス動作が完了し、データ線  $REFBD$  および  $CELBD$  が再び、接地電圧レベルにプリチャージされる。このデータ線  $REFBD$  および  $CELBD$  の接地電圧レベルへの駆動により、MOSトランジスタ  $NQ_1$  および  $NQ_2$  を介して、内部ノード  $REFN$  および  $CELN$  も、接地電圧レベルに放電されて、これらの内部ノード  $REFN$  および  $CELN$  も接地電圧レベルにプリチャージされる。

#### 【0053】

C MOSトランスマッシュゲート  $TX_1$  および  $TX_2$  を用いて、センス動作時、内部ノード  $REFN$  および  $CELN$  をイコライズしつつ参照電流  $I_{ref}$  およびセル電流  $I_{cel}$  を供給することにより、メモリセル NMC の駆動電流のカレントミラー段を構成する P チャネルMOSトランジスタ  $PQ_2$  および  $PQ_3$  が十分飽和領域で動作させることができ、最も感度の高い領域で高速でセンス動作を行なうことができる。

#### 【0054】

内部ノード  $REFN$  および  $CELN$  の電位変化は、MOSトランジスタ  $NQ_1$  および  $NQ_2$  の機能により、内部データ線  $REFBD$  および  $CELBD$  へは伝達されない。すなわち、MOSトランジスタ  $NQ_1$  および  $NQ_2$  により、内部ノード  $REFN$  および  $CELN$  は、データ線  $REFBD$  および  $CELBD$  と容量的に分離されており、セル電流  $I_{cel}$  および参照電流  $I_{ref}$  の大きさに応じて、内部ノード  $CELN$  および  $REFN$  に高速で電位変化を生じさせることができる。

#### 【0055】

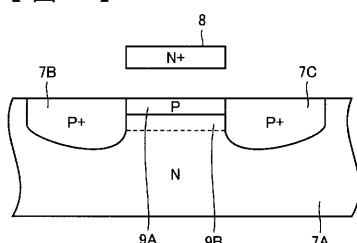

図 4 は、図 2 に示されるセンスアンプに含まれる P チャネルMOSトランジスタの断面構造を概略的に示す図である。図 4 において、P チャネルMOSトランジスタは、N型半導体基板領域（たとえばウェルまたは基板） $7A$  と、この半導体基板領域  $7A$  表面に間をおいて形成される P 型不純物領域  $7B$  および  $7C$  と、これらの不純物領域  $7B$  および  $7C$  の間の基板領域表面に形成される P 型不純物ドープ層  $9A$  と、この不純物ドープ層  $9A$  上に図示しないゲート絶縁膜を介して形成されるゲート電極  $8$  を含む。このゲート電極  $8$  は、通常、N型不純物をドープした多結晶シリコンで構成される。

#### 【0056】

この図 4 に示す P チャネルMOSトランジスタにおいては、ゲート電極  $8$  が、N型半導体であり、この半導体基板領域  $7A$  表面の電子が、ゲート電極層  $8$  方向へ移動する。この半導体基板領域  $10$  表面の電子の影響を相殺するために、P 型不純物ドープ層  $9A$  を設ける。この場合、チャネル領域  $9B$  は、この P 型不純物ドープ層  $9A$  下部に形成され、埋込チャネルを形成する。この埋込チャネル  $9A$  においては、ゲート電極  $8$  にソース領域（不純物領域  $7B$  または  $7C$ ）の電圧レベルよりも低い電圧レベルを印加することにより、電子が半導体基板領域  $7A$  表面から下部へ移動し、空乏層が広がり、埋込チャネル領域  $9B$  に、反転層が形成され、この P チャネルMOSトランジスタがオン状態となる。

#### 【0057】

この図 4 に示す埋込チャネル方式の P チャネルMOSトランジスタにおいては、P 型不純物ドープ層  $9A$  が設けられており、このため、オフリーク電流が流れるため、しきい値電圧の絶対値を十分に小さくすることができない。また、しきい値電圧の絶対値が N MOSトランジスタと比べて大きく、また、多数キャリアも質量の大きいホールであり、その電流駆動力も N チャネルMOSトランジスタと比べて小さい。したがって、P チャネルMOSトランジスタを利用する場合、一般的には、チャネル幅を広くして、電流駆動力を大きくする対策がとられる。しかしながら、この昇圧電圧  $V_{bs}$  を用いることにより、内部電源電圧  $V_{CC}$  が低い場合においても、センスアンプ動作時、このカレントミラー段を構成する P チャネルMOSトランジスタ  $PQ_2$  および  $PQ_3$  および  $PQ_1$  を飽和領域で動作させることができまた、電流駆動力も大きくすることができます。これにより、安定に、センスアンプにおいてカレントミラー段の P チャネルMOSトランジスタが、ゲート電圧に従って自乗特性で規定される大きさの電流を駆動することができ、正確なセンス動作を行

10

20

30

40

50

なうことができる。

【0058】

したがって、NチャネルMOSトランジスタに対して、N型不純物をドープしたポリシリコンをゲート電極として利用し、一方、PチャネルMOSトランジスタに対しては、P型不純物をドープした多結晶シリコンをゲート電極として利用するデュアルゲートプロセスを用いる必要がなく、製造工程が簡略化される。

【0059】

[変更例]

図5は、この発明の実施の形態1に従うセンスアンプの変更例の構成を示す図である。

図5において、センスアンプは、内部ノードND1と内部ノードREFNの間に接続され

かつそのゲートが内部ノードREFNに接続されるPチャネルMOSトランジスタPQ1

0と、内部ノードND1およびND10の間に接続されかつそのゲートが内部ノードREFNに接続されるPチャネルMOSトランジスタPQ11と、内部ノードND1と内部ノードND11の間に接続されかつそのゲートが内部ノードCELNに接続されるPチャネルMOSトランジスタPQ12と、内部ノードND1と内部ノードCELNの間に接続され

かつそのゲートが内部ノードCELNに接続されるPチャネルMOSトランジスタPQ13と、相補イコライズ指示信号EQおよびEQに従って、内部ノードND10およびND11を電気的に短絡するCMOSトランスマッシュゲートTX10と、内部ノードと接地ノードの間に接続されかつそのゲートが内部ノードND10に接続されるNチャネルMOSトランジスタNQ10と、内部ノードND11と接地ノードの間に接続されかつそのゲートが内部ノードND10に接続されるNチャネルMOSトランジスタNQ11を含む。

10 20 20

【0060】

この図5に示すセンスアンプの他の構成は、図2に示すセンスアンプの構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

【0061】

PチャネルMOSトランジスタPQ4、PQ5およびPQ10-PQ13は、すべて埋込チャネル方式のPチャネルMOSトランジスタで構成される。PチャネルMOSトランジスタPQ10およびPQ11がカレントミラー段を構成し、またNチャネルMOSトランジスタNQ10およびNQ11がカレントミラー段を構成し、またさらに、PチャネルMOSトランジスタPQ12およびPQ13が、カレントミラー段を構成する。

30

【0062】

図5に示すセンスアンプの動作は、図3に示すタイミング図により示される。内部ノードREFNおよびCELNを同一電位に維持した状態で、参照電流Irefおよびセル電流Icelをセンス動作時流す。MOSトランジスタPQ10およびPQ11により参照電流Irefと同じ大きさの電流がノードND10に供給され、また、MOSトランジスタNQ10およびNQ11により、同じ大きさの電流が、ノードND10およびND11により駆動される。

【0063】

MOSトランジスタPQ12およびPQ13が、カレントミラー段を構成し、セル電流Icelと同じ大きさの電流を、内部ノードND11へ供給する。したがって、イコライズ完了後のセンス動作時、内部ノードND10およびND11には、これらの参照電流Irefおよびセル電流Icelの大きさに応じた電位差が生じる。したがって、内部ノードND11またはND10の電位を内部読出データとして出力することにより、高速で、メモリセルデータを読出すことができる。

40

【0064】

この図5に示すセンスアンプの構成の場合、内部ノードND10およびND11に、参照電流Irefおよびセル電流Icelの電位差が生じる。したがって、メモリセルデータ読出時、内部ノードREFNおよびCELNの容量の影響を抑制することができ、高速で、かつ高精度でメモリセルデータを読出すことができる。

10

20

30

40

50

**【 0 0 6 5 】**

この図5に示すセンスアンプにおいても、昇圧電源ノードN D 1に内部電源電圧V C Cよりも高い昇圧電圧V b sを供給することにより、カレントミラー段を構成するM O SトランジスタP Q 1 0 - P Q 1 3およびN Q 1 0 , N Q 1 1を、飽和領域で動作させることができ、高速で、カレントミラー動作により、メモリセルデータの電流センスを行なって内部読出データを生成することができる。

**【 0 0 6 6 】**

以上のように、この発明の実施の形態1に従えば、メモリセルデータを読出すセンスアンプの電源電圧に、内部電源電圧よりも高い昇圧電圧を用いており、カレントミラー段を構成するトランジスタを飽和領域で低電源電圧下においても確実に動作させることができ、高精度でセンス動作を行なうことができる。10

**【 0 0 6 7 】**

また、参照ビット線およびビット線のプリチャージは、内部電源電圧を利用してあり、昇圧電圧は、センス動作のみに利用しており、この昇圧電圧生成のための消費電力を低減することができる。

**【 0 0 6 8 】****[ 実施の形態2 ]**

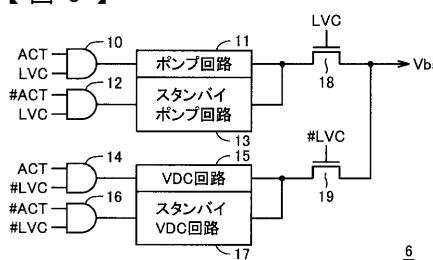

図6は、実施の形態1におけるセンスアンプに供給される昇圧電圧V b sを発生する部分の構成を概略的に示す図である。図6に示す昇圧電圧発生部は、図1に示す内部電圧発生回路6に含まれる。20

**【 0 0 6 9 】**

図6において、昇圧電圧発生部は、動作モード指示信号A C Tと低電圧指示信号L V Cを受けるA N D回路1 0と、A N D回路1 0の出力信号に応答して選択的に活性化され、活性化時、チャージポンプ動作により昇圧電圧を生成するポンプ回路1 1と、補の動作モード指示信号A C Tと低電圧指示信号L V Cを受けるA N D回路1 2と、A N D回路1 2の出力信号に従って活性化され、活性化時、チャージポンプ動作により、昇圧電圧を生成するスタンバイポンプ回路1 3と、動作モード指示信号A C Tと補の低電圧指示信号L V Cを受けるA N D回路1 4と、A N D回路1 4の出力信号の活性化時動作し、外部電源電圧を降圧して降圧電圧を生成する内部降圧回路(V D C回路)1 5と、補の動作モード指示信号A C Tと補の低電圧指示信号L V Cを受けるA N D回路1 6と、A N D回路1 6の出力信号に従って選択的に活性化され、活性化時、外部電源電圧を降圧するスタンバイV D C回路1 7と、低電圧指示信号L V Cの活性化時導通し、ポンプ回路1 1およびスタンバイポンプ回路1 3の出力電圧をセンス昇圧電圧V b sとして伝達するトランスファーゲート1 8と、補の低電圧指示信号L V Cの非活性時導通し、V D C回路1 5およびスタンバイV D C回路1 7の生成電圧をセンス昇圧電圧V b sとして伝達するトランスファーゲート1 9を含む。30

**【 0 0 7 0 】**

図6においては、このトランスファーゲート1 8および1 9が、それぞれNチャネルM O Sトランジスタで構成される場合を一例として示す。これらのトランスファーゲート1 8および1 9は、C M O Sトランスマッシュゲートで構成されてもよく、また、ポルテージフォロアで構成されても良い。40

**【 0 0 7 1 】**

動作モード指示信号A C Tは、この不揮発性半導体記憶装置がアクセスされるときに活性状態となり、動作サイクル期間中Hレベルに維持される。補の動作モード指示信号A C Tは、この不揮発性半導体記憶装置がスタンバイ状態のときに活性化される。

**【 0 0 7 2 】**

定電圧指示信号L V Cは、外部電源電圧(V E X)が1 . 8 Vであり、昇圧電圧V b sが2 . 5 Vのときに活性化される(Hレベルに設定される)。一方、外部電源電圧(V E X)が3 . 3 Vであり、昇圧電圧V b sが、2 . 5 Vの場合に、補の低電圧指示信号L V CがHレベルに設定される。50

## 【0073】

したがって、外部電源電圧が、たとえば1.8Vであり、昇圧電圧V<sub>b</sub>sが、外部電源電圧よりも高い場合には、VDC回路15およびスタンバイVDC回路17は、常時非活性状態に維持される。一方、ポンプ回路11およびスタンバイポンプ回路13が、この不揮発性半導体記憶装置のアクティブサイクルおよびスタンバイサイクルにそれぞれ活性化され、昇圧動作を行なって昇圧電圧V<sub>b</sub>sを生成する。トランスマルチゲート18が導通状態に設定され、これらのポンプ回路11およびスタンバイポンプ回路13の出力電圧が昇圧電圧として伝達される。

## 【0074】

一方、外部電源電圧が、3.3Vであり、昇圧電圧V<sub>b</sub>sよりも高い場合には、低電圧指示信号LVCがLレベルに設定され、補の低電圧指示信号LVCがHレベルに設定される。この状態においては、ポンプ回路11およびスタンバイポンプ回路13は、AND回路10および12の出力信号が常時Lレベルであるため、非活性状態に維持される。また、トランスマルチゲート18も非導通状態に維持される。トランスマルチゲート19が、導通状態となるため、AND回路14および16の出力信号に従って、VDC回路15およびスタンバイVDC回路17が、それぞれ、この不揮発性半導体記憶装置のアクティブサイクルおよびスタンバイサイクル時に活性化されて、降圧動作により、たとえば2.5Vの内部電圧を生成して、センス昇圧電圧V<sub>b</sub>sを生成する。

## 【0075】

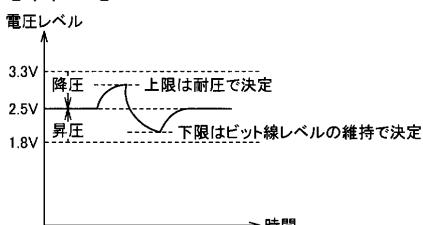

図7は、昇圧電圧V<sub>b</sub>sの電圧変化許容範囲を概略的に示す図である。ポンプ回路11およびスタンバイポンプ回路13を用いて外部電源電圧を昇圧して昇圧電圧V<sub>b</sub>sを生成する場合、ポンプ動作により、この昇圧電圧V<sub>b</sub>sには、リップルが生じる。この場合、昇圧電圧V<sub>b</sub>sの上限値は、この昇圧電圧V<sub>b</sub>sを使用するMOSトランジスタの耐圧(デューティを考慮する)で決定される。一方、この昇圧電圧V<sub>b</sub>sの下限値は、センス動作時にビット線を介してメモリセルのドレインに印加される読出電圧に要求される電圧レベルを必要期間維持する電圧レベルに設定される(この場合、昇圧電圧の下限電圧レベルは、バイアス電圧V<sub>bias</sub>の電圧レベルに応じて決定される)。これらの上下限値を満たすように、ポンプ回路11およびスタンバイポンプ回路13のポンプ数、レベル検知精度、応答速度およびデカップル容量値を設定する。

## 【0076】

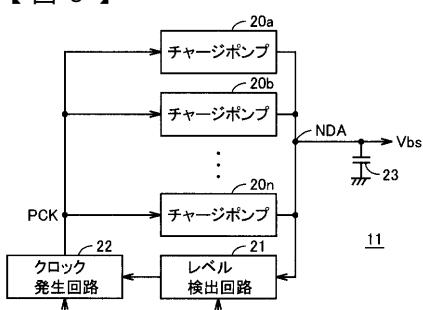

図8は、ポンプ回路11の構成の一例を概略的に示す図である。図8において、ポンプ回路11は、並列に設けられるチャージポンプ20a-20nと、出力ノードNDAからの昇圧電圧V<sub>b</sub>sの電圧レベルを検出するレベル検出回路21と、レベル検出回路21の出力信号に従って選択的に活性化され、活性化時、ポンプクロック信号PCKを生成するクロック発生回路22を含む。出力ノードNDAには、デカップル容量23が接続され、昇圧電圧V<sub>b</sub>sを安定化する。

## 【0077】

レベル検出回路21およびクロック発生回路22へは、図6に示すAND回路10からのイネーブル信号ENPが与えられ、このイネーブル信号ENPの活性化時、レベル検出回路21およびクロック発生回路22が動作する。レベル検出回路21は、このイネーブル信号ENPの活性化時、昇圧電圧V<sub>b</sub>sが所定電圧レベル以上のときに、クロック発生回路22のクロック発生動作を停止させ、所定電圧レベル以下となると、クロック発生回路22にポンプクロック信号PCKを発生させる。

## 【0078】

クロック発生回路22は、たとえばリングオシレータで構成され、レベル検出回路21の出力信号とイネーブル信号ENPがともに活性状態のときに、所定の周期のポンプクロック信号PCKを生成する。

## 【0079】

チャージポンプ20a-20nは、ポンプクロック信号PCKに従って容量素子を利用するチャージポンプ動作を行なって、出力ノードNDAへ電荷を供給して、昇圧電圧V<sub>b</sub>

10

20

30

40

50

s を生成する。

【 0 0 8 0 】

このレベル検出回路 21 の検出精度、および応答速度と、デカップル容量 23 の容量値およびチャージポンプ 20a - 20n の数を、図 7 に示す昇圧電圧の上限値および下限値を満たすように設定する。

【 0 0 8 1 】

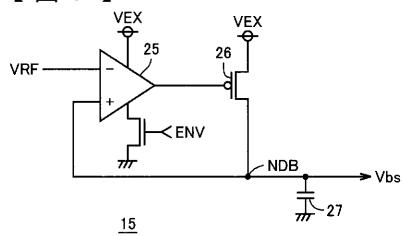

図 9 は、図 6 に示す VDC 回路 15 の構成の一例を概略的に示す図である。図 9 において、VDC 回路 15 は、出力ノード NDB 上の電圧 Vbs と基準電圧 VRF とを比較する比較回路 25 と、比較回路 25 の出力信号に従って外部電源ノードから出力ノード NDB へ電流を供給する電流ドライブトランジスタ 26 と、出力ノード NDB の電圧を安定化するデカップル容量 27 を含む。

10

【 0 0 8 2 】

比較回路 25 は、図 6 に示す AND 回路 14 の出力信号（イネーブル信号）ENV に従って選択的に活性化される。比較回路 25 は、活性化時、出力ノード NDB 上の電圧 Vbs と基準電圧 VRF とを比較し、電圧 Vbs が基準電圧 VRF よりも高いときには、電流ドライブトランジスタ 26 をオフ状態とする。一方、この電圧 Vbs が基準電圧 VRF よりも低いときには、比較回路 25 は、電流ドライブトランジスタ 26 のコンダクタンスを大きくして、外部電源ノードから出力ノード NDB へ電流を供給させて、電圧 Vbs の電圧レベルを上昇させる。

【 0 0 8 3 】

この電流ドライブトランジスタ 26 および出力ノード NDB および比較回路 25 のファイードバックループの応答特性、比較回路 25 の比較精度およびデカップル容量 27 の容量値を適当な値に設定することにより、センス昇圧電源電圧 Vbs のリップルを、図 7 示す上下限値の範囲内に設定することができる。

【 0 0 8 4 】

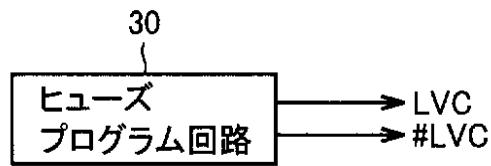

図 10 は、低電圧指示信号 LVC および LVC を発生する部分の構成の一例を示す図である。図 10 においては、ヒューズプログラム回路 30 により、低電圧指示信号 LVC および LVC が生成される。このヒューズプログラム回路 30 は、溶断可能なリンク素子（ヒューズ素子）を含み、このリンク素子を選択的に溶断することにより、これらの低電圧指示信号 LVC および LVC の一方を L レベル、他方を H レベルに設定する。

30

【 0 0 8 5 】

この図 10 に示すヒューズプログラム回路 30 の構成に代えて、特定のボンディングパッドの電圧レベルをボンディングワイヤなどにより設定して、低電圧指示信号 LVC および LVC が生成されてもよい。また、これに代えて、マスク配線を用いて、マスタスライス工程のスライス工程においてこれらの信号 LVC および LVC の電圧レベルが設定されてもよい。

【 0 0 8 6 】

なお、スタンバイポンプ回路 13 およびスタンバイ VDC 回路 17 も、それぞれ、ポンプ回路 11 および VDC 回路 15 と同様の構成を有し、スタンバイ時の電圧 Vds のリーキ電流などに起因する電圧レベルの低下を補償することが要求されるだけである。したがって、これらのスタンバイポンプ回路 13 およびスタンバイ VDC 回路 17 は、電荷供給力は小さく、応じて、生成されるリップルも小さく、応答速度およびレベル検出精度は、アクティブサイクル時に動作するポンプ回路 11 および VDC 回路ほど、厳格には要求されない。

40

【 0 0 8 7 】

以上のように、この発明の実施の形態 2 に従えば、センス昇圧電源電圧を、ポンプ回路または VDC 回路を用いて生成しており、外部電源電圧レベルに応じて、センス昇圧電源電圧を生成する回路を切り替えることにより、最適レベルのセンス昇圧電源電圧を生成することができる。

【 0 0 8 8 】

また、外部電源電圧の電圧レベルが異なる用途に対しても、同一の回路構成で対応することができ、設計効率が改善される。

#### 【0089】

##### [実施の形態3]

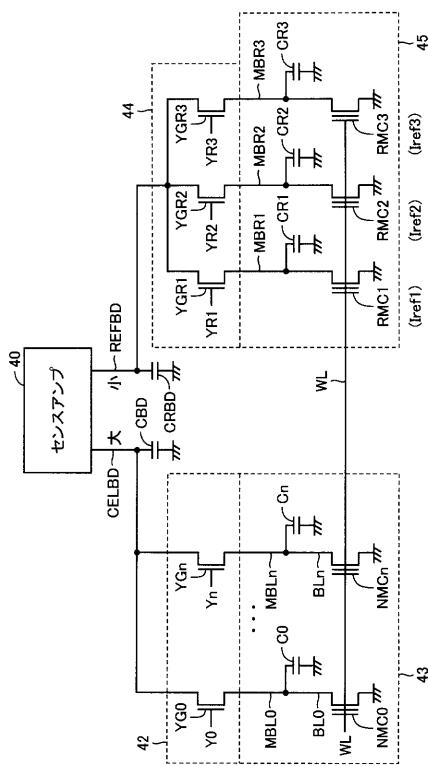

図11は、この発明の実施の形態3に従う不揮発性半導体記憶装置のデータ読出部の構成を概略的に示す図である。図11において、センスアンプ40は、図2または図5に示す構成を一例として有する。このセンスアンプ40に接続される内部読出データ線CELBDおよびおよび参照データ線REFBDには、それぞれ容量CBDおよびCRBDが接続される。

#### 【0090】

内部読出データ線（以下、セルセンスノードと称す）CELBDが、列選択ゲート回路42を介してメモリセルアレイ43のメインビット線MBL0 - MBLnに接続される。この列選択ゲート回路42においては、Y選択信号y0 - ynをそれぞれゲートに受けるY選択ゲートYGO - YGnが、メインビット線MBL0 - MBLnそれぞれに対応して設けられる。メインビット線MBL0 - MBLnは、それぞれ、図示しないブロック選択ゲートを介してビット線BL0 - BLnに接続される。図11においては、このブロック選択ゲートは図面を簡略するために示していない。

#### 【0091】

ビット線BL0 - BLnには、メモリセルNMC0 - NMCnがそれぞれ接続される。1行に整列して配置されるメモリセルNMC0 - NMCnに対してワード線WLが共通に設けられる。メインビット線MBL0 - MBLnそれぞれには、容量C0 - Cnが存在する。この容量C0 - Cnは、配線容量などの寄生容量であってもよく、また対向する電極およびこれらの対向する電極の間の絶縁膜を有する現実の容量素子で構成されてもよい。

#### 【0092】

センスアンプ40に接続される参照データ線（以下、参照センスノードと称す）REFBDには、参照セル選択ゲート回路44を介して参照セルアレイ45に結合される。この参照セルアレイ45は、ワード線WLに結合される参照セルRMC1 - RMC3を含む。これらの参照セルRMC1 - RMC3は、それぞれ、導通時、参照電流Iref1、Iref2、Iref3を駆動する。これらの参照電流Iref1、Iref2、Iref3は、互いに値が異なり、4値データ読出時において読出データに応じて、これらの参照セルRMC1 - RMC3から選択的に1つを導通状態とすることにより、4値データの値を、2分割探索法に従って判定する。

#### 【0093】

この参照セルアレイ45においても、メモリセルアレイ43と同様ブロック選択ゲートを介して参照セルが参照メインビット線MBR1 - MBR3に結合される。これらの参照メインビット線MBR1 - MBR3には、容量CR1 - CR3がそれぞれ存在する。これらの容量CR1 - CR3も、また、配線容量などの寄生容量であってもよく、また現実の容量素子であってもよい。

#### 【0094】

これらの参照メインビット線MBR1 - MBR3それぞれに対応して、セル選択ゲートYGR1 - YGR3が設けられる。これらのセル選択ゲートYGR1 - YGR3のゲートへは、セル選択信号YR1 - YR3がそれぞれ与えられる。これらのセル選択ゲートYGR1 - YGR3は、それぞれ、参照データ線（参照センスノード）REFBDに共通に結合される。

#### 【0095】

メモリセルNMC0 - NMCnは、それぞれ、4値データを格納する。この場合、参照セル選択信号YR1 - YR3のうちの参照セル選択信号YR2が選択状態へ駆動され、まず中間値の参照電流Iref2を供給し、メモリセルの駆動電流Icelと比較される。この第1回目の比較結果に従って、セル選択信号YR1およびYR3の一方が選択状態へ駆動される。したがって、これらの参照セル選択信号YR1 - YR3は、選択メモリセル

10

20

30

40

50

の記憶情報に応じて、その選択シーケンスが決定される。

【0096】

メモリセルのデータ読出時(センス時)においては、ワード線WLの電圧レベルは一定である。参照セルを切換え、参照電流を変更することにより、ワード線電圧を変更する場合に比べて高速で、センスアンプ40によるセンス動作を行なってメモリセルデータを読出す。

【0097】

この図11に示す構成において、センスノードCELBDおよびREFBDの付随する容量は、以下の関係を満たすように設定される。

【0098】

$$\begin{aligned} C_{BD} + C_i &> C_{RBD} + C_{Rj} : \\ i = 0 - n, j &= 1 - 3 \end{aligned}$$

すなわち、セルセンスノードCELBDに接続される容量の値が、参照センスノードREFBDの容量値よりも常に大きくなる。次に、図11に示す不揮発性半導体記憶装置の4値データ読出時の動作について説明する。

【0099】

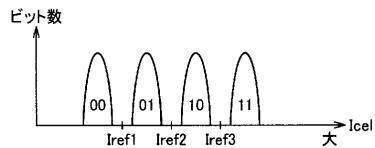

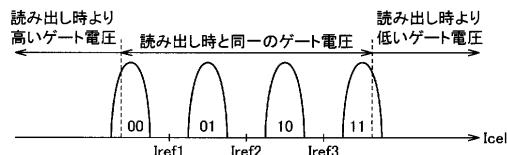

図12は、メモリセルNMC0-NMCnの電流分布を概略的に示す図である。これらのメモリセルNMC0-NMCnは、4値データ(00)、(01)、(10)、および(11)のいずれかを記憶しており、これらの4値データ(00)、(01)、(10)、および(11)の順に、メモリセルの駆動電流(セル電流)が大きくなる(しきい値電圧が小さくなる)。参照電流Iref1は、データ(00)および(01)に対応するセル電流の間の電流値であり、参照電流Iref2は、データ(01)および(10)に対応する電流の間の電流値である。参照電流Iref3は、データ(10)および(11)に対応する電流の間の電流値である。

【0100】

4値データ読出時においては、まず参照セルRMC2を選択し、参照電流Iref2を生成する。選択メモリセルの記憶データに応じて、この参照電流Iref2よりも大きなセル電流または小さなセル電流が駆動され、この大小判定により、上位ビットが“0”または“1”であると判定される。この判定結果に基づいて、参照電流が、参照電流Iref1またはIref3に設定される。これにより、下位ビットが“0”であるか“1”であるかが判定される。これらの2回のセンス動作により、4値データを読出することができる。

【0101】

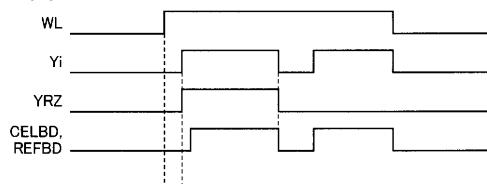

図13は、この図11に示す不揮発性半導体記憶装置のデータ読出時の動作を示すタイミング図である。以下、図13を参照して、図11に示す不揮発性半導体記憶装置のデータ読出動作について説明する。

【0102】

まず、ワード線WLが選択状態へ駆動され、その電圧レベルが所定の電圧レベルのHレベルとなる。

【0103】

次いで、列選択ゲート回路42において、Y選択信号Yiがアドレス信号に従って選択状態へ駆動され、この選択列のメインビット線MBLiが、セルセンスノードCELBDに結合される。同様、また参照セル選択ゲート回路44において、参照セル選択信号YR2がHレベルとなり、参照セルRMC2に接続される参照メインビット線MBR2が、参照センスノードREFBDに結合される。

【0104】

次いで、センスアンプ40が活性化され、先の実施の形態1において説明したように、センスアンプ40内からのプリチャージ電流に従ってセンスノードCELBDおよびREFBDが所定の電圧レベルへ駆動される。これらのセンスノードCELBDおよびREFBDの電圧レベルが一定電圧レベルとなると、参照セルRMC2および選択メモリ

10

20

30

40

50

セルNMCi（図示せず）のドレイン電位が同じとなる。これにより、センスアンプ40において、この選択メモリセルNMCiと参照セルRMC2の駆動電流の差動増幅を行うことができる。

#### 【0105】

参照セル選択信号YR2により、選択メモリセルNMCiの上位ビットの読出が完了すると、一旦、Y選択信号Yiおよび参照セル選択信号YR2が、Lレベルとなる。センスアンプ40が一旦非活性化され、センスノードCELBDおよびREFBDが接地電圧レベルにプリチャージされる。再び、Y選択信号Yiと参照セル選択信号YR1またはYR3が選択状態へ駆動される。参照セル選択信号YR1およびYR3のいずれが選択状態へ駆動されるかは、先の1回目のセンス動作により読出されたデータにより決定される。1回目のセンス動作と同様のセンス動作が、センスノードCELBDおよびREFBDが同一電圧レベルに収束した後に実行される。10

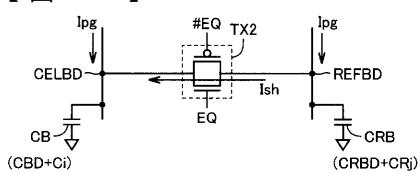

#### 【0106】

このセンス動作時において、センスノードCELBDおよびREFBDの容量値は不平衡である。センスアンプ40によるプリチャージ動作時においては、図14に示すように、センスノードREFBDとCELBDは、CMOSトランジションゲートTX2により電気的に短絡された状態にある。したがって、参照センスノードREFBDに対する容量CRB（=CRBD+CRj）が、セルセンスノードCELBDの容量（=CBD+Ci）よりも小さいため、この参照センスノードREFBDの電位は、セルセンスノードCELBDの電位よりも早く上昇する。このときCMOSトランジションゲートTX2はオン状態であるため、参照センスノードREFBDからセルセンスノードCELBDへ電流Is hが流れ、プリチャージ電流Ip gに加えて、選択メモリセルが接続されるビット線へ供給される。これにより、セルセンスノードCELBDの電位上昇速度が増加され、高速で、これらのセンスノードCELBDおよびREFBDを所定電圧レベルに収束させることができ、応じて早いタイミングでセンス動作を行なうことができる。センスノードの容量値が非平衡状態であるため、2回目のセンス動作時においても、再び、高速で、これらのセンスノードCELBDおよびREFBDを所定の電圧レベルへ収束させることができ、同様に、2回目のセンス動作開始タイミングをも早くすることができ、応じてアクセス時間を短縮することができる。20

#### 【0107】

なお、このセンスアンプ40の参照センスノードREFBDに接続する容量の容量値を、選択メモリセルが接続されるセルセンスノードCLBDの容量値よりも小さくする構成としては、現実の容量素子が、それらの容量値が調整されて、これらのセンスノードREFBDおよびCELBDに接続されてもよく、また、この参照センスノードREFBDの配線の長さ／幅を小さくして、その寄生容量を小さくすることにより実現されてもよい。30

#### 【0108】

なお、上述の説明においては、メモリセルNMCが、4値データを格納している場合について説明している。しかしながら、このメモリセルが2値データ（“1”および“0”）を記憶するメモリセルの場合であっても、同様、1回のセンス動作が行なわれるだけであり、センス動作開始タイミングを早くすることができ、アクセス時間を短縮することができる。40

#### 【0109】

以上のように、この発明の実施の形態3に従えば、センスアンプの参照センスノードの容量を、このセンスアンプのセルセンスノードの容量よりも小さくしており、高速で、これらのセンスノードおよび参照センスノードの電位を所定電圧レベルに収束させることができ、アクセス時間を短縮することができる。

#### 【0110】

##### [実施の形態4]

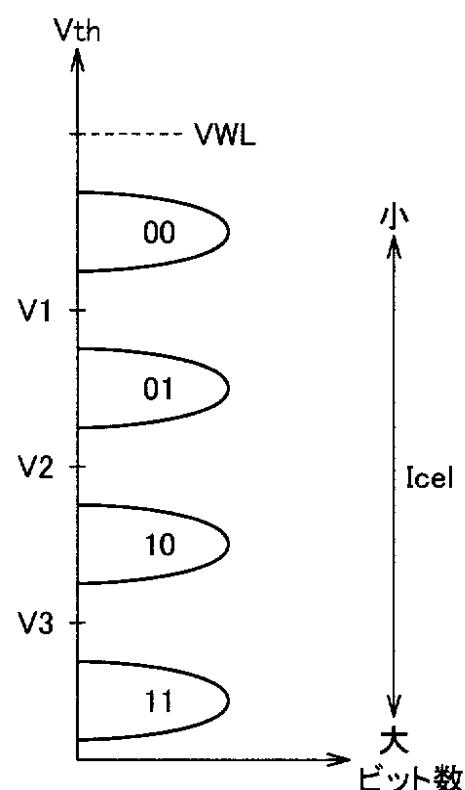

図15は、この発明の実施の形態4におけるメモリセルの記憶データのしきい値電圧の分布の一例を概略的に示す図である。図15においては、4値データを記憶するメモリセ50

ルのしきい値電圧の分布を示す。データ(11)を記憶するメモリセルのしきい値電圧は、電圧V3よりも低い。データ(10)を記憶するメモリセルのしきい値電圧は、電圧V2およびV3の間に分布する。データ(01)を記憶するメモリセルのしきい値電圧は、電圧V1およびV2の間に分布する。データ(00)を記憶するメモリセルのしきい値電圧は、電圧V1よりも高い電圧レベルであり、また、データ読出時にワード線に与えられるワード線読出電圧VWLよりも低い電圧レベルである。メモリセルのしきい値電圧が低いほど、ワード線読出電圧VWL印加時のメモリセル電流Icelが大きくなる。したがって、データ(11)を記憶するメモリセルの駆動電流が、データ(00)を記憶するメモリセルの駆動電流よりもデータ読出時大きくなる。

## 【0111】

消去動作時および書き込み動作時においては、このメモリセルの記憶データに応じて、そのしきい値電圧が設定される。今、しきい値電圧が最も低くされる状態を消去状態と呼ぶことにする。すなわち、データ(11)を記憶する状態が、消去状態である。この消去動作後、記憶データに応じて、順次、メモリセルのしきい値が高くされ、データの書き込みが行なわれる。この書き込み動作時および消去動作時においては、しきい値電圧の分布範囲の上限および下限内に、メモリセルのしきい値電圧が存在するかのベリファイ動作が行なわれる。

## 【0112】

ベリファイ動作時においては、ベリファイセンスアンプを用いてベリファイ参照電流を生成して各データに応じた上限電流および下限電流を設定して、メモリセル電流が、そのベリファイ参照電流の規定する領域内に存在するかの判定が行なわれる。このベリファイ動作時において、ワード線へは、従来、通常のデータ読出時（外部へのデータ読出）と同様のワード線読出電圧VWLが印加される。

## 【0113】

4値データを書き込んだ後のメモリセルの電流分布としては、図12に示される電流分布が得られる。このような電流分布に基づいてベリファイ動作を行なう場合、各セル電流領域の上限値および下限値のベリファイ電流が生成されて、メモリセルの駆動電流と比較される。ベリファイ時に用いられるベリファイセンスアンプは、通常のデータ読出用のセンスアンプと同一構成を有しており、ベリファイ動作およびデータ読出動作にセンスアンプが共用されてもよいが、以下では説明を簡単にするため、ベリファイセンスアンプと読出用のセンスアンプ（実施の形態1において詳細に説明したセンスアンプ）は、別々に設けられるとして説明する。

## 【0114】

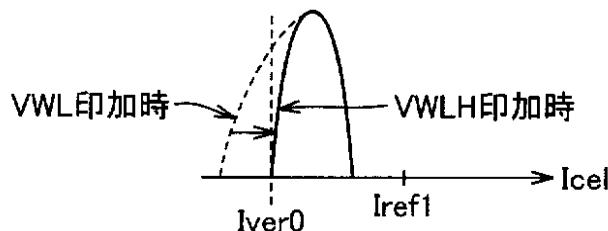

このベリファイ動作時において、図16に示すように、電流分布領域の下端（データ0）の下部の領域のメモリセルに対するベリファイ動作時においては、ワード線電圧（メモリセルトランジスタのゲート電圧）を、通常のデータ読出時に与えられる電圧VWLよりも高い電圧レベルに設定してベリファイ動作を行なう。電流分布の下端のセルのベリファイ動作時、読出電圧VWL印加時におけるセル電流が、図17に示すように下側ベリファイ電流Iver0よりも低いメモリセルに対しては、ほぼオフ状態であり、駆動電流は極めて小さい。センスアンプにおいては、通常の読出時と同程度のセル電流が供給することにより、メモリセルデータを正確にセンスして正確なベリファイ動作を保証することができる。この場合、下限電流よりも小さなセル電流のメモリセルに対しては再度消去を行って、そのしきい値電圧を高くすることにより、正確に、駆動電流分布、すなわち、しきい値電圧分布を狭くすることができ、多値データ記憶時における各データ値に対応する駆動電流分布領域を狭くすることができ、多値データの各参照電流に対するマージンを大きくすることができる。

## 【0115】

この電流分布のメモリセルのベリファイ時、すなわち下限電流のベリファイ時においては、通常のデータ読出時に印加される読出ワード線電圧VWLよりも高い電圧VWLHをベリファイ時に印加する。この場合、図17の破線で示す領域メモリセルの駆動電流が大きくなり、下側ベリファイ電流Iver0よりも高くなり、これらのメモリセルが、データ

10

20

30

40

50

タ(00)を格納していることが検証される。また、正確に、データ(00)のメモリセルの分布領域の上限ベリファイ時においては、上限ベリファイ電流を供給して、データ(00)を記憶するメモリセルの駆動電流が、参照電流 $I_{ref1}$ よりも下部にあることが識別される。このデータ(00)の記憶するメモリセルの電流分布の識別可能領域を、下限側において広くすることができ、正確な検証動作を行なうことができる。

#### 【0116】

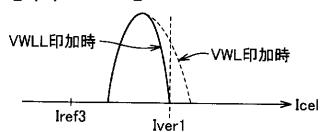

一方、この電流分布の上部のメモリセルの検証時においては、図16に示すように、読出ワード線電圧 $VWL$ よりも低いゲート電圧を印加する。この状態において、図18に示すように、通常の読出ワード線電圧 $VWL$ 印加時の破線で示すメモリセルの駆動電流は、それよりも低いベリファイワード線電圧 $VWLL$ 印加時には小さくなり、上限ベリファイ電流 $Iver1$ よりも小さい電流レベルに低下する。

10

#### 【0117】

電流分布上端のメモリセルにおいては、過剰に電流が流れ、配線抵抗などにおける電圧降下で、ビット線電圧レベルを維持することができなくなり、メモリセルのドレイン電圧が低下する。この結果、セル電流 $Icel$ が低減されるため、上側に広がるメモリセル電流分布を正確に得ることができない。また、このような電流分布上端のメモリセルが駆動する過剰電流は、センスアンプの電源に昇圧電圧を用いる場合消費電流が大きくなり、昇圧電圧発生部は、安定に昇圧電圧を生成することができなくなる可能性がある。メモリセル電流分布上端のベリファイ動作時においては、ワード線電圧を、読出ワード線電圧 $VWL$ よりも低い電圧 $VWLL$ に設定し、ベリファイ動作を行なうことにより、読出ワード線電圧 $VWL$ を印加したベリファイ動作時よりも、広範囲のメモリセル電流の分布を識別することができ、過剰セル電流を駆動するメモリセルを識別して、そのしきい値電圧を高くして、駆動電流を低減することができる。これにより、電流分布の上限の識別可能領域が広くなり、その識別結果に従ってしきい値電圧の調整を行うことにより、しきい値電圧分布すなわちしきい値電圧分布を狭くすることができ、センスアンプに対するセル電流の分布を小さくすることができ、正確なセンス動作を保証することができる。

20

#### 【0118】

したがって、この書込／消去時のベリファイ動作時に、読出ワード線電圧 $VWL$ を用いてベリファイ動作を行なう構成に代えて、そのベリファイ対象のメモリセルの電流分布の位置に応じてワード線電圧を変更することにより、メモリセル電流分布の上限および下限の識別の範囲を広くすることができ、書込／消去のベリファイを正確に行なうことができ、書込／消去時間を短縮することができる。

30

#### 【0119】

また、中央の参照電流 $Iref1$ 、 $Iref2$ および $Iref3$ の近傍の電流分布でのベリファイ動作時においては、ベリファイ時のワード線電圧を読出ワード線電圧 $VWL$ と同じ電圧レベルに設定する。これにより、データ読出時とベリファイ動作時のワード線電圧が同じであり、ベリファイ時および通常動作時において高精度のセンス動作を行なうことができる。

#### 【0120】

なお、図18において、メモリセル電流分布の上限領域のメモリセルのベリファイ動作時において、単に、ワード線に印加される電圧を、電圧 $VWLL$ に設定し、このときのセル電流が、参照電流 $Iref3$ よりも高い電流であるかを判定するベリファイ動作が行なわれてもよい。たとえば、データ(11)の記憶するメモリセルにおいて、ワード線に6V印加時、下限領域が $60\mu A$ の電流を駆動し、上限のメモリセルが $100\mu A$ を駆動する状態を考える。この場合、ワード線電圧を4Vに設定し、上限領域のメモリセルの駆動電流を、 $60\mu A$ に設定する。センスアンプにおいて、データ(11)の上限領域および下限領域いずれにおいてもメモリセル電流がともに $60\mu A$ であり、ベリファイ電流として、参照電流 $Iref3$ と同じ大きさの電流を利用することにより、正確なベリファイ動作を行なうことができる。ただし、この場合、参照セルにおいては、同様、ワード線電圧が低下しており、その駆動電流が小さくされているため、参照セルの駆動する参照電流を

40

50

を利用して、上限領域のベリファイ動作を行なうことはできない（参照電流を駆動する電流が、参照電流  $I_{ref3}$  よりも小さくなっているため）。この場合、ベリファイ電流を、ベリファイ参照セルまたは定電流回路を利用して別途生成してベリファイ動作を行う。

#### 【0121】

また、データ（00）の電流分布の下限領域についても、ベリファイワード線電圧を高くしてベリファイ電流として参照電流  $I_{ref1}$  が用いられても良い。この場合においても、参照電流は、ベリファイ電流発生回路を利用して生成する。

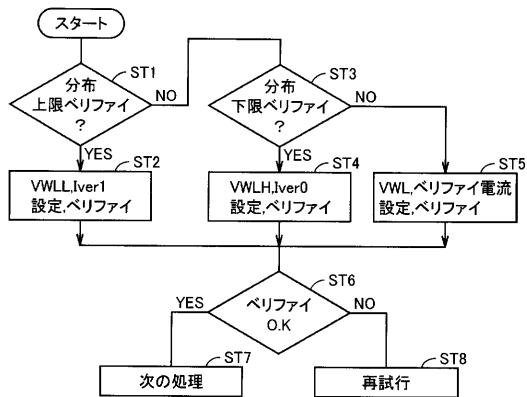

#### 【0122】

図19は、この発明の実施の形態4に従う半導体記憶装置のベリファイ動作を示すフロー図である。以下、図19を参照して、この発明の実施の形態4に従うベリファイ動作について説明する。なお、以下の説明においては、メモリセルのしきい値電圧の低い状態から順次しきい値電圧を高い状態へ設定する書きシーケンスを一例として示す。

#### 【0123】

ベリファイ動作時において、まずメモリセルがすべてしきい値電圧が低い状態に設定され、分布上限（電流分布の上限値）に対するベリファイ動作が行なわれるかの判定が行なわれる（ステップST1）。この電流分布の上限のセルに対するベリファイ動作が行なわれる場合、ワード線電圧を電圧  $VWL_L$  に設定し、また、参照電流としてベリファイ電流  $I_{ver1}$  を設定し、ベリファイ動作を実行する（ステップST2）。

#### 【0124】

一方、ステップST1において分布上限以外のセルに対するベリファイであると判定されると、次いで、セル電流分布の下限値、すなわちしきい値電圧の最も大きい状態に対するベリファイ動作が行なわれるかの判定が実行される（ステップST3）。電流分布の下限領域のメモリセルに対するベリファイ動作である場合には、ワード線電圧が、電圧  $VWL_H$  に設定され、また、参照電流としてベリファイ電流  $I_{ver0}$  が設定され、ベリファイ動作が実行される（ステップST4）。

#### 【0125】

電流分布の上限領域および下限領域いずれでもない場合には、対応の記憶データの領域の電流分布の上限または下限に応じてベリファイ電流が設定される。このとき、ワード線には、読み出ワード線電圧  $VWL$  に設定され、ベリファイ動作が実行される（ステップST5）。

#### 【0126】

ステップST2、ST4およびST5におけるベリファイ動作により、正確に対応のメモリセルがベリファイ電流条件（ベリファイ電流以下または以上）を満たしているかの判定が行なわれる（ステップST6）。このベリファイ判定動作時において、所定の条件が満たされていると判定された場合には、各ベリファイ動作シーケンスに応じて次の処理が実行される（ステップST7）。一方、ベリファイ動作時において、この不良セル、すなわちベリファイ条件を満たさないメモリセルが存在する場合には、再び、その不良セルのしきい値電圧を調整することが再び行なわれる（ステップST8）。この再試行のステップ（ST8）が実行された後、再び、ステップST1に戻り、ベリファイ動作が実行される。

#### 【0127】

ベリファイ動作は、メモリセルの記憶データに応じて消去を含む各データ書き込み後、各データについて実行される。

#### 【0128】

メモリセルデータの書き込み／消去が実行されるとき、予め定められたベリファイシーケンスに従ってベリファイ動作が実行される。このベリファイ動作時、図1に示す制御回路5の制御の下に、内部電圧発生回路6からのワード線電圧  $Vw$  の電圧レベルを調整し、またベリファイ電流が、ベリファイ対象のデータに応じた電流レベルに設定されて、図1に示す読み出回路4に含まれるベリファイセンスアンプに供給される。この場合、読み出回路4内のセンスアンプが、ベリファイ動作およびデータ読み出動作两者において共通に用いられる

10

20

30

40

50

場合には、参照セルからの参照電流に代えて、ベリファイ電流がセンスアンプへ供給される。

### 【0129】

以上のように、この発明の実施の形態4に従えば、メモリセルの電流分布の上限および下限に対し、ベリファイ時のワード線電圧を調整しており、下限領域のメモリセルおよび上限領域のメモリセルの識別可能領域を広くすることができ、正確なベリファイ動作を行なうことができる。

### 【0130】

また、電流分布の上限および下限領域の間の領域のメモリセルに対しては、データ読出と同じ電圧レベルのベリファイ電圧が供給されており、ベリファイ動作時およびデータ読出動作モード時において同じマージンでセンス動作を行なうことができ、データ読出時および書き込み/消去ベリファイ時におけるセンス動作を高精度に一致させることができ、高精度のセンス動作を実現することができる。

### 【0131】

#### [実施の形態5]

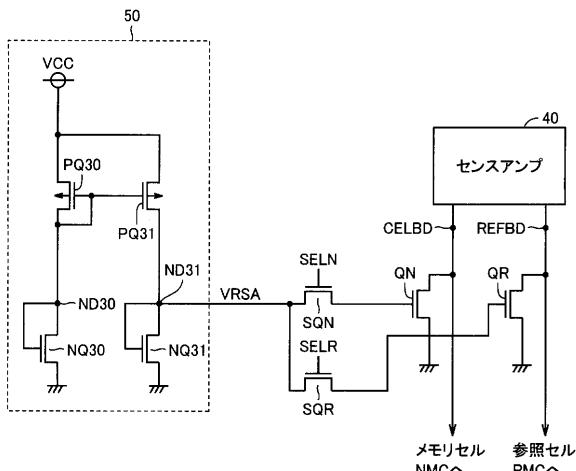

図20は、この発明の実施の形態5に従う不揮発性半導体記憶装置のセンスアンプに関する部分の構成を示す図である。図20において、センスアンプ40は、実施の形態1に示すセンスアンプと同様の構成を備え、センスノードCELBDおよびREFBDが、それぞれ、メモリセルNMCおよび参照セルRMCにセンス動作時結合される。この図20に示す構成においては、センスアンプ40に対して、定電圧VRSAを生成する定電圧発生回路50と、選択信号SELNに従って定電圧VRSAを伝達するトランスマジックアーティSQNと、センスノードCELBDに結合され、定電圧VRSAを転送ゲートSQNを介してゲートに受けて、センスノードCELBDから定電流を接地ノードへ放電するNチャネルMOSトランジスタQNと、選択信号SELRに従って、定電圧VRSAを伝達する転送ゲートSQRと、転送ゲートSQRを介してゲートに定電圧VRSAを受け、参照センスノードREFBDから定電流を接地ノードへ放電するNチャネルMOSトランジスタQRがさらに設けられる。

### 【0132】

定電圧発生回路50は、内部電源ノードとノードND30の間に接続されかつそのゲートがノードND30に接続されるPチャネルMOSトランジスタPQ30と、内部ノードND30と接地ノードの間に接続されかつそのゲートがノードND30に接続されるNチャネルMOSトランジスタNQ30と、電源ノードと内部ノードND31の間に接続されかつそのゲートが内部ノードND30に接続されるPチャネルMOSトランジスタPQ31と、ノードND31と接地ノードの間に接続されかつそのゲートがノードND31に接続されるNチャネルMOSトランジスタNQ31を含む。

### 【0133】

MOSトランジスタNQ31、QNおよびQRは、サイズ(チャネル幅とチャネル長の比)が同じである。PチャネルMOSトランジスタPQ30およびPQ31はカレントミラー段を構成し、MOSトランジスタPQ31は、MOSトランジスタPQ30を流れる電流のミラー電流を内部電源ノードから供給する。ノードND30へMOSトランジスタPQ30から供給される電流により電圧がMOSトランジスタにより生成され、これらのMOSトランジスタPQ30およびNQ30の駆動電流が等しくなるようにノードND30の電圧レベルが設定され、応じて、一定の電流がこれらのMOSトランジスタPQ30およびNQ30に流れる。この一定電流のミラー電流がMOSトランジスタPQ31を介して流れる。MOSトランジスタNQ31が、電流/電圧変換素子として機能し、このMOSトランジスタPQ31から供給される電流を電圧に変換して、定電圧VRSAを生成する。

### 【0134】

選択信号SELNおよびSELRは、この定電圧VRSAに比べて十分高い電圧レベルであり、転送ゲートSQNおよびSQRは、導通時、この定電圧VRSAを、閾値電圧損

10

20

30

40

50

失を伴うことなく、それぞれ、MOSトランジスタQNおよびQRのゲートに伝達する。転送ゲートSQNの導通時、MOSトランジスタNQ31およびQNがカレントミラー回路を構成し、MOSトランジスタQNには、MOSトランジスタNQ31を流れる電流と同じ大きさの電流が流れる（サイズが同じ場合）。同様、転送ゲートSQRの導通時、MOSトランジスタNQ31およびQRがカレントミラー回路を構成し、MOSトランジスタQRが、このMOSトランジスタNQ31が駆動する電流と同じ大きさの電流を駆動する（サイズが同じ場合）。

#### 【0135】

この定電圧発生回路50において、MOSトランジスタPQ30のサイズ（チャネル幅）を変更可能にすることにより、この定電圧VRSAの電圧レベルを変更することができ、MOSトランジスタQNおよびQRが駆動する電流量を、所望の値に設定することができる。次に、図20に示す回路の動作について説明する。

#### 【0136】

(i) SELN=Lレベル、かつSELR=Hレベル：

この状態においては、転送ゲートSQNがオフ状態、転送ゲートSQRがオン状態であり、参照セルRMCに対して設けられるトランジスタQRが定電流源として動作する。この状態において、参照セルRMCを選択しない状態で、メモリセルNMCを選択してセンスアンプ40でセンス動作を行なう。この場合、参照セルRMCが規定する参照電流値と異なる電流値でセンス動作を行なうことができる。したがって、この状態で、定電圧発生回路50のMOSトランジスタPQ30のサイズを変更して、定電圧VRSAを変更することにより、MOSトランジスタQRの駆動電流を変更することができ、メモリセルNMCを流れる電流値を詳細に解析することができる。

#### 【0137】

(ii) SELN=HレベルかつSELR=Lレベル：

この状態においては、転送ゲートSQNがオン状態、転送ゲートSQRがオフ状態であり、MOSトランジスタQNが、定電圧VRSAに従って、定電流をセルセンスノードCELB0から駆動する。この状態においては、メモリセルNMCの選択は行なわず、参照セルRMCを選択して、センスアンプ40でセンス動作を行なう。MOSトランジスタPQ30のサイズ（チャネル幅）を変更してその駆動電流を変更することにより、定電圧発生回路50からの定電圧VRSAを変更して、MOSトランジスタQNが駆動する電流を変更することができる。したがって、この場合、参照セルRMCを流れる電流値を詳細に解析することができる。参照電流を所望の値に設定したい場合、このセンス動作の結果を用いて、所望の参照電流が得られるように、参照セルのしきい値電圧を制御することができる。

#### 【0138】

(iii) SELN=HレベルかつSELR=Hレベル：

この状態においては、転送ゲートSQNおよびSQRがともにオン状態であり、MOSトランジスタQNおよびQRがともに定電流を駆動する。この状態において、メモリセルNMCおよび参照セルRMCをともに選択することにより、センスアンプ40のセンスノードCELB0およびREFBDを流れる電流にオフセットを持たせることができる。

#### 【0139】

一般的な差動増幅器においては、電流値に対して感度が一定でなく、いわゆるヒット範囲と呼ばれる感度の高い電流範囲と比較的感度の低い電流範囲とが存在する。このMOSトランジスタQNおよびQRをともにオン状態に設定することにより、センスアンプ40のカレントミラーパートを流れる電流にオフセットを持たせることにより、感度の高い電流範囲に移行させてセンス動作を行なわせることができ、高精度な電流差動増幅を実現することができる。

#### 【0140】

したがって、センスアンプ40のセンスノードCELB0およびREFBDに、選択的に活性化されかつ互いに独立に活性化される定電流源を接続して、定電流を駆動すること

10

20

30

40

50

により、メモリセルおよび参照セルを流れる電流を詳細に解析することができ、また、センスアンプ40のセンスノードに対してオフセット電流を流すことができ、センス感度の高い領域でセンス動作を行なうことができ、高精度のセンス動作を行なうことができる。

#### 【0141】

なお、この図20に示す構成において、転送ゲートSQNおよびSQRがオフ状態のときには、MOSトランジスタQNおよびQRのゲートがフローティング状態となる。この場合、転送ゲートSQNおよびSQRと相補的に導通するNチャネルMOSトランジスタを用いて、これらのMOSトランジスタQNおよびQRのゲートを接地ノードに結合する。これにより、MOSトランジスタQNおよびQRのゲートが、フローティング状態になるのを防止することができる。10

#### 【0142】

また、転送ゲートSQNおよびSQRに代えて、CMOSトランスマッシュゲートが用いられてもよい。

#### 【0143】

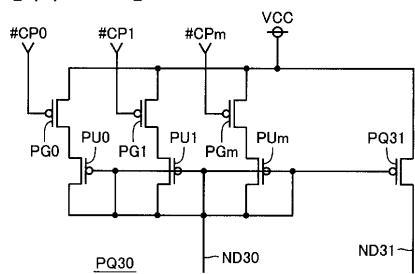

図21は、図20に示す定電圧発生回路50のMOSトランジスタPQ30のサイズ変更の構成の一例を示す図である。図21において、PチャネルMOSトランジスタPQ30は、内部電源ノードに結合されるPチャネルMOSトランジスタPG0-PGmと、これらのMOSトランジスタPG0-PGmと直列に接続される単位PチャネルMOSトランジスタPU0-PUmを含む。MOSトランジスタPU0-PUmは、それぞれゲートおよびドレインが、内部ノードND30に共通に接続される。MOSトランジスタPG0-PGmのゲートには、それぞれ、制御信号CP0-CPmが与えられる。この内部ノードND30は、またMOSトランジスタPQ31のゲートに接続される。20

#### 【0144】

これらのMOSトランジスタPG0-PGmはそれぞれのオン抵抗を十分に小さく設定する。MOSトランジスタPG0-PGmを選択的にオン状態に設定することにより、対応の単位MOSトランジスタPU0-PUmが、電流を駆動し、カレントミラ一段のマスター段トランジスタとして機能する。したがって、MOSトランジスタPG0-PGmを選択的に導通状態に設定し、カレントミラ一段のトランジスタPQ30の駆動電流量を単位トランジスタの駆動電流量ステップで変更することにより、MOSトランジスタPQ31の駆動電流を調整することができる。30

#### 【0145】

MOSトランジスタPQ31は、単位トランジスタPU0-PUmの所定数のトランジスタを導通状態としたときにミラービーが1となるように、そのサイズを設定することにより、選択的にMOSトランジスタPG0-PGmをオン状態に設定することにより、MOSトランジスタPQ31およびPQ31の駆動電流のミラービーmを、1よりも小さい値および1よりも大きい値に設定することができ、MOSトランジスタPQ31の駆動電流を増減することができる。

#### 【0146】

制御信号CP0-CPmは、図1に示す制御回路5に含まれるテスト制御回路から、テストモード時に選択的に活性化されればよい。センスアンプのオフセット電流設定時においては、この制御信号CP0-CPmを選択的に活性状態(Lレベル)に不揮発性メモリ素子で構成されるレジスタ回路などにおいて設定する、または、解析結果に従ってヒューズプログラム回路のヒューズのプログラムにより設定することにより実現することができる。40

#### 【0147】

以上のように、この発明の実施の形態5に従えば、センスアンプのセンスノードへ定電流源を選択的に結合し、これらの定電流源を互いに独立に活性/非活性化しており、メモリセルおよび参照セルの電流特性を詳細に解析することができ、またセンスアンプの動作範囲を最適範囲に設定することができる。

#### 【0148】

[実施の形態 6]

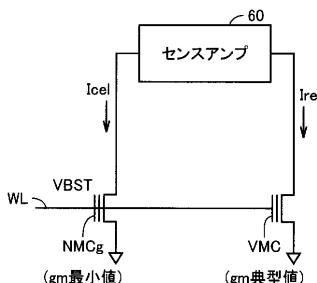

図22は、この発明の実施の形態6に従う不揮発性半導体記憶装置の要部の構成を概略的に示す図である。図22において、センスアンプ60に、メモリセルNMCgおよびベリファイ参照セルVMCが結合される。これらのメモリセルNMCgおよびベリファイ参照セルVMCは、ワード線WLに共通に結合される。このベリファイ参照セルVMCは、その相互コンダクタンスgmが典型値を有し、メモリセルNMCgが、その相互コンダクタンスgmが、最小値を有する状態を考える。このメモリセルNMCgを消去する場合、ワード線WLに消去電圧を印加して、メモリセルNMCgのしきい値を変化させる。この消去動作は、ここでは、メモリセルNMCgの相互コンダクタンスgmを大きくする、すなわちメモリセルNMCgのしきい値電圧の絶対値を小さくする動作とする。

10

【0149】

消去動作および書き込み後のベリファイ動作により、メモリセルNMCgの相互コンダクタンスgmを大きくし、ワード線WLにベリファイ電圧VBSTを印加して、このメモリセルNMCgとベリファイ参照セルVMCの駆動電流が同じ大きさとなる状態に設定される。ベリファイ参照セルは、ベリファイ対象のデータそれぞれに対応して配置され、ベリファイ対象のデータが、値が異なる場合においてもワード線には、同一電圧レベルの電圧が印加されるとする。ベリファイ動作としては実施の形態4の構成と組み合わされてもよい。

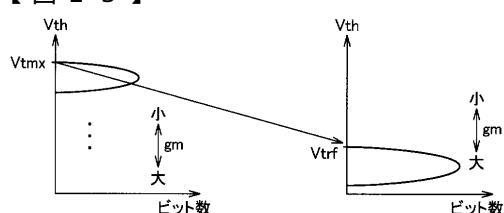

【0150】

したがって、図23に示すように、最小の相互コンダクタンスgmに対応するしきい値電圧Vthが最も大きい電圧Vtmxを有するメモリセルのしきい値電圧は、消去状態では、しきい値電圧Vtrfよりも低い値となり、典型的な相互コンダクタンスを有するベリファイ参照セルと同じしきい値電圧を有する状態に設定される。

20

【0151】

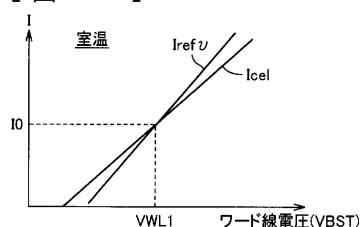

この状態においては、図24に示すように、室温状態においてはベリファイ参照セルVMCの駆動する電流IrefvとメモリセルNMCgの駆動する電流Icelが、ベリファイ電圧VWL1印加時、電流値I0で等しくなる。メモリセルNMCgおよびベリファイ参照セルVMCは、この製造工程時における製造パラメータのばらつきなどにより、ゲート電圧と駆動電流の特性に差が存在する。したがって、これらのゲート電圧(Vg)と駆動電流(Id)の間の関係、すなわちVg - Id特性も、その温度依存性が異なる。

30

【0152】

したがって、たとえば図25に示すように、温度100において、ベリファイ参照セルVMCおよびメモリセルNMCgの電流特性が変化し、電圧VWL1をワード線に印加した場合に、駆動電流は、ベリファイ参照セルでは電流値I1であり、メモリセルでは、電流値I2になった状態を考える。ベリファイ動作時においては、このベリファイ参照電流Irefvとセル電流Icelを等しくする状態で、すべてのメモリセルの消去が完了する。しかしながら、このように電流値が異なる場合、セル電流Icelが、ベリファイ参照電流Irefvと等しくなるように、さらに消去動作を行なう必要がある。このため、メモリセルのしきい値電圧がさらに変化するため、メモリセルのしきい値電圧分布が広くなる。

40

【0153】

したがって、消去動作後のデータ書込時においても、同様、ベリファイ時、各データに対して、ベリファイ電流とメモリセル電流に差が生じるため、同様、しきい値電圧分布が、広くなる。このため、多値データ記憶時において、しきい値電圧分布領域の間隔が狭くなり、データ読出のマージンが小さくなる。このようなしきい値電圧分布を小さくするためには、温度100においては、ワード線ベリファイ電圧VWL2を供給することにより、参照電流Irefvとセル電流Icelを一致させることができ、室温時と同様のしきい値電圧分布を実現することができる。

【0154】

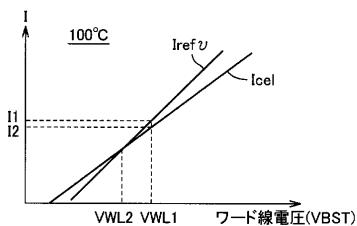

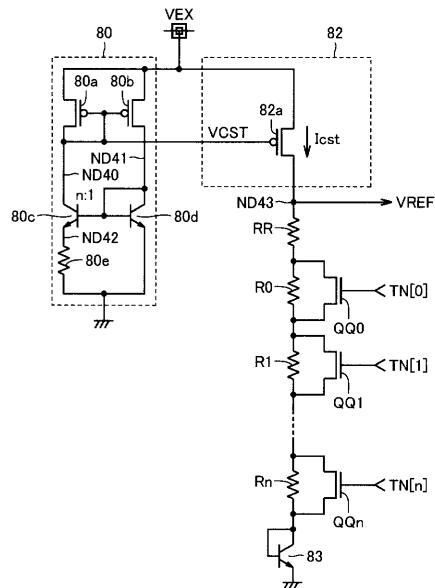

図26は、この発明の実施の形態6に従うベリファイ電圧発生部の構成を概略的に示す

50

図である。図26において、ベリファイ電圧発生部は、基準電圧VREFの電圧レベルを設定する多ビットレベル制御信号TN[n:0]とベリファイ電圧VBSTの分圧比を設定する多ビット分圧制御信号TM[n:0]を生成するコントローラ70と、コントローラ70からの多ビットレベル制御信号TN[n:0]に従ってその電圧レベルが設定される基準電圧VREFを生成するVREF発生回路72と、多ビット分圧比制御信号TM[n:0]に従ってベリファイ電圧VBSTを分圧して分圧電圧DVSTを生成する分圧回路78と、分圧回路78からの分圧電圧DVSTと基準電圧VREFとを比較し、その比較結果に基づいてポンプイネーブル信号PENを生成するレベル検出回路74と、ポンプイネーブル信号PENの活性化時、チャージャポンプ動作を行なってワード線ベリファイ電圧VBSTを生成するポンプ回路76を含む。

10

## 【0155】

VREF発生回路72からの基準電圧VREFは、コントローラ70からの多ビットレベル制御信号TN[n:0]に従って電圧レベルが変化し、応じて、その温度依存性を調整する。分圧回路78において電圧制御信号TM[n:0]に従ってワード線ベリファイ電圧VBSTの分圧比を調整することにより、この基準電圧VREFの電圧レベルの変化を補償する。これにより、ベリファイワード線電圧VBSTの電圧レベルに対して、正の方向および負の方向いずれにおいても、温度依存性を持たせることが可能となる。

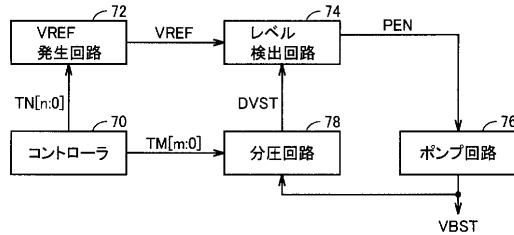

## 【0156】

図27は、図26に示すVREF発生回路72の構成の一例を示す図である。図27において、VREF発生回路72は、外部電源電圧VEXから、外部電源電圧VEXに依存しない一定の定電圧VCSTを生成する定電圧発生回路80と、定電圧発生回路80からの定電圧VCSTに従って一定の大きさの電流Icstを供給する定電流源82と、定電流源82の出力ノードND43に対して直列に接続される抵抗素子RRおよびR0-Rnと、抵抗素子Rnと接地ノードの間に接続されかつそのベースがコレクタに接続されるNPNバイポーラトランジスタ83と、抵抗素子R0-Rnそれぞれに並列に接続されかつそれぞれのゲートに制御ビットTN[0]-TN[n]を受けるNチャネルMOSトランジスタQQ0-QQnを含む。

20

## 【0157】

定電圧発生回路80は、外部電源ノードと内部ノードND40の間に接続されかつそのゲートが内部ノードND40に接続されるPチャネルMOSトランジスタ80aと、外部電源ノードと内部ノードND41の間に接続されかつそのゲートが内部ノードND40に接続されるPチャネルMOSトランジスタ80bと、ノードND40およびND42の間に接続されかつそのベースがノードND41に接続されるNPNバイポーラトランジスタ80cと、内部ノードND41と接地ノードの間に接続されかつそのベースが内部ノードND41に接続されるNPNバイポーラトランジスタ80dと、内部ノードND42と接地ノードの間に接続される抵抗素子80eを含む。

30

## 【0158】

バイポーラトランジスタ80cの駆動電流は、バイポーラトランジスタ80dのエミッタ面積のn倍に設定される。

40

## 【0159】

この定電圧発生回路80においては、MOSトランジスタ80aおよび80bがカレントミラー段を構成し、同じ大きさの電流を供給する。一方、バイポーラトランジスタ80cおよび80bは、たとえば、バイポーラトランジスタ80dが、1つの単位バイポーラトランジスタで構成され、一方、バイポーラトランジスタ80cが、n個の並列接続される単位バイポーラトランジスタで構成され、等価的に、エミッタ面積が、バイポーラトランジスタ80cは、バイポーラトランジスタ80dのn倍となり、エミッタ電流がn倍に設定される。この場合、ノードND42には、これらのバイポーラトランジスタ80cおよび80dのベース-エミッタ間電圧Vbeの差に対応する電圧が生じる。したがって、この抵抗素子80eの抵抗値をZ(80E)とした場合、抵抗素子80eに流れる電流I(80e)は、次式で表わされる。

50

## 【0160】

$$I(80e) = V_T \cdot \ln(n) / Z(80e)$$

ここで、 $V_T$ は、熱電圧であり、 $k \cdot T / q$ で表される。 $k$ はボルツマン定数であり、 $q$ は電荷を示す。

## 【0161】

この抵抗素子 $80e$ に流れる電流は、MOSトランジスタ $80a$ を介して外部電源ノードから供給され、このMOSトランジスタ $80a$ のゲート、すなわちノードND40には、この電流 $I(80e)$ に対応する定電圧 $V_{CST}$ が現れる。抵抗素子 $80e$ は拡散抵抗で例えば形成され、抵抗素子 $80e$ の抵抗値 $Z(80e)$ が大きな正の温度係数を有しており、電流 $I(80e)$ は、その熱電圧の温度依存性が打ち消され、この結果、定電圧 $V_{CST}$ は、ほぼ温度に依存しない一定の電圧となる。

10

## 【0162】

定電流源 $82$ は、この定電圧発生回路 $80$ のMOSトランジスタ $80a$ とカレントミラー回路を構成するPチャネルMOSトランジスタ $82a$ を含む。したがって、このMOSトランジスタ $82a$ には、MOSトランジスタ $80a$ を流れる電流 $I(80e)$ のミラーレンジスト $I_{cst}$ が流れる。この電流 $I_{cst}$ は、温度依存性がほぼ補償された温度依存性のない電流である。

## 【0163】

制御ビット $TN[0] - TN[n]$ により、MOSトランジスタ $QQ0 - QQn$ を選択的にオン状態またはオフ状態に設定する。これにより、抵抗素子 $R0 - Rn$ が選択的に短絡され、抵抗素子 $RR$ と接地ノードの間の抵抗値が変化する。したがって、この定電流源 $82$ からの定電流 $I_{cst}$ の電圧降下量が変化し、応じて、ノードND43からの基準電圧 $VREF$ の電圧レベルが調整される。出力ノードND43からの基準電圧 $VREF$ は、抵抗素子 $RR$ の抵抗値を $R(RR)$ とし、抵抗素子 $R0 - Rn$ それぞれの抵抗値を $R(R)$ とし、トランジスタ $QQ0 - QQn$ のうちの導通状態のトランジスタの数を $m$ とし、バイポーラトランジスタ $83$ のベース-エミッタ間電圧を $Vbe$ とすると、次式で表わされる。

20

## 【0164】

$$VREF = I_{cst} \cdot (R(RR) + m \cdot R(R)) + Vbe$$

このバイポーラトランジスタ $83$ のベース-エミッタ間電圧 $Vbe$ は、負の温度係数を有しており、また抵抗素子 $R0 - Rn$ は各々拡散抵抗で形成され、正の温度係数を有する。したがって、これらの抵抗素子 $R0 - Rn$ を制御ビット $TN[0] - TN[n]$ に従って選択的に短絡することにより、この基準電圧 $VREF$ の温度依存性を、正および負のいずれの方向にも調整することができる。

30

## 【0165】

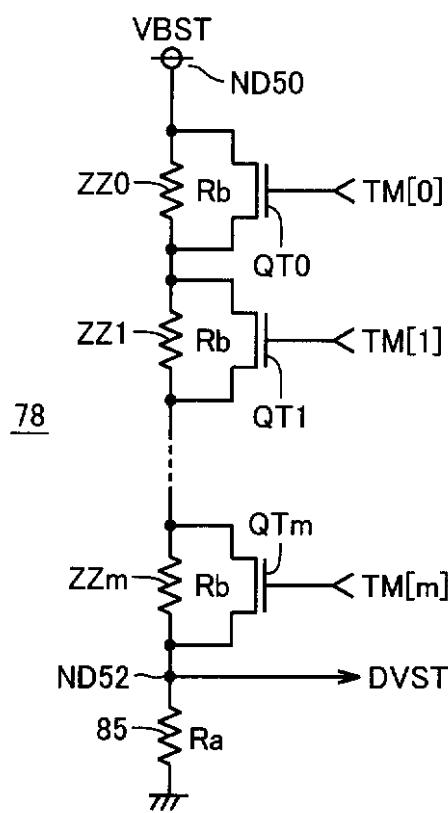

図28は、図26に示す分圧回路78の構成の一例を示す図である。図28において、分圧回路78は、ベリファイワード線電圧 $VBST$ を受けるノードND50と出力ノードND52の間に直列に接続される抵抗素子 $ZZ0 - ZZm$ と、出力ノードND52と接地ノードの間に接続される抵抗素子 $85$ と、抵抗素子 $ZZ0 - ZZm$ とそれぞれ並列に接続されかつそれぞれのゲートに制御ビット $TM[0] - TM[n]$ を受けるNチャネルMOSトランジスタ $QTO - QTm$ を含む。出力ノードND52から分圧 $DVST$ が出力される。

40

## 【0166】

抵抗素子 $ZZ0 - ZZm$ および $85$ は、拡散抵抗でたとえば構成され、それぞれの抵抗値は正の温度係数を有する。抵抗素子 $ZZ0 - ZZm$ は、同一の抵抗値 $Rb$ を有し、抵抗素子 $85$ が、抵抗値 $Ra$ を有する。

## 【0167】

この図28に示す分圧回路78の構成において、ベリファイ電圧ノードND50と出力ノードND52の間に、 $k$ 個の抵抗素子が接続された場合、分圧電圧 $DVST$ は、次式で与えられる。

50

## 【0168】

$$D V S T = V B S T \cdot R a / (R a + k \cdot R b)$$

この分圧電圧  $D V S T$  が、基準電圧  $V R E F$  と等しくなるように、レベル検出回路 74において、ポンプイネーブル信号  $P E N$  が選択的に活性化される。温度依存性を変更するために、図 27 に示す  $V R E F$  発生回路 72 において、抵抗素子  $R 0 - R n$  を選択的に短絡させた場合、基準電圧  $V R E F$  の電圧レベルが変化する。この基準電圧  $V R E F$  の電圧レベルの変化を、分圧電圧  $D V S T$  の変化により補償し、同一電圧レベルで、温度依存性の異なる基準電圧  $V R E F$  を生成する。

## 【0169】

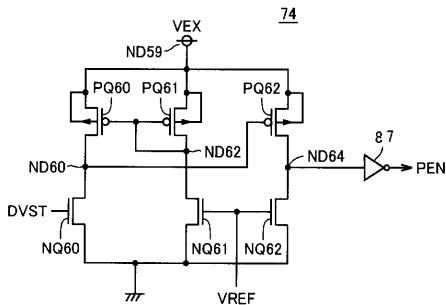

図 29 は、図 26 に示すレベル検出回路 74 の構成の一例を示す図である。図 29 において、レベル検出回路 74 は、電源ノード  $N D 5 9$  と内部ノード  $N D 6 0$  の間に接続されかつそのゲートが内部ノード  $N D 6 2$  に接続される P チャネル MOS トランジスタ  $P Q 6 0$  と、電源ノード  $N D 5 9$  と内部ノード  $N D 6 2$  の間に接続されかつそのゲートが内部ノード  $N D 6 0$  と接地ノードの間に接続されかつそのゲートに分圧電圧  $D V S T$  を受ける N チャネル MOS トランジスタ  $N Q 6 0$  と、内部ノード  $N D 6 2$  と接地ノードの間に接続され、かつそのゲートに基準電圧  $V R E F$  を受ける N チャネル MOS トランジスタ  $N Q 6 1$  と、電源ノード  $N D 5 9$  とノード  $N D 6 4$  の間に接続されかつそのゲートが内部ノード  $N D 6 0$  に接続される P チャネル MOS トランジスタ  $P Q 6 2$  と、内部ノード  $N D 6 4$  と接地ノードの間に接続されかつそのゲートで基準電圧  $V R E F$  を受ける N チャネル MOS トランジスタ  $N Q 6 2$  と、ノード  $N D 6 4$  上の電圧信号を反転してポンプイネーブル信号  $P E N$  を生成するインバータ 87 を含む。

## 【0170】

P チャネル MOS トランジスタ  $P Q 6 0 - P Q 6 2$  は、それぞれのバックゲートが、電源ノード  $N D 5 9$  に接続される。この電源ノード  $N D 5 9$  は、外部電源電圧  $V E X$  が与えられてもよく、また内部電源電圧  $V C C$  に与えられてもよい。基準電圧  $V R E F$  および分圧電圧  $D V S T$  の電圧レベルに対して、最もよい感度でこのレベル検出回路 70 が検出動作を行なえるように、この電源ノード  $N D 5 9$  へ与えられる電圧レベルは定められればよい。

## 【0171】

この図 29 に示すレベル検出回路 74 の構成において、分圧電圧  $D V S T$  が基準電圧  $V R E F$  よりも高いときには、ノード  $N D 6 0$  の電圧レベルが低下し、MOS トランジスタ  $P Q 6 2$  のコンダクタンスが大きくなり、ノード  $N D 6 4$  への供給電流が増大する。MOS トランジスタ  $N Q 6 2$  は、出力ノード  $N D 6 4$  に対する負荷素子として機能し、急激なノード  $N D 6 4$  の電圧レベル変化を抑制する。このノード  $N D 6 4$  の電圧レベルの上昇に応じてインバータ 87 からのポンプイネーブル信号  $P E N$  が L レベルとなり、図 26 に示すポンプ回路 76 のポンプ動作が停止される。

## 【0172】

一方、基準電圧  $V R E F$  が分圧電圧  $D V S T$  よりも高いときには、ノード  $N D 6 0$  の電圧レベルが上昇し、MOS トランジスタ  $P Q 6 2$  のコンダクタンスが低下し、ノード  $N D 6 4$  が MOS トランジスタ  $N Q 6 2$  を介して放電される。応じて、インバータ 87 からのポンプイネーブル信号  $P E N$  が H レベルに立上がり、図 26 に示すポンプ回路 76 が活性化される。したがって、この図 29 に示すレベル検出回路 74 は、基準電圧  $V R E F$  と分圧電圧  $D V S T$  が等しくなるようにポンプ回路 76 のポンプ動作を制御するように、ポンプイネーブル信号  $P E N$  が活性 / 非活性化される。

## 【0173】

なお、この場合、ワード線ベリファイ電圧  $V B S T$  は、次式で表わされる。

## 【0174】

$$V B S T$$

$$= D V S T \cdot (R a + k \cdot R b) / R a$$

10

20

30

40

50

$$= V_{REF} \cdot (R_a + k \cdot R_b) / R_a$$

$$= \{ I_{cst} \cdot (R_{(RR)} + m \cdot R(R) + V_{be}) \cdot (R_a + k \cdot R_b) / R_a$$

上式において、抵抗値  $R_a$  および  $R_b$  の項は、その分母および分子により、温度特性が相殺される。一方、{}内においては、ベース-エミッタ間電圧  $V_{be}$  および抵抗値  $R_{(RR)} + m \cdot R(R)$  が、それぞれ負の温度特性および正の温度特性を有しており、この抵抗値  $R_{(RR)} + m \cdot R(R)$  を調整することにより、ベリファイ電圧  $V_{BST}$  の温度特性を、電圧レベルを変更することなく、変更することができる。

#### 【0175】

したがって、ベリファイ電圧  $V_{BST}$  の電圧レベルを制御ビット  $T_M[n:0]$  により設定し、この温度特性を、制御ビット  $T_N[n:0]$  に設定することにより、広い温度範囲にわたって、正確に、参照セルのベリファイ電流とメモリセルの駆動電流が一致するよう、ベリファイワード線電圧を生成してベリファイ動作を行なうことができる。室温においてベリファイ参照電流とセル電流とが一致したとき（電圧  $V_{WL1}$ ）、100においては、ベリファイ電圧の電圧レベルがその温度特性にしたがって変化し電圧  $V_{WL2}$  となり、ベリファイ参照電流とセル電流とが一致する。したがって、一旦ベリファイ電圧の電圧レベルおよび温度特性が設定されれば、温度に依存することなくしきい値電圧分布（電流分布）を等しくすることができ、広い温度範囲にわたって、しきい値電圧の分布が一定とすることができます。

#### 【0176】

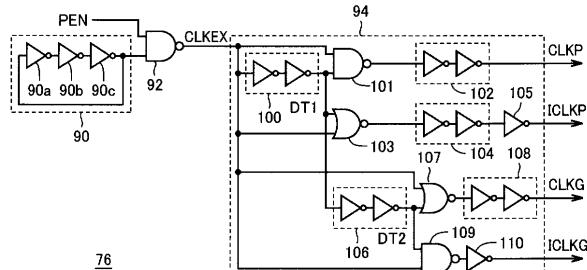

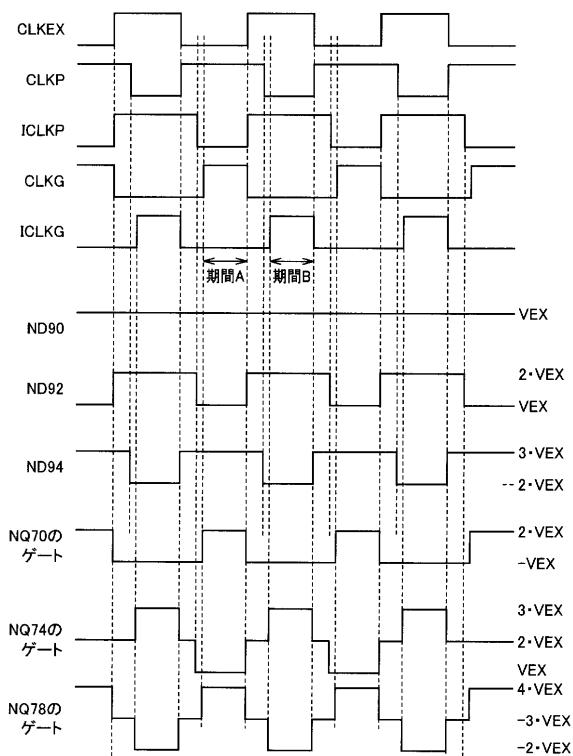

図30は、図26に示すポンプ回路76に含まれるポンプ制御信号を発生する部分の構成の一例を示す図である。図30において、ポンプ回路76は、クロック信号を発生するクロック発生回路90と、このクロック発生回路90の出力信号とポンプイネーブル信号  $PEN$  とを受けてメインポンプ制御信号  $CLKEX$  を生成するNAND回路92と、メインポンプ制御信号  $CLKEX$  に従って互いに位相の異なるポンプ制御信号  $CLKP$ 、 $CLKG$  および  $ICLK$  を生成するポンプ制御信号発生回路94を含む。

#### 【0177】

クロック発生回路90は、奇数段のリング状に接続されるインバータ  $90a - 90c$  を含む。これらのインバータ  $90a - 90c$  により、リングオシレータが形成され、所定の周期で変化するクロック信号が生成される。

#### 【0178】

NAND回路92は、ポンプイネーブル信号  $PEN$  がHレベルのときには、インバータとして動作し、クロック発生回路90からのクロック信号を反転してメインポンプ制御信号  $CLKEX$  を変化させる。一方、ポンプイネーブル信号  $PEN$  がLレベルに設定されたときには、NAND回路92は、クロック信号発生回路90の出力信号に係らずメインポンプ制御信号  $CLKEX$  をHレベルに固定する。

#### 【0179】

ポンプ制御信号発生回路94は、メインポンプ制御信号  $CLKEX$  を所定時間  $DT1$  遅延する遅延回路100と、遅延回路100の出力信号とメインポンプ制御信号  $CLKEX$  を受けるNAND回路101と、NAND回路101の出力信号をバッファ処理してポンプ制御信号  $CLKP$  を生成するバッファ回路102と、遅延回路100の出力信号とメインポンプ制御信号  $CLKEX$  とを受けるNOR回路103と、NOR回路103の出力信号をバッファ処理するバッファ回路104と、バッファ回路104の出力信号を反転してポンプ制御信号  $ICLK$  を生成するインバータ105と、遅延回路100の出力信号をさらに時間  $DT2$  遅延する遅延回路106と、遅延回路106の出力信号とメインポンプ制御信号  $CLKEX$  とを受けるNOR回路107と、NOR回路107の出力信号をバッファ処理してポンプ制御信号  $CLKG$  を生成するバッファ回路108と、遅延回路106の出力信号とメインポンプ制御信号  $CLKEX$  とを受けるNAND回路109と、NAND回路109の出力信号を反転してポンプ制御信号  $ICLK$  を生成するインバータ110を含む。

#### 【0180】

10

20

30

40

50

遅延回路 100 および 106 並びにバッファ回路 102、104、および 108 は、それぞれ、2 段の継続接続されるインバータでたとえば構成される。遅延回路 100 および 106 により生成されるポンプ制御信号の位相を異ならせ、バッファ回路 102、104、および 108 によりポンプ制御信号の波形整形およびタイミングの微調整を行う。

#### 【0181】

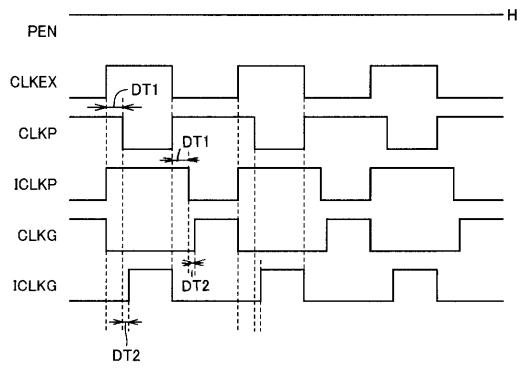

図 31 は、図 30 に示すポンプ制御信号発生回路の動作を示すタイミング図である。以下、図 31 を参照して、ポンプイネーブル信号 P E N が H レベルのときのポンプ制御信号発生回路 94 の動作について説明する。

#### 【0182】

メインポンプ制御信号 C L K E X が H レベルに立上ると、N O R 回路 103 の出力信号が L レベルとなり、インバータ 105 からのポンプ制御信号 I C L K P が H レベルに立上がる。また、N O R 回路 107 の出力信号が、同様、L レベルとなり、バッファ回路 108 の出力するポンプ制御信号 C L K G が L レベルに立下がる。ここで、バッファ回路 104 および 108 は、信号のバッファ処理を行うだけであり、そのゲート遅延時間は十分小さくされている。

#### 【0183】

一方、遅延回路 100 の出力信号が、その遅延時間 D T 1 経過後に H レベルになると、N A N D 回路 101 の出力信号が L レベルとなり、バッファ回路 102 からのポンプ制御信号 C L K P が L レベルに立下がる。

#### 【0184】

また、遅延回路 100 および 106 の有する遅延時間 D T 1 および D T 2 が経過すると、N A N D 回路 110 の出力信号が L レベルとなり、インバータ 110 からのポンプ制御信号 I C L K G が H レベルに立上がる。

#### 【0185】

メインポンプ制御信号 C L K E X が L レベルに立下ると、N A N D 回路 101 の出力信号が H レベルとなり、応じて、ポンプ制御信号 C L K P が H レベルに立上がる。また、N A N D 回路 109 の出力信号が H レベルとなり、インバータ 110 からのポンプ制御信号 I C L K G が L レベルに立下がる。

#### 【0186】

遅延回路 100 の有する遅延時間 D T 1 が経過すると、N O R 回路 103 の出力信号が H レベルとなり、応じて、インバータ 105 からのポンプ制御信号 I C L K P が L レベルに立下がる。さらに、遅延回路 106 の有する遅延時間 D T 2 が経過すると、N O R 回路 107 の出力信号が H レベルとなり、バッファ回路 108 の出力するポンプ制御信号 C L K G が H レベルに立上がる。

#### 【0187】

以降、メインポンプ制御信号 C L K E X の立上がりおよび立下りに従って同じ動作が繰返される。

#### 【0188】

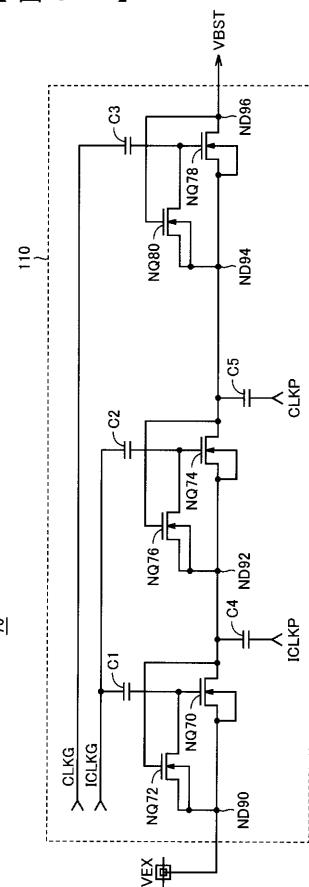

図 32 は、図 26 に示すポンプ回路 76 に含まれる昇圧ポンプ 110 の構成の一例を示す図である。図 32 においては、3 段の電荷転送段で、この昇圧ポンプが構成される場合を一例として示す。さらに多くの電荷転送段が接続されてもよい。

#### 【0189】

図 32 において、ポンプ回路 76 に含まれる昇圧ポンプ 115 は、外部電源ノード N D 90 と内部ノード N D 92 の間に接続され、かつそのゲートに容量素子 C 1 を介してポンプ制御信号 C L K G を受ける N チャネル M O S トランジスタ N Q 70 と、M O S トランジスタ N Q 70 のゲートと外部電源ノード N D 90 の間に接続され、かつそのゲートがノード N D 92 に接続される N チャネル M O S トランジスタ N Q 72 と、ノード N D 92 とノード N D 94 の間に接続されかつそのゲートに容量素子 C 2 を介してポンプ制御信号 I C L K G を受ける N チャネル M O S トランジスタ N Q 74 と、M O S トランジスタ N Q 74 のゲートとノード N D 92 の間に接続されかつそのゲートがノード N D 94 に接続される

10

20

30

40

50

NチャネルMOSトランジスタNQ76と、ノードND94と出力ノードND96の間に接続されかつそのゲートに容量素子C3を介してポンプ制御信号CLKGを受けるNチャネルMOSトランジスタNQ78と、MOSトランジスタNQ78のゲートとノードND94の間に接続されかつそのゲートが出力ノードND96に接続されるNチャネルMOSトランジスタNQ80と、ノードND92に、ポンプ制御信号ICLK Pに従ってチャージャポンプ動作を行なう容量素子C4と、ノードND94に対してポンプ制御信号CLKPに従ってチャージャポンプ動作を行なう容量素子C5を含む。容量素子C1およびC4と、MOSトランジスタNQ70およびNQ72との構成が、1つの電荷転送段を構成し、また、する。容量素子C2およびC5と、MOSトランジスタNQ74およびNQ76との構成が、1つの電荷転送段を構成し、容量素子C3と、MOSトランジスタNQ78およびNQ80とが、最終段の電荷転送段を構成する。ノードND96からワード線ベリファイ電圧VBSTが出力される。10

#### 【0190】

図33は、図32に示す昇圧ポンプ回路110の動作を示すタイミング図である。以下、図33を参照して、この図32に示す昇圧ポンプ回路110の安定動作時の動作について説明する。

#### 【0191】

ノードND90は、外部電源電圧VEXレベルに維持される。ポンプ制御信号ICLK Pが、メインポンプ制御信号CLKEXの立上がりに応答して立上ると、ノードND92の電圧レベルが、このポンプ制御信号の振幅（外部電源電圧VEX）だけ上昇する。応じて、MOSトランジスタNQ72がオン状態となり、MOSトランジスタNQ70のゲート電圧が、外部電源電圧VEXレベルにプリチャージされる。20

#### 【0192】

このとき、また、ポンプ制御信号CLKGが、Lレベルに立下り、容量素子C1およびC3によるチャージャポンプ動作が行なわれる。このとき、MOSトランジスタNQ72がオン状態であり、MOSトランジスタNQ70のゲート電位は、外部電源電圧VEXレベルに維持され、MOSトランジスタNQ70は、オフ状態に維持される。また、MOSトランジスタNQ74は、そのゲート電位が3・VEXであり、MOSトランジスタNQ76がオン状態であり、容量素子C4によるチャージポンプ動作によりそのゲートおよびソース電位が等しくなり、オフ状態にある。これにより、ノードND92がフローティング状態になり、容量素子C4チャージポンプ動作によりノードND92が確実に、2・VEXの電圧レベルにプリチャージされる。30

#### 【0193】

また、ポンプ制御信号CLKGの立下りに応答して、MOSトランジスタNQ78のゲート電位が、電圧4・VEXから、電圧3・VEXに低下し、MOSトランジスタNQ78のゲートおよびソース電位が等しくなり、MOSトランジスタNQ78がオフ状態となる。このとき、ノードND94の電位は、電圧3・VEXである。

#### 【0194】

次いで、ポンプ制御信号CLKPが、HレベルからLレベルに低下すると、ノードND94の電圧レベルが、電圧VEXだけ低下する。このとき、既に、ポンプ制御信号CLKGの立下りに従って、MOSトランジスタNQ78のゲート電位は、3・VEXレベルまで低下している状態であり、MOSトランジスタNQ80がオン状態となり（出力電圧VBSTが、2・VEXよりも高い電圧レベル）、容量素子C5のチャージポンプ動作により、MOSトランジスタNQ78のゲート電圧が、2・VEXまで低下し、MOSトランジスタNQ78は確実にオフ状態を維持する。40

#### 【0195】

このポンプ制御信号CLKPの立下がった後、ポンプ制御信号ICLK GがHレベルとなり、容量素子C2のチャージポンプ動作によりMOSトランジスタNQ74のゲート電位が、電圧2・VEXから電圧3・VEXに上昇する。これにより、MOSトランジスタNQ74が、オン状態となる。このときにはノードND92およびND94は、同一電圧50

レベルでり、MOSトランジスタNQ76はオフ状態を維持する。

【0196】

次いで、メインポンプ制御信号CLKEXの立ち上がりに応答して、ポンプ制御信号CLKPがHレベルに立ち上がり、容量素子C5のチャージポンプ動作により、ノードND94の電圧レベルが、電圧2·VEXから電圧3·VEXに上昇する。このノードND94の電位上昇に従ってMOSトランジスタNQ76がオン状態となり、MOSトランジスタNQ74のゲート電位が、ノードND92と同一電圧レベルの2·VEXレベルにチャージャされる。

【0197】

また、MOSトランジスタNQ80がオン状態となり、MOSトランジスタNQ78のゲート電位が、電圧3·VEXとなる。 10

【0198】

このとき、ほぼ同じタイミングでポンプ制御信号ICLKがHレベルからLレベルとなり、容量素子C2のチャージポンプ動作により、MOSトランジスタNQ74のゲート電位が3·VEXから2·VEX隣、MOSトランジスタNQ74がオフ状態となる。 20

【0199】

次いで、ポンプ制御信号ICLKがHレベルからLレベルに低下すると、ノードND92の電圧レベルが、容量素子C4のチャージャポンプ動作により低下し、電圧VEXレベルとなる。応じてMOSトランジスタNQ72がオフ状態となり、MOSトランジスタNQ70のゲート電位が、外部電源電圧VEXレベルに維持され、MOSトランジスタNQ70がオフ状態を維持する。 20

【0200】

また、MOSトランジスタNQ76がオン状態となり、MOSトランジスタNQ74のゲート電位がさらに低下し、電圧VEXとなり、MOSトランジスタNQ74が確実にオフ状態に維持される。 30

【0201】

次いで、ポンプ制御信号CLKGがLレベルからHレベルに立上ると、容量素子C1のチャージャポンプ動作により、MOSトランジスタNQ70のゲート電位が電圧VEXから、電圧2·VEXレベルに上昇し、MOSトランジスタNQ70がオン状態となり、ノードND92へ外部電源電圧VEXが伝達され、ノードND92の電圧レベルが、電圧VEXレベルとなる。また、容量素子C3のチャージポンプ動作により、MOSトランジスタNQ78のゲート電位が、4·VEXにまで上昇し、MOSトランジスタNQ78がオン状態となり、ノードND94から出力ノードND96へ電荷が転送され、出力ノードND96の電位レベルが上昇する。このとき、ポンプ制御信号ICLKの立ち下がりに従って、すでにMOSトランジスタNQ74のゲート電位は、ノードND92のゲート電位の電圧レベルと同じ電圧VEXレベルに設定されており、MOSトランジスタNQ74はオフ状態を維持する。 30

【0202】

次いで、メインポンプ制御信号CLKEXの立ち上がりに応答して、ポンプ制御信号CLKGがLレベルに立下ると、容量素子C1およびC3により、MOSトランジスタNQ70およびNQ78のゲート電位が電圧VEXだけ低下し、MOSトランジスタNQ70およびNQ78がオフ状態となる。 40

【0203】

また、ほぼ同一のタイミングでポンプ制御信号ICLKがHレベルに立ち上がり、ノードND92の電位が上昇し、MOSトランジスタNQ70のゲート電位がMOSトランジスタNQ72により外部電源電圧VEXレベルに設定され、MOSトランジスタNQ70は、確実にオフ状態に設定される。 50

【0204】

また、MOSトランジスタNQ76がオン状態であり、MOSトランジスタNQ76を介してMOSトランジスタNQ74のゲート電位が電圧2·VEXとなる。この状態にお

いても、まだMOSトランジスタNQ74は、ゲートおよびソース電位が同じであり、オフ状態を維持する。

【0205】

したがって、この期間Aにおいて、MOSトランジスタNQ70およびNQ78を介して電荷の転送が行われ、正電荷がノードND90からノードND92へ転送され、またノードND94から出力ノードND96へ正電荷が伝達される。

【0206】

次いで、ポンプ制御信号CLKPがLレベルに低下し、ノードND94の電圧レベルが低下し、MOSトランジスタNQ76がオフ状態となる。このノードND94の電位低下に従って、MOSトランジスタNQ80により、MOSトランジスタNQ78のゲート電位は、先のポンプ制御信号CLKGの立下がりにより低下した電圧3·VEXを維持し、MOSトランジスタNQ78はオフ状態を維持する。

10

【0207】

次いで、ポンプ制御信号ICLKがLレベルからHレベルに立上がると、容量素子C2のチャージャポンプ動作により、MOSトランジスタNQ74のゲート電位が電圧2·VEXから3·VEXの電圧レベルに上昇し、MOSトランジスタNQ74が導通し、ノードND92の電圧2·VEXを、ノードND94へ伝達し、ノードND94の電圧レベルが、2·VEXレベルとなる。これにより、ノードND94が確実に、電圧2·VEXレベルにプリチャージされる。

【0208】

次いで、ポンプ制御信号ICLKがLレベルに立ち下がり、また、ポンプ制御信号CLKPがHレベルとなると、MOSトランジスタNQ74のゲート電位が、容量素子C2のチャージポンプ動作により電圧2·VEXとなり、また、MOSトランジスタNQ78のゲート電位が、MOSトランジスタNQ80によりノードND94と同一の電圧3·VEXとなる。

20

【0209】

従って、この期間Bにおいて、内部で、MOSトランジスタNQ74を介してノードND92からノードND94への電荷の転送が行われる。

【0210】

以降、この動作を繰返すことにより、ノードND90からノードND92への電荷転送とノードND94からノードND96への電荷転送と、ノードND92からノードND94への電荷転送とが交互に行なわれる。これにより、ノードND94の電圧レベルが、電圧2·VEXと3·VEXの間で変化し、ノードND96からの電圧VBSTとして、最大3·VEXの電圧を生成することができる。さらに高い電圧が必要な場合には、この交互に電荷転送を行なう電荷転送段の段数を増加させる。

30

【0211】

この昇圧ポンプ回路110のポンプ動作を、ポンプ制御信号に従って選択的に活性化することにより、ワード線ベリファイ電圧VBSTの電圧レベルを所定電圧レベルに（基準電圧VREFレベル）に設定することができる。

【0212】

なお、このベリファイ電圧は、多値データの各データに対して同一電圧レベルに設定され、ベリファイ参照セルまたはベリファイ参照電流を各データに対応して変化させて、ベリファイ動作が行われても良い。また、これに代えて、ベリファイ参照電流レベルは同一として、各データに対応してベリファイ電圧レベルが変更されてベリファイ動作が行われても良い。また、実施の形態4と組合せて用いられても良い。

40

【0213】

以上のように、この発明の実施の形態6に従えば、ベリファイ動作時のワード線ベリファイ電圧を、その絶対値を変化させることなく温度依存性を持たせており、メモリセルとベリファイ参照セルの特性が異なる場合においても、ベリファイ参照セルとメモリセルの駆動電流とゲート電圧との関係の温度依存性を補償して、正確に、参照セル電流とメモリ

セル電流とを一致させることができ、応じてしきい値電圧分布を調整することができる。

【産業上の利用可能性】

【0214】

この発明は、参照セルとメモリセルの駆動電流を差動増幅する電流センス型の読出回路を備える2値以上のデータを記憶する不揮発性半導体記憶装置に対して適用することができる。

【図面の簡単な説明】

【0215】

【図1】この発明に従う不揮発性半導体記憶装置の全体の構成を概略的に示す図である。

10

【図2】図1に示す読出回路に含まれるセンスアンプの構成の一例を示す図である。

【図3】図2に示すセンスアンプの動作を示すタイミング図である。

【図4】図2に示すセンスアンプに含まれるPチャネルMOSトランジスタの断面構造を概略的に示す図である。

【図5】図1に示す読出回路に含まれるセンスアンプの変更例を示す図である。

【図6】この発明の実施の形態2に従う内部電圧発生回路の構成を概略的に示す図である。

【図7】図6に示す内部電圧発生回路の発生電圧の制御変化範囲を概略的に示す図である。

【図8】図6に示すポンプ回路の構成を概略的に示す図である。

20

【図9】図6に示すVDC回路の構成の位置例を概略的に示す図である。

【図10】図6に示す低電圧指示信号を発生する部分の構成の一例を概略的に示す図である。

【図11】この発明の実施の形態3に従う不揮発性半導体記憶装置の要部の構成を概略的に示す図である。

【図12】この発明の実施の形態3におけるメモリセル電流の分布を概略的に示す図である。

【図13】図11に示すセンスアンプのセンス動作を示すタイミング図である。

【図14】図11に示すセンスノードの電流経路を概略的に示す図である。

【図15】この発明の実施の形態4に従う不揮発性半導体記憶装置のメモリセルのしきい値電圧分布を概略的に示す図である。

30

【図16】この発明の実施の形態4に従う不揮発性半導体記憶装置のベリファイ動作時のゲート電圧印加態様を概略的に示す図である。

【図17】図16に示す電流分布の下限領域のメモリセルの駆動電流分布の変化を模式的に示す図である。

【図18】図16に示す電流分布の上限領域のメモリセルのベリファイ動作時のメモリセル駆動電流分布の変化を概略的に示す図である。

【図19】この発明の実施の形態4に従う不揮発性半導体装置のベリファイ動作時の動作を示すフロー図である。

【図20】この発明の実施の形態5に従う不揮発性半導体記憶装置の要部の構成を概略的に示す図である。

40

【図21】図20に示す定電流源カレントミラー段の構成の一例を示す図である。

【図22】この発明の実施の形態6に従う不揮発性半導体記憶装置のベリファイ参照セルおよびメモリセルのベリファイ時の接続を概略的に示す図である。

【図23】この発明の実施の形態6におけるメモリセルのしきい値電圧の変化を概略的に示す図である。

【図24】この発明の実施の形態6におけるメモリセルとベリファイ参照セルのVg - Id特性を概略的に示す図である。

【図25】この発明の実施の形態6におけるメモリセルおよびベリファイ参照セルのId - Vgの高温時の特性を示す図である。

【図26】この発明の実施の形態6におけるベリファイ電圧発生部の構成を概略的に示す

50

図である。

【図27】図26に示すV R E F発生回路の構成の一例を示す図である。

【図28】図26に示す分圧回路の構成の一例を示す図である。

【図29】図26に示すレベル検出回路の構成の位置例を示す図である。

【図30】図26に示すポンプ回路に含まれるポンプ制御信号発生部の構成を示す図である。

【図31】図30に示すポンプ制御信号発生回路の動作を示すタイミング図である。

【図32】図26に示すポンプ回路に含まれる昇圧ポンプ回路の構成の一例を示す図である。

【図33】図32に示す昇圧分布回路の動作を示すタイミング図である。

10

#### 【符号の説明】

##### 【0216】

1 メモリセルアレイ、2 行選択駆動回路、3 列選択回路、4 読出回路、5 制御回路、6 内部電圧発生回路、P Q 1 - P Q 5 PチャネルMOSトランジスタ、N Q 1 - N Q 4 NチャネルMOSトランジスタ、N M C メモリセル、R M C 参照セル、7 A 半導体基板領域、7 B , 7 C 不純物領域、8 ゲート電極、9 A P型不純物導通層、9 B 埋込チャネル、P Q 1 0 - P Q 1 3 PチャネルMOSトランジスタ、N Q 1 0 , N Q 1 1 NチャネルMOSトランジスタ、1 1 ポンプ回路、1 3 スタンバイポンプ回路、1 5 V D C 回路、1 7 スタンバイV D C 回路、1 8 , 1 9 転送ゲート、2 0 a - 2 0 n チャージャポンプ、2 1 レベル検出回路、2 2 クロック発生回路、2 3 デカップル容量、2 5 比較回路、2 6 電流ドライブトランジスタ、2 7 デカップル容量、4 0 センスアンプ、4 2 Y選択ゲート、4 3 メモリセルアレイ、4 4 参照セル選択ゲート、4 5 参照セルアレイ、N M C 0 - N M C n メモリセル、R M C 1 - R M C 3 参照セル、T X 2 CMOSトランスマッショングート、5 0 低電圧発生回路、Q R , Q N NチャネルMOSトランジスタ、S Q N , S Q R 転送ゲート、6 0 センスアンプ、V M C ベリファイ参照セル、7 0 コントローラ、7 2 V R E F 発生回路、7 4 レベル検出回路、7 6 ポンプ回路、7 8 分圧回路、8 0 低電圧発生回路、8 2 定電流源、R R , R 0 - R n 抵抗素子、8 3 バイポーラトランジスタ、Q Q 0 - Q Q n NチャネルMOSトランジスタ、Z Z 0 - Z A m 抵抗素子。 20

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【 図 25 】

【 図 2 6 】

【 図 27 】

【 図 2 8 】

【 図 29 】

【 図 3 0 】

【図3-1】

【図3-2】

【図3-3】

---

フロントページの続き

(72)発明者 久保 貴志

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 伊藤 孝

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 柏崎 泰宏

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 小倉 卓

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 古谷 清広

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5B125 BA01 BA19 CA03 DB08 EE00 EG06 EG16 EH01 FA01 FA02

FA05