(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7263019号**

**(P7263019)**

(45)発行日 令和5年4月24日(2023.4.24)

(24)登録日 令和5年4月14日(2023.4.14)

(51)国際特許分類

|         |                 |         |       |   |

|---------|-----------------|---------|-------|---|

| G 0 1 R | 19/00 (2006.01) | G 0 1 R | 19/00 | M |

| G 0 1 R | 19/32 (2006.01) | G 0 1 R | 19/32 |   |

| G 0 3 G | 15/22 (2006.01) | G 0 1 R | 19/00 | A |

| G 0 1 R | 35/00 (2006.01) | G 0 3 G | 15/22 |   |

|         |                 | G 0 1 R | 35/00 | E |

請求項の数 18 (全24頁)

(21)出願番号 特願2019-4385(P2019-4385)

(22)出願日 平成31年1月15日(2019.1.15)

(65)公開番号 特開2020-112476(P2020-112476)

A)

(43)公開日 令和2年7月27日(2020.7.27)

審査請求日 令和4年1月6日(2022.1.6)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100123559

弁理士 梶 俊和

(74)代理人 100177437

弁理士 中村 英子

(72)発明者 小嶋 敬造

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

審査官 永井 皓喜

最終頁に続く

(54)【発明の名称】 電圧検知装置及び画像形成装置

**(57)【特許請求の範囲】****【請求項1】**

1次側と2次側とが絶縁され、前記1次側において流れた電流に応じた電圧を前記2次側において出力する伝達手段と、

所定の直流電圧を出力する基準電源と、

検知の対象となる交流電源の交流電圧を出力する電圧出力手段と、

前記伝達手段の前記1次側に、前記基準電源から前記所定の直流電圧を供給する第1の状態と、前記電圧出力手段から出力された前記検知の対象となる交流電源の交流電圧を供給する第2の状態と、の間で切り替わる切替手段と、

前記伝達手段の前記2次側に設けられ、前記切替手段を前記第1の状態に切り替えて前記伝達手段より出力された電圧から補正值を取得し、前記切替手段を前記第2の状態に切り替えて前記伝達手段より出力された電圧から検知値を取得し、前記検知値を前記補正值により補正し、前記検知の対象となる交流電源の交流電圧を取得する制御手段と、を備えることを特徴とする電圧検知装置。

**【請求項2】**

前記2次側に設けられ、前記伝達手段から出力された電圧のアナログ値をデジタル値に変換するアナログ - デジタル変換手段を備え、

前記制御手段は、アナログ - デジタル変換手段により変換されたデジタル値に基づいて前記伝達手段から出力された電圧の情報を取得することを特徴とする請求項1に記載の電圧検知装置。

**【請求項 3】**

前記切替手段は、前記伝達手段に前記交流電圧を供給するときに接続状態となり、前記伝達手段への前記交流電圧の供給を遮断するときに非接続状態となる第1の接続手段と、前記伝達手段に前記基準電源の前記所定の電圧を供給するときに接続状態となり、前記伝達手段への前記所定の電圧の供給を遮断するときに非接続状態となる第2の接続手段と、を有し、

前記制御手段は、前記第1の接続手段を非接続状態及び前記第2の接続手段を接続状態とすることにより前記第1の状態とし、前記第1の接続手段を接続状態及び前記第2の接続手段を非接続状態とすることにより前記第2の状態とすることを特徴とする請求項2に記載の電圧検知装置。

10

**【請求項 4】**

前記制御手段は、前記第1の状態において、前記所定の電圧に応じたデジタル値に基づいて、前記伝達手段により出力された電圧に応じたデジタル値を補正するための前記補正值を求め、前記第2の状態において、前記伝達手段により出力された電圧に応じたデジタル値に基づき検知した電圧を前記補正值により補正することを特徴とする請求項3に記載の電圧検知装置。

**【請求項 5】**

前記制御手段は、前記第2の状態において前記アナログ - デジタル変換手段から出力される複数のデジタル値を取得し、前記複数のデジタル値のうちのピーク値を用いて前記交流電圧の値を取得することを特徴とする請求項3又は請求項4に記載の電圧検知装置。

20

**【請求項 6】**

前記基準電源及び前記電圧出力手段は、前記第1の状態において前記アナログ - デジタル変換手段から出力されたデジタル値と、前記交流電圧が所定値のときに前記アナログ - デジタル変換手段から出力されたデジタル値とが略等しくなるように設定されることを特徴とする請求項3から請求項5のいずれか1項に記載の電圧検知装置。

**【請求項 7】**

前記交流電圧を半波整流する整流手段を備え、

前記伝達手段は、前記整流手段により半波整流された電圧が入力されることを特徴とする請求項3から請求項6のいずれか1項に記載の電圧検知装置。

**【請求項 8】**

30

前記交流電圧を全波整流する整流手段を備え、

前記伝達手段は、前記整流手段により全波整流された電圧が入力されることを特徴とする請求項3から請求項5のいずれか1項に記載の電圧検知装置。

**【請求項 9】**

前記伝達手段の前記2次側に接続され、抵抗値を調整することが可能な抵抗素子を備え、

前記制御手段は、前記第1の状態において前記アナログ - デジタル変換手段が出力したデジタル値と目標値との差である前記補正值が小さくなるように、前記第2の状態において前記抵抗素子の抵抗値を調整することを特徴とする請求項8に記載の電圧検知装置。

**【請求項 10】**

前記目標値は、前記第1の状態において前記アナログ - デジタル変換手段から出力されたデジタル値と、前記交流電圧の値が所定値のときに前記アナログ - デジタル変換手段から出力されたデジタル値とが略等しくなるように設定されることを特徴とする請求項9に記載の電圧検知装置。

40

**【請求項 11】**

ハイレベル又はローレベルのゼロクロス信号を出力するゼロクロス回路と、

前記伝達手段の前記2次側に接続され、抵抗値を調整することが可能な抵抗素子と、

を備え、

前記切替手段は、前記ゼロクロス回路であり、前記ゼロクロス信号がハイレベルのときに前記第1の状態に切り替わり、前記ゼロクロス信号がローレベルのときに前記第2の状態に切り替わることを特徴とする請求項2に記載の電圧検知装置。

50

**【請求項 1 2】**

前記制御手段は、前記第1の状態において前記アナログ - デジタル変換手段から出力されたデジタル値と目標値との差である前記補正值が小さくなるように、前記第2の状態において前記抵抗素子の抵抗値を調整することを特徴とする請求項11に記載の電圧検知装置。

**【請求項 1 3】**

前記制御手段は、前記抵抗素子の抵抗値を調整することにより前記第1の状態において前記アナログ - デジタル変換手段から出力されたデジタル値と前記目標値との差が所定の範囲内となった後に、前記第2の状態において得られたデジタル値に基づいて、前記交流電圧の実効値を求ることにより前記交流電圧の値を取得することを特徴とする請求項12に記載の電圧検知装置。

10

**【請求項 1 4】**

前記目標値は、前記第1の状態において前記アナログ - デジタル変換手段から出力されたデジタル値と、前記交流電圧の値が所定値のときに前記アナログ - デジタル変換手段から出力されたデジタル値とが略等しくなるように設定されることを特徴とする請求項13に記載の電圧検知装置。

**【請求項 1 5】**

前記伝達手段は、フォトカプラであることを特徴とする請求項1から請求項1 4のいずれか1項に記載の電圧検知装置。

20

**【請求項 1 6】**

前記伝達手段は、トランスであることを特徴とする請求項1から請求項1 4のいずれか1項に記載の電圧検知装置。

**【請求項 1 7】**

請求項1から請求項1 6のいずれか1項に記載の電圧検知装置と、

未定着のトナー像を形成する画像形成手段と、

未定着のトナー像を定着する定着手段と、

を備えることを特徴とする画像形成装置。

**【請求項 1 8】**

請求項3から請求項14のいずれか1項に記載の電圧検知装置と、

未定着のトナー像を形成する画像形成手段と、

未定着のトナー像を定着する定着手段と、

前記電圧検知装置により検知した前記交流電圧に基づいて、前記定着手段に供給する電力を決定する前記制御手段と、

を備えることを特徴とする画像形成装置。

30

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、電圧検知装置及び画像形成装置に関し、絶縁された2極間の伝達を目的とした電圧検知装置に関する。

40

**【背景技術】****【0 0 0 2】**

従来、絶縁された1次2次間に於いて、一方のアナログ電圧情報を他方へ伝達する回路は多く利用されている。例えば、交流電源が接続される加熱定着器を備えた画像形成装置では、交流電源からの入力電圧値を検知し、加熱定着器の制御に利用している。例えば、加熱定着器の立ち上げ時に投入される電力は、検知した入力電圧値及び定着処理の目標温度に応じて、予め設定したデューティにより決定される。これにより、オーバーシュートや電力不足のない制御を行ったり、異常な電圧が入力されたときには装置の動作を停止させたりしている。例えば、特許文献1では、交流電源の交流電圧からフォトカプラを用いて生成したゼロクロス信号に基づいて交流電源の交流電圧を検知している。従来の電源電圧検知装置は、ゼロクロス信号の直流成分から直流電圧を生成することで、交流電源の入

50

力電圧値を検知する。こうすることで、交流電源の入力電圧値にサグ、ノイズ等の電圧異常があった場合でも入力電圧を検知できるようにしている。

#### 【0003】

近年は、多くの国や地域で電子機器が使用されており、国や地域によって交流電源の条件も様々である。例えば、高周波のノイズが重畠する場合や、ラインインピーダンスが高く、負荷電流の変動時に電圧ドロップが発生する場合等がある。このように、電源電圧が歪むと、加熱定着器に投入される電力に過不足が発生し、画像品質の低下を招くおそれがある。このため、交流電源の電圧検知装置としても、上述したような種々の条件下でより正確な電圧情報を検知することが求められている。また、交流電源の入力電圧値の電圧検知装置以外でも、1次側のアナログ電圧情報（以下、1次電圧情報という）を2次側へ伝達するケースは存在する。例えば、特許文献2に示されるような温度検知装置である。このような温度検知装置は、1次側の発熱体と2次側の温度検知体が混在してなる従来の加熱装置に対し、温度検知体を1次側で構成することで加熱装置内の安全上の距離を取る必要をなくし、小型化を図ったものである。この温度検知装置では、1次2次間の伝達は光信号を用いて行われている。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【文献】特開2013-217843号公報

特開平11-344882号公報

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、上述した従来の絶縁された1次2次間の伝達構成では、1次2次の伝達率（電流伝達率（Current Transfer Ratio）、以下、CTRとする）の影響を大きく受ける。CTRが温度条件や経時条件等によって大きく変わると、同じ1次電圧情報であっても2次側で変換され得られる電圧も大きく変わってしまう。更にフォトカプラを用いてゼロクロス信号を生成する構成では、交流電源の交流電圧のサグ、ノイズ等によって、ゼロクロス信号にも本来のゼロクロスとは異なるタイミングでパルスが発生する。そして、ゼロクロス信号の直流成分から生成される直流電圧は本来よりも低くなる。そのため、実際の交流電源電圧と検出された電源電圧との間に誤差が生じてしまう。

30

#### 【0006】

本発明は、このような状況のもとでなされたもので、温度変化や経年変化の影響を受けず、精度よく電圧検知を行うことを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

上述した課題を解決するために、本発明は、以下の構成を備える。

#### 【0008】

(1) 1次側と2次側とが絶縁され、前記1次側において流れた電流に応じた電圧を前記2次側において出力する伝達手段と、所定の直流電圧を出力する基準電源と、検知の対象となる交流電源の交流電圧を出力する電圧出力手段と、前記伝達手段の前記1次側に、前記基準電源から前記所定の直流電圧を供給する第1の状態と、前記電圧出力手段から出力された前記検知の対象となる交流電源の交流電圧を供給する第2の状態と、の間で切り替わる切替手段と、前記伝達手段の前記2次側に設けられ、前記切替手段を前記第1の状態に切り替えて前記伝達手段より出力された電圧から補正値を取得し、前記切替手段を前記第2の状態に切り替えて前記伝達手段より出力された電圧から検知値を取得し、前記検知値を前記補正値により補正し、前記検知の対象となる交流電源の交流電圧を取得する制御手段と、を備えることを特徴とする電圧検知装置。

40

#### 【0009】

(2) 前記(1)に記載の電圧検知装置と、未定着のトナー像を形成する画像形成手段

50

と、未定着のトナー像を定着する定着手段と、を備えることを特徴とする画像形成装置。

【発明の効果】

【0010】

本発明によれば、温度変化や経年変化の影響を受けず、精度よく電圧検知を行うことができる。

【図面の簡単な説明】

【0011】

【図1】実施例1の電圧検知装置の回路構成図

【図2】実施例1の電圧検知装置の動作説明図

【図3】実施例1の演算値特性を示すグラフ

10

【図4】実施例1の補正係数を説明するグラフ

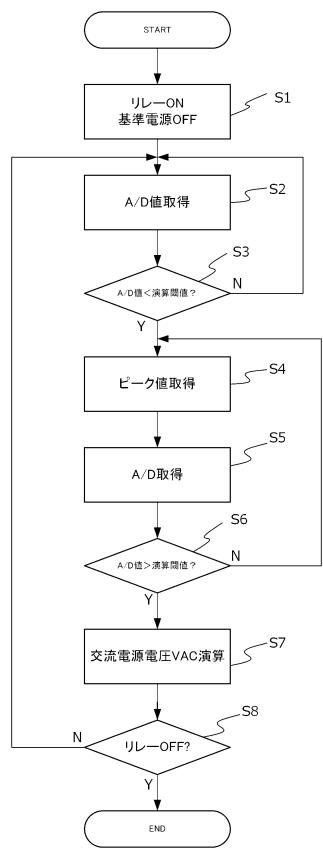

【図5】実施例1の交流電源電圧の演算処理を示すフロー チャート

【図6】実施例2の電圧検知装置の回路構成図

【図7】実施例2の電圧検知装置の動作説明図

【図8】実施例3の電圧検知装置の回路構成図

【図9】実施例3の電圧検知装置の動作説明図

【図10】実施例4の電圧検知装置の回路構成図

【図11】実施例4の電圧検知装置の動作説明図

【図12】実施例4の演算値特性を示すグラフ

【図13】実施例5の画像形成装置の構成を示す図

20

【発明を実施するための形態】

【0012】

上述した課題を解決するための本発明の具体的な構成について、以下の実施例に基づいて説明する。なお、以下に示す実施例は一例であって、この発明の技術的範囲をそれらのみに限定する趣旨のものではない。具体的には、本発明では交流電源の入力電圧を検知するために入力電圧を1次側のアナログ電圧情報（以下、1次電圧情報という）としているが、それに限定するものではない。例えば、サーミスタ等の温度検知素子によって温度を検知するために、サーミスタ等によって検知した温度に基づく電圧を1次電圧情報としてもよい。また、A C / D C コンバータが有するトランジスタの1次巻線に流れる1次電流を電圧に変換して1次電圧情報としてもよい。

30

【実施例1】

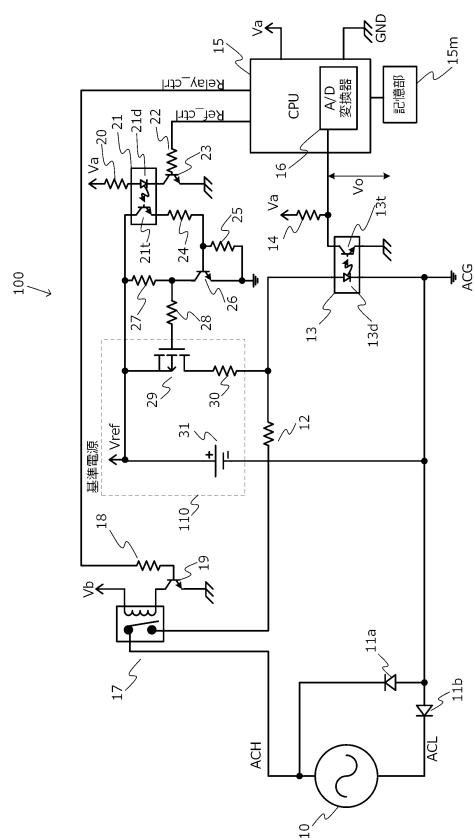

【0013】

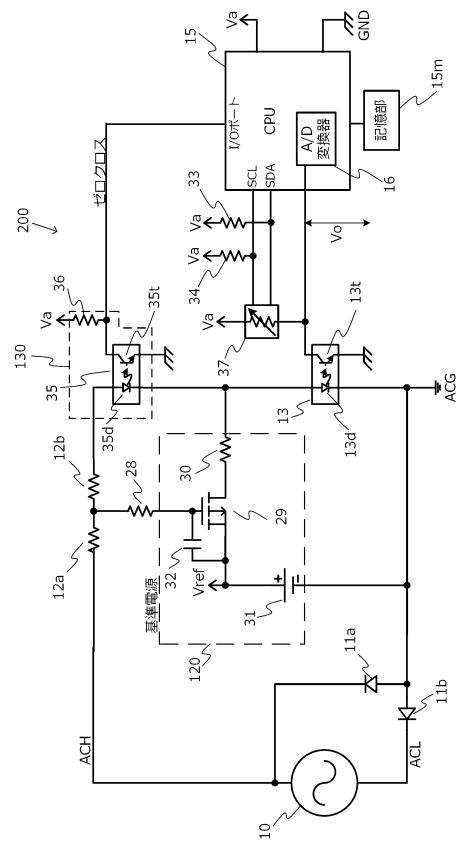

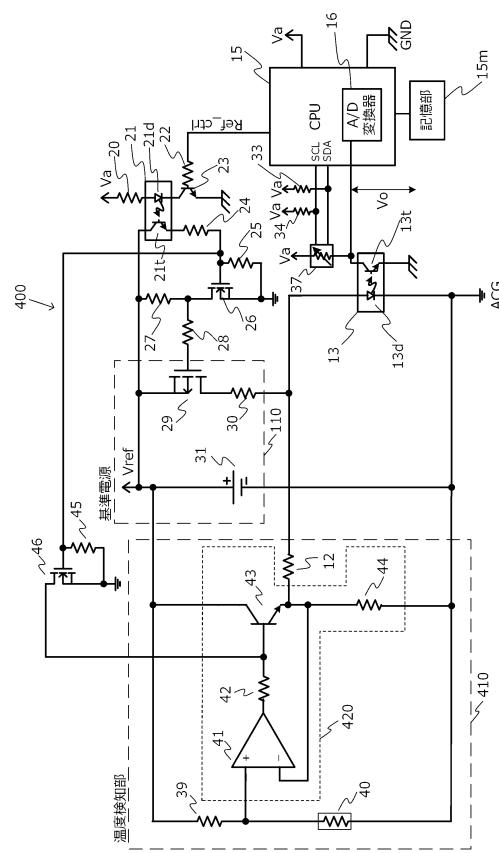

[電圧検知装置]

図1は実施例1の交流電源の入力電圧（以下、交流電源電圧という）を検知するための電圧検知装置の回路構成を説明する図である。実施例1の電圧検知装置100は、交流電源10を1次側の入力とし、絶縁素子であるフォトカプラ13によって2次側へ交流電源電圧の情報を伝達し、2次側に伝達された交流電源電圧の情報（電圧のアナログ値）をCPU15に入力する。フォトカプラ13は、1次側の情報を2次側に伝達する伝達手段として機能する。また、実施例1では、検知の対象は交流電源10の交流電圧である。制御手段であるCPU15は、入力された交流電源電圧の情報に基づいて交流電源電圧の値（以下、交流電源電圧値という）VACを演算している。また電圧検知装置100は、基準電源110とリレー17とを備える。基準電源110は、ダイオード11a、ダイオード11bによって整流された、電圧ACGを基準とした基準電圧31、電界効果トランジスタ（以下、FETと記す）29、抵抗30を有する。基準電圧31は、所定の電圧である基準電圧31をフォトカプラ13に供給するための電源である。ダイオード11a、11bは、交流電圧を半波整流する整流手段として機能する。

40

【0014】

第1の接続手段であるリレー17は、交流電源10からの電圧供給を接続・遮断するためのリレーである。リレー17は、フォトカプラ13に交流電圧を供給するときに接続状態となり、フォトカプラ13への交流電圧の供給を遮断するときに非接続状態となる。C

50

P U 1 5 は、電圧検知装置 1 0 0 が備える基準電源 1 1 0 及びリレー 1 7 のオン又はオフを制御している。また、C P U 1 5 は、記憶部 1 5 m から後述する換算テーブル等の情報を読み出したり、後述するピーク値の取得のために後述する A / D 値を記憶部 1 5 m に一時的に記憶したりする。

#### 【 0 0 1 5 】

交流電源 1 0 の一方のラインを A C H 、他方のラインを A C L とする。リレー 1 7 は、1 次側がライン A C H に接続されている。リレー 1 7 の 2 次側は、電源 V b とトランジスタ 1 9 に接続されている。トランジスタ 1 9 は、コレクタ端子にリレー 1 7 の 2 次側を介して電源 V b が接続され、ベース端子に抵抗 1 8 を介して C P U 1 5 が接続され、エミッタ端子は接地されている。フォトカプラ 1 3 の 1 次側のダイオード 1 3 d は、アノード側に抵抗 1 2 を介してリレー 1 7 の 1 次側が接続され、カソード側にダイオード 1 1 b を介してライン A C L が接続されている。抵抗 1 2 は、交流電源 1 0 からフォトカプラ 1 3 に流れる電流を制限するための抵抗である。フォトカプラ 1 3 の 2 次側のトランジスタ 1 3 t は、コレクタ端子に抵抗 1 4 を介して電源 V a が接続され、エミッタ端子が接地されている。トランジスタ 1 3 t のコレクタ端子は、C P U 1 5 が有するアナログ - デジタル（以下、A / D とする）変換器 1 6 にも接続されている。フォトカプラ 1 3 は、1 次側のダイオード 1 3 d に流れた電流を 2 次側で電圧に変換する電圧変換手段としても機能する。A / D 変換器 1 6 は、フォトカプラ 1 3 のトランジスタ 1 3 t から出力されたアナログの電圧（検知電圧 V o ）の値をデジタル値に変換するアナログ - デジタル変換手段として機能する。C P U 1 5 は、A / D 変換器 1 6 により変換されたデジタル値に基づいて交流電源 1 0 の交流電圧の値を取得する。10

#### 【 0 0 1 6 】

基準電源 1 1 0 と C P U 1 5 との間には、C P U 1 5 が基準電源 1 1 0 からフォトカプラ 1 3 への入力を接続したり遮断したりするための回路が設けられている。この回路は、フォトカプラ 2 1 を有し、フォトカプラ 2 1 の 1 次側のトランジスタ 2 1 t は、エミッタ端子に抵抗 2 4 を介してトランジスタ 2 6 のベース端子が接続されており、コレクタ端子には基準電圧 V r e f が接続されている。フォトカプラ 2 1 の 2 次側のダイオード 2 1 d は、アノード側に抵抗 2 0 を介して電源 V a が接続され、カソード側にトランジスタ 2 3 のコレクタ端子が接続されている。トランジスタ 2 3 は、ベース端子に抵抗 2 2 を介して C P U 1 5 が接続され、エミッタ端子は接地されている。トランジスタ 2 6 は、コレクタ端子に抵抗 2 7 を介して基準電圧 V r e f が接続され、エミッタ端子が接地されている。トランジスタ 2 6 のベース端子とエミッタ端子の間には抵抗 2 5 が接続されている。抵抗 2 7 とトランジスタ 2 6 のコレクタ端子との接続点には、抵抗 2 8 を介して F E T 2 9 のゲート端子が接続されている。20

#### 【 0 0 1 7 】

C P U 1 5 は、電源 V a によって動作している。C P U 1 5 は、トランジスタ 1 9 のベース端子にハイレベル（以下、H i とする）又はローレベル（以下、L o とする）の R e l a y \_ c t r 1 信号を出力することにより、リレー 1 7 の接続又は遮断を制御する。C P U 1 5 は、トランジスタ 2 3 のベース端子にハイレベル（以下、H i とする）又はローレベル（以下、L o とする）の R e f \_ c t r 1 信号を出力することにより、基準電源 1 1 0 のフォトカプラ 1 3 への入力又は非入力を制御する。30

#### 【 0 0 1 8 】

C P U 1 5 は、R e l a y \_ c t r 1 信号を L o とすることで、トランジスタ 1 9 をオフし、リレー 1 7 を遮断した状態とする。これにより、交流電源電圧がフォトカプラ 1 3 の 1 次側のダイオード 1 3 d に供給されなくなる。また、C P U 1 5 は、R e l a y \_ c t r 1 信号を H i とすることで、トランジスタ 1 9 をオンし、リレー 1 7 を接続した状態とする。これにより、交流電源電圧がフォトカプラ 1 3 の 1 次側のダイオード 1 3 d に供給される。

#### 【 0 0 1 9 】

C P U 1 5 は、R e f \_ c t r 1 信号を L o とすることで、トランジスタ 2 3 をオフし40

10

20

30

40

50

、フォトカプラ21を非導通状態とし、トランジスタ26をオフし、FET29をオフする。これにより電圧Vref（基準電圧31）がフォトカプラ13の1次側のダイオード13dに供給されなくなる。また、CPU15は、Ref\_cotr1信号をHiとして、トランジスタ23をオンし、フォトカプラ21を導通状態とし、トランジスタ26をオンし、FET29をオンする。これにより電圧Vref（基準電圧31）がフォトカプラ13の1次側のダイオード13dに供給される。

#### 【0020】

FET29は、フォトカプラ13への基準電源110の電圧の供給を接続又は遮断する第2の接続手段として機能する。FET29は、フォトカプラ13に基準電源110の電圧を供給するときに接続状態となり、フォトカプラ13への基準電源110の電圧の供給を遮断するときに非接続状態となる。なお、リレー17（第1の接続手段）とFET29（第2の接続手段）とは、フォトカプラ13の1次側に、基準電源110から電圧を供給する第1の状態と、交流電源10から交流電圧を供給する第2の状態とを切り替える切替手段として機能する。検知電圧Voについては後述する。

10

#### 【0021】

##### [電圧検知装置の動作]

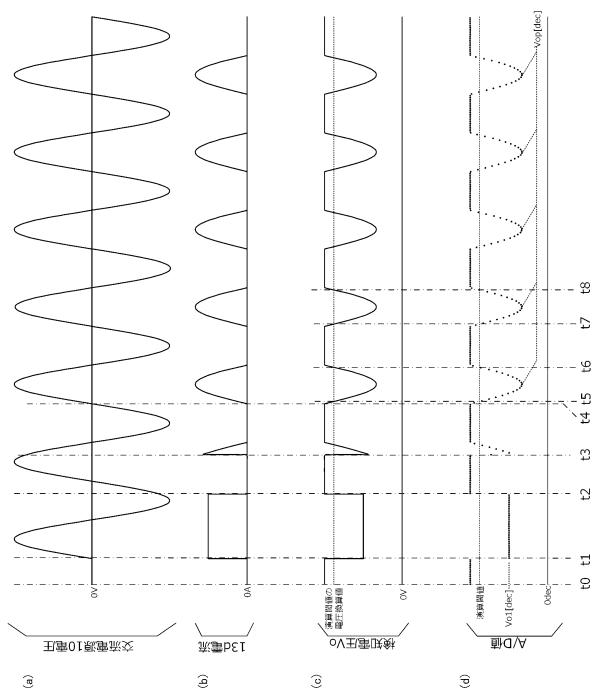

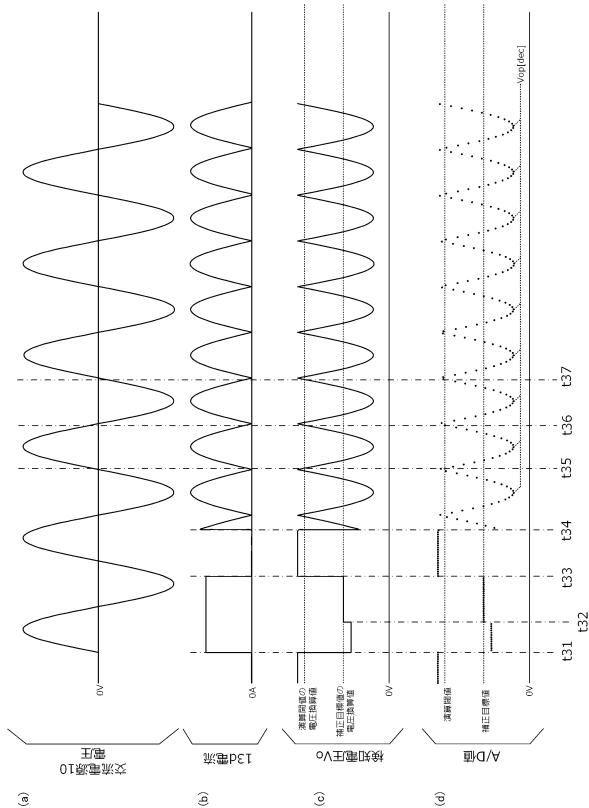

図2は図1の電圧検知装置100の各部動作を説明する図である。図2は、(a)に交流電源10の電圧(交流電源電圧)の波形を示し、(b)にフォトカプラ13の1次側のダイオード13dに流れる電流の波形を示す。(c)はCPU15に入力される電圧(デジタル値に変換される前の電圧)(以下、検知電圧という)Voの波形を示す。なお、点線は、A/D変換器16の演算閾値を電圧に換算した値(電圧換算値)を示す。(d)はCPU15のA/D変換器16によって検知電圧Voをデジタル値に変換した後の値(以下、A/D値という)(単位:dec)を示す。なお、点線は、演算閾値と後述する検知電圧Vo1とを示す。横軸はいずれも時間を示す。

20

#### 【0022】

以下、図1の電圧検知装置100の動作詳細について、図2を用いて説明する。時刻t0は、1次側の情報が2次側に伝達されていない初期状態である。この初期状態では、フォトカプラ13のダイオード13dに交流電源10及び基準電源110のどちらからも電流が供給されない。そのためCPU15は、トランジスタ19がオフとなり、リレー17がオープン状態(遮断状態)となるように、Relay\_cotr1信号をLoとする。また、時刻t0では、トランジスタ23がオフとなり、FET29がオフとなるようにRef\_cotr1信号をLoとしている。これによりフォトカプラ13のダイオード13dには電流が流れず、2次側の出力である検知電圧Voはハイレベル(Va)となる。したがって、時刻t0において、A/D変換器16の出力であるA/D値は、仮にA/D変換器16の分解能が10ビットであれば、上限値の1023又は1023に近い値となる。

30

#### 【0023】

時刻t1で、CPU15は基準電源110からの電流がフォトカプラ13のダイオード13dに流れるように制御する。具体的には、CPU15は、Relay\_cotr1信号をLoとしリレー17を遮断し、Ref\_cotr1信号をHiとしてFET29をオンし電圧Vref(基準電圧31)がフォトカプラ13に供給されるようにする。2次側では、ダイオード13dの発光を受けて、フォトカプラ13のトランジスタ13tにコレクタ電流が流れる。実施例1では、このコレクタ電流と、電源Va、抵抗14によって検知電圧Voが定まる。しかしながら、ダイオード13dに流れる電流値が同じであっても、トランジスタ13tに流れるコレクタ電流は、フォトカプラ13の経年変化や使用される温度環境等の影響を受け変動する。このため、検知電圧Voは大きくばらついてしまう。そのため、電圧検知装置100の温度特性及び経年変化によるばらつきの補正が必要となる。

40

#### 【0024】

実施例1では、時刻t1～t2の期間は、電圧検知装置100の温度特性及び経年変化による検知電圧Voのばらつきを補正する補正期間である。時刻t1～t2でCPU15は、入力された検知電圧VoをA/D変換器16によってA/D値に変換する。CPU1

50

5は、A/D変換器16によって変換されたA/D値に基づいて、交流電源電圧値を検知する。以下、CPU15が検知電圧V<sub>o</sub>をA/D変換器16によりA/D値に変換することを、検知電圧V<sub>o</sub>を読み取る、と表現し、得られたA/D値を、読み取ったA/D値、と表現する。なお、実施例1では、時刻t<sub>1</sub>～t<sub>2</sub>の補正期間に得られたA/D値と、交流電源10の電圧が110V（所定値）のときのA/D値とが等しくなるように設定されている。

#### 【0025】

ここで、CPU15がRelay\_ctrl1信号をL<sub>o</sub>、Ref\_ctrl1信号をH<sub>i</sub>とし、基準電源110からダイオード13dに流れる電流をI<sub>ref</sub>とする。また、CPU15がRelay\_ctrl1信号をH<sub>i</sub>、Ref\_ctrl1信号をL<sub>o</sub>とし、交流電源10からダイオード13dに流れるピーク電流をI<sub>ac</sub>とする。このとき、電流I<sub>ref</sub>と電流I<sub>ac</sub>とが等しくなるように設定している。また、ダイオード（11a、11b、13d）の順方向電圧、FET29のオン抵抗による電圧ドロップ等、その他抵抗成分を無視したとする。そうすると、これら電流の調整は、基準電源110の基準電圧31と抵抗30、及び抵抗12を（1）式の関係にすることで実現できる。なお（1）式では、基準電圧31をV<sub>31</sub>、抵抗30をR<sub>30</sub>、抵抗12をR<sub>12</sub>としている。

#### 【数1】

$$I_{ac} = 110\sqrt{2}/R_{12} = I_{ref} = V_{31}/R_{30} \cdots \cdots (1)$$

10

20

#### 【0026】

このようにして、予め定めた特定の交流電源電圧値に対して（1）式が成り立つようにすることで、電圧検知装置100の温度特性及び経年変化による検知ばらつきを補正することが可能となる。図2では、（1）式が成り立つ際のA/D値をV<sub>o1</sub>[dec]としA/D値の図に点線で示している。

#### 【0027】

##### [補正方法]

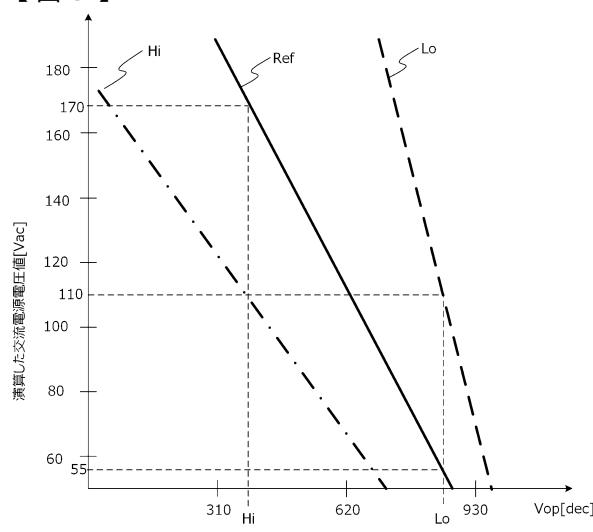

ここで実施例1における、電圧検知装置100の温度特性及び経年変化による検知ばらつきの補正を伴う交流電源電圧値V<sub>AC</sub>の演算の補正方法を図3、図4を用いて説明する。ここで、補正前の交流電源電圧値をV<sub>ac</sub>と表記し、補正後の交流電源電圧値をV<sub>AC</sub>と表記する。図3はA/D値から交流電源電圧値V<sub>ac</sub>に換算するためのテーブルをグラフ化したものである。図3に示すグラフの横軸V<sub>op</sub>[dec]は、連続的に検知電圧V<sub>o</sub>を読み取ったA/D値のピーク値であり、図2(d)のA/D値に示すV<sub>op</sub>[dec]である。ピーク値V<sub>op</sub>[dec]の演算方法は後述する時刻t<sub>5</sub>～t<sub>6</sub>の説明内で述べる。また、CPU15は、図3に示す実線で示された基準となる換算テーブル(R<sub>ef</sub>)のみを記憶部15mに記憶している。図3に示すそのほかの破線(L<sub>o</sub>)や一点鎖線(H<sub>i</sub>)で示すテーブルは、A/D変換器16で読み取ったA/D値と、後述する図4の補正値である補正係数に基づき求められる。このため、L<sub>o</sub>とH<sub>i</sub>に示すテーブルは記憶部15mには予め記憶されていない。なお、図3では、説明を簡略化するため、基準となる換算テーブルと等しい伝達特性をR<sub>ef</sub>とし、フォトカプラ13の伝達効率が基準となる伝達効率よりも低下した場合をL<sub>o</sub>とし、伝達効率が基準となる伝達効率よりも高い場合をH<sub>i</sub>として示している。

30

40

#### 【0028】

図4は、交流電源電圧値V<sub>ac</sub>からばらつき補正後の交流電源電圧値V<sub>AC</sub>を算出するための補正係数をグラフ化したものである。図4は、横軸には補正期間に検知電圧V<sub>o</sub>を読み取ったA/D値であるV<sub>oc</sub>を示し、縦軸に補正係数を示す。図4は、図3に示すR<sub>ef</sub>の換算テーブルから求めた交流電源電圧値V<sub>ac</sub>から、L<sub>o</sub>やH<sub>i</sub>といった伝達効率

50

の異なる場合の交流電源電圧値  $V_{ac}$  を求めるための補正係数を示している。なお、図4にも図3と同じく  $R_{ef}$ 、 $L_o$ 、 $H_i$  を記載している。以下、 $R_{ef}$  の換算テーブルを  $R_{ef}$  換算テーブルという。

#### 【0029】

上述したように、補正期間  $t_1 \sim t_2$  では(1)式が成り立っている。しかしながら、フォトカプラ13による1次2次間の伝達効率が、使用が進んだことや温度環境によって変化する。このため、(1)式が成り立つ補正期間であっても、検知電圧  $V_o$  及び検知電圧  $V_o$  を変換した A/D 値は必ずしも一定ではない。そのため CPU15 は、補正期間に読み取った A/D 値である  $V_{oc} [dec]$  が、110V $ac$  のピーク電圧に相当するとして、次のように補正を行う。

10

#### 【0030】

まず、図4の補正係数は、基準電源110からの電流  $I_{ref}$  がフォトカプラ13のダイオード13dに流れる期間、すなわち、図2における時刻  $t_1 \sim t_2$  の補正期間に求められる。具体的には、CPU15は、図2の時刻  $t_1 \sim t_2$  の補正期間に読み取った A/D 値である  $V_{oc} [dec]$  から図4に示す補正係数を求める。補正係数は、基準となる伝達効率の場合、すなわち  $V_{oc}$  が  $V_o 1$  のときに 1 となるように設定されている。このときの A/D 値  $V_{oc}$  を図4では  $R_{ef}$  としている。また、例えば、補正期間に読み取った A/D 値である  $V_{oc}$  が A/D 値  $H_i$  であった場合には補正係数は 0.65 となり、補正期間に読み取った A/D 値である  $V_{oc}$  が A/D 値  $L_o$  であった場合には補正係数は 2.0 となる。

20

#### 【0031】

補正期間に読み取った A/D 値  $V_{oc}$  と図4とから求めた補正係数を  $Z$  とする。また、ピーク値  $V_{op}$  と図3の  $R_{ef}$  換算テーブルとから補正前の交流電源電圧  $V_{ac}$  が求められる。求めた交流電源電圧値  $V_{ac}$  が、(2)式のような1次式で表わされるとき、補正後の交流電源電圧値  $VAC$  は(3)式となる。

#### 【数2】

$$V_{ac} = a \times V_{op}[dec] + b \cdots (2)$$

$V_{op}[dec]$ :連続的に読み取った A/D 値のピーク値

30

$$VAC = V_{ac} \times Z \cdots \cdots (3)$$

#### 【0032】

例えば、図2の時刻  $t_1 \sim t_2$  の補正期間に、CPU15が読み取った A/D 値  $V_{oc} [dec]$  が、 $L_o$  であったとする。CPU15は、図4から、補正係数  $Z$  として“2.0”を取得する。そして、CPU15は、図3の  $R_{ef}$  換算テーブルから、A/D 値  $V_{op}$  が  $L_o$  となる交流電源電圧値  $V_{ac}$  を求める。この場合、CPU15は、交流電源電圧  $V_{ac}$  として 55V $ac$  を取得する。実際には、交流電源 10 の電圧値は 110V であるが、フォトカプラ13の伝達効率の変化によって検知電圧  $V_o$  のばらつきが生じている。CPU15は、(3)式の交流電源電圧値  $V_{ac}$  に 55V $ac$  を代入し、補正係数  $Z$  に 2.0 を代入して、補正後の交流電源電圧値  $VAC$  として 110V $ac$  を算出する。これにより、フォトカプラ13の伝達効率の変化による検知電圧  $V_o$  のばらつきが補正される。

40

#### 【0033】

また、例えば、図2の時刻  $t_1 \sim t_2$  の補正期間に、CPU15が読み取った A/D 値  $V_{oc} [dec]$  が、 $H_i$  であったとする。CPU15は、図4から、補正係数  $Z$  として“0.65”を取得する。そして、CPU15は、図3の  $R_{ef}$  換算テーブルから、A/D 值  $V_{op}$  が  $H_i$  となる交流電源電圧値  $V_{ac}$  を求める。この場合、CPU15は、交流電源電圧  $V_{ac}$  として 170V $ac$  を取得する。実際には、交流電源 10 の電圧値は 110V であるが、フォトカプラ13の伝達効率の変化によって検知電圧  $V_o$  のばらつきが生じて

50

いる。CPU15は、(3)式の交流電源電圧値 $V_{ac}$ に170V $V_{ac}$ を代入し、補正係数 $Z$ に0.65を代入して、補正後の交流電源電圧値 $V_{AC}$ として110.5V $V_{ac}$ を算出する。これにより、フォトカプラ13の伝達効率の変化による検知電圧 $V_o$ のばらつきが補正される。

#### 【0034】

このように図4の補正係数 $Z$ と図3のRef換算テーブルとを用いることで、フォトカプラ13の実際の伝達特性に合わせた適切な交流電源電圧値 $V_{AC}$ を求めることができる。なお、実施例1では、補正期間( $t_1 \sim t_2$ )では、補正係数 $Z$ のみを求め、時刻 $t_5$ 以降の交流電源10の入力時に、補正後の交流電源電圧値 $V_{AC}$ を求めるようにしている。

#### 【0035】

図2の説明に戻る。図2の時刻 $t_2$ において、CPU15は、Ref\_c\_tr1信号をLoとし(Ref\_c\_tr1信号はLoのまま)、時刻 $t_3$ でRef\_c\_tr1信号をHiとする(Ref\_c\_tr1信号はLoのまま)。これにより時刻 $t_2 \sim t_3$ の期間は、リレー17とFET29の両方がオフ状態となる。この時刻 $t_2 \sim t_3$ の期間は、ダイオード13dが過電流状態となることを防止するために設けられたデッドタイム期間である。時刻 $t_3$ ではリレー17がオン状態、FET29がオフ状態となり、フォトダイオード13dには交流電源10から電流が供給され、検知電圧 $V_o$ は交流電源10の電圧に基づいた値となる。

#### 【0036】

##### [交流電源電圧値 $V_{AC}$ の演算]

ここまで、上述の範囲では、電圧検知装置100の温度特性及び経年変化による検知ばらつきの補正に関する説明をした。図2の時刻 $t_3$ 以後においては、交流電源電圧値 $V_{AC}$ の演算について記載する。実施例1では、CPU15は、検知電圧 $V_o$ を読み取ったA/D値より、ピーク値を検出することで、交流電源電圧値 $V_{AC}$ を演算している。このピーク値とは、図2におけるA/D値の $V_{op} [dec]$ である。

#### 【0037】

図1に示す実施例1の構成では、交流電源10の電圧が高いほどフォトカプラ13のダイオード13dに流れる電流が大きくなる(図2(b)参照)。そのため、交流電源10が入力された場合の検知電圧 $V_o$ は、図2の時刻 $t_4 \sim t_6$ のように交流電源10に反比例した値となる。よって実施例1におけるピーク値 $V_{op}$ とは、所定期間(例えば、時刻 $t_4 \sim t_6$ )内のA/D値の中で最も小さい値としている。

#### 【0038】

##### (交流電源電圧値 $V_{AC}$ を求める演算処理)

図5は、CPU15によってA/D値から上述のピーク値 $V_{op}$ を算出し、交流電源電圧値 $V_{AC}$ を演算するまでの説明するフローチャートである。ステップ(以下、Sとする)1でCPU15は、Ref\_c\_tr1信号をHiとしてリレー17をオン(ON)状態にし、Ref\_c\_tr1信号をLoとして基準電源110からの入力を遮断(OFF)する(図2 時刻 $t_3$ )。これにより、CPU15は、交流電源10から入力される電圧を検知する状態となる。CPU15は、A/D変換器16により変換したA/D値と、図2に記載の演算閾値とを比較して、以降の各処理を進める。その処理方法について図2の時刻 $t_4 \sim t_6$ 及び図5を用いて説明する。

#### 【0039】

図2における時刻 $t_4$ のとき、CPU15は図5のS2、S3の処理を実施している。S2でCPU15は、検知電圧 $V_o$ を読み取ったA/D値を取得する。S3でCPU15は、S2で取得したA/D値が演算閾値よりも小さいか否かを判断する。S3でCPU15は、A/D値が演算閾値以上であると判断した場合、処理をS2に戻し、A/D値が演算閾値よりも小さいと判断した場合、処理をS4に進める。例えば、図2の時刻 $t_4$ におけるA/D値と演算閾値との関係は、A/D値 > 演算閾値であるため、CPU15は再びS2の処理を行う。CPU15は、時刻 $t_5$ でA/D値 < 演算閾値となるまでは、S2、S3を繰り返し実行する。

10

20

30

40

50

**【 0 0 4 0 】**

時刻  $t_5$  で  $A/D$  値 < 演算閾値となると、CPU15 はピーク値  $V_{op}$  を算出するための S4 ~ S6 の処理を実行する。S4 で CPU15 は、ピーク値  $V_{op}$  を取得し、S5 で  $A/D$  値を取得し、S6 で、S5 で取得した  $A/D$  値が演算閾値よりも大きいか否かを判断する。S6 で CPU15 は、 $A/D$  値が演算閾値以下であると判断した場合、処理を S4 に戻し、 $A/D$  値が演算閾値よりも大きいと判断した場合、処理を S7 に進める。例えば、時刻  $t_5$  で  $A/D$  値 < 演算閾値となってから (S3 Y)、時刻  $t_6$  で  $A/D$  値 > 演算閾値となるまでの間に取得した複数の  $A/D$  値 (複数のデジタル値) の中で、最小値となった  $A/D$  値を更新し続けることでピーク値  $V_{op}$  を取得する。

**【 0 0 4 1 】**

例えば、CPU15 が前回取得した  $A/D$  値を “A” とし、今回取得した  $A/D$  値を “B” とする。CPU15 は、“A” と “B” とを比較し、例えば “B” の方が小さいと判断した場合は、“B” を最小値 (すなわち、その時点におけるピーク値) として記憶部 15m に記憶する。次に、S5 の処理において最新の  $A/D$  値を取得し、S6 では S5 で取得した  $A/D$  値と演算閾値との比較を行う。ここで  $A/D$  値が演算閾値よりも小さいままであれば再び S4 の処理を行う。S5 で取得した  $A/D$  値を “C” とすると、CPU15 は、S4 では先ほどまで最小値 (その時点でのピーク値) として記憶している “B” と今回取得した “C” を比較する。その結果、CPU15 が “B” の方が小さいと判断した場合は、“B” を最小値として継続して記憶部 15m に記憶し、“C” の方が小さいと判断した場合は “C” を最小値として記憶部 15m に記憶し直す。このようにして CPU15 は、所定の期間 (例えば、時刻  $t_4 \sim t_6$ ) におけるピーク値  $V_{op}$  を取得する。

**【 0 0 4 2 】**

図2の時刻  $t_6$  で  $A/D$  値 > 演算閾値となると、S7 で CPU15 は、交流電源電圧値  $V_{AC}$  の演算を行う。CPU15 は、S4 で求めたピーク値  $V_{op}$  から図3の Ref 特性 (Ref 換算テーブル) を用いて、補正前の交流電源電圧値  $V_{ac}$  を求める。続いて CPU15 は、時刻  $t_1 \sim t_2$  の期間に  $V_{oc}$  と図4の情報とを用いて求めておいた補正係数  $Z$  を用いて、(3)式から補正後の交流電源電圧値  $V_{AC}$  を演算する。S8 で CPU15 は、リレー 17 をオフするか否かを判断し、リレー 17 をオフしないと判断した場合は処理を S2 に戻し、リレー 17 をオフすると判断した場合は処理を終了する。以上のような手順で、交流電源電圧値  $V_{AC}$  を求めることができる。

**【 0 0 4 3 】**

時刻  $t_6$  のタイミングで S7 の処理によって求めた交流電源電圧値  $V_{AC}$  は、その後時刻  $t_7$  で再びピーク値  $V_{op}$  を取得する S4 の処理が開始され、時刻  $t_8$  で再び S7 の交流電源電圧値  $V_{AC}$  の演算がなされるまで記憶される。すなわち、CPU15 によって一度演算された交流電源電圧値  $V_{AC}$  は、交流電源 10 の 1 周期の間、記憶部 15m に記憶され、以降、交流電源電圧値  $V_{AC}$  は 1 周期毎に更新される。S2 ~ S7 の処理は、リレー 17 がオフされるまで継続される (S8)。そして再び CPU15 が、Ref\_c\_tr1 信号を Lo、Ref\_c\_tr1 信号を Hi として補正期間が始まると、CPU15 は時刻  $t_1 \sim t_2$  期間で説明した補正係数  $Z$  を再度取得する。

**【 0 0 4 4 】**

なお、実施例 1 では、CPU15 がピーク値  $V_{op}$  を取得して交流電源電圧値  $V_{AC}$  の演算をしているが、これは特許請求の範囲を限定するものではない。例えば、オペアンプ等による演算器でピークホールド信号を生成して検知電圧  $V_o$  とし、それを CPU15 で取得してもよい。また、取得した  $A/D$  値より実効値演算を実施し、算出した実効値より交流電源電圧値  $V_{AC}$  を演算してもよい。また、実施例 1 におけるその他構成も一例であって、この発明の技術的範囲をそれらのみに限定する趣旨のものではない。具体的には、伝達手段であるフォトカプラ 13 はその他の光伝達素子であってもよいし、絶縁トランジスト等によるものであってもよい。また、基準電源 110 は基準電源の機能を満たすものであれば交流の基準電源であっても直流の基準電源であってもよい。これらの変形は、以下の実施例においても同様である。

### 【0045】

従来の技術では、温度条件や経時条件によってフォトカプラ等の1次2次間の電流伝達が大きく変わるために、高精度な交流電源10の電圧検知ができなかった。それに対し、実施例1によれば、電圧検知装置の温度特性及び経年変化による検知ばらつき補正を行うことで、温度変化や経年変化の影響を受けず、精度よく電圧検知を行うことができる。

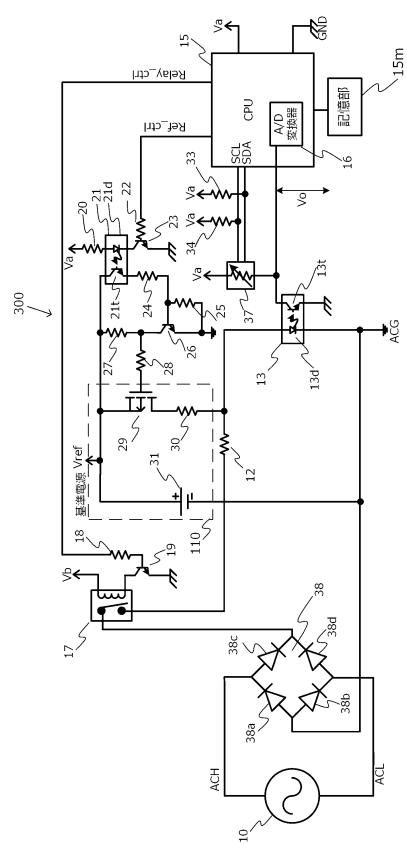

### 【実施例2】

#### 【0046】

##### [電圧検知装置]

実施例2における電圧検知装置200の構成及び動作について、図6、図7を用いて説明する。図6は実施例2における電圧検知装置200の回路構成を示したものである。図6において、図1に示した実施例1の回路構成の各部に付した符号と同一符号で示されるものは、同じ機能を有する構成要素を示している。図6は、実施例1で示した図1に比べると、Ref\_c tr1信号によるFET29の駆動回路と、Relay\_c tr1信号によるリレー17の駆動回路及びリレー17が削除されている。その上で、抵抗12が12a、12bのように2つに分かれ、その中間点が抵抗28を介してFET29のゲート端子に接続されている。更に、フォトカプラ35、抵抗36からなるゼロクロス回路130が追加されている。また、実施例1の抵抗14は図6ではデジタルポテンショメータ-37(以下、DPM37と記す)となり、CPU15とI-squared-Cによる通信が可能となっている。DPM37は、CPU15からの制御により抵抗値を調整することが可能な抵抗素子である。その他は、実施例1と同じ構成である。

10

#### 【0047】

実施例2の基準電源120は、FET29のゲート端子とソース端子との間にコンデンサ32が接続されている。実施例2のフォトカプラ13の1次側のダイオード13dは、アノード側にフォトカプラ35の1次側のダイオード35dが接続されている。フォトカプラ13の2次側のトランジスタ13tは、コレクタ端子にDPM37が接続されている。DPM37は一端が抵抗33を介して電源Vaに接続され、他端が抵抗34を介して電源Vaに接続されている。DPM37の一端はCPU15のSDA端子にも接続され、他端はCPU15のSCL端子にも接続されている。フォトカプラ35の2次側のトランジスタ35tは、コレクタ端子に抵抗36を介して電源Vaが接続され、エミッタ端子は接地されている。トランジスタ35tのコレクタ端子は、CPU15にも接続されている。CPU15は、フォトカプラ35からゼロクロス信号を入力される。

20

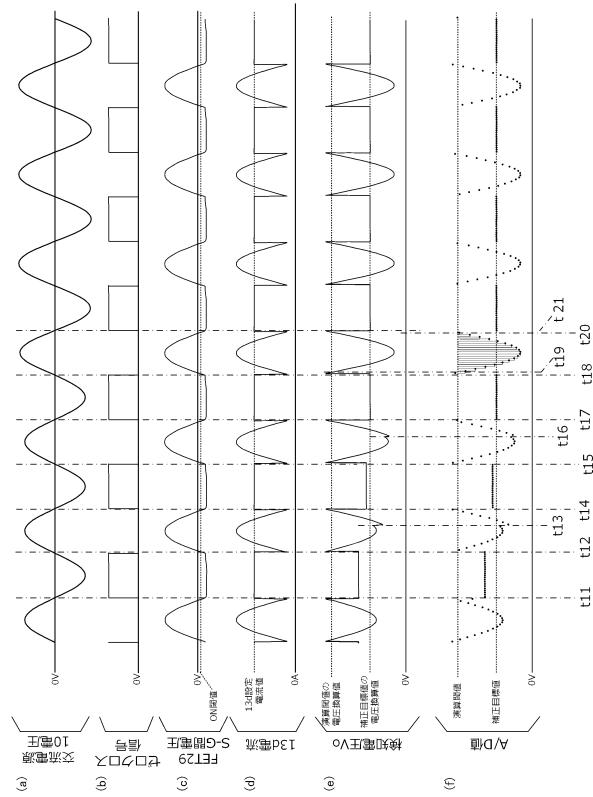

#### 【0048】

また図7は実施例2の特徴的な動作を時系列に説明するための参考波形である。図7(a)は、交流電源10の電圧の波形を示し、(b)はゼロクロス回路130から入力されたゼロクロス信号の波形を示す。(c)は、基準電源120のFET29のソース端子とゲート端子との間の電圧(S-G間電圧)の波形を示し、(d)はフォトカプラ13のダイオード13dに流れる電流の波形を示す。(c)にはFET29のオン閾値(ON閾値)を点線で示す。(d)にはダイオード13dの設定電流値を点線で示す。(e)は検知電圧Voを示し、(f)は検知電圧Voを読み取ったA/D値を示す。(e)には演算閾値の電圧換算値及び補正目標値(目標値)の電圧換算値を点線で示す。(f)には演算閾値及び補正目標値を点線で示す。横軸はいずれも時間を示す。

30

#### 【0049】

##### [ゼロクロス回路]

以下動作の詳細について、ゼロクロス回路130、基準電源120の順に説明する。ゼロクロス回路130は、交流電源10に同期してハイレベル又はローレベルの信号(以下、H/L信号という)を出力する回路である。交流電源10のACH側がプラス電位となりフォトカプラ35のダイオード35dに順方向電流が流れると、トランジスタ35tがオン状態となる。これにより電源Vaから抵抗36に電流が流れ、ローレベルのゼロクロス信号がCPU15のI/Oポートに入力される。また、交流電源10のACH側がマイナス電位のときにはトランジスタ35tがオフ状態となって逆の動作となり、ゼロクロス

40

50

信号はハイレベルとなる。

#### 【0050】

##### [ 基準電源 120 ]

続いて基準電源 120 の説明をする。基準電源 120 の FET 29 は、交流電源 10 に同期してオン / オフされる。図 7 の FET 29 のソース端子とゲート端子の間の電圧 ( S - G 間電圧 ) に示すように、FET 29 は P チャネルの MOSFET であるため、ソース電圧を基準としてゲート電圧がオン閾値以下になるとオン状態となる。すなわち、交流電源 10 の ACH 側がプラス電位となり、フォトカプラ 35 のダイオード 35d 及びフォトカプラ 13 のダイオード 13d に順方向電流が流れている間は、FET 29 はオフとなる。また、交流電源 10 の ACH 側がマイナス電位のときは、FET 29 はオンとなり、基準電源 120 からの電流が抵抗 30 を介してフォトカプラ 13 のダイオード 13d に流れれる。これによりフォトカプラ 13 のダイオード 13d には、図 7 ( d ) に示すように、交流電源 10 の ACH からの電流と、基準電源 120 からの電流とが交互 ( 交流電圧の半周期ごと ) に流れれる。よって、2 次側の検知電圧  $V_o$  も、図 7 ( e ) に示すように、交流電源 10 の交流電圧に応じた電圧と、基準電源 120 に応じた電圧とが交互に現れる。

10

#### 【0051】

##### [ 補正方法及び交流電源電圧値 VAC の演算方法 ]

続いて実施例 2 の補正方法及び交流電源電圧値 VAC の演算方法について説明する。実施例 2 の補正期間及び交流電源電圧値 VAC の演算期間の切り替えには、ゼロクロス信号が用いられる。具体的には、ゼロクロス信号がハイレベルの期間を補正期間 ( 第 1 の状態 ) 、ゼロクロス信号がローレベルの期間を交流電源電圧値 VAC の演算期間 ( 第 2 の状態 ) とする。このように、実施例 2 では、交流電源 10 に同期したゼロクロス信号を用いることで、CPU 15 による補正期間及び交流電源電圧値 VAC の演算期間の切り替え判断を、単純化している。

20

#### 【0052】

図 7 の時刻  $t_{11}$  でゼロクロス信号がローレベルからハイレベルになると、検知電圧  $V_o$  は、基準電源 120 に応じた電圧となる。CPU 15 は、時刻  $t_{12}$  でゼロクロス信号がハイレベルからローレベルになるまでの間に検知電圧  $V_o$  の値を A/D 変換器 16 で A/D 値に変換する。CPU 15 は、読み取った A/D 値と、図 7 ( f ) の補正目標値とを比較し、その比較結果に応じて DPM 37 の抵抗値を調整する。図 7 ( f ) の補正目標値は、実施例 1 で示した図 4 の補正係数が 1.0 となる値である。補正目標値は、図 3 の REF 特性を用いて交流電源電圧値 VAC を演算しても高精度な結果を得ることができるよう、DPM 37 の抵抗値を調整することによって検知電圧  $V_o$  を調整するための基準値である。

30

#### 【0053】

実施例 1 では、CPU 15 が記憶する図 3 の REF 特性 ( REF 換算テーブル ) と実際の特性とのズレを、補正期間内に読み取った A/D 値 ( $V_{oc}$  に対応) から補正係数 Z を取得することで、高精度な交流電源電圧値 VAC を演算していた。一方、実施例 2 では、図 3 の REF 特性と実際の特性とが一致するように、読み取った A/D 値が補正目標値と一致するように DPM 37 の抵抗値を調整する。なお、実施例 2 においても交流電源 10 の電圧が 110V であるときに (1) 式が成り立つように設定している。そのため、補正目標値は REF 特性の 110V ( 所定値 ) での A/D 値 ( $V_{o1} [dec]$  ) となる。これにより、より高い分解能で電圧を検知することが可能となる。

40

#### 【0054】

図 7 に示すように、時刻  $t_{11} \sim t_{12}$  の補正期間で読み取った A/D 値と補正目標値との関係が、A/D 値 > 補正目標値の関係にある場合、CPU 15 は DPM 37 の抵抗値が高くなるように I-squared-C 通信により DPM 37 を調整する。具体的には、実施例 2 では時刻  $t_{12}$  で補正期間の読み取りと補正目標値との比較が完了し、その後、所定時間が経過した時刻  $t_{13}$  のタイミングで DPM 37 の抵抗値が調整されている。また、その調整後の抵抗値は、読み取った A/D 値、A/D 値を読み取った際の DPM 3

50

7 の抵抗設定値と、補正目標値、補正後の DPM37 の抵抗設定値との比率により決定される。

#### 【 0 0 5 5 】

時刻 t14 ~ t15 で再び補正期間になると、CPU15 は再度 A/D 値を取得し、同様に補正目標値との比較、及び DPM37 の抵抗値の調整を実施する。図 7 では、時刻 t16 で再度 DPM37 の抵抗値が調整され、時刻 t17 ~ t18 の補正期間では、読み取った A/D 値と補正目標値とが略等しくなっている。このように、CPU15 は、A/D 値と補正目標値とが等しくなるまで DPM37 の抵抗値の調整を繰り返し実施する。なお、実際の動作では、A/D 値と補正目標値とが全く等しくなることは極めて困難であり、時間を要するため、補正目標値にある程度の幅を持たせることで補正時間の短縮化を図るようにするとよい。すなわち、A/D 値と補正目標値との差が小さくなるように、具体的には、その差が所定の範囲内となるようにすればよい。

10

#### 【 0 0 5 6 】

時刻 t17 ~ t18 のように補正期間で読み取った A/D 値と補正目標値とが略等しくなると、CPU15 は DPM37 の抵抗値調整が完了したと判断する。CPU15 は、DPM37 の抵抗値の調整が完了した直後のゼロクロス信号がローレベルとなっている期間、すなわち時刻 t18 ~ t21 で、交流電源電圧値 VAC の演算を実行する。時刻 t11 ~ t12、時刻 t14 ~ t15 のように DPM37 の抵抗値の調整が完了していない場合には、時刻 t12 ~ t14、時刻 t15 ~ t17 のゼロクロス信号がローレベルの期間での交流電源電圧値 VAC の演算は実施しない。すなわち、実施例 2 では、交流電源 10 の 1 周期毎に A/D 値と補正目標値との比較を行って、補正目標値とのずれが解消された後に、言い換えれば最適な補正值でもって交流電源電圧値 VAC を演算することができる。

20

#### 【 0 0 5 7 】

時刻 t18 ~ t21 の期間における交流電源電圧値 VAC の演算の具体的方法は、実効値演算による方法とする。実施例 2 においても、実施例 1 で示したように、ピーク電圧 Vop によるものでもよい。実施例 2 では実効値演算にすることで、歪んだ交流電源 10 の場合でも高精度な交流電源電圧値 VAC の演算が可能となる。交流電源電圧値 VAC の演算を実効値演算によって実施する場合には、(4) 式を用いて検知電圧 V0 より実効値 RMS を求める。

#### 【 数 3 】

30

$$RMS = \sqrt{\frac{1}{T} \int_0^T f(V_a - V_o)^2 dt} \dots \dots (4)$$

Va : 検知電圧 V0 の基準電圧

T : 交流電源 10 の 1 / 2 周期

#### 【 0 0 5 8 】

(4) 式の 1 / 2 周期 T は図 7 のゼロクロス信号がローレベルとなる時刻 t18 ~ t21 の期間となる。また、(4) 式の実効値 RMS を CPU15 で演算する場合は、読み取った A/D 値から (5) 式で演算する。

40

#### 【 数 4 】

$$RMS = \sqrt{\frac{(Vot[dec] - Vdec_0)^2 + (Vot[dec] - Vdec_1)^2 + \dots + (Vot[dec] - Vdec_{n-1})^2 + (Vot[dec] - Vdec_n)^2}{n}} \dots \dots (5)$$

50

$V_{o t} [dec]$  : 演算閾値に相当する A / D 値

$V_{dec}$  : 所望のサンプリング周期で読み取った A / D 値

#### 【0059】

実施例 2 の場合の  $0 \sim n$  は、A / D 値が演算閾値以下となる期間に取得した A / D 値の個数であり、図 7 の時刻  $t_{19} \sim t_{20}$  に取得した A / D 値となる。また、A / D 値のサンプリング周期は可能な限り短い方が交流電源電圧値 VAC の検知精度を高めることができる。交流電源 10 に重畠するノイズ周波数にもよるが、少なくとも 5 kHz ~ 20 kHz のサンプリング周波数が必要となる。そして、CPU15 は、図 3 の横軸  $V_{op} [dec]$  が実効値 RMS となった交流電源電圧 REF 特性のテーブルを記憶部 15 m に記憶しており、その REF 特性から交流電源電圧値 VAC を演算する。これにより、交流電源 10 に高周波ノイズや低周波ノイズが重畠した場合であっても、交流電源 10 の正確な実効電圧を把握することが可能となる。

10

#### 【0060】

実施例 2 では、以上のような構成とすることで、更に高い分解能で交流電源電圧値 VAC を検知することが可能となる。更には、交流電源 10 の 1 周期毎に補正值の見直しをかけることができるため、電圧検知装置 200 の温度条件が刻々と変化するような場合であっても、高精度な交流電源の電圧検知ができる。

20

#### 【0061】

以上、実施例 2 によれば、温度変化や経年変化の影響を受けず、精度よく電圧検知を行うことができる。

#### 【実施例 3】

#### 【0062】

##### [ 電圧検知装置 ]

実施例 3 の電圧検知装置の構成及び動作について、図 8、図 9 を用いて説明する。図 8 は実施例 3 の電圧検知装置 300 の回路構成を示したものである。図 8 において、図 1 に示した実施例 1 の電圧検知装置 100 の構成、及び図 6 に示した実施例 2 の電圧検知装置 200 の各部に付した符号と同一符号で示されるものは、同じ機能を有する構成要素を示している。実施例 1 で示した図 1 では、交流電源 10 の後に配置されたダイオード 11a、ダイオード 11b によって負電圧の整流を行っていた。図 8 では、ダイオード 38a、ダイオード 38b、ダイオード 38c、ダイオード 38d による整流手段であるブリッジダイオード 38 による全波整流に変わっている。また、フォトカプラ 13 の 2 次側は図 6 に記載の実施例 2 と同じ DPM37 となっている。その他は実施例 1 の形態と同じ構成であり、説明を省略する。

30

#### 【0063】

##### [ 電圧検知装置の動作 ]

以下動作の詳細について図 9 を用いて説明する。図 9 は実施例 3 の特徴的な動作を時系列に説明するための参考波形である。図 9 (a) には交流電源 10 の電圧の波形を示し、(b) にはフォトカプラ 13 のダイオード 13d に流れる電流の波形を示す。(c) には検知電圧  $V_o$  の波形を示し、演算閾値の電圧換算値及び補正目標値の電圧換算値を点線で示す。(d) には検知電圧  $V_o$  を読み取った A / D 値を示し、演算閾値及び補正目標値を点線で示す。いずれも横軸は、時間を示す。なお、図 9 に記載の演算閾値、補正目標値、及びピーク値  $V_{op} [dec]$  は図 2、図 7 に記載するものと同一であるため、説明は省略する。

40

#### 【0064】

実施例 3 の補正期間は、図 9 における時刻  $t_{31} \sim t_{33}$  であり、実施例 1 と同じく CPU15 が  $Re1ay\_ctr1$  信号を  $Lo$  とし、 $Ref\_ctr1$  信号を  $Hi$  とする。これにより、フォトカプラ 13 のダイオード 13d に基準電源 110 からの電流のみを流すようになる。そして補正方法は、CPU15 が、実施例 2 と同じく、読み取った A / D 値と図 9 に記載の補正目標値とを比較し、比較結果に応じて DPM37 の抵抗値を調整する。図 9 では時刻  $t_{31} \sim t_{32}$  で読み取った A / D 値と補正目標値とを比較し、CPU

50

15が時刻 t 3 2 で DPM 3 7 の抵抗値を調整している。

#### 【0065】

交流電源電圧値 VAC の演算は、図 5 で示した実施例 1 と同じく、変換された A/D 値が演算閾値を超える期間でピーク電圧 Vop を求める方法である。しかしながら、DPM 3 7 の抵抗値調整を実施しているため、実施例 1 で求めた補正係数 Z は実施例 3 では不要である。そのため CPU 15 は、算出したピーク電圧 Vop と図 3 の REF 特性 (Ref 換算テーブル) に基づいて交流電源電圧値 VAC の演算を行う。そして実施例 3 が他実施例と大きく異なるところは、検知電圧 Vo が全波波形であるという点である（図 9 (c) 参照）。図 9 に示す時刻 t 3 4 以降の交流電源電圧値 VAC の演算は、全波波形に対して実施する。

10

#### 【0066】

よって CPU 15 は、時刻 t 3 5 ~ t 3 6 の期間で交流電源電圧値 VAC を演算し、その結果は時刻 t 3 7 で更新されるまで保持される。つまり実施例 1 及び実施例 2 では、算出した交流電源電圧値 VAC は交流電源 10 の 1 周期毎に更新されていたのに対し、実施例 3 では交流電源 10 の半周期毎に更新される。そのため、実施例 3 では、交流電源 10 の正半波及び負半波のどちらか一方にのみ高周波ノイズや低周波ノイズが重畠した場合であっても、交流電源 10 の正確な実効値を把握することが可能となる。

#### 【0067】

実施例 3 では、以上のような構成とすることで、交流電源 10 の全波波形に対して交流電源電圧値 VAC の演算が可能となる。交流電源 10 の正半波及び負半波のどちらか一方にのみ高周波ノイズや低周波ノイズが重畠した場合であっても、交流電源の正確な実効電圧を検知することができる。

20

#### 【0068】

以上、実施例 3 によれば、温度変化や経年変化の影響を受けず、精度よく電圧検知を行うことができる。

#### 【実施例 4】

#### 【0069】

##### [ 電圧検知装置 ]

実施例 4 の電圧検知装置の構成及び動作について、図 10、図 11、図 12 を用いて説明する。図 10 は実施例 4 の電圧検知装置 400 の回路構成を示したものである。図 10 において、図 1 に示した実施例 1 の回路構成、及び図 6 に示した実施例 3 の回路構成、図 8 に示した実施例 3 の回路構成各部に付した符号と同一符号で示されるものは、同じ機能を有する構成要素を示している。

30

#### 【0070】

実施例 1 ~ 実施例 3 では、交流電源 10 の電圧値 (VAC) を演算するために電圧を検知する電圧検知装置であったが、実施例 4 は温度を検知するための電圧検知装置である。以下、電圧検知装置 400 を温度検知装置 400 とする。温度検知装置 400 は、例えば画像形成装置等の 1 次側に配置された発熱体の温度を検知することを目的として利用される。すなわち、実施例 4 では、検知の対象は発熱体の温度である。したがって、実施例 1 では、2 次側から検知したい 1 次情報として、交流電源 10 が接続され、その 1 次情報を電圧にするための回路部品であるダイオード 11a、ダイオード 11b が構成されていた。これに対し実施例 4 では、1 次側には温度情報を検知するための温度検知部 410 が構成されている。

40

#### 【0071】

##### [ 温度検知部 ]

温度検知部 410 は、基準電圧 31 を抵抗 39 と温度検知素子であるサーミスタ 40 で分圧した電圧を、バッファ回路 420 を介してフォトカプラ 13 へ接続するように構成している。温度検知部 410 は、サーミスタ 40 で検知した温度の情報を電圧に変換する電圧変換手段として機能する。バッファ回路 420 は、オペアンプ 41、抵抗 42、トランジスタ 43、抵抗 44 で構成された電流增幅のためのバッファ回路である。抵抗 39 とサ

50

一ミスタ 4 0 の分圧値はオペアンプ 4 1 の非反転入力端子（+ 端子）に入力される。オペアンプ 4 1 の出力端子は抵抗 4 2 を介してトランジスタ 4 3 のベース端子に接続される。トランジスタ 4 3 は、コレクタ端子に基準電圧 3 1 の + 側が接続され、エミッタ端子に抵抗 4 4 の一端が接続されている。抵抗 4 4 の他端は基準電圧 3 1 の - 端子に接続されている。トランジスタ 4 3 のエミッタ端子と抵抗 4 4 の一端との接続点は、オペアンプ 4 1 の反転入力端子（- 端子）に入力されている。また、トランジスタ 4 3 のエミッタ端子と抵抗 4 4 の一端との接続点は、抵抗 1 2 を介してフォトカプラ 1 3 のダイオード 1 3 d のアノード側に接続されている。

#### 【 0 0 7 2 】

基準電圧 3 1 の抵抗 3 9 とサーミスタ 4 0 の分圧値は、発熱体近傍にサーミスタ 4 0 を配置することで温度に応じて変化する。バッファ回路 4 2 0 の出力である抵抗 4 4 の両端に発生する電圧は、オペアンプ 4 1 のオフセット電圧を無視すると、サーミスタ 4 0 の両端に発生する電圧と等しくなる。このバッファ回路 4 2 0 は、フォトカプラ 1 3 のダイオード 1 3 d に十分な電流を流すために備えられている。

10

#### 【 0 0 7 3 】

また、実施例 1 では、`Relay_c tr1` 信号と `Ref_c tr1` 信号によってフォトカプラ 1 3 への入力情報を切り替えていたのに対し、実施例 3 では `Ref_c tr1` 信号のみで切り替えを行えるよう、FET 4 6 を備えている。FET 4 6 は、ドレイン端子にオペアンプ 4 1 の出力端子が抵抗 4 2 を介して接続され、ゲート端子にフォトカプラ 2 1 のトランジスタ 2 1 t のエミッタ端子が抵抗 2 4 を介して接続されている。FET 4 6 のソース端子は接地されている。抵抗 4 5 は、FET 4 6 のゲート端子とソース端子との間に接続されている。`Ref_c tr1` 信号が `Hi` になると、フォトカプラ 2 1 がオンして FET 4 6 のゲート電圧が上昇する。これにより、トランジスタ 4 3 がオフ（オープン）となり、温度検知部 4 1 0 からの出力は停止する。FET 4 6 がオンするとともに、FET 2 6 、FET 2 9 もオン状態となり、基準電源 1 1 0 からの電流がフォトカプラ 1 3 のダイオード 1 3 d に供給される。このようにしてフォトカプラ 1 3 への入力情報を切り替えている。また、`Ref_c tr1` 信号が `Lo` になると、FET 2 9 がオフし基準電源 1 1 0 からの電流のフォトカプラ 1 3 のダイオード 1 3 d への供給が遮断される。また、FET 4 6 もオフし、温度検知部 4 1 0 から抵抗 1 2 を介してフォトカプラ 1 3 に電流が供給される。

20

#### 【 0 0 7 4 】

FET 4 6 は、オン状態（第 1 の接続状態）のとき、フォトカプラ 1 3 への温度検知部 4 1 0 により変換された電圧の供給を遮断し、かつ、フォトカプラ 1 3 へ基準電源 1 1 0 の電圧を供給する。FET 4 6 は、オフ状態（第 2 の接続状態）のとき、フォトカプラ 1 3 に温度検知部 4 1 0 により変換された電圧を供給し、かつ、フォトカプラ 1 3 への基準電源 1 1 0 の電圧の供給を遮断する。そのほかの回路動作は実施例 1 と等しいため、説明を省略する。

30

#### 【 0 0 7 5 】

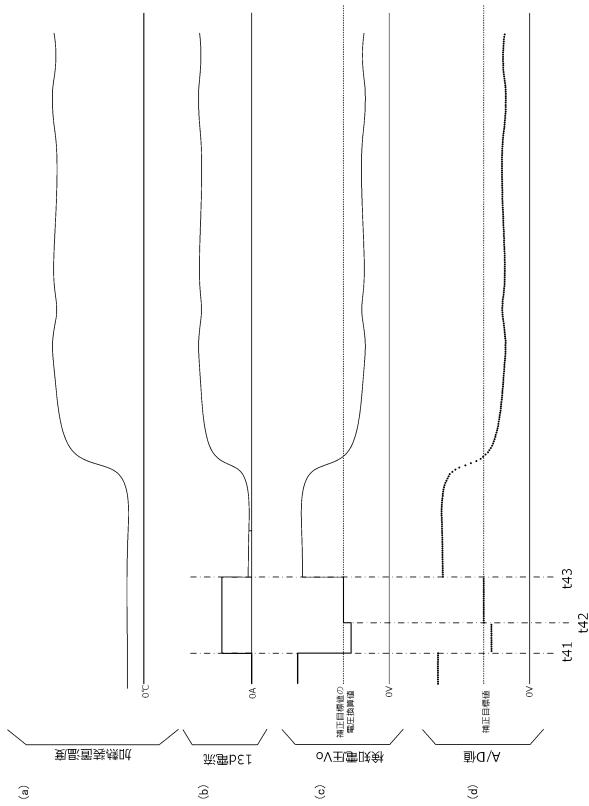

##### [ 温度検知装置の動作 ]

図 1 1 は実施例 4 における特徴的な動作を時系列に説明するための参考波形である。図 1 1 ( a ) には、加熱装置（不図示）の温度を示し、( b ) にはフォトカプラ 1 3 のダイオード 1 3 d に流れる電流の波形を示す。( c ) には検知電圧  $V_o$  を示し、補正目標値の電圧換算値を点線で示す。( d ) は検知電圧  $V_o$  を読み取った A / D 値を示し、補正目標値を点線で示す。横軸はいずれも時間を示す。なお、図 1 1 に記載の補正目標値は図 7 、図 9 に記載するものと同一であるため、説明は省略する。

40

#### 【 0 0 7 6 】

図 1 1 に示す時刻  $t_{4 1} \sim t_{4 3}$  は、実施例 3 で説明した補正期間（時刻  $t_{3 1} \sim t_{3 3}$  ）と同じである。すなわち、`Ref_c tr1` 信号を `Hi` として基準電源 1 1 0 からの電流をフォトカプラ 1 3 のダイオード 1 3 d に流した際の A / D 値が補正目標値と等しくなるように DPM 3 7 の抵抗値が調整されている。

50

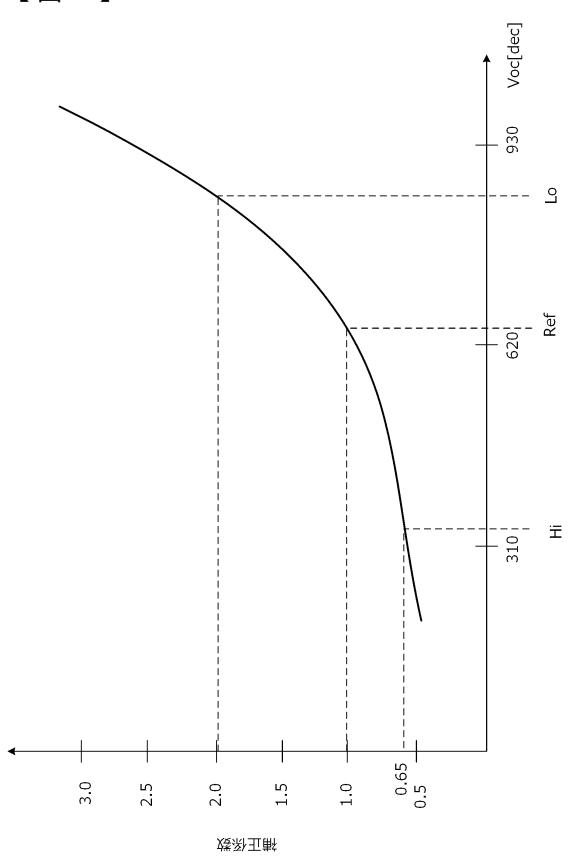

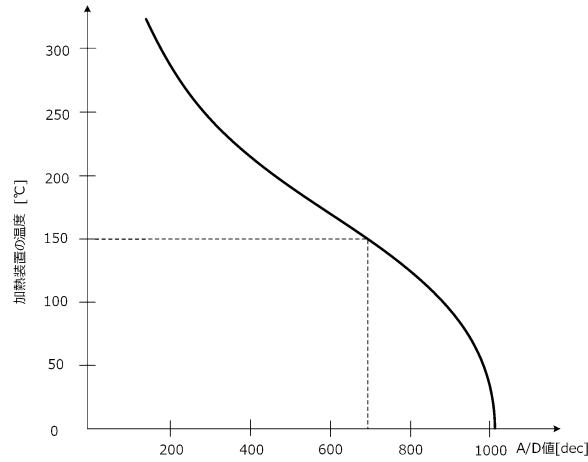

### 【0077】

(検知温度とA / D値との関係)

図12はCPU15が記憶部15mに記憶している加熱装置の温度と温度検知装置400により読み取ったA / D値との関係を示している。図12は、横軸にA / D値 [dec]を示し、縦軸に加熱装置の温度 [ ]を示す。実施例4では、時刻t41～t43の補正期間に読み取ったA / D値と、図12に示す加熱装置の温度が150度のときのA / D値 (A / D [dec]) とが等しくなるように設定されている。

### 【0078】

すなわち、Ref\_c tr1信号をHiとしたとき、基準電源110からダイオード13dに流れる電流をIrefとする。Ref\_c tr1信号をLoとしたとき、温度検知部410からダイオード13dに流れるピーク電流をItempとする。このとき、電流Irefと加熱装置の温度が150度のときのピーク電流Itempとが等しくなるようにしている。このことは、実施例1に記載した(1)式と同様の考え方であり、実施例4においての伝達率の補正効果を得るためにある。

10

### 【0079】

これら電流Irefとピーク電流Itempの調整は、オペアンプ41の入力オフセット電圧、FET29のオン抵抗を無視すると、(6)式の関係にすることで実現できる。なお(6)式では、基準電圧31をV31、抵抗30をR30、抵抗12をR12、抵抗39をR39、サーミスタ40の抵抗をTH40としている。

### 【数5】

20

$$I_{temp} = \frac{V31 \times TH40}{R12(R39 + TH40)} = I_{ref} = \frac{V31}{R30} \dots\dots (6)$$

### 【0080】

このようにして、サーミスタ40の抵抗値が予め定めた特定の温度における抵抗値のときに(6)式が成り立つようにすることで、温度検知装置400の温度特性及び経年変化による検知ばらつきを補正することが可能となる。なお、補正期間におけるA / D値の調整は、実施例2同様に許容される範囲を持って調整する。図11では、CPU15は、時刻t41の補正期間の開始後に読み取ったA / D値の補正目標値からのズレを時刻t42でDPM37の抵抗値を調整することで調整し、時刻t42～t43で補正目標値と等しいことを確認している。

30

### 【0081】

補正期間が終了すると、CPU15は実施例1同様にRef\_c tr1信号をLoとして、取得したA / D値から記憶部15mに予め記憶しているテーブル値を使って所定の値を算出する。実施例4では、図12の特性を使って加熱装置(不図示)の温度を算出する。実施例4の場合、2次側から検知したい1次情報は、加熱装置(不図示)の温度であり、その温度に応じてA / D値が変動する。つまり、これまでの実施例1～3のように、A / D値からピーク値や実効値を求める演算を行う必要はない。そのため、CPU15への入力情報であるA / D値そのものが図12のグラフの横軸(A / D値 [dec])となっている。以上のように、CPU15は、読み取ったA / D値から温度情報を演算し、加熱装置(不図示)の発熱体の温度を制御する。

40

### 【0082】

従来の技術では、温度条件や経時条件によってフォトカプラ等の1次2次の電流伝達が大きく変わるために、高精度な入力交流電源10の電圧検知ができなかった。以上のように、1次側の温度情報を2次側で検知する温度検知装置においても、実施例4のような補正機能を備える。これにより、電圧検知回路の温度特性及び経年変化による検知ばらつき補正することが可能となり、従来よりも高精度に温度情報を検知することができる。

50

**【0083】**

以上、実施例4によれば、温度変化や経年変化の影響を受けず、精度よく電圧検知を行うことができる。

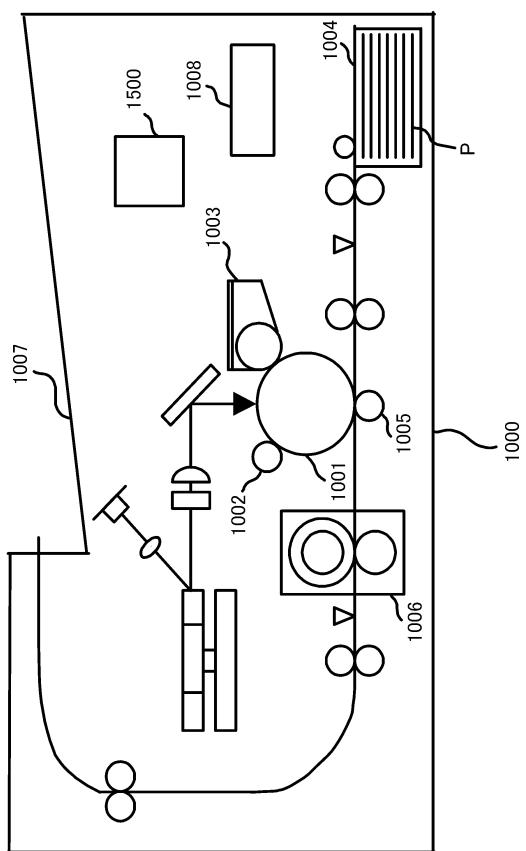

**【実施例5】****【0084】****[レーザビームプリンタの説明]**

図13に、上述した電圧検知装置100～400を備える画像形成装置の一例として、レーザビームプリンタの概略構成を示す。レーザビームプリンタ1000（以下、プリンタ1000という）は、感光ドラム1001、帯電部1002、現像部1003を備えている。感光ドラム1001は、静電潜像が形成される像担持体である。帯電部1002は、感光ドラム1001を一様に帯電する。現像部1003は、感光ドラム1001に形成された静電潜像をトナーにより現像することでトナー像を形成する。感光ドラム1001上（像担持体上）に形成されたトナー像をカセット1004から供給された記録材としてのシートPに転写部1005によって転写する。シートPに転写した未定着のトナー像を定着手段である定着器1006によって定着してトレイ1007に排出する。この感光ドラム1001、帯電部1002、現像部1003、転写部1005が未定着のトナー像を形成する画像形成部（画像形成手段）である。また、プリンタ1000は、電源装置1008を備え、電源装置1008からモータ等の駆動部と制御部1500へ電力を供給している。制御部1500は、CPU（不図示）を有しており、画像形成部による画像形成動作やシートPの搬送動作等を制御している。なお、制御部1500がCPU15を有してもよい。

10

20

**【0085】**

プリンタ1000は、プリント動作を終了させると所定時間が経過した後、プリント動作をすぐに実行できるスタンバイ状態に遷移する。更に所定時間が経過した後、プリンタ1000は待機時の消費電力を低減するため、スタンバイ状態から低消費電力モードであるスリープ状態に遷移する。プリンタ1000はスリープ状態、スタンバイ状態、プリント状態の3つの状態を持ち、制御部1500がそれぞれの状態に遷移させる。なお、本発明の電源装置を適用することができる画像形成装置は、図1に例示された構成に限定されない。

**【0086】**

30

プリンタ1000が備えるCPUは、実施例1（又は実施例2～4）のCPU15であってもよい。実施例1（又は実施例2、3）の電圧検知装置100（又は200、300）を備えるプリンタ1000は、電圧検知装置100（又は200、300）によって交流電源10の入力電圧値を検知する。CPU15は、例えば、電圧検知装置100（又は200、300）により検知した補正後の交流電源電圧値VACと定着処理の目標温度とに基づいて、定着器1006が有する発熱体（不図示）に投入する電力を決定する。また、実施例4の電圧検知装置（又は温度検知装置）400を備えるプリンタ1000は、電圧検知装置400によって定着器1006が有する発熱体（不図示）の温度を検知する。すなわち、定着器1006が実施例4の加熱装置に相当する。

**【0087】**

40

以上、実施例5によれば、温度変化や経年変化の影響を受けず、精度よく電圧検知を行うことができる。

**【符号の説明】****【0088】**

- 13 フォトカプラ

- 15 CPU

- 16 A/D変換器

- 17 リレー

- 29 P-MOSFET

- 110 基準電源

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【図 5】

【図 6】

【図 7】

【図 8】

10

20

30

40

50

【図 9】

【図 10】

10

20

30

40

【図 11】

【図 12】

50

【図 1 3】

10

20

30

40

50

---

フロントページの続き

(56)参考文献

特開平10-111322(JP,A)

特開2013-217843(JP,A)

特開2015-210276(JP,A)

特開2011-112911(JP,A)

特開2017-3425(JP,A)

特開2015-224886(JP,A)

特開2006-310333(JP,A)

特開2018-87719(JP,A)

(58)調査した分野 (Int.Cl., DB名)

G01R 19/00

G01R 31/26

G01R 31/00

G01R 35/00

G03G 21/00

G03G 15/20