(12) 发明专利

(10) 授权公告号 CN 107507805 B

(45) 授权公告日 2021.03.09

(21) 申请号 201710644974.7

(74) 专利代理机构 中国专利代理(香港)有限公司 72001

(22) 申请日 2012.10.24

代理人 叶培勇 付曼

(65) 同一申请的已公布的文献号

申请公布号 CN 107507805 A

(51) Int.CI.

H01L 21/82 (2006.01)

(43) 申请公布日 2017.12.22

H01L 21/336 (2006.01)

(30) 优先权数据

H01L 21/28 (2006.01)

2011-233264 2011.10.24 JP

H01L 29/786 (2006.01)

(62) 分案原申请数据

(56) 对比文件

201210411643.6 2012.10.24

CN 103035735 A, 2013.04.10

(73) 专利权人 株式会社半导体能源研究所

审查员 张海洋

地址 日本神奈川县厚木市

(72) 发明人 栄林克明 日向野聰 山崎舜平

权利要求书1页 说明书35页 附图20页

(54) 发明名称

半导体装置以及半导体装置的制造方法

(57) 摘要

本发明提供一种可靠性高的半导体装置以及该半导体装置的制造方法。本发明的目的之一是高成品率地制造可靠性高的半导体装置以实现高生产化。在具有依次层叠有栅电极层、栅极绝缘膜、氧化物半导体膜并且设置有与氧化物半导体膜接触的源电极层及漏电极层的晶体管的半导体装置的制造中，通过蚀刻工序在形成源电极层及漏电极层，然后进行去除存在于氧化物半导体膜表面及其附近的因蚀刻工序而产生的杂质的工序。

1. 一种半导体装置的制造方法,包括如下步骤:

隔着栅极绝缘膜在栅电极层上形成岛状氧化物半导体膜;

在所述岛状氧化物半导体膜上形成导电膜;

通过使用含有卤素元素的蚀刻气体的等离子体处理对所述导电膜进行加工来形成源电极层和漏电极层;以及

对所述岛状氧化物半导体膜进行杂质去除处理以去除包含于所述蚀刻气体中的所述卤素元素,

其中,所述杂质去除处理是溶液处理,以及

其中,作为所述杂质去除处理,进行氧等离子体处理或一氧化二氮等离子体处理之后进行使用稀氢氟酸溶液的洗涤处理。

2. 根据权利要求1所述的半导体装置的制造方法,其中作为所述杂质去除处理进行使用稀氢氟酸溶液的洗涤处理。

3. 根据权利要求1所述的半导体装置的制造方法,其中所述岛状氧化物半导体膜的经过所述杂质去除处理的表面的卤素浓度为 $5 \times 10^{18} \text{ atoms/cm}^3$ 以下。

4. 一种半导体装置的制造方法,包括如下步骤:

隔着栅极绝缘膜在栅电极层上形成岛状氧化物半导体膜;

形成与所述岛状氧化物半导体膜电连接的导电膜;

通过使用含有卤素元素的蚀刻气体的等离子体处理对所述导电膜进行加工来形成源电极层和漏电极层;以及

对所述岛状氧化物半导体膜进行杂质去除处理以去除包含于所述蚀刻气体中的所述卤素元素,

其中,所述杂质去除处理是溶液处理,以及

其中,作为所述杂质去除处理,进行氧等离子体处理或一氧化二氮等离子体处理之后进行使用稀氢氟酸溶液的洗涤处理。

5. 根据权利要求4所述的半导体装置的制造方法,其中作为所述杂质去除处理进行使用稀氢氟酸溶液的洗涤处理。

6. 根据权利要求4所述的半导体装置的制造方法,其中所述岛状氧化物半导体膜的经过所述杂质去除处理的表面的卤素浓度为 $5 \times 10^{18} \text{ atoms/cm}^3$ 以下。

## 半导体装置以及半导体装置的制造方法

### 技术领域

[0001] 本发明涉及一种半导体装置以及半导体装置的制造方法。

[0002] 在本说明书中,半导体装置是指能够通过利用半导体特性而工作的所有装置,因此电光装置、半导体电路及电子设备都是半导体装置。

### 背景技术

[0003] 通过利用形成在具有绝缘表面的衬底上的半导体薄膜来形成晶体管的技术备受瞩目。该晶体管被广泛地应用于集成电路(IC)、图像显示装置(简单地记载为显示装置)等的电子设备。作为可以应用于晶体管的半导体薄膜,硅类半导体材料被广泛地周知。此外,作为其他材料氧化物半导体受到关注。

[0004] 例如,已经公开了一种使用包含铟(In)、镓(Ga)及锌(Zn)的非晶氧化物(IGZO类非晶氧化物)的半导体层的晶体管(参照专利文献1)。

[0005] [专利文献1]日本专利申请公开2011-181801号公报

[0006] 另外,对于具有使用氧化物半导体的晶体管的半导体装置来说,能否实现高可靠性是决定其能否迈入商品化的重要因素。

[0007] 但是,半导体装置由具有复杂结构的多个薄膜构成并利用多种材料、方法及工序制造。因此,由于所采用的制造工序,有可能导致形成的半导体装置出现形状不良或电特性低下。

### 发明内容

[0008] 鉴于上述问题,本发明的目的之一是提供一种具有使用氧化物半导体的晶体管的高可靠性的半导体装置。

[0009] 另外,本发明的目的之一是高成品率地制造可靠性高的半导体装置以实现高生产化。

[0010] 在具有底栅结构的晶体管的半导体装置中,可以防止当形成以与氧化物半导体膜接触的方式设置在氧化物半导体膜上的源电极层及漏电极层时所使用的蚀刻气体中的元素作为杂质残留在氧化物半导体膜的表面。具体地,例如可以采用如下方式。

[0011] 本发明的一个方式是一种半导体装置的制造方法,包括如下步骤:在绝缘表面上形成栅电极层;在栅电极层上形成栅极绝缘膜;隔着栅极绝缘膜在栅电极层上形成岛状的氧化物半导体膜;在栅极绝缘膜及岛状的氧化物半导体膜上形成导电膜;通过利用使用含有卤素元素的蚀刻气体的等离子体处理对导电膜进行加工形成源电极层及漏电极层;对氧化物半导体膜进行杂质去除处理来去除包含于蚀刻气体中的元素。

[0012] 另外,在上述半导体装置的制造方法中,在进行了杂质去除处理之后,氧化物半导体膜表面的卤素元素浓度(例如,氯浓度)为 $5 \times 10^{18} \text{ atoms/cm}^3$ 以下,优选为 $1 \times 10^{18} \text{ atoms/cm}^3$ 以下。

[0013] 另外,在上述半导体装置的制造方法中,作为杂质去除处理,优选进行氧等离子体

处理或一氧化二氮等离子体处理。再者,优选进行利用稀氢氟酸溶液的洗涤处理。

[0014] 根据本发明的一个方式的半导体装置,其包括:设置在绝缘表面上的栅电极层;设置在栅电极层上的栅极绝缘膜;设置在栅极绝缘膜上的岛状的氧化物半导体膜;以接触于氧化物半导体膜的方式设置的源电极层及漏电极层,其中源电极层及漏电极层覆盖氧化物半导体膜的沟道宽度方向的端部,并且氧化物半导体膜表面的卤素元素(例如,氯浓度)为 $5 \times 10^{18} \text{ atoms/cm}^3$ 以下。

[0015] 另外,在根据上述结构的氧化物半导体膜中,与源电极层及漏电极层重叠的区域的厚度大于不与源电极层及漏电极层重叠的区域的厚度。

[0016] 如上所述,为了形成源电极层或漏电极层等在氧化物半导体膜上并与之接触的膜的图案,优选采用使用含有卤素元素的蚀刻气体的等离子体处理。但是,当氧化物半导体膜暴露于含有卤素元素的蚀刻气体时,有如下顾虑:因包含于上述蚀刻气体中的卤素元素(例如,氯、氟)氧化物半导体膜中的氧被抽出,而使氧化物半导体膜的界面附近形成氧缺陷。另外,当在蚀刻工序之后氧化物半导体膜表面及其附近残留有包含于蚀刻气体中的卤素元素时,氧化物半导体膜中有可能形成氧缺陷。当氧化物半导体膜中生成氧缺陷时,氧化物半导体膜的背沟道低电阻化(n型化)而可能导致寄生沟道的形成。

[0017] 例如,当作为氧化物半导体膜使用含有铟的氧化物半导体材料,并且在以接触于氧化物半导体膜的方式设置的源电极层及漏电极层的加工中使用含有三氯化硼( $\text{BCl}_3$ )的蚀刻气体时,有时氧化物半导体膜中的 $\text{In}-\text{O}-\text{In}$ 键与蚀刻气体中的 $\text{Cl}$ 发生反应而变成包含 $\text{In}-\text{Cl}$ 键和氧脱离了的 $\text{In}$ 元素的膜。由于氧脱离了的 $\text{In}$ 元素具有悬空键,因此在氧化物半导体膜中发生氧脱离的部分中存在氧缺陷。

[0018] 另外,当卤素元素的蚀刻气体中包含卤素以外的元素(例如,硼)时,其也成为导致氧化物半导体膜的背沟道低电阻化(n型化)的主要原因之一。

[0019] 于是,在本发明的一个方式中,通过在设置在氧化物半导体膜上的源电极层及漏电极层的蚀刻加工之后进行杂质去除处理,去除可能引起氧化物半导体膜的低电阻化的杂质。由此,可以实现半导体装置的高可靠性。

[0020] 本发明的一个方式涉及一种半导体装置,该半导体装置具有晶体管或包含晶体管的电路。例如,本发明的一个方式涉及一种半导体装置,该半导体装置具有沟道形成区由氧化物半导体形成的晶体管或包含该晶体管的电路。例如,本发明涉及:LSI;CPU;安装在电源电路中的功率器件;包括存储器、晶闸管、转换器以及图像传感器等的半导体集成电路;以液晶显示面板为代表的电光装置;具有发光元件的发光显示装置;以及作为部件安装有上述装置的电子设备。

[0021] 本发明可以提供一种具有使用氧化物半导体的晶体管的高可靠性的半导体装置。

[0022] 此外,可以高成品率地制造可靠性高的半导体装置,由此可以实现高生产化。

## 附图说明

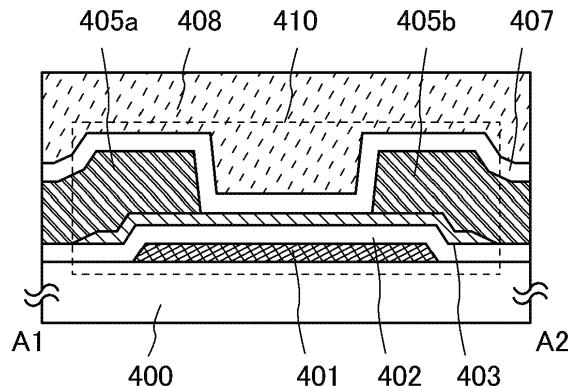

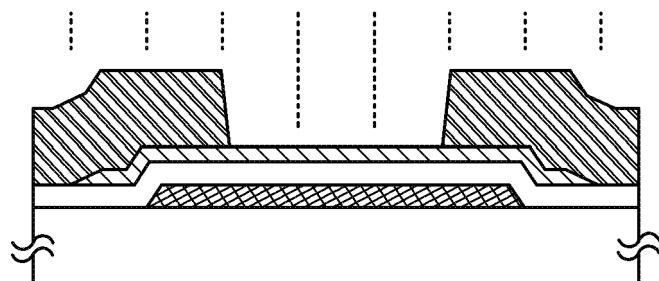

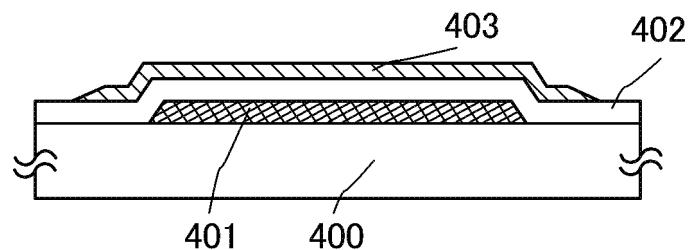

[0023] 图1A至1D是说明半导体装置的一个方式的平面图及截面图;

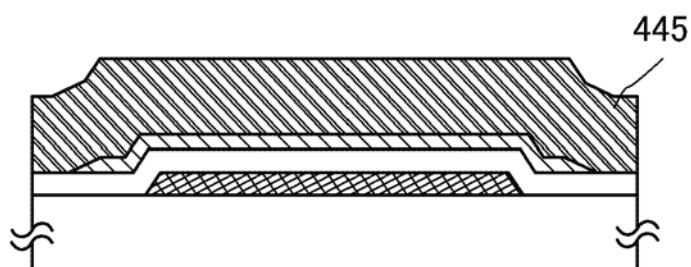

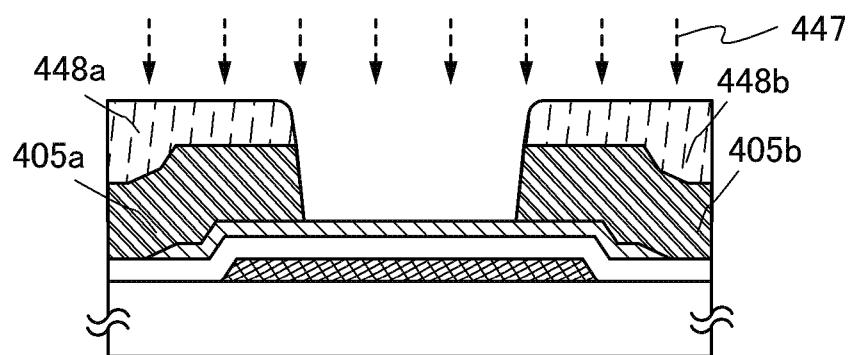

[0024] 图2A至2E是说明半导体装置的制造方法的一个方式的截面图;

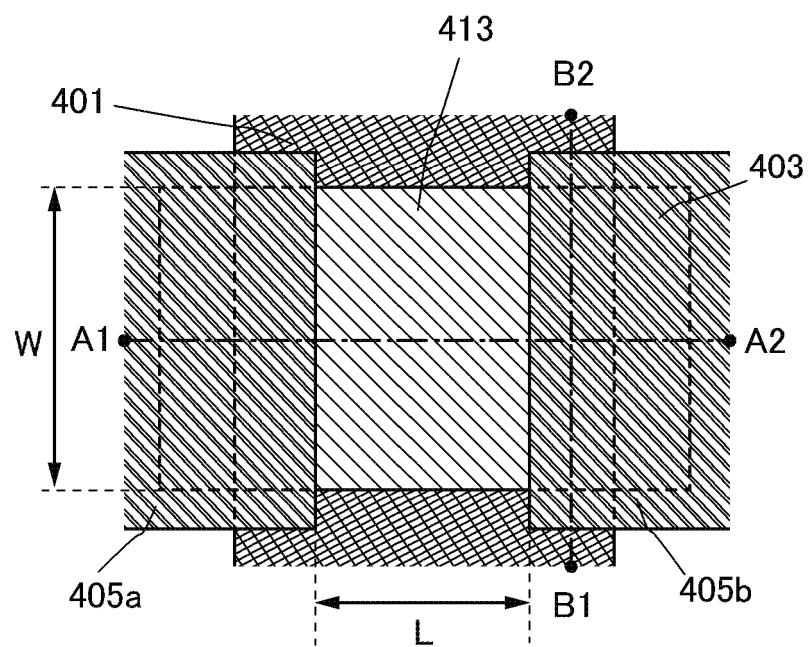

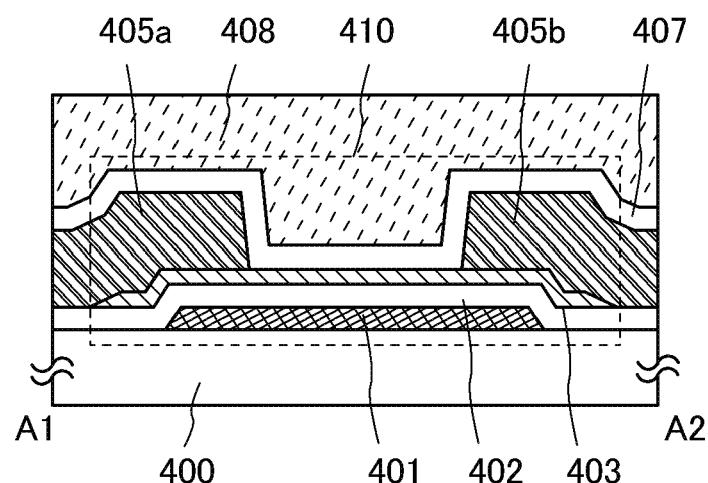

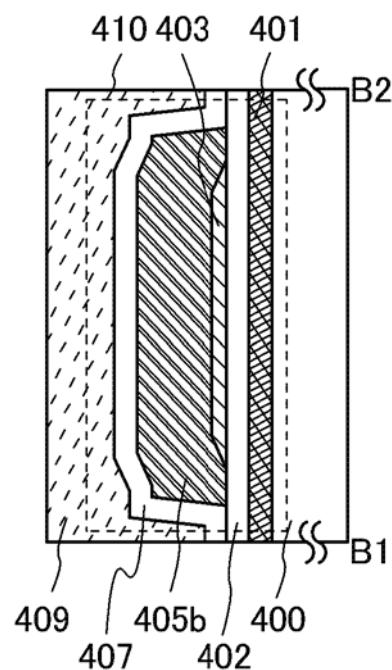

[0025] 图3A至3D是说明半导体装置的一个方式的平面图及截面图;

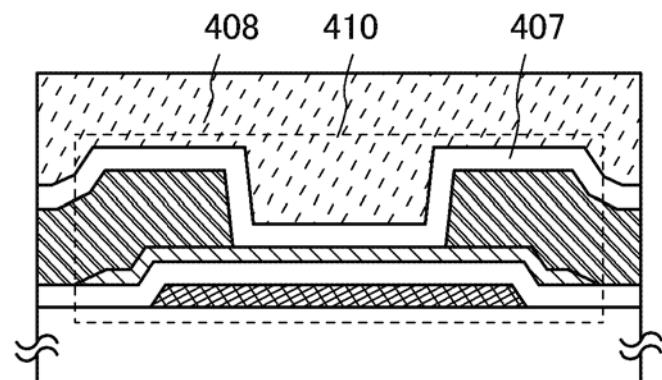

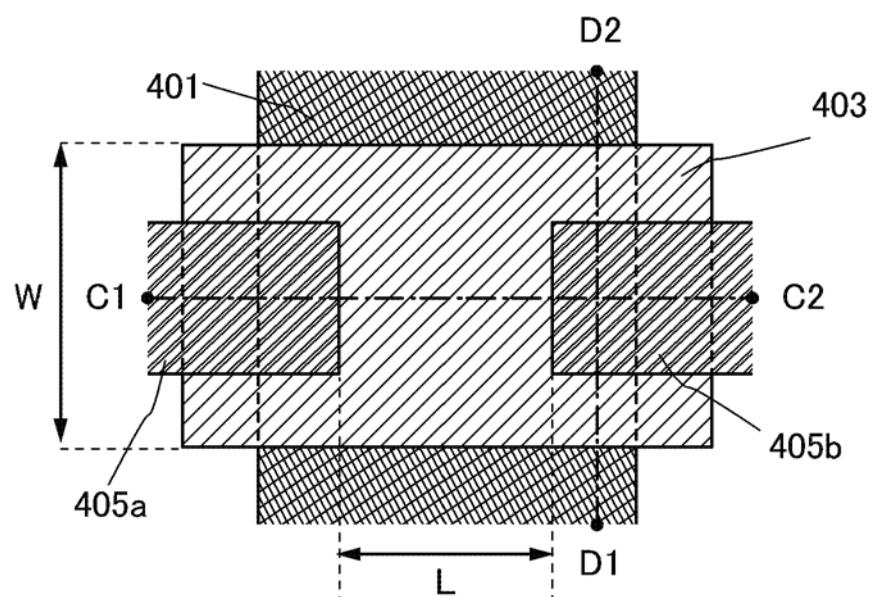

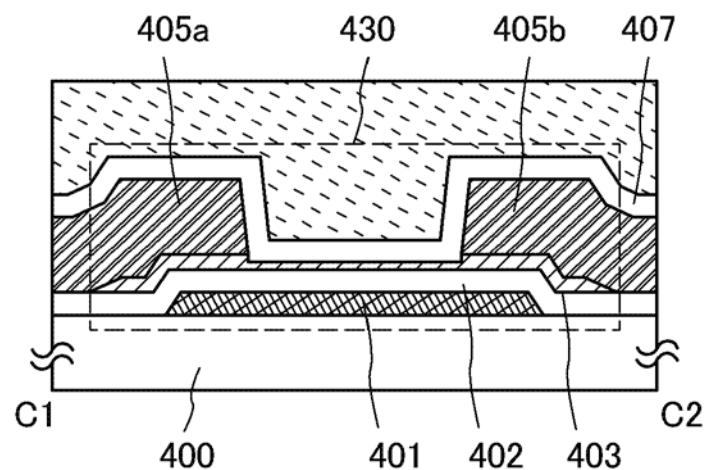

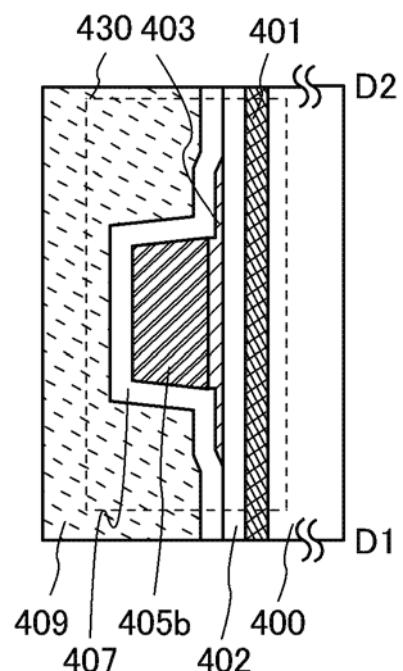

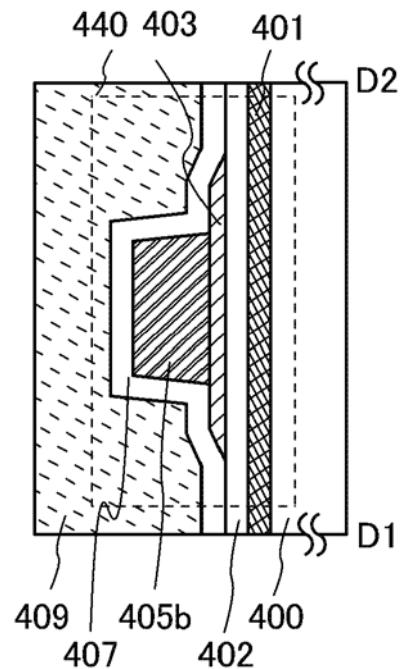

[0026] 图4A至4E是说明半导体装置的一个方式的平面图及截面图;

- [0027] 图5A至5C是说明半导体装置的一个方式的平面图及截面图；

- [0028] 图6A和6B是说明半导体装置的一个方式的平面图及截面图；

- [0029] 图7A和7B是示出半导体装置的一个方式的截面图；

- [0030] 图8A和8B是示出半导体装置的一个方式的电路图及截面图；

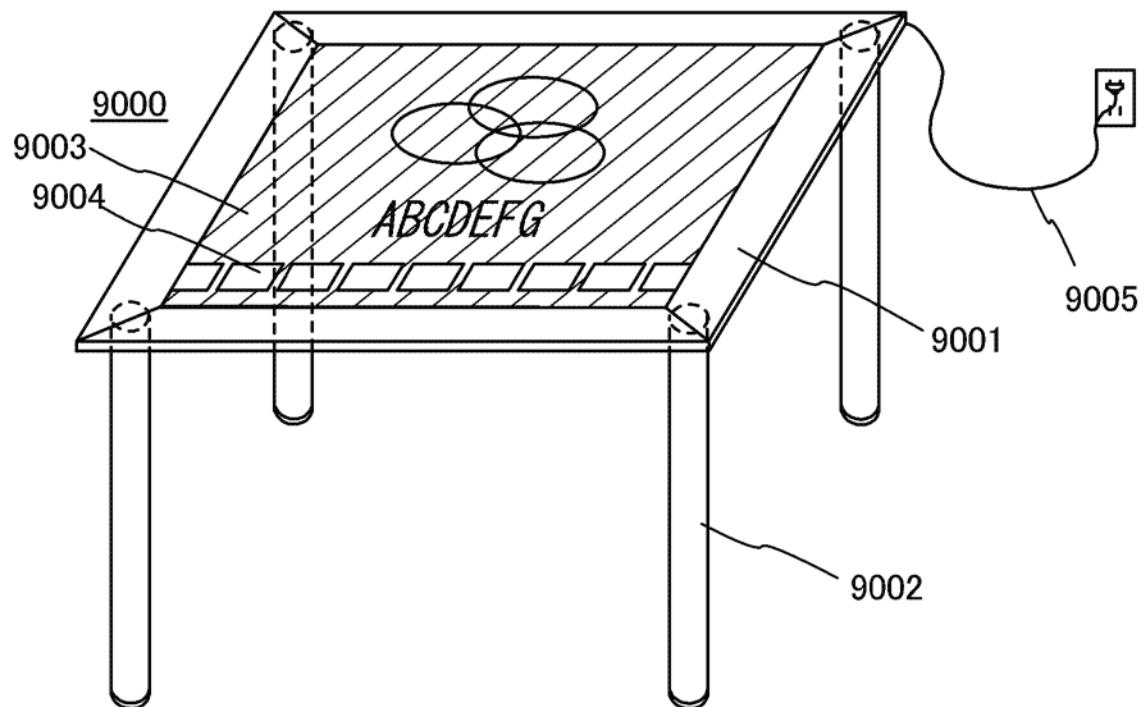

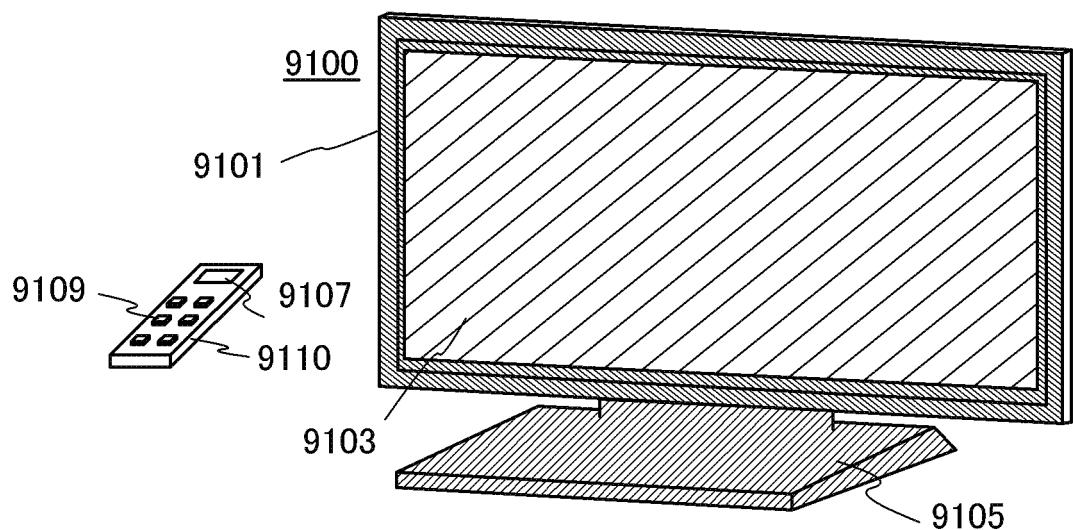

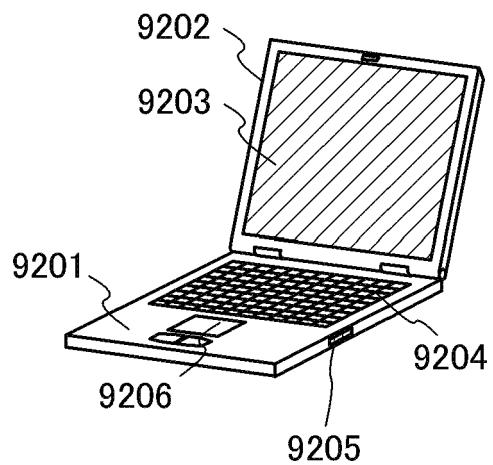

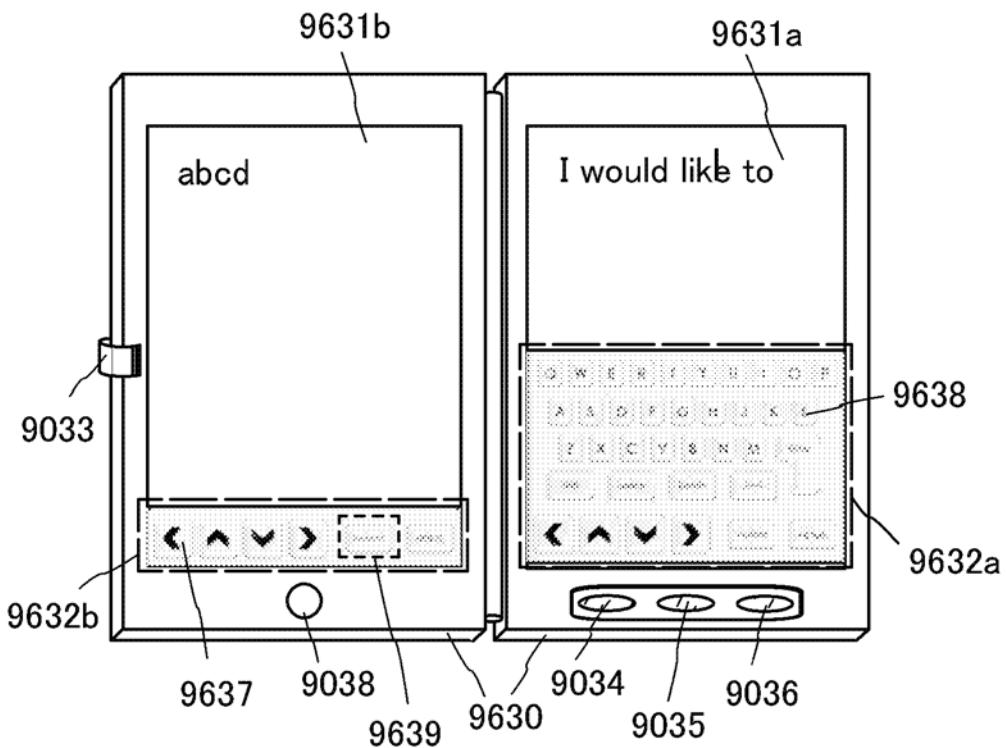

- [0031] 图9A至9C是示出电子设备的图；

- [0032] 图10A至10C是示出电子设备的图；

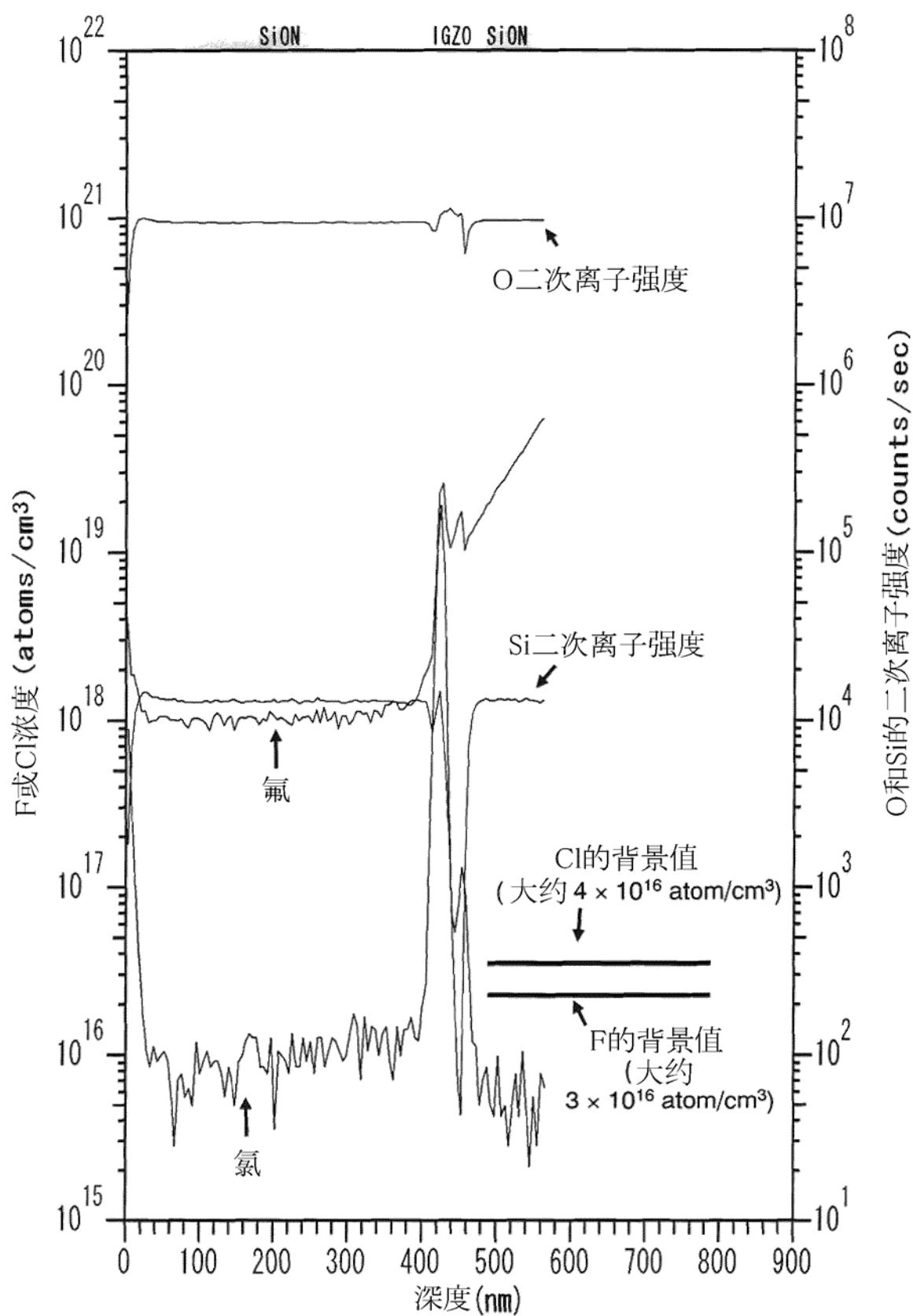

- [0033] 图11是示出SIMS测量结果的图；

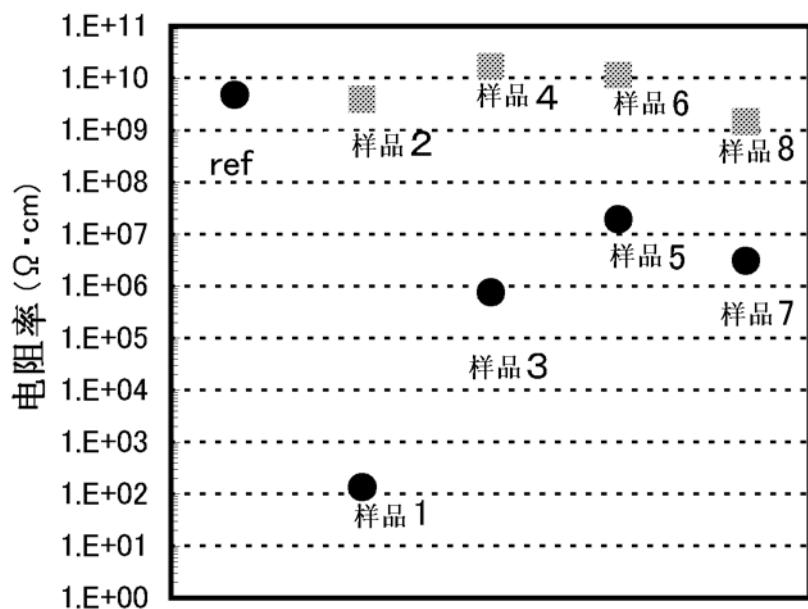

- [0034] 图12是示出稀氢氟酸处理的有无与电阻率的关系的图表；

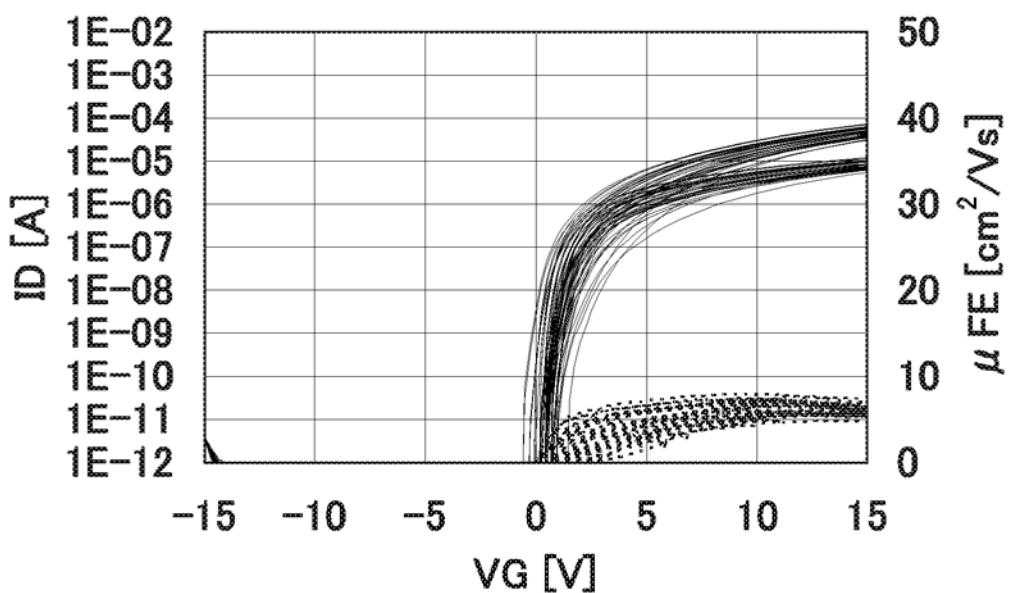

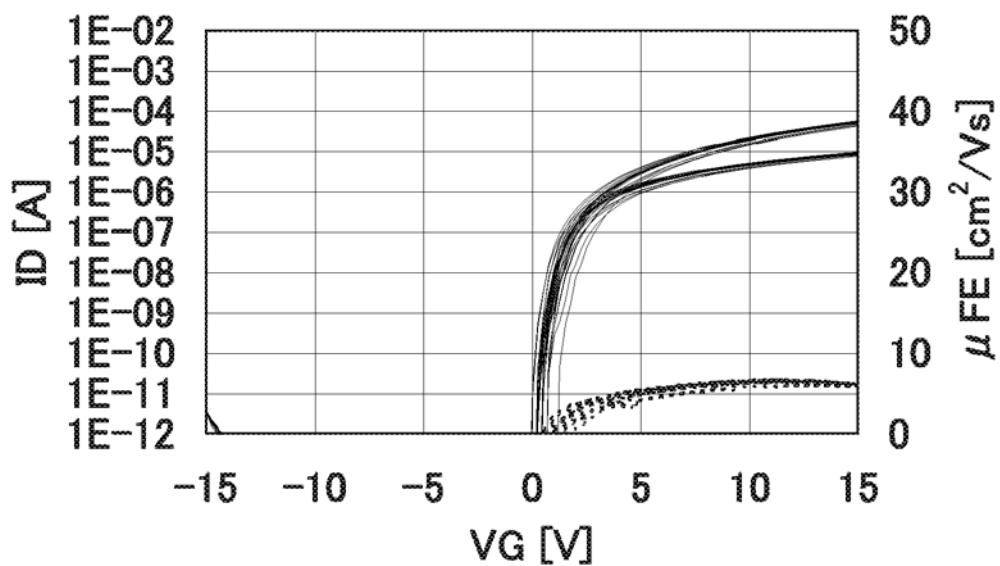

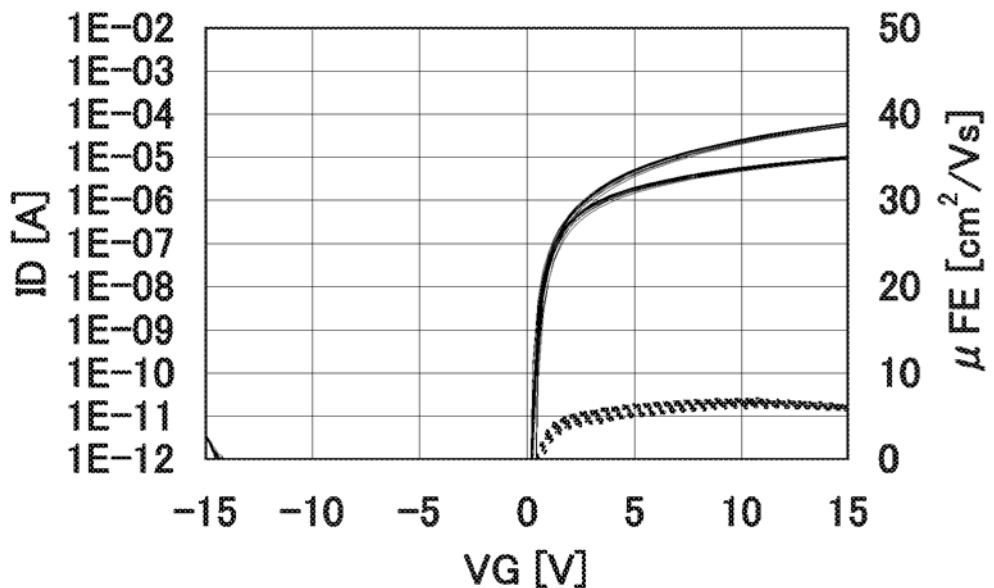

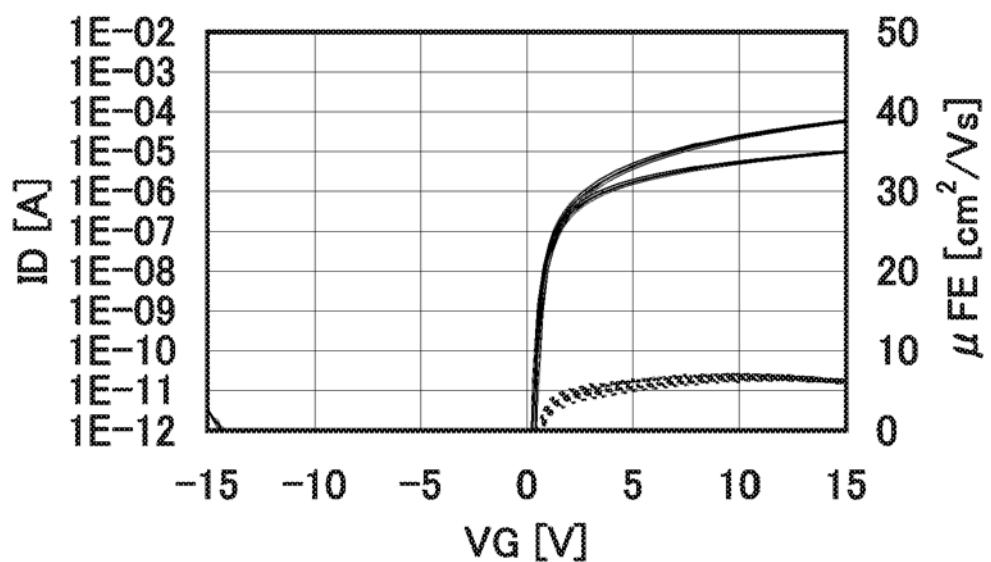

- [0035] 图13A和13B是示出样品A及样品B的电特性的图表；

- [0036] 图14A和14B是示出样品C及样品D的电特性的图表。

## 具体实施方式

[0037] 下面，参照附图详细地说明本说明书所公开的发明的实施方式。但是，所属技术领域的普通技术人员可以很容易地理解一个事实，就是本说明书所公开的发明的方式及详细内容可以被变换为各种各样的形式而不局限于以下说明。并且，本说明书所公开的发明不应被看作仅限定于以下实施方式的描述内容。另外，为了方便起见附加了第一、第二等序数词，其并不表示工序顺序或叠层顺序。此外，本说明书中的序数词不表示特定发明的事项的固有名称。

### [0038] 实施方式1

[0039] 在本实施方式中，参照图1A至1D以及图2A至2E说明半导体装置及半导体装置的制造方法的一个方式。在本实施方式中，作为半导体装置的一个例子示出具有氧化物半导体膜的晶体管。

[0040] 晶体管既可以采用形成一个沟道形成区的单栅结构，又可以采用形成两个沟道形成区的双栅结构(double-gate)，还可以采用形成三个沟道形成区的三栅结构。或者，也可以是具有隔着栅极绝缘膜配置在沟道形成区上下的两个栅电极层的双栅型。

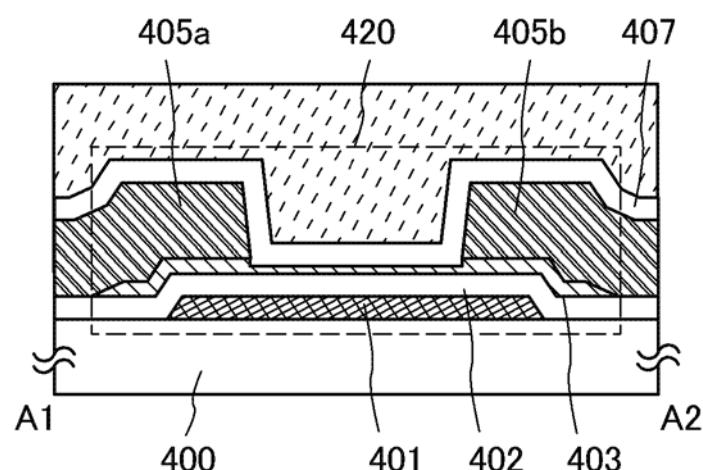

[0041] 图1A至1D所示的晶体管410示出为底栅结构的一种的也被称为反交错型晶体管的晶体管的一个例子。图1A是晶体管410的平面图，图1B是沿着图1A的A1-A2的截面图(沟道长度方向的截面图)，图1C是沿着图1A的B1-B2的截面图。另外，在图1A中，L表示沟道长度，W表示沟道宽度。注意，在图1A中，为了方便起见，省略晶体管410的构成要素的一部分(例如，栅极绝缘膜402等)而进行图示。

[0042] 如图1A至1D所示，具有晶体管410的半导体装置在具有绝缘表面的衬底400上包括：栅电极层401；栅极绝缘膜402；氧化物半导体膜403；源电极层405a及漏电极层405b。另外，还设置有覆盖晶体管410的绝缘膜407以及平坦化绝缘膜408。

[0043] 在图1A所示的晶体管410中，氧化物半导体膜403与绝缘膜407的界面的卤素元素浓度(例如，氯浓度)降至 $5 \times 10^{18} \text{ atom/cm}^3$ 以下，优选为 $1 \times 10^{18} \text{ atom/cm}^3$ 以下。由此，可以抑制晶体管的背沟道的低电阻化(n型化)，从而可以形成寄生沟道的形成得到抑制的晶体管410。由此，可以使晶体管410具有高可靠性。

[0044] 另外，如图1A及1C所示，在晶体管410中，源电极层405a及漏电极层405b覆盖氧化物半导体膜403的沟道宽度W方向的端部。通过采用该结构，在形成源电极层405a及漏电极

层405b时,可以防止氧化物半导体膜403的端部暴露于使用含有卤素元素的蚀刻气体的等离子体中。

[0045] 另外,在形成源电极层405a及漏电极层405b时,有时因氧化物半导体膜403的一部分被去除而形成具有槽部(凹部)的氧化物半导体膜403。另外,在形成源电极层405a及漏电极层405b之后进行杂质去除工序(后面详细说明)时,有时因氧化物半导体膜403的一部分被去除而形成具有槽部(凹部)的氧化物半导体膜403。此时,如图1D所示,形成包括具有槽部(凹部)的氧化物半导体膜403的晶体管420。另外,晶体管420的沟道宽度W方向的截面图(沿着图1A的B1-B2的截面图)与图1C相同。

[0046] 用作氧化物半导体膜403的氧化物半导体优选至少包含铟(In)。尤其是优选包含In及锌(Zn)。此外,作为用来降低使用该氧化物半导体膜的晶体管的电特性变化的稳定剂,除了上述元素以外优选还包含镓(Ga)。此外,作为稳定剂优选包含锡(Sn)。另外,作为稳定剂优选包含铪(Hf)。此外,作为稳定剂优选包含铝(Al)。另外,作为稳定剂优选包含锆(Zr)。

[0047] 此外,作为其他稳定剂,也可以包含镧系元素的镧(La)、铈(Ce)、镨(Pr)、钕(Nd)、钐(Sm)、铕(Eu)、钆(Gd)、铽(Tb)、镝(Dy)、钬(Ho)、铒(Er)、铥(Tm)、镱(Yb)、镥(Lu)中的一种或多种。

[0048] 例如,作为氧化物半导体可以使用氧化铟;氧化锡;氧化锌;In-Zn类氧化物、In-Mg类氧化物、In-Ga类氧化物;In-Ga-Zn类氧化物(也称为IGZO)、In-Al-Zn类氧化物、In-Sn-Zn类氧化物、In-Hf-Zn类氧化物、In-La-Zn类氧化物、In-Ce-Zn类氧化物、In-Pr-Zn类氧化物、In-Nd-Zn类氧化物、In-Sm-Zn类氧化物、In-Eu-Zn类氧化物、In-Gd-Zn类氧化物、In-Tb-Zn类氧化物、In-Dy-Zn类氧化物、In-Ho-Zn类氧化物、In-Er-Zn类氧化物、In-Tm-Zn类氧化物、In-Yb-Zn类氧化物、In-Lu-Zn类氧化物;以及In-Sn-Ga-Zn类氧化物、In-Hf-Ga-Zn类氧化物、In-Al-Ga-Zn类氧化物、In-Sn-Al-Zn类氧化物、In-Sn-Hf-Zn类氧化物、In-Hf-Al-Zn类氧化物。

[0049] 例如,“In-Ga-Zn类氧化物”是指以In、Ga、Zn为主要成分的氧化物,对In、Ga、Zn的比率没有限制。另外,也可以含有In、Ga、Zn以外的金属元素。

[0050] 另外,作为氧化物半导体,也可以使用表示为 $InM_0_3 (ZnO)_m$ ( $m > 0$ 且m不是整数)的材料。注意,M表示选自Ga、Fe、Mn和Co中的一种或多种金属元素。此外,作为氧化物半导体,也可以使用表示为 $In_2Sn_0_5 (ZnO)_n$ ( $n > 0$ 且n是整数)的材料。

[0051] 例如,可以使用原子数比为 $In:Ga:Zn = 1:1:1$ (=1/3:1/3:1/3)、 $In:Ga:Zn = 2:2:1$ (=2/5:2/5:1/5)、 $In:Ga:Zn = 3:1:2$ (=1/2:1/6:1/3)的In-Ga-Zn类氧化物或与其类似的组成的氧化物。另外,优选使用原子数比为 $In:Sn:Zn = 1:1:1$ (=1/3:1/3:1/3)、 $In:Sn:Zn = 2:1:3$ (=1/3:1/6:1/2)或 $In:Sn:Zn = 2:1:5$ (=1/4:1/8:5/8)的In-Sn-Zn类氧化物或与其类似的组成的氧化物。

[0052] 但是,含有铟的氧化物半导体不局限于此,可以根据所需要的半导体特性(迁移率、阈值、偏差等)而使用适当的组成的材料。另外,优选采用适当的载流子浓度、杂质浓度、缺陷密度、金属元素及氧的原子数比、原子问距离、密度等,以得到所需要的半导体特性。

[0053] 例如,在使用In-Sn-Zn氧化物的晶体管中比较容易得到高迁移率。但是,在使用In-Ga-Zn类氧化物的晶体管中也可以通过减小块内缺陷密度提高迁移率。

[0054] 例如,In、Ga、Zn的原子数比为 $In:Ga:Zn = a:b:c$ ( $a+b+c=1$ )的氧化物的组成与原

子数比为In:Ga:Zn=A:B:C (A+B+C=1) 的氧化物的组成类似是指a、b、c满足  $(a-A)^2 + (b-B)^2 + (c-C)^2 \leq r^2$  的状态, r例如可以为0.05。其他氧化物也是同样的。

[0055] 氧化物半导体膜403有可能处于单晶、多晶 (polycrystal) 或非晶等状态。

[0056] 氧化物半导体膜403优选为CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor: C轴取向结晶氧化物半导体) 膜。

[0057] CAAC-OS膜不是完全的单晶, 也不是完全的非晶。CAAC-OS膜是在非晶相中具有结晶部的结晶-非晶混合相结构的氧化物半导体膜。另外, 一般该结晶部分的尺寸为能够容纳于一个边长小于100nm的立方体内的尺寸。另外, 在使用透射电子显微镜 (TEM: Transmission Electron Microscope) 观察时的图像中, 包含于CAAC-OS膜中的非晶部与结晶部的边界不明确。另外, 在CAAC-OS膜中利用TEM观察不到晶界 (grain boundary)。因此, 在CAAC-OS膜中, 起因于晶界的电子迁移率的降低得到抑制。

[0058] 包含于CAAC-OS膜中的结晶部的c轴在平行于CAAC-OS膜的被形成面的法线向量或CAAC-OS膜的表面的法线向量的方向上一致, 在从垂直于ab面的方向看时具有三角形或六角形的原子排列, 且在从垂直于c轴的方向看时, 金属原子排列为层状或者金属原子和氧原子排列为层状。另外, 不同结晶部的a轴及b轴的方向也可以彼此不同。在本说明书中, 在只记载“垂直”时, 包括85°以上且95°以下的范围。另外, 当只记载“平行”时, 包括-5°以上且5°以下的范围。

[0059] 另外, 在CAAC-OS膜中, 结晶部的分布也可以不均匀。例如, 在CAAC-OS膜的形成过程中, 当从氧化物半导体膜的表面一侧进行结晶生长时, 有时与被形成面附近相比表面附近的结晶部所占的比例更高。另外, 通过对CAAC-OS膜添加杂质, 有时在该杂质添加区中结晶部发生非晶化。

[0060] 由于包含于CAAC-OS膜中的结晶部的c轴在平行于CAAC-OS膜的被形成面的法线向量或CAAC-OS膜的表面的法线向量的方向上一致, 所以有时其根据CAAC-OS膜的形状 (被形成面的截面形状或膜表面的截面形状) 而朝向不同的方向。另外, 结晶部的c轴方向是平行于形成CAAC-OS膜时的被形成面的法线向量或表面的法线向量的方向。结晶部是通过成膜或通过在成膜之后进行加热处理等的晶化处理而形成的。

[0061] 使用CAAC-OS膜的晶体管能够降低由可见光或紫外光的照射引起的电特性变动。因此, 该晶体管的可靠性高。

[0062] 另外, 也可以用氮取代构成氧化物半导体膜的氧的一部分。

[0063] 另外, 像CAAC-OS那样的具有结晶部的氧化物半导体可以进一步降低块体内缺陷, 通过提高表面的平坦性, 可以得到处于非晶状态的氧化物半导体的迁移率以上的迁移率。为了提高表面的平坦性, 优选在平坦的表面上形成氧化物半导体, 具体地, 优选在平均面粗糙度 (Ra) 为1nm以下, 优选为0.3nm以下, 更优选为0.1nm以下的表面上形成氧化物半导体。

[0064] 另外, Ra是将JIS B0601:2001 (ISO4287:1997) 中定义的算术平均粗糙度扩大为三维以使其能够应用于曲面, 可以以“将从基准面到指定面的偏差的绝对值平均而得的值”表示, 以如下算式定义。

$$[0065] Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

[0066] 这里, 指定面是指成为测量粗糙度对象的面, 并且是以坐标  $(x_1, y_1, f(x_1, y_1))$ 、 $(x_1,$

$y_2, f(x_1, y_2))$ 、 $(x_2, y_1, f(x_2, y_1))$  及  $(x_2, y_2, f(x_2, y_2))$  的四点表示的四角形的区域, 指定面投影在xy平面的长方形的面积为 $S_0$ , 基准面的高度(指定面的平均高度)为 $Z_0$ 。可以利用原子力显微镜(AFM:Atomic Force Microscope)测定 $R_a$ 。

[0067] 但是, 由于在本实施方式中说明的晶体管410为底栅晶体管, 所以在氧化物半导体膜的下方有衬底400、栅电极层401及栅极绝缘膜402。因此, 为了获得上述平坦的表面, 可以在形成栅电极层401及栅极绝缘膜402之后进行CMP处理等平坦化处理。

[0068] 将氧化物半导体膜403的厚度设定为1nm以上且30nm以下(优选为5nm以上且10nm以下), 可以适当地利用溅射法、MBE(Molecular Beam Epitaxy:分子束外延)法、CVD法、脉冲激光淀积法、ALD(Atomic Layer Deposition:原子层淀积)法等。此外, 氧化物半导体膜403可以使用在以大致垂直于溅射靶材表面的方式设置有多个衬底表面的状态下进行成膜的溅射装置形成。

[0069] 接着, 使用图2A至2E示出具有晶体管410的半导体装置的制造方法的一个例子。

[0070] 对可用作具有绝缘表面的衬底400的衬底没有很大的限制, 但是衬底400需要至少具有能够承受在后面进行的热处理的程度的耐热性。例如, 可以使用如硼硅酸钡玻璃和硼硅酸铝玻璃等的玻璃衬底、陶瓷衬底、石英衬底、蓝宝石衬底等。另外, 作为衬底400, 也可以采用以硅或碳化硅等为材料的单晶半导体衬底或多晶半导体衬底、以硅锗等为材料的化合物半导体衬底、SOI衬底等, 还可以使用在这些衬底上设置有半导体元件的衬底。

[0071] 此外, 作为衬底400也可以使用柔性衬底制造半导体装置。在制造具有柔性的半导体装置时, 既可以在柔性衬底上直接形成包含氧化物半导体膜403的晶体管410, 也可以在其他制造衬底上形成包含氧化物半导体膜403的晶体管410, 然后从制造衬底将其剥离并转置到柔性衬底上。注意, 为了从制造衬底剥离晶体管并转置到柔性衬底上, 优选在制造衬底与包含氧化物半导体膜的晶体管410之间设置剥离层。

[0072] 也可以在衬底400上设置绝缘膜作为基底膜。作为绝缘膜, 可以通过等离子体CVD法或溅射法等并使用如下材料形成: 氧化硅、氧氮化硅、氧化铝、氧氮化铝、氧化铪、氧化镓等氧化物绝缘材料; 氮化硅、氮氧化硅、氮化铝、氮氧化铝等氮化绝缘材料; 它们的混合材料。

[0073] 可以对衬底400(或衬底400及绝缘膜)进行加热处理。例如, 可以使用利用高温气体进行加热处理的GRTA(Gas Rapid Thermal Anneal; 气体快速热退火)装置以650°C进行1分至5分的加热处理。另外, 作为GRTA的高温气体使用如氩等的稀有气体或氮那样的即使进行加热处理也不与被处理物产生反应的惰性气体。另外, 也可以利用电炉以500°C进行30分至1小时的加热处理。

[0074] 接着, 在衬底400上形成成为栅电极层(包括使用与其相同的层形成的布线)的导电膜。导电膜可以使用钼、钛、钽、钨、铝、铜、铬、钕、钪等的金属材料或以这些材料为主要成分的合金材料形成。此外, 作为导电膜, 可以使用以掺杂有磷等杂质元素的多晶硅膜为代表的半导体膜、镍硅化物等硅化物膜。导电膜既可以是单层结构, 又可以是叠层结构。

[0075] 另外, 导电膜可以使用氧化铟-氧化锡、包含氧化钨的铟氧化物、包含氧化钨的铟锌氧化物、包含氧化钛的铟氧化物、包含氧化钛的铟锡氧化物、氧化铟-氧化锌以及添加有氧化硅的铟锡氧化物等导电材料。此外, 也可以采用上述导电材料与上述金属材料的叠层结构。

[0076] 此外,作为与栅极绝缘膜402接触的导电膜,可以使用包含氮的金属氧化物,具体地说,包含氮的In-Ga-Zn-O膜、包含氮的In-Sn-O膜、包含氮的In-Ga-O膜、包含氮的In-Zn-O膜、包含氮的Sn-O膜、包含氮的In-O膜以及金属氮化膜(InN、SnN等)。这些膜具有5eV(电子伏特)以上,优选具有5.5eV(电子伏特)以上的功函数,并且当将它们用作栅电极层时,可以使晶体管的电特性的阈值电压成为正值,而可以实现所谓的常关闭型(normally off)的开关元件。

[0077] 在本实施方式中,利用溅射法形成100nm厚的钨膜。

[0078] 接着,利用光刻工序在导电膜上形成抗蚀剂掩模,并通过选择性的蚀刻形成栅电极层401。在形成栅电极层401之后,去除抗蚀剂掩模。作为导电膜的蚀刻,可以使用干蚀刻和湿蚀刻中的一方或双方。

[0079] 另外,可以在形成栅电极层401之后对衬底400及栅电极层401进行加热处理。例如,可以利用GRTA装置以650℃进行1分至5分的加热处理。或者,利用电炉以500℃进行30分至1小时的加热处理。

[0080] 接着,在栅电极层401上形成栅极绝缘膜402。

[0081] 另外,为了提高栅极绝缘膜402的覆盖性,可以对栅电极层401的表面进行平坦化处理。尤其是当作为栅极绝缘膜402使用厚度较薄的绝缘膜时,优选栅电极层401表面具有良好的平坦性。

[0082] 将栅极绝缘膜402的厚度设定为1nm以上20nm以下,并可以适当地利用溅射法、MBE法、CVD法、PECVD法、脉冲激光淀积法、ALD法等。此外,栅极绝缘膜402也可以使用在以大致垂直于溅射靶材表面的方式设置有多个衬底表面的状态下进行成膜的溅射装置形成。

[0083] 栅极绝缘膜402可以使用如下材料形成:氧化硅;氧化镓;氧化铝;氮化硅;氧氮化硅;氧氮化铝;氮氧化硅。此外,通过作为栅极绝缘膜402的材料使用氧化铪、氧化钇、硅酸铪(HfSi<sub>x</sub>O<sub>y</sub> (x>0, y>0))、添加有氮的硅酸铪(HfSiO<sub>x</sub>N<sub>y</sub> (x>0, y>0))、铝酸铪(HfAl<sub>x</sub>O<sub>y</sub> (x>0, y>0))以及氧化镧等high-k材料,可以降低栅极泄漏电流。另外,栅极绝缘膜402可以使用上述材料形成单层结构或叠层结构。

[0084] 优选栅极绝缘膜402的与氧化物半导体膜403接触的部分含有氧。尤其是,优选栅极绝缘膜402的膜中(块体中)至少含有超过化学计量组成比的量的氧。例如,当将氧化硅膜用于栅极绝缘膜402时,组成通式为SiO<sub>2+a</sub>(注意,a>0)。

[0085] 通过以接触于氧化物半导体膜403的方式形成成为氧的供应源的包含多量的(过剩的)氧的栅极绝缘膜402,可以从该栅极绝缘膜402对氧化物半导体膜403供应氧。也可以通过在氧化物半导体膜403与栅极绝缘膜402至少部分接触的状态下进行加热处理来对氧化物半导体膜403供应氧。

[0086] 通过对氧化物半导体膜403供应氧,可以填补膜中的氧缺陷。再者,优选考虑到所制造的晶体管的尺寸和栅极绝缘膜402的台阶覆盖性而形成栅极绝缘膜402。

[0087] 在本实施方式中,通过高密度等离子体CVD法形成200nm厚的氧氮化硅膜。

[0088] 或者,可以在形成栅极绝缘膜402之后对衬底400、栅电极层401、及栅极绝缘膜402进行加热处理。例如,可以利用GRTA装置以650℃进行1分至5分的加热处理。或者,利用电炉以500℃进行30分至1小时的加热处理。

[0089] 接着,在栅极绝缘膜402上形成氧化物半导体膜403(参照图2A)。

[0090] 在形成氧化物半导体膜403的工序中,为了尽量不使氧化物半导体膜403包含氢或水,优选作为形成氧化物半导体膜403的预处理,在溅射装置的预热室中对形成有栅极绝缘膜402的衬底进行预热,使附着于衬底及栅极绝缘膜402的氢或水分等杂质脱离而排出。另外,作为设置在预热室中的排气单元优选使用低温泵。

[0091] 也可以对栅极绝缘膜402中的与氧化物半导体膜403接触的区域进行平坦化处理。对平坦化处理没有特别的限制,而作为平坦化处理可以使用抛光处理(例如,化学机械抛光(Chemical Mechanical Polishing: CMP)法)、干蚀刻处理及等离子体处理。

[0092] 作为等离子体处理,例如可以进行引入氩气来产生等离子体的反溅射。反溅射是指使用RF电源在氩气氛下对衬底一侧施加电压,来在衬底附近形成等离子体以进行表面改性的方法。另外,也可以使用氮、氦、氧等代替氩气氛。通过进行反溅射,可以去除附着于栅极绝缘膜402表面的粉状物质(也称为微粒、尘屑)。

[0093] 作为平坦化处理,既可以多次进行抛光处理、干蚀刻处理及等离子体处理,又可以组合上述处理而进行。此外,当组合上述处理而进行时,对工序顺序也没有特别的限制,可以根据栅极绝缘膜402表面的凹凸状态适当地设定。

[0094] 此外,优选在成膜时包含多量的氧的条件(例如,在氧比率为100%的气氛下利用溅射法进行成膜等)下形成氧化物半导体膜403,使其成为包含多量的氧(优选为包含与氧化物半导体处于结晶状态时的化学计量组成相比氧含量过剩的区域)的膜。

[0095] 另外,在本实施方式中,作为氧化物半导体膜403通过利用装有AC电源的溅射装置的溅射法形成35nm厚的In-Ga-Zn类氧化物膜(IGZO膜)。在本实施方式中,使用原子数比为In:Ga:Zn=1:1:1(1/3:1/3:1/3)的In-Ga-Zn类氧化物靶材。另外,成膜条件如下:氧及氩气氛下(氧流量比率为50%);压力为0.6Pa;电源功率为5kW;衬底温度为170℃。该成膜条件下的成膜速度为16nm/min。

[0096] 作为形成氧化物半导体膜403时使用的溅射气体,优选使用去除了氢、水、羟基或氢化物等杂质的高纯度气体。

[0097] 在保持为减压状态的成膜室中保持衬底。然后,在去除成膜室内的残留水分的同时引入去除了氢和水分的溅射气体,使用上述靶材在衬底400上形成氧化物半导体膜403。为了去除成膜室内的残留水分,优选使用吸附型的真空泵,例如低温泵、离子泵、钛升华泵。此外,作为排气单元,也可以使用添加有冷阱的涡轮泵。因为在使用低温泵进行排气的成膜室中,例如氢原子、水(H<sub>2</sub>O)等包含氢原子的化合物等被排出(更优选的是,包含碳原子的化合物也被排出),所以可以降低包含在该成膜室中形成的氧化物半导体膜403中的氢、水、羟基或氢化物等杂质的浓度。

[0098] 另外,优选以不使栅极绝缘膜402暴露于大气的方式连续形成栅极绝缘膜402和氧化物半导体膜403。通过以不使栅极绝缘膜402暴露于大气的方式连续形成栅极绝缘膜402和氧化物半导体膜403,可以防止氢或水分等杂质附着于栅极绝缘膜402表面。

[0099] 通过对膜状的氧化物半导体膜进行光刻工序而加工为岛状可以形成氧化物半导体膜403。

[0100] 另外,也可以通过喷墨法形成用来形成岛状的氧化物半导体膜403的抗蚀剂掩模。在通过喷墨法形成抗蚀剂掩模时不需要光掩模,由此可以降低制造成本。

[0101] 另外,氧化物半导体膜的蚀刻可以采用干蚀刻和湿蚀刻中的一方或双方。例如,作

为用于氧化物半导体膜的湿蚀刻的蚀刻剂,可以使用混合有磷酸、醋酸及硝酸的溶液等。此外,也可以使用ITO-07N(由日本关东化学株式会社制造)。另外,也可以通过利用ICP(Inductively Coupled Plasma:感应耦合等离子体)蚀刻法的干蚀刻进行蚀刻加工。

[0102] 另外,也可以对氧化物半导体膜403进行用来去除过剩的氢(包括水或羟基)(脱水化或脱氢化)的加热处理。将加热处理的温度设定为300℃以上且700℃以下或低于衬底的应变点。加热处理可以在减压下或氮气氛下等进行。

[0103] 另外,当作为氧化物半导体膜403使用结晶氧化物半导体膜时,也可以进行用于晶化的加热处理。

[0104] 在本实施方式中,将衬底引入到加热处理装置之一的电炉中,在氮气氛下以450℃对氧化物半导体膜403进行1小时的加热处理,并且在氮及氧气氛下以450℃对其进行1小时的加热处理。

[0105] 另外,加热处理装置不局限于电炉,也可以使用利用电阻发热体等的发热体所产生的热传导或热辐射对被处理物进行加热的装置。例如,可以使用GRTA(Gas Rapid Thermal Anneal:气体快速热退火)装置、LRTA(Lamp Rapid Thermal Anneal:灯快速热退火)装置等RTA(Rapid Thermal Anneal:快速热退火)装置。LRTA装置是通过利用从卤素灯、金卤灯、氙弧灯、碳弧灯、高压钠灯或者高压汞灯等的灯发射的光(电磁波)的辐射来加热被处理物的装置。GRTA装置是使用高温气体进行加热处理的装置。作为高温的气体,使用氩等稀有气体或氮等不因加热处理而与被处理物发生反应的惰性气体。

[0106] 例如,作为加热处理,也可以进行如下GRTA,即将衬底放入加热为650℃至700℃的高温的惰性气体中,在加热几分钟之后,将衬底从惰性气体中取出。

[0107] 另外,在加热处理中,氮或氩、氖、氙等稀有气体优选不包含水、氢等。另外,优选将引入到加热处理装置中的氮或氩、氖、氙等稀有气体的纯度设定为6N(99.9999%)以上,优选设定为7N(99.99999%)以上(即,将杂质浓度设定为1ppm以下,优选设定为0.1ppm以下)。

[0108] 此外,也可以在通过加热处理加热氧化物半导体膜403之后,对相同的炉中引入高纯度的氧气体、高纯度的一氧化二氮气体或超干燥空气(使用CRDS(cavity ring-down laser spectroscopy:光腔衰荡光谱法)方式的露点仪进行测定时的水分量是20ppm(露点换算,-55℃)以下,优选的是1ppm以下,更优选的是10ppb以下的空气)。氧气体或一氧化二氮气体优选不包含水、氢等。或者,优选将引入加热处理装置中的氧气体或一氧化二氮气体的纯度设定为6N以上,优选设定为7N以上(即,将氧气体或一氧化二氮气体中的杂质浓度设定为1ppm以下,优选设定为0.1ppm以下)。通过利用氧气体或一氧化二氮气体的作用来供应利用脱水化或脱氢化处理进行杂质排除工序的同时减少的氧化物半导体的主要成分材料的氧,可以使氧化物半导体膜403高纯度化及i型(本征)化。

[0109] 另外,用来脱水化或脱氢化的加热处理既可以在形成膜状的氧化物半导体膜之后进行,又可以在形成岛状的氧化物半导体膜403之后进行。

[0110] 另外,用来脱水化或脱氢化的加热处理既可以进行多次,又可以兼作其他加热处理。

[0111] 通过在将氧化物半导体膜加工为岛状的氧化物半导体膜403之前且在膜状的氧化物半导体膜覆盖栅极绝缘膜402的状态下进行用来脱水化或脱氢化的加热处理,可以防止因加热处理而释放包含在栅极绝缘膜402中的氧,所以是优选的。

[0112] 另外,也可以对经过脱水化或脱氢化处理的氧化物半导体膜403引入氧(至少包含氧自由基、氧原子和氧离子中的任何一个)来对其供应氧。

[0113] 此外,由于脱水化或脱氢化处理,有可能构成氧化物半导体的主要成分材料的氧也同时发生脱离而减少。在氧脱离的部分中存在氧缺陷,并且因该氧缺陷而产生导致晶体管的电特性变动的施主能级。

[0114] 因此,优选对经过脱水化或脱氢化处理的氧化物半导体膜供应提供氧(至少包含氧自由基、氧原子和氧离子中的任一种)。通过对氧化物半导体膜供应氧,可以填补膜中的氧缺陷。

[0115] 通过对经过脱水化或脱氢化处理的氧化物半导体膜403引入氧而对其供应氧,可以使氧化物半导体膜403高纯度化且i型(本征)化。具有高纯度化且i型(本征)化的氧化物半导体膜403的晶体管的电特性变动被抑制,所以该晶体管在电性上稳定。

[0116] 作为氧的引入方法,可以使用离子注入法、离子掺杂法、等离子体浸没式离子注入法、等离子体处理等。

[0117] 当对氧化物半导体膜403引入氧时,既可以对氧化物半导体膜403直接引入氧,也可以透过后面形成的绝缘膜407等其他膜对氧化物半导体膜403引入氧。当透过其他膜引入氧时,使用离子注入法、离子掺杂法、等离子体浸没式离子注入法等即可,但是当对被露出的氧化物半导体膜403直接引入氧时,也可以使用等离子体处理等。

[0118] 优选在进行脱水化或脱氢化处理之后对氧化物半导体膜403引入氧,但是不局限于此。此外,也可以多次进行对经过上述脱水化或脱氢化处理的氧化物半导体膜403的氧的引入。

[0119] 优选设置于晶体管中的氧化物半导体膜包含与氧化物半导体处于结晶状态时的化学计量组成相比氧含量过剩的区域。在此情况下,氧含量超过氧化物半导体的化学计量组成。或者,氧含量超过氧化物半导体处于单晶时的氧含量。有时在氧化物半导体的晶格之间存在氧。

[0120] 通过去除氧化物半导体中的氢或水分来使其尽量不包含杂质而高纯度化,并通过对其供应氧来填补氧缺陷,可以形成i型(本征)的氧化物半导体或无限趋近于i型(本征)的氧化物半导体。由此,可以使氧化物半导体的费米能级(Ef)达到与本征费米能级(Ei)相同程度。因此,通过将该氧化物半导体膜用于晶体管,可以降低起因于氧缺陷的晶体管的阈值电压Vth的偏差、阈值电压的偏移ΔVth。

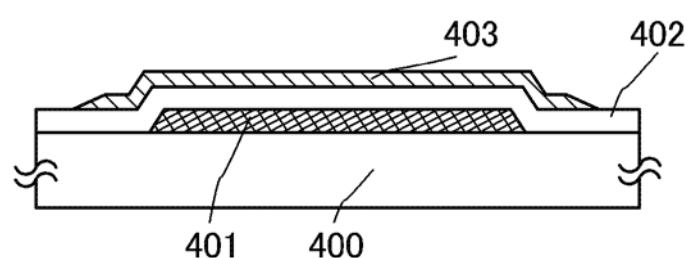

[0121] 接着,在栅电极层401、栅极绝缘膜402及氧化物半导体膜403上形成成为源电极层和漏电极层(包括由与此相同的层形成的布线)的导电膜445(参照图2B)。

[0122] 作为该导电膜445,使用能够承受在后面进行的加热处理的材料。作为用于源电极层及漏电极层的导电膜445,例如可以使用含有选自铝(Al)、铬(Cr)、铜(Cu)、钽(Ta)、钛(Ti)、钼(Mo)、钨(W)中的元素的金属膜或以上述元素为成分的金属氮化物膜(氮化钛膜、氮化钼膜、氮化钨膜)等。此外,还可以采用在Al、Cu等的金属膜的下侧和上侧的一方或双方层叠Ti、Mo、W等高熔点金属膜或它们的金属氮化物膜(氮化钛膜、氮化钼膜、氮化钨膜)的结构。另外,作为用于源电极层及漏电极层的导电膜445,也可以使用导电金属氧化物。作为导电金属氧化物,可以使用氧化铟(In<sub>2</sub>O<sub>3</sub>)、氧化锡(SnO<sub>2</sub>)、氧化锌(ZnO)、氧化铟-氧化锡(In<sub>2</sub>O<sub>3</sub>-SnO<sub>2</sub>,简称为ITO)、氧化铟-氧化锌(In<sub>2</sub>O<sub>3</sub>-ZnO)或使它们的金属氧化物材料包含氧化

硅的材料。

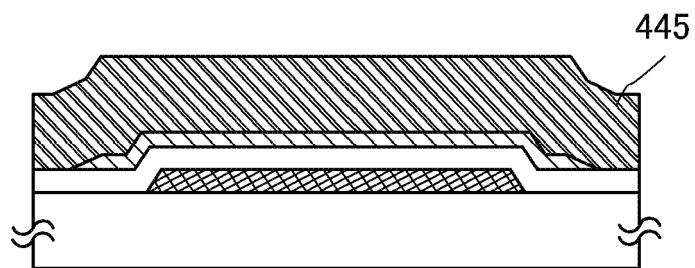

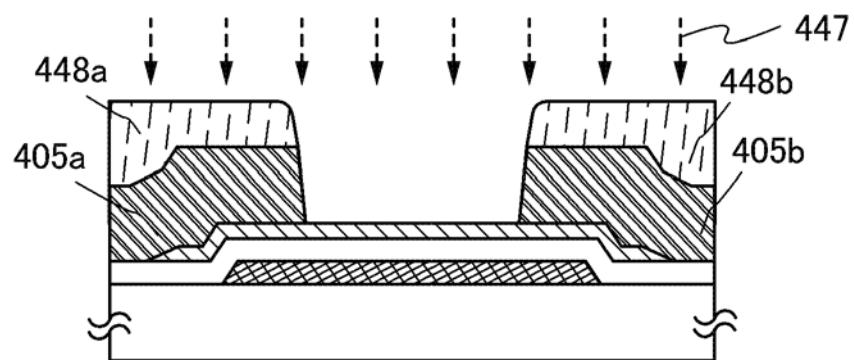

[0123] 通过光刻工序在导电膜445上形成抗蚀剂掩模448a及抗蚀剂掩模448b,并且选择性地进行蚀刻来形成源电极层405a及漏电极层405b(参照图2C)。在形成源电极层405a及漏电极层405b之后去除抗蚀剂掩模448a、448b。

[0124] 作为形成该抗蚀剂掩模448a、448b时的曝光,优选使用紫外线、KrF激光、ArF激光等。后面形成的晶体管410的沟道长度L取决于在氧化物半导体膜403上相邻的源电极层405a的下端部与漏电极层405b的下端部之间的间隔宽度。另外,当进行曝光以使沟道长度L短于25nm时,可以使用波长极短,即,几nm至几十nm的超紫外线(Extreme Ultraviolet)进行形成抗蚀剂掩模448a、448b时的曝光。利用超紫外线的曝光的分辨率高且景深大。因此,也可以将后面形成的晶体管的沟道长度L设定为10nm以上且1000nm以下,由此可以实现电路的工作速度的高速化。

[0125] 此外,为了缩减用于光刻工序的光掩模数及工序数,也可以使用通过透过的光成为多种强度的曝光掩模的多级灰度掩模形成的抗蚀剂掩模进行蚀刻工序。由于使用多级灰度掩模形成的抗蚀剂掩模成为具有多种厚度的形状,且通过进行蚀刻进一步改变形状,因此可以用于加工为不同图案的多个蚀刻工序。由此,可以使用一个多级灰度掩模形成至少对应于两种以上的不同图案的抗蚀剂掩模。由此,可以缩减曝光掩模数,并还可以缩减与其对应的光刻工序,从而可以实现工序的简化。

[0126] 在本实施方式中,在导电膜445的蚀刻中,使用含有卤素元素的气体447。作为含有卤素元素的气体447,可以使用含有氯的气体,例如,可以使用含有氯(Cl<sub>2</sub>)、三氯化硼(BCl<sub>3</sub>)、四氯化硅(SiCl<sub>4</sub>)、四氯化碳(CC<sub>4</sub>)等的气体。另外,作为含有卤素元素的气体447,可以使用含有氟的气体,例如,含有四氟化碳(CF<sub>4</sub>)、六氟化硫(SF<sub>6</sub>)、三氟化氮(NF<sub>3</sub>)、或三氟甲烷(CHF<sub>3</sub>)等的气体。或者,对上述气体添加了氦(He)、氩(Ar)等的稀有气体的气体等。

[0127] 作为蚀刻方式,可以使用平行平板型RIE(Reactive Ion Etching,反应离子蚀刻)法或ICP(Inductively Coupled Plasma:感应耦合等离子体)蚀刻法。适当地调节蚀刻条件(施加到线圈型电极的电力量、施加到衬底一侧的电极的电力量、衬底一侧的电极温度等),以便能够蚀刻为所希望的加工形状。

[0128] 在本实施方式中,作为导电膜445使用通过溅射法形成的100nm厚的钛膜、400nm厚的铝膜及100nm厚的钛膜的叠层。作为导电膜445的蚀刻,利用干蚀刻法对钛膜、铝膜及钛膜的叠层进行蚀刻来形成源电极层405a及漏电极层405b。

[0129] 在本实施方式中,在以第一蚀刻条件对上层的钛膜及铝膜的两层进行蚀刻之后,以第二蚀刻条件去除残留的下层的钛膜。注意,第一蚀刻条件为:利用蚀刻气体(BCl<sub>3</sub>:Cl<sub>2</sub>=750sccm:150sccm);偏压功率为1500W;ICP电源功率为0W;压力为2.0Pa。第二蚀刻条件为:利用蚀刻气体(BCl<sub>3</sub>:Cl<sub>2</sub>=700sccm:100sccm);偏压功率为750W;ICP电源功率为0W;压力为2.0Pa。

[0130] 另外,优选的是,当对导电膜445进行蚀刻工序时,使导电膜445的蚀刻条件最适化以防止氧化物半导体膜403被蚀刻而消失或断开。但是,由于很难仅对导电膜445进行蚀刻而完全不使氧化物半导体膜403被蚀刻,因此有时当对导电膜445进行蚀刻时氧化物半导体膜403被部分蚀刻,氧化物半导体膜403成为具有槽部(凹部)的氧化物半导体膜。

[0131] 在用来形成源电极层405a及漏电极层405b的蚀刻工序中,当采用含有卤素元素的

蚀刻气体时,当氧化物半导体膜403暴露于该蚀刻气体中时,由于包含于该蚀刻气体中的卤素元素(例如,氯、氟)氧化物半导体膜403中的氧被抽出,而有可能导致氧化物半导体膜403的表面形成氧缺陷。另外,在蚀刻工序之后,由于氧化物半导体膜403表面及其附近残留有包含于该蚀刻气体中的卤素元素,有可能导致氧化物半导体膜403中形成氧缺陷。如此,当氧化物半导体膜403中发生氧缺陷时,导致氧化物半导体膜403的背沟道低电阻化(n型化),而有可能形成寄生沟道。

[0132] 例如,当作为氧化物半导体膜403使用含有铟的氧化物半导体材料,并且在以接触于氧化物半导体膜的方式设置的源电极层及漏电极层的加工中使用含有三氯化硼( $BCl_3$ )的蚀刻气体时,有时氧化物半导体膜中的In-O-In键与蚀刻气体中的Cl发生反应而变成包含In-Cl键和氧脱离了的In元素的膜。由于氧脱离了的In元素具有悬空键,因此在氧化物半导体膜中发生氧脱离的部分中存在氧缺陷。

[0133] 另外,由于含有卤素元素的蚀刻气体中还含有卤素元素之外的元素(例如,硼),而也可能成为导致氧化物半导体膜的背沟道低电阻化(n型化)的主要原因之一。

[0134] 在本实施方式中,由于在形成源电极层405a及漏电极层405b的蚀刻工序中采用含有卤素元素的气体447,因此生成的杂质为卤素(在本实施方式中为氯)类杂质(卤素元素或含有卤素元素的化合物)。另外,如本实施方式所示,当含有卤素元素的气体447中含有硼时,作为生成的杂质还包括硼或含有硼的化合物。

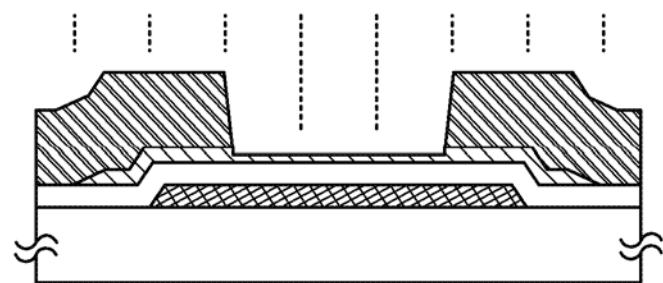

[0135] 因此,在形成源电极层405a及漏电极层405b之后,进行去除存在于氧化物半导体膜403表面及其附近的杂质的工序(参照图2D)。作为杂质去除工序,优选利用:使用氧、一氧化二氮或稀有气体(典型的有氩)的等离子体处理;或者使用稀释氢氟酸、水、显影液或TMAH溶液的溶液处理等。另外,作为稀释氢氟酸,例如,当使用 $1/10^3$ 稀释氢氟酸(氢氟酸:0.05%)对IGZO膜进行处理时,1秒钟膜厚度减少1nm至3nm,当使用 $2/10^5$ 稀释氢氟酸(氢氟酸:0.0025%)对IGZO膜进行处理时,1秒钟膜厚度减少0.1nm左右。通过对氧化物半导体膜403进行杂质去除处理,可使氧化物半导体膜403表面的氯浓度降低至 $5 \times 10^{18} \text{ atom/cm}^3$ 以下,优选为 $1 \times 10^{18} \text{ atom/cm}^3$ 以下。在本实施方式中,示出作为杂质去除工序进行使用一氧化二氮的等离子体处理的例子。

[0136] 通过上述工序,可以制造根据本实施方式的晶体管410(参照图2E)。

[0137] 在本实施方式中,在源电极层405a及漏电极层405b上以与氧化物半导体膜403接触的方式形成用作保护绝缘膜的绝缘膜407。

[0138] 作为绝缘膜407,至少将其厚度形成为1nm以上,并可以适当地采用溅射法等的不使水、氢等的杂质混入到膜中的方法形成。当绝缘膜407包含氢时,有如下忧虑:因氢侵入到氧化物半导体膜403或者氢抽出氧化物半导体膜403中的氧而使氧化物半导体膜的背沟道低电阻化(n型化),而形成寄生沟道。因此,为了使绝缘膜407成为尽量不包含氢的膜,在成膜方法中不使用氢是十分重要的。

[0139] 作为绝缘膜407,典型地可以使用氧化硅、氧氮化硅、氧化铝、氧氮化铝、氧化铪、氧化镓、氮化硅、氮化铝、氮氧化铝等的无机绝缘膜的单层或叠层。

[0140] 因此,当作为脱水化或脱氢化处理进行加热工序时,优选对氧化物半导体膜403供应氧。通过对氧化物半导体膜403供应氧,可以填充膜中的氧缺陷。

[0141] 在本实施方式中,以绝缘膜407为供应源对氧化物半导体膜403供应氧,因此示出

绝缘膜407为含有氧的氧化物绝缘膜(例如,氧化硅膜、氧氮化硅膜)的例子。当以绝缘膜407为氧供应源时,优选绝缘膜407为包含较多(过剩)氧的膜(优选为包括包含与氧化物半导体处于结晶状态时的化学计量组成相比氧含量过剩的区域的膜),由此可以有效地发挥氧供应源的作用。

[0142] 在本实施方式中,作为绝缘膜407利用溅射法形成厚度为300nm的氧化硅膜。将成膜时的衬底温度设定为室温以上300℃以下,即可。在本实施方式中设定为100℃。可以在稀有气体(典型的是氩)气氛下、氧气气氛下或稀有气体和氧的混合气氛下,利用溅射法形成氧化硅膜。此外,作为靶材,可以使用氧化硅靶材或硅靶材。例如,使用硅靶子在含有氧气的气氛中利用溅射法形成氧化硅膜。

[0143] 与形成氧化物半导体膜403时同样,为了去除残留在绝缘膜407的成膜室内的水分,优选使用吸附型的真空泵(低温泵等)。可以降低在使用低温泵排气的成膜室中形成的绝缘膜407所包含的杂质的浓度。此外,作为用来去除残留在绝缘膜407的成膜室内的水分的排气装置,也可以采用配备有冷阱的涡轮分子泵。

[0144] 作为当形成绝缘膜407时使用的溅射气体,优选使用去除了氢、水等杂质的高纯度气体。

[0145] 接着,在其一部分(沟道形成区)接触于绝缘膜407的状态下,对氧化物半导体膜403进行加热工序。

[0146] 将加热工序的温度设定为250℃以上700℃以下,或者设定为400℃以上700℃以下,或者设定为低于衬底的应变点。例如,将衬底放进加热处理装置之一种的电炉中,在氮气气氛下以250℃对氧化物半导体膜进行一小时的加热工序。

[0147] 该加热工序可以使用与进行脱水化或脱氢化处理的加热工序相同的加热方法及加热装置。

[0148] 在减压、氮、氧、超干燥空气(使用CRDS(cavity ring-down laser spectroscopy:光腔衰荡光谱法)方式的露点仪来测定时的水分量为20ppm(露点换算为-55℃)以下,优选为1ppm以下,更优选为10ppb以下的空气)、或者稀有气体(氩、氦等)的气氛下进行加热工序,即可。但是,上述氮、氧、超干燥空气、稀有气体等的气氛优选不包含水、氢等。此外,优选将引入到加热处理装置中的氮、氧、稀有气体的纯度设定为6N(99.9999%)以上,优选设定为7N(99.99999%)以上(即,将杂质浓度设定为1ppm以下,优选设定为0.1ppm以下)。

[0149] 此外,因为在使氧化物半导体膜403和含有氧的氧化膜407接触的状态下进行加热工序,所以可以通过含有氧的氧化膜407对氧化物半导体膜403供应由于杂质的排除工序而同时减少的构成氧化物半导体膜403的主要成分材料之一的氧。

[0150] 另外,还可以在绝缘膜407上设置高致密度的无机绝缘膜。例如,利用溅射法在绝缘膜407上形成氧化铝膜。通过提高氧化铝膜的致密度(膜密度为3.2g/cm<sup>3</sup>以上,优选为3.6g/cm<sup>3</sup>以上),可以对晶体管410赋予稳定的电特性。膜密度可以利用卢瑟福背散射分析(RBS, Rutherford Backscattering Spectrometry)或X射线反射(XRR, X-Ray Reflectometry)等测定。

[0151] 可用于设置在晶体管410上的保护绝缘膜的氧化铝膜具有高遮断效果(阻挡效果),即,不使氢、水分等杂质及氧这两者透过膜的效果。

[0152] 因此,氧化铝膜用作一种保护膜,该保护膜防止在制造工序中及制造工序后导致

电特性变动的氢、水分等杂质混入到氧化物半导体膜403并且防止从氧化物半导体膜403释放氧化物半导体的主要构成材料的氧。

[0153] 此外,为了降低起因于晶体管410的表面凹凸,也可以形成平坦化绝缘膜408。作为平坦化绝缘膜408,可以使用聚酰亚胺树脂、丙烯酸树脂、苯并环丁烯类树脂等的有机材料。此外,除了上述有机材料之外,还可以使用低介电常数材料(low-k材料)等。另外,也可以层叠多个由上述材料形成的绝缘膜来形成平坦化绝缘膜408。

[0154] 例如,作为平坦化绝缘膜408可以形成1500nm厚的丙烯酸树脂膜。丙烯酸树脂膜可以利用涂布法涂布丙烯酸树脂之后进行烧结(例如在氮气氛下以250℃进行1小时的烧结)来形成。

[0155] 可以在形成平坦化绝缘膜408之后进行加热处理。例如,在氮气氛下以250℃进行1小时的加热处理。

[0156] 如此,可以在形成晶体管410之后进行加热处理。另外,加热处理可以多次进行。

[0157] 通过上述工序,制造图1B及1C所示的晶体管410。

[0158] 另外,在进行杂质去除工序时,优选以不使氧化物半导体膜403因蚀刻而发生断裂或消失的方式对杂质去除工序的条件进行最优化。但是,由于很难到达完全不使氧化物半导体膜403被蚀刻的条件,因此有时氧化物半导体膜403露出的部分被部分去除而使氧化物半导体膜403具有槽部(凹部)。此时,如图1D所示,可以形成包括具有槽部(凹部)的氧化物半导体膜403的晶体管420。另外,晶体管420的沟道宽度W方向的截面图(沿着图1A的B1-B2的截面图)与图1C相同。

[0159] 另外,起因于蚀刻工序的杂质(典型的有卤素元素(例如氯、氟)、含有卤素元素的化合物)、硼或含有硼的化合物)的浓度可以利用SIMS(Secondary Ion Mass Spectrometry:二次离子质谱分析技术)等方法计算。

[0160] 图11示出利用二次离子质谱分析(SIMS:Secondary Ion Mass Spectrometry)对没有进行杂质去除工序制造的晶体管的氧化物半导体膜中的氯浓度进行测量的结果。样品的晶体管除了没有进行溶液处理之外其他的结构都与本实施方式的晶体管410相同,并且使用相同的材料及方法制造。另外,在晶体管410上形成有绝缘膜407。另外,测量范围是在深度方向上层叠有为保护绝缘膜的氧氮化硅膜(厚度400nm)、为氧化物半导体膜的IGZO膜、为栅极绝缘膜的氧氮化硅膜的区域。该测量从保护绝缘膜向深度方向进行。

[0161] 如图11所示,为氧化物半导体膜的IGZO膜中的氯浓度高于 $1 \times 10^{19} \text{ atoms/cm}^3$ ,由此可知氧化物半导体膜中含有氯。

[0162] 如上所述,通过进行杂质去除工序,可以防止氧化物半导体膜403表面及其附近残留起因于蚀刻工序的杂质(典型的有卤素元素(例如,氯、氟)、含有卤素元素的化合物、硼或含有硼的化合物)。另外,可以使氧化物半导体膜403表面中的起因于蚀刻工序的杂质(例如,氯)的浓度降至 $5 \times 10^{18} \text{ atoms/cm}^3$ 以下(优选为 $1 \times 10^{18} \text{ atoms/cm}^3$ 以下)。

[0163] 因此,可以提供包括使用氧化物半导体膜403的具有稳定电特性的晶体管410且可靠性高的半导体装置。此外,可以高成品率地制造可靠性高的半导体装置,由此可以实现高生产化。

[0164] 实施方式2

[0165] 在本实施方式中,参照图3A至3D以及图4A至4E说明半导体装置及半导体装置的制

造方法的一个方式。与上述实施方式相同的部分或者具有与上述实施方式类似的功能的部分可以用上述实施方式类似的方法形成。此外,省略相同部分的详细说明。

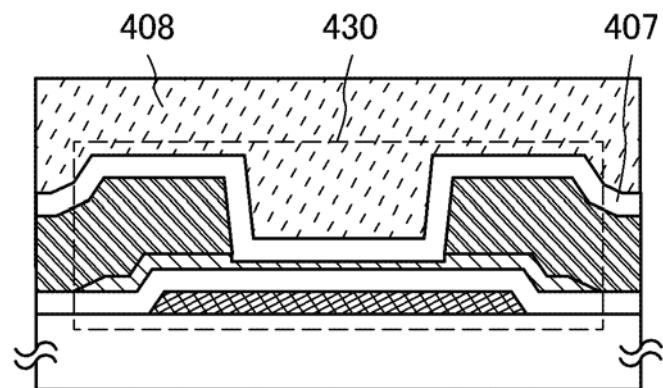

[0166] 图3A至3D所示的晶体管430示出为底栅结构的一种的也被称为反交错型晶体管的晶体管的一个例子。图3A是晶体管430的平面图,图3B是沿着图3A的C1-C2的截面图(沟道长度方向的截面图),图3C是沿着图3A的D1-D2的截面图。另外,在图3A中,L表示沟道长度,W表示沟道宽度。注意,在图3A中,为了方便起见,省略晶体管430的构成要素的一部分(例如,栅极绝缘膜402等)而进行图示。

[0167] 如图3A至3C所示,具有晶体管430的半导体装置在具有绝缘表面的衬底400上包括:栅电极层401;栅极绝缘膜402;氧化物半导体膜403;源电极层405a及漏电极层405b。另外,还设置有覆盖晶体管430的绝缘膜407。

[0168] 在图3A至3C所示的晶体管430中,氧化物半导体膜403与绝缘膜407的界面的卤素元素浓度(例如,氯浓度)降至 $5 \times 10^{18} \text{ atom/cm}^3$ 以下,优选为 $1 \times 10^{18} \text{ atom/cm}^3$ 以下。由此,可以抑制晶体管的背沟道的低电阻化(n型化),从而可以形成寄生沟道的形成得到抑制的晶体管430。由此,可以使晶体管430具有高可靠性。

[0169] 另外,如图3A至3C所示,在晶体管430中,源电极层405a及漏电极层405b的宽度比氧化物半导体膜403的沟道宽度W短,因此氧化物半导体膜403的端部露出。因此,在形成源电极层405a及漏电极层405b时,有时氧化物半导体膜403的一部分被去除。并且,在形成源电极层405a及漏电极层405b之后,在进行杂质去除工序时,有时氧化物半导体膜403的一部分被去除。此时,如图3B和3C所示,由于氧化物半导体膜403的一部分被去除,氧化物半导体膜403中的与源电极层405a及漏电极层405b重叠的区域的厚度比不与源电极层405a及漏电极层405b重叠的区域的厚度厚。

[0170] 另外,当氧化物半导体膜403没有被去除时,如图3D所示那样形成晶体管440。另外,晶体管440的沟道长度L方向的截面图(图3A的C1-C2的截面图)与图1B所示的晶体管410相同。

[0171] 接着,使用图4A至4E示出具有晶体管430的半导体装置的制造方法的一个例子。

[0172] 首先,在衬底400上形成成为栅电极层(包括使用与其相同的层形成的布线)的导电膜。在本实施方式中,作为导电膜利用溅射法形成厚度为100nm的钨膜。

[0173] 接着,利用光刻工序在导电膜上形成抗蚀剂掩模,并进行选择性的蚀刻来形成栅电极层401。形成栅电极层401之后去除抗蚀剂掩模。

[0174] 接着,在栅电极层401上形成栅极绝缘膜402。在本实施方式中,利用高密度等离子体CVD法形成200nm厚的氧氮化硅膜。

[0175] 接着,在栅极绝缘膜402上形成氧化物半导体膜403(参照图4A)。在本实施方式中,作为氧化物半导体膜403,通过使用具有AC电源装置的溅射装置的溅射法,形成厚度为35nm的In-Ga-Zn类氧化物膜(IGZO膜)。在本实施方式中,使用原子数比为In:Ga:Zn=1:1:1(1/3:1/3:1/3)的In-Ga-Zn类氧化物靶材。另外,成膜条件如下:氧及氩气(氧流量比率为50%);压力为0.6Pa;电源功率为5kW;衬底温度为170℃。该成膜条件下的成膜速度为16nm/min。

[0176] 也可以对氧化物半导体膜403进行用来去除(脱水化或脱氢化)过剩的氢(包括水及羟基)的加热处理。在本实施方式中,将衬底引入到加热处理装置之一的电炉中,在氮气

气下以450°C对氧化物半导体膜403进行1小时的加热处理,并且在氮及氧气气下以450°C对其进行1小时的加热处理。

[0177] 接着,在栅电极层401、栅极绝缘膜402、氧化物半导体膜403上形成成为源电极层及漏电极层(包括使用与其相同的层形成的布线)的导电膜445(参照图4B)。在本实施方式中,利用溅射法层叠厚度为100nm的钛膜、厚度为400nm的铝膜及厚度为100nm的钛膜,并利用干蚀刻法蚀刻钛膜、铝膜及钛膜的叠层来形成源电极层405a和漏电极层405b。

[0178] 另外,在本实施方式中,由于源电极层405a及漏电极层405b的宽度比氧化物半导体膜403的沟道宽度W短,因此氧化物半导体膜403的端部露出。因此,优选的是,当对导电膜445进行蚀刻工序时,使导电膜445的蚀刻条件最适化以防止氧化物半导体膜403被蚀刻而消失或断开。但是,由于很难仅对导电膜445进行蚀刻而完全不使氧化物半导体膜403被蚀刻,因此有时当对导电膜445进行蚀刻时氧化物半导体膜403被部分蚀刻。此时,由于氧化物半导体膜403的一部分被去除,氧化物半导体膜403中的与源电极层405a及漏电极层405b重叠的区域的厚度比不与源电极层405a及漏电极层405b重叠的区域的厚度厚。

[0179] 在形成源电极层405a及漏电极层405b的蚀刻工序中,当采用含有卤素元素的蚀刻气体时,当氧化物半导体膜403暴露于该蚀刻气体中时,由于包含于该蚀刻气体中的卤素元素(例如,氯、氟)氧化物半导体膜403中的氧被抽出,而有可能导致氧化物半导体膜403的表面形成氧缺陷。当氧化物半导体膜403中发生氧缺陷时,导致氧化物半导体膜403的背沟道低电阻化(n型化),而有可能形成寄生沟道。

[0180] 当另外,由于含有卤素元素的蚀刻气体中的卤素元素之外的元素(例如,硼)也可能成为导致氧化物半导体膜403的背沟道低电阻化的主要原因之一。

[0181] 在本实施方式中,由于在形成源电极层405a及漏电极层405b的蚀刻工序中采用含有卤素元素的气体447,因此生成的杂质为卤素(在本实施方式中为氯)类杂质(卤素元素或含有卤素元素的化合物)。另外,如本实施方式所示,当含有卤素元素的气体447中含有硼时,作为生成的杂质还包括硼或含有硼的化合物。

[0182] 因此,在形成源电极层405a及漏电极层405b之后,进行去除存在于氧化物半导体膜403表面及其附近的杂质的工序(参照图4D)。作为杂质去除工序,优选利用:使用氧、一氧化二氮或稀有气体(典型的有氩)的等离子体处理;或者使用稀释氢氟酸、水、显影液或TMAH溶液的溶液处理等。另外,作为稀释氢氟酸,例如,当使用 $1/10^3$ 稀释氢氟酸(氢氟酸:0.05%)对IGZO膜进行处理时,1秒钟膜厚度减少1nm至3nm,当使用 $2/10^5$ 稀释氢氟酸(氢氟酸:0.0025%)对IGZO膜进行处理时,1秒钟膜厚度减少0.1nm左右。通过对氧化物半导体膜403进行杂质去除处理,可使氧化物半导体膜403表面的卤素元素浓度(例如,氯浓度)降低至 $5 \times 10^{18} \text{ atom/cm}^3$ 以下,优选为 $1 \times 10^{18} \text{ atom/cm}^3$ 以下。在本实施方式中,作为杂质去除工序示出使用 $1/10^3$ 稀氢氟酸进行溶液处理的例子。

[0183] 另外,在进行杂质去除工序时,优选以不使氧化物半导体膜403因蚀刻而发生断裂或消失的方式对杂质去除工序的条件进行最优化。但是,由于很难到达完全不使氧化物半导体膜403被蚀刻的条件,因此有时氧化物半导体膜403露出的部分被部分去除而使氧化物半导体膜403具有槽部(凹部)。在图4D中示出如下情况:在经过杂质去除工序之后,氧化物半导体膜403的一部分被去除,氧化物半导体膜403中形成有槽部(凹部)。如图4D所示,与源电极层405a及漏电极层405b重叠的区域的厚度比不与源电极层405a及漏电极层405b重叠

的区域的厚度厚。另外,沟道宽度W方向的截面图可以参照图3C的截面图。

[0184] 通过上述工序,制造本实施方式的晶体管430(参照图4E)。

[0185] 在本实施方式中,源电极层405a及漏电极层405b上以接触氧化物半导体膜403的方式形成成为保护绝缘膜的绝缘膜407。例如,利用CVD法形成400nm厚的氮化硅膜。另外,也可以在形成保护绝缘膜之后进行加热处理。例如,在氮气气氛下以300℃进行1小时的加热处理。

[0186] 此外,也可以形成平坦化绝缘膜408以减少因晶体管430产生的表面凹凸。

[0187] 例如,在保护绝缘膜上作为平坦化绝缘膜408可以形成1500nm厚的丙烯酸树脂膜。丙烯酸树脂膜可以利用涂布法涂布丙烯酸树脂之后进行烧结(例如在氮气气氛下以250℃进行1小时的烧结)来形成。

[0188] 可以在形成平坦化绝缘膜之后进行加热处理。例如,在氮气气氛下以250℃进行1小时的加热处理。

[0189] 如上所述,通过进行杂质去除工序,可以防止氧化物半导体膜403的表面及其附近残留杂质。因此,在晶体管430中,氧化物半导体膜403表面中的起因于蚀刻工序的杂质(典型的有卤素元素(例如,氯、氟)或硼或含有硼的化合物的浓度得到降低。另外,可以使氧化物半导体膜403与绝缘膜407的界面的起因于蚀刻工序的杂质(典型的有卤素元素(例如,氯、氟)、硼、磷、铝、铁或碳)浓度降至 $5 \times 10^{18} \text{ atoms/cm}^3$ 以下(优选为 $1 \times 10^{18} \text{ atoms/cm}^3$ 以下)。

[0190] 由此,可以提供包含使用氧化物半导体膜403的具有稳定电特性的晶体管430的可靠性高的半导体装置。此外,可以高成品率地制造可靠性高的半导体装置,由此可以实现高生产化。

[0191] 实施方式3

[0192] 通过使用实施方式1或实施方式2中的任一个所示的晶体管可以制造具有显示功能的半导体装置(也称为显示装置)。此外,通过将包括晶体管的驱动电路的一部分或整个部分与像素部一体地形成在相同的衬底上,可以形成系统整合型面板(system-on-panel)。

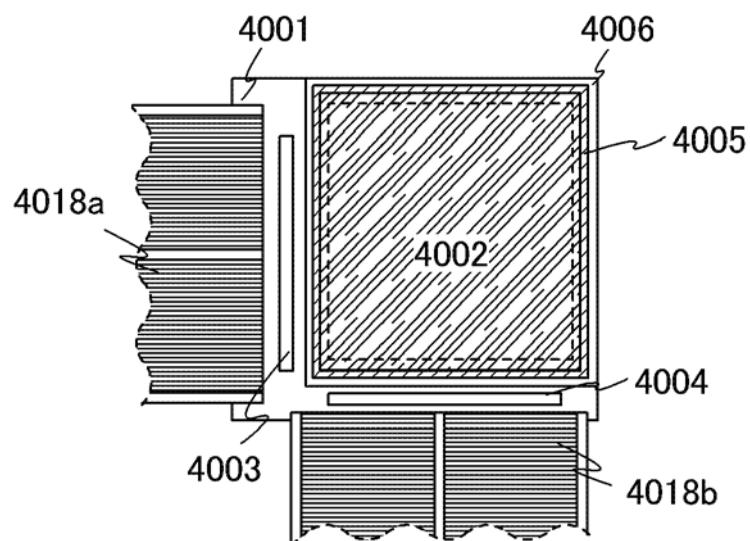

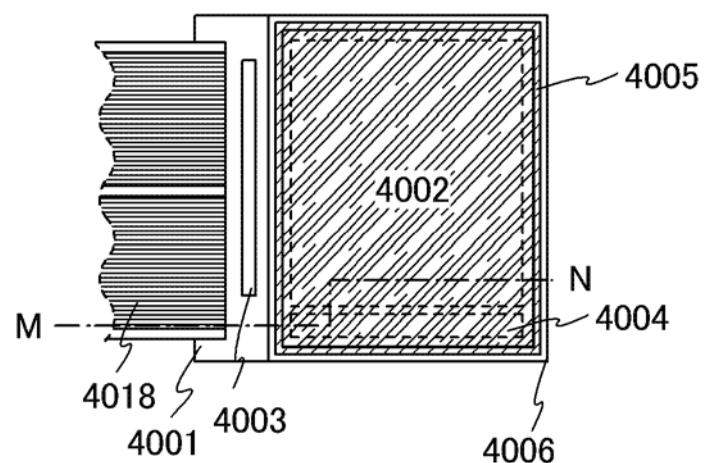

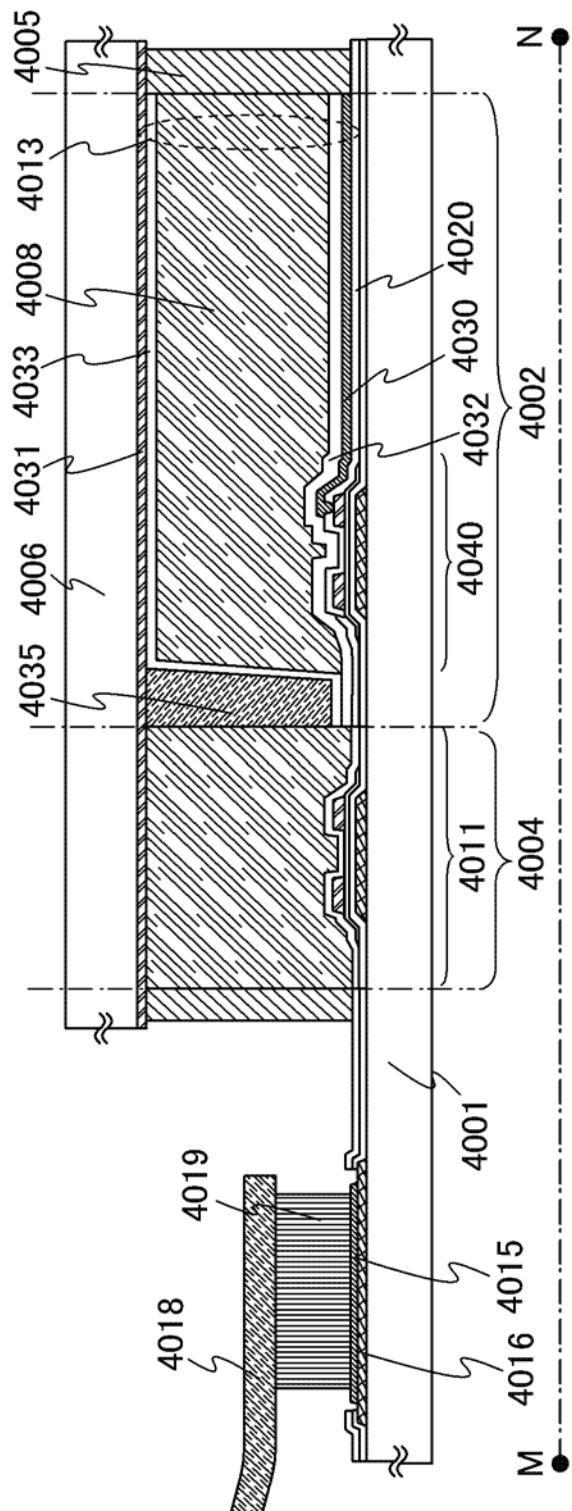

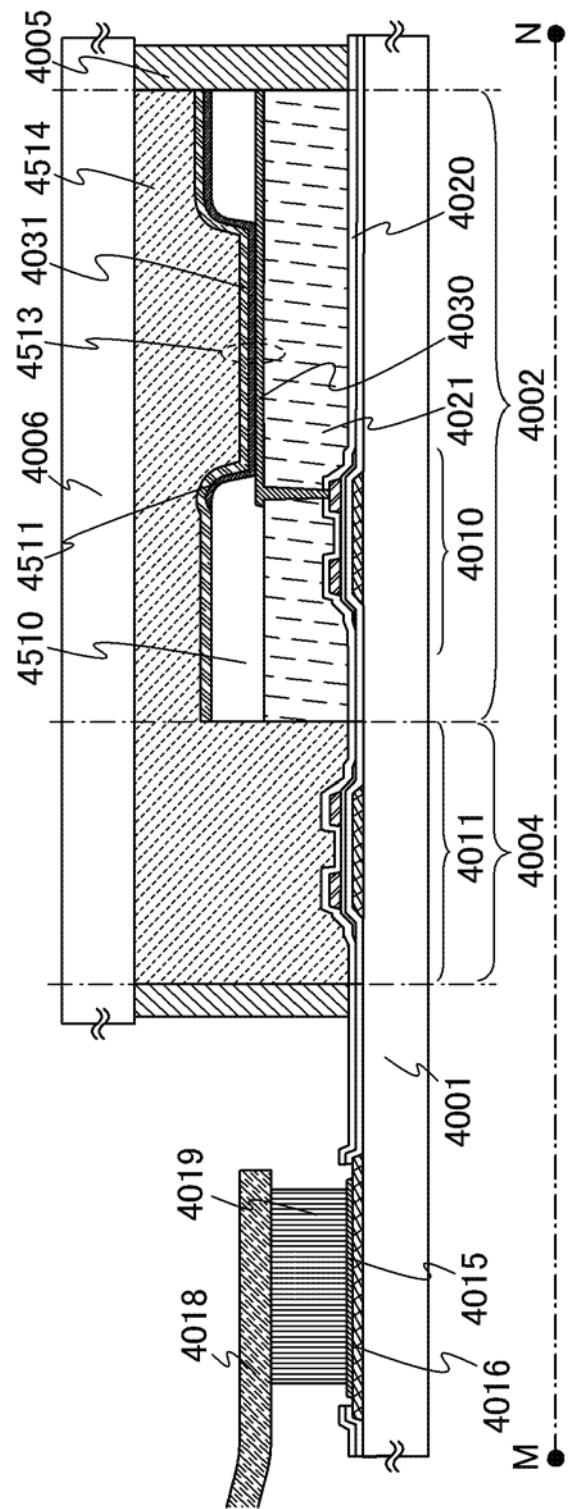

[0193] 在图5A中,以围绕设置在第一衬底4001上的像素部4002的方式设置密封剂4005,使用第二衬底4006进行密封。在图5A中,在第一衬底4001上的与由密封剂4005围绕的区域不同的区域中安装有使用单晶半导体膜或多晶半导体膜形成在另行准备的衬底上的扫描线驱动电路4004、信号线驱动电路4003。此外,供应到另行形成的信号线驱动电路4003、扫描线驱动电路4004或者像素部4002的各种信号及电位从FPC(Flexible printed circuit,柔性印刷电路)4018a、4018b供应。

[0194] 在图5B和5C中,以围绕设置在第一衬底4001上的像素部4002和扫描线驱动电路4004的方式设置有密封剂4005。此外,在像素部4002和扫描线驱动电路4004上设置有第二衬底4006。因此,像素部4002及扫描线驱动电路4004与显示元件一起由第一衬底4001、密封剂4005以及第二衬底4006密封。在图5B和5C中,在第一衬底4001上的与由密封剂4005围绕的区域不同的区域中安装有使用单晶半导体膜或多晶半导体膜形成在另行准备的衬底上的信号线驱动电路4003。在图5B和5C中,供应到另行形成的信号线驱动电路4003、扫描线驱动电路4004或者像素部4002的各种信号及电位从FPC4018供应。

[0195] 此外,图5B和5C示出另行形成信号线驱动电路4003并且将其安装到第一衬底4001

的实例,但是不局限于该结构。既可以另行形成扫描线驱动电路并进行安装,又可以仅另行形成信号线驱动电路的一部分或者扫描线驱动电路的一部分并进行安装。

[0196] 另外,对另行形成的驱动电路的连接方法没有特别的限制,而可以采用COG (Chip On Glass, 玻璃覆晶封装) 方法、引线键合方法或者TAB (Tape Automated Bonding, 卷带式自动接合) 方法等。图5A是通过COG方法安装信号线驱动电路4003、扫描线驱动电路4004的例子,图5B是通过COG方法安装信号线驱动电路4003的例子,而图5C是通过TAB方法安装信号线驱动电路4003的例子。

[0197] 此外,显示装置包括显示元件为密封状态的面板和在该面板中安装有IC诸如控制器等的模块。

[0198] 注意,本说明书中的显示装置是指图像显示装置、显示装置或光源(包括照明装置)。另外,显示装置还包括:安装有诸如FPC、TAB胶带或TCP的连接器的模块;在TAB胶带或TCP的端部设置有印刷线路板的模块;或者通过COG方式将IC(集成电路)直接安装到显示元件的模块。

[0199] 此外,设置在第一衬底上的像素部及扫描线驱动电路具有多个晶体管,可以应用实施方式1或实施方式2所示的晶体管。

[0200] 作为设置在显示装置中的显示元件,可以使用液晶元件(也称为液晶显示元件)、发光元件(也称为发光显示元件)。发光元件将由电流或电压控制亮度的元件包括在其范畴内,具体而言,包括无机EL (Electro Luminescence, 电致发光)、有机EL等。此外,也可以应用如电子墨水等的因电作用而对比度发生变化的显示媒介。

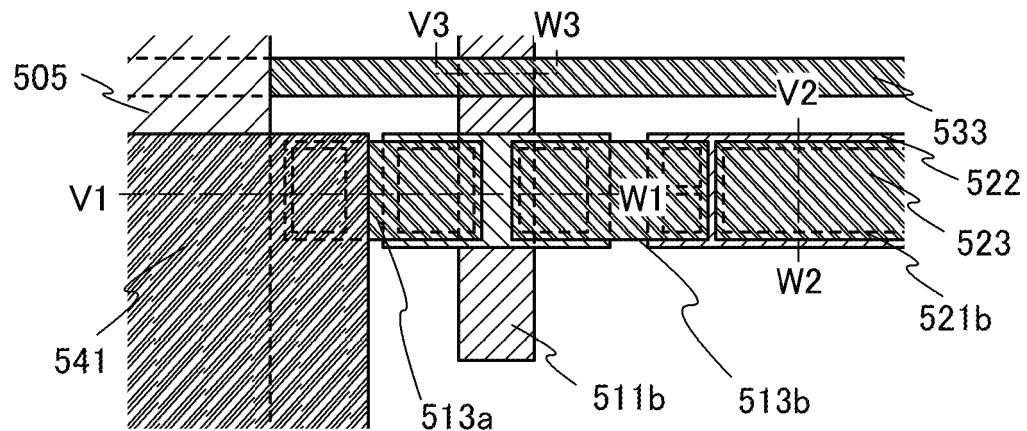

[0201] 参照图5A至图7B对半导体装置的一个方式进行说明。图7A和7B是沿着图5B的点划线M-N的截面图。

[0202] 如图5A至5C及图7A和7B所示,半导体装置包括连接端子电极4015及端子电极4016,连接端子电极4015及端子电极4016通过各向异性导电膜4019电连接到FPC4018、4018b所具有的端子。

[0203] 连接端子电极4015由与第一电极层4030相同的导电膜形成,并且,端子电极4016由与晶体管4010、晶体管4011的栅电极层相同的导电膜形成。

[0204] 此外,设置在第一衬底4001上的像素部4002、扫描线驱动电路4004具有多个晶体管,在图7A和7B中例示出像素部4002所包含的晶体管4010、扫描线驱动电路4004所包含的晶体管4011。在图7A中,在晶体管4010及晶体管4011上设置有绝缘膜4020,在图7B中还设置有绝缘膜4021。

[0205] 作为晶体管4010及晶体管4011,可以使用实施方式1或实施方式2所示的晶体管。在本实施方式中示出使用与实施方式1所示的晶体管410相同的结构及相同的制造方法形成的晶体管的例子。

[0206] 晶体管4010、4011以与实施方式1所示的晶体管410相同的结构及制造方法形成。其制造方法如下:通过使用含有卤素元素的蚀刻气体的蚀刻工序形成源电极层及漏电极层,然后进行去除氧化物半导体膜表面及其附近的包含于蚀刻气体中的杂质的工序。作为杂质去除工序,例如优选使用稀氢氟酸处理、使用氧或一氧化二氮的等离子体处理等。

[0207] 由于可以防止氧化物半导体膜表面及其附近被包含于蚀刻气体中的杂质污染,因此可以使晶体管4010、4011的氧化物半导体膜表面的卤素元素浓度为 $5 \times 10^{18} \text{ atoms/cm}^3$ 以

下(优选为 $1 \times 10^{18}$ atoms/cm<sup>3</sup>以下)。

[0208] 因此,作为图5A至5C及图7A和7B所示的本实施方式的使用氧化物半导体膜且具有稳定的电特性的晶体管4010、4011的半导体装置,可以提供可靠性高的晶体管。另外,可以高成品率地制造可靠性高的半导体装置,由此可以实现高生产化。

[0209] 此外,还可以在与驱动电路用晶体管4011的氧化物半导体膜的沟道形成区域重叠的位置再设置导电层。通过将导电层设置在与氧化物半导体膜的沟道形成区域重叠的位置,可以进一步降低偏压温度试验(BT试验)前后的晶体管4011的阈值电压的变化量。此外,导电层的电位既可以与晶体管4011的栅电极层的电位相同,又可以不同,并且,该导电层还可以用作第二栅电极层。此外,导电层的电位也可以为GND、0V或者也可以为浮动状态。

[0210] 此外,该导电层还具有遮蔽外部的电场的功能,即不使外部的电场作用到内部(包括晶体管的电路部)的功能(尤其是,遮蔽静电的静电遮蔽功能)。利用导电层的遮蔽功能,可以防止由于静电等外部的电场的影响而使晶体管的电特性变动。

[0211] 设置在像素部4002中的晶体管4010电连接到显示元件,而构成显示面板。显示元件只要能够进行显示就没有特别的限制,而可以使用各种各样的显示元件。

[0212] 图7A示出作为显示元件使用液晶元件的液晶显示装置的例子。在图7A中,作为显示元件的液晶元件4013包含第一电极层4030、第二电极层4031以及液晶层4008。另外,以夹持液晶层4008的方式设置有用作取向膜的绝缘膜4032、4033。第二电极层4031设置在第二衬底4006一侧,第一电极层4030和第二电极层4031夹着液晶层4008而层叠。

[0213] 此外,间隔物4035是通过对绝缘膜选择性地进行蚀刻而获得的柱状间隔物,并且它是为控制液晶层4008的膜厚(液晶盒间隙(cell gap))而设置的。另外,也可以使用球状间隔物。

[0214] 当作为显示元件使用液晶元件时,可以使用热致液晶、低分子液晶、高分子液晶、高分子分散型液晶、铁电液晶、反铁电液晶等。上述液晶材料(液晶组成物)根据条件而呈现胆甾相、近晶相、立方相、手性向列相、各向同性相等。

[0215] 另外,也可以将不使用取向膜的呈现蓝相的液晶组成物用于液晶层4008。在此情况下,液晶层4008与第一电极层4030及第二电极层4031接触。蓝相是液晶相的一种,是指当使胆甾相液晶的温度上升时从胆甾相转变到各向同性相之前出现的相。蓝相可以使用混合液晶及手性试剂的液晶组成物呈现。此外,为了扩大呈现蓝相的温度范围,对呈现蓝相的液晶组成物添加聚合性单体及聚合引发剂等,进行高分子稳定化的处理来可以形成液晶层。由于呈现蓝相的液晶组成物的响应时间短,并且其具有光学各向同性,所以不需要取向处理,且视角依赖性小。另外,由于不需要设置取向膜而不需要摩擦处理,因此可以防止由于摩擦处理而引起的静电破坏,并可以降低制造工序中的液晶显示装置的不良、破损。从而,可以提高液晶显示装置的生产率。在使用氧化物半导体膜的晶体管中,晶体管的电特性因静电的影响而有可能显著地变动而越出设计范围。因此,将呈现蓝相的液晶组成物用于具有使用氧化物半导体膜的晶体管的液晶显示装置是更有效的。

[0216] 此外,液晶材料的固有电阻为 $1 \times 10^9 \Omega \cdot \text{cm}$ 以上,优选为 $1 \times 10^{11} \Omega \cdot \text{cm}$ 以上,更优选为 $1 \times 10^{12} \Omega \cdot \text{cm}$ 以上。另外,本说明书中的固有电阻的值为以20℃测量的值。

[0217] 考虑到配置在像素部中的晶体管的漏电流等而以能够在指定期间中保持电荷的方式设定设置在液晶显示装置中的存储电容器的大小。可以考虑到晶体管的截止电流等设

定存储电容器的大小。通过使用具有本说明书所公开的氧化物半导体膜的晶体管,设置具有各像素中的液晶电容的1/3以下,优选为1/5以下的电容大小的存储电容器,就足够了。

[0218] 使用本说明书所公开的氧化物半导体膜的晶体管可以抑制截止状态下的电流值(截止电流值)。因此,可以延长图像信号等电信号的保持时间,在开启电源的状态下也可以延长写入间隔。因此,可以降低刷新工作的频度,所以可以达到抑制耗电量的效果。

[0219] 此外,使用本说明书所公开的氧化物半导体膜的晶体管可以得到比较高的场效应迁移率,所以能够进行高速驱动。例如,通过将这种能够进行高速驱动的晶体管用于液晶显示装置,可以在同一衬底上形成像素部中的开关晶体管及驱动电路部中的驱动晶体管。也就是说,因为作为驱动电路不需要另行使用由硅片等形成的半导体装置,所以可以缩减半导体装置的部件数。另外,在像素部中也通过使用能够进行高速驱动的晶体管,可以提供高质量的图像。

[0220] 液晶显示装置可以采用TN(Twisted Nematic,扭曲向列)模式、IPS(In-Plane-Switching,平面内转换)模式、FFS(Fringe Field Switching,边缘电场转换)模式、ASM(Axially Symmetric aligned Micro-cell,轴对称排列微单元)模式、OCB(Optical Compensated Birefringence,光学补偿弯曲)模式、FLC(Ferroelectric Liquid Crystal,铁电性液晶)模式、AFLC(Anti Ferroelectric Liquid Crystal,反铁电性液晶)模式等。

[0221] 此外,也可以使用常黑型液晶显示装置,例如采用垂直配向(VA)模式的透过型液晶显示装置。作为垂直配向模式,可以列举几个例子,例如可以使用MVA(Multi-Domain Vertical Alignment,多象限垂直取向)模式、PVA(Patterned Vertical Alignment,垂直取向构型)模式、ASV(Advanced Super View,高级超视觉)模式等。另外,也可以将本实施方式应用于VA型液晶显示装置。VA型液晶显示装置是控制液晶显示面板的液晶分子的排列的方式之一。VA型液晶显示装置是在不被施加电压时液晶分子朝向垂直于面板的方向的方式。此外,也可以使用被称为多畴化或多畴设计的方法,即将像素(pixel)分成几个区域(子像素)且使分子分别倒向不同方向的方法。

[0222] 此外,在显示装置中,适当地设置黑矩阵(遮光层)、偏振构件、相位差构件、抗反射构件等的光学构件(光学衬底)等。例如,也可以使用利用偏振衬底以及相位差衬底的圆偏振。此外,作为光源,也可以使用背光灯、侧光灯等。

[0223] 此外,作为像素部中的显示方式,可以采用逐行扫描方式或隔行扫描方式等。此外,作为当进行彩色显示时在像素中控制的颜色因素,不局限于RGB(R表示红色,G表示绿色,B表示蓝色)这三种颜色。例如,也可以采用RGBW(W表示白色)或对RGB追加黄色(yellow)、青色(cyan)、品红色(magenta)等中的一种以上的颜色。另外,也可以按每个颜色因素的点使其显示区的大小不同。但是,所公开的发明不局限于彩色显示的显示装置,而也可以应用于单色显示的显示装置。

[0224] 此外,作为显示装置所包含的显示元件,可以应用利用电致发光的发光元件。利用电致发光的发光元件根据发光材料是有机化合物还是无机化合物被区分,一般地,前者被称为有机EL元件,而后者被称为无机EL元件。

[0225] 在有机EL元件中,通过对发光元件施加电压,电子及空穴分别从一对电极注入到包含发光性的有机化合物的层,以使电流流过。并且,通过这些载流子(电子及空穴)重新结合,发光性的有机化合物形成激发态,当从该激发态回到基态时发光。由于这种机理,这种

发光元件被称为电流激发型发光元件。在本实施方式中,示出作为发光元件使用有机EL元件的例子。

[0226] 无机EL元件根据其元件结构而分类为分散型无机EL元件和薄膜型无机EL元件。分散型无机EL元件具有发光层,其中发光材料的粒子分散在粘合剂中,并且其发光机理是利用施主能级和受主能级的施主-受主重新结合型发光。薄膜型无机EL元件具有一种结构,其中,发光层夹在介电层之间,并且由电极夹持该夹着发光层的介电层,其发光机理是利用金属离子的内壳层电子跃迁的定域型发光 (localized type light emission)。另外,这里作为发光元件使用有机EL元件进行说明。

[0227] 为了取出发光,使发光元件的一对电极中的至少一个具有透光性即可。并且,在衬底上形成晶体管及发光元件。发光元件可以采用下述结构中的任何一个:从与衬底相反一侧的表面取出发光的顶部发射结构;从衬底一侧的表面取出发光的底部发射结构;以及从衬底一侧的表面及与衬底相反一侧的表面取出发光的双面发射结构。

[0228] 图6A、6B及图7B示出作为显示元件使用发光元件的发光装置的例子。

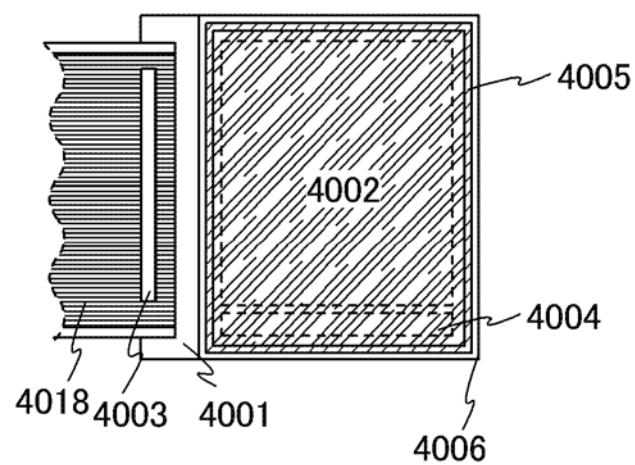

[0229] 图6A是发光装置的平面图,图6B是沿着图6A中的锁链线V1-W1、V2-W2及V3-W3切断的截面。另外,在图6A的平面图中,未图示电致发光层542及第二电极层543。

[0230] 图6A和6B所示的发光装置在衬底500上具有晶体管510、电容元件520及布线层交叉部530,其中晶体管510与发光元件540电连接。另外,图6A和6B示出经过衬底500提出发光元件540所发射的光的下面发射型结构的发光装置。

[0231] 作为晶体管510,可以使用实施方式1或实施方式2所示的晶体管。在本实施方式中示出使用与实施方式1所示的晶体管410相同的结构及相同的制造方法形成的晶体管的例子。

[0232] 晶体管510包含栅电极层511a、511b、栅极绝缘膜502、氧化物半导体膜512以及用作源电极层或漏电极层的导电层513a、513b。

[0233] 作为以与实施方式1所示的晶体管410相同的结构及制造方法形成的晶体管510,通过使用含有卤素元素的蚀刻气体的蚀刻工序形成用作源电极层或漏电极层的导电层513a、513b之后,进行去除氧化物半导体膜表面及其附近的包含于蚀刻气体中的杂质的工序。作为杂质去除工序,例如优选使用稀氢氟酸处理、使用氧或一氧化二氮的等离子体处理等。

[0234] 由于可以防止氧化物半导体膜表面及其附近被包含于蚀刻气体中的杂质污染,因此可以使晶体管510的氧化物半导体膜表面的卤素元素浓度为 $5 \times 10^{18} \text{atoms/cm}^3$ 以下(优选为 $1 \times 10^{18} \text{atoms/cm}^3$ 以下)。

[0235] 因此,作为图6A和6B所示的本实施方式的使用氧化物半导体膜512且具有稳定的电特性的晶体管510的半导体装置,可以提供可靠性高的半导体装置。另外,可以高成品率地制造可靠性高的半导体装置,由此可以实现高生产化。

[0236] 电容元件520包含导电层521a、521b、栅极绝缘膜502、氧化物半导体膜522及导电层523,其中由导电层521a、521b及导电层523夹持栅极绝缘膜502及氧化物半导体膜522。

[0237] 布线层交叉部530是栅电极层511a、511b与导电层533的交叉部,栅电极层511a、511b与导电层533隔着栅极绝缘膜502交叉。

[0238] 在本实施方式中,作为栅电极层511a及导电层521a使用30nm厚的钛膜,作为栅电

极层511b及导电层521b使用200nm厚的铜薄膜。由此,栅电极层为钛膜与铜薄膜的叠层结构。

[0239] 氧化物半导体膜512、522使用25nm厚的IGZO膜。

[0240] 在晶体管510、电容元件520及布线层交叉部530上形成有层间绝缘膜504,并且在层间绝缘膜504上的与发光元件540重叠的区域中设置有滤色片层505。在层间绝缘膜504及滤色片层505上设置有用作平坦化绝缘膜的绝缘膜506。

[0241] 在绝缘膜506上设置有包含依次叠层第一电极层541、电致发光层542及第二电极层543的叠层结构的发光元件540。在到达导电层513a的形成在绝缘膜506及层间绝缘膜504中的开口中第一电极层541与导电层513a接触,由此实现发光元件540与晶体管510的电连接。另外,以覆盖第一电极层541的一部分及该开口的方式设置有分隔壁507。

[0242] 层间绝缘膜504可以使用利用等离子体CVD法形成的200nm以上且600nm以下厚的氧氮化硅膜。另外,绝缘膜506可以使用1500nm厚的光敏丙烯酸树脂膜,分隔壁507可以使用1500nm厚的光敏聚酰亚胺膜。

[0243] 作为滤色片层505,例如可以使用彩色的透光树脂。作为彩色的透光树脂,可以使用感光或非感光有机树脂。优选使用感光有机树脂层,因为可以缩减抗蚀剂掩模的数量来简化工序。

[0244] 彩色是指除了黑、灰、白等的无彩色之外的颜色,滤色片层使用只透过被着色的彩色光的材料来形成。至于彩色,可以使用红色、绿色、蓝色等。另外,还可以使用青色(cyan)、品红色(magenta)、黄色(yellow)等。只透过被着色的彩色光意味着滤色片层中的透过光在彩色光的波长中具有峰值。滤色层片考虑所包含的着色材料的浓度与光的透过率的关系以适当地控制最适合的膜厚度即可。例如,可以滤色片层505的膜厚度为1500nm以上且2000nm以下。

[0245] 在图7B所示的发光元件中,作为显示元件的发光元件4513电连接到设置在像素部4002中的晶体管4010。另外,发光元件4513的结构是第一电极层4030、场致发光层4511、第二电极层4031的叠层结构,但是,不局限于所示结构。根据从发光元件4513取出的光的方向等,可以适当地改变发光元件4513的结构。

[0246] 分隔壁4510、507使用有机绝缘材料或无机绝缘材料形成。尤其是,优选使用感光树脂材料,在第一电极层4030、541上形成开口部,并且将该开口部的侧壁形成为具有连续曲率的倾斜面。

[0247] 场致发光层4511、542可以使用一个层构成,也可以使用多个层的叠层构成。

[0248] 为了防止氧、氢、水分、二氧化碳等侵入到发光元件4513及发光元件540中,也可以在第二电极层4031、543及分隔壁4510、507上形成保护膜。作为保护膜,可以形成氮化硅膜、氮氧化硅膜、DLC膜等。

[0249] 另外,为了防止氧、氢、水分、二氧化碳等侵入到发光元件4513、540中,也可以通过蒸镀法形成覆盖发光元件4513、540的包含有机化合物的层。

[0250] 此外,在由第一衬底4001、第二衬底4006以及密封剂4005密封的空间中设置有填充材料4514并被密封。如此,为了不暴露于外部气体,优选使用气密性高且脱气少的保护薄膜(粘合薄膜、紫外线固化树脂薄膜等)、覆盖材料进行封装(封入)。

[0251] 作为填充材料4514,除了氮或氩等惰性气体以外,也可以使用紫外线固化树脂或

热固化树脂,例如可以使用PVC(聚氯乙烯)、丙烯酸树脂、聚酰亚胺、环氧树脂、硅酮树脂、PVB(聚乙烯醇缩丁醛)或EVA(乙烯-醋酸乙烯酯)。例如,作为填充材料使用氮,即可。

[0252] 另外,如果需要,则也可以在发光元件的射出表面上适当地设置诸如偏振片或者圆偏振片(包括椭圆偏振片)、相位差板( $\lambda/4$ 板, $\lambda/2$ 板)、滤色片等的光学薄膜。此外,也可以在偏振片或者圆偏振片上设置防反射膜。例如,可以进行抗眩光处理,该处理是利用表面的凹凸来扩散反射光而可以降低眩光的处理。

[0253] 此外,作为显示装置,也可以提供驱动电子墨水的电子纸。电子纸也称为电泳显示装置(电泳显示器),并具有如下优点:与纸同样的易读性;其耗电量比其他显示装置的耗电量低;形状薄且轻。

[0254] 电泳显示装置可以采用各种各样的形式。电泳显示装置是如下装置,即在溶剂或溶质中分散有包含具有正电荷的第一粒子和具有负电荷的第二粒子的多个微囊,并且通过对微囊施加电场使微囊中的粒子向相互相反的方向移动,以仅显示集中在一方的粒子的颜色。另外,第一粒子或第二粒子包含染料,当没有电场时不移动。此外,第一粒子的颜色和第二粒子的颜色不同(该颜色包括无色)。

[0255] 这样,电泳显示装置是利用介电常数高的物质移动到高电场区域,即所谓的介电泳效应(dielectrophoretic effect)的显示器。

[0256] 分散有上述微囊的溶剂被称为电子墨水,并且该电子墨水可以印刷到玻璃、塑料、布、纸等的表面上。另外,还可以通过使用滤色片、具有色素的粒子来进行彩色显示。

[0257] 此外,微囊中的第一粒子及第二粒子可以使用选自导电材料、绝缘材料、半导体材料、磁性材料、液晶材料、铁电性材料、电致发光材料、电致变色材料、磁泳材料中的一种材料或这些材料的复合材料。

[0258] 此外,作为电子纸,也可以应用使用旋转球(twisting ball)显示方式的显示装置。旋转球显示方式是如下方法,即将分别涂为白色和黑色的球形粒子配置在作为用于显示元件的电极层的第一电极层与第二电极层之间,使第一电极层与第二电极层之间产生电位差来控制球形粒子的方向,以进行显示。

[0259] 另外,在图5A至图7B中,作为第一衬底4001、衬底500、第二衬底4006,除了玻璃衬底以外,也可以使用柔性的衬底。例如,可以使用具有透光性的塑料衬底等。作为塑料,可以使用FRP(Fiberglass-Reinforced Plastics,玻璃纤维强化塑料)板、PVF(聚氟乙烯)薄膜、聚酯薄膜或丙烯酸树脂薄膜。此外,若不需要透光性,则也可以使用以铝或不锈钢等为材料的金属衬底(金属薄膜)。例如,也可以使用具有由PVF薄膜或聚酯薄膜夹住铝箔的结构的薄片。

[0260] 在本实施方式中,作为绝缘膜4020使用氧化铝膜。绝缘膜4020可以利用溅射法或等离子体CVD法等形成。

[0261] 在氧化物半导体膜上作为绝缘膜4020设置的氧化铝膜具有高遮断效果(阻挡效果),即,不使氢、水分等杂质以及氧这两者透过膜的效果。

[0262] 因此,氧化铝膜用作保护膜,而防止在制造工序中及制造之后导致晶体管的特性变动的氢、水分等杂质混入到氧化物半导体膜,并且防止从氧化物半导体膜释放氧化物半导体的主要构成材料的氧。

[0263] 另外,作为用作平坦化绝缘膜的绝缘膜4021、506,可以使用丙烯酸树脂、聚酰亚胺

树脂、苯并环丁烯类树脂、聚酰胺树脂、环氧树脂等具有耐热性的有机材料。此外,除了上述有机材料以外,也可以使用低介电常数材料(low-k材料)、硅氧烷类树脂、PSG(磷硅玻璃)、BPSG(硼磷硅玻璃)等。另外,也可以通过层叠多个由这些材料形成的绝缘膜来形成绝缘膜。

[0264] 对绝缘膜4021、506的形成方法没有特别的限制,可以根据其材料利用如溅射法、SOG法、旋涂法、浸渍法、喷涂法、液滴喷射法(喷墨法等)、印刷法(丝网印刷、胶版印刷等)等的方法以及如刮刀、辊涂机、幕式涂布机、刮刀式涂布机等的器具来形成绝缘膜4021、506。

[0265] 显示装置通过使来自光源或显示元件的光透过来进行显示。因此,设置在光透过的像素部中的衬底、绝缘膜、导电膜等薄膜全都对可见光的波长区域的光具有透光性。

[0266] 关于对显示元件施加电压的第一电极层及第二电极层(也称为像素电极层、公共电极层、对置电极层等),可以根据取出光的方向、设置电极层的地方以及电极层的图案结构选择透光性或反射性。

[0267] 作为第一电极层4030、541及第二电极层4031、543,可以使用含有氧化钨的铟氧化物、含有氧化钨的铟锌氧化物、含有氧化钛的铟氧化物、含有氧化钛的铟锡氧化物、铟锡氧化物(以下称为ITO)、铟锌氧化物、添加有氧化硅的铟锡氧化物、石墨烯等具有透光性的导电材料。

[0268] 此外,第一电极层4030、第一电极层541、第二电极层4031及第二电极层543可以使用钨(W)、钼(Mo)、锆(Zr)、铪(Hf)、钒(V)、铌(Nb)、钽(Ta)、铬(Cr)、钴(Co)、镍(Ni)、钛(Ti)、铂(Pt)、铝(Al)、铜(Cu)、银(Ag)等金属、其合金或其金属氮化物中的一种或多种来形成。

[0269] 在本实施方式中,图6A和6B所示的发光装置具有下面发射型结构,所以第一电极层541具有透光性,而第二电极层543具有反射性。因此,当将金属膜用于第一电极层541时,优选将金属膜形成得薄,以便使其具有透光性。另外,当将具有透光性的导电膜用于第二电极层543时,优选将具有反射性的导电膜层叠在其上。

[0270] 此外,第一电极层4030、第一电极层541、第二电极层4031及第二电极层543可以使用包括导电高分子(也称为导电聚合体)的导电组成物来形成。作为导电高分子,可以使用所谓的π电子共轭类导电高分子。例如,可以举出聚苯胺或其衍生物、聚吡咯或其衍生物、聚噻吩或其衍生物、或者由苯胺、吡咯和噻吩中的两种以上构成的共聚物或其衍生物等。

[0271] 此外,由于晶体管容易因静电等而损坏,所以优选设置用来保护驱动电路的保护电路。保护电路优选使用非线性元件构成。

[0272] 如上所述,通过应用实施方式1或实施方式2所示的晶体管,可以提供具有各种各样的功能的半导体装置。

[0273] 本实施方式所示的结构或方法等可以与其他的实施方式所示的结构或方法等适当地组合而实施。

[0274] 实施方式4

[0275] 通过使用实施方式1或实施方式2所示的晶体管,可以制造具有读取对象物的信息的图像传感器功能的半导体装置。

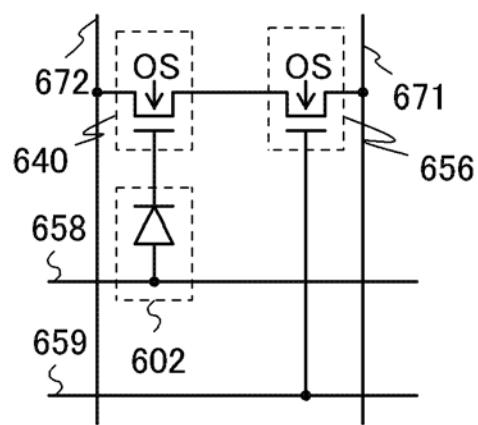

[0276] 图8A示出具有图像传感器功能的半导体装置的一个例子。图8A是光电传感器的等效电路,而图8B是示出光电传感器的一部分的截面图。

[0277] 光电二极管602的一个电极电连接到光电二极管复位信号线658,而光电二极管602的另一个电极电连接到晶体管640的栅极。晶体管640的源极和漏极中的一个电连接到

光电传感器参考信号线672,而晶体管640的源极和漏极中的另一个电连接到晶体管656的源极和漏极中的一个。晶体管656的栅极电连接到栅极信号线659,晶体管656的源极和漏极中的另一个电连接到光电传感器输出信号线671。

[0278] 注意,在本说明书的电路图中,为了使使用氧化物半导体膜的晶体管一目了然,将使用氧化物半导体膜的晶体管的符号表示为“OS”。在图8A中,晶体管640和晶体管656可以应用实施方式1或实施方式2所示的晶体管,是使用氧化物半导体膜的晶体管。在本实施方式中示出使用与实施方式1所示的晶体管410同样的结构及同样的制造方法形成的晶体管的例子。

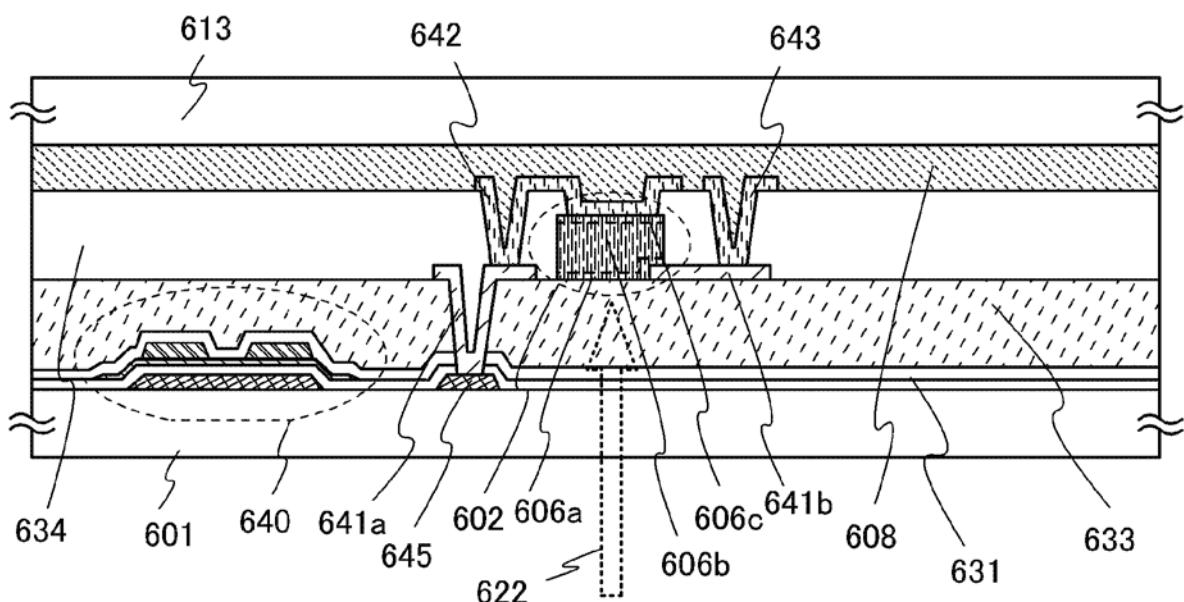

[0279] 图8B是示出光电传感器中的光电二极管602和晶体管640的截面图,其中在具有绝缘表面的衬底601(TFT衬底)上设置有用作传感器的光电二极管602和晶体管640。在光电二极管602和晶体管640上使用粘合层608设置有衬底613。

[0280] 在晶体管640上设置有绝缘膜631、层间绝缘膜633以及层间绝缘膜634。光电二极管602设置在层间绝缘膜633上,并且光电二极管602具有如下结构:在形成于层间绝缘膜633上的电极层641a、641b与设置在层间绝缘膜634上的电极层642之间从层间绝缘膜633一侧依次层叠有第一半导体膜606a、第二半导体膜606b及第三半导体膜606c。

[0281] 电极层641b与形成在层间绝缘膜634中的导电层643电连接,并且电极层642通过电极层641a与导电层645电连接。导电层645与晶体管640的栅电极层电连接,并且光电二极管602与晶体管640电连接。

[0282] 在此,例示出一种pin型光电二极管,其中层叠用作第一半导体膜606a的具有p型导电型的半导体膜、用作第二半导体膜606b的高电阻的半导体膜(I型半导体膜)、用作第三半导体膜606c的具有n型导电型的半导体膜。

[0283] 第一半导体膜606a是p型半导体膜,而可以由包含赋予p型的杂质元素的非晶硅膜形成。使用包含属于周期表中的第13族的杂质元素(例如,硼(B))的半导体材料气体通过等离子体CVD法来形成第一半导体膜606a。作为半导体材料气体,可以使用硅烷( $SiH_4$ )。另外,可以使用 $Si_2H_6$ 、 $SiH_2Cl_2$ 、 $SiHCl_3$ 、 $SiCl_4$ 、 $SiF_4$ 等。另外,也可以使用如下方法:在形成不包含杂质元素的非晶硅膜之后,使用扩散法或离子注入法将杂质元素引入到该非晶硅膜。优选在使用离子注入法等引入杂质元素之后进行加热等来使杂质元素扩散。在此情况下,作为形成非晶硅膜的方法,可以使用LPCVD法、气相生长法或溅射法等。优选将第一半导体膜606a的厚度设定为10nm以上且50nm以下。

[0284] 第二半导体膜606b是I型半导体膜(本征半导体膜),而可以由非晶硅膜形成。为了形成第二半导体膜606b,通过等离子体CVD法使用半导体材料气体来形成非晶硅膜。作为半导体材料气体,可以使用硅烷( $SiH_4$ )。或者,也可以使用 $Si_2H_6$ 、 $SiH_2Cl_2$ 、 $SiHCl_3$ 、 $SiCl_4$ 或 $SiF_4$ 等。也可以通过LPCVD法、气相生长法、溅射法等形成第二半导体膜606b。优选将第二半导体膜606b的厚度设定为200nm以上且1000nm以下。

[0285] 第三半导体膜606c是n型半导体膜,而可以由包含赋予n型的杂质元素的非晶硅膜形成。使用包含属于周期表中的第15族的杂质元素(例如,磷(P))的半导体材料气体通过等离子体CVD法形成第三半导体膜606c。作为半导体材料气体,可以使用硅烷( $SiH_4$ )。或者,也可以使用 $Si_2H_6$ 、 $SiH_2Cl_2$ 、 $SiHCl_3$ 、 $SiCl_4$ 或 $SiF_4$ 等。另外,也可以使用如下方法:在形成不包含杂质元素的非晶硅膜之后,使用扩散法或离子注入法将杂质元素引入到该非晶硅膜。优选

在使用离子注入法等引入杂质元素之后进行加热等来使杂质元素扩散。在此情况下,作为形成非晶硅膜的方法,可以使用LPCVD法、气相生长法或溅射法等。优选将第三半导体膜606c的厚度设定为20nm以上且200nm以下。

[0286] 此外,第一半导体膜606a、第二半导体膜606b以及第三半导体膜606c也可以不使用非晶半导体形成,而使用多晶半导体或微晶半导体(Semi Amorphous Semiconductor, SAS)形成。

[0287] 此外,由于光电效应生成的空穴的迁移率低于电子的迁移率,因此当p型半导体膜一侧的表面用作光接收面时, pin型光电二极管具有良好的特性。这里示出将光电二极管602从形成有pin型光电二极管的衬底601的面接收的光转换为电信号的例子。此外,来自其导电型与用作光接收面的半导体膜一侧相反的半导体膜一侧的光是干扰光,因此,电极层优选使用具有遮光性的导电膜。另外,也可以将n型半导体膜一侧的表面用作光接收面。

[0288] 通过使用绝缘材料且根据材料使用溅射法、等离子体CVD法、SOG法、旋涂法、浸渍法、喷涂法、液滴喷射法(喷墨法等)、印刷法(丝网印刷、胶版印刷等)等,来可以形成绝缘膜631、层间绝缘膜633、层间绝缘膜634。

[0289] 作为绝缘膜631,可以使用无机绝缘材料,诸如氧化硅层、氧氮化硅层、氧化铝层、氧氮化铝层等氧化物绝缘膜、氮化硅层、氮氧化硅层、氮化铝层、氮氧化铝层等氮化物绝缘膜的单层或叠层。

[0290] 在本实施方式中,作为绝缘膜631使用氧化铝膜。绝缘膜631可以通过溅射法或等离子体CVD法形成。

[0291] 在氧化物半导体膜上作为绝缘膜631设置的氧化铝膜具有高遮断效果(阻挡效果),即不使氢、水分等杂质及氧的双方透过膜的效果。

[0292] 因此,氧化铝膜用作保护膜,而防止在制造工序中及制造之后导致晶体管的特性变动的氢、水分等杂质混入到氧化物半导体膜,并且防止从氧化物半导体膜释放氧化物半导体的主要构成材料的氧。

[0293] 作为层间绝缘膜633、634,优选采用用作减少表面凹凸的平坦化绝缘膜的绝缘膜。作为层间绝缘膜633、634,例如可以使用聚酰亚胺、丙烯酸树脂、苯并环丁烯树脂、聚酰胺或环氧树脂等具有耐热性的有机绝缘材料。除了上述有机绝缘材料之外,也可以使用低介电常数材料(low-k材料)、硅氧烷类树脂、PSG(磷硅玻璃)、BPSG(硼磷硅玻璃)等的单层或叠层。

[0294] 通过检测入射到光电二极管602的光622,可以读取检测对象的信息。另外,在读取检测对象的信息时,可以使用背光灯等的光源。

[0295] 作为以与实施方式1所示的晶体管410相同的结构及制造方法形成的晶体管640,通过使用包含卤素元素的蚀刻气体的蚀刻工序形成源电极层及漏电极层之后,进行去除氧化物半导体膜表面及其附近的包含于蚀刻气体中的杂质的工序。作为杂质去除工序,例如优选使用稀氢氟酸处理、使用氧或一氧化二氮的等离子体处理等。

[0296] 由于可以防止氧化物半导体膜表面及其附近被包含于蚀刻气体中的杂质污染,因此可以使晶体管640的氧化物半导体膜表面的卤素元素的杂质浓度为 $5 \times 10^{18} \text{ atoms/cm}^3$ 以下(优选为 $1 \times 10^{18} \text{ atoms/cm}^3$ 以下)。

[0297] 因此,可以提供使用本实施方式的氧化物半导体膜且具有稳定的电特性的晶体管

640的可靠性高的半导体装置。另外,可以高成品率地制造可靠性高的半导体装置,由此可以实现高生产化。

[0298] 本实施方式所示的结构或方法等可以与其他的实施方式所示的结构或方法等适当地组合而实施。

[0299] 实施方式5

[0300] 可以将本说明书所公开的半导体装置应用于多种电子设备(包括游戏机)。作为电子设备,可以举出电视装置(也称为电视或电视接收机)、用于计算机等的显示器、数码相机、数码摄像机、数码相框、移动电话机、便携式游戏机、移动信息终端、声音再现装置、游戏机(弹子机、投币机等)框体游戏机等。图9A至9C示出这些电子设备的具体例子。

[0301] 图9A示出具有显示部的桌子9000。在桌子9000中,框体9001组装有显示部9003,利用显示部9003可以显示图像。另外,在此示出利用四个腿部9002支撑框体9001的结构。另外,框体9001具有用来供应电力的电源供应线9005。

[0302] 实施方式1至实施方式4中的任一所示的半导体装置可以应用于显示部9003,由此可以对电子设备赋予高可靠性。

[0303] 显示部9003具有触屏输入功能。当用指头等接触显示于桌子9000的显示部9003中的显示按钮9004时,可以进行屏面操作或信息输入。并且当使桌子具有能够与其他家电产品进行通讯的功能或能够控制其他家电产品的功能,可以将桌子用作通过屏面操作控制其他家电产品的控制装置。例如,通过使用实施方式4所示的具有图像传感器功能的半导体装置,可以使显示部9003具有触屏输入功能。

[0304] 另外,利用设置于框体9001的铰链也可以将显示部9003的屏面以垂直于地板的方式立起来,从而也可以将桌子用作电视装置。虽然如果在小房间里设置大屏面的电视装置则自由使用的空间变小,然而,如果在桌子内安装有显示部则可以有效地利用房间的空间。

[0305] 图9B示出电视装置9100的一个例子。在电视装置9100中,框体9101组装有显示部9103。利用显示部9103可以显示图像。此外,在此示出利用支架9105支撑框体9101的结构。

[0306] 可以通过利用框体9101所具备的操作开关、另外提供的遥控操作机9110进行电视装置9100的操作。通过利用遥控操作机9110所具备的操作键9109,可以进行频道及音量的操作,并可以对在显示部9103上显示的映像进行操作。此外,也可以采用在遥控操作机9110中设置显示从该遥控操作机9110输出的信息的显示部9107的结构。

[0307] 图9B所示的电视装置9100具备接收机及调制解调器等。电视装置9100可以利用接收机接收一般的电视广播。再者,电视装置通过调制解调器连接到有线或无线方式的通信网络,也可以进行单向(从发送者到接收者)或双向(在发送者和接收者之间或在接收者之间等)的信息通信。

[0308] 实施方式1至实施方式4中的任一所示的半导体装置可以应用于显示部9103、9107,由此可以对电视装置及遥控操作机赋予高可靠性。

[0309] 图9C示出计算机,该计算机包含主体9201、框体9202、显示部9203、键盘9204、外部连接端口9205、定位装置9206等。

[0310] 实施方式1至实施方式4中的任一个所示的半导体装置都可以用于显示部9203,由此可以制造具有高可靠性的计算机。

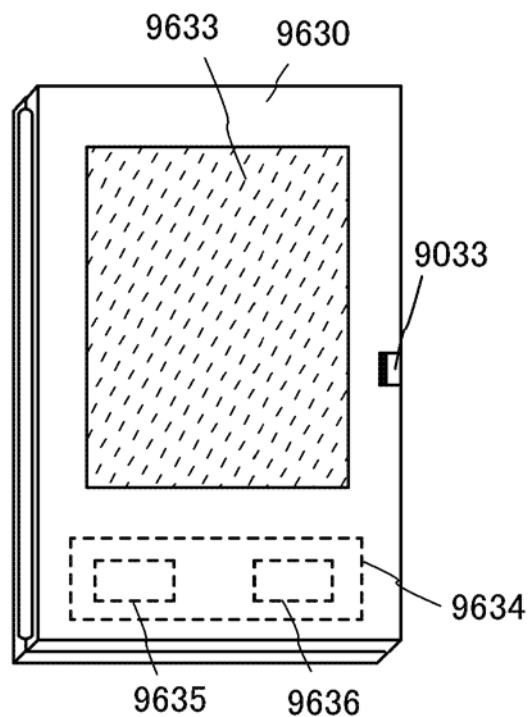

[0311] 图10A和10B是能够进行折叠的平板终端。图10A示出打开的状态。平板终端包含框

体9630、显示部9631a、显示部9631b、显示模式切换开关9034、电源开关9035、省电模式切换开关9036、卡子9033以及操作开关9038。

[0312] 实施方式1至实施方式4中的任一所示的半导体装置可以应用于显示部9631a及显示部9631b,由此可以对平板终端赋予高可靠性。

[0313] 在显示部9631a中,可以将其一部分用作触摸屏的区域9632a,并且可以通过接触所显示的操作键9638来输入数据。此外,作为一个例子,显示部9631a的一半只具有显示的功能,并且另一半具有触摸屏的功能,但是不局限于该结构。也可以采用显示部9631a的整个区域具有触摸屏的功能的结构。例如,可以在显示部9631a的全面显示键盘来将其用作触摸屏,并且将显示部9631b用作显示画面。

[0314] 此外,在显示部9631b中,与显示部9631a同样也可以将显示部9631b的一部分用作触摸屏的区域9632b。此外,通过使用指头或触屏笔等接触触摸屏上的键盘显示切换按钮9639的位置上,可以在显示部9631b上显示键盘。

[0315] 此外,也可以对触摸屏的区域9632a和触摸屏的区域9632b同时进行触摸输入。

[0316] 另外,显示模式切换开关9034能够进行竖屏显示和横屏显示等显示的方向的切换以及黑白显示和彩色显示的切换等。根据通过平板终端所内置的光传感器所检测的使用时的外光的光量,省电模式切换开关9036可以使显示的亮度设定为最适合的亮度。平板终端除了光传感器以外还可以内置陀螺仪和加速度传感器等检测倾斜度的传感器等的其他检测装置。

[0317] 此外,图10A示出显示部9631b的显示面积与显示部9631a的显示面积相同的例子,但是不局限于此,一方的尺寸可以与另一方的尺寸不同,其显示质量也可以不同。例如,例如可以使用显示部中的一方能够进行比另一方更高精细度的显示的显示面板。

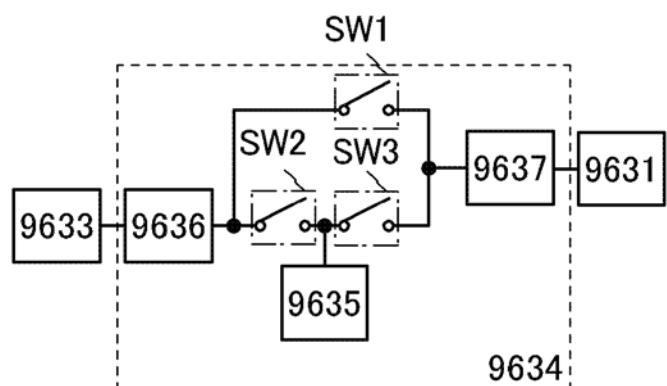

[0318] 图10B示出合上的状态,并且平板终端包括框体9630、太阳能电池9633、充放电控制电路9634、电池9635以及DCDC转换器9636。此外,在图10B中,作为充放电控制电路9634的一个例子示出具有电池9635和DCDC转换器9636的结构。

[0319] 此外,平板终端能够进行折叠,因此不使用时可以合上框体9630。因此,可以保护显示部9631a和显示部9631b,而可以提供一种具有良好的耐久性且从长期使用的观点来看具有良好的可靠性的平板终端。

[0320] 此外,图10A和10B所示的平板终端还可以具有如下功能:显示各种各样的信息(静态图像、动态图像、文字图像等);将日历、日期或时刻等显示在显示部上;对显示在显示部上的信息进行操作或编辑的触摸输入;通过各种各样的软件(程序)控制处理等。

[0321] 通过利用安装在平板终端的表面上的太阳能电池9633,可以将电力供应到触摸屏、显示部或图像信号处理部等。另外,可以将太阳能电池9633设置在框体9630的单面或双面,由此可以高效地对电池9635进行充电。另外,当作为电池9635使用锂离子电池时,有可以实现小型化等的优点。

[0322] 另外,参照图10C所示的方框图对图10B所示的充放电控制电路9634的结构和工作进行说明。图10C示出太阳能电池9633、电池9635、DCDC转换器9636、转换器9637、开关SW1至SW3以及显示部9631,电池9635、DCDC转换器9636、转换器9637、开关SW1至SW3对应图10B所示的充放电控制电路9634。

[0323] 首先,说明在利用外光使太阳能电池9633发电时的工作的例子。使用DCDC转换器

9636对太阳能电池9633所产生的电力进行升压或降压以使它成为用来对电池9635进行充电的电压。并且,当利用来自太阳能电池9633的电力使显示部9631工作时使开关SW1导通,并且,利用转换器9637将其升压或降压到显示部9631所需要的电压。另外,可以采用当不进行显示部9631中的显示时,使开关SW1截止且使开关SW2导通来对电池9635进行充电的结构。

[0324] 注意,作为发电单元的一个例子示出太阳能电池9633,但是不局限于此,也可以使用压电元件(piezoelectric element)或热电转换元件(珀耳帖元件(Peltier element))等其他发电单元进行电池9635的充电。例如,也可以使用以无线(不接触)的方式能够收发电力来进行充电的无线电力传输模块或组合其他充电方法进行充电。

[0325] 本实施方式所示的结构或方法等可以与其他的实施方式所示的结构或方法等适当地组合而实施。

[0326] 实施例1

[0327] 在本实施例中,在氧化物半导体膜上以与其接触的方式形成金属膜,然后进行干蚀刻去除金属膜。通过如下实验观察是否进行去除干蚀刻时产生的杂质与电阻率的关系。

[0328] 首先,作为比较例的样品,利用使用溅射法的成膜装置在玻璃衬底上形成厚度为95nm的IGZO膜,并测量其电阻率。其结果为 $4.8 \times 10^9 \Omega \cdot \text{cm}$ 。通过形成顶面形状为弯曲形状的电极(厚度为100nm的钛膜、厚度为400nm的铝膜及厚度为100nm的钛膜的叠层),并通过测量电压-电流的两个端子算出电阻,来得到IGZO膜的电阻率。

[0329] 在如下成膜条件下形成IGZO膜:使用In:Ga:Zn=1:1:1[原子数比]的氧化物靶材,在氧及氩气氛下(氧流量比率50%),压力为0.6Pa,AC电源电力为5kW,衬底温度为170℃。

[0330] 利用溅射法的成膜装置包括:可以使用真空泵等真空排气单元(低温泵、涡轮分子泵等)进行减压的溅射处理室;固定被处理衬底的衬底架;支撑溅射靶材的靶材架;对应于由靶材架支撑的溅射靶材的电极;对上述电极施加用于溅射的AC电压(或DC电压)的电力供应单元;以及向溅射处理室内供应气体的气体供应单元。另外,在制造样品时,尽可能地以不混入杂质的方式将溅射处理室内设定为高真空的状态,至于水分在露点为-40℃以下,优选在露点为-50℃以下的干燥氮气氛中进行成膜。

[0331] 另外,作为样品1,在玻璃衬底上形成厚度为95nm的IGZO膜之后,在第一干蚀刻条件下进行180秒的蚀刻之后,将其浸渍于纯水中,形成电极,来测量电阻率。样品1的结果是 $130 \Omega \cdot \text{cm}$ 。另外,作为样品2,在第一干蚀刻条件后,以稀氢氟酸(以1/100的比例稀释的)浸渍30秒之后,形成电极测量电阻率。样品2的结果是 $3.9 \times 10^9 \Omega \cdot \text{cm}$ 。

[0332] 由上述结果可知:由于使用含有卤素元素的气体的干蚀刻杂质附着或混入IGZO膜而导致IGZO膜的电阻率下降,通过利用稀氢氟酸进行表面处理杂质被去除,而使IGZO膜接近进行干蚀刻之前的状态。

[0333] 另外,作为样品3,在玻璃衬底上形成厚度为95nm的IGZO膜之后,在第二干蚀刻条件下进行180秒的蚀刻之后,将其浸渍于纯水中,形成电极,来测量电阻率。另外,作为样品4,在第二干蚀刻条件后,以稀氢氟酸(以1/100的比例稀释的)浸渍30秒之后,形成电极测量电阻率。

[0334] 另外,作为样品5,在玻璃衬底上形成厚度为95nm的IGZO膜之后,在第三干蚀刻条件下进行180秒的蚀刻之后,将其浸渍于纯水中,形成电极,来测量电阻率。另外,作为样品

6,在第三干蚀刻条件后,以稀氢氟酸(以1/100的比例稀释的)浸渍30秒之后,形成电极测量电阻率。

[0335] 另外,作为样品7,在玻璃衬底上形成厚度为95nm的IGZO膜之后,在第四干蚀刻条件下进行180秒的蚀刻之后,将其浸渍于纯水中,形成电极,来测量电阻率。另外,作为样品8,在第四干蚀刻条件后,以稀氢氟酸(以1/100的比例稀释的)浸渍30秒之后,形成电极测量申阻率。

[0336] 表1示出第一干蚀刻条件、第二干蚀刻条件、第三干蚀刻条件及第四干蚀刻条件。另外,作为进行干蚀刻的装置使用ICP(Inductively Coupled Plasma:电感耦合等离子体)蚀刻装置。

[0337] [表1]

|        | ICP    | Bias | Pressure | Cl <sub>2</sub> | BCl <sub>3</sub> | SF <sub>6</sub> | O <sub>2</sub> | Time  |

|--------|--------|------|----------|-----------------|------------------|-----------------|----------------|-------|

|        | (W)    | (W)  | (Pa)     | (sccm)          | (sccm)           | (sccm)          | (sccm)         | (sec) |

| [0338] | 第一蚀刻条件 | 2000 | 200      | 2.0             | -                | -               | 900            | 100   |

|        | 第二蚀刻条件 | 2000 | 1000     | 2.5             | 540              | -               | 540            | -     |

|        | 第三蚀刻条件 | 0    | 1500     | 2.0             | 150              | 750             | -              | -     |

|        | 第四蚀刻条件 | 2000 | 1000     | 2.5             | -                | 380             | 700            | -     |

[0339] 另外,图12是以电阻率为纵轴,分别示出比较例的电阻率(ref)与样品1至样品8的电阻率的图表。由上述结果可知:即使改变干蚀刻的条件,通过利用稀氢氟酸进行表面处理,可以使IGZO膜接近进行干蚀刻之前的状态,优选的是与进行干蚀刻之前相同的状态。

[0340] 由以上结果可知:通过进行杂质去除处理,可以去除引起氧化物半导体膜的低电阻化的杂质,由此可以抑制氧化物半导体膜的低电阻化。

[0341] 实施例2

[0342] 在本实施例中,对杂质去除处理的有无与晶体管特性的关系进行比较的结果进行说明。

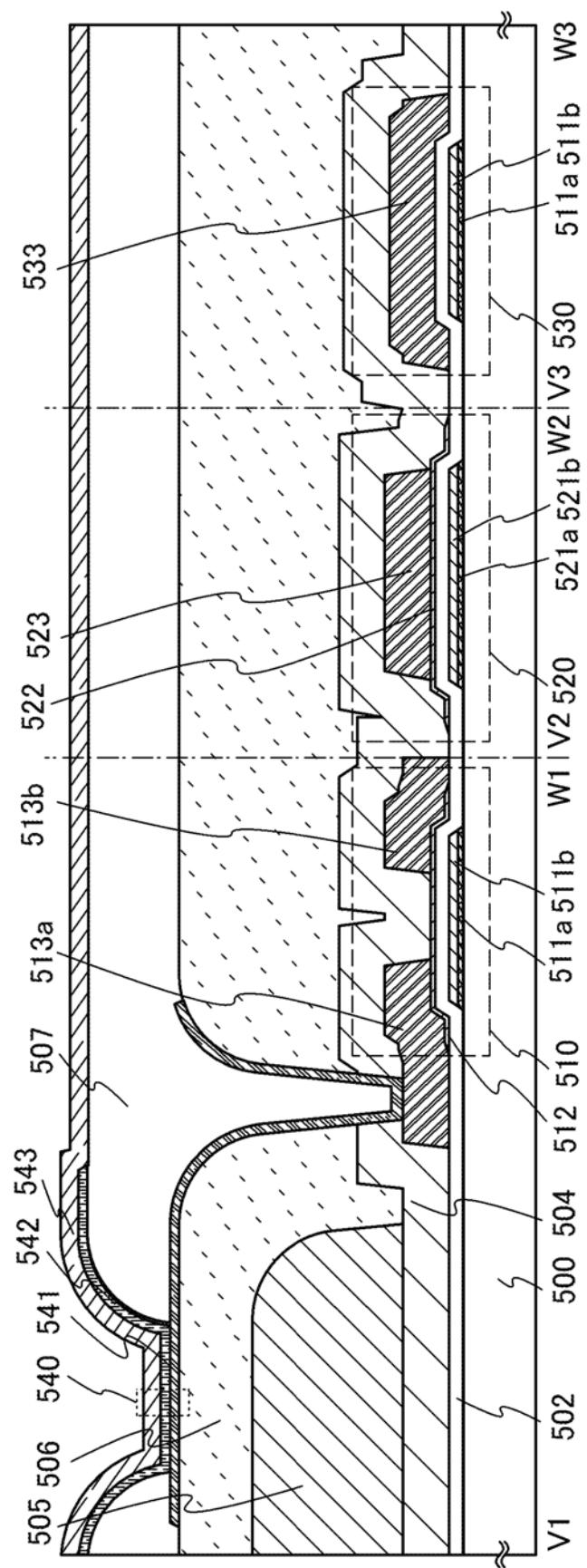

[0343] 下面,对本实施例中使用的样品A至样品D的制造方法进行说明。另外,参照图4A至4E对本实施例中制造的样品A至样品D所具有的晶体管的制造方法进行说明。

[0344] 首先,对样品A的制造方法进行说明。如图4A所示,作为衬底400,在玻璃衬底上作为基底绝缘膜形成100nm的氮化硅膜和150nm的氧氮化硅膜。然后,利用溅射法,形成30nm厚的氮化钽膜、200nm厚的铜膜、30nm厚的钨膜,并利用光刻工序在钨膜上形成抗蚀剂掩模,进行选择性的蚀刻形成栅电极层401。注意,图4A至4E没有示出基底绝缘膜。

[0345] 接着,在栅电极层401上作为栅极绝缘膜402,利用等离子体CVD法形成50nm厚的氮化硅膜、270nm厚的氧氮化硅膜。氮化硅膜的成膜条件为:SiH<sub>4</sub>/N<sub>2</sub>=50sccm/5000sccm、成膜功率为150W(RF)、成膜压力为40Pa、衬底温度为350℃。氧氮化硅膜的成膜条件为:SiH<sub>4</sub>/N<sub>2</sub>O=20sccm/3000sccm、电极面积为6000cm<sup>2</sup>时的成膜功率为100W(RF)、成膜压力为40Pa、衬底

温度为350℃。

[0346] 接着,在栅极绝缘膜402上,利用溅射法作为氧化物半导体膜形成35nm厚的IGZO膜。IGZO膜在如下条件下形成:作为溅射靶材使用In:Ga:Zn=1:1:1[原子数比];作为溅射气体将100sccm的氩与100sccm的氧供应至溅射装置的处理室内;将处理室内的压力控制为0.6Pa;并采用5kW的功率。另外,形成IGZO膜时的衬底温度为170℃。

[0347] 接着,通过光刻工序在氧化物半导体膜上形成抗蚀剂掩模,通过进行选择性的蚀刻形成岛状氧化物半导体膜403。

[0348] 接着,在氮气氛下以450℃进行1小时的加热处理,并在氮与氧的混合气氛下以450℃进行1小时的第一加热处理。

[0349] 接着,如图4B所示,在岛状氧化物半导体膜403上,作为导电膜445利用溅射法形成50nm厚的钨膜、100nm厚的铝膜、100nm厚的钛膜。然后,如图4C所示,通过光刻工序,在铝膜上形成抗蚀剂掩模,通过进行选择性的蚀刻,形成源电极层405a及漏电极层405b。

[0350] 这里,将铝膜及钛膜的蚀刻条件设定为:蚀刻气体( $BCl_3:Cl_2=750sccm:150sccm$ );偏置功率为1500W;ICP电源功率为0W;压力为2.0Pa。将钨膜的蚀刻条件设定为:蚀刻气体( $SF_6:BCl_3=700sccm:380sccm$ );ICP电源功率为2000W;偏置功率为1000W;压力为2.5Pa。

[0351] 接着,在氮气氛下以300℃进行1小时的第二加热处理。

[0352] 接着,如图4E所示,在氧化物半导体膜403、源电极层405a及漏电极层405b上,作为层间绝缘膜形成400nm的氧化硅膜和200nm的氧氮化硅膜。

[0353] 接着,在氮气氛下以300℃进行1小时的第三加热处理。

[0354] 接着,作为层间绝缘膜形成1.5μm的聚酰亚胺。

[0355] 接着,在氮气氛下以300℃进行1小时的第四加热处理。

[0356] 接着,在层间绝缘膜中形成到达源电极层405a及漏电极层405b的开口。最后,利用溅射法形成100nm厚的钛膜、400nm厚的铝膜及100nm厚的钛膜。然后,通过光刻工序在钛膜上形成抗蚀剂掩模,通过进行选择性的蚀刻形成电极层。

[0357] 通过上述工序制造样品A。

[0358] 接着,对样品B的制造方法进行说明。作为样品B,到源电极层及漏电极层的形成工序为止,与样品A采用相同的工序。

[0359] 如图4D所示,在形成源电极层405a及漏电极层405b之后,对氧化物半导体膜403进行氧等离子体处理。作为氧等离子体处理采用如下条件:使用ICP装置,ICP电源功率为0W,偏置功率为500W,压力为2.0Pa,衬底温度为80℃。

[0360] 然后,从第二加热处理到电极层形成工序为止,采用与样品A同样的工序制造样品B。

[0361] 接着,对样品C的制造方法进行说明。作为样品C,到形成源电极层及漏电极层的工序为止,与样品A采用相同的工序。

[0362] 如图4D所示,在形成源电极层405a及漏电极层405b之后,对氧化物半导体膜403进行氧等离子体处理。作为氧等离子体处理采用如下条件:使用ICP装置,ICP电源功率为0W,偏置功率为500W,压力为2.0Pa,衬底温度为80℃。

[0363] 接着,将氧化物半导体膜浸渍于稀释氢氟酸(1/500稀释)中60秒。

[0364] 然后,从第二加热处理至电极层形成工序为止,采用与样品A同样的工序制造样品

C。

[0365] 接着,对样品D的制造方法进行说明。除了将氧化物半导体膜403浸渍于稀释氢氟酸中的时间与样品C不同之外,采用与样品C同样的工序制造样品D。

[0366] 作为样品D,将氧化物半导体膜403浸渍于稀释氢氟酸(1/500稀释)中120秒。

[0367] 接着,分别对样品A至样品D的电特性进行评价。

[0368] 图13A示出样品A的Vg-Id特性的测量结果,图13B示出样品B的Vg-Id特性的测量结果,图14A示出样品C的Vg-Id特性的测量结果,图14B示出样品D的Vg-Id特性的测量结果。

[0369] 由图13A和13B及图14A和14B的结果可知:在形成源电极层405a及漏电极层405b之后没有进行杂质去除工序的样品A的电特性不均匀;相对于此,在形成源电极层405a及漏电极层405b之后进行了氧等离子体处理的样品B与样品A相比,电特性不均匀得到降低;另外,除了氧等离子体处理之外还进行了稀释氢氟酸处理的样品C及样品D的电特性不均匀得到进一步降低。

[0370] 由以上结果可知:在形成源电极层405a及漏电极层405b之后,通过进行杂质去除工序可以改善晶体管的电特性不均匀。

[0371] 符号说明

[0372] 400 衬底

[0373] 401 栅电极层

[0374] 402 栅极绝缘膜

[0375] 403 氧化物半导体膜

[0376] 405a 源电极层

[0377] 405b 漏电极层

[0378] 407 绝缘膜

[0379] 408 平坦化绝缘膜

[0380] 410 晶体管

[0381] 420 晶体管

[0382] 430 晶体管

[0383] 440 晶体管

[0384] 445 导电膜

[0385] 447 气体

[0386] 448a 抗蚀剂掩模

[0387] 448b 抗蚀剂掩模

[0388] 500 衬底

[0389] 502 栅极绝缘膜

[0390] 504 层间绝缘膜

[0391] 505 滤色片层

[0392] 506 绝缘膜

[0393] 507 分隔壁

[0394] 510 晶体管

[0395] 511a 栅电极层

- [0396] 511b 栅电极层

- [0397] 512 氧化物半导体膜

- [0398] 513a 导电层

- [0399] 513b 导电层

- [0400] 520 电容元件

- [0401] 521a 导电层

- [0402] 521b 导电层

- [0403] 522 氧化物半导体膜

- [0404] 523 导电层

- [0405] 530 布线层交叉部

- [0406] 533 导电层

- [0407] 540 发光元件

- [0408] 541 电极层

- [0409] 542 场致发光层

- [0410] 543 电极层

- [0411] 601 衬底

- [0412] 602 光电二极管

- [0413] 606a 半导体膜

- [0414] 606b 半导体膜

- [0415] 606c 半导体膜

- [0416] 608 粘合层

- [0417] 613 衬底

- [0418] 631 绝缘膜

- [0419] 633 层间绝缘膜

- [0420] 634 层间绝缘膜

- [0421] 640 晶体管

- [0422] 641a 电极层

- [0423] 641b 电极层

- [0424] 642 电极层

- [0425] 643 导电层

- [0426] 645 导电层

- [0427] 656 晶体管

- [0428] 658 光电二极管复位信号线

- [0429] 659 栅极信号线

- [0430] 671 光电传感器输出信号线

- [0431] 672 光电传感器参考信号线

- [0432] 4001 衬底

- [0433] 4002 像素部

- [0434] 4003 信号线驱动电路

- [0435] 4004 扫描线驱动电路

- [0436] 4005 密封剂

- [0437] 4006 衬底

- [0438] 4008 液晶层

- [0439] 4010 晶体管

- [0440] 4011 晶体管

- [0441] 4013 液晶元件

- [0442] 4015 连接端子电极

- [0443] 4016 端子电极

- [0444] 4019 各向异性导电膜

- [0445] 4020 绝缘膜

- [0446] 4021 绝缘膜

- [0447] 4030 电极层

- [0448] 4031 电极层

- [0449] 4032 绝缘膜

- [0450] 4033 绝缘膜

- [0451] 4035 间隔物

- [0452] 4510 分隔壁

- [0453] 4511 场致发光层

- [0454] 4513 发光元件

- [0455] 4514 填充材料

- [0456] 9000 桌子

- [0457] 9001 框体

- [0458] 9002 腿部

- [0459] 9003 显示部

- [0460] 9004 显示按钮

- [0461] 9005 电源供应线

- [0462] 9033 卡子

- [0463] 9034 开关

- [0464] 9035 电源开关

- [0465] 9036 开关

- [0466] 9038 操作开关

- [0467] 9100 电视装置

- [0468] 9101 框体

- [0469] 9103 显示部

- [0470] 9105 支架

- [0471] 9107 显示部

- [0472] 9109 操作键

- [0473] 9110 遥控操作机

- [0474] 9201 主体

- [0475] 9202 框体

- [0476] 9203 显示部

- [0477] 9204 键盘

- [0478] 9205 外部连接端口

- [0479] 9206 定位装置

- [0480] 9630 框体

- [0481] 9631 显示部

- [0482] 9631a 显示部

- [0483] 9631b 显示部

- [0484] 9632a 区域

- [0485] 9632b 区域

- [0486] 9633 太阳能电池

- [0487] 9634 充放电控制电路

- [0488] 9635 电池

- [0489] 9636 DCDC转换器

- [0490] 9637 转换器

- [0491] 9638 操作键

- [0492] 9639 按钮

图 1A

图 1B

图 1C

图 1D

图 2A

图 2B

图 2C

图 2D

图 2E

图 3A

图 3B

图 3C

图 3D

图 4A

图 4B

图 4C

图 4D

图 4E

图 5A

图 5B

图 5C

图 6A

图 6B

图 7A

图 7B

图 8A

图 8B

图 9A

图 9B

图 9C

图 10A

图 10B

图 10C

图 11

图 12

图 13A

图 13B

图 14A

图 14B