# **United States Patent**

| [72] | Inventors | Vernon R. Herald                    |

|------|-----------|-------------------------------------|

|      |           | Chicago;                            |

|      |           | Paul M. Kolesar, Chicago; Robert A. |

|      |           | Payne, Des Plaines, all of, Ill.    |

| [21] | Appl. No. | 626,459                             |

| [22] | Filed     | Mar. 28, 1967                       |

| [45] | Patented  | July 20, 1971                       |

| [73] | Assignee  | Stewart-Warner Corporation          |

|      | -         | Chicago, Ill.                       |

|      |           |                                     |

- [54] DISPLAY SYSTEM

- 20 Claims, 24 Drawing Figs.

- [51]

Int. Cl.

G09f 9/34

[50]

Field of Search

340/324,

334, 337, 336, 339, 324.1, 347 DD, 174, 154, 152

- [56] References Cited

### UNITED STATES PATENTS

| 1,054,336 | 2/1913  | Brown         | 340/339 |

|-----------|---------|---------------|---------|

| 2,911,622 | 11/1959 | Ayres et al   | 340/174 |

| 3,225,342 | 12/1965 | Clark         | 340/324 |

| 3,273,140 | 9/1966  | Foster et al. | 340/334 |

## 111 3,594,778

| 2,181,682 | 11/1939 | Scheidegger | 340/154 |

|-----------|---------|-------------|---------|

| 3,462,739 | 8/1969  |             | 340/152 |

| D         |         |             |         |

Primary Examiner—John W. Caldwell Assistant Examiner—Marshall M. Curtis Attorneys—Augustus G. Douvas, William J. Newman and Norton Lesser

ABSTRACT: Control System for a data display system such as a scoreboard, message board or the like wherein display indicators having location addresses, on the board, are addressed and actuated through a logic system which first receives and stores address data pertaining to a particular indicator, receives display character data, and automatically reads out the address data to the board for enabling the desired indicator followed by the display character data to actuate it to display the desired character. A buffer memory is provided for controlling the input to the logic system from a variety of input devices including console keyboard, punch tape typewriter and reader as well as magnetic memory storage devices. Circuits are provided in conjunction with the buffer for updating particular message data existing in the buffer as required by changes in the game or other information.

SHEET 01 OF 21

BA

3,594,778

27

26

25

24

23

22

2

20

<u>o</u>

SHEET

02 OF 21

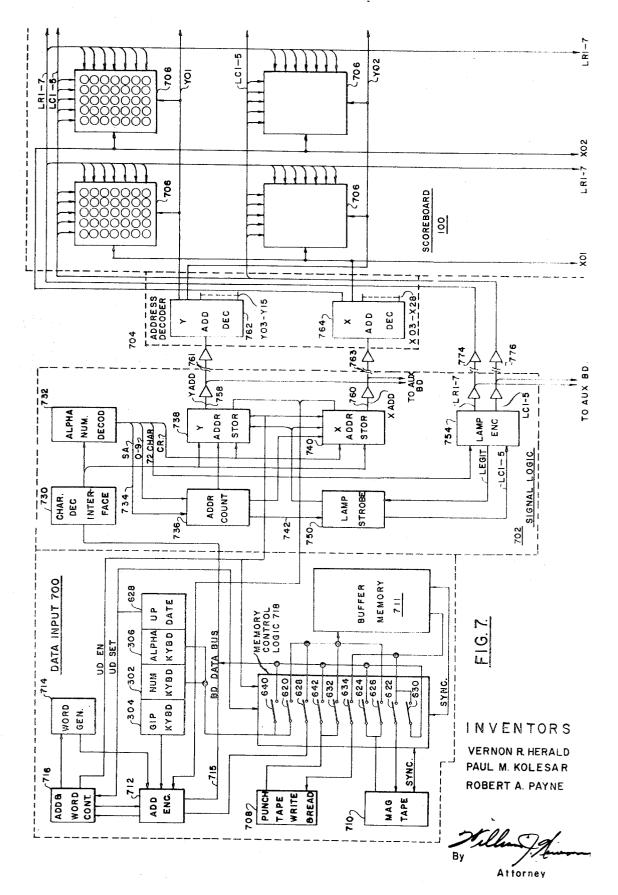

F I G. 5A.

INVENTORS VERNON R. HERALD PAUL M. KOLESAR ROBERT A. PAYNE

By

3,594,778

SHEET 03 OF 21

3,594,778

....

SHEET 04 OF 21

VERNON R.HERAL PAUL M. KOLESAR ROBERT A. PAYNE

Al By

SHEET 05 OF 21

INVENTOR S VERNON R. HERALD PAUL M. KOLESAR ROBERT A. PAYNE

By Willia Attorney

3,594.778

3,594,778

# SHEET 07 OF 21

# MODIFIED ASCII CODE

|          |    |    |    |    |         |    | ······ | ·               |   |    |   |       | -     |

|----------|----|----|----|----|---------|----|--------|-----------------|---|----|---|-------|-------|

|          |    |    |    |    | •       | 0  | 0      | 0               | 0 | 1  | 1 | 1     | 1     |

|          |    |    |    |    |         | 0  | 0      | 1               | 1 | 0  | 0 | 1     | 1     |

|          |    |    |    | 0  | 1       | 0  | 1      | 0               | 1 | 0  | 1 |       |       |

|          |    |    |    |    | COLUMAN |    |        |                 |   |    |   |       |       |

| 07 06 05 | 04 | 63 | 62 | 61 | ROW     | 0  | 1      | 2               | 3 | 4  | 5 | 6     | 7     |

|          | 0  | 0  | 0  | 0  | 0       |    |        | SPACE           | 0 |    | P | ALL   | ALL   |

|          | 0  | 0  | 0  | 1  | . 1 ,   |    |        | /               | 1 | A  | Q | SCI   | SCIG  |

| 1        | 0  | 0  | Ż  | 0  | 2 2     |    |        |                 | 2 | 8  | R | SC2   | SC 17 |

|          | 0  | 0  | 1  | 1  | 33      |    |        | #               | 3 | с  | 5 | 503   | SC 18 |

|          | 0  | 1  | 0  | 0  | 4 4     |    |        | \$              | 4 | 0  | 7 | SC4   | 5019  |

|          | 0  | 1  | 0  | 1  | 5 s     |    |        | °/o             | 5 | E  | U | 505   | 5020  |

|          | 0  | 1  | 1  | 0  | 60      |    |        | &               | 6 | F  | V | 506   | 5621  |

|          | 0  | 1  | 1  | 1  | 7.7     |    | ETB    | /               | 7 | G  | W | 507   | 5022  |

|          | 1  | 0  | 0  | 0  | 80      |    |        |                 | 8 | 4  | x | 5 C 8 | 5C 23 |

|          | 1  | 0  | 0  | 1  | 9,      |    |        | )               | 9 | I  | У | 509   | SC24  |

|          | 1  | 0  | 1  | 0  | 10 2    |    |        | *SA             |   | σ  | Z | 5010  | SC 25 |

| -        | 1  | 0  | 1  | 1  | و [[    |    |        | +               |   | K  |   | SC11  | SC 26 |

|          | 1  | 1  | 0  | 0  | 12 4    |    |        | BLANK<br>MESS + |   | ۷  |   | SC12  | 5627  |

|          | 1  | 1  | 0  | 1  | 135     | CR |        | -               |   | М  |   | SC13  |       |

|          | 1  | 1  | 1  | 0  | 146     |    |        |                 |   | N  |   | sc14  |       |

|          | 1  | 1  | 1  | 1  | 15 7    |    |        | /               | ? | 0. |   | SC 15 |       |

FIG. 9.

INVENTORS VERNON R. HERALD PAUL M. KOLESAR ROBERT A PAYNE

Kille By

Attornev

SHEET 08 OF 21

SHEET 09 OF 21

Attornev

3,594.778

### SHEET 10 OF 21

By Man Martiney

3,594,778

3,594,778

3,594,778

SHEET 13 OF 21

By William Man

3,594,778

3,594,778

SHEET 15 OF 21

By Willia Attor Day

3,594,778

SHEET 17 OF 21

3,594,778

SHEET 18 OF 21

3,594,778

SHEET 19 OF 21

T.

3,594,778

SHEET 20 OF 21

### INVENTORS VERNON R. HERALD PAUL M. KOLESAR

ROBERT A. PAYNE

By Millian A.

SHEET 21 OF 21

3,594,778

Willin J. Men Вý

DISPLAY SYSTEM

#### **BACKGROUND OF INVENTION**

1

The system herein described and claimed is a digital controlled, all electronic, semiconductor system having highly flexible input and display output capabilities operable at very high speeds. It is capable of addressing and reading in display data to any location on the display board without having to 10 switch through a number of other locations and without disturbing the data at any other location. That is, any display device or indicator at the display board may be reached and caused to display a desired character merely by inserting the proper address data followed by the desired character data. 15 The address data enables the desired indicator at the desired location on the board and the display data triggers that indicator to operate in accordance with the desired character. Any other desired display device or indicator may then be addressed and triggered, or, in the case of message information 20 display, the next sequenced indicator may be automatically addressed to display the desired character. Hence, the system has full flexibility to provide an almost unlimited array of visual arrangements.

The system has the capability of being served by a variety of different types of input devices. Through the use of a sequentially operated buffer memory and unique control circuits therefor, information may be read in at any speed from a typewriter-type keyboard, a punch tape reader, magnetic tape or drum storage etc., and read out to the display board at a 30 in accordance with the first figure to which they are referenced in the description

In addition provisions are made for the convenient change of any data in a message to be displayed on the board. For example, during a baseball game it is desirable to display up-todate information regarding ballgames being played by other 35 baseball team such as the inning of play, score, battery, and first game score if a doubleheader is being played. Since one or more segments of this information changes frequently during the course of a game, it is desirable to change only the required information segments without having to reprogram 40 the whole message each time the message is displayed.

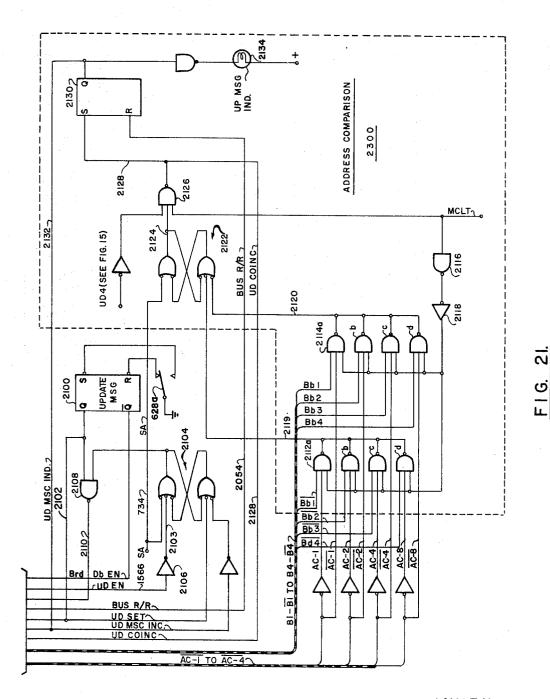

The present system provides apparatus for updating display data previously read into the buffer memory including means for encoding the address data of the display device to be changed and means for comparing the encoded address with 45 the address data in each data segment in the buffer memory to locate the data segment to be updated. Means including the keyboard are also included to erase the display data in the data segment and enter the updating display data.

It is therefore an object of this invention to provide a new 50 display system for informational message display.

It is also an object of this invention to provide a display system having flexible data input means including a variety of different data input devices.

Another object of this invention is to provide a display 55 system having facilities to update selected portions of stored messages.

Further, it is an object of this invention to provide a display system including a buffer memory input which controls the speed of data input to the message board controls from a 60 variety of input devices and forms a part of the apparatus for updating previously programmed message data.

Other objects and features will become apparent with a further reading of this specification making special reference to the accompanying drawings in which:

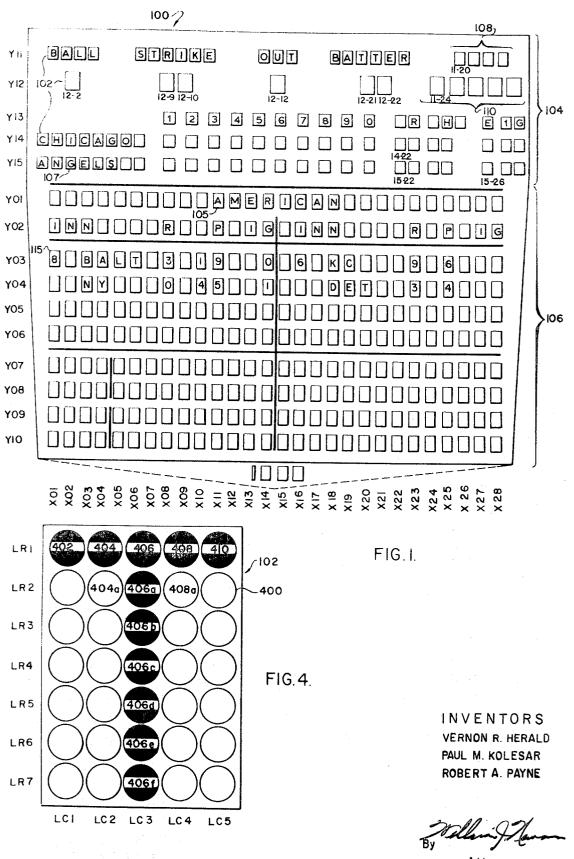

FIG. 1 is an elevation view of a display board of the type to be used in an athletic stadium for the display of game statistics and message information;

FIG. 2 is an elevation view of an auxiliary scoreboard;

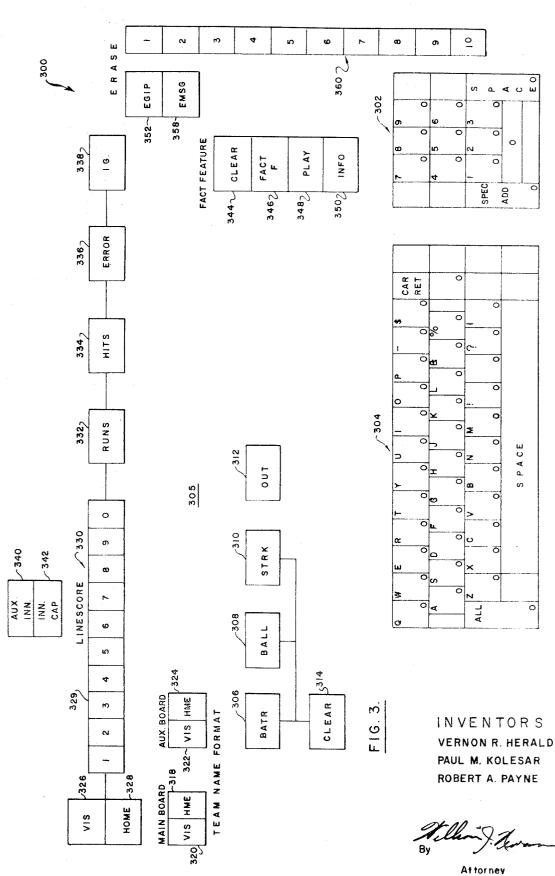

FIG. 3 is a plan view of a portion of the operator control 70 console for operating the scoreboards of FIGS. 1 and 2;

FIG. 4 is an elevation view of an indicator of the type used in the scoreboards of FIGS. 1 and 2;

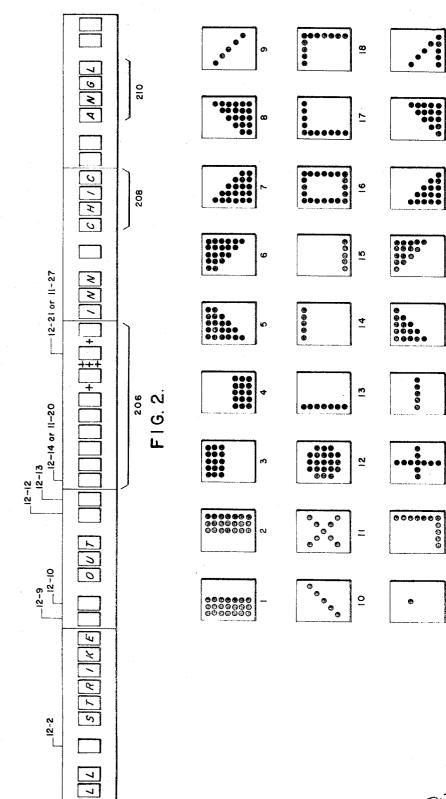

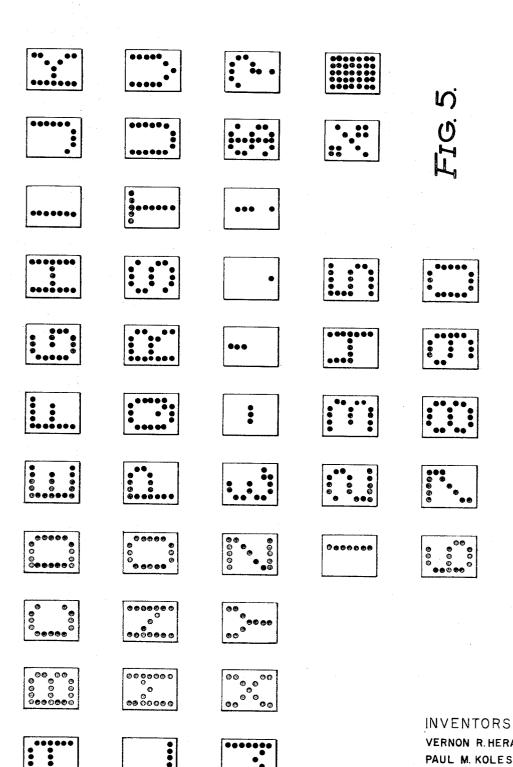

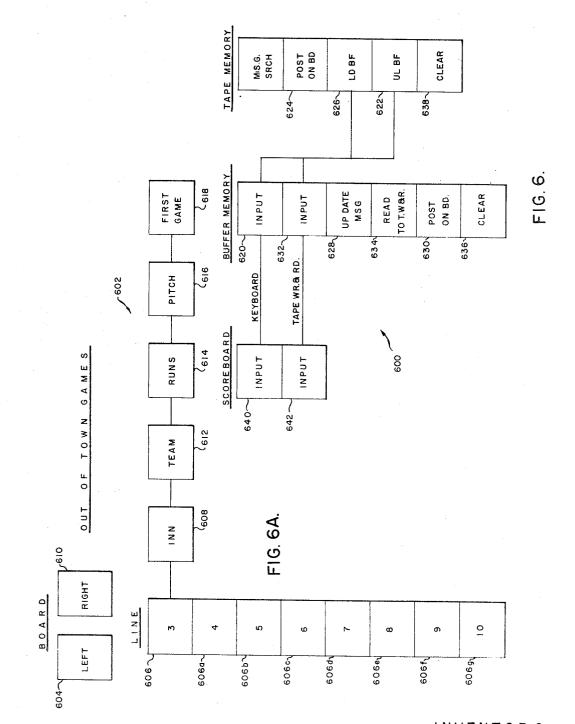

FIG. 5 depicts alpha-numeric and punctuation characters of the type which may be displayed on the indicator of FIG. 4; FIG. 5a depicts special characters which may be displayed on the indicator of FIG. 4 for shaping pictures and/or designs on the message portion of the scoreboard of FIG. 1; FIGS. 6 and 6a are plan views of other portions of the

operator console for operating the scoreboards;

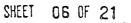

FIG. 7 is a block diagram of the display control system of this invention;

FIG. 8 is a schematic diagram of a control circuit for each individual indicator;

FIG. 9 is a table of modified ASCII coded representations for the display characters shown in FIGS. 5 and 5a; and

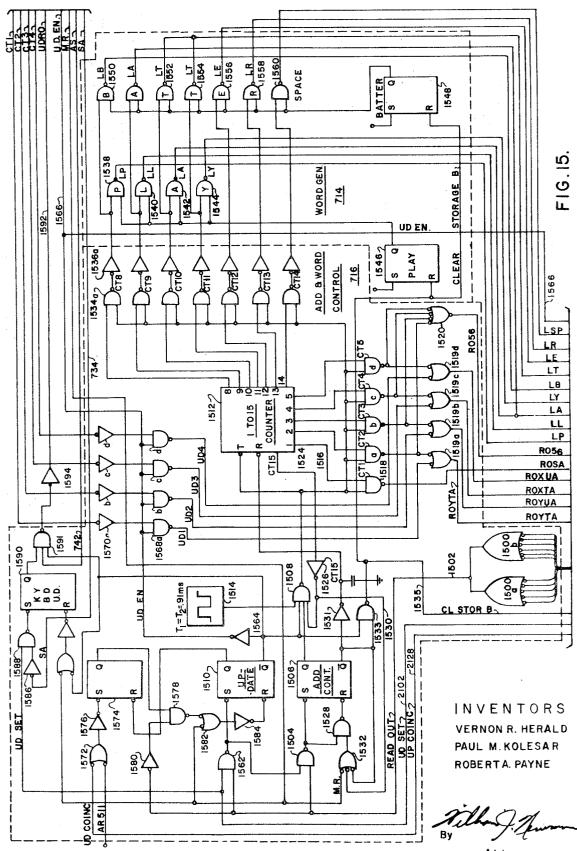

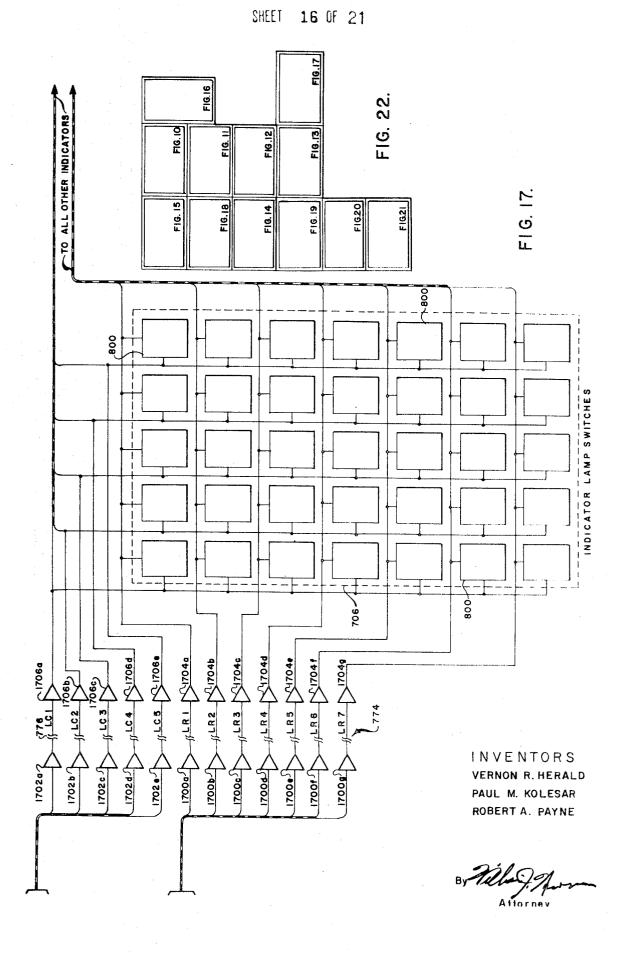

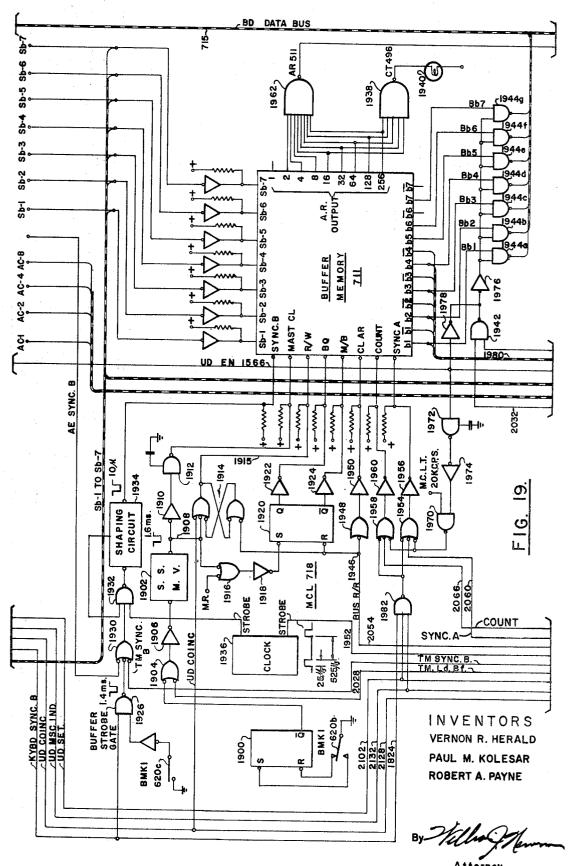

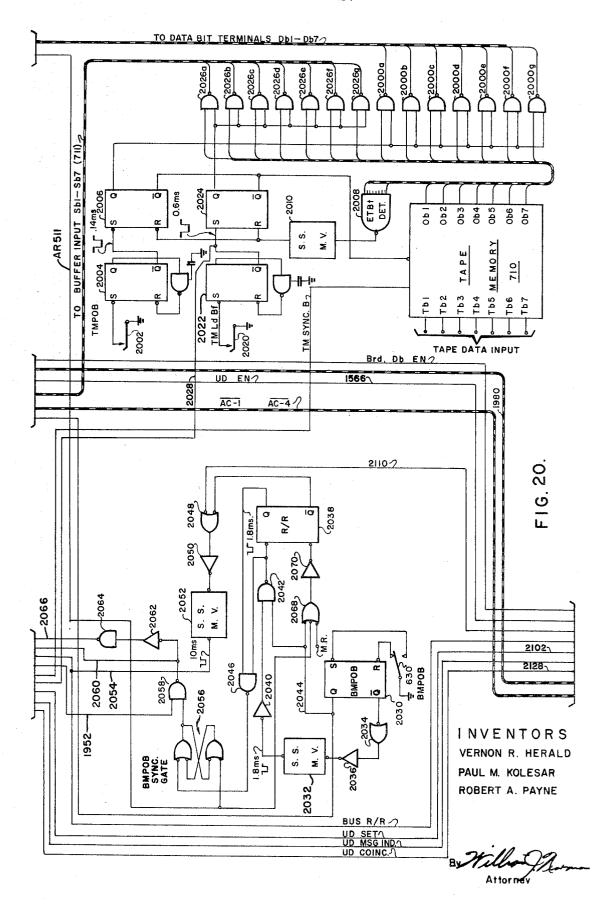

FIGS. 10 through 21 are schematic diagrams of the control system to be arranged in the manner shown in FIG. 22;

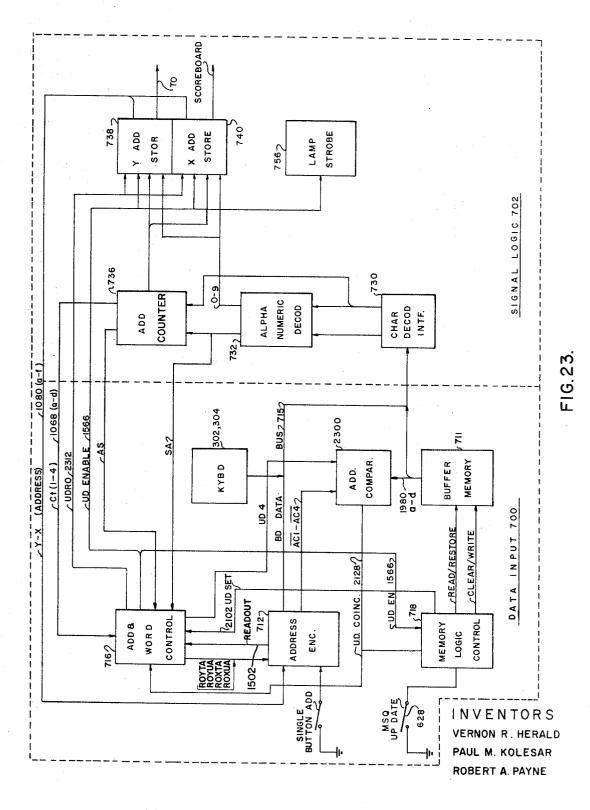

FIG. 23 is a block diagram of the circuits utilized in performing the update function.

Although the features of this invention pertain to any type of display system, they will be herein described with reference to a scoreboard system which embodies all of the claimed features. The scoreboard hereinafter described is essentially of the type now being used in the Anaheim Stadium at Anaheim, Calif. In the description to follow, the reference numbers used will be coded by means of the 100's and 1000's digits to the particular figure in which the component or element first appears and that component or element will retain that number in any subsequent figure in which it appears. Thus, an element with the number 246 would be found in FIG. 2 whereas an element with number 1216 would be found in FIG. 12. Conductors extending between one or more figures will be numbered in accordance with the first figure to which they are referenced in the description.

#### GENERAL DESCRIPTION OF SCOREBOARD AND CONSOLE (FIGS. 1, 2 & 3)

The scoreboard display portion of the system comprises a main scoreboard 100 (FIG. 1) made up of a plurality of display devices or indicators 102 which may register alpha-numeric characters or other designs if desired as will be described hereinafter. If the main board is located in the park so that certain portions of the spectators cannot view it, one or more auxiliary scoreboards 200 (FIG. 2) may be located at appropriate locations. The auxiliary scoreboard 200 is also made up of display indicators 102 of essentially the same type utilized in the main board. The main scoreboard 100 is divided into two basic sections, namely, the game in progress section 104 and the message portion 106, while the auxiliary scoreboard 200 is devoted strictly to the game in progress information.

As shown in FIG. 1 the scoreboard display panel is arranged in rows (Y01 through Y15) and columns (X01 through X28) of indicators for the purpose of exact addressing of any desired indicator. Thus, any indicator on the display panel 100 may be referred to by stating its address in terms of its Y number and its X number. In the system described the first row of the message section 106 is designated Y01 and the message portion continues through row Y10 while the game in progress portion includes rows Y11 through Y15. Thus, the indicator 105, upon which the letter A in the word AMER-ICAN is portrayed, has the location address Y01-X11. whereas the indicator 107 displaying the letter G in the word ANGELS is located by the address Y15-X03. In the system described each Y and X address number must consist of two digits to satisfy the system logic as will be seen later. Hence, 65 address numbers under 10 must be preceded by a zero, e.g. 01.02 etc.

Any indicator on the board except certain fixed caption indicators in the game in progress section 104 may be reached to display a desired character by reading into the control 70 system the proper address for that indicator. This is accomplished, for example, by the use of the numeric keyboard 302, forming a part of the operators console 300 shown in FIG. 3. Thus, indicator 105 may be reached to display the letter A by first punching the key marked SPEC. ADD. (Special Address) 75 followed by the number 01 for the Y address, which is in turn

followed by the number 11 for the X address. The subsequent actuation of the A key in the typewriterlike alpha keyboard 304 will then cause the latter A to be displayed on addressed indicator 105. The following indicators are then automatically sequentially addressed so that the operator needs merely to punch the alpha keys M, E, R, I, C, A and N to display the whole word AMERICAN.

If the message is longer than the row, then further message display is impeded until the carriage return key 305 is actuated to cause the automatic addressing of the first indicator in the next row. The message may then be continued until the last indicator in the last row of the message section (Y10-X28) is reached. Further automatic advancing of the address is then prevented because the next numbered indicator row Y11 is in the game in progress section 104. Thus, the indicators in the Game in Progress Section cannot be inadvertently affected, when writing in a message on the Message Section 106.

As previously mentioned, the game in progress section 104 of the main scoreboard 100 as well as the auxiliary scoreboard 200 are devoted to information pertaining to the particular game being played. The top two rows of indicator Y11 and Y12 are used for the display of play by play information while the next three rows Y13 through Y15 are used for the inning 25 in addition to the multibutton addressing previously described by inning or line score information as well as the game totals. This section of the board is controlled by the upper portion 305 of the operators console shown in FIG. 3. The indicators in the top row Y11 displaying the words BALL, STRIKE, tuated by a power switch directly connected to those indicators and are not controlled by the control logic of the system hereinafter described. These indicators might also be arranged to display fixed captions for football games in which case the words DOWN, TO GO, QTR, and BALL ON will be displayed. The indicators in row Y13 displaying the captions R. H, E and 1G are also fixed caption indicators not controllable by the control logic.

To display the desired play by play information the operator manipulates the proper button 306, 308, 310 or 312 which au- 40 tomatically addresses the related numeric indicators immediately below the appropriate fixed captions. The numeric information is then read in by means of the numeric keyboard 302. Thus, the present batter's number is displayed by first 45 operating key 306 which automatically addresses numeric indicator Y12-X21 followed by the player's number inserted from the keyboard 302. Each ball and strike of the batter is registered by operation of buttons 308 and 310, followed by the insertion of the numeric data from keyboard 302. When the 50 next batter comes to bat the previous batter's number and the balls and strikes may be erased by operation of the CLEAR button 314.

The ball, strike and out data is displayed on the auxiliary scoreboard 200 simultaneously with its display on the main 55 board 100. The numeric indicators immediately following the fixed captions on the auxiliary board 200 are designated by the same addresses as the corresponding numeric indicators on the main board so that they may be controlled together. Thus, the indicator immediately after the fixed caption indica-60 tors spelling BALL on the auxiliary board 200 has the same address, Y12-XO2, as the indicator immediately under the fixed caption indicators spelling BALL on the main board 100.

The group of indicators 206 are used for displaying various 65 information including the present batter's number. However, since these indicators are used for other information, fixed caption indicators cannot be used and the word BATTER is automatically displayed by means of the control logic. Therefore, when the operator actuates button 306 on the console, 70 the control logic automatically generates the word BATTER and causes it to be displayed on the first six indicators of the group 206. The insertion of the batter's number automatically causes its display on the last two indicators of the group 206

indicators of group 206 and the word is generated in a manner which will be hereinafter described with respect to the control logic system.

The line score information of rows Y13 through Y15 of the main board is also controlled by means of single button addressing in a manner similar to the play by play information of lines Y11 and Y12. For example the word ANGELS is written onto indicators Y15-X01 through Y15-X06 on the main board 100 by use of the home team button 318 in the team 10 name format portion of the console 300 which automatically addresses indicator Y15-X01. This is followed by the insertion from the alpha character buttons on keyboard 304, the letters spelling out the name ANGELS. The visiting team name format button 320 is used for the single button ad-15 dressing of indicator Y14-X01 for writing in the name of the visiting team. Separate auxiliary board team name format buttons 322 and 324 are provided because the names are to be abbreviated in indicator groups 208 and 210 on the auxiliary board 200. However, if the same number of indicators were 20 provided as in the main scoreboard, the names could be written in simultaneously on the two boards by giving them both the same address.

It is to be noted that the single button means of addressing is for writing in the word AMERICAN, and this capability extends throughout all of the scoreboard so as to give double access to any indicators therein.

The line score statistics may be inserted in rows Y14 and OUT and BATTER are fixed caption indicators which are ac- 30 Y15 for the visitor and home teams, respectively by actuation of the appropriate team buttons 326, 328 followed by the appropriate inning button from inning button group 330 or one of the buttons 332, 334, 336 or 338, which ever is required for the information to be displayed. This addresses the proper in-35 dicator in the line score portion of the board and the subsequent input of a numerical character from keyboard 302 will cause the proper display. Thus, to indicate an ANGELS run in the third inning, the operator will press the home team button 328 followed by the third inning button 329 of the line score inning group 330, followed by the numeric character 1 button on numeric keyboard 302.

> The auxiliary board only displays the total runs of each team on the indicators immediately following the team name groups 208 and 210 and are addressed simultaneously with the runs indicators Y14-X22 and Y15-X22 when the respective team buttons 326, 328 and the runs button 332 are actuated. A subsequent insertion of the numeric data from keyboard 302 will cause the data to be displayed simultaneously on the two boards. The inning number is entered into the auxiliary board following the fixed caption indicators displaying INN by operation of the AUX INN button 340, followed by the appropriate number from keyboard 302. The INN CAP button 342 is used for displaying the inning captions 1 through 0 in row Y13 of the main board 100.

> The fact feature controls on the console, including buttons 344, 346, 348 and 350, are used for displaying pertinent facts about a particular play in the nine indicators in rows Y11 and Y12 at the upper right-hand corner of the main board 100 and in the group of indicators 206 on the auxiliary board 200. The FACT F. button 346 is a one button address selector for the group of four indicators 108 in row Y11 and is used for writing any desired two, three or four-letter word thereon. It also addresses the first four indicators in the group 206 on auxiliary board 200. Thus, if it is desired to display the rule book number pertaining to a particular play, the operator presses the FACT F. button 346 and writes in the word RULE from the alpha keyboard 304. The INFO button 350 is then pressed which addresses the first indicator in group 110 and the rule book number is entered into the indicators 110 from the numeric keyboard 302. This information is also displayed on the auxiliary board group 206.

The play button 348 automatically displays the word PLAY on the indicators of group 108 of the main board and also on on the auxiliary board. The addresses for the auxiliary board 75 the first four indicators of the group 206 on the auxiliary

10

board. The indicator group 110 and the last five indicators of group 206 are then automatically addressed for insertion of the desired information. Thus, if the shortstop commits an error, the operator would press the play button 348 to display the word PLAY on the proper indicators and immediately enter the display data E6 from the keyboards 304, 302 to designate an error by the shortstop.

The erase function buttons 352, 358 and 360 perform the obvious function of extinguishing the bulbs in particular indicators on the scoreboards. The EGIP button 352, which stands for Erase Game In Progress, serves to erase all of the information displayed in the section 104 of the main scoreboard as well as the information on the auxiliary scoreboard, except for the fixed caption indicators. The EMSG button 358 provides for the erasure of all the information in the 10 rows forming the message section 106 of the message board. The group of button 360 provide for the erasure of a selected row in the message portion 106 of the scoreboard and that row is erased merely be depressing the particular button corresponding to the row desired to the erased.

FIGS. 6 and 6a show additional console buttons for controlling the input and flow of data in the display system. The group of buttons 600 control the flow of data between the memory in a manner which will be described in detail in the description of the circuit diagrams of FIGS. 10 through 21.

The group of buttons 602 are single button address types which aid in displaying the out-of-town game format in the message portion 106 of the scoreboard as shown in FIG. 1. 30 The word AMERICAN is written into row Y01 in the manner previously described and the inning captions are inserted in row Y02 in a similar manner. The actual data pertaining to the out-of-town games is easily inserted in lines Y03 to Y10 by means of single button addressing in the following manner. 35 The Baltimore-New York game is first programmed by actuating the left button 604, the line 3 button 606 and the inning button 608. The actuation of these three will develop the address Y03-X01 for selecting indicator 115 at which the number 8 for the 8th inning is to be displayed. Actuation of 40 the right button 610 along with the line 3 button 606 and inning button 608 will cause the automatic selection of indicator Y03-X16 for the game displayed on the right-hand side of the format. The digit 6 for display on indicator Y03-X16 is inserted by means of the numeric keyboard 302 as previously 45described. Likewise, the team name, number of runs, pitcher's number and first game score information is inserted by means of the buttons 612, 614, 616 and 618, respectively, with the proper row being selected by the line buttons 606, 606g. The proper side of the board is selected by means of the left and right buttons 604, 610 and the display data is written in by the alpha and numeric keyboards 302, 304.

It is not desirable to maintain the out-of-town information displayed on the message portion 106 of the scoreboard constantly throughout the game because of the need to display courtesy notes, advertising, crowd handling instructions, songs, etc. at different times during the game. Therefore, provisions are made for maintaining the out-of-town information in a storage memory from which it may be read out and 60displayed on the board whenever desired. To accomplish this the data is read into a buffer memory (to be described later) instead of going directly to the display board. From the buffer it may be written out to the board or into a permanent storage device such as a magnetic tape memory (also to be described 65 later) or a punch tape typewriter.

To program and store the out-of-town game format the buffer memory keyboard input (BMKI) button 620 is actuated before writing in the out-of-town game information with the group of buttons 602 and keys 302, 304. After the data has 70 been inserted into the buffer memory, it is transferred into the magnetic tape memory by depressing the tape memory unload buffer button 622. The message is then permanently stored on the magnetic tape for use at any time. Messages are stored at

sequent use in any well-known manner which does not form a part of this invention. If desired, the stored data may be posted directly onto the message portion of the scoreboard from the tape by depressing the tape memory post on board button 624 after selecting the desired message on the tape by any wellknown means. Otherwise the information may be read from the tape into the buffer for subsequent readout to the board by use of the tape memory load-to-buffer switch 626.

The out-of-town game information of course changes during the course of the afternoon or evening, and it is therefore desirable to provide means for updating the information where required without having to reprogram the whole message. This can be accomplished in the present system by reading the message stored on tape back into the buffer memory through the actuation of the tape memory load-tobuffer switch 626 and correcting the information while the message is in the buffer memory.

The address of the indicator to be updated is read into the 20 system logic either by one of the single addressing buttons or by the numerical keyboard 302 after which the update message button 628 is actuated to cause the inserted address to be sequentially compared with each of the addresses stored in the message buffer memory. When the address is found, a keyboards, the scoreboard, the buffer memory and the tape 25 light (not shown) in the data message button 628 goes on indicating that address has been found and the update data may be read in from the proper keyboard 302, 304. The updated message in the buffer then may be transferred directly to the scoreboard by actuation of the buffer memory post-on-board (BMPOB) switch 630 and/or returned to the tape memory by means of the tape memory unload buffer switch 622.

> The button 632 provides for the input of data from a punched tape typewriter and reader to the buffer memory while the button 634 enables reading of the buffer memory data back to the tape typewriter and reader in order to check the data contents of the buffer. The buffer memory clear button 636 is merely a mechanical interlock with the other buffer memory switches and enables the operator to release any of the other buffer memory switches after the function has been performed. The tape memory clear switch 636 performs the same function for the tape memory function buttons.

> The button 640 provides for the direct reading to the scoreboard from the buttons and keys on the console 300, while the button 642 provides for the direct reading to the scoreboard from the tape typewriter and reader.

The manner in which the manipulation of the various buttons in the group 600 perform their indicated functions will be described in later sections of the specification relating to the 50 control logic of the system.

### DISPLAY CHARACTERS (FIGS. 4 and 5)

The display devices or indicators 102 utilized in the display system herein described are individual modules, each com-55 prising a matrix of 35 lamps 400 arranged in seven rows (LR-1 through LR-7) and five columns (LC-1 through LC-5) as indicated in FIG. 4. The different characters are formed by illumination of the lamps in the desired pattern. FIG. 5 shows the standard alpha, numeric and punctuation displays as they would be formed on a 35-lamp matrix.

A large variety of other display characters may also be formed by the lamp matrix indicators 102 which can be used in forming pictures, designs or animated displays on the message portion 106 of the scoreboard. FIG. 5a shows a number of different display characters which may be programmed for use in this manner.

It is to be understood that other indicator configurations might be utilized without departing from the teachings of this invention. For example, the lamps 400 need not necessarily be arranged in 5×7 matrices, but may be arranged in any convenient manner with any number of lamps. Also, it may be desireable to use other visually observable elements than lamps depending upon the use of the board. Whereas light particular address locations on the tape and retrieved for sub- 75 bulbs mounted in a board having a black surface is preferred

for out door display systems where a wide range of ambient light conditions call for the use of transmitted light, indoor locations may call for other visually observable elements. For example, if the board is located in a constant high illumination ambient area, it may be desireable to utilize reflective mem- 5 bers such as white painted discs or the like instead of lamps 400.

In additions, for certain aspects of this invention it may be desirable to use other types of visual displays than the matrixtype indicators. Some message board applications might call 10 for alpha-numeric wheels or belts or any of the other wellknown types of alpha-numeric character displays and where applicable the use of such are contemplated.

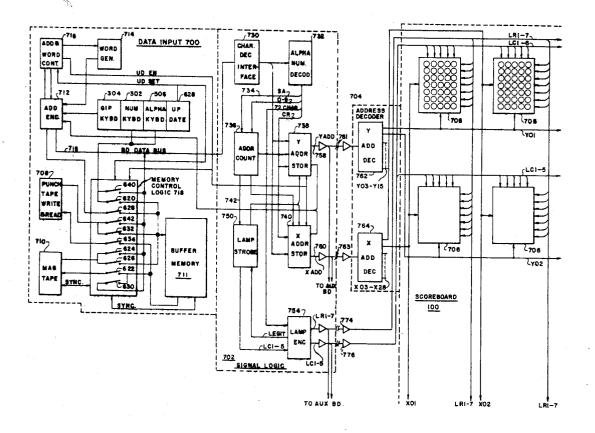

### GENERAL DESCRIPTION OF CONTROL SYSTEM (FIG. 7)

The control system as shown in the block diagram of FIG. 7 comprises data input means 700 and signal logic means 702, as well as the address decoder means 704 and the indicator 20 circuits 706 (one for each indicator 102).

The data input means 700 which is controllable by the operator, provides data in the form of a modified ASCII digital code such as shown in the table of FIG. 9 to the signal logic 702 which then transforms it into appropriate signals for transmission over cables to the scoreboards. There the signals enable the desired indicators and actuate the appropriate lamps in the selected indicators to display any of the characters in FIGS. 5 and 5a. The address data is generated in the data input 700 in binary coded decimal form utilizing the ASCII code while the display data is in ordinary binary form using the ASCII code. The data is presented to the signal logic by the alpha-numeric keyboards 304, 302 previously mentioned, by punch tape typewriter and reader 708, and by storage devices 35 such as a magnetic tape memory 710 and buffer memory 711. Also, address and display data for certain words (e.g. BATTER or PLAY) can be automatically encoded into the modified ASCII code for serial transmission to the signal logic 702 by means of the address and word control circuit 716, address encoder 712 and word generator 714 in a manner to be described in more detail hereinafter.

The flow of data between the various input devices 302, 304, 306, 708, 710, 711 and 712, as well as the flow of data through the board data bus 715 to the signal logic, is con- 45 trolled by a memory control logic circuit 718. The memory control logic 718 performs the functions of the buttons in console group 600 (FIG. 6) as indicated by the corresponding reference numbers of the switches shown in the memory control logic box 718 in FIG. 7. The showing of these function 50 buttons as switches in FIG. 7 is symbolic only and the circuits for performing the various functions will be discussed in detail with respect to the detailed schematic drawings of FIGS. 10 through 21

The signal logic **702** provides the control function by which <sup>55</sup> the proper indicators on the scoreboard 100 are addressed and actuated to display the desired character in accordance with the address and character display data received from the data input 700. The seven bit ASCII code signals are received from the data input 700 by the character decoder interface 730 in the signal logic. The alpha-numeric decoder 732 then transforms the ASCII code signals into a single conductor signal on one of the 72 output conductors, each of which is representative of one of the display characters in FIGS. 5 and 65 5a or on a special instruction conductor such as the Special Address or Carriage Return.

As previously described, address data is always immediately preceded by a special address character which indicates to the signal logic that the immediately following two digits represent 70 the Y, or row address, while the third and fourth digits indicate the column, or X address. The alpha-numeric decode 732 recognizes the special address character and sends a signal over conductor 734 to start the operation of the address

dresses are then received and stored in their respective address storage circuits 738 and 740 respectively. After the four address digits have been stored, the address counter 736 sends a signal over conductor 742 to the lamp strobe circuit 750 which enables the read out of the character display data when

it is received in the lamp encoder circuit 754. The character display data is received by the character

decoder interface 730 and the alpha-numeric decoder 732 which furnishes a signal pulse on one of the 72 lines to the lamp encoder 754. If the lamp encoder 754 recognizes it as a legitimate character display signal which is able to be displayed by an indicator lamp matrix, a Legit signal is provided over line 756 to the lamp strober 750.

The receipt of the Address Stored signal and the Legit signal cause the lamp strober 750 to operate to read the address data from the Y and X address storage circuits 738, 740, in parallel fashion over their respective multiline conductors 758, 760 and cables 761, 763 to the Y and X address decoders 762, 764 at the scoreboards 100 and 200.

The parallel received signals at the Y and X address decoders 762 and 764 are transformed into a simultaneous single signal on one of the 15 output lines of the Y address decoder and one of the 28 output lines of the X address decoder. Each of the 15 lines of the Y address decoder is con-25 nected to a respective row of indicators Y01 through Y15 whereas each of the 28 output lines of the X address decoder 764 is connected to a respective column of indicators X01 through X28. Thus, each indicator 102 is connected to one line from the Y address decoder 762 and one line from the X 30 address decoder 764 and when the particular indicator receives simultaneous signals from both it is enabled to receive the immediately following character display data to actuate its lamps 400 in accordance with the character to be displayed.

Immediately after the Y and X address data has been read out of the storage devices 738, 740 the lamp strobe 750 signals the lamp encoder 754 to transmit signals in accordance with the character display data over its output data conductors 768 40 and strobe conductors 770 through the respective cables 772 774 to the particular preaddressed indicator circuit 706 at the scoreboard.

The lamp encoder data output and cable 774 are 7-line conductors each of which is connected to enable a respective row of lamps in the 5×7 lamp matrix indicators. The strobe output and cable 776 are 5-line conductors each of which is connected to enable a respective column of lamps in the 5×7 lamp matrix indicators. The five strobe conductors transmit five consecutive pulse signals, one on each line, which are delivered successively to the five lamp columns in sequential order from the left-hand column to the right-hand column of each lamp matrix indicator. The simultaneous receipt of lamp data signals over one or more of the seven data lines connected to the rows of indicator lamps in coincidence with the lamp column strobe signals causes the appropriate lamps in each column to be actuated in accordance with the particular character to be displayed.

Referring back to FIG. 4 for a more precise description of the lamp data and strobe signal operation of the indicator 60 lamps 400, it will be noted that each of the rows of lamps are marked respectively LR1 through LR7 whereas each of the columns are marked LC1 through LC5. Each of the lamps in rows LR1 through LR7 connected to be enabled by a signal on the corresponding one of the seven data lines from the lamp encoder 754 while the five columns of LAMPE LC1 through LC5 are connected to be actuated by lamps pulse on a respective one of the five strobe lines from the lamp encoder 754. Thus, to form the letter T as shown on the indicator 102 in

FIG. 4, the first pulse LC1 on the first of the five strobe lines from the lamp encoder will correspond with a simultaneous signal on the first data line which corresponds to the lamp row or LR1 row of indicator lamps. Thus, lamp 402 is lit with the first strobe pulse. The second strobe pulse on the second digit counter 736. The four address digits for the Y and X ad- 75 strobe line of the 5-line strobe output of lamp encoder 754 is

received simultaneously at the indicator 102 with another LR1 signal on the first lamp data line of the 7-line data output from the lamp encoder. Thus, lamp 404 is lit on the second or LC2 pulse. The LC3 strobe pulse on the third of the five strobe lines from the lamp encoder is received simultaneously with pulses on each one of the seven lamp data lines from the lamp encoder so that all seven of the lamps 406 through 406f are lit on the third or LC3 strobe pulse. Likewise, lamps 408 and 410 are lit on strobe pulses LC4 and LC5, respectively, to complete the letter T on the lamp indicator 102. Means are provided in the indicator circuit 706 for each indicator 102 for maintaining the actuated lamps lit until a reset signal is received by the indicator circuit 706 to turn out all energized lamps in a manner to be hereinafter described.

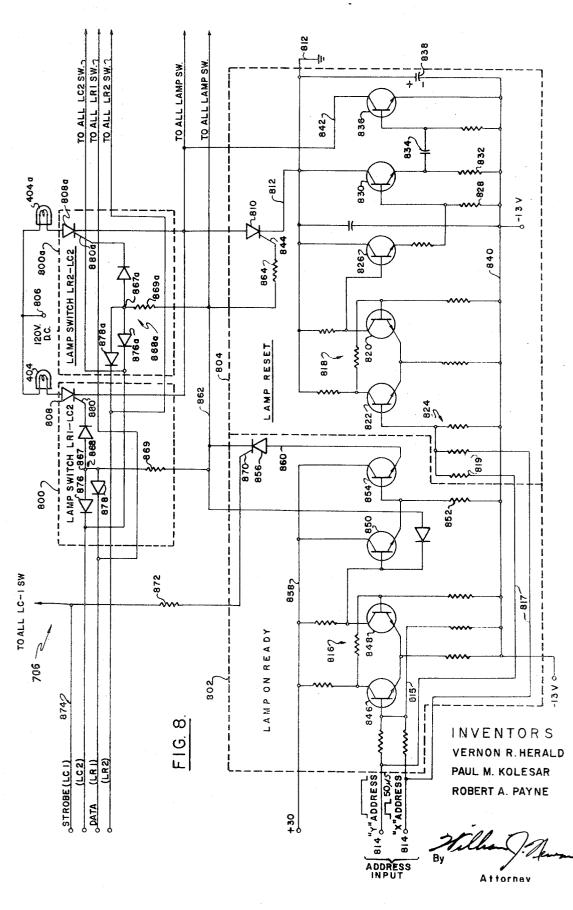

#### **INDICATOR CIRCUIT (FIG. 8)**

Reference is now made to FIG. 8 showing in schematic form an indicator circuit 706 which is used to control the lamps in each indicator 102 for the display of a desired character. The 20 indicator circuit 706 includes 35 lamp switch circuits such as 800 and 800a, one for each lamp in the  $5 \times 7$  matrix in the indicator. As will be seen switches 800 and 800a control lamps 404, 404a in matrix positions LR1-LC2 and LR2-LC2 respectively. There is also a lamp on-ready circuit 802 for preparing 25 the circuit responsive to the receipt of the indicator address data corresponding to the particular indicator, and a lamp reset circuit 804 for turning off any previously lit lamps in the indicator responsive to the receipt of the particular indicator 30 address data

The energizing circuit for each of the lamps in the indicator extends from a 120 volt DC source 806 through the respective lamps 404, 404a and lamp switch silicon controlled rectifiers 808, 808a in the respective lamp switch circuits 800, 800a. 35 The cathodes of all the lamp switch SCR's 808, 808a are connected together and to the anode of a reset SCR 810 in the lamp reset circuit 804, the cathode of which is connected to ground at 812. Thus, any lamp 400, 400a may be energized through the actuation of its respective lamp switch SCR 808, 40 808a and the reset SCR 810. All of the lamps may be extinguished or reset by the cutoff of reset SCR 810 in a manner to be hereinafter described.

The Y and X address data is received at terminals 814 in the form of simultaneously appearing positive going pulses. The X 45 address pulse is 50 microseconds long and the Y address pulse is substantially longer being governed by the speed of data input as will become apparent hereinafter.

The Y and X address pulses are ANDed at the input \$15 to a Schmidt monostable multivibrator circuit 816 in the lamp 50 on-ready circuit 802 and, by means of conductors 817 and resistors 819, at the input 824 to another Schmidt monostable multivibrator circuit 818 in the lamp reset circuit 804. The Schmidt circuit 818 in the lamp reset circuit 804 has a short 55 hysteresis curve so that its duty cycle is governed by the short X address data signal. Transistor 820 is normally conducting but transistor 822 goes into conduction upon receipt of the Y and X address signals at the input circuit 824 to the base of transistor 822. The conduction of transistor 822 causes 820 to 60 cut off, and the positive pulse at the collector thereof is fed to the base of emitter follower transistor 826. The positive pulse across emitter resistor 828 pulses emitter follower transistor 830 into conduction, and the positive pulse across its emitter resistor 832 is transmitted through capacitor 834 to the base 65 of transistor 836. The emitter-collector circuit of transistor 836 thus provides an effective shunt across reset SCR 810 from the grounded cathode \$12 of the reset SCR 810 through capacitor 838, negative 13-volt conductor 840, the emittercollector circuit of transistor 836, and conductor 842 to the 70 anode of SCR 810. Thus, conduction of transistor 836 places -13 volts from the charged capacitor 838 directly across the reset SCR 810 to cut it off and open the energizing circuits to any previously lit lamps 400, 400a. After the 50 microsecond

cutting off transistor 836 to remove the shunt from across the reset SCR 810. The reset SCR 810 will of course not conduct again until a positive signal is received on its gate 844.

The lamp on-ready circuit 802 operates responsive to the receipt of the Y and X address pulses to prepare the lamp switch circuits 800 and also to reactivate reset SCR 810 in the following manner. The two address signals are ANDed at the input 815 of the Schmidt multivibrator circuit 816 which in contrast to the Schmidt circuit 818 in the lamp reset circuit 10 804 has a long duty cycle of at least 450 microseconds. Thus, it will not follow the 50 microsecond X address pulse as does the lamp reset multivibrator 818. The normally off transistor 846 is triggered into conduction by the ANDed address pulses 15 causing transistor 848 to cut off. The positive going signal at the collector of transistor 848 triggers emitter follower transistor 850 into conduction and the positive pulse across its emitter resistor 852 appears at the base of transistor 854. Positive 30 volts is thus placed on the anode of a triggering SCR 856 from the +30 volt conductor 858 through the collector to emitter circuit of transistor 854 and conductor 860. The cathode of SCR 856 is connected through conductor 862 and resistor 864 to the gate 844 of reset SCR 810 so that when SCR 856 goes into conduction it triggers the reset SCR into conduction. The gate 870 of SCR 856 is connected through resistor 872 to the first indicator lamp strobe signal (LC1) line 874 so that it is triggered into conduction at the initiation of data character input signals to the indicator after the indicator has been addressed.

The triggering SCR 856 also functions to enable each of the 35 lamp switch circuits 800 in the indicator. It does so by placing a positive signal to the respective gate circuits 868, 868a in each of the lamp switch circuits 800, 800a through resistors 869, 869a when it goes into conduction. The positive signal from the triggering SCR 856 to the lamp SCR gate circuits does not throw these SCRs into conduction unless and until positive signals are simultaneously received on the cathodes of both diodes 876, 878, 876a, 878a in each lamp switch circuit 800.800a.

As will be seen in the later description of the lamp encoder circuit 754 the strobe signals and data signals provided therefrom to the scoreboard indicator circuits 706 are normally at negative potential and rise to positive potential to signify character display data. Thus if the character display data requires that lamp 404 be lit as in the letter T shown in FIG. 4, the diodes 876, 878 will receive simultaneous positive signals from the LR1 and LC2 inputs. Junction 867 goes high and the triggering SCR 856 supplies positive current to the gate 880 of the lamp switch SCR 806 causing it to conduct and complete the circuit for the lamp 404. The letter T does not call for lamp 404a to be lit so that while an LC2 signal will be received at diode 876a in the LR2-LC2 lamp switch circuit 800a, negative voltage remains at diode 878a and no current is delivered to the SCR gate 880a.

Once a lamp switch SCR 808 is triggered into conduction it remains conducting to keep the lamp lit until a subsequent receipt of address data indicates the selection again of that particular indicator which causes reset SCR \$10 to be cut off in the manner previously described and in turn the lamp switch SCR's including SCR 808.

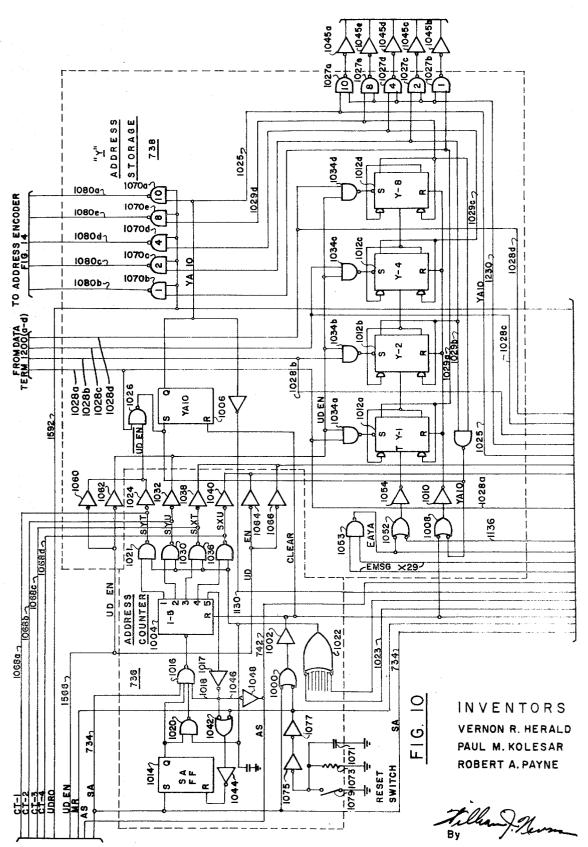

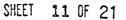

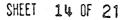

#### ADDRESS-CHARACTER SIGNAL LOGIC (FIGS. 10-22)

#### Address Data Storage

This section describes the basic address and character data handling circuits of the signal logic 702 between the data input 700 and the scoreboard 100. This discussion will be best understood with reference to FIGS. 10 through 21 arranged in the format indicated in FIG. 22.

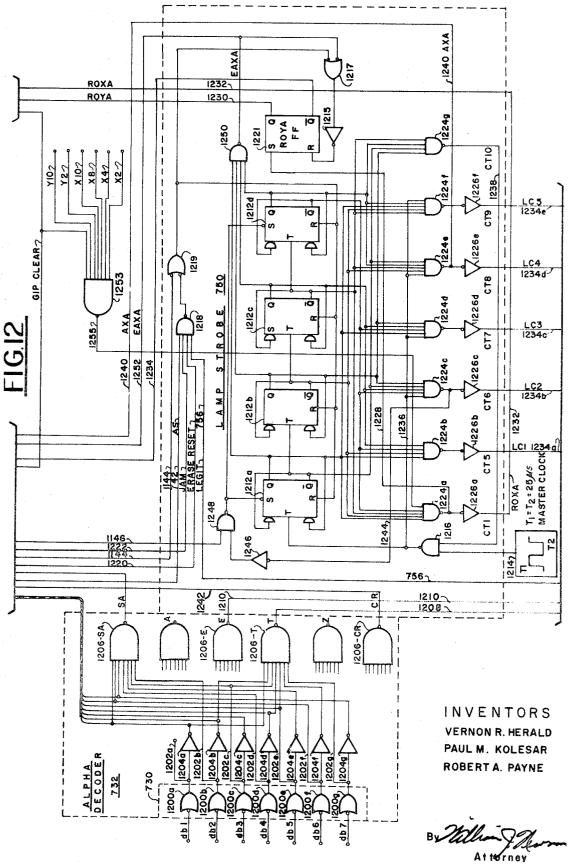

All of the address and character display data from the data input 700 is received at the data bus terminals db1 through db7(FIG. 12) at the character decoder interface 730 from the X address pulse the Schmidt circuit 818 restores to normal 75 data bus 715. The various code producing devices in the Data

Input 700 deliver signals to the terminals db1 through db7 such that a low or ground signal represents the presence of a data bit and a high represents its absence. The signal at the output of each of the NOR gates 1200a through g in the character decoder interface therefore represents the data bits 1 through 7 of the modified ASCII code shown in the chart of FIG. 9. The code is thus presented to the alpha-numeric decoder 732 in the form of high and low signals corresponding, respectively, to the 1's and 0's in the table of FIG. 9.

Conductors 1202*a* through *g* provide a straight pass through 10of the data bit 1 through 7 signals and negators 1204a through g provide the inverse of the data bit 1 through 7 signals, each of which is connected to appropriate NAND gates 1206 (FIG. 12) and 1100 (FIG. 11) in the alpha-numeric decoder 732 corresponding to a particular alpha, numeric, punctuation, or 15 special characters or a special instruction (Special Address or Carriage Return). The alpha decoder NAND gates 1206 shown in FIG. 12, and the numeric decoder NAND gates 1100, shown in FIG. 11, are all essentially the same (thus only representative gates are shown), and all of the gates are connected to the character decoder interface 730 so that each will present an output pulse when the ASCII code for its particular character is received. As an example, the alpha character T is represented by the modified ASCII code (FIG. 9) 0010101, and the corresponding high and low signals will be presented at the outputs of NOR gates 1200a through 1200g of the character decoder interface 730. It will be noted that the T NAND gate 1206-T receives the negated data bit 1 signal, the negated data bit 2 signal, the straight data bit 3 signal, the negated data bit 4 signal, straight through data bit 4 signal, the negated data bit 6 signal and the straight data bit signal. Thus, it will respond to the character T data, and not to any other data. The special address (SA) NAND gate 1206-SA, carriage return (CR) NAND gate 1206-CR, and the numeric decoder NAND gates 1100-0 through 9 (FIG. 11) operate in the same manner to provide single conductor outputs responsive to the respective 7-bit data character input.

As previously described every time it is desired to insert address data into the system to seek a desired indicator, the numerical data pertaining to the Y and X coordinates must be preceded by the special address character (SA). This may be performed by the operator punching the special address button on the numeric keyboard 302 at the console 300 which initiates the code 0101010 at the input to the alpha-numeric 45 decoder 732. Seven high inputs are presented to the SA NAND gate 1206-SA to produce a low on the special address conductor 734.

The SA signal readies the Y and X address storage circuits address data by presenting a low or ground pulse signal to NOR gate 1000 (FIG. 10) in the address counter circuit 736. The high at the output of NOR gate 1000 is inverted by negator 1002, and the resulting ground on the CLEAR conductors resets a five-count address digit counter 1004 and the Y tens 55 digit storage flip-flop 1006. The y tens storage device 1006 is a set-reset type flip-flop which performs a storage function by flipping to its Q state (high voltage at Q output) responsive to a ground pulse at its set S input and remains in that state until a ground pulse is applied to its reset R input.

The clear signal is NOR'd at gate 1008 and inverted at 1010, so that a ground reset signal is also applied to the reset terminals of the four Y units digit storage flip-flops 1012a through 1012d. These flip-flops are each of the conventional triggered type which is reset to its  $\overline{Q}$  state by a ground signal at 65 its reset R terminal and set to its Q state by a ground signal at the set S terminal. Also the circuit may be flipped between its Q and  $\overline{Q}$  states responsive to low signals at the trigger input T provided ground does not appear at the R or S inputs.

In addition the clear signal feeds to the X address storage 70 circuit 740 (FIG. 11) where it similarly resets the X tens and units flip-flops 1100a through 1100f through NOR gates 1102, 1104, 1106 and negators 1108, 1110 and 1112. Thus, pressing the SA button resets all of the X and Y storage flip-flops as well as the 5-count address digit counter 1004.

In addition, the SA ground signal also sets the set-reset type flip-flop 1014 in the address counter circuit 736, the set or Q output of which goes high responsive to the low SA signal at the set input. The high Q output of flip-flop 1014 is applied to NAND gate 1016 which also has three other inputs as follows: a normally high input on conductor 1018 at the output of negator 1017 which goes low at count 5 of the address digit counter 1004; a high output from NAND gate 1020 which gees low when a numeral button is pushed as will be

hercinafter described; and the SA signal on conductor 734 which is low until the special address button is released. To facilitate this explanation it will be assumed that the keyboard buttons actuate grounding switches directly connected to the data bus terminals db1-db7. The actual keyboard circuits will be described in detail later. Therefore, when the special address button is released all four inputs to the NAND gate 1016 go high and a ground output is applied to the counter 1004.

The address digit counter 1004 actually counts the number of digits in the address data inserted into the Y and X storages 20 and prepares the logic for receipt of character display data upon completion of the address data input. The counter 1004 is a conventional type made up of three set-reset type flipflops (not shown) and provides a high signal successively on the output lines 1 through 5 responsive to the first five succes-25 sive low pulses at its input following its reset. Thus, the first low at the address digit counter input caused by the cessation of the SA signal provides a high pulse to NAND gate 1021 connected to the count 1 output of the counter, and it remains there until the operator punches the first numerical key at 30 keyboard 302 representing the tens digit of the Y address to be stored.

As an example, assume that the desired address is Y09-X25. After punching the SA button the numeral button "0" is pressed to produce seven high inputs to the zero NAND gate 35 1100-0. The low output on the zero line 1023 from the gate 1100-0 is applied to one of the inputs of NOR gate 1022 which acts as a numerical input detector. It is connected to the outputs of each of the numeric NAND gates 1100-0 through 1100-9 to produce a high signal at its output responsive to the

40 input of any number. The high output from the numeral detector NOR gate 1022 is NANDed with the count 1 signal of the counter 1004 at gate 1021 to cause a set Y tens storage signal through negator 1024 to NAND gate 1026. The outer input to NAND gate 1026 is through conductor 1028a which is connected (not shown) to the output of NOR gate 1200ain the character decoder interface. The conductors 1028a through 1028d carry signals according to the first four bits of the ASCII code with the respective binary weights 1, 2, 4 and 8. 738 (FIG. 10) and 740 (FIG. 11) for storage of the Y and X 50 These conductors thus provide the address data input to the storage circuits 738 and 740 as will be further shown. Therefore, if the Y address is any one of the numbers 10 to 15 a coincidence will appear at the output of NAND gate 1026 and

provide a ground signal to the set terminal of the Y tens storage flip-flop 1006. The Y tens flip-flop would flip to its Q state placing a high voltage on the YA 10 line 1025 to the Y10 read out NAND gate 1027a signifying tens digits in the Y address. Since the Y address in out example was 09 no pulse appears on 1028a and the Y tens storage flip-flop 1006 is not set

60 When the operator released the zero keyboar button at the console the input to NAND gate 1020 from the numeral detector NOR gate 1022 goes low to provide a high to the counter input NAND gate 1016. Since the special address conductor is high, the set output of the special address flipflop 1014 is still high, and the count 5 conductor 1018 is high, the gate 1016 is satisfied and produces a ground signal to the counter 1004. The counter then advances to its count 2 state to send an enabling signal to NAND gate 1030 in readiment for storage of the Y units digit.

The operator next presses the keyboard button "9" and the alpha-numeric decoder 732 sends a low signal which is NOR'd in gate 1022 causing gate 1020 to inhibit the counter input gate 1016. The high output of gate 1022 is NANDed at gate 1030 with the count 2 output signal of counter 1004 and the 75 low therefrom is inverted by negator 1032. The high at the output of negator 1032 is applied to the Y units bits NAND gates 1034a through d which have their other inputs connected to separate ones of the b1 through b4 data bit lines 1028a through d. Since the units digit of the Y address is the numeral 9, highs will appear on the b1 and b4 bit lines 1028aand 1028d to NAND gates 1034a and 1034d and the ground pulses therefrom will set the Y unit flip-flop 1012a (having binary weight 1) and flip-flop 1012d (having binary weight 8). The Q outputs of Y units storage flip-flops 1012a through 1012d are connected via conductors 1029a through 1029d to the binary weighted readout NAND gates 1027b through 1027e, respectively. For the number 9 in the example address Y09-X25 NAND gates 1027b and 1027e will have high inputs at one of their inputs. A readout signal will later appear at the second input as will be hereinafter described. It is to be noted that the bit 5 through bit 7 data channels are not used for storing the address number because, as may be seen, in the code chart of FIG. 9 they are not required to distinguish the numerals 0 through 9.

When the operator releases the 9 keyboard button, the counter input gate 1016 delivers a low to the counter 1004 to step it to its count 3 condition enabling the set X tens digit NAND gate 1036. The operator presses the keyboard button for the number two representing the tens digit of the X address 25 25 causing numeral detector NOR gate 1022 to open the set X tens digit NAND gate 1036. The high from negator 1038 is presented to the NAND gates 1114a, 1114b at the set inputs to the X tens digits storage flip-flops 1100e, 1100f in the X pressed a high appears on the conductor 1028b (FIG. 10) to the NAND gate 1114b, thus setting the X20 storage flip-flop 1100f. A high signal is thus delivered to one input of the X20 read out NAND gate 1115a over conductor 1117. If the X address had been a number 10 through 19 the bit 1 conductor 1028a would have carried a high to satisfy the NAND gate 1114a and set the X10 flip-flop 1100e. Likewise, if the X address had been between 1 and 9 neither the X10 nor the X20 flip-flops would have been set.

Release of the keyboard numeral 2 button by the operator advances the counter 1004 to its step count 4 condition to prepare for storage of the X address units digit in the X units digit flip-flops 1100a through 1100d. Depression by the operator of the digit 5 for the units digit of the example X address 25 45 produces high outputs on the binary weight 1 line 1028a and the binary weight 4 line 1028c. These are each NANDed with the set X unit signal at NAND gates 1116a and 1116c to set the X1 and X4 flip-flops 1100a, 1100c and send high signals to the first inputs of X units read out NAND gates 1115c and 50 1115e via lines 1119 and 1121.

Release of the numeral 5 keyboard button steps the counter 1004 to its count 5 condition which closes the counter input gate 1016 by placing a ground on the conductor 1018. The address digit counter is thus inhibited from further pulsing until 55 it receives a subsequent reset signal. The count 5 output of the counter also causes the SA flip-flop 1014 to be reset by means of NOR gate 1042 and negator 1044.

The count 5 output of the counter 1004 also produces the 60 addressed stored signal (AS) at the output of negator 1048 which is fed by the negator 1017. The addressed stored (AS) signal is transmitted via conductor 742 to the lamp strober 750 (FIG. 12) indicating that the full address has been stored. The signal logic is thus set to receive the character display data for actuating the desired lamps in the addressed indicator.

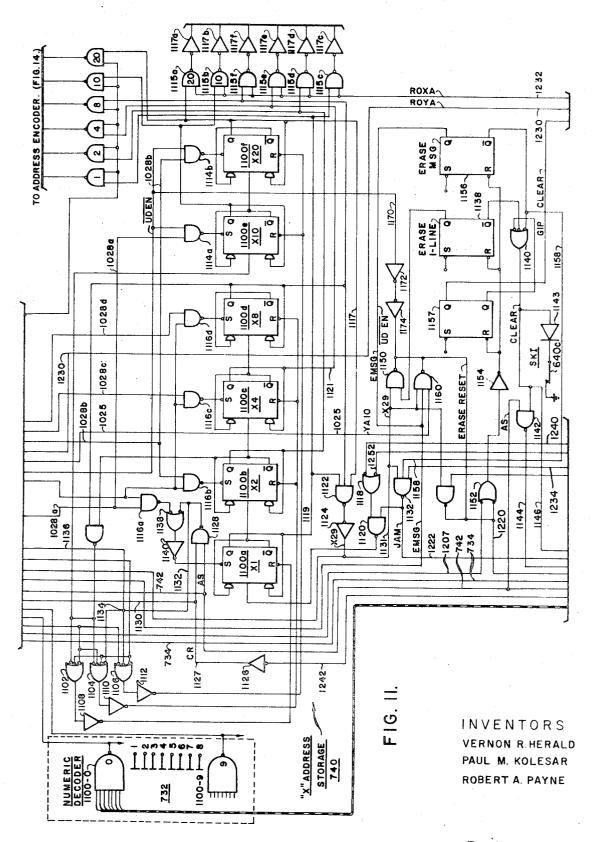

**Display Character Lamp Encoding**

To display the desired character after addressing the proper 70 indicator, the operator presses one of the alpha or numeric buttons on the respective keyboards 302, 304 which causes the proper signals to appear at the data bit 1 through data bit 7 terminals at the character decoder interface 730. The alpha-

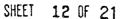

proper NAND gate in the series 1206 or 1100 in the manner previously described, and the single line output signal is presented to the lamp encoder 754 shown in detail in FIG. 13.

The lamp encoder 754 comprises a matrix of 35 NAND gates 1300a through g, 1301a through g, 1302a through g, 1303a through g, and 1304a through g. The matrix corresponds to the  $5 \times 7$  matrix of lamps 400 in the indicators 102 so that each NAND gate is associated with a particular lamp position in the indicator matrix. The NAND gates in the

column marked 1300 correspond to the lamps in column LC-1 of the indicator and similarly the column 1301 corresponds to the column LC-2 etc. Likewise, the NAND gates in the a row correspond to the lamps in lamp row LR-1 of the indicator matrix, those in row b correspond to lamp row LR-2, etc.

To describe the detailed operation of the lamp encoder 754 it will be assumed that the alpha character T is desired to be displayed on the previously addressed indicator Y09-X25. The code table of FIG. 9 shows that the code for the letter T is 20 0010101 and this code will open the gate 1206 T to produce a low signal on conductor 1208.

The signal on the "T" conductor 1208 is applied through appropriate NOR gates 1306 to NAND gate 1300a in the first column of gates, to NAND gate 1301a in the second column, to gates 1302a through g in the third column, to gate 1303a in the fourth column, and to gate 1304a in the fifth column which as may be seen by the shading of these NAND gates forms a letter T. The high signals at the first inputs to the storage circuit 740 (FIG. 11). Since the number 2 has been 30 selected NAND gates remain as long as the data signal from the data input lasts. During this time the address data is strobed out of the address data storages followed by the strobing of the display data from the encoder NAND gates, one column at a time in a manner described in the nest section of this specification.

> In a similar manner any other of the display characters may be encoded by the lamp encoder 754. For example, if the letter "E" is selected, the signal from the output of the E NAND gate 1206-E in the alpha numeric decoder 732 is delivered to the appropriate NAND gates 1300i a through g in the first column, gates 1301a, d and g in the second column, gates 1302a, d and g in the third column, gates 1303a, d and g in the fourth column and gates 1304a and g in the fifth column.

> The number of input NOR gates 1306 to the lamp encoder NAND gates may be materially reduced by combining inputs to various gates which are common to a number of different display characters. For example, each of the letters E, F, D, K, M, N, P, R and W as well as the all-lamps-lit character and a number of the other special characters shown in 5a call for all of the lamps in the first column LC-1 to be lit. Thus, the output lines from the decoder NAND gates for all of these characters are NOR'd at gate 1308 to produce a single line for signalling the first column of NAND gates 1300a through g for all of these display characters. Likewise, the characters 2, 3, 5, 6, 8, 9 and \$ as well as the alpha characters B and E all have common thereto the LR1, LR4 and LR7 lamps in columns LC2, LC3 and LC4. Nor gate 1310 provides for these common displays. Other lamp groups may also be so combined to limit the number of input NOR gates 1306 which may be calculated from an analysis of the display characters.

If display character data has been encoded by the circuit 754 in the manner set forth a signal is generated to start the 65 readout of the address and character display data to the scoreboard. If one of the display characters is encoded, a legit signal is sent to the lamp strober 750 which controls the read out of the address and display character data. The legit signal is derived from the inputs of certain NAND gates making up the matrix in the lamp encoder 754. NAND gate 1300b, which corresponds to the second lamp from the top in the first column of lamps (LC1-LR2), is actuated whenever any of the alpha-numeric characters is selected except I, J, T, Z, -, ', , !, 1, 3, 7 and various special characters shown in FIG. 5a. numeric decoder 732 produces a single line output from the 75 Thus, a high signal on conductor 1309 from the input to NAND gate 1300b will indicate a legitimate character display when any but the above listed characters are encoded by the lamp encoder NAND gate matrix. It may be seen that the characters I, J, T, Z, ', 1, !, 3 and 7 all have either the top lamp (LR1) or bottom lamp (LR7) in the third column (LC3) of 5 lamps lit and therefore conductors 1311 and 1313 connected respectively to the inputs of NAND gates 1302a and 1302g, will carry signals indicating the legitimate display of any of those characters. The inverted signals from the lines are joined with the inverted signal from conductor 1309 at junction 1320 and are NOR'd with signals generated by the selection of the remaining characters (1, -, space) not having a previously discussed legitimate signal, at NOR gate 1315.

The high-going legit signal at the output of NOR gate 1315 is applied to the lamp strober enabling gate 1218 via conductor 756.

#### Address and Display Character Readout

The lamp strober circuit **750** (FIG. 12) performs the func- 20 tion of a master timer for controlling the readout of the address data to the scoreboard as well as the readout and display of the character data. It comprises a 15 count counter made up of four conventional triggered flip-flops 1212*a* through *d* pulsed by a master oscillator 1214 which constantly produces 25 25 microsecond pulses at its output to NAND gate 1216. The other input to gate 1216 is connected to the normally high count 10 output of the counter so that the trigger input to the first flip-flop 1212*a* receives clock pulses from multivibrator 1214 only until count 10 is reached. 30

The lamp strober counter is inhibited from counting, however, until the storage of the address data and the encoding of the display character data because of the inhibit gate 1218. The normally high output of gate 1218 is inverted by NOR gate 1219 presenting ground reset and inhibit voltage to the reset terminals of the counter flip-flops. The ground voltage also serves to reset the readout Y address (ROYA) flip-flop 1221 through the double inversion of NOR gate 1217 and negator 1219.

The lamp strober inhibiting NAND gate 1218 is satisfied by the completion of storage of the address as indicated by the address stored AS signal on conductor 742, and the encoding of a legitimate display character in the lamp encoder as indicated by the legit signal on conductor 756. The erase reset 45 input from line 1220 to gate 1218 is normally positive and remains so except for an occurrence during the message board erase function as will be hereinafter described. The jam conductor input is also high as long as the last indicator X28 in a particular row has not been previously addressed as will be 50 discussed in detail later.

Thus, upon the receipt of the legit signal the gate 1218 releases the inhibit from the counter flip-flop reset terminals and the trigger input to the first flip-flop 1212*a* is pulsed by the multivibrator clock 1214 through the NAND gate 1216 to 55 start the timing function.

Count 1 of the lamp strober timer is utilized to initiate the readout of the Y and X address data from the respective storage circuits to the scoreboard. Count 1 is initiated by the first 25 microsecond multivibrator pulse after the inhibit is released and appears as a 50 microsecond long ground pulse at the output of the count 1 NAND gate 1224a and as a high pulse at the output of negator 1226a. The ground pulse from gate 1224a is applied over conductor 1228 to the set input of 65 the readout Y address (ROYA) flip-flop 1221 which puts a high at its Q output. The high signal from the Q output of the ROYA flip-flop is applied over the ROYA conductor 1230 to the Y address output NAND gates 1027a through e where it is NANDed with the binary code address signals from the Y 70 storage flip-flops 1012a through d, 1006 in accordance with the Y address of the desired indicator to read out the address data through amplifying negator circuits 1045a through e and over the cables to the scoreboards. The ROYA signal remains as long as the legit signal appears at the counter inhibit gate 75 1218 and when it terminates the ROYA flip-flop is reset through NOR gate 1219, NOR gate 1217 and negator 1215 as previously discussed.

The 50 microsecond high going count 1 signal at the output of negator 1226*a* is the readout X address (ROYA) signal and provides a high over conductor 1232 to the X address readout NAND gates 1115a through *f* where it is NANDed with the X address storage data from the X address storage flip-flops 1100a through 1100e and read out through amplifying negator circuits 1117a through *f* and over the cable to the scoreboards.

Counter outputs 2 through 4 of the lamp strober counter are unused. At count 5 the strobe LC1 pulse for reading out the first column of display character data is derived at NAND gate 1224b which therefore appears as a 50 microsecond high pulse on line 1234a at the output of negator 1226b. At count 6 the strobe LC2 pulse for column 2 information is derived on line 1234b. Likewise the LC3, LC4 and LC5 pulses are derived, respectively, from the count 7, count 8 and count 9 outputs on the lines 1234c to 1234e. However, whereas, the LC1 signal pulse is a 50 microsecond pulse, the LC2 through LC5 pulses are 25 microsecond pulses because of the connection via conductor 1236 from the output of the timer clock 25 output NAND gate 1216 to the fifth input of the NAND gates 1224c-1224f.

The LC1 through LC5 pulses are directed to respective columns of lamp encoder NAND gates 1300 through 1304, as well as to the LC1 through LC5 output terminals 1314a

30 through e to the cable leading to the scoreboard. Thus, each of the LC1 through 5 strobe pulses is NANDed with the appropriate display character data encoded signals appearing at the NAND gates in the lamp encoder matrix to provide LR1 through LR7 signals on the 7-lamp row output conductors

35 1316a through g and lamp row data terminals 1318a through e to the cable leading to the scoreboard. Thus, the strobe signals comprising the single pulses in sequential time relationship

from LC1 through LC5 appear at terminals 1314*a* through *e*, and simultaneous with each LC pulse the data pulses corresponding to the required lamps to be lit for forming the desired display character sequentially appear at the lamp row 1 through 7 terminals 1318*a* through 1318*g*.

The address and character display data having all been read out to the scoreboard, the lamp strober counter advances to count 10 which develops a ground pulse over conductor 1238 to the clock timer output gate 1216. Further clock pulses are inhibited from being transmitted to the lamp strober counter flip-flops and the counter stops. Reset of the counter occurs when the legit signal to inhibit gate 1218 disappears to place ground at the reset terminals of the flip-flops 1212a-d and 1221.

The lamp strober 750 also causes the X address storage 740 to advance its stored number to the next succeeding X20, X8 number thus causing the automatic addressing of the next succeeding scoreboard indicator 102 without the operator having to insert the address data. It will be seen that at count 8 of the lamp strobe counter, a ground signal appears on the advance X address (AXA) conductor 1240 from the output of count 8

60 NAND gate 1224e. The signal is inverted at NOR gate 1118 to present a high input to NAND gate 1120. The jam signal at the other input to NAND gate 1120 is also high except when X29 designating the end of a row is addressed, so the output of the gate 1120 goes low to provide a trigger pulse to the X1 flip-65 flop 1100a in the X address storage circuit 740. The trigger pulse advances the count registered therein by one digit in a

well-known manner to raise the address one number. The Y address storage circuit 738 maintains the Y address date previously stored so that data is now stored in the address storage circuits indicative of the next succeeding indicator in the desired row.

When the last indicator in a row has been addressed and the character display data pertaining thereto has been transmitted, it is desirable to stop the automatic advancing of the X address until the next row indicators is addressed. A jam signal is therefore generated which prevents further data input until a carriage return signal is received by the logic which automatically causes the storage circuit 738 and 740 to register the address of the first indicator in the next row.

The X address designating the end of the row (No. 29, or 5 one more than the number of indicators) is detected by NAND gate 1122 which is fed by the Q outputs of the X20,X8 and X1 flip-flops of the X address storage. When all three are high indicating the X address number 29 the gate 1122 opens 10 to provide a high signal on the X29 conductor 1131 through negator 1124 to the jam NAND gate 1132. Conductor 1158 at the second input of NAND gate 1132 from the erase function circuits to be hereinafter discussed, is normally high, as is conductor 1234 to the third input from the  $\overline{Q}$  output of the ROYA 15 flip-flop 1221. This  $\overline{ROYA}$  signal prevents jamming until after read out to the scoreboard of the data pertaining to the 28th indicator in the row.

As previously discussed the output of the jamming NAND 20 gate 1132 forms an input to the lamp strober inhibit gate 1218 over conductor 1222. When the jam signal goes low indicating the end of the row, the gate 1218 is closed placing a low signal on the reset terminals of the lamp strober counter flip-flops preventing any further strobe cycling until the signal on the 25 jam line 1222 again goes high.

The low jam signal from the jam NAND gate 1132 is also sent to NAND gate 1120 closing that gate to prevent any further advancing of the X address in the X address storage.

The signal logic stays in the jammed condition until a carriage return (CR) signal is received. The ASCII code for the carriage return arriving at the character decoder interface 730 is detected by the carriage return alpha decoder NAND gate 1206CR sending a low signal on conductor 1242 and inverted 35 to a high by negator 1126 connected to the input of a NAND gate 1128 in the X address storage.

The other input to the gate 1128 is the address stored (AS) signal on conductor 742 derived from the count 5 output of the 5-count counter 1004 in the address counter circuit 736. It 40will be recalled that the counter 1004 remains in the count 5 condition until reset. The ASCR signal from the output of gate 1128 triggers the Y address storage to advance to the next number via conductor 1132, junction 1134, conductor 1136, 45 NOR gate 1052 and negator 1054 to the trigger input of the Y1 flip-flop 1012a of Y address storage circuit. The ASCR signal appearing at junction 1134 also resets the X address storage to the number 1 to indicate the first indicator in the next row by causing low signals to the reset terminals of the bi- 50 nary weighted 2, 4 and 8 flip-flops 1100b, c and d, as well as X10, X20 flip-flops 1100e and f, through the NOR gates 1104, 1106 and negators 1110, 1112, respectively. The binary weighted 1 flip-flop 1100a is set to its 1 condition by the ASCR signal through NOR gate 1138 and negator 1140 whose output is connected to the set terminal of the flip-flop 1100a.

The shift of the X address storage from the X29 address to the X1 address causes the X29 detector NAND gate 1122 to close, removing the high from the first input of the jam NAND 60 gate 1132, and hence restoring the high on the jam signal line 1222 to the lamp strober inhibit gate 1218.

It is also desirable to jam the further readin of data after the last row Y10 of the message board has been actuated to prevent message information from interfering with the ballgame information in the upper portion 104 of the scoreboard (rows 11 through 15). If the Y address stored in the Y address storage circuit is 10 or higher, ground appears on the YA 10 conductor 1130 due to the set condition of the YA 10 storage flip-flop 1006 in the Y address storage circuit 738. Thus, the carriage return CR signal does not reach the ASCR gate 1128 if the Y address is ten or greater preventing the advance of the Y address, and the jam signal continues until the logic is subsequently reset. 75

### 18

#### Master Reset

It is desirable that the X and Y address storage, the counter and the SA flip-flops be reset to zero when the equipment power is first turned on. This is effected by capacitor 1071 and resistor 1073 connected to the input of negator 1075. The negator 1075, being the type that ordinarily has a momentary high input when power is on, has a ground signal at its input when the power is initially turned on due to the action of capacitor 1071. Thus, a momentary ground appears at the output of negator 1077 (needed for loading purposes) and feeds through NOR gate 1000 and negator 1002 to reset the address counter 1004 and the Y and X address storage flipflops in the same manner as the SA signal, as previously described. The output of negator 1077 is also directed to NOR gate 1042 which through negator 1044 provides a ground reset pulse to the SA flip-flop 1014.

A switch 1079 between the input of negator 1075 and ground is also provided for resetting the address storage address counter and SA flip-flops without having to previously turn off the power or generate an SA character signal. The reset switch thus enables reset of the address storage circuits when necessary for service procedures.

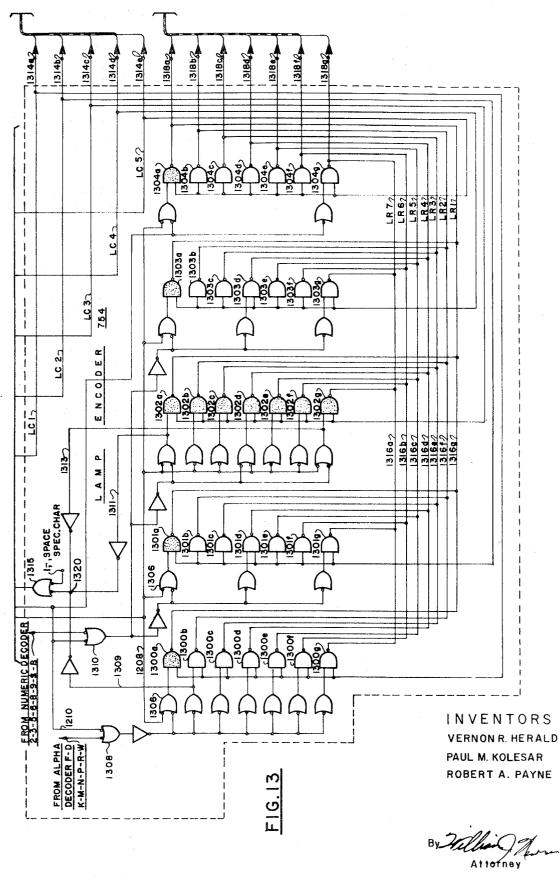

#### SCOREBOARD ADDRESS DECODING AND CHARACTER DATE DISTRIBUTION