등록특허 10-2665148

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년05월09일

(11) 등록번호 10-2665148

(24) 등록일자 2024년05월07일

- (51) 국제특허분류 (Int. Cl.)

*H01C 1/148* (2006.01) *H01C 1/032* (2006.01)

*H01C 17/065* (2006.01) *H01C 17/28* (2006.01)

*H01C 7/06* (2006.01) *H01C 7/18* (2006.01)

- (52) CPC특허분류

*H01C 1/148* (2013.01)

*H01C 1/032* (2013.01)

- (21) 출원번호 10-2018-7014893

- (22) 출원일자(국제) 2016년10월26일

심사청구일자 2021년10월25일

- (85) 번역문제출일자 2018년05월25일

- (65) 공개번호 10-2018-0075607

- (43) 공개일자 2018년07월04일

- (86) 국제출원번호 PCT/US2016/058809

- (87) 국제공개번호 WO 2017/075016

국제공개일자 2017년05월04일

- (30) 우선권주장

14/928,893 2015년10월30일 미국(US)

- (56) 선행기술조사문현

CN102024538 A\*

US20090322467 A1\*

- \*는 심사관에 의하여 인용된 문현

(73) 특허권자

비쉐이 테일 일렉트로닉스, 엘엘씨

미국 네브래스카 컬럼버스 23 스트리트 1122 (우:68602)

(72) 발명자

스미스 클락

미국 네브래스카주 68601 컬럼버스 37번 애버뉴 2980

와이어트 토드

미국 네브래스카주 68601 컬럼버스 30번 스트리트 4535

(74) 대리인

김태홍, 김진희

전체 청구항 수 : 총 21 항

심사관 : 방인환

## (54) 발명의 명칭 표면 실장 저항기 및 그 제조 방법

**(57) 요약**

저항기와 저항기 제조 방법이 본 명세서에 기술되어 있다. 저항기는 저항성 소자 및 복수의 전도성 소자들을 포함한다. 복수의 전도성 소자들은 유전체 물질을 통해 서로 전기적으로 절연될 수 있고, 복수의 전도성 소자들 각각과 저항성 소자의 표면 사이에 배치된 접착 물질을 통해 저항성 소자에 열적으로 결합될 수 있다. 복수의 전도성 소자들은 전도성 층과 납땜 가능 층을 통해 저항성 소자에 결합될 수 있다.

대 표 도 - 도1a

(52) CPC특허분류

*H01C 17/065* (2013.01)

*H01C 17/281* (2013.01)

*H01C 7/06* (2013.01)

*H01C 7/18* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

저항기에 있어서,

제 1 측 및 대향하는 제 2 측, 상부 표면 및 대향하는 하부 표면을 포함하는 저항성 소자(resistive element)로서, 상기 저항성 소자의 높이는 상기 상부 표면과 상기 하부 표면 사이에 있는 것인, 상기 저항성 소자;

간극에 의해 분리되고 상기 간극에 적어도 부분적으로 위치된 유전체 물질에 의해 서로 전기적으로 절연된 제 1 전도성 소자 및 제 2 전도성 소자로서, 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자는 접착제를 통해 상기 저항성 소자의 상부 표면에 열적으로 결합되고,

상기 제 1 전도성 소자는 상기 간극에 인접한 내측 부분 및 상기 저항성 소자의 상기 제 1 측에 인접한 외측 부분을 포함하고, 상기 외측 부분은 계단형이거나, 각지거나 또는 라운드형인 상부 외측 코너 부분을 갖고, 상기 제 1 전도성 소자는 상기 저항성 소자의 높이와 동일한 방향을 따라 두께 변화(varied thickness)를 갖고, 상기 내측 부분은 상기 외측 부분의 일부의 제 2 두께보다 큰 제 1 두께를 갖고,

상기 제 2 전도성 소자는 상기 간극에 인접한 내측 부분 및 상기 저항성 소자의 상기 제 2 측에 인접한 외측 부분을 포함하고, 상기 제 2 전도성 소자의 상기 외측 부분은 계단형이거나, 각지거나 또는 라운드형인 상부 외측 코너 부분을 갖고, 상기 제 2 전도성 소자는 상기 저항성 소자의 상기 높이와 동일한 방향을 따라 두께 변화를 갖고, 상기 제 2 전도성 소자의 상기 내측 부분은 상기 제 2 전도성 소자의 상기 외측 부분의 일부의 제 2 두께보다 큰 제 1 두께를 갖고;

상기 제 1 전도성 소자의 제 1 외측 에지 및 상기 저항성 소자의 상기 제 1 측의 제 1 외측 에지는 제 1 측면을 형성하고, 상기 제 2 전도성 소자의 제 2 외측 에지 및 상기 저항성 소자의 상기 제 2 측의 제 2 외측 에지는 제 2 측면을 형성하는 것인, 상기 제 1 전도성 소자 및 제 2 전도성 소자;

상기 제 1 측면을 커버하고 상기 저항성 소자의 하부 표면의 적어도 일부 아래로 연장되도록 배치된 제 1 도금 층(plated layer); 및

상기 제 2 측면을 커버하고 상기 저항성 소자의 상기 하부 표면의 적어도 일부 아래로 연장되도록 배치된 제 2 도금 층

을 포함하는, 저항기.

#### 청구항 2

제 1 항에 있어서, 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자는 열 확산기(heat spreader)들을 포함하는 것인, 저항기.

#### 청구항 3

제 1 항에 있어서, 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자는 상기 저항성 소자에 대한 지지체(support)를 제공하는 것인, 저항기.

#### 청구항 4

제 1 항에 있어서, 상기 접착제는 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자와 상기 저항성 소자 사이에만 배치되는 것인, 저항기.

#### 청구항 5

제 1 항에 있어서, 상기 제 1 전도성 소자의 상기 외측 부분 중 더 낮은 표면은 상기 저항성 소자를 향해 연장되고, 상기 제 2 전도성 소자의 상기 외측 부분 중 더 낮은 표면은 상기 저항성 소자를 향해 연장되는 것인, 저항기.

**청구항 6**

제 1 항에 있어서, 상기 제 1 도금 층의 적어도 일부는 상기 제 1 전도성 소자의 외측 부분에 인접한 상기 제 1 전도성 소자의 형상을 따르고, 상기 제 2 도금 층의 적어도 일부는 상기 제 2 전도성 소자의 외측 부분에 인접한 상기 제 2 전도성 소자의 형상을 따르는 것인, 저항기.

**청구항 7**

제 1 항에 있어서, 상기 유전체 물질이 상기 접착제의 상부 표면의 적어도 일부를 커버하고, 제 2 유전체 물질이 상기 저항성 소자의 상기 하부 표면의 적어도 일부를 커버하는 것인, 저항기.

**청구항 8**

제 1 항에 있어서, 상기 저항성 소자는 구리, 또는 니켈, 또는 알루미늄, 또는 망간, 또는 구리, 니켈, 알루미늄, 망간 중 하나 이상의 조합 또는 구리, 니켈, 알루미늄, 망간 중 하나 이상의 합금을 포함하는 것인, 저항기.

**청구항 9**

제 1 항에 있어서, 상기 저항성 소자의 상기 제 1 층에 인접한 상기 저항성 소자의 상기 하부 표면을 따라 배치된 제 1 전도성 층, 및 상기 저항성 소자의 상기 제 2 층에 인접한 상기 저항성 소자의 상기 하부 표면을 따라 배치된 제 2 전도성 층

을 더 포함하는, 저항기.

**청구항 10**

제 1 항에 있어서, 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자는 구리 또는 알루미늄을 포함하는 것인, 저항기.

**청구항 11**

저항기를 제조하는 방법에 있어서 - 상기 저항기는 상기 저항기의 상부와 하부 사이에서 연장되는 높이를 가짐 - ,

접착제를 사용하여 저항성 소자의 상부 표면에 열 확산기를 포함하는 전도체를 라미네이팅하는 단계;

상기 전도체를 제 1 전도성 소자 및 제 2 전도성 소자로 분할하기 위해 상기 전도체를 마스킹 및 패터닝하는 단계로서, 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자는 간극에 의해 분리되고, 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자 각각은 상기 저항기의 높이를 따라 두께 변화를 포함하고 - 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자 각각은 상기 간극에 인접하여 상기 저항기의 상기 높이의 적어도 일부를 따라 연장되는 증가된 두께를 가짐 - , 상기 제 1 전도성 소자 및 제 2 전도성 소자 각각은, 상부 부분 및, 계단형이거나, 각지거나 또는 라운드형인 외측 코너 부분을 갖는 상부 외측 코너 부분을 포함하는 것인, 상기 마스킹 및 패터닝하는 단계;

상기 저항성 소자를 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자에 열적으로 결합시키기 위해 각자의 제 1 도금 층 및 제 2 도금 층으로 상기 제 1 전도성 소자, 상기 제 2 전도성 소자 및 상기 저항성 소자의 외측 면들을 도금하는 단계로서, 상기 제 1 도금 층 및 상기 제 2 도금 층은 상기 저항성 소자의 하부 표면 아래로 연장된 부분을 각각 갖는 것인, 상기 도금하는 단계; 및

상기 제 1 전도성 소자 및 상기 제 2 전도성 소자를 서로 전기적으로 격리하기 위해 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자의 적어도 일부를 상에 그리고 상기 간극 내에 적어도 부분적으로 유전체 물질을 퇴적하는 단계

를 포함하는, 저항기를 제조하는 방법.

**청구항 12**

저항기에 있어서,

부착된 회로 기판으로부터 떨어져 배치되도록 구성된 상부 표면, 상기 상부 표면에 대향하는 하부 표면, 제 1 측면 및 대향하는 제 2 측면을 포함하는 저항성 소자 - 상기 저항성 소자의 높이는 상기 상부 표면 및 상기 하부 표면 사이에 있음 -;

접착제를 통해, 상기 제 1 측면에 인접한 상기 저항성 소자의 상기 상부 표면에 열적으로 결합된 열 확산기를 포함하는 제 1 전도성 소자로서, 상기 제 1 전도성 소자는 계단형이거나, 각지거나 또는 라운드형인 상부 외측 코너 부분을 포함하는 것인, 상기 제 1 전도성 소자;

접착제를 통해, 상기 제 2 측면에 인접한 상기 저항성 소자의 상기 상부 표면에 열적으로 결합된 열 확산기를 포함하는 제 2 전도성 소자로서, 상기 제 2 전도성 소자는 계단형이거나, 각지거나 또는 라운드형인 상부 외측 코너 부분을 포함하며, 상기 제 1 전도성 소자와 상기 제 2 전도성 소자 사이에 간극(gap)이 제공되며, 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자 각각은 상기 간극에 인접하여 상기 저항성 소자의 높이와 동일한 방향을 따라 증가된 두께를 가지는 것인, 상기 제 2 전도성 소자;

상기 저항성 소자의 상기 제 1 측면 및 상기 제 1 전도성 소자의 외측 측부 예지를 커버하는 제 1 도금 층으로서, 상기 제 1 도금 층은 상기 저항성 소자의 상기 하부 표면의 일부 아래로 연장된 부분을 포함하는 것인, 상기 제 1 도금 층;

상기 저항성 소자의 상기 제 2 측면 및 상기 제 2 전도성 소자의 외측 측부 예지를 커버하는 제 2 도금 층으로서, 상기 제 2 도금 층은 상기 저항성 소자의 상기 하부 표면의 일부 아래로 연장된 부분을 포함하는 것인, 상기 제 2 도금 층;

상기 제 1 전도성 소자 및 상기 제 2 전도성 소자의 상부 표면들을 커버하고 상기 제 1 전도성 소자와 상기 제 2 전도성 소자 사이의 상기 간극을 충전하는 제 1 유전체 물질; 및

상기 저항성 소자의 하부 표면의 적어도 일부를 커버하는 제 2 유전체 물질

을 포함하는, 저항기.

### 청구항 13

제 12 항에 있어서, 상기 접착제는 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자와 상기 저항성 소자 사이에만 배치되는 것인, 저항기.

### 청구항 14

제 12 항에 있어서, 상기 제 1 전도성 소자는 상기 제 1 전도성 소자의 외측 부분에 인접하여 상기 저항성 소자의 높이와 동일한 방향을 따라 감소된 두께를 가지고, 상기 제 2 전도성 소자는 상기 제 2 전도성 소자의 외측 부분에 인접하여 상기 저항성 소자의 높이와 동일한 방향을 따라 감소된 두께를 가지는 것인, 저항기.

### 청구항 15

제 14 항에 있어서, 상기 제 1 도금 층의 적어도 일부는 상기 제 1 전도성 소자의 형상을 따르고, 상기 제 2 도금 층의 적어도 일부는 상기 제 2 전도성 소자의 형상을 따르는 것인, 저항기.

### 청구항 16

제 13 항에 있어서, 상기 제 1 유전체 물질은 상기 접착제의 상부 표면의 적어도 일부를 커버하고, 제 2 유전체 물질은 상기 저항기의 하부 표면의 적어도 일부를 포함하는 것인, 저항기.

### 청구항 17

제 12 항에 있어서, 상기 제 1 전도성 소자의 하부 표면의 일부는 상기 저항성 소자를 향해 연장되고, 상기 제 2 전도성 소자의 하부 표면의 일부는 상기 저항성 소자를 향해 연장되는 것인, 저항기.

### 청구항 18

제 12 항에 있어서, 상기 저항성 소자의 제 1 측면에 인접한 상기 저항성 소자의 하부 표면을 따라 배치된 제 1 전도성 층, 및 상기 저항성 소자의 제 2 측면에 인접한 상기 저항성 소자의 하부 표면을 따라 배치된 제 2 전도성 층

을 더 포함하는, 저항기.

### 청구항 19

저항기를 제조하는 방법에 있어서,

접착제를 사용하여, 회로 기판으로부터 떨어져 배치되도록 구성된 저항성 소자의 상부 표면에 열 확산기를 포함하는 전도체를 라미네이팅하는 단계;

상기 전도체를 제 1 전도성 소자 및 제 2 전도성 소자로 분할하기 위해 상기 전도체를 마스킹 및 패터닝하는 단계로서, 상기 제 1 전도성 소자 및 상기 제 2 전도성 소자는 간극에 의해 분리되어 있는 것인, 상기 마스킹 및 패터닝 단계;

상기 제 1 전도성 소자를 상기 간극에 인접하는 두꺼운 내측 부분 및 상기 저항성 소자의 제 1 측에 인접하여 위치된 얇은 외측 부분을 포함하도록 형성하는 단계;

상기 제 2 전도성 소자를 상기 간극에 인접하는 두꺼운 내측 부분 및 상기 저항기의 제 2 측에 인접하여 위치된 얇은 외측 부분을 포함하도록 형성하는 단계로서, 상기 저항기의 상기 제 1 측 및 상기 저항기의 상기 제 2 측은 상기 저항성 소자의 대향하는 측들 상에 있는 것인, 상기 형성하는 단계;

상기 저항성 소자의 상기 제 1 측을 따라 제 1 도금 층으로 상기 저항성 소자를 도금하는 단계로서, 상기 제 1 도금 층 각각의 적어도 일부는 상기 저항성 소자의 상기 제 1 측에 인접한 상기 저항성 소자의 하부 표면의 적어도 일부 아래로 연장되는 것인, 상기 제 1 도금 층으로 상기 저항성 소자를 도금하는 단계;

상기 저항성 소자의 상기 제 2 측을 따라 제 2 도금 층으로 상기 저항성 소자를 도금하는 단계로서, 상기 제 2 도금 층 각각의 적어도 일부는 상기 저항성 소자의 상기 제 2 측에 인접한 상기 저항성 소자의 상기 하부 표면의 적어도 일부 아래로 연장되는 것인, 상기 제 2 도금 층으로 상기 저항성 소자를 도금하는 단계; 및

상기 제 1 전도성 소자 및 상기 제 2 전도성 소자를 서로 전기적으로 격리하기 위해 유전체 물질을 퇴적하는 단계

를 포함하는, 저항기를 제조하는 방법.

### 청구항 20

제 9 항에 있어서, 상기 제 1 도금 층은 상기 제 1 전도성 층의 하부 표면의 적어도 일부 아래로 연장되고, 상기 제 2 도금 층은 상기 제 2 전도성 층의 하부 표면의 적어도 일부 아래로 연장되는 것인, 저항기.

### 청구항 21

제 18 항에 있어서, 상기 제 1 도금 층은 상기 제 1 전도성 층의 하부 표면의 적어도 일부 아래로 연장되고, 상기 제 2 도금 층은 상기 제 2 전도성 층의 하부 표면의 적어도 일부 아래로 연장되는 것인, 저항기.

## 발명의 설명

### 기술 분야

[0001] 본 출원은 2015년 10월 30일자에 출원된 미국 특허 출원 제14/928,893호의 우선권을 주장하며, 이것의 전체 내용은 본 명세서에 완전히 설명된 것처럼 참조로써 본원에 포함된다.

[0002] 본 출원은 전자 부품 분야에 관한 것으로, 더 구체적으로는 저항기 및 저항기의 제조에 관한 것이다.

### 배경 기술

[0003] 저항기는 전기 에너지를 소산되는 열로 변환하여 전기 저항을 제공하는 회로에 사용되는 수동 부품이다. 저항기는 전류 제한, 전압 분배, 전류 레벨 감지, 신호 레벨 조정 및 능동 소자 바이어스를 포함하여 많은 목적을 위해 전기 회로에 사용될 수 있다. 자동차 제어 장치와 같은 용도에는 고 전력 저항기가 요구될 수 있으며, 이러한 저항기는 많은 와트의 전력을 소산시키도록 요구될 수 있다. 또한, 이들 저항기가 비교적 높은 저항 값을 갖도록 요구되는 경우, 이러한 저항기는 매우 얇은 저항성 소자를 지지하고 또한 오랜 시간 동안 최대 전력 부하에서 자신의 저항 값을 유지할 수 있도록 만들어져야 한다.

공지된 전기 저항기에는 저항성 소자 및 저항성 소자의 대향하는 단부로부터 연장되는 종단(termination)이 제공된다. 종단은 저항성 요소 아래로 접혀 있으며, 저항성 요소와 종단 사이에 열 전도성이며 전기 절연성이 필수로 제공된다. 종단은 저항기를 전자 회로 어셈블리에 장착하는 기능을 수행한다.

### 발명의 내용

[0004] 저항기와 저항기 제조 방법이 본 명세서에 기술되어 있다.

[0005] 본 발명의 실시예에 따르면, 저항기는 저항성 소자 및 복수의 분리된 전도성 소자들을 포함한다. 복수의 전도성 소자들은 유전체 물질을 통해 서로 전기적으로 절연될 수 있고, 복수의 전도성 소자들 각각과 저항성 소자의 표면 사이에 배치된 접착 물질을 통해 저항성 소자에 열적으로 결합될 수 있다. 복수의 전도성 소자들은 또한 전도성 층과 납땜 가능 층을 통해 저항성 소자에 전기적으로 결합될 수 있다.

[0006] 본 발명의 다른 양태에 따르면, 상부 표면, 하부 표면, 제 1 측면 및 대향하는 제 2 측면을 갖는 저항성 소자를 포함하는 저항기가 제공된다. 제 1 전도성 소자 및 제 2 전도성 소자가 접착제에 의해 저항성 소자의 상부 표면에 접합된다. 제 1 전도성 소자와 제 2 전도성 소자 사이에 간극(gap)이 제공된다. 제 1 전도성 소자와 제 2 전도성 소자의 위치 결정(positioning)은 저항성 소자의 제 1 측면 및 제 2 측면에 인접한 저항성 소자의 상부 표면의 노출된 부분을 남긴다. 제 1 전도성 층이 제 1 측면에 인접한 저항성 소자의 상부 표면의 노출된 부분을 커버하고, 접착제 및 제 1 전도성 소자와 접촉한다. 제 2 전도성 층이 제 2 측면에 인접한 저항성 소자의 상부 표면의 노출된 부분을 커버하고, 접착제 및 제 2 전도성 소자와 접촉한다. 제 3 전도성 층이 저항성 소자의 제 1 측면에 인접하게 저항성 소자의 하단 부분을 따라 배치된다. 제 4 전도성 층이 저항성 소자의 제 2 측면에 인접하게 저항성 소자의 하단 부분을 따라 배치된다. 유전체 물질이 제 1 전도성 소자 및 제 2 전도성 소자의 상부 표면을 커버하고, 제 1 전도성 소자와 제 2 전도성 소자 사이의 간극을 충전한다. 유전체 물질은 저항기의 외부 표면 상에 퇴적되고, 저항기의 상부 및 하부 양자 모두 상에 퇴적될 수 있다.

[0007] 저항기 제조 방법이 또한 제공된다. 상기 방법은, 접착제를 사용하여 저항성 소자에 전도체를 라미네이팅하는 단계; 전도체를 복수의 전도성 소자들로 분할하기 위해 전도체를 마스킹 및 패터닝하는 단계; 저항성 소자로부터 접착 물질의 일부를 선택적으로 제거하는 단계; 저항성 소자를 복수의 전도성 소자들에 전기적으로 결합시키기 위해 저항성 소자를 하나 이상의 전도성 층들로 도금하는 단계; 및 복수의 전도성 소자들을 서로 전기적으로 절연시키기 위해 적어도 복수의 전도성 소자들 상에 유전체 물질을 퇴적하는 단계를 포함한다.

[0008] 본 발명의 다른 양태에 따르면, 저항기가 제공되고, 상기 저항기는 저항성 소자, 및 접착 물질을 통해 저항성 소자에 열적으로 결합되며, 유전체 물질에 의해 서로 전기적으로 절연되는 제 1 전도성 소자 및 제 2 전도성 소자를 포함한다. 제 1 전도성 층이 저항성 소자의 제 1 측면 및 제 1 전도성 소자의 측면과 직접 접촉하도록 배치된다. 제 2 전도성 층이 저항성 소자의 제 2 측면 및 제 2 전도성 소자의 측면과 직접 접촉하도록 배치된다. 제 1 납땜 가능 층 및 제 2 납땜 가능 층이 저항기의 측면을 형성한다.

### 도면의 간단한 설명

[0009] 보다 자세한 이해는 첨부된 도면들과 함께 예시로서 주어진 다음의 설명으로부터 얻어질 수 있다.

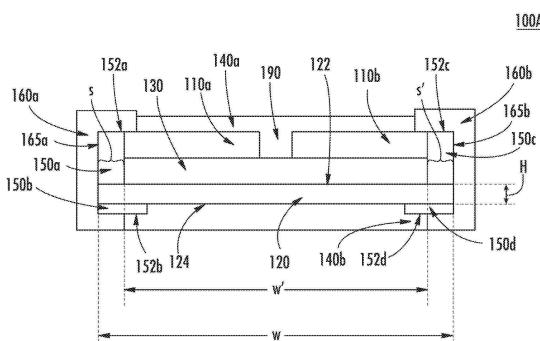

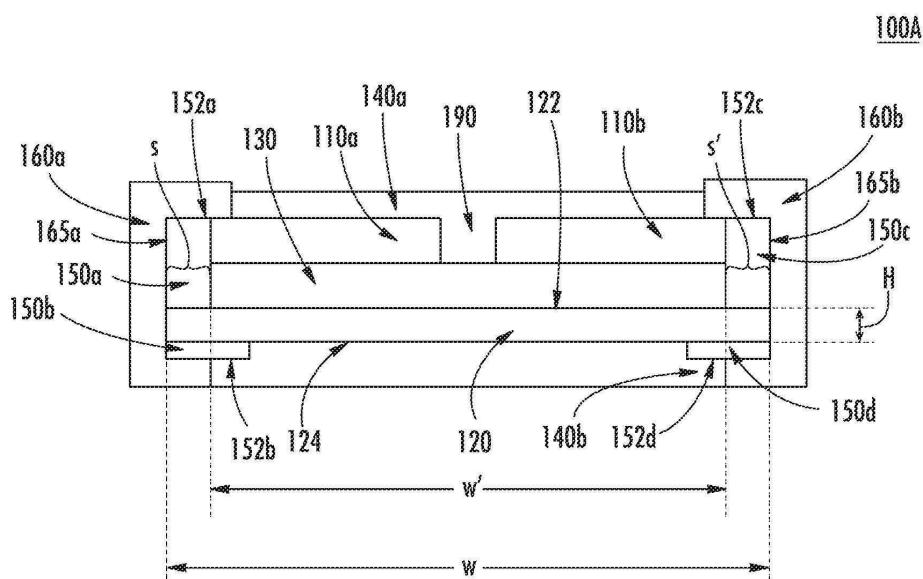

도 1a는 본 발명에 따른 저항기의 실시예의 단면도를 도시한다.

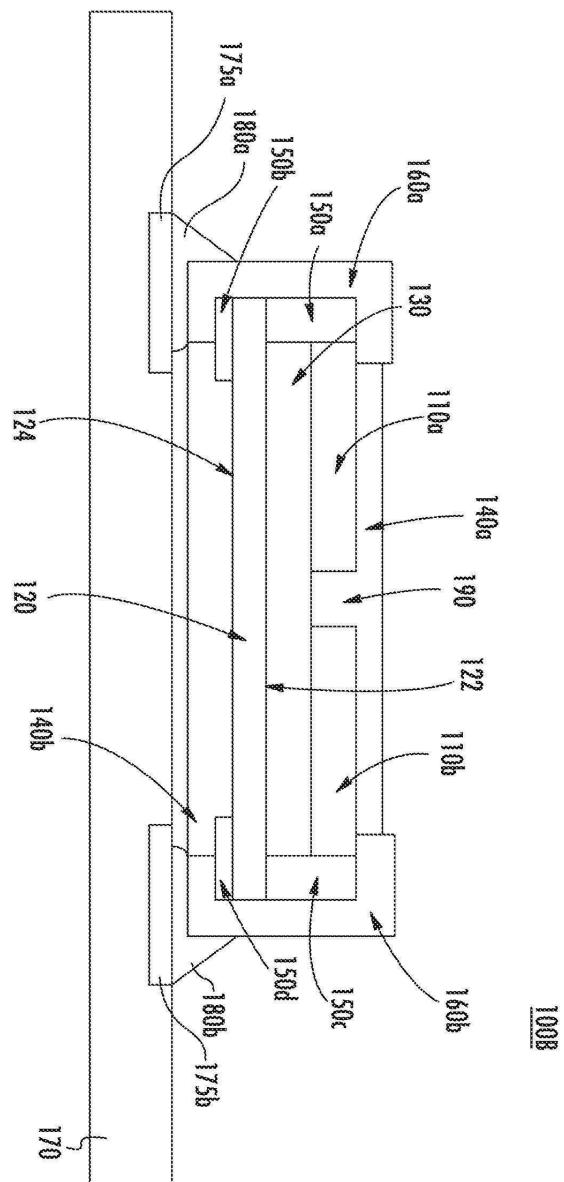

도 1b는 회로 기판에 장착된 도 1a의 저항기를 도시한다.

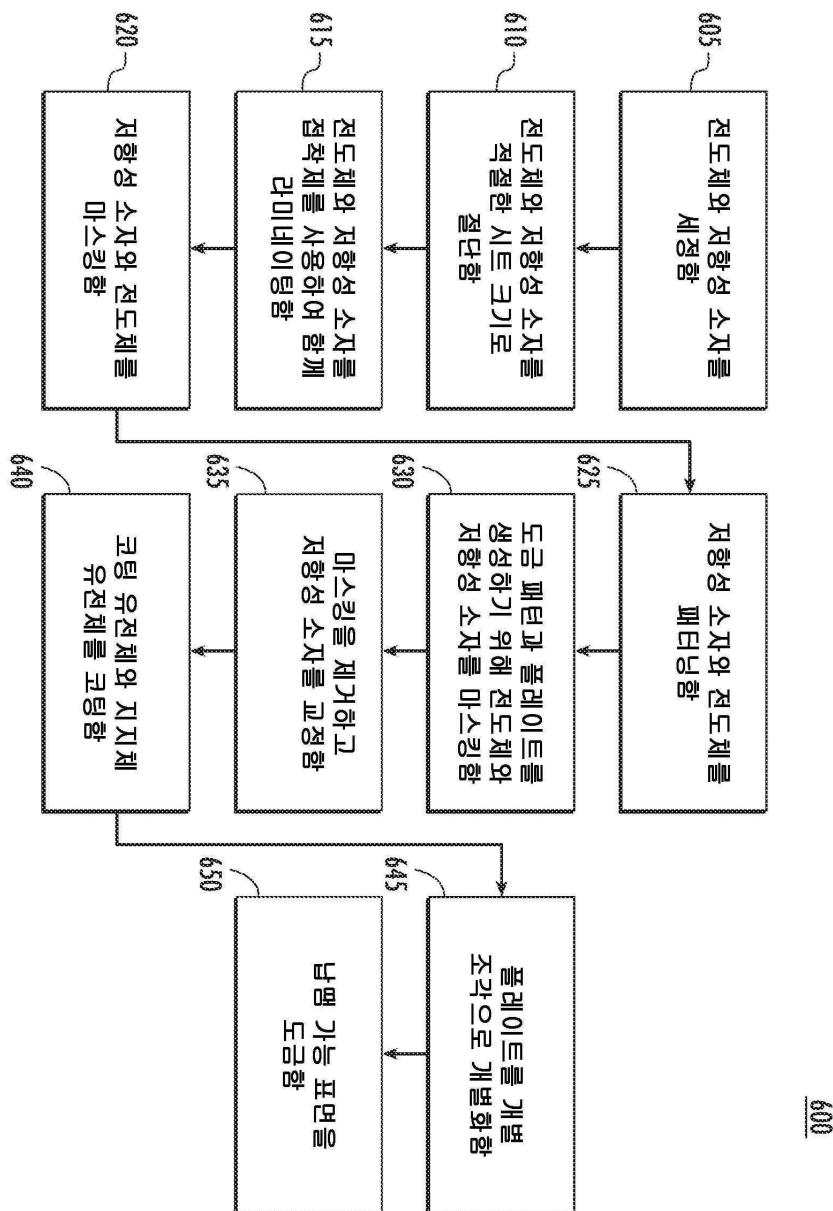

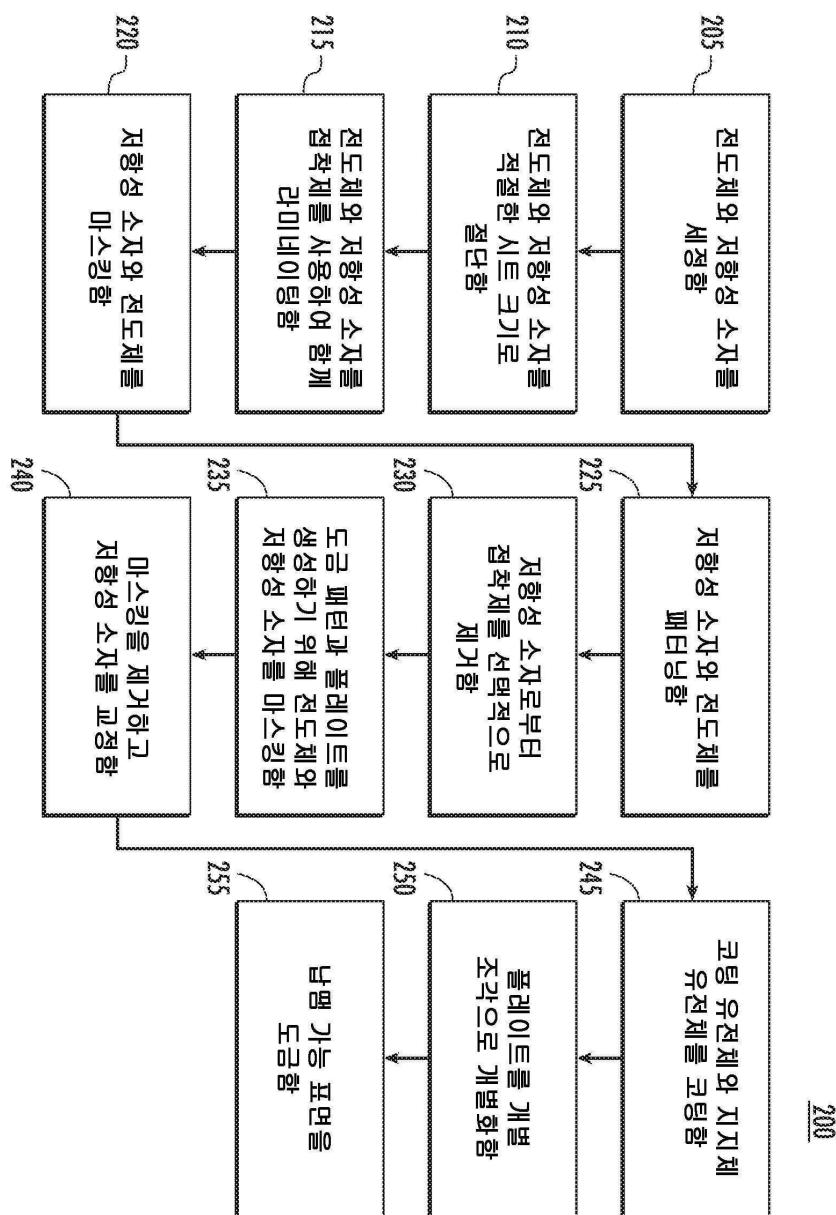

도 2는 도 1a의 저항기를 제조하는 예시적인 방법의 흐름도를 도시한다.

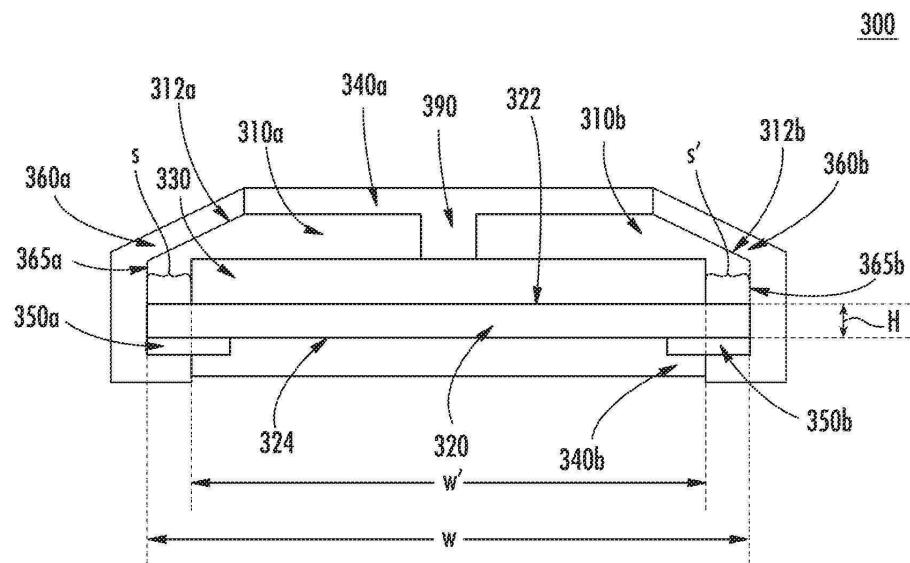

도 3은 본 발명에 따른 저항기의 실시예의 단면도를 도시한다.

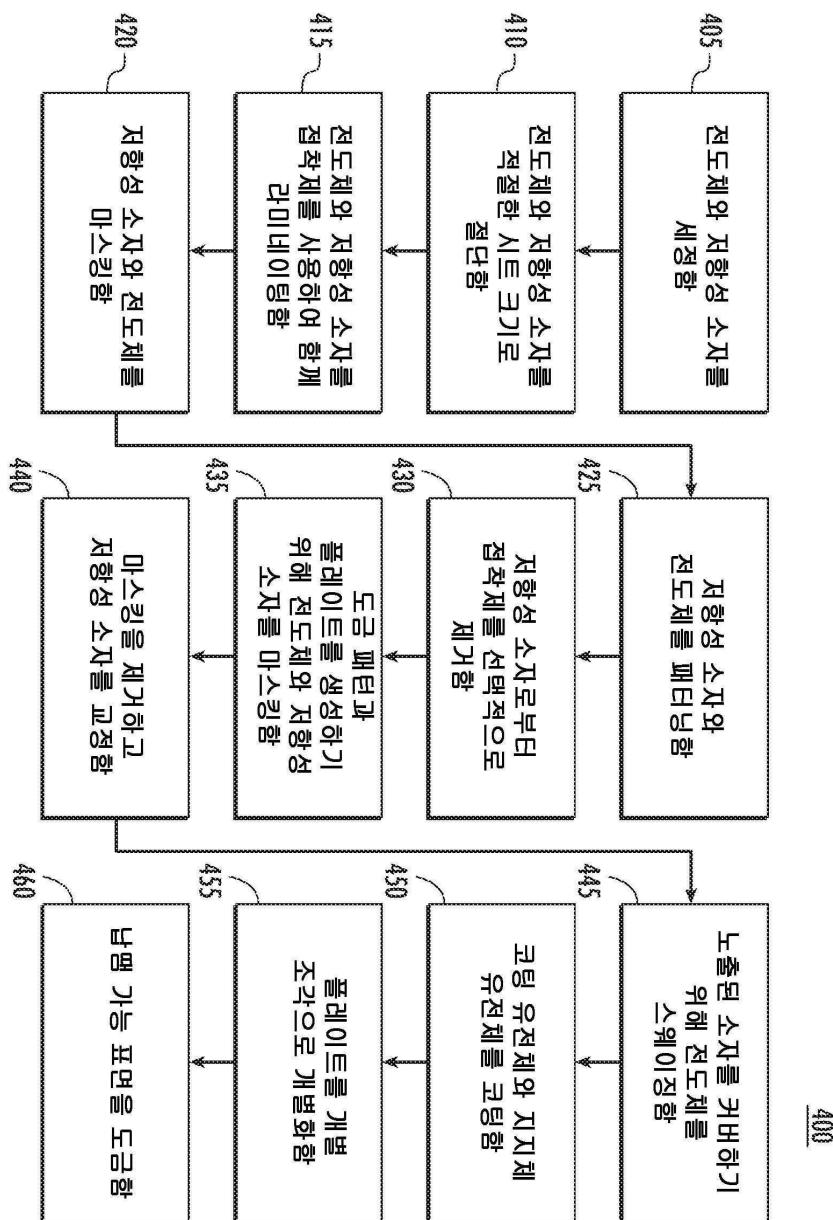

도 4는 도 3의 저항기를 제조하는 예시적인 방법의 흐름도이다.

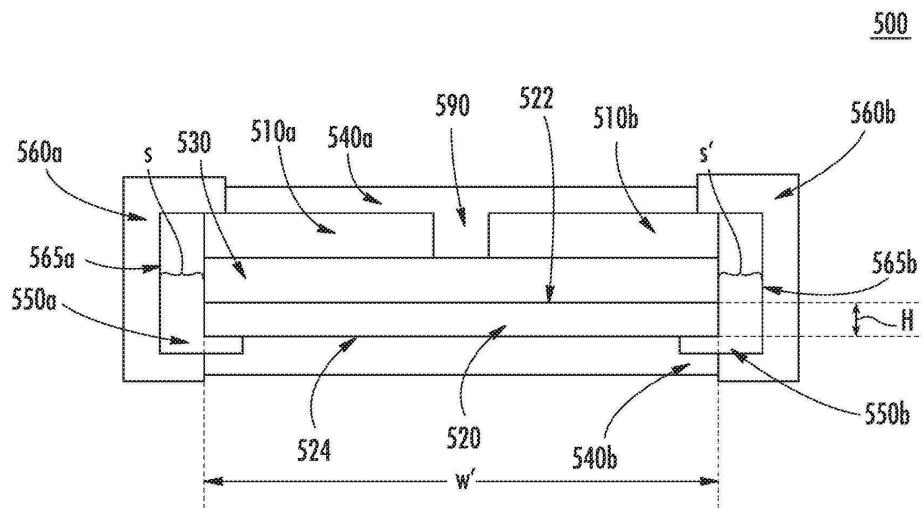

도 5는 본 발명에 따른 저항기의 실시예의 단면도를 도시한다.

도 6은 도 5의 저항기를 제조하는 예시적인 방법의 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0010] 특정 용어가 단지 편의를 위해 다음의 설명에서 사용되며 제한하는 것은 아니다. 단어 "오른쪽", "왼쪽", "상부", "하부"는 참조가 이루어지는 도면에서의 방향을 지정한다. 청구 범위 및 명세서의 해당 부분에서 사용

되는 "하나"라는 단어는 특별히 언급되지 않는 한, 참조된 항목의 하나 이상을 포함하는 것으로 정의된다. 이 용어에는 위에서 특별히 언급된 단어, 그 파생어 및 유사한 취지의 단어가 포함된다. 문구 "적어도 하나" 뒤에 "A, B 또는 C"와 같은 두 개 이상의 항목의 목록은, A, B 또는 C 중 임의의 개별적인 것 및 이들의 임의의 조합을 의미한다.

[0011] 도 1a는 본 발명의 실시예에 따른 예시적인 저항기(100)(도 1a에서 100A 및 도 1b에서 100B로 표시됨)의 다이어 그램이다. 도 1에 도시된 저항기(100A)는 저항기를 가로지르고 제 1 납땜 가능 층(160a)과 제 2 납땜 가능 층(160b)(이는 이하 상세하게 설명됨) 사이에 배치된 저항성 소자(120)를 포함한다. 예시를 목적으로 도 1a에 도시된 방향에서, 저항성 소자는 상부 표면(122) 및 하부 표면(124)을 갖는다. 저항성 소자(120)는 포일 저항기(foil resistor)인 것이 바람직하다. 저항성 소자는, 비제한적인 예를 들어, 구리, 합금(구리, 니켈, 알루미늄 또는 망간) 또는 이들의 조합으로 형성될 수 있다. 저항성 소자는 구리-니켈-망간(CuNiMn)의 합금, 니켈-크롬-알루미늄(NiCrAl)의 합금 또는 니켈-크롬(NiCr)의 합금 또는 포일 저항기로 사용하기에 적합한 것으로 당업자에게 공지된 다른 합금으로 형성될 수 있다. 저항성 소자(120)는 도 1a에서 "w"로 지정된 폭을 갖는다. 또한, 저항성 소자(120)는 도 1a에서 높이 "H"로 지정된 높이 또는 두께를 갖는다.

[0012] 도 1a에 도시된 바와 같이, 제 1 전도성 소자(110a) 및 제 2 전도성 소자(110b)는 저항성 소자(120)의 대향 측 단부에 인접하게 배치되며, 제 1 전도성 소자(110a)와 제 2 전도성 소자(110b) 사이에 간극(190)이 제공되는 것이 바람직하다. 전도성 소자들(110a 및 110b)은 예를 들어, C110 또는 C102 구리와 같은 구리를 포함하는 것이 바람직할 수 있다. 그러나 예를 들어, 알루미늄과 같은 양호한 열 전달 특성을 갖는 다른 금속이 전도성 소자에 사용될 수 있고, 당업자는 전도성 소자로서 사용하기 위한 다른 허용 가능한 금속을 인식할 것이다. 바람직하게는, 제 1 전도성 소자(110a) 및 제 2 전도성 소자(110b)는 저항성 소자(120)의 외부 측면 에지(또는 외부 측면)까지 완전히 연장되지 않고, 저항성 소자(120)의 에지에 인접한 공간(s 및 s')을 남긴다. 저항성 소자(120)의 상부 표면(122)의 노출된 부분은 저항성 소자(120)의 측면 에지에 인접한 공간(s 및 s') 각각을 향한다.

[0013] 전도성 소자들(110a 및 110b)은 접착 물질(130)을 통해 저항성 소자(120)에 라미네이팅(laminated)되거나, 다른 식으로 본딩(bonded), 접합(joined) 또는 부착(attached)될 수 있으며, 상기 접착 물질(130)은 비제한적인 예로서 DUPONT™ PYRALUX™ 또는 시트 혹은 액체 형태의 다른 아크릴(acrylic), 에폭시(epoxy), 폴리이미드(polyimide) 접착제 같은 물질을 포함할 수 있다. 도 1a에 도시된 바와 같이, 접착 물질(130)은 제 1 전도성 소자(110a)의 측면 에지로부터 제 2 전도성 소자(110b)의 대향 측면 에지까지, 저항성 소자의 중앙 부분만을 따라 연장되는 것이 바람직하다. 제 1 전도성 소자(110a), 제 2 전도성 소자(110b) 및 접착 물질(130)은 'w'로 표시된 저항성 소자(120)의 상부 표면(122)에 인접한 폭을 따라 연장된다.

[0014] 제 1 전도성 층(150a) 및 제 2 전도성 층(150c)이 저항성 소자(120)의 상부 표면(122)에 인접하고 전도성 소자들(110a 및 110b)의 외부 측면 에지(또는 외부 측면)를 따라, 공간(s 및 s')에 제공되어 이들에 전기적 연결을 제공한다. 바람직하게, 제 1 전도성 층(150a) 및 제 2 전도성 층(150c)은 전도성 소자들(110a 및 110b)의 외부 측면 에지(또는 외부 측면)를 따라 그리고 저항성 소자의 상부 표면(122) 상에 도금된다. 바람직한 실시예에서, 구리가 전도성 층에 사용될 수 있다. 그러나 당업자라면 인식할 수 있는 바와 같이, 임의의 도금 가능하고 전도성이 높은 금속이 사용될 수 있다.

[0015] 도 1a에 도시된 바와 같이, 추가적인 제 3 전도성 층(150b) 및 제 4 전도성 층(150d)이 저항성 소자(120)의 하부 표면(124)의 적어도 일부를 따라 그리고 대향 측면 단부에 인접하게 배치된다. 전도성 층들(150b 및 150d)은 저항성 소자(120)의 대향 외부 측면 에지(또는 외부 측면), 및 제 1 전도성 층(150a)과 제 2 전도성 층(150c)의 대향 외부 측면 에지(또는 외부 측면)와 정렬되는 것이 바람직한 대향 외부 에지를 갖는다. 바람직하게는, 제 3 전도성 층(150b) 및 제 4 전도성 층(150d)은 저항성 소자(120)의 하부 표면(124)에 도금된다.

[0016] 저항성 소자(120)의 정렬된 외부 측면 에지(또는 외부 측면) 및 전도성 층들(150a, 150b, 150c, 150d)의 외부 측면 에지(또는 외부 측면)는 납땜 가능 층들을 수용하도록 구성된 납땜 가능 표면을 형성한다. 납땜 가능 층들(160a 및 160b)은 저항기(100A)가 회로 기판에 납땜될 수 있게 하기 위해 저항기(100A)의 측 방향 단부(165a 및 165b)에 개별적으로 부착될 수 있으며, 이는 도 1b와 관련하여 보다 상세히 설명된다. 도 1a에 도시된 바와 같이, 납땜 가능 층들(160a 및 160b)은 전도성 층들(150b 및 150d)의 하부 표면(152b 및 152d)을 따라 적어도 부분적으로 연장되는 부분들을 포함하는 것이 바람직하다. 도 1a에 도시된 바와 같이, 납땜 가능 층들(160a 및 160b)은 전도성 층들(150a 및 150c)의 상부 표면(152a 및 152c)을 따라 연장되고 또한 전도성 소자들(110a 및 110b)의 상부 표면을 따라 적어도 부분적으로 연장되는 부분들을 포함하는 것이 바람직하다.

[0017] 유전체 물질(140)이 예를 들어, 코팅에 의해 저항기(100)의 하나의 표면 또는 표면들 상에 퇴적될 수 있다. 유

전체 물질(140)은 공간 또는 간극을 충전하여 구성 요소들을 서로 전기적으로 절연시킬 수 있다. 도 1a에 도시된 바와 같이, 제 1 유전체 물질(140a)이 저항기의 상단 부분에 퇴적된다. 제 1 유전체 물질(140a)은 납땜 가능 층들(160a 및 160b)의 부분들 사이에서 연장되고, 전도성 소자들(110a 및 110b)의 노출된 상부 표면을 커버하는 것이 바람직하다. 제 1 유전체 물질(140a)은 또한 전도성 소자들(110a 및 110b) 사이의 간극(190)을 충전하여, 간극(190)을 향하는 접착 물질(130)의 노출된 부분을 커버한다. 제 2 유전체 물질(140b)이 저항성 소자(120)의 하부 표면을 따라 납땜 가능 층들(160a 및 160b)의 부분들 사이에 퇴적되고, 전도성 층들(150b 및 150d)의 노출된 부분 및 저항성 소자(120)의 하부 표면(124)을 커버한다.

[0018] 도 1b는 회로 기판(170) 상에 장착된 예시적인 저항기(110B)의 다이어그램이다. 저항기(100B)는 저항기(100A)와 동일하고, 동일한 부분들은 도 1b에서 동일한 번호가 지정되어 있다. 도 1b에 도시된 예에서, 저항기(100B)는 납땜 가능 층들(160a 및 160b)과 회로 기판(170) 상의 대응하는 솔더 패드들(175a 및 175b) 사이에 솔더 연결부(180a 및 180b)를 사용하여 회로 기판(170)에 장착된다.

[0019] 전도성 소자들(110a 및 110b)은 접착 물질(130)을 통해 저항성 소자(120)에 결합되고, 전도성 층(150a 및 150c)을 통해 측면 또는 외부 측면 단부 또는 표면에서 저항성 소자에 연결된다. 전도성 소자들(110a 및 110b)은 저항성 소자(120)에 열적으로 및/또는 기계적으로 및/또는 전기적으로 결합/연결되거나 다른 식으로 본딩, 접합 또는 부착될 수 있음을 인식한다. 전도성 소자들(110a 및 110b)은 전도성 층들(150a 및 150c)에 열적으로 및/또는 기계적으로 및/또는 전기적으로 결합/연결되거나 다른 식으로 본딩, 접합 또는 부착될 수 있음을 또한 인식한다. 특히, 전도성 층(150a 및 150c)은 저항기(100B)가 회로 기판에 장착될 때 회로 기판(170)으로부터 가장 멀리 있는 저항성 소자의 표면(122)으로부터 저항성 소자(120)와 전도성 소자들(110a 및 110b) 사이에 전기적 연결을 만든다는 것을 유념한다. 저항성 소자(120)와 전도성 소자들(110a 및 110b) 각각의 측 방향 단부 사이의 열적, 전기적 및/또는 기계적 결합/연결은, 전도성 소자들(110a 및 110b)이 저항성 소자(120)에 대한 지지체로서 그리고 열 확산기(heat spreader)로서 사용될 수 있게 한다. 저항성 소자(120)에 대한 지지체로서 전도성 소자들(110a 및 110b)의 사용은, 저항성 소자(120)가 자립 저항성 소자(self-supporting resistive elements)에 비해 더 얇게 만들어질 수 있게 하고, 이는 저항기(100B)가 약 0.015"와 약 0.001" 사이의 포일 두께를 사용하여  $1m\Omega$  내지  $20m\Omega$ 의 저항 값을 갖도록 할 수 있다. 저항성 소자(120)에 대한 지지체를 제공할 뿐만 아니라, 열 확산기로서 전도성 소자들(110a 및 110b)의 효율적인 사용은 열 확산기를 사용하지 않는 저항기에 비해 저항기(100B)가 보다 높은 전력을 소산하게 할 수 있다. 예를 들어, 2512 크기의 금속 스트립 저항기의 일반적인 정격 전력은 1W이다. 본 명세서에 설명된 실시예들을 사용하면, 2512 크기의 금속 스트립 저항기에 대한 정격 전력은 3W일 수 있다.

[0020] 또한, 회로 기판(170)으로부터 가장 멀리 있는 저항성 소자의 표면 상에 저항성 소자(120)와 전도성 소자들(110a 및 110b) 사이의 전기적 연결을 만드는 것은, 저항기(100)와 회로 기판(170) 사이의 솔더 접합부(solder joint)에 대한 저항성 소자 대 전도성 소자 연결부의 노출을 피할 수 있으며, 이는 열 팽창 계수(thermal coefficient of expansion; TCE)로 인해 저항기의 고장 위험을 감소시키거나 제거할 수 있다. 또한, PCB에 가장 근접한 저항성 소자의 측면 상에 전도성 층(예컨대, 150b 및 150d)의 사용은, 강한 솔더 접합부를 생성하고 솔더 리플로우(solder reflow) 동안 PCB 패드 상에 저항기를 센터링하는 것을 도울 수 있다.

[0021] 다른 저항기 설계 및 그 제조 방법의 예시가 저항기(100A, 100B)와 동일한 일반적인 설계 목표를 달성할 수 있는 상이한 설계를 설명하기 위해 도 2, 도 3, 도 4, 도 5 및 도 6과 관련하여 이하에서 설명된다. 그러나 당업자는 본 발명개시의 범위 내에서 다른 저항기 설계 및 그 제조 방법이 만들어질 수 있다는 것을 이해할 것이다.

[0022] 도 2는 도 1의 저항기를 제조하는 예시적인 방법(200)의 흐름도이다. 도 2에 도시된 예시적인 방법에서, 전도성 층 및 저항성 소자(120)는 세정되고(205) 예를 들어, 원하는 시트 크기로 절단될 수 있다(210). 전도성 층 및 저항성 소자(120)는 접착 물질(130)을 사용하여 함께 라미네이팅될 수 있다(215). 저항성 소자(120) 및 전도성 층은 원하는 대로 마스킹되고(220) 패터닝될 수 있다(225). 예를 들어, 저항기(100)의 경우 전도성 층의 마스킹 및 패터닝은 예를 들어 전도성 층을 분리하여 전도성 소자들(110a 및 110b)을 형성하는 데 사용될 수 있다. 예를 들어, 전도성 소자들(110a 및 110b)과 저항성 소자(120) 사이에 전기적 연결을 만들 전도성 층(150a 및 150c)에 대한 공간을 형성하기 위해, 접착 물질(130)의 적어도 일부가 저항성 소자(120)의 표면(122)으로부터 선택적으로 제거될 수 있다(230).

[0023] 전도성 소자들(110a 및 110b) 및 저항성 소자(120)는 도금 패턴을 생성하기 위해 원하는 대로 마스킹될 수 있고, 그런 다음 도금될 수 있다(235). 도금은 예를 들어, 하나 이상의 전도성 층들(150a, 150b, 150c 및 150d)을 퇴적시키는 데 사용될 수 있다. 일단 도금이 완료되면, 마스킹은 저항성 소자가 교정(calibrated)될 수 있

도록 제거될 수 있고(240), 이러한 교정은 예를 들어 저항기에 대한 목표 저항 값에 기초하여, 특정 위치에서 저항성 포일을 절단하여 전류 경로를 조작함으로써 또는 저항성 포일을 얇게 함으로써 달성될 수 있다. 유전체 물질(140)이 저항기(100)의 상부 표면, 하부 표면 또는 상부 표면과 하부 표면 양자 모두 상에 퇴적된다. 유전체 물질(140)은 예를 들어, 코팅에 의해 전도성 소자들(110a 및 110b)의 노출된 상부 표면 상에 퇴적되는 것이 바람직하다(245). 유전체 물질(140a)은 전도성 소자들(110a 및 110b) 사이의 임의의 공간을 충전하여 이들을 서로 전기적으로 절연시킬 수 있다. 그런 다음, 이 방법에 의해 형성된 플레이트가 개개의 조각으로 개별화되어 개별 저항기(100)를 형성할 수 있다(250). 그런 다음, 납땜 가능 층들(160a 및 160b)이 예를 들어, 도금에 의해 개별 저항기들(100)의 측 방향 에지(165a 및 165b)에 부착되거나 그 위에 형성될 수 있다(255).

[0024] 도 3은 본 발명의 실시예에 따른 또 다른 예시적인 저항기(300)의 다이어그램이다. 저항기(100)와 유사하게, 도 3에 도시된 저항기(300)는 저항기를 가로지르고 제 1 납땜 가능 층(360a)과 제 2 납땜 가능 층(360b)(이는 이하 상세하게 설명됨) 사이에 배치된 저항성 소자(320)를 포함한다. 예시를 목적으로 도 3에 도시된 방향에서, 저항성 소자(320)는 상부 표면(322) 및 하부 표면(324)을 갖는다. 저항성 소자는 포일 저항기인 것이 바람직하다. 저항성 소자(320)는 도 3에서 w로 지정된 폭을 갖는다. 또한, 저항성 소자(320)는 도 3에서 높이 "H"로 지정된 높이 또는 두께를 갖는다. 저항성 소자(320)의 상부 표면(322)의 노출된 부분은 저항성 소자(320)의 측면 에지에 인접한 공간(s 및 s') 각각을 향한다.

[0025] 도 3에 도시된 바와 같이, 제 1 전도성 소자(310a) 및 제 2 전도성 소자(310b)는 저항성 소자(320)의 대향 측면 단부에 인접하게 배치되며, 제 1 전도성 소자(310a)와 제 2 전도성 소자(310b) 사이에 간극(390)이 제공되는 것이 바람직하다. 전도성 소자들(310a 및 310b)은 구리를 포함하는 것이 바람직할 수 있다.

[0026] 전도성 소자들(310a 및 310b)은 접착 물질(330)을 통해 저항성 소자(320)에 라미네이팅되거나 다른 식으로 접합 또는 부착될 수 있다. 도 3에 도시된 바와 같이, 접착 물질(330)은 저항성 소자의 중앙 부분만을 따라 연장되며, w'로 설계된 저항성 소자(320)의 상부 표면에 인접한 폭을 따라 연장되는 것이 바람직하다.

[0027] 각각의 전도성 소자(310a 및 310b)가 간극(390)의 외부 에지로부터 접착 물질(330)의 개개의 외부 에지까지 저항성 소자(320)의 상부 표면(322)의 일부분을 따라 연장되고, 각각이 공간(s 및 s')에 배치되고 저항성 소자(320)의 상부 표면(322)과 직접 접촉하도록 저항성 소자(320)를 향해 바깥쪽으로 그리고 아래쪽으로 비스듬히 놓이는 부분을 갖도록 전도성 소자들(310a 및 310b)은 형상화된다. 전도성 소자들(310a 및 310b)의 각진 부분은, 전도성 소자들(310a 및 310b)과 저항성 소자(320)의 표면(322) 사이에 s로 지정된 영역에서 전기적, 열적 및 기계적으로 긴밀한 접촉을 제공하고, 전도성 소자들(310a 및 310b)과 저항성 소자(320)의 표면(322) 사이에 s'로 지정된 영역에서 전기적, 열적 및 기계적으로 긴밀한 접촉을 제공하도록 배치되고 배열되는 것이 바람직하다. 전도성 소자들(310a 및 310b)의 상단 부분(312a 및 312b)의 형상은 변경될 수 있으며, 이는 영역이 설명된 바와 같이 긴밀한 접촉을 제공하는 한 거의 인지하기 힘든 단차부터 둥근 에지와 같은 둥근 모양, 및 몇 도에서 90도 미만의 경사를 갖는 각도까지 다양할 수 있다.

[0028] 도 3에 도시된 바와 같이, 제 1 전도성 층(350a) 및 제 2 전도성 층(350b)이 저항성 소자(320)의 하부 표면(324)을 따라 대향 측면 단부를 따라 배치된다. 전도성 층들(350a 및 350b)은 저항성 소자(320)의 대향 외부 에지, 및 전도성 층들(310a 및 310b)의 대향 외부 에지와 정렬되는 것이 바람직한 대향 외부 에지를 갖는다. 바람직하게는, 제 1 전도성 층(350a) 및 제 2 전도성 층(350b)은 저항성 소자(320)의 하부 표면(324)에 도금된다.

[0029] 저항성 소자(320)의 외부 측면 에지(또는 외부 측면), 전도성 소자들(310a, 310b)의 외부 측면 및 전도성 층들(350a 및 350b)의 외부 측면 에지(또는 외부 측면)는 납땜 가능 층들을 수용하도록 구성된 납땜 가능 표면을 형성한다. 납땜 가능 층들(360a 및 360b)은 저항기(300)가 회로 기판에 납땜될 수 있게 하기 위해 저항기(300)의 측 방향 단부(365a 및 365b)에 부착될 수 있다. 도 3에 도시된 바와 같이, 납땜 가능 층들(360a 및 360b)은 전도성 소자들(310a 및 310b)의 기울어진 상단 부분(312a 및 312b)을 따라 연장되고, 전도성 소자들(310a 및 310b)의 상부 표면을 따라 적어도 부분적으로 연장되며, 또한 전도성 층들(350a 및 350b)의 하부 표면을 따라 적어도 부분적으로 연장되는 부분들을 포함하는 것이 바람직하다.

[0030] 유전체 물질(340)이 예를 들어, 코팅에 의해 저항기(300)의 표면들 상에 퇴적될 수 있다. 유전체 물질(340)은 공간 또는 간극을 충전하여 구성 요소들을 서로 전기적으로 절연시킬 수 있다. 도 3에 도시된 바와 같이, 제 1 유전체 물질(340a)이 저항기의 상단 부분에 퇴적된다. 제 1 유전체 물질(340a)은 납땜 가능 층들(360a 및 360b)의 부분들 사이에서 연장되고, 전도성 소자들(310a 및 310b)의 노출된 상부 표면을 커버하는 것이 바람직하다. 제 1 유전체 물질(340a)은 또한 전도성 소자들(310a 및 310b) 사이의 간극(390)을 충전하여, 간극(390)을 향하는 접착 물질(330)의 노출된 부분을 커버한다. 제 2 유전체 물질(340b)이 저항성 소자(320)의 하부

표면을 따라 납땜 가능 층들(360a 및 360b)의 부분들 사이에 퇴적되고, 전도성 층들(350a 및 350d)의 노출된 부분 및 저항성 소자(320)의 하부 표면(324)을 커버한다.

[0031] 도 4는 저항기(300)를 제조하는 예시적인 방법(400)의 흐름도이다. 도 4에 도시된 예시적인 방법에서, 전도성 층 및 저항성 소자(320)는 세정되고(405) 예를 들어, 원하는 시트 크기로 절단될 수 있다(410). 전도성 층 및 저항성 소자(320)는 접착 물질(330)을 사용하여 함께 라미네이팅될 수 있다(415). 저항성 소자(320) 및 전도성 층은 원하는 대로 마스킹되고(420) 패터닝될 수 있다(425). 예를 들어, 저항기(300)의 경우 전도성 층의 마스킹 및 패터닝은 예를 들어 전도성 층을 분리하여 전도성 소자들(310a 및 310b)을 형성하는 데 사용될 수 있다. 예를 들어, 전도성 소자들(310a 및 310b)과의 직접적 연결을 위한 공간을 만들기 위해, 접착 물질(330)의 적어도 일부가 저항성 소자(320)의 표면(322)으로부터 선택적으로 제거될 수 있다(430).

[0032] 전도성 소자들(310a 및 310b) 및 저항성 소자(320)는 도금 패턴을 생성하기 위해 원하는 대로 마스킹될 수 있고, 그런 다음 도금될 수 있다(435). 도금은 예를 들어, 저항성 소자(320)의 표면(324) 상에 하나 이상의 전도성 층들(350a 및 350b)을 퇴적시키는 데 사용될 수 있다. 일단 도금이 완료되면, 마스킹은 저항성 소자가 교정될 수 있도록 제거될 수 있고(440), 이러한 교정은 예를 들어 저항기에 대한 목표 저항 값에 기초하여, 특정 위치에서 저항성 포일을 절단하여 전류 경로를 조작함으로써 또는 저항성 포일을 얇게 함으로써 달성될 수 있다. 그런 다음, 전도성 소자들(310a 및 310b)은 접착 물질(330)의 선택적 제거에 의해 노출되었던 저항성 소자(320)의 표면(322) 부분을 커버하도록 스웨이징(swaged)될 수 있다(445).

[0033] 유전체 물질(340)이 예를 들어, 코팅에 의해 전도성 소자들(310a 및 310b) 및 저항성 소자(320)의 하부 표면(324) 중 하나 또는 양자 모두 상에 퇴적될 수 있다(450). 유전체 물질(340a)은 전도성 소자들(310a 및 310b) 사이의 임의의 공간을 충전하여 이들을 서로 전기적으로 절연시킬 수 있다. 그런 다음, 이 방법에 의해 형성된 플레이트가 개개의 조각으로 개별화되어 개별 저항기(300)를 형성할 수 있다(455). 그런 다음, 납땜 가능 층들(360a 및 360b)이 예를 들어, 도금에 의해 개별 저항기들(300)의 측 방향 에지(365a 및 365b)에 부착되거나 그 위에 형성될 수 있다(460).

[0034] 도 5는 본 발명의 실시예에 따른 또 다른 예시적인 저항기(500)의 다이어그램이다. 저항기(100 및 300)와 유사하게, 도 5에 도시된 저항기(500)는 저항기를 가로지르고 제 1 납땜 가능 층(560a)과 제 2 납땜 가능 층(560b) (이는 이하 상세하게 설명됨) 사이에 위치한 저항성 소자(520)를 포함한다. 예시를 목적으로 도 5에 도시된 방향에서, 저항성 소자는 상부 표면(522) 및 하부 표면(524)을 갖는다. 저항성 소자(520)는 포일 저항기인 것이 바람직하다. 저항성 소자(520)는 도 5에서 *w'*로 지정된 폭을 갖는다. 또한, 저항성 소자(520)는 도 5에서 높이 "H"로 지정된 높이 또는 두께를 갖는다. 저항성 소자(520)의 노출된 측면은 저항성 소자(520)의 측면 에지에 인접한 도 5에서 *s* 및 *s'*로 표시된 공간 각각을 향한다.

[0035] 도 5에 도시된 바와 같이, 제 1 전도성 소자(510a) 및 제 2 전도성 소자(510b)는 저항성 소자(520)의 대향 측면 단부에 인접하게 배치되며, 제 1 전도성 소자(510a)와 제 2 전도성 소자(510b) 사이에 간극(590)이 제공되는 것이 바람직하다. 전도성 소자들(510a 및 510b)은 구리를 포함하는 것이 바람직할 수 있다. 바람직하게, 제 1 전도성 소자(510a)와 제 2 전도성 소자(510b)는 저항성 소자(520)의 외부 에지와 정렬된다.

[0036] 전도성 소자들(510a 및 510b)은 접착 물질(530)을 통해 저항성 소자(520)에 라미네이팅되거나 다른 식으로 접합 또는 부착될 수 있다. 도 5에 도시된 바와 같이, 접착 물질(530)은 저항성 소자(520)의 전체 상부 표면(522)을 따라 연장되는 것이 바람직하다. 저항성 소자(520) 및 접착 물질(530)은 *w'*로 표시된 폭을 갖는다.

[0037] 제 1 전도성 층(550a) 및 제 2 전도성 층(550b)이 저항성 소자(520), 접착 물질(530) 및 전도성 소자들(510a 및 510b) 각각의 외부 측면 에지(또는 외부 측면)를 따라, 공간(*s* 및 *s'*)에 제공되어, 이들에 전기적 연결을 제공한다. 바람직하게, 제 1 전도성 층(550a) 및 제 2 전도성 층(550b)은 전도성 소자들(510a 및 510b) 및 저항성 소자(520)의 외부 에지를 따라 그리고 저항성 소자(520)의 하부 표면(524)에 도금된다.

[0038] 저항성 소자(520), 접착 물질(530) 및 전도성 층들(550a, 550b)의 정렬된 외부 측면 에지(또는 외부 측면)는, 납땜 가능 층들을 수용하도록 구성된 납땜 가능 표면을 형성한다. 납땜 가능 층들(560a 및 560b)은 저항기(500)가 회로 기판에 납땜될 수 있게 하기 위해 저항기(500)의 측 방향 단부(565a 및 565b)에 개별적으로 부착될 수 있다. 도 5에 도시된 바와 같이, 납땜 가능 층들(560a 및 560b)은 전도성 층들(550a 및 550b)의 하부 표면을 따라 적어도 부분적으로 연장되고 또한 전도성 층들(550a 및 550b) 및 전도성 소자들(510a 및 510b)의 상부 표면을 따라 적어도 부분적으로 연장되는 부분들을 포함하는 것이 바람직하다.

[0039] 유전체 물질(540)이 예를 들어, 코팅에 의해 저항기(500)의 표면들 상에 퇴적될 수 있다. 유전체 물질(540)은

공간 또는 간극을 충전하여 이들을 서로 전기적으로 절연시킬 수 있다. 도 5에 도시된 바와 같이, 제 1 유전체 물질(540a)이 저항기의 상단 부분 상에 퇴적된다. 제 1 유전체 물질(540a)은 납땜 가능 충들(560a 및 560b)의 부분들 사이에서 연장되고, 전도성 소자들(510a 및 510b)의 노출된 상부 표면을 커버하는 것이 바람직하다. 제 1 유전체 물질(540a)은 또한 전도성 소자들(510a 및 510b) 사이의 간극(590)을 충전하여, 간극(590)을 향하는 접착 물질(530)의 노출된 부분을 커버한다. 제 2 유전체 물질(540b)이 저항성 소자(520)의 하부 표면을 따라 납땜 가능 충들(560a 및 560b)의 부분들 사이에 퇴적되고, 전도성 충들(550a 및 550b)의 노출된 부분 및 저항성 소자(520)의 하부 표면(524)을 커버한다.

[0040] 도 6은 저항기(500)를 제조하는 예시적인 방법의 흐름도이다. 도 6에 도시된 예시적인 방법에서, 전도성 충 및 저항성 소자(520)는 세정되고(605) 예를 들어, 원하는 시트 크기로 절단될 수 있다(610). 전도성 충 및 저항성 소자(520)는 접착 물질(530)을 사용하여 함께 라미네이팅될 수 있다(615). 저항성 소자(520) 및 전도성 충은 원하는 대로 마스킹되고(620) 패터닝될 수 있다(625). 예를 들어, 저항기(500)의 경우 전도성 충의 마스킹 및 패터닝은 예를 들어 전도성 충을 분리하여 전도성 소자들(510a 및 510b)을 형성하는 데 사용될 수 있다.

[0041] 전도성 소자들(510a 및 510b) 및 저항성 소자(520)는 도금 패턴을 생성하기 위해 원하는 대로 마스킹될 수 있고, 그런 다음 도금될 수 있다(630). 도금은 예를 들어, 하나 이상의 전도성 충들(550a 및 550b)을 퇴적시키는 데 사용될 수 있다. 일단 도금이 완료되면, 마스킹은 저항성 소자가 교정될 수 있도록 제거될 수 있고(635), 이러한 교정은 예를 들어 저항기에 대한 목표 저항 값에 기초하여, 특정 위치에서 저항성 포일을 절단하여 전류 경로를 조작함으로써 또는 저항성 포일을 얇게 함으로써 달성될 수 있다. 유전체 물질(540)이 (예를 들어, 코팅에 의해) 전도성 소자들(510a 및 510b) 및 저항성 소자(520) 중 하나 또는 양자 모두 상에 퇴적될 수 있다(640). 유전체 물질(540a)은 전도성 소자들(510a 및 510b) 사이의 임의의 공간을 충전하여 이들을 서로 전기적으로 절연시킬 수 있다. 그런 다음, 이 방법에 의해 형성된 플레이트가 개개의 조각으로 개별화되어 개별 저항기(500)를 형성할 수 있다(645). 그런 다음, 납땜 가능 충들(560a 및 560b)이 예를 들어, 도금에 의해 개별 저항기들(500)의 측 방향 예지(565a 및 565b)에 부착되거나 그 위에 형성될 수 있다(650). 도 5 및 도 6에서 도시된 실시예들에서, 접착 물질(530)은 개별화(singulation) 동안 전단 가공될 수 있으므로, 도금 전에 저항성 소자를 노출시키기 위한 2차 레이징(lasing) 작업에서 캡톤(Kapton)과 같은 특정 접착 물질을 제거할 필요가 없다.

[0042] 본 발명의 특징 및 요소들이 특정한 조합으로 예시적인 실시예들에서 설명되었지만, 각 특징은 예시적인 실시예들의 다른 특징 및 요소들 없이 단독으로 사용될 수 있거나, 또는 본 발명의 다른 특징 및 요소들과 함께 또는 본 발명의 다른 특징 및 요소들 없이 다양한 조합으로 사용될 수 있다.

## 도면

### 도면 1a

도면 1b

도면2

## 도면3

## 도면4

## 도면5

도면6