19 RÉPUBLIQUE FRANÇAISE

#### INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

**PARIS**

11 No de publication :

(à n'utiliser que pour les commandes de reproduction)

②1) Nº d'enregistrement national :

13 59053

3 011 123

(51) Int Cl<sup>8</sup>: **H 01 L 27/115** (2013.01)

| 12 DEMANDE DE BREVET D'INVENTION                                                                                                                                        |                                       |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|

| Date de dépôt : 20.09.13.  Priorité :                                                                                                                                   | 71 Demandeur(s): SEMICONSULTOR — FR.  |  |  |  |  |

| Date de mise à la disposition du public de la demande : 27.03.15 Bulletin 15/13.                                                                                        | 72 Inventeur(s): TOREN WILLEM-JAN.    |  |  |  |  |

| Liste des documents cités dans le rapport de recherche préliminaire : Se reporter à la fin du présent fascicule  Références à d'autres documents nationaux apparentés : | 73 Titulaire(s): SEMICONSULTOR.       |  |  |  |  |

| Demande(s) d'extension :                                                                                                                                                | 74 Mandataire(s): CABINET YVES DEBAY. |  |  |  |  |

CELLULE DE MEMOIRE NON VOLATILE, PROCEDE DE PROGRAMMATION D'EFFACEMENT ET DE LECTURE D'UNE TELLE CELLULE ET DISPOSITIF DE MEMOIRE NON VOLATILE.

La présente invention propose une cellule de mémoire non volatile et un dispositif de mémoire non volatile fonctionnant avec une faible tension de programmation et d'effacement, avec une très bonne rétention en mémoire. De plus, la cellule de mémoire non volatile comprend un circuit de sortie permettant une lecture rapide et à faible puissance

des informations de la cellule de mémoire.

# Cellule de mémoire non volatile, procédé de programmation, d'effacement et de lecture d'une telle cellule et dispositif de mémoire non volatile

#### DOMAINE TECHNIQUE

La présente invention concerne des mémoires non volatiles programmables et/ou effaçables et pouvant être lues électriquement. Plus spécifiquement, l'invention concerne une cellule de mémoire non volatile dont la structure permet, d'une part, sa programmation et/ou son effacement électriques plus efficaces avec de plus faibles potentiels, et avec une rétention en mémoire améliorée, et, d'autre part, une lecture plus efficace de la cellule. L'invention concerne également un dispositif de mémoire non volatile et un procédé pour programmer, effacer et lire électriquement ces cellules de mémoire.

#### CONTEXTE

Les mémoires non volatiles existent depuis de nombreuses années dans de nombreux domaines liés à l'électronique et/ou à l'informatique. Ces mémoires permettent le stockage d'informations, même lorsque le dispositif de mémoire n'est pas alimenté. La technologie au-delà de ces mémoires s'appuie sur des transistors à effet de champ, et plus particulièrement des transistors à effet de champ à grille flottante ou FGFET. En fait, la programmation de cellules de mémoire comprenant des FGFET consiste à injecter des électrons dans la grille flottante des FET des cellules de mémoire. D'autre part, l'effacement d'une cellule de mémoire consiste en la réduction du nombre d'électrons présents dans la grille flottante de chaque FET. Etant donné que la grille flottante est isolée électriquement dans le FET, lorsqu'aucune énergie n'est fournie au FET, les électrons tendent à rester dans la grille flottante. L'inconvénient de cette technologie est le besoin d'un potentiel électrique élevé pour programmer et effacer une cellule de mémoire, afin de permettre l'injection d'électrons, par effet tunnel. Par

exemple, ces potentiels élevés peuvent interférer avec la programmation des cellules voisines. Par ailleurs, l'utilisation répétée de ces potentiels élevés peut réduire la durée de vie des composants.

5

10

15

20

25

30

La demande de brevet US n° 4 203 158 présente un dispositif de mémoire MOS programmable électriquement et effaçable électriquement approprié pour des mémoires à circuits intégrés à haute densité. Les porteurs sont tunnélisés entre une grille flottante et une région dopée dans le substrat pour programmer et effacer le dispositif : une zone minimum de mince couche d'oxyde est utilisée pour séparer la région dopée de la grille flottante. Un inconvénient du dispositif de mémoire présenté dans cette demande consiste en ce que la couche d'oxyde n'a pas une épaisseur constante. Aussi, une difficulté de production apparaîtra probablement. Un autre inconvénient consiste en le besoin d'utiliser des potentiels électriques très élevés pour programmer et pour effacer le dispositif de mémoire.

La demande de brevet US n°5 029 130 présente une cellule de mémoire programmable et effaçable électriquement à transistor unique. Le transistor unique comporte une source, un drain avec une région de canal entre eux, définis sur un substrat. Une première couche isolante se trouve au-dessus des régions de source, de canal et de drain. Une grille flottante est positionnée sur la première couche isolante au-dessus d'une partie de la région de canal et au-dessus d'une partie de la région de drain. Une deuxième couche isolante et ensuite une grille de commande se trouvent audessus de la grille flottante. L'effacement de la cellule est accompli par le mécanisme effet tunnel de Fowler-Nordheim de la grille flottante, à travers la deuxième couche isolante, jusqu'à la grille de commande. La programmation est accomplie par les électrons provenant de la source migrant à travers la région de canal au-dessous de la grille de commande et ensuite par une injection provoquant une chute de potentiel brusque à travers la première couche isolante dans la grille flottante. Cependant, le transistor décrit dans cette demande comprend une grille flottante et une grille de commande.

Cette application ne peut pas s'appliquer à des transistors comprenant seulement une grille flottante.

5

10

15

20

25

30

La demande de brevet US n°6 157 058 présente une configuration de dispositif à FET pour des mémoires programmables et effaçables électriquement, qui ajoute des composants verticaux à une structure de cellule à grille flottante précédemment plane. L'efficacité de l'injection d'électrons du canal vers la grille flottante est ensuite améliorée de nombreux ordres d'amplitude parce que les électrons accélérés dans le canal pénètrent dans la direction de mouvement, directement dans la grille flottante. Par conséquent, une grande efficacité d'injection peut être obtenue à des tensions de fonctionnement beaucoup plus faibles, et le temps de programmation est diminué, lequel a été un facteur limitatif dans les applications d'EEPROM. Cependant, même si la forme de la structure à grille flottante était conçue pour faciliter l'injection d'électrons chauds du canal du transistor vers la grille flottante, elle n'améliore pas le mouvement des électrons de la grille flottante vers le canal. Aussi, il ne semble pas que le dispositif de mémoire décrit dans cette demande améliore le maintien en mémoire.

En plus de retenir des informations, ces mémoires permettent la lecture d'informations. Par exemple, la demande de brevet français n° 13/56836 présentait une cellule de mémoire non volatile qui comprend un transistor de lecture permettant la lecture d'informations mémorisées dans ladite cellule de mémoire. Cependant, la lecture est effectuée en mesurant le courant qui passe à travers la cellule, sa détection pouvant prendre du temps.

#### **DESCRIPTION DE L'INVENTION**

La présente invention consiste, par conséquent, à proposer une cellule de mémoire non volatile, qui surmonte un ou plusieurs des inconvénients de l'art antérieur. La présente invention propose une cellule de mémoire non volatile et un dispositif de mémoire non volatile fonctionnant

avec une faible tension de programmation et d'effacement, avec une très bonne rétention en mémoire. De plus, la cellule de mémoire non volatile comprend un circuit de sortie permettant une lecture rapide et à faible puissance des informations de la cellule de mémoire.

L'invention concerne une cellule de mémoire non volatile caractérisée en ce qu'elle comprend :

- au moins un substrat en silicium dopé, séparé physiquement et électriquement en deux sections par une partie de substrat dopé dont le dopage est opposé à celui du substrat en silicium dopé,

- au moins trois composants isolés insérés chacun dans une tranchée, la première tranchée étant fabriquée dans la première section du substrat en silicium dopé, les deuxième et troisième tranchées étant fabriquées dans la partie de substrat dopée et étant respectivement adjacentes aux première et deuxième sections du substrat en silicium dopé, les premier et deuxième composants isolés étant séparés par la première section du substrat en silicium dopé, les deuxième et troisième composants isolés étant séparés par la partie de substrat dopée,

- au moins deux couches de silicium dont le dopage est opposé à celui du substrat en silicium, une première couche de silicium recouvrant au moins partiellement la première section du substrat en silicium et une deuxième couche de silicium recouvrant au moins partiellement la deuxième section du substrat en silicium,

- une région de source et une région de drain avec un canal induit entre les deux régions, l'une de ces régions étant adjacente à la première couche de silicium, une structure de grille comprenant une couche diélectrique et une couche conductrice étant placée au moins au-dessus du canal, le substrat en silicium, les régions de source et de drain et la structure de grille formant un

10

5

15

20

25

transistor de sélection pour permettre la circulation d'électrons au moins dans la première couche de silicium,

- une structure de grille flottante au-dessus des deux couches de silicium, ladite structure comprenant au moins une mince couche diélectrique et au moins une couche conductrice,

- un circuit de transistor à effet de champ CMOS comprenant :

- une première région de source et une première région de drain avec un canal induit entre les deux régions, ces régions étant respectivement adjacentes aux premier et deuxième composants isolés, le dopage des régions étant différent de celui du substrat en silicium,

- une deuxième région de source et une deuxième région de drain avec un canal induit entre les deux régions, ces régions étant respectivement adjacentes aux deuxième et troisième composants isolés, les régions ayant le même dopage que le substrat en silicium dopé.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce qu'au moins une partie de la couche diélectrique et au moins une partie de la couche conductrice placées au-dessus de la première couche de silicium ont une forme en marche d'escalier.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que la première section du substrat en silicium dopé a une forme en marche d'escalier.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que l'angle de la forme en marche d'escalier formée dans la couche diélectrique de la structure de grille flottante est compris entre 30° et 180°, de préférence entre 30° et 90° lorsqu'il est mesuré à partir d'une direction parallèle à la surface du substrat.

10

5

15

25

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que la deuxième couche de silicium est un conducteur électrique d'un condensateur, l'autre conducteur électrique étant la couche conductrice de la structure de grille flottante.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que le substrat en silicium est de puits dopés P.

5

10

15

20

25

30

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que les régions de drain et de source du transistor de sélection sont dopées N+.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que la première région de drain et la première région de source du circuit CMOS sont dopées N+, tandis que la deuxième région de drain et la deuxième région de source du circuit CMOS sont dopées P+.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que les deux sections du substrat en silicium et la partie de substrat dopée se trouvent sur une région de puits dopés N profonds afin d'isoler électriquement les deux sections du substrat en silicium.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que la couche conductrice de la structure de grille et la couche conductrice de la structure de grille flottante sont faites de silicium polycristallin.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que les composants isolés, la couche diélectrique de la structure de grille et la couche diélectrique de la structure de grille flottante sont faites d'oxyde de silicium.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que l'épaisseur de la couche diélectrique d'au moins la structure de grille flottante est constante, la valeur de l'épaisseur étant comprise entre 50 et 200 angströms.

Selon une autre caractéristique, la cellule de mémoire non volatile est caractérisée en ce que l'épaisseur et la forme en marche d'escalier de la couche diélectrique de la structure de grille flottante permettent la diminution de la tension de programmation et/ou d'effacement de la couche conductrice de la structure de grille flottante, de sorte que ladite tension de programmation et/ou d'effacement soit compatible avec la tension requise pour faire fonctionner le circuit CMOS.

Un autre but de la présente invention est de proposer un procédé pour programmer une cellule de mémoire non volatile, la cellule étant connectée à des moyens de commande commandant ladite cellule et à un générateur de puissance connecté à la cellule, caractérisé par l'injection d'électrons de la première couche de silicium vers la couche conductrice de la structure de grille flottante à travers le haut de la forme en marche d'escalier de la couche diélectrique, le procédé comprenant :

15

10

5

l'étape d'application d'un potentiel positif à la couche conductrice de la structure de grille et à la deuxième couche de silicium grâce au générateur de puissance, induisant la polarisation de la couche conductrice de la structure de grille flottante par effet de couplage capacitif,

20

l'étape d'application d'un potentiel négatif à la région de drain du transistor de sélection et à la première section du substrat en silicium dopé grâce au générateur de puissance connecté à ladite région de drain et à la première section du substrat en silicium, induisant la circulation d'électrons de la région de drain vers la région de source du transistor de sélection, ladite circulation d'électrons polarisant négativement la première couche de silicium adjacente à la région de source du transistor de sélection,

25

30

la deuxième section du substrat en silicium dopé et la partie de substrat dopée étant polarisées à 0 volt. Un autre but de la présente invention consiste à proposer un procédé pour effacer une cellule de mémoire non volatile, la cellule étant connectée à des moyens de commande commandant ladite cellule et à un générateur de puissance connecté à la cellule, caractérisé par l'injection d'électrons de la couche conductrice de la structure de grille flottante vers la première couche de silicium à travers le bas de la forme en marche d'escalier de la couche diélectrique, le procédé comprenant :

10

5

l'étape d'application d'un potentiel négatif à la deuxième section du substrat en silicium dopé et à la deuxième couche de silicium grâce au générateur de puissance, induisant la polarisation de la couche conductrice de la structure de grille flottante par effet de couplage capacitif,

15

20

25

l'étape d'application d'un potentiel positif à la couche conductrice de la structure de grille et à la région de drain du transistor de sélection grâce au générateur de puissance connecté à ladite couche conductrice et à ladite région de drain, induisant la polarisation positive de la première couche de silicium adjacente à la région de source du transistor de sélection,

la première section du substrat en silicium dopé et la partie de substrat dopée étant polarisées à 0 volt.

Un autre but de la présente invention consiste à proposer un procédé pour lire une cellule de mémoire non volatile, caractérisé par la détection de l'état logique du circuit CMOS grâce à des moyens de commande, la partie de substrat dopée et la deuxième région de source du circuit CMOS étant polarisées à un potentiel positif connu V<sub>dd</sub>, grâce au générateur de puissance commandé par les moyens de commande, les deux sections du substrat en silicium dopé, la deuxième couche de silicium et la première région de source du circuit CMOS étant polarisées à 0 volt, la variation de la tension de sortie V<sub>out</sub> du circuit CMOS étant lue par les moyens de commande, ladite

tension de sortie étant le potentiel des première et deuxième régions de drain du circuit CMOS.

Un autre but de la présente invention consiste à proposer un dispositif de mémoire non volatile caractérisé en ce qu'il comprend une pluralité de cellules de mémoire non volatile, ladite pluralité de cellules formant une matrice de N rangées et M colonnes.

5

10

15

20

25

Selon une autre caractéristique, le dispositif de mémoire non volatile est caractérisé en ce que les première et deuxième régions de drain du circuit CMOS et la couche conductrice de la structure de grille de chaque cellule d'une rangée sont connectées à une seule ligne de bit, ladite ligne de bit étant connectée au générateur de puissance et aux moyens de commande.

Selon une autre caractéristique, le dispositif de mémoire non volatile est caractérisé en ce que les première et deuxième régions de drain du circuit CMOS de chaque cellule d'une rangée sont connectées à une première ligne de bit, tandis que la couche conductrice de la structure de grille de chaque cellule de la même rangée est connectée à une deuxième ligne de bit, lesdites lignes de bit étant connectées au générateur de puissance et aux moyens de commande.

Selon une autre caractéristique, le dispositif de mémoire non volatile est caractérisé en ce que chaque cellule du dispositif peut être programmée, effacée ou lue de manière sélective et de manière indépendante.

L'invention, ses caractéristiques et ses avantages, deviendront plus évidents à la lecture de la description qui suit avec référence aux dessins joints, sur lesquels :

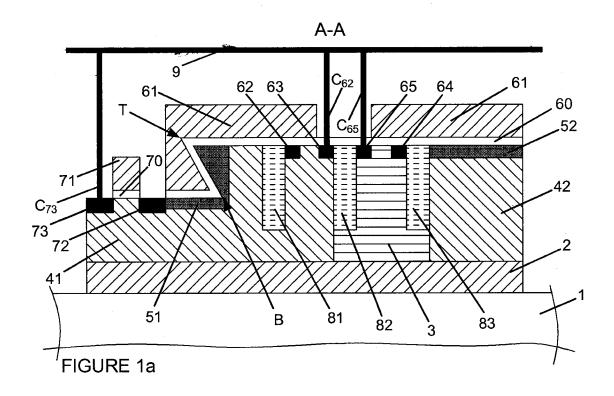

La figure 1a montre une vue en coupe d'une cellule de mémoire non volatile selon l'invention dans un mode de réalisation.

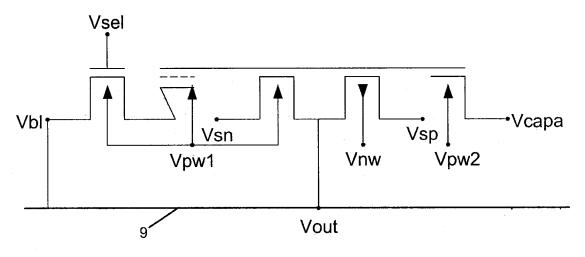

La figure 1b montre un schéma d'une cellule de mémoire non volatile selon l'invention.

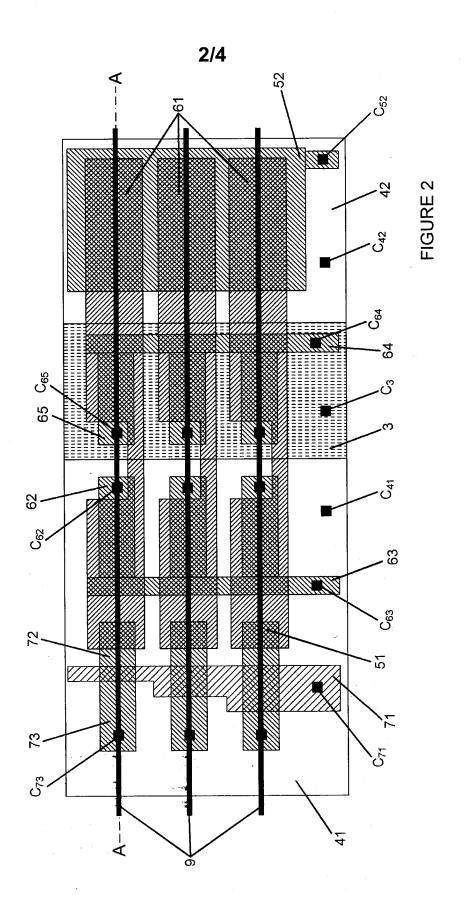

La figure 2 montre une vue de dessus de trois cellules de mémoire non volatile connectées les unes aux autres.

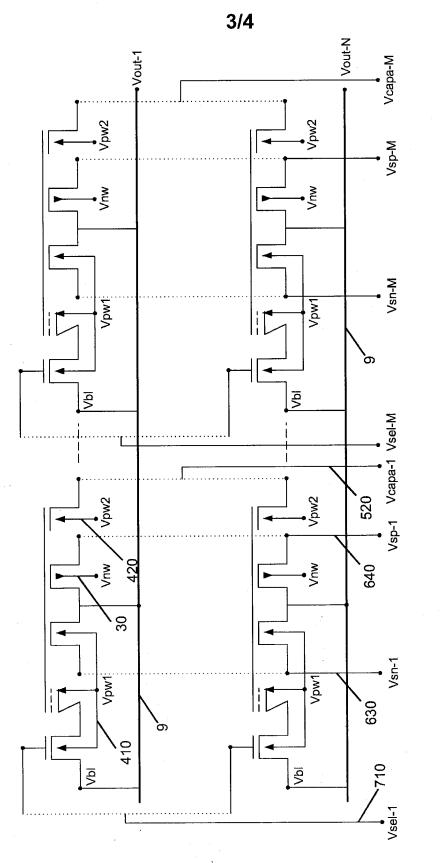

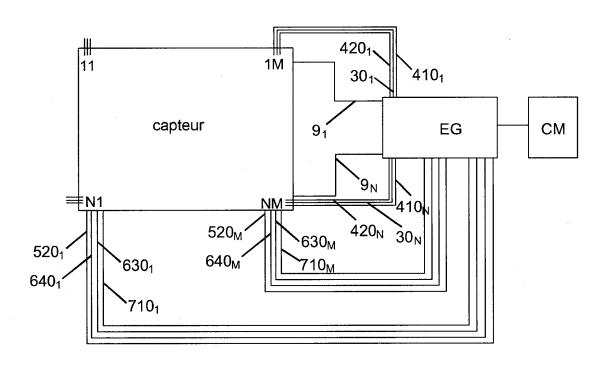

La figure 3 montre un schéma d'une matrice d'une pluralité de cellules de mémoire non volatile, formant un dispositif de mémoire non volatile selon l'invention.

5

15

20

25

30

La figure 4 montre une représentation d'un dispositif de mémoire non volatile selon l'invention, connecté à la source de puissance et aux moyens de commande.

## DESCRIPTION DE MODES DE REALISATION PREFERES DE 10 L'INVENTION

Avec référence aux figures 1 à 4, l'invention va maintenant être décrite.

Dans un mode de réalisation, la cellule de mémoire non volatile est fabriquée sur un substrat de coeur dopé (1), par exemple fait de silicium. Par exemple, et d'une manière non limitative, ce substrat de coeur (1) est dopé P.

Dans un mode de réalisation, la cellule de mémoire non volatile comprend au moins un substrat en silicium dopé (4), ledit substrat en silicium étant de puits dopés P d'une manière non limitative. Afin d'isoler électriquement le substrat en silicium de puits dopés P (4) du substrat de coeur dopé P (1), la cellule de mémoire non volatile comprend également, entre le substrat de coeur et le substrat en silicium, une région de puits N profonds (2). Par exemple, cette région peut être implantée avant la formation du substrat en silicium de puits dopés P.

Dans un mode de réalisation montré sur la figure 1a, le substrat en silicium de puits dopés P (4) comprend deux sections séparées physiquement et électriquement (41, 42). Afin de réaliser cela, une partie en silicium dopée dont le dopage est opposé à celui du substrat en silicium dopé (4) est implantée entre les deux sections séparées (41, 42) du substrat en silicium dopé. Par exemple, et d'une manière non limitative, la partie en

silicium dopée est de puits dopés N. Ainsi, il y a deux sections de puits dopés P (41, 42) différentes réalisées dans le substrat en silicium de puits dopés P (4), lesdites sections étant isolées électriquement l'une par rapport à l'autre. Ci-après, ces deux sections du substrat en silicium de puits dopés P seront appelées première section de puits dopés P (41) et deuxième section de puits dopés P (42). Les deux sections dopées étant séparées électriquement, elles peuvent être polarisées différemment grâce à un générateur de puissance, par exemple et d'une manière non limitative, un générateur électrique.

Dans un mode de réalisation, une première tranchée est réalisée dans la première section (41) du substrat en silicium de puits dopés P, et un premier composant isolé (81) est inséré dans cette première tranchée. Dans un mode de réalisation, des deuxième et troisième tranchées sont réalisées dans la partie de substrat de puits dopés N (3), lesdites deuxième et troisième tranchées étant respectivement adjacentes à la première section (41) et à la deuxième section (42) du substrat en silicium de puits dopés P. Ensuite, un deuxième composant isolé (82) est inséré dans la deuxième tranchée, tandis qu'un troisième composant isolé (83) est inséré dans la troisième tranchée. Ces opérations sont effectuées selon le processus connu d'isolement de tranchées peu profondes. Par exemple et d'une manière non limitative, les composants isolés sont des composants diélectriques, par exemple faits d'oxyde de silicium.

Dans un mode de réalisation, les premier et deuxième composants isolés (81, 82) sont séparés par la première section (41) du substrat en silicium de puits dopés P, tandis que les deuxième et troisième composants isolés (82, 83) sont séparés par la partie de substrat de puits dopés N (3).

Dans un mode de réalisation, la cellule de mémoire non volatile comprend au moins deux couches de silicium (52, 51) qui sont formées audessus de chaque section du substrat en silicium (4). Dans un mode de réalisation, mais d'une manière non limitative, une première couche de silicium (51) est formée dans la première section (41) du substrat en silicium,

la première couche recouvrant partiellement la première section, et une deuxième couche de silicium (52) est formée dans la deuxième section (42) du substrat en silicium, la deuxième couche recouvrant au moins partiellement la deuxième section. Dans un mode de réalisation, la première couche de silicium (51) n'est pas formée au-dessus de la première section (41) du substrat en silicium à puits dopés P situé entre le premier composant isolé (81) et le deuxième composant isolé (82). Les couches de silicium (52, 51) sont fortement dopées, et leur dopage est opposé à celui du substrat en silicium (4). Dans un mode de réalisation préféré, mais d'une manière non limitative, les couches de silicium sont dopées N+.

5

10

15

20

25

30

Dans un mode de réalisation, la cellule de mémoire non volatile comprend une région de source (72) et une région de drain (73), avec un canal induit entre les deux régions, et l'une de ces régions est adjacente à la première couche de silicium (51). Ces régions de drain/source (72, 73) sont implantées dans la première section (41) du substrat en silicium. Dans un mode de réalisation préféré, et d'une manière non limitative, ces régions de source/drain sont dopées N+, étant donné que la première section (41) du substrat en silicium est de puits dopés P. La cellule de mémoire non volatile comprend également une structure de grille, ladite structure comprenant une couche isolée (70) et une couche conductrice (71) au-dessus de la couche isolée. La couche isolée, par exemple un composant diélectrique fait d'oxyde de silicium, est déposée sur la première section (41) du substrat en silicium, où aucune couche de silicium dopée (51) n'est présente. Dans un autre mode de réalisation, la couche isolée, par exemple un composant diélectrique fait d'oxyde de silicium, est développée sur la première section (41) du substrat en silicium, où aucune couche de silicium dopée (51) n'est présente. Ensuite, une couche conductrice (71), par exemple faite de silicium polycristallin, est déposée sur la couche isolée (70). La structure de grille est déposée au-dessus du canàl induit, de sorte que les régions de source/drain (72, 73) et la structure de grille forment un transistor de sélection appelé FET pour permettre ou non la circulation d'électrons au moins dans la première

couche de silicium (51). La couche conductrice (71) de la structure de grille est connectée au générateur de puissance.

Dans un mode de réalisation, la cellule de mémoire non volatile comprend une structure de grille flottante, ladite structure comprenant au moins une couche isolée (60) et au moins une couche conductrice (61) audessus de la couche isolée. Par exemple et d'une manière non limitative, la structure de grille flottante comprend une couche isolée (60) et une couche conductrice (61). La couche isolée, par exemple un composant diélectrique fait d'oxyde de silicium, est déposée sur le substrat en silicium à puits dopés P, à l'exception des autres régions de source et de drain (72, 73) du transistor de sélection. Ensuite, une couche conductrice, par exemple faite de silicium polycristallin, est déposée sur la couche isolée. Par exemple et d'une manière non limitative, l'épaisseur des couches isolées (60, 70) de la structure de grille et des structures de grille flottante est comprise entre 50 et 500 angströms, de préférence entre 50 et 200 angströms, et plus préférablement autour de 80 à 100 angströms.

Le dépôt de la structure de grille et de la structure de grille flottante est effectué avant l'implantation des régions de source/drain (72, 73) du transistor de sélection, tandis que l'implantation des couches de silicium dopées (52, 51) est effectuée avant le dépôt de la structure de grille et de la structure de grille flottante. Par conséquent, il y a des régions dopées audessous des structures de grille, qui sont, par exemple et d'une manière non limitative, fortement dopées N+. Physiquement, ces couches de silicium dopées N+ (52, 51) sont implantées avant le dépôt des structures de grille. Par exemple et d'une manière non limitative, la structure de grille et la structure de grille flottante sont fabriquées en même temps.

Dans un mode de réalisation, au moins une extrémité de la couche diélectrique (60) placée au-dessus de la première couche de silicium (51) et placée à proximité de la région de drain/source (72) a une forme en marche d'escalier afin d'améliorer l'injection d'électrons dans la couche conductrice (61) de la structure de grille flottante ou dans la première couche de silicium

(51), en fonction de la manière selon laquelle la couche conductrice (61) de la structure de grille flottante et la première couche de silicium (51) sont polarisées grâce au générateur de puissance. Dans un mode de réalisation préféré mais d'une manière non limitative, la première section (41) du substrat en silicium (4) a une forme en marche d'escalier.

Dans un mode de réalisation, mais d'une manière non limitative, l'angle de la forme en marche d'escalier formée dans la couche diélectrique (60) de la structure de grille flottante est compris entre 30° et 90° lorsqu'il est mesuré à partir d'une direction parallèle à la surface du substrat. Dans un mode de réalisation préféré, l'angle de la forme en marche d'escalier forme un Z. Dans un autre mode de réalisation, l'angle de la forme en marche d'escalier formée dans la couche diélectrique (60) de la structure de grille flottante est supérieur à 90°. Cette forme particulière de la couche isolée (60) permet l'utilisation d'un potentiel électrique plus faible pour programmer ou effacer la cellule de mémoire non volatile, tandis que la couche diélectrique reste suffisamment épaisse pour garantir une bonne retenue des électrons.

Il est ensuite possible de programmer ou d'effacer des cellules de mémoire non volatile de l'invention avec des potentiels électriques plus faibles que ceux utilisés habituellement, tandis que la couche diélectrique (60) de la structure de grille flottante de la cellule de mémoire reste aussi épaisse que les couches diélectriques utilisées habituellement, ou est même un petit peu plus épaisse que les couches diélectriques utilisées généralement. En conséquence, la forme en marche d'escalier (ou forme en Z) de la couche isolée (60) de la structure de grille flottante de l'invention combine une meilleure fiabilité (l'utilisation d'un plus petit potentiel électrique est moins perturbante pour les cellules de mémoire voisines), une plus faible consommation de puissance et une meilleure retenue des électrons dans la couche conductrice (61) de la structure de grille flottante. Un avantage est que la cellule de mémoire non volatile peut être programmée ou effacée avec des tensions qui sont proches de celles utilisées pour faire fonctionner d'autres composants électroniques, par exemple et d'une manière non

limitative des composants tels que des circuits de transistors à effet de champ CMOS. Cet avantage sera ensuite décrit avec plus de précision ultérieurement dans la description.

5

10

15

20

25

30

Dans un mode de réalisation, la cellule de mémoire non volatile comprend un circuit de transistor à effet de champ CMOS. Par exemple et d'une manière non limitative, ce circuit CMOS est un circuit inverseur unique comprenant un transistor NMOS et un transistor PMOS. Ce circuit CMOS comprend une première région de source (62) et une première région de drain (63) avec un canal induit entre les deux régions. La première région de source est adjacente au premier composant isolé (81), tandis que la première région de drain est adjacente au deuxième composant isolé (82). Les premières régions de drain et de source sont fortement dopées, et leur dopage est opposé à celui du substrat en silicium de puits dopés P (4). Physiquement, ces premières régions de source et de drain (62, 63) sont implantées avant le dépôt des structures de grilles. Par exemple et d'une manière non limitative, les premières régions de source et de drain du circuit CMOS sont dopées N+, la première région de source, la première région de drain et la structure de grille flottante formant le transistor NMOS du circuit CMOS. Le circuit CMOS comprend une deuxième région de source (64) et une deuxième région de drain (65) avec un canal induit entre les deux régions. La deuxième région de source est adjacente au troisième composant isolé (83), tandis que la deuxième région de drain est adjacente au deuxième composant isolé (82). Physiquement, ces deuxièmes régions de source et de drain (64, 65) sont implantées avant le dépôt des structures de grilles. Les deuxièmes régions de drain et de source sont fortement dopées, et leur dopage est similaire à celui du substrat en silicium de puits dopés P (4), excepté que les deuxièmes régions de drain et de source sont plus fortement dopées que le substrat en silicium dopé (4). Par exemple et d'une manière non limitative, les deuxièmes régions de source et de drain du circuit CMOS sont dopées P+, la deuxième région de source, la deuxième

région de drain et la structure de grille flottante formant le transistor PMOS du circuit CMOS.

Dans un mode de réalisation, le circuit CMOS forme un transistor de lecture dont l'objet est de caractériser l'état de la cellule de mémoire non volatile ou de caractériser le potentiel de la structure de grille flottante, afin de savoir si ladite cellule est déjà programmée ou pas. Le rôle de ce transistor de lecture sera expliqué davantage dans le texte de la description.

Le procédé pour programmer la cellule de mémoire non volatile selon l'invention va maintenant être décrit dans un mode de réalisation préféré. La cellule de mémoire est à la fois connectée par l'intermédiaire de connecteurs (C<sub>3</sub>, C<sub>42</sub>, C<sub>52</sub>, C<sub>62</sub>, C<sub>63</sub>, C<sub>64</sub>, C<sub>65</sub>, C<sub>71</sub> et C<sub>73</sub>) au moins au générateur de puissance et aux moyens de commande : les moyens de commande commandent le générateur de puissance et la cellule de mémoire. Dans un mode de réalisation, les moyens de commande sont compris dans la cellule de mémoire non volatile.

La programmation de la cellule de mémoire non volatile est obtenue grâce à l'injection d'électrons par effet tunnel de la première couche de silicium (51) vers la couche conductrice (61) de la structure de grille flottante. Afin de réaliser cela, la différence de potentiel électrique entre la couche conductrice (61) de la structure de grille flottante et la première couche de silicium (51) doit être suffisamment grande pour permettre la circulation d'électrons à travers la couche diélectrique (60) de la structure de grille flottante.

La première étape du procédé pour programmer la cellule de mémoire non volatile consiste à appliquer un potentiel électrique positif  $V^+$  à la deuxième couche de silicium (52) de la cellule, ladite couche étant connectée au générateur de puissance. Le potentiel électrique de la deuxième couche de silicium (52) est  $V_{CAPA}$ . La deuxième couche de silicium est considérée comme étant un conducteur électrique d'un condensateur, l'autre conducteur électrique étant la couche conductrice (61) de la structure

de grille flottante. Ainsi, la polarisation de la couche conductrice de la structure de grille flottante est induite par effet de couplage capacitif. Par exemple et d'une manière non limitative, la deuxième couche de silicium (52) est polarisée à environ 3,3 volts, c'est-à-dire que  $V_{CAPA}=3,3$  volts, induisant la polarisation positive de la couche conductrice (61) de la structure de grille flottante. Pendant la même étape, le potentiel positif  $V^+$  est également appliqué à la couche conductrice (71) de la structure de grille du transistor de sélection. Le potentiel électrique de la couche conductrice de la structure de grille du transistor de sélection est  $V_{SEL}$ . Ainsi,  $V_{SEL}=3,3$  volts.

La deuxième étape du procédé pour programmer la cellule de mémoire non volatile consiste à appliquer un potentiel électrique négatif V à la fois à la première section (41) du substrat en silicium, par exemple et d'une manière non limitative  $V_{PW1} = -3,3$  volts, et à la région de drain (73) du transistor de sélection, par exemple et d'une manière non limitative  $V_{BL} = -3,3$  volts. Ces polarisations sont réalisées grâce au générateur de puissance connecté au transistor de sélection et à la première section (41) du substrat en silicium. Cela induit une circulation d'électrons de la région de drain (73) vers la région de source (72) du transistor de sélection étant adjacente à la première couche de silicium (51), le potentiel de ladite couche devient négatif grâce à la circulation d'électrons. Par exemple et d'une manière non limitative, le potentiel électrique de la première couche de silicium (51) est autour de -3,3 volts.

Ainsi, la couche conductrice (61) de la structure de grille flottante est polarisée positivement, tandis que le potentiel de la première couche de silicium (51) est négatif. Par exemple et d'une manière non limitative, la différence de potentiel entre la couche conductrice (61) de la structure de grille flottante et la première couche de silicium (51) est d'environ 7 volts. Grâce à la forme en marche d'escalier de la couche diélectrique de la structure de grille flottante, le champ électrique en haut (T) de la forme en marche d'escalier est la somme vectorielle de deux composantes du champ

électrique. Le champ électrique est suffisamment élevé pour permettre la circulation d'électrons de la première couche de silicium (51) vers la couche conductrice (61) de la structure de grille flottante.

Pendant les première et deuxième étapes, la partie de substrat en silicium de puits N (3) et la deuxième section (42) du substrat en silicium sont polarisées à 0 V, ainsi  $V_{NW} = V_{PW2} = 0$  volt.

5

10

15

20

25

30

Le procédé pour effacer la cellule de mémoire non volatile selon l'invention va maintenant être décrit dans un mode de réalisation préféré.

L'effacement de la cellule de mémoire non volatile est obtenu grâce à l'injection d'électrons par effet tunnel de la couche conductrice (61) de la structure de grille flottante vers la première couche de silicium (51). Afin de réaliser cela, la différence de potentiel entre la couche conductrice (61) de la structure de grille flottante et la première couche de silicium (51) doit être suffisamment grande pour permettre la circulation d'électrons à travers la couche diélectrique (60) de la structure de grille flottante.

La première étape du procédé pour effacer la cellule de mémoire non volatile consiste en l'application d'un potentiel électrique négatif V à la fois à la deuxième section (42) du substrat en silicium et à la deuxième couche de silicium (52) de la cellule, ladite couche et ladite deuxième section étant connectées au générateur de puissance. La polarisation de la couche conductrice (61) de la structure de grille flottante est ensuite induite par effet de couplage capacitif. Par exemple et d'une manière non limitative, la deuxième couche de silicium (52) et la deuxième section (42) du substrat en silicium sont polarisées à environ -3,3 volts, c'est-à-dire que V<sub>CAPA</sub> = V<sub>PW2</sub> = -3,3 volts, induisant la polarisation négative de la couche conductrice (61) de la structure de grille flottante.

La deuxième étape du procédé pour effacer la cellule de mémoire non volatile consiste en l'application d'un potentiel électrique positif  $V^+$  à la fois à la couche conductrice (71) de la structure de grille du transistor de sélection, par exemple et d'une manière non limitative  $V_{\rm SEL} = 3,3$  volts, et à la

région de drain (73) du transistor de sélection, par exemple et d'une manière non limitative  $V_{BL}=3,3$  volts. Ces polarisations sont réalisées grâce au générateur de puissance connecté à la couche conductrice (71) de la structure de grille du transistor de sélection et à la région de drain (73) du transistor de sélection. Cela induit une polarisation positive des régions de source et de drain (72, 73) du transistor de sélection. La région de source (72) du transistor de sélection est adjacente à la première couche de silicium (51), le potentiel de ladite couche (51) devenant positif grâce à la circulation d'électrons. Par exemple et d'une manière non limitative, le potentiel électrique de la première couche de silicium est autour de 3,3 volts.

Ainsi, la couche conductrice (61) de la structure de grille flottante est polarisée négativement, tandis que le potentiel de la première couche de silicium (51) est positif. Par exemple et d'une manière non limitative, la différence de potentiel entre la couche conductrice (61) de la structure de grille flottante et la première couche de silicium (51) est d'environ 7 volts. Grâce à la forme en marche d'escalier de la couche diélectrique (60) de la structure de grille flottante, le champ électrique dans le bas (B) de la forme en marche d'escalier est la somme vectorielle de deux composantes du champ électrique. Le champ électrique est suffisamment élevé pour permettre la circulation d'électrons de la couche conductrice (61) de la structure de grille flottante vers la première couche de silicium (51).

Pendant les première et deuxième étapes, la première section (41) du substrat en silicium et la partie de substrat en silicium à puits dopés N (3) sont polarisées à 0 V, ainsi  $V_{PW1} = V_{NW} = 0$  volt.

Le procédé pour lire la cellule de mémoire non volatile selon l'invention va maintenant être décrit dans un mode de réalisation préféré. La cellule de mémoire est connectée par des connecteurs au moins à la fois au générateur de puissance et aux moyens de commande : les moyens de commande commandent le générateur de puissance et la cellule de mémoire. Dans un mode de réalisation, une tranchée est réalisée dans la couche conductrice (61) de la structure de grille flottante juste au-dessus des

première (63) et deuxième (65) régions de drain du circuit CMOS. Cette tranchée ne divise pas la couche conductrice (61) en deux morceaux. Cette tranchée est réalisée afin de connecter les première et deuxième régions de drain du circuit CMOS l'une à l'autre grâce à un conducteur (9), ledit conducteur étant lié à la fois au générateur de puissance et aux moyens de commande. Dans un mode de réalisation préféré, les première (63) et deuxième (65) régions de drain du circuit CMOS et la région de drain (73) du transistor de sélection sont connectées les unes aux autres grâce à un conducteur appelé ligne de bit (9).

5

10

15

20

25

30

L'étape du procédé pour lire la cellule de mémoire non volatile consiste en la détection de l'état logique du circuit CMOS; afin de réaliser cela, la partie de substrat de puits dopés N (3) et la deuxième région de source (64) du circuit CMOS sont toutes deux polarisées à un potentiel positif V<sub>dd</sub> connu, dont la valeur est, par exemple et d'une manière non limitative, de 3,3 volts. Les hommes du métier comprendront que la partie de substrat de puits N (3) est connectée au générateur électrique par l'intermédiaire d'un connecteur (C<sub>3</sub>). Ils comprendront également qu'un circuit CMOS est un circuit intégré logique, dans lequel les signaux détectés sont un courant très faible induit par des tensions en créneaux passant très rapidement de 0 volt à V<sub>dd</sub>, et vice versa. Ainsi, le potentiel électrique de la partie de substrat de puits N (3) est V<sub>NW</sub>, tandis que le potentiel de la deuxième région de source (64) du circuit CMOS est V<sub>SP</sub>. Par exemple et d'une manière non limitative,  $V_{NW} = V_{SP} = 3.3$  volts. Bien entendu, les première et deuxième sections (41, 42) du substrat en silicium dopé sont également connectées au générateur de puissance, et leurs potentiels électriques sont respectivement V<sub>PW1</sub> et V<sub>PW2</sub>. Durant le procédé pour lire la cellule de mémoire non volatile, les première et deuxième sections (41, 42) du substrat en silicium sont polarisées à 0 V, et c'est pareil pour la première région de source (62) du circuit CMOS. Alors,  $V_{SN} = V_{PW1} = V_{PW2} = 0$  volt.  $V_{CAPA}$  est compris entre 0 volt et 3,3 volts. Ce procédé de lecture, dans lequel la variation du potentiel électrique Vout de la sortie du circuit CMOS est détectée, donne des informations concernant l'état logique du circuit CMOS et concernant l'état de la cellule de mémoire non volatile d'une manière beaucoup plus rapide que la mesure du courant (c'est-à-dire de la circulation d'électrons de la première couche de silicium (51) vers le transistor de lecture).

5

10

15

20

25

30

Dans un mode de réalisation, montré sur les figures 2, 3 et 4, un autre objet de l'invention consiste à proposer un dispositif de mémoire non volatile, ledit dispositif comprenant une pluralité de cellules de mémoire non volatile, formant une matrice de N rangées et M colonnes de cellules. Dans un mode de réalisation montré sur la figure 3, les première (63) et deuxième (65) régions de drain du circuit CMOS et la région de drain (73) du transistor de sélection de chaque cellule d'une rangée sont connectées à une seule ligne de bit (9), ladite ligne de bit étant connectée au générateur de puissance et aux moyens de commande. Par exemple, il y a N lignes de bit dans le dispositif. Dans un autre mode de réalisation, les première (63) et deuxième (65) régions de drain du circuit CMOS de chaque cellule d'une rangée sont connectées à une première ligne de bit, tandis que la couche conductrice (73) de la structure de grille de chaque cellule de la même rangée est connectée à une deuxième ligne de bit, lesdites lignes de bit étant connectées au générateur de puissance et aux moyens de commande. Dans un mode de réalisation, chaque cellule du dispositif peut être programmée ou effacée ou lue de manière sélective.

Les hommes du métier comprendront que chaque cellule du dispositif est entourée d'un matériau isolé afin d'isoler électriquement les cellules les unes des autres. Ainsi, seules les lignes de bit (9) peuvent connecter les unes aux autres les première (63) et deuxième (65) régions de drain du circuit CMOS et/ou la région de drain (73) du transistor de sélection de chaque cellule d'une rangée.

Autrement dit, il est possible de programmer ou d'effacer n'importe quelle cellule du dispositif en ouvrant le transistor de sélection, c'est-à-dire en appliquant une tension positive à la couche conductrice (71) de la structure de grille du transistor de sélection et une tension à la région de

drain (73) du transistor de sélection, ladite tension étant positive pour un effacement ou négative pour une programmation. Ainsi, même si un potentiel positif est appliqué à la région de drain (73) du transistor de sélection de chaque cellule d'une rangée dans le dispositif (parce que les régions de drain (73) des cellules d'une rangée sont connectées à la même ligne de bit), un transistor de sélection d'une cellule individuelle ne peut être ouvert que si un potentiel est appliqué à la couche conductrice (71) de la structure de grille du transistor de sélection. De cette manière, la programmation ou l'effacement d'une cellule de mémoire non volatile ne perturbe pas les cellules voisines du dispositif de mémoire non volatile.

Il est également possible de lire n'importe quelle cellule du dispositif en fermant le transistor de sélection, c'est-à-dire en appliquant un potentiel de 0 volt à la couche conductrice (71) de la structure de grille, alors, quel que soit le potentiel de la région de drain (73) du transistor de sélection, le potentiel de la région de source (72) du transistor de sélection reste invariant. Ainsi, aucune programmation ou aucun effacement n'est possible. De plus, pour toute cellule devant être lue, un potentiel positif est appliqué à la deuxième région de source (64) du circuit CMOS et un potentiel de 0 volt est appliqué à la première région de source (62) du circuit CMOS de ladite cellule. Et pour toute cellule qui ne doit pas être lue dans la même ligne, aucun potentiel n'est appliqué aux première et deuxième régions de source (62, 64) du circuit CMOS de ladite cellule, de sorte que la lecture d'une cellule n'est pas perturbée par les cellules voisines du dispositif de mémoire non volatile.

La présente invention a été décrite avec référence au mode de réalisation préféré. On doit comprendre que le type des régions semi-conductrices, l'agencement du dispositif et la polarité des tensions sont choisis uniquement à des fins d'illustration, et un homme du métier reconnaîtrait d'autres variantes, changements et modifications. Par exemple, toutes les caractéristiques techniques présentées dans le texte de la description peuvent être appliquées à des cellules de mémoire non volatile

comprenant une structure de grille flottante réalisée selon le processus connu de réalisation de grille flottante double en silicium polycristallin.

#### REVENDICATIONS

- 1. Cellule de mémoire non volatile, caractérisée en ce qu'elle comprend :

- au moins un substrat en silicium dopé (4), séparé physiquement et électriquement en deux sections (41, 42) par une partie de substrat dopé (3) dont le dopage est opposé à celui du substrat en silicium dopé,

10

15

20

- au moins trois composants isolés (81, 82, 83) insérés chacun dans une tranchée, la première tranchée étant fabriquée dans la première section (41) du substrat en silicium dopé, les deuxième et troisième tranchées étant fabriquées dans la partie de substrat dopée (3) et étant respectivement adjacentes aux première (41) et deuxième (42) sections du substrat en silicium dopé, les premier (81) et deuxième (82) composants isolés étant séparés par la première section (41) du substrat en silicium dopé, les deuxième (82) et troisième (83) composants isolés étant séparés par la partie de substrat dopée (3),

- au moins deux couches de silicium (51, 52) dont le dopage est opposé à celui du substrat en silicium (4), une première couche de silicium (51) recouvrant au moins partiellement la première section (41) du substrat en silicium et une deuxième couche de silicium (52) recouvrant au moins partiellement la deuxième section (42) du substrat en silicium,

- une région de source (72) et une région de drain (73) avec un canal induit entre les deux régions, l'une de ces régions (72) étant adjacente à la première couche de silicium (51), une structure de grille comprenant une couche diélectrique (70) et une couche conductrice (71) étant placée au moins au-dessus du canal, la première section du substrat en silicium (41), les régions de source (72) et de drain (73) et la structure de grille formant un transistor de sélection pour permettre la circulation d'électrons au moins dans la première couche de silicium (51),

- une structure de grille flottante au-dessus des deux couches de silicium (51, 52), ladite structure comprenant au moins une mince couche diélectrique (60) et au moins une couche conductrice (61),

- un circuit de transistor à effet de champ CMOS comprenant :

5

15

20

25

- une première région de source (62) et une première région de drain (63) avec un canal induit entre les deux régions, ces régions étant respectivement adjacentes aux premier (81) et deuxième (82) composants isolés, le dopage des régions étant différent de celui du substrat en silicium (4),

- une deuxième région de source (64) et une deuxième région de drain (65) avec un canal induit entre les deux régions, ces régions étant respectivement adjacentes aux deuxième (82) et troisième (83) composants isolés, les régions ayant le même dopage que le substrat en silicium dopé (4).

- 2. Cellule de mémoire non volatile selon la revendication 1, caractérisée en ce qu'au moins une partie de la couche diélectrique et une partie de la couche conductrice placées au-dessus de la première couche de silicium (51) ont une forme en marche d'escalier.

- 3. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 et 2, caractérisée en ce que la première section (41) du substrat en silicium dopé a une forme en marche d'escalier.

- 4. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 3, caractérisée en ce que l'angle de la forme en marche d'escalier formée dans la couche diélectrique (60) de la structure de grille flottante est compris entre 30° et 180°, de préférence entre 30° et 90° lorsqu'il est mesuré à partir d'une direction parallèle à la surface du substrat.

- 5. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 4, caractérisée en ce que la deuxième couche de silicium (52) est un conducteur électrique d'un condensateur, l'autre conducteur électrique étant la couche conductrice (62) de la structure de grille flottante.

- 6. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 5, caractérisée en ce que le substrat en silicium (4) est de puits dopés P.

- 7. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 6, caractérisée en ce que les régions de drain (73) et de source (72) du transistor de sélection sont dopées N+.

5

10

15

20

- 8. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 7, caractérisée en ce que la première région de drain (63) et la première région de source (62) du circuit CMOS sont dopées N+, tandis que la deuxième région de drain (65) et la deuxième région de source (64) du circuit CMOS sont dopées P+.

- 9. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 8, caractérisée en ce que les deux sections (41, 42) du substrat en silicium et la partie de substrat dopée (3) se trouvent sur une région de puits dopés N profonds afin d'isoler électriquement les deux sections du substrat en silicium.

- 10. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 9, caractérisée en ce que la couche conductrice (71) de la structure de grille et la couche conductrice (61) de la structure de grille flottante sont faites de silicium polycristallin.

- 11. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 10, caractérisée en ce que les composants isolés (81, 82, 83), la couche diélectrique (70) de la structure de grille et la couche diélectrique (60) de la structure de grille flottante sont faits d'oxyde de silicium.

- 12. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 11, caractérisée en ce que l'épaisseur de la couche diélectrique (60) d'au moins la structure de grille flottante est constante, la valeur de l'épaisseur étant comprise entre 50 et 200 angströms.

13. Cellule de mémoire non volatile selon l'une quelconque des revendications 1 à 12, caractérisée en ce que l'épaisseur et la forme en marche d'escalier de la couche diélectrique (60) de la structure de grille flottante permettent la diminution de la tension de programmation et/ou d'effacement de la couche conductrice (61) de la structure de grille flottante, de sorte que ladite tension de programmation et/ou d'effacement soit compatible avec la tension requise pour faire fonctionner le circuit CMOS.

5

10

15

20

25

- 14. Procédé pour programmer une cellule de mémoire non volatile selon les revendications 1 à 13, la cellule étant connectée à des moyens de commande (CM) commandant ladite cellule et à un générateur de puissance (EG) connecté à la cellule, caractérisé par l'injection d'électrons de la première couche de silicium (51) vers la couche conductrice (61) de la structure de grille flottante à travers le haut (T) de la forme en marche d'escalier de la couche diélectrique (51), le procédé comprenant :

- l'étape d'application d'un potentiel positif à la couche conductrice (71) de la structure de grille et à la deuxième couche de silicium (52) grâce au générateur de puissance, induisant la polarisation de la couche conductrice (61) de la structure de grille flottante par effet de couplage capacitif,

- l'étape d'application d'un potentiel négatif à la région de drain (73) du transistor de sélection et à la première section (41) du substrat en silicium dopé grâce au générateur de puissance connecté à ladite région de drain et à la première section (41) du substrat en silicium, induisant la circulation d'électrons de la région de drain (73) vers la région de source (72) du transistor de sélection, ladite circulation d'électrons polarisant négativement la première couche de silicium (51) adjacente à la région de source (72) du transistor de sélection,

la deuxième section (42) du substrat en silicium dopé et la partie de substrat dopée (3) étant polarisées à 0 volt.

15. Procédé pour effacer une cellule de mémoire non volatile selon les revendications 1 à 13, la cellule étant connectée à des moyens de commande commandant ladite cellule et à un générateur de puissance connecté à la cellule, caractérisé par l'injection d'électrons de la couche conductrice (61) de la structure de grille flottante vers la première couche de silicium (51) à travers le bas (B) de la forme en marche d'escalier de la couche diélectrique (51), le procédé comprenant :

5

10

15

25

- l'étape d'application d'un potentiel négatif à la deuxième section (42) du substrat en silicium dopé et à la deuxième couche de silicium (52) grâce au générateur de puissance, induisant la polarisation de la couche conductrice (61) de la structure de grille flottante par effet de couplage capacitif,

- l'étape d'application d'un potentiel positif à la couche conductrice (71) de la structure de grille et à la région de drain (73) du transistor de sélection grâce au générateur de puissance connecté à ladite couche conductrice et à ladite région de drain, induisant la polarisation positive de la première couche de silicium (51) adjacente à la région de source (72) du transistor de sélection,

la première section (41) du substrat en silicium dopé et la partie de 20 substrat dopée (3) étant polarisées à 0 volt.

16. Procédé pour lire une cellule de mémoire non volatile selon les revendications 1 à 13, caractérisé par la détection de l'état logique du circuit CMOS grâce à des moyens de commande, la partie de substrat dopée (3) et la deuxième région de source (64) du circuit CMOS étant polarisées à un potentiel positif V<sub>dd</sub> connu, grâce au générateur de puissance commandé par les moyens de commande, les deux sections (41, 42) du substrat en silicium dopé, la deuxième couche de silicium (52) et la première région de source (62) du circuit CMOS étant polarisées à 0 volt, la variation de la tension de sortie V<sub>out</sub> du circuit CMOS étant lue par les moyens de commande, ladite

tension de sortie étant le potentiel des première (63) et deuxième (65) régions de drain du circuit CMOS.

17. Dispositif de mémoire non volatile, caractérisé en ce qu'il comprend une pluralité de cellules de mémoire non volatile selon l'une quelconque des revendications 1 à 13, ladite pluralité de cellules formant une matrice de N rangées et M colonnes.

5

10

- 18. Dispositif de mémoire non volatile selon la revendication 17, caractérisé en ce que les première (63) et deuxième (65) régions de drain du circuit CMOS et la couche conductrice (71) de la structure de grille de chaque cellule d'une rangée sont connectées à une seule ligne de bit (9), ladite ligne de bit étant connectée au générateur de puissance et aux moyens de commande.

- 19. Dispositif de mémoire non volatile selon la revendication 17, caractérisé en ce que les première (63) et deuxième (65) régions de drain du circuit CMOS de chaque cellule d'une rangée sont connectées à une première ligne de bit, tandis que la couche conductrice (71) de la structure de grille de chaque cellule de la même rangée est connectée à une deuxième ligne de bit, lesdites lignes de bit étant connectées au générateur de puissance et aux moyens de commande.

- 20. Dispositif de mémoire non volatile selon l'une quelconque des revendications 17 à 19, caractérisé en ce que chaque cellule du dispositif peut être programmée, effacée ou lue de manière sélective et de manière indépendante.

FIGURE 1b

FIGURE 3

FIGURE 4

#### **RAPPORT DE RECHERCHE** PRÉLIMINAIRE

N° d'enregistrement national

FA 789713 FR 1359053

établi sur la base des dernières revendications déposées avant le commencement de la recherche

|          | IMENTS CONSIDÉRÉS COMME PERTINENTS                                                                                                                                                             | concernée(s) | à l'invention par l'INPI                       |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------|--|

| atégorie | Citation du document avec indication, en cas de besoin,<br>des parties pertinentes                                                                                                             |              |                                                |  |

| Υ        | US 2012/037971 A1 (KWON OH-KYUM [KR] ET<br>AL) 16 février 2012 (2012-02-16)<br>* colonnes 76-85; figures 13, 14 *                                                                              | 1-20         | H01L27/115                                     |  |

| Y        | US 5 587 945 A (LIN JONATHAN [US] ET AL)<br>24 décembre 1996 (1996-12-24)<br>* colonne 1, ligne 17 - ligne 37; figure 1                                                                        | 1-20         |                                                |  |

| Y        | US 2009/065838 A1 (NAGAO TAKESHI [JP])<br>12 mars 2009 (2009-03-12)<br>* alinéas [0005] - [0008], [0037] -<br>[0045]; figure 3 *                                                               | 2-4          |                                                |  |

| A        | US 5 272 368 A (TURNER JOHN E [US] ET AL)<br>21 décembre 1993 (1993-12-21)<br>* colonne 2, ligne 41 - colonne 3, ligne<br>40; figure 1 *                                                       | 1-20         |                                                |  |

| A        | US 5 892 709 A (PARRIS PATRICE M [US] ET AL) 6 avril 1999 (1999-04-06) * colonne 2, ligne 10 - ligne 47; figures 1,3,5 * * colonne 7, ligne 50 - ligne 63 * * colonne 8, ligne 36 - ligne 55 * | 1-20         | DOMAINES TECHNIQUES RECHERCHÉS (IPC) H01L G11C |  |

|          | Date d'achèvement de la recherche                                                                                                                                                              |              | Examinateur                                    |  |

|          | 20 juin 2014                                                                                                                                                                                   | Mos          | ig, Karsten                                    |  |

1 EPO FORM 1503 12.99 (P04C14)

- autre document de la même catégorie

A : arrière-plan technologique

O : divulgation non-écrite

P : document intercalaire

- de dépôt ou qu'à une date postérieure. D : cité dans la demande

- L : cité pour d'autres raisons

- & : membre de la même famille, document correspondant

### ANNEXE AU RAPPORT DE RECHERCHE PRÉLIMINAIRE RELATIF A LA DEMANDE DE BREVET FRANÇAIS NO. FR 1359053 FA 789713

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche préliminaire visé ci-dessus.

Les dits membres sont contenus au fichier informatique de l'Office européen des brevets à la date du20-06-2014 Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets, ni de l'Administration française

| Document brevet cité<br>au rapport de recherche |    | Date de publication |                | Membre(s) de la<br>famille de brevet(s |   | Date de<br>publication                 |

|-------------------------------------------------|----|---------------------|----------------|----------------------------------------|---|----------------------------------------|

| US 2012037971                                   | A1 | 16-02-2012          | US<br>US       | 2012037971<br>2014035017               |   | 16-02-2012<br>06-02-2014               |

| US 5587945                                      | Α  | 24-12-1996          | AUCI           | JN                                     |   |                                        |

| US 2009065838                                   | A1 | 12-03-2009          | JP<br>US       | 2009070943<br>2009065838               |   | 02-04-2009<br>12-03-2009               |

| US 5272368                                      | Α  | 21-12-1993          | EP<br>JP<br>US | 0515039<br>H0697453<br>5272368         | A | 25-11-1992<br>08-04-1994<br>21-12-1993 |

| US 5892709                                      | Α  | 06-04-1999          | JP<br>JP<br>US | 4463334<br>H10335505<br>5892709        | Α | 19-05-2010<br>18-12-1998<br>06-04-1999 |