## (12) 发明专利

(10) 授权公告号 CN 111048551 B

(45) 授权公告日 2025.05.13

(21) 申请号 201910716259.9

(51) Int.CI.

(22) 申请日 2019.08.05

H10K 59/121 (2023.01)

(65) 同一申请的已公布的文献号

H10K 59/123 (2023.01)

申请公布号 CN 111048551 A

H10K 59/131 (2023.01)

H10K 59/80 (2023.01)

(43) 申请公布日 2020.04.21

(56) 对比文件

(30) 优先权数据

US 2017148856 A1, 2017.05.25

10-2018-0121197 2018.10.11 KR

US 2018145115 A1, 2018.05.24

(73) 专利权人 三星显示有限公司

审查员 金政

地址 韩国京畿道龙仁市

(72) 发明人 崔原瑀 成宇镛 金秀燕 徐政汉

李抒娟 李亨燮 张文源 蔡昇根

(74) 专利代理机构 北京铭硕知识产权代理有限公司 11286

专利代理人 张晓 尹淑梅

权利要求书4页 说明书16页 附图18页

## (54) 发明名称

显示面板

## (57) 摘要

提供了一种显示面板。所述显示面板包括：多个显示元件，布置在显示区域中；开口；多层，包括第一层和设置在第一层上的第二层；以及凹槽。每个显示元件包括像素电极、设置在像素电极上的发射层和设置在发射层上的对电极。显示区域围绕开口。凹槽位于开口与显示区域之间。凹槽在多层的厚度方向上具有凹的底切剖面，第二层包括朝向凹槽的中心突出的一对尖端，并且每个尖端的长度小于约 $2\mu m$ 。

1. 一种显示面板,所述显示面板包括:

多个显示元件,布置在显示区域中,其中,每个显示元件包括像素电极、设置在所述像素电极上的发射层和设置在所述发射层上的对电极;

开口,其中,所述显示区域围绕所述开口;

多层,包括第一层和设置在所述第一层上的第二层;以及

凹槽,位于所述开口与所述显示区域之间,

其中,所述凹槽在所述多层的厚度方向上具有凹的底切割面,所述第二层包括朝向所述凹槽的中心突出的一对尖端,并且每个尖端的长度等于或大于 $0.3\mu\text{m}$ 并且小于 $2\mu\text{m}$ 。

2. 如权利要求1所述的显示面板,其中,所述第一层包括有机材料,并且所述第二层包括无机材料。

3. 如权利要求2所述的显示面板,其中,所述第二层包括无机绝缘层或金属层。

4. 如权利要求1所述的显示面板,其中,所述凹槽包括:

第一孔或第一凹部,形成在所述第一层中;以及

第二孔,形成在所述第二层中,

其中,所述第二孔连接到所述第一孔或所述第一凹部。

5. 如权利要求4所述的显示面板,其中,所述一对尖端之间的距离大于所述第一孔或所述第一凹部的深度。

6. 如权利要求4所述的显示面板,其中,所述第一孔或所述第一凹部的深度大于所述每个尖端的所述长度。

7. 如权利要求6所述的显示面板,其中,所述每个尖端的所述长度相对于所述第一孔或所述第一凹部的所述深度为 $0.05 < (\ell/dp) < 0.50$ ,并且

其中,  $\ell$  是所述每个尖端的所述长度,并且  $dp$  是所述第一孔或所述第一凹部的所述深度。

8. 如权利要求4所述的显示面板,其中,所述第一孔或所述第一凹部的深度等于或小于所述第一层的厚度。

9. 如权利要求4所述的显示面板,所述显示面板还包括:

第一功能层,设置在所述像素电极与所述发射层之间;和/或第二功能层,设置在所述发射层与所述对电极之间,

其中,所述第一功能层和/或所述第二功能层在所述一对尖端周围断开,并且所述对电极在所述一对尖端周围断开,并且

其中,所述第一孔或所述第一凹部的深度比所述第一功能层和/或所述第二功能层的厚度以及所述对电极的厚度的总和大。

10. 如权利要求9所述的显示面板,所述显示面板还包括:

盖层,设置在所述对电极上,

其中,所述第一孔或所述第一凹部的所述深度比所述第一功能层和/或所述第二功能层的所述厚度、所述对电极的所述厚度以及所述盖层的厚度的总和大。

11. 如权利要求1所述的显示面板,所述显示面板还包括:

基底;以及

像素电路,设置在所述基底上,

其中,所述像素电路包括电连接到所述像素电极的薄膜晶体管。

12. 如权利要求11所述的显示面板,其中,所述基底包括所述多层。

13. 如权利要求11所述的显示面板,其中,所述多层设置在所述基底上。

14. 一种显示面板,所述显示面板包括:

开口;

多个显示元件,其中,每个显示元件包括像素电极、发射层和对电极,其中,所述多个显示元件位于围绕所述开口的显示区域中;

多层,包括第一层和设置在所述第一层上的第二层;以及

凹槽,位于所述开口与所述显示区域之间并且具有底切剖面,

其中,所述凹槽设置在所述多层的厚度方向上,所述第二层包括朝向所述凹槽的中心突出的一对尖端,并且所述凹槽的穿过所述第一层的部分的深度大于每个尖端的长度,并且

其中,所述每个尖端的所述长度等于或大于 $0.3\mu\text{m}$ 并且小于 $2\mu\text{m}$ 。

15. 如权利要求14所述的显示面板,其中,所述深度等于或小于所述第一层的厚度。

16. 如权利要求15所述的显示面板,其中,所述一对尖端之间的距离大于所述深度。

17. 如权利要求14所述的显示面板,其中,所述每个尖端的所述长度相对于所述深度为 $0.05 < (\ell/dp) < 0.50$ ,并且

其中,  $\ell$  是所述每个尖端的所述长度,并且  $dp$  是所述深度。

18. 如权利要求14所述的显示面板,所述显示面板还包括:

第一功能层,设置在所述像素电极与所述发射层之间;和/或第二功能层,设置在所述发射层与所述对电极之间,

其中,所述第一功能层和/或所述第二功能层在所述一对尖端周围断开,并且所述对电极在所述一对尖端周围断开,并且

其中,所述深度比所述第一功能层和/或所述第二功能层的厚度以及所述对电极的厚度的总和大。

19. 如权利要求18所述的显示面板,所述显示面板还包括:

盖层,设置在所述对电极上,

其中,所述深度比所述第一功能层和/或所述第二功能层的所述厚度、所述对电极的所述厚度以及所述盖层的厚度的总和大。

20. 如权利要求14所述的显示面板,其中,所述深度为 $2\mu\text{m}$ 或更大。

21. 如权利要求14所述的显示面板,所述显示面板还包括:

基底;以及

像素电路,设置在所述基底上,

其中,所述像素电路包括电连接到所述像素电极的薄膜晶体管。

22. 如权利要求21所述的显示面板,其中,所述基底包括所述多层。

23. 如权利要求21所述的显示面板,其中,所述多层设置在所述基底上。

24. 一种显示面板,所述显示面板包括:

基底,具有开口;

多个发光二极管,布置在围绕所述开口的显示区域中;

封装层,在所述多个发光二极管上,所述封装层包括第一无机封装层、在所述第一无机封装层上的有机封装层和在所述有机封装层上的第二无机封装层;以及

多层结构,设置在所述开口与所述显示区域之间,

其中,所述多层结构包括:第一层;以及第二层,在所述第一层上方,所述第二层具有尖端,所述尖端在平行于所述基底的顶表面上的水平方向上突出超过所述第一层的侧表面与所述第二层的底表面相遇的点,其中,所述尖端的长度等于或大于 $0.3\mu\text{m}$ 并且小于 $2\mu\text{m}$ ,并且所述长度是所述点与所述尖端的侧表面之间的距离。

25. 如权利要求24所述的显示面板,其中:

所述第一层的材料不同于所述第二层的材料。

26. 如权利要求25所述的显示面板,其中,所述第二层包括金属层。

27. 如权利要求24所述的显示面板,其中:

所述第二层的厚度小于所述第一层的厚度。

28. 如权利要求24所述的显示面板,其中,所述多个发光二极管中的每个包括:

像素电极;

发射层,与所述像素电极叠置;

对电极的一部分,所述对电极对应于所述多个发光二极管;以及

功能层的一部分,在所述像素电极与所述对电极的所述一部分之间,所述功能层对应于所述多个发光二极管。

29. 如权利要求28所述的显示面板,其中:

所述功能层和所述对电极中的每个被所述第二层的所述尖端断开。

30. 如权利要求29所述的显示面板,其中:

所述第一层的厚度大于所述功能层的厚度和所述对电极的厚度的总和。

31. 如权利要求29所述的显示面板,其中:

所述功能层和所述对电极的部分在所述第二层的顶表面上并且被所述第一无机封装层覆盖。

32. 如权利要求31所述的显示面板,其中:

所述第一无机封装层延伸以连续地覆盖所述尖端的所述侧表面和底表面以及所述第一层的所述侧表面。

33. 如权利要求29所述的显示面板,其中:

所述有机封装层分别与被所述尖端断开的所述功能层和所述对电极叠置。

34. 如权利要求28所述的显示面板,其中:

所述功能层包括从空穴传输层、空穴注入层、电子传输层和电子注入层中选择的一个或更多个。

35. 一种显示面板,所述显示面板包括:

基底,具有开口;

多个发光二极管,布置在围绕所述开口的显示区域中;

封装层,在所述多个发光二极管上;以及

多层结构,设置在所述开口与所述显示区域之间,其中,所述多层结构包括:第一层;以

及第二层,在所述第一层上方,其中,所述第二层的厚度小于所述第一层的厚度,其中:

所述第二层具有尖端,所述尖端在平行于所述基底的顶表面上的水平方向上突出超过所述第一层的侧表面与所述第二层的底表面相遇的点,并且

所述尖端的长度等于或大于 $0.3\mu\text{m}$ 并且小于 $2\mu\text{m}$ ,并且所述长度是所述点与所述尖端的侧表面之间的距离。

36. 如权利要求35所述的显示面板,其中:

所述第一层的材料不同于所述第二层的材料,并且

所述第二层包括金属层。

37. 如权利要求35所述的显示面板,其中,所述多个发光二极管中的每个包括:

像素电极;

发射层,与所述像素电极叠置;

对电极的一部分,所述对电极对应于所述多个发光二极管;以及

功能层的一部分,在所述像素电极与所述对电极的所述一部分之间,所述功能层对应于所述多个发光二极管。

38. 如权利要求37所述的显示面板,其中:

所述功能层和所述对电极中的每个被所述第二层的所述尖端断开。

39. 如权利要求38所述的显示面板,其中:

所述第一层的厚度大于所述功能层的厚度和所述对电极的厚度的总和。

40. 如权利要求38所述的显示面板,其中,所述封装层包括:

第一无机封装层,以及

有机封装层,在所述第一无机封装层上,

其中,所述第一无机封装层覆盖所述功能层和所述对电极的在所述第二层的顶表面上的部分,并且延伸以连续地覆盖所述尖端的所述侧表面和底表面以及所述第一层的所述侧表面。

41. 如权利要求40所述的显示面板,其中:

所述有机封装层分别与被所述尖端断开的所述功能层和所述对电极叠置。

42. 如权利要求38所述的显示面板,其中:

所述功能层包括从空穴传输层、空穴注入层、电子传输层和电子注入层中选择的一个或更多个。

43. 一种电子装置,所述电子装置包括:

根据权利要求1至42中任一项所述的显示面板;以及

组件,与所述显示面板的开口对应,

其中,所述组件包括相机或传感器。

## 显示面板

[0001] 本申请要求于2018年10月11日在韩国知识产权局提交的第10-2018-0121197号韩国专利申请的优先权，该韩国专利申请的公开内容通过引用全部包含于此。

### 技术领域

[0002] 示例性实施例涉及一种包括凹槽的显示面板和一种包括该显示面板的显示装置。

### 背景技术

[0003] 随着显示装置已变得越来越薄且越来越轻，它们的使用范围日益增大。

[0004] 随着由显示装置的显示区域占据的区域增大，正在添加可以与显示装置组合或相关联的功能。作为在增大显示区域的同时添加各种功能的方式，正在研究在显示区域中包括开口的显示装置。

### 发明内容

[0005] 在包括开口的显示装置中，诸如湿气的异物可能穿过开口的侧面进行渗透。在这种情况下，与开口相邻的显示元件会被损坏。

[0006] 示例性实施例包括一种具有可以防止湿气穿过开口的结构的显示面板和一种包括所述显示面板的显示装置。

[0007] 根据示例性实施例，一种显示面板包括布置在显示区域中的多个显示元件。每个显示元件包括像素电极、设置在像素电极上的发射层以及设置在发射层上的对电极。显示面板还包括开口。显示区域围绕开口。显示面板还包括：多层，包括第一层和设置在第一层上的第二层；以及凹槽，位于开口与显示区域之间。凹槽在多层的厚度方向上具有凹的底切剖面，第二层包括朝向凹槽的中心突出的一对尖端，并且每个尖端的长度小于约 $2\mu\text{m}$ 。

[0008] 在示例性实施例中，每个尖端的长度约等于或大于约 $0.3\mu\text{m}$ 并且小于约 $2\mu\text{m}$ 。

[0009] 在示例性实施例中，第一层包括有机材料，并且第二层包括无机材料。

[0010] 在示例性实施例中，第二层包括无机绝缘层或金属层。

[0011] 在示例性实施例中，凹槽包括：第一孔或第一凹部，形成在第一层中；以及第二孔，形成在第二层中。第二孔连接到第一孔或第一凹部。

[0012] 在示例性实施例中，一对尖端之间的距离大于第一孔或第一凹部的深度。

[0013] 在示例性实施例中，第一孔或第一凹部的深度大于每个尖端的长度。

[0014] 在示例性实施例中，每个尖端的长度相对于第一孔或第一凹部的深度为约 $0.05 < (\ell/d\text{p}) < 0.50$ ，其中， $\ell$ 是每个尖端的长度，并且 $d\text{p}$ 是第一孔或第一凹部的深度。

[0015] 在示例性实施例中，第一孔或第一凹部的深度约等于或小于第一层的厚度。

[0016] 在示例性实施例中，显示面板还包括：第一功能层，设置在像素电极与发射层之间；和/或第二功能层，设置在发射层与对电极之间。第一功能层和/或第二功能层在一对尖端周围断开，并且对电极在一对尖端周围断开。第一孔或第一凹部的深度比第一功能层和/或第二功能层的厚度以及对电极的厚度的总和大。

- [0017] 在示例性实施例中,显示面板还包括设置在对电极上的盖层。第一孔或第一凹部的深度比第一功能层和/或第二功能层的厚度、对电极的厚度以及盖层的厚度的总和大。

- [0018] 在示例性实施例中,显示面板还包括基底和设置在基底上的像素电路。像素电路包括电连接到像素电极的薄膜晶体管。

- [0019] 在示例性实施例中,基底包括多层。

- [0020] 在示例性实施例中,多层设置在基底上。

- [0021] 根据示例性实施例,一种显示面板包括开口和多个显示元件。每个显示元件包括像素电极、发射层和对电极。多个显示元件位于围绕开口的显示区域中。显示面板还包括:多层,包括第一层和设置在第一层上的第二层;以及凹槽,位于开口与显示区域之间并且具有底切剖面。凹槽设置在多层的厚度方向上,第二层包括朝向凹槽的中心突出的一对尖端,并且凹槽的穿过第一层的部分的深度大于每个尖端的长度。

- [0022] 在示例性实施例中,每个尖端的长度约等于或大于约 $0.3\mu\text{m}$ 并且小于约 $2\mu\text{m}$ 。

- [0023] 在示例性实施例中,所述深度约等于或小于第一层的厚度。

- [0024] 在示例性实施例中,一对尖端之间的距离大于所述深度。

- [0025] 在示例性实施例中,每个尖端的长度相对于所述深度为约 $0.05 < (\ell/d_p) < 0.50$ ,其中, $\ell$ 是每个尖端的长度,并且 $d_p$ 是深度。

- [0026] 在示例性实施例中,显示面板还包括:第一功能层,设置在像素电极与发射层之间;和/或第二功能层,设置在发射层与对电极之间。第一功能层和/或第二功能层在一对尖端周围断开,并且对电极在一对尖端周围断开。所述深度比第一功能层和/或第二功能层的厚度以及对电极的厚度的总和大。

- [0027] 在示例性实施例中,显示面板还包括设置在对电极上的盖层。所述深度比第一功能层和/或第二功能层的厚度、对电极的厚度以及盖层的厚度的总和大。

- [0028] 在示例性实施例中,所述深度为约 $2\mu\text{m}$ 或更大。

- [0029] 在示例性实施例中,显示面板还包括基底和设置在基底上的像素电路。像素电路包括电连接到像素电极的薄膜晶体管。

- [0030] 在示例性实施例中,基底包括多层。

- [0031] 在示例性实施例中,多层设置在基底上。

## 附图说明

- [0032] 通过参照附图详细描述本公开的示例性实施例,本公开的以上和其它特征将变得更明显,在附图中:

- [0033] 图1是根据示例性实施例的显示装置的透视图;

- [0034] 图2是根据示例性实施例的显示装置的剖视图;

- [0035] 图3是根据示例性实施例的显示面板的平面图;

- [0036] 图4是显示面板的多个像素中的一个像素的等效电路图;

- [0037] 图5是根据示例性实施例的位于显示面板的非显示区域中的信号线的视图;

- [0038] 图6是根据示例性实施例的位于显示面板的第一非显示区域中的凹槽的视图;

- [0039] 图7是根据示例性实施例的显示面板的多个像素中的一个像素的剖视图;

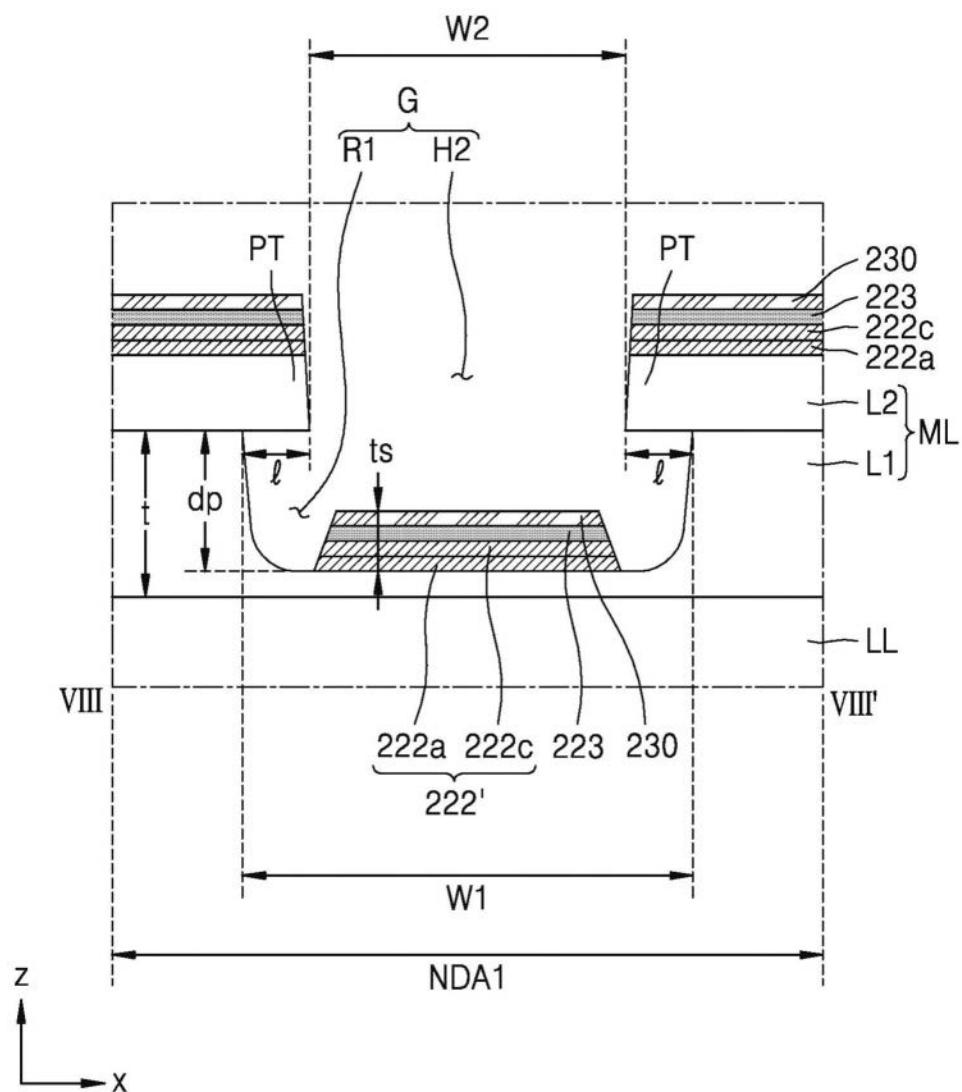

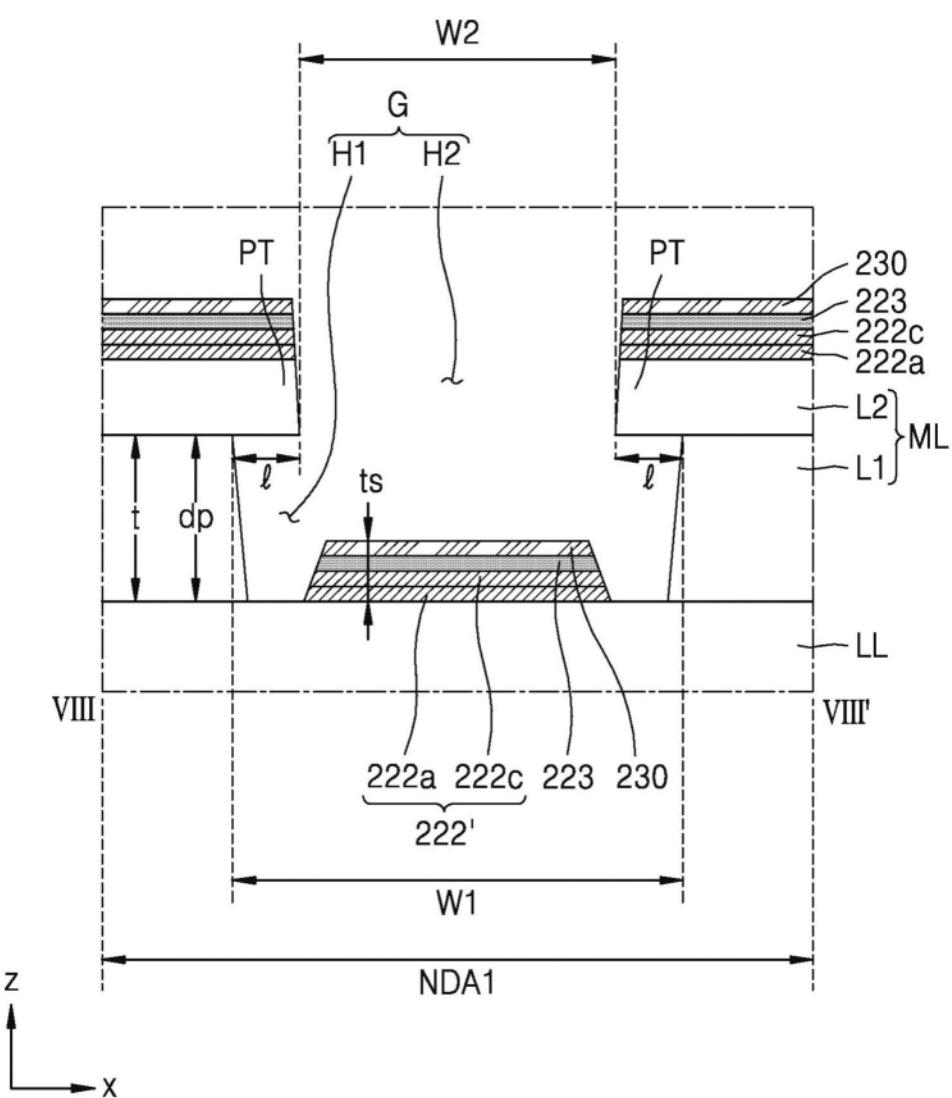

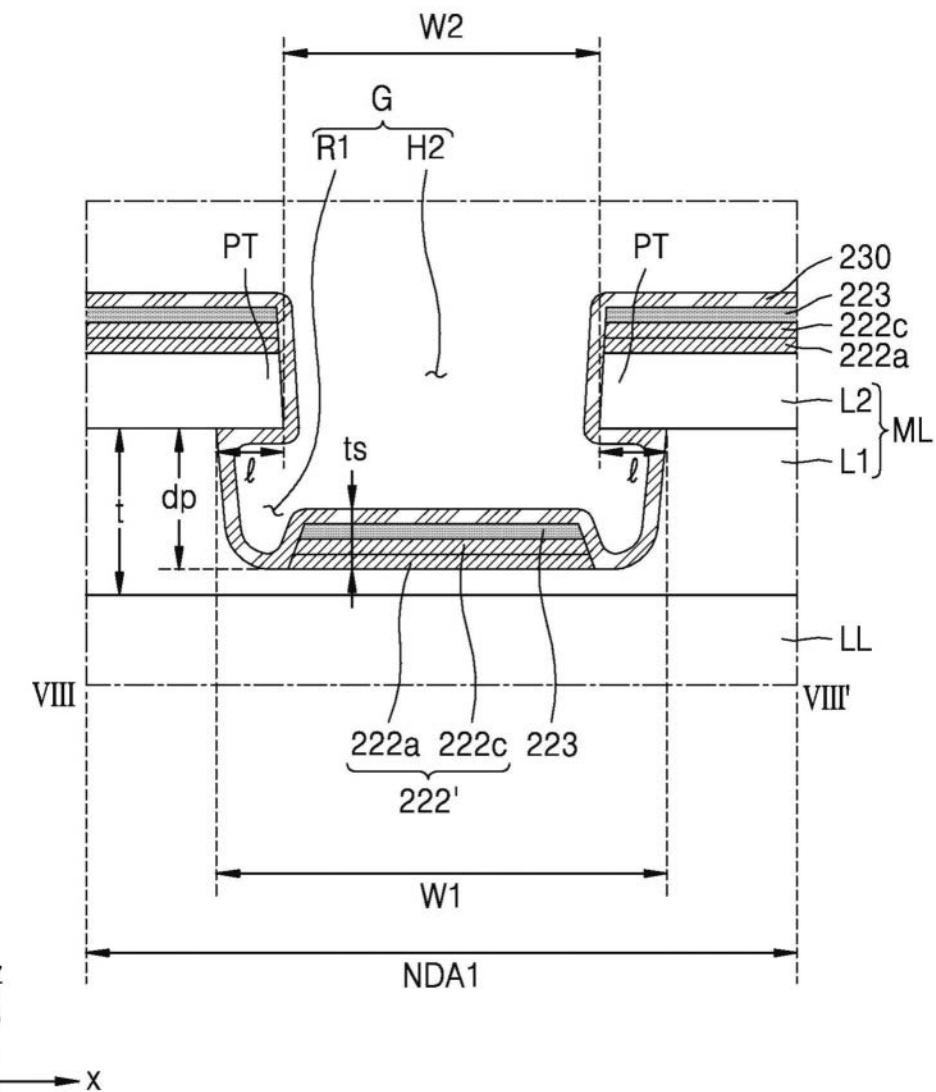

- [0040] 图8A至图8D是根据示例性实施例的显示面板的凹槽的剖视图;

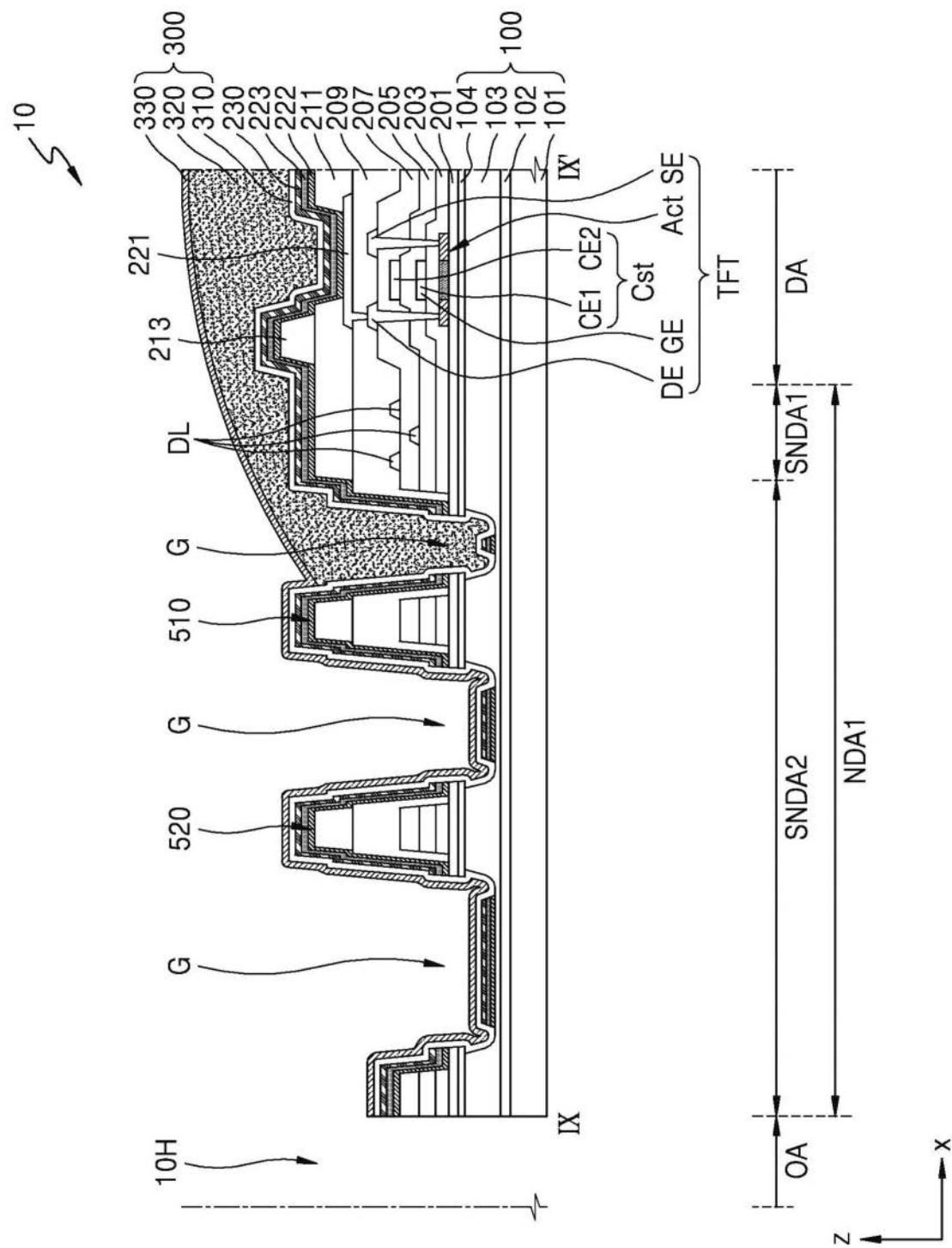

- [0041] 图9是根据示例性实施例的显示面板的剖视图；

- [0042] 图10是根据示例性实施例的显示面板的凹槽的剖视图；

- [0043] 图11是根据示例性实施例的显示面板的凹槽的剖视图；

- [0044] 图12是根据示例性实施例的显示面板的凹槽的剖视图；

- [0045] 图13是根据示例性实施例的显示面板的凹槽的剖视图；

- [0046] 图14是根据示例性实施例的显示面板的凹槽的剖视图；

- [0047] 图15是根据示例性实施例的布置在显示面板的第一非显示区域中的凹槽的剖视图；

- [0048] 图16是根据示例性实施例的布置在显示面板的第一非显示区域中的凹槽的剖视图；以及

- [0049] 图17是根据示例性实施例的显示面板的剖视图。

### 具体实施方式

[0050] 在下文中将参照附图来更充分地描述本公开的示例性实施例。贯穿附图，同样的附图标记可以表示同样的元件。

[0051] 如这里所使用的，术语“和/或”包括相关所列项中的一个或更多个的任何组合和所有组合。例如，“a、b和c中的至少一个(种/者)”可以被理解为指仅a、仅b、仅c、a和b两者、a和c两者、b和c两者以及a、b和c的全部或它们的变型。

[0052] 将理解的是，术语“第一”、“第二”、“第三”等在这里用于将一个元件与另一元件区分开，并且元件不受这些术语的限制。因此，示例性实施例中的“第一”元件可以在另一示例性实施例中被描述为“第二”元件。

[0053] 如这里所使用的，除非上下文另外清楚地指出，否则单数形式“一”、“一个(种/者)”和“该(所述)”也意图包括复数形式。

[0054] 为了易于描述，在这里可以使用诸如“在……之下”、“在……下方”、“下”“在……下面”、“在……上方”、“上”等的空间相对术语来描述如附图中示出的一个元件或特征与另一(其它)元件或特征的关系。将理解的是，空间相对术语意图包括除了附图中描绘的方位之外的装置在使用或操作中的不同方位。例如，如果附图中的装置被翻转，则被描述为“在”其它元件或特征“下方”或“之下”或者“下面”的元件随后将被定位为“在”所述其它元件或特征“上方”。因此，示例性术语“在……下方”和“在……下面”可以包含上方和下方两种方位。

[0055] 将理解的是，当诸如膜、区域、层或元件的组件被称为“在”另一组件“上”，“连接到”、“结合到”或者“相邻于”另一组件时，该组件可以直接在所述另一组件上，直接连接到、直接结合到、直接相邻于另一组件，或者可以存在中间组件。还将理解的是，当组件被称为“在”两个组件“之间”时，该组件可以是两个组件之间的唯一组件，或者也可以存在一个或更多个中间组件。还将理解的是，当组件被称为“覆盖”另一组件时，该组件可以是覆盖所述另一组件的唯一组件，或者一个或更多个中间组件也可以覆盖所述另一组件。

[0056] 当某一实施例可以不同地实施时，可以与所描述的顺序不同地执行特定的工艺顺序。例如，可以基本同时执行两个连续描述的工艺或者以与所描述的顺序相反的顺序执行两个连续描述的工艺。

[0057] 如这里所使用的术语“约”包括所述值，并且意味着考虑到所讨论的测量和与特定量的测量相关的误差(即，测量系统的限制)，在如本领域普通技术人员确定的特定值的可接受的偏差范围内。例如，“约”可以表示在本领域普通技术人员所理解的一个或更多个标准偏差内。此外，将理解的是，尽管参数在这里可以被描述为具有“约”某一值，但是如本领域普通技术人员将理解的是，根据示例性实施例，参数可以是测量误差内的精确特定值或近似特定值。

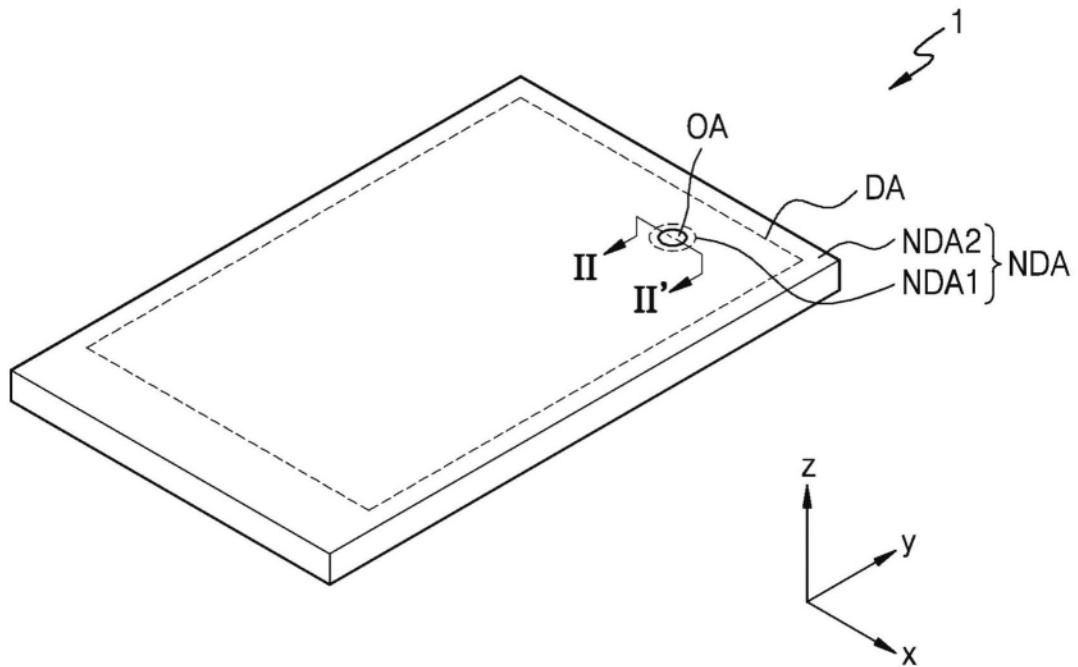

[0058] 图1是根据示例性实施例的显示装置1的透视图。

[0059] 参照图1，显示装置1包括发射光的显示区域DA和不发射光的非显示区域NDA。非显示区域NDA与显示区域DA相邻。显示装置1可以通过利用从布置在显示区域DA中的多个像素发射的光来提供预定图像。

[0060] 显示装置1包括被显示区域DA至少部分地围绕的开口区域OA。在示例性实施例中，如图1中所示，开口区域OA被显示区域DA完全地围绕。非显示区域NDA可以包括围绕开口区域OA的第一非显示区域NDA1和围绕显示区域DA的外围的第二非显示区域NDA2。第一非显示区域NDA1可以完全地围绕开口区域OA，显示区域DA可以完全地围绕第一非显示区域NDA1，并且第二非显示区域NDA2可以完全地围绕显示区域DA。

[0061] 尽管有机发光显示装置被示例性地描述为根据下面的示例性实施例的显示装置1，但显示装置不限于此。例如，在示例性实施例中，可以使用诸如无机发光显示装置和量子点发光显示装置的各种类型的显示装置。

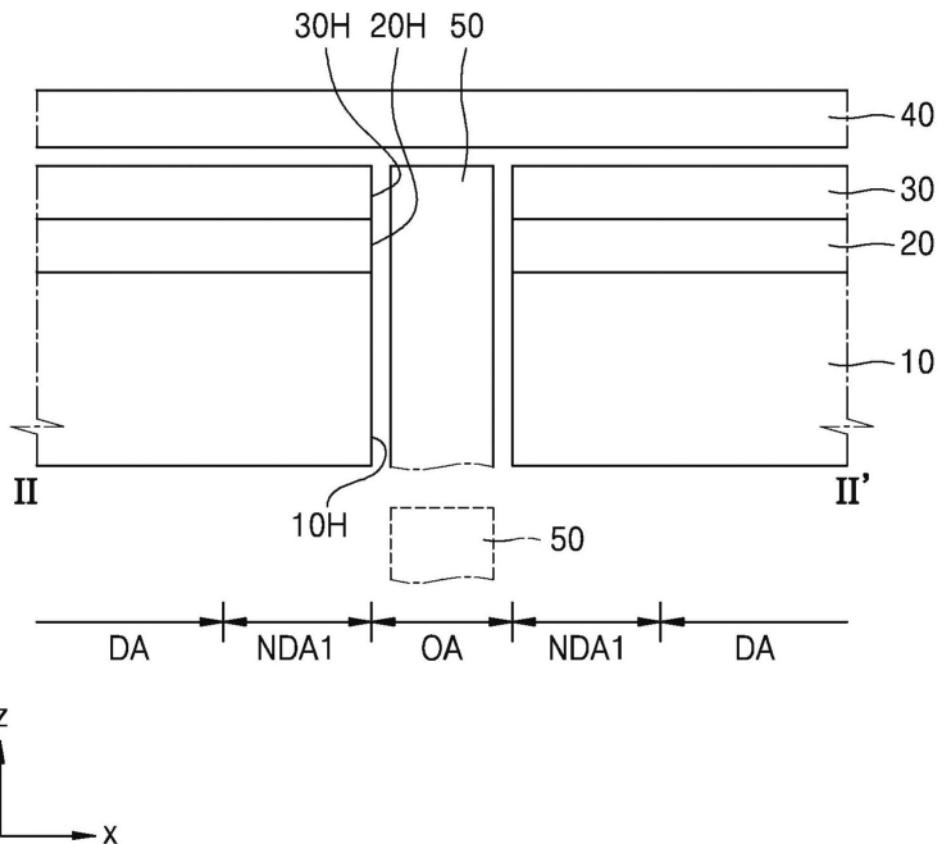

[0062] 图2是根据示例性实施例的显示装置1的剖视图，并且可以与沿图1的线II-II'截取的剖面对应。

[0063] 参照图2，显示装置1可以包括显示面板10、布置在显示面板10上的输入感测构件20以及光学功能构件30。这些构件可以被窗40覆盖。显示装置1可以应用于诸如以移动电话、笔记本计算机和智能手表为例的各种电子设备。

[0064] 显示面板10可以显示图像。显示面板10包括布置在显示区域DA中的像素。每个像素可以包括显示元件和连接到显示元件的像素电路。显示元件可以包括例如有机发光二极管、无机发光二极管或者量子点发光二极管。

[0065] 输入感测构件20获得与外部输入(诸如以触摸事件为例)对应的坐标信息。输入感测构件20可以包括感测电极(或触摸电极)和连接到感测电极的迹线。输入感测构件20可以布置在显示面板10上。

[0066] 输入感测构件20可以直接形成在显示面板10上，或者可以单独地形成然后使用例如诸如光学透明粘合剂(OCA)的粘合剂层结合到显示面板10。例如，输入感测构件20可以在形成显示面板10的工艺之后相继形成。在这种情况下，在示例性实施例中，粘合剂层不布置在输入感测构件20与显示面板10之间。尽管图2示出了输入感测构件20布置在显示面板10与光学功能构件30之间，但本公开不限于此。例如，在示例性实施例中，输入感测构件20可以布置在光学功能构件30上。

[0067] 光学功能构件30可以包括防反射层。防反射层可以降低通过窗40从外部朝向显示面板10入射的光(外部光)的反射率。防反射层可以包括例如延迟器和偏振器。延迟器可以包括膜型延迟器或液晶型延迟器。延迟器可以包括 $\lambda/2$ 延迟器和/或 $\lambda/4$ 延迟器。偏振器可以包括膜型偏振器或液晶型偏振器。膜型偏振器可以包括可拉伸的合成树脂膜，液晶型偏振

器可以包括以预定排列布置的液晶。延迟器和偏振器中的每个还可以包括保护膜。延迟器和偏振器自身或它们的保护膜可以被定义为防反射层的基本层。

[0068] 在示例性实施例中,防反射层可以包括黑矩阵和滤色器。可以考虑分别从显示面板10的像素发射的光的颜色来布置滤色器。在示例性实施例中,防反射层可以包括相消干涉结构。相消干涉结构可以包括分别布置在不同层中的第一反射层和第二反射层。由第一反射层反射的第一反射光和由第二反射层反射的第二反射光可以进行相消干涉,因此,可以减小外部光的反射率。

[0069] 光学功能构件30可以包括透镜层。透镜层可以改善从显示面板10发射的光的发射效率或者减小光的颜色偏差。透镜层可以包括具有凹透镜形状或凸透镜形状的层并且/或包括分别具有不同折射率的多个层。光学功能构件30可以包括防反射层和透镜层两者,或者包括防反射层和透镜层中的一个。

[0070] 显示面板10、输入感测构件20和/或光学功能构件30可以包括开口。在这方面,在示例性实施例中,如图2中所示,显示面板10、输入感测构件20和光学功能构件30可以分别包括彼此叠置的第一开口10H、第二开口20H和第三开口30H。第一开口10H、第二开口20H和第三开口30H设置在与开口区域OA对应的位置中。在示例性实施例中,显示面板10、输入感测构件20和光学功能构件30中的至少一个不包括开口。例如,在示例性实施例中,显示面板10、输入感测构件20和光学功能构件30中的一个或两个不包括开口。

[0071] 组件50可以对应于开口区域OA。例如,组件50可以设置在开口区域OA内或附近。例如,如由图2中的实线所示,组件50可以位于第一开口10H、第二开口20H和第三开口30H内部,或者如由图2中的虚线所示,组件50可以与第一开口10H、第二开口20H和第三开口30H对齐地位于显示面板10下方。

[0072] 组件50可以包括电子元件。例如,组件50可以包括利用光或声音的电子元件。例如,电子元件可以是发射和/或接收光的诸如红外传感器的传感器、接收光并捕获图像的相机、输出并感测光或声音以测量距离或识别指纹的传感器、输出光的小型灯或者输出声音的扬声器。利用光的电子元件可以利用诸如可见光、红外光和紫外光的各种波段的光。在示例性实施例中,开口区域OA可以被理解为透射区域,从组件50输出到外部或者从外部朝向组件50传播的光和/或声音可以穿过该透射区域。

[0073] 在示例性实施例中,在显示装置1被用作智能手表或汽车仪表板的情况下,组件50可以是包括钟表指针或指示预定信息(例如,车辆的速度等)的指针等的构件。在显示装置1包括钟表指针或用于汽车的仪表板的情况下,组件50可以通过窗40暴露到外部,窗40可以包括与开口区域OA对应的开口。

[0074] 如上所述,组件50可以包括与显示面板10的功能相关的元件或诸如增加显示面板10的美感的附件的元件。

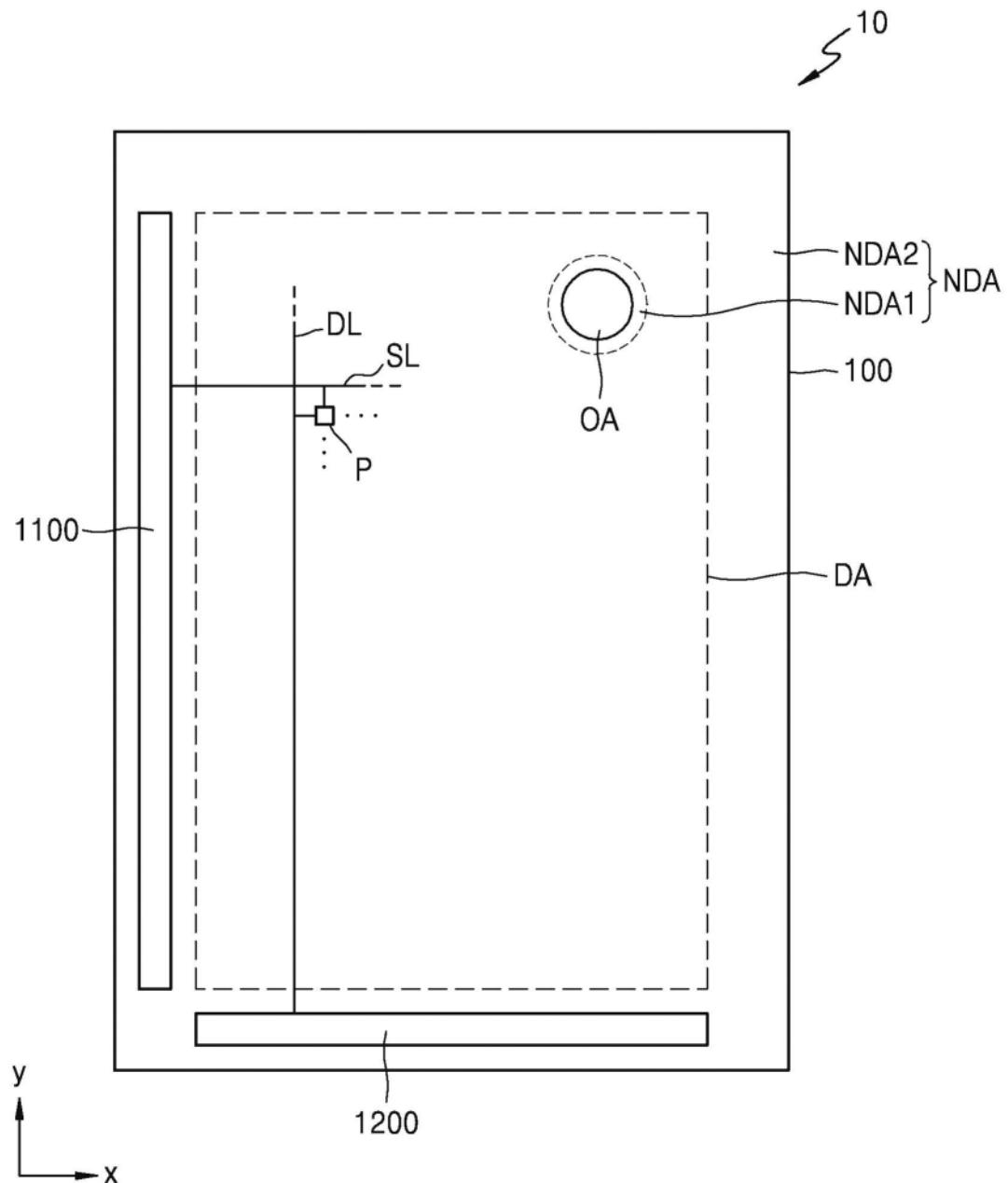

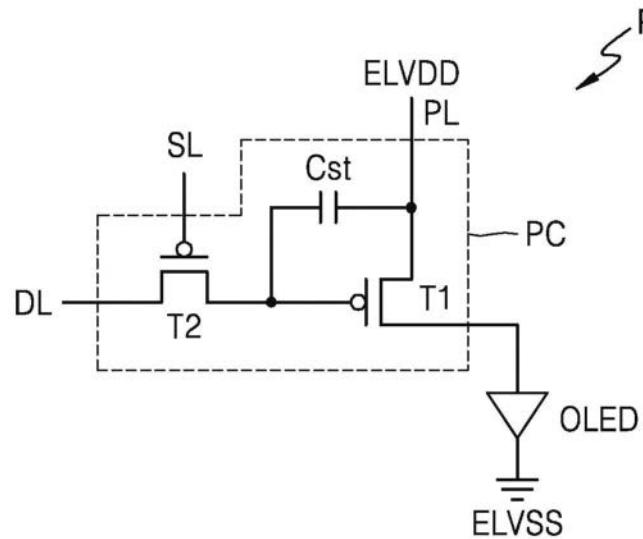

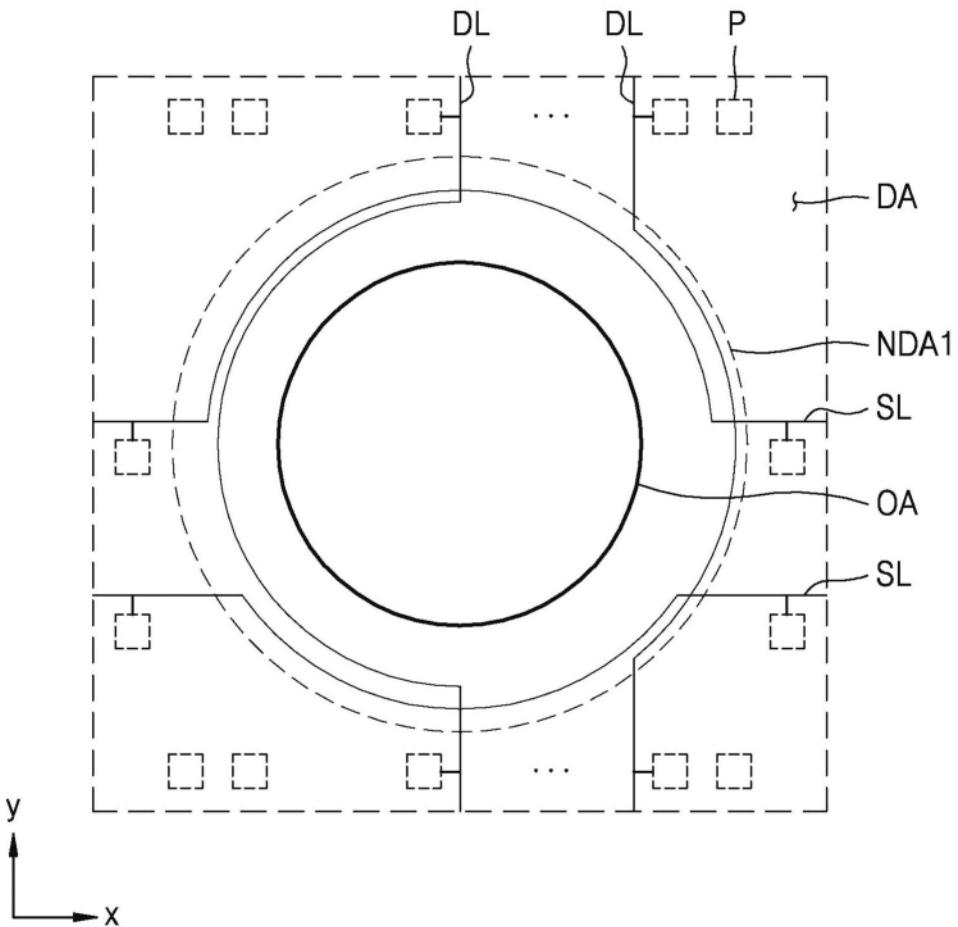

[0075] 图3是根据示例性实施例的显示面板10的平面图。图4是显示面板10的多个像素中的一个像素的等效电路图。

[0076] 参照图3,显示面板10包括显示区域DA、第一非显示区域NDA1和第二非显示区域NDA2。图3示出了显示面板10的基底100。显示面板10的基底100包括开口区域OA、第一非显示区域NDA1和第二非显示区域NDA2。

[0077] 显示面板10包括布置在显示区域DA中的多个像素P。如图4中所示,每个像素P包括

像素电路PC和作为显示元件连接到像素电路PC的有机发光二极管OLED。像素电路PC可以包括第一薄膜晶体管T1、第二薄膜晶体管T2和存储电容器Cst。每个像素P可以通过有机发光二极管OLED发射例如红光、绿光、蓝光或白光。

[0078] 第二薄膜晶体管T2可以是开关薄膜晶体管，可以连接到扫描线SL和数据线DL，并且可以响应于从扫描线SL输入的开关电压，将从数据线DL输入的数据电压传输到第一薄膜晶体管T1。存储电容器Cst可以连接到第二薄膜晶体管T2和驱动电压线PL，并且可以存储与从第二薄膜晶体管T2传输的电压和供应到驱动电压线PL的第一电源电压ELVDD之间的差对应的电压。

[0079] 第一薄膜晶体管T1可以是驱动薄膜晶体管，可以连接到驱动电压线PL和存储电容器Cst，并且可以响应于存储在存储电容器Cst中的电压来控制从驱动电压线PL流过有机发光二极管OLED的驱动电流。有机发光二极管OLED可以通过使用驱动电流而发射具有预定亮度的光。有机发光二极管OLED的对电极(例如，阴极)可以接收第二电源电压ELVSS。

[0080] 尽管参照图4描述了像素电路PC包括两个薄膜晶体管和一个存储电容器，但本公开不限于此。例如，根据示例性实施例，薄膜晶体管的数量和/或存储电容器的数量可以根据像素电路PC的设计而不同地改变。

[0081] 再次参照图3，第一非显示区域NDA1可以围绕开口区域OA。第一非显示区域NDA1是其中没有布置诸如有机发光二极管OLED的显示元件的区域。将信号提供到设置在开口区域OA周围的像素P的信号线可以穿过第一非显示区域NDA1的一部分(如后面图9中所描述的)，或将在下面进行描述的凹槽可以布置在第一非显示区域NDA1中。向每个像素P提供扫描信号的扫描驱动器1100、向每个像素P提供数据信号的数据驱动器1200、提供第一电源电压ELVDD和第二电源电压ELVSS的主电源布线等可以布置在第二非显示区域NDA2中。尽管在图3中示出了数据驱动器1200与基底100的一个侧面相邻，但本公开不限于此。例如，在示例性实施例中，数据驱动器1200可以布置在柔性印刷电路板(FPCB)上，该柔性印刷电路板电连接到布置在显示面板10的一侧上的垫(pad，也可以称为“焊盘”)。

[0082] 图5是根据示例性实施例的显示面板10的一部分的平面图，并且示出了位于第一非显示区域NDA1中的信号线。

[0083] 参照图5，像素P可以在显示区域DA中相对于开口区域OA布置，并且第一非显示区域NDA1可以位于开口区域OA与显示区域DA之间。

[0084] 像素P可以相对于开口区域OA彼此间隔开。在平面图中，像素P可以在y方向上竖直地布置并且开口区域OA设置在沿y方向竖直布置的像素P之间，并且/或像素P可以在x方向上水平地布置并且开口区域OA设置在沿x方向水平布置的像素P之间。

[0085] 在向像素P供应信号的信号线之中的与开口区域OA相邻的信号线可以绕行/绕过开口区域OA。穿过显示区域DA的数据线DL之中的一些数据线DL可以在y方向上延伸，向竖直地布置且开口区域OA设置在其间的像素P提供数据信号，并且在第一非显示区域NDA1中沿开口区域OA的边缘绕行/绕过。穿过显示区域DA的扫描线SL之中的一些扫描线SL可以在x方向上延伸，向水平布置且开口区域OA设置在其间的像素P提供扫描信号，并且在第一非显示区域NDA1中沿开口区域OA的边缘绕行/绕过。

[0086] 这里，当线被描述为绕行/绕过开口区域OA时，将理解的是，线的延伸方向被调整为使得线设置在开口区域OA周围而不设置在开口区域OA内。

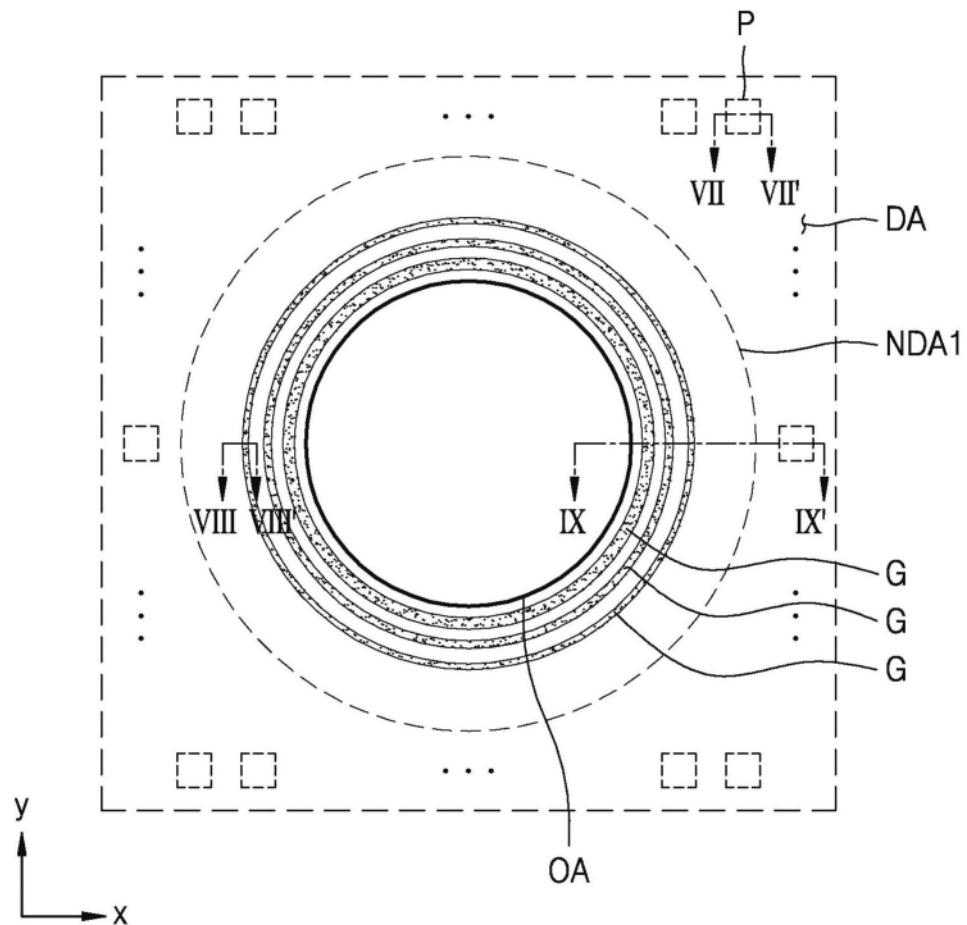

[0087] 图6是根据示例性实施例的显示面板10的一部分的平面图，并且示出了位于第一非显示区域NDA1中的凹槽G。

[0088] 一个或更多个凹槽G位于开口区域OA与显示区域DA之间。在这方面，尽管在图6中示出了三个凹槽G位于开口区域OA与显示区域DA之间，但本公开不限于此。例如，在示例性实施例中，一个、两个、四个或更多个凹槽G可以布置在第一非显示区域NDA1中。

[0089] 当在基底100的主表面上的垂直方向上观看时，凹槽G可以在第一非显示区域NDA1中具有完全地围绕开口区域OA的环形形状。每个凹槽G的直径可以大于开口区域OA的直径。围绕开口区域OA的凹槽G可以在平面图中彼此间隔开。

[0090] 参照图5和图6，相比于数据线DL和/或扫描线SL的绕行/绕过开口区域OA的边缘的绕行/绕过部分，凹槽G可以更靠近开口区域OA。例如，凹槽G与开口区域OA之间的距离可以比开口区域OA与数据线DL和/或扫描线SL的绕行/绕过开口区域OA的边缘的绕行/绕过部分之间的距离短。

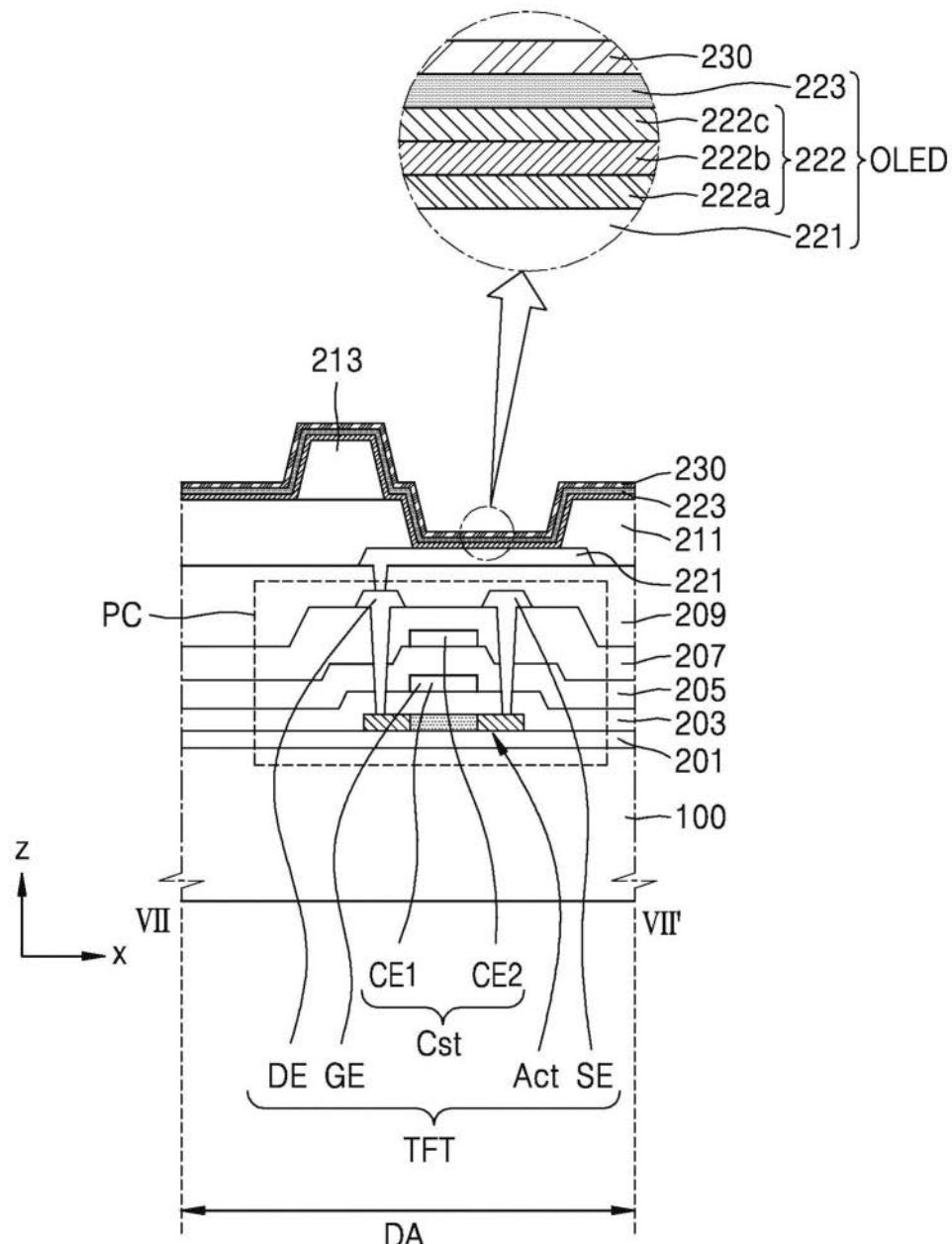

[0091] 图7是根据示例性实施例的显示面板10的多个像素P中的一个像素P的剖视图，并且可以对应于沿图6的线VII-VII'截取的剖面。

[0092] 参照图7，像素电路PC和电连接到像素电路PC的有机发光二极管OLED可以布置在显示区域DA中。

[0093] 可以形成位于基底100之上的薄膜晶体管TFT、存储电容器Cst以及电连接到薄膜晶体管TFT和存储电容器Cst的像素电极221。像素电路PC可以布置在基底100之上，并且有机发光二极管OLED可以位于像素电路PC之上。

[0094] 基底100可以包括例如聚合物树脂或玻璃。在示例性实施例中，基底100可以包括诸如聚醚砜(PES)、聚芳酯(PAR)、聚醚酰亚胺(PEI)、聚萘二甲酸乙二醇酯(PEN)、聚对苯二甲酸乙二醇酯(PET)、聚苯硫醚(PPS)、聚酰亚胺(PI)、聚碳酸酯(PC)、三乙酸纤维素(TAC)和/或乙酸丙酸纤维素(CAP)的聚合物树脂。基底100可以是柔性的。基底100可以包括包含SiO<sub>2</sub>作为主要成分的玻璃材料，或者可以包括诸如增强塑料的树脂，并且可以具有刚性特性。

[0095] 缓冲层201可以布置在基底100上，缓冲层201被构造为防止杂质渗透到薄膜晶体管TFT的半导体层Act中。缓冲层201可以包括诸如以氮化硅或氧化硅为例的无机绝缘材料，并且可以包括包含无机绝缘材料的单层或多层。

[0096] 像素电路PC可以布置在缓冲层201上。像素电路PC包括薄膜晶体管TFT和存储电容器Cst。薄膜晶体管TFT可以包括半导体层Act、栅电极GE、源电极SE和漏电极DE。图7中示出的薄膜晶体管TFT可以对应于参照图4描述的驱动薄膜晶体管T1。尽管图7中示出的示例性实施例示出了其中栅电极GE布置在半导体层Act之上并且在栅电极GE与半导体层Act之间设置有栅极绝缘层203的顶栅型薄膜晶体管，但本公开不限于此。例如，在示例性实施例中，薄膜晶体管TFT可以包括底栅型薄膜晶体管。

[0097] 半导体层Act可以包括多晶硅。可选择地，半导体层Act可以包括非晶硅、氧化物半导体或有机半导体。栅电极GE可以包括低电阻金属材料。栅电极GE可以包括诸如以Mo、Al、Cu和/或Ti等为例的导电材料。栅电极GE可以包括包含上述材料的多层或单层。

[0098] 设置在半导体层Act与栅电极GE之间的栅极绝缘层203可以包括诸如以氧化硅、氮化硅、氮氧化硅、氧化铝、氧化钛、氧化钽和氧化铪为例的无机绝缘材料。栅极绝缘层203可

以包括包含上述材料的多层或单层。

[0099] 源电极SE和漏电极DE可以包括具有优异的导电性的材料。源电极SE和漏电极DE中的每个可以包括包含例如Mo、Al、Cu和/或Ti的导电材料，并且可以包括包含上述材料的多层或单层。在示例性实施例中，源电极SE和漏电极DE可以包括Ti/Al/Ti的三层。

[0100] 存储电容器Cst包括下电极CE1和上电极CE2，下电极CE1和上电极CE2彼此叠置并且第一层间绝缘层205设置在下电极CE1与上电极CE2之间。存储电容器Cst可以与薄膜晶体管TFT叠置。在这方面，图7中示出了薄膜晶体管TFT的栅电极GE用作存储电容器Cst的下电极CE1。然而，本公开不限于此。例如，在示例性实施例中，存储电容器Cst不与薄膜晶体管TFT叠置。存储电容器Cst可以被第二层间绝缘层207覆盖。

[0101] 第一层间绝缘层205和第二层间绝缘层207可以包括诸如以氧化硅、氮化硅、氮氧化硅、氧化铝、氧化钛、氧化钽和氧化铪为例的无机绝缘层。第一层间绝缘层205和第二层间绝缘层207可以包括包含上述材料的单层或多层。

[0102] 包括薄膜晶体管TFT和存储电容器Cst的像素电路PC可以被第一绝缘层209覆盖。第一绝缘层209可以包括平坦化绝缘层并且可以包括基本上平坦的表面。第一绝缘层209可以包括有机绝缘材料，有机绝缘材料包括酰亚胺类聚合物、诸如聚甲基丙烯酸甲酯(PMMA)和聚苯乙烯(PS)的通用聚合物、具有酚类基团的聚合物衍生物、丙烯酸类聚合物、芳醚类聚合物、酰胺类聚合物、氟类聚合物、对二甲苯类聚合物、乙烯醇类聚合物或它们的共混物。在示例性实施例中，第一绝缘层209可以包括聚酰亚胺。可选择地，第一绝缘层209可以包括无机绝缘材料，或者可以包括无机绝缘材料和有机绝缘材料。

[0103] 像素电极221可以形成在第一绝缘层209上。像素电极221可以包括诸如以氧化铟锡(ITO)、氧化铟锌(IZO)、氧化锌(ZnO)、氧化铟( $In_2O_3$ )、氧化铟镓(IGO)或氧化铝锌(AZO)为例的导电氧化物。在示例性实施例中，像素电极221可以包括包含例如Ag、Mg、Al、Pt、Pd、Au、Ni、Nd、Ir、Cr和/或它们的混合物的反射层。在示例性实施例中，像素电极221还可以包括在反射层上或之下包含例如ITO、IZO、ZnO或 $In_2O_3$ 的层。

[0104] 第二绝缘层211可以形成在像素电极221上。第二绝缘层211可以包括像素限定层。第二绝缘层211可以包括使像素电极221的顶表面的一部分暴露的开口，并且可以覆盖像素电极221的边缘。第二绝缘层211可以包括有机绝缘材料。可选择地，第二绝缘层211可以包括诸如以氮化硅、氮氧化硅或氧化硅为例的无机绝缘材料。可选择地，第二绝缘层211可以包括有机绝缘材料和无机绝缘材料。

[0105] 中间层222可以包括发射层222b、布置在发射层222b之下的一第一功能层222a和/或布置在发射层222b上的第二功能层222c。发射层222b可以包括发射预定颜色的光的低分子有机材料或聚合物有机材料。

[0106] 第一功能层222a可以包括有机层。第一功能层222a可以包括单层或多层。例如，在第一功能层222a包括聚合物材料的情况下，第一功能层222a包括具有单层结构的空穴传输层(HTL)，并且可以包括聚(3,4-乙撑二氧噻吩)(PEDOT)或聚苯胺(PANI)。在第一功能层222a包括低分子材料的情况下，第一功能层222a可以包括空穴注入层(HIL)和HTL。

[0107] 第二功能层222c可以包括有机层。在示例性实施例中，可以省略第二功能层222c。例如，在第一功能层222a和发射层222b包括聚合物材料的情况下，可以设置第二功能层222c。第二功能层222c可以是单层或多层。第二功能层222c可以包括电子传输层(ETL)和/

或电子注入层(EIL)。

[0108] 可以针对显示区域DA中的每个像素P布置中间层222的发射层222b。中间层222的第一功能层222a和第二功能层222c不仅可以设置在图7的显示区域DA中,而且可以设置在将参照图8A和图8B描述的第一非显示区域NDA1中。

[0109] 对电极223可以包括具有低逸出功的导电材料。例如,对电极223可以包括包含以Ag、Mg、Al、Pt、Pd、Au、Ni、Nd、Ir、Cr、Li、Ca或它们的合金为例的半透明层。可选择地,对电极223还可以在包含上述材料的半透明层上包括包含例如ITO、IZO、ZnO或In<sub>2</sub>O<sub>3</sub>的层。对电极223不仅可以设置在显示区域DA中,而且可以设置在第一非显示区域NDA1中。中间层222和对电极223可以通过沉积法形成。

[0110] 间隔件213可以设置在第二绝缘层211上。间隔件213可以包括诸如以聚酰亚胺为例的有机绝缘材料。可选择地,间隔件213可以包括诸如以氮化硅或氧化硅为例的无机绝缘材料,或者可以包括有机绝缘材料和无机绝缘材料。

[0111] 间隔件213可以包括与第二绝缘层211的材料不同的材料。可选择地,间隔件213可以包括与第二绝缘层211的材料相同的材料。在这种情况下,第二绝缘层211和间隔件213可以在使用例如半色调掩模的掩模工艺期间同时形成。在示例性实施例中,第二绝缘层211和间隔件213可以包括聚酰亚胺。

[0112] 盖层230可以布置在对电极223上。盖层230可以包括LiF、无机材料和/或有机材料。在示例性实施例中,可以省略盖层230。

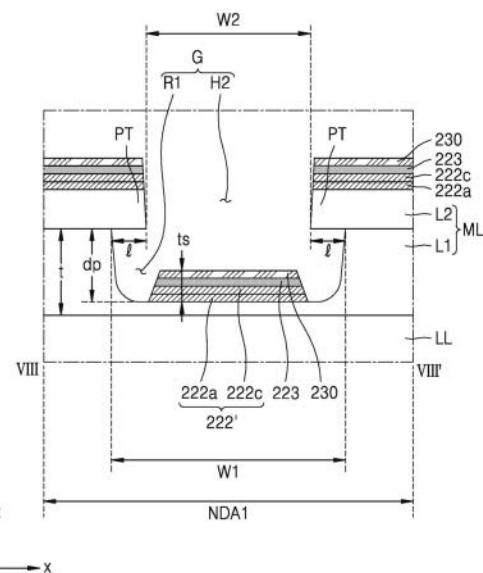

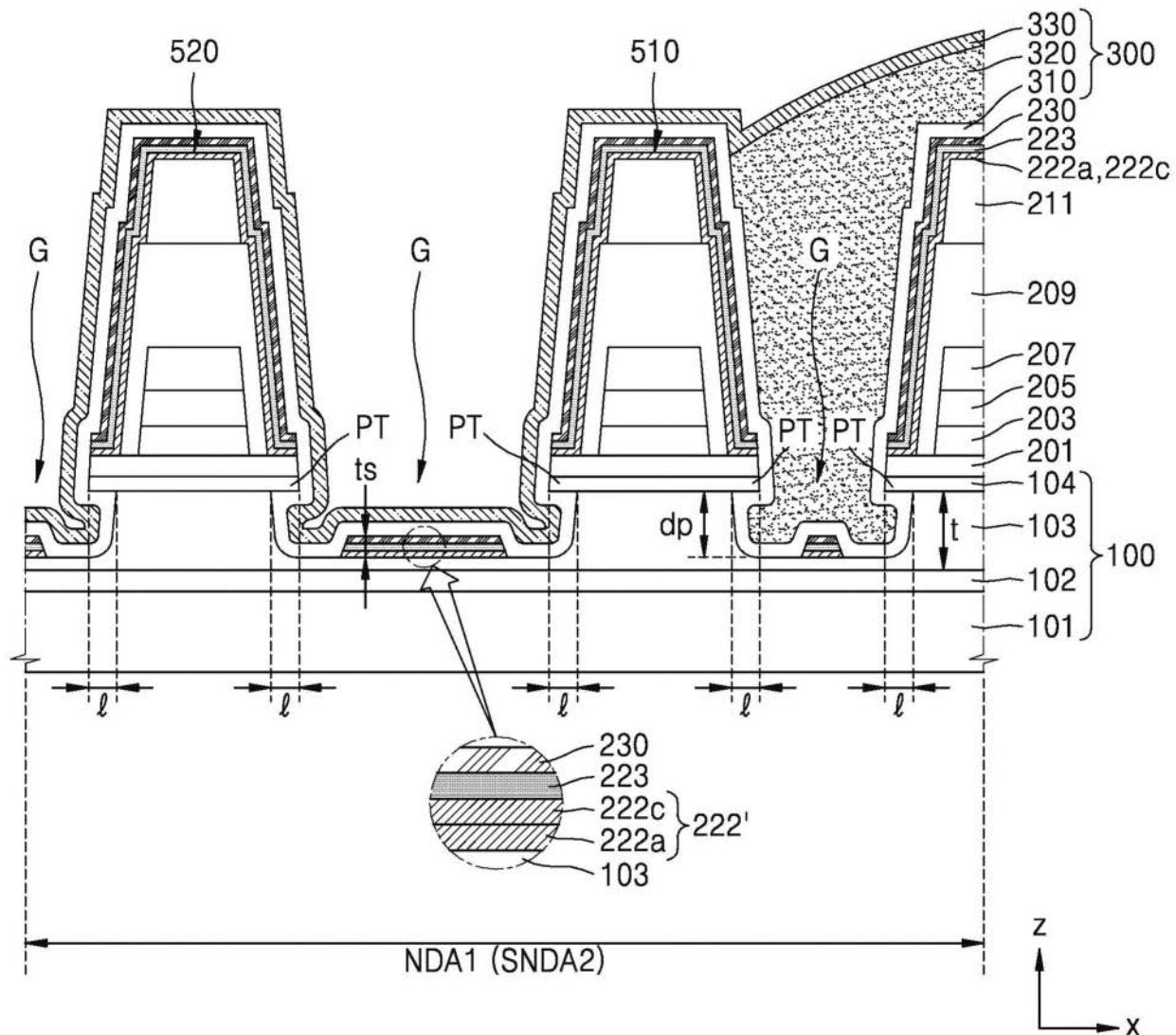

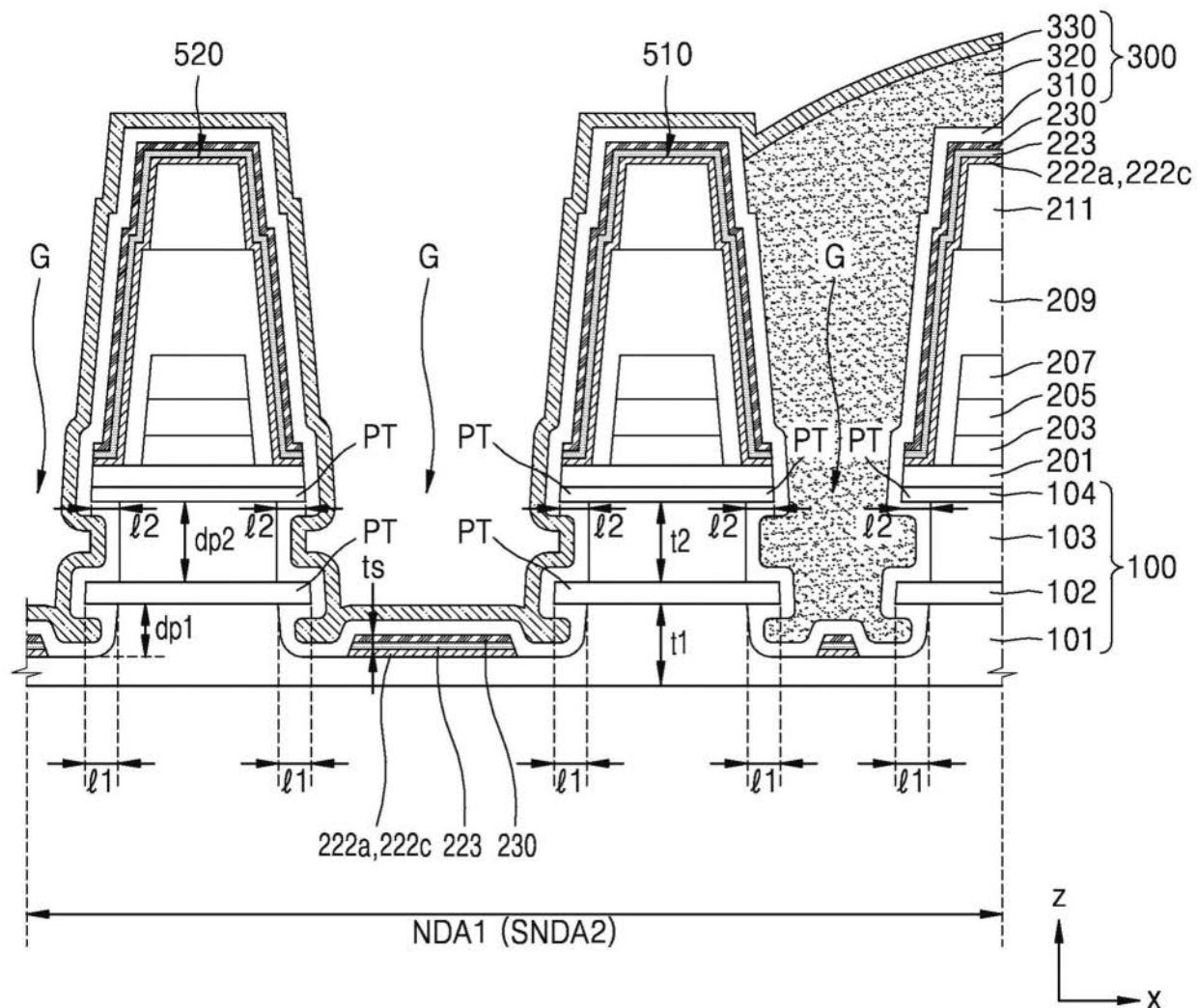

[0113] 图8A至图8D是根据示例性实施例的显示面板10的凹槽G中的一个凹槽G的剖视图,并且可以对应于沿图6的线VIII-VIII'截取的剖视图。

[0114] 参照图8A和图8B,凹槽G可以形成在多层ML中。多层ML包括分别包含不同材料的至少两个层。在这方面,图8A和图8B示出了包括包含有机材料的第一层L1和包含无机材料的第二层L2的多层ML。第一层L1可以包括有机绝缘材料。例如,第一层L1可以包括诸如聚酰亚胺的聚合物树脂。第二层L2可以包括诸如以氮化硅、氮氧化硅和/或氧化硅为例的无机绝缘材料。可选择地,第二层L2可以包括金属。

[0115] 图8A和图8B的多层ML可以对应于参照图7描述的显示面板10的元件的一部分。例如,多层ML可以对应于构成显示面板10的层(例如,设置在基底100之上的层)的一部分。

[0116] 凹槽G可以形成在多层ML中,并且可以在多层ML的深度方向上(例如,在z方向上)具有深度。参照图8A,可以通过蚀刻第二层L2形成穿过第二层L2的第二孔H2,并且可以通过蚀刻第一层L1形成在第一层L1的厚度方向上(例如,在z方向上)是凹的的第一凹部R1。第一凹部R1和第二孔H2可以在空间上彼此连接以构成凹槽G。可选择地,如图8B中所示,可以通过蚀刻第二层L2来形成穿过第二层L2的第二孔H2,并且可以通过蚀刻第一层L1来形成穿过第一层L1的第一孔H1。第一孔H1和第二孔H2可以在空间上连接以构成凹槽G。上述蚀刻可以包括各向同性蚀刻和/或各向异性蚀刻。

[0117] 凹槽G的穿过第二层L2的部分的宽度可以小于凹槽G的穿过第一层L1的部分的宽度。例如,第二孔H2的宽度(或直径)W2可以小于第一凹部R1或第一孔H1的宽度(或直径)W1。

[0118] 凹槽G可以具有底切剖面。相比于第一层L1的限定第一凹部R1或第一孔H1的侧面,第二层L2的限定第二孔H2的侧面可以在与基底100的顶表面(或底表面)平行的方向(例如,x方向)上进一步朝向凹槽G的中心突出。第二层L2的朝向凹槽G的中心突出的部分可以构成

悬突于第一层L1的限定第一凹部R1或第一孔H1的侧面的一对檐部。所述一对檐部也可以被称为一对突出的尖端或尖端PT。

[0119] 可以在形成上面参照图7描述的中间层222的工艺之前形成凹槽G。盖层230可以包括LiF。类似于子层222'和对电极223，盖层230(例如，LiF层)可以通过热蒸发形成。中间层222的子层222'、对电极223和盖层230可以被凹槽G断开。在这方面，图8A和图8B中示出了第一功能层222a、第二功能层222c、对电极223和盖层230在凹槽G的尖端PT周围断开。例如，如图8A和图8B中所示，第一功能层222a、第二功能层222c、对电极223和盖层230中的每个的第一部分设置在第二层L2的顶部上，第一功能层222a、第二功能层222c、对电极223和盖层230中的每个的第二部分设置在凹槽G中，并且这些第一部分和第二部分彼此不连接。尽管图8A和图8B中示出了第一功能层222a、第二功能层222c、对电极223和盖层230在凹槽G或尖端PT周围断开，但本公开不限于此。例如，在示例性实施例中，可以省略第一功能层222a和第二功能层222c中的一个和/或盖层230。

[0120] 一对尖端PT中的每个的长度 $\ell$ 可以小于约2μm并且大于约0μm。这里，可以在剖视图中从直接位于包括尖端PT的第二层L2之下的一层L1的侧表面和顶表面在其处彼此相交的点朝向凹槽G的中心在水平方向(或平行于基底100的顶表面或底表面的方向，例如，x方向)上来测量尖端PT的长度 $\ell$ 。尖端PT的长度 $\ell$ 可以选自于大于约0μm且小于约2μm的范围。例如，在示例性实施例中，尖端PT的长度 $\ell$ 可以是约0.3μm≤ $\ell$ <约2.0μm、约0.5μm≤ $\ell$ <约2.0μm、约0.8μm≤ $\ell$ <约2.0μm、或约1.0μm≤ $\ell$ <约2.0μm。在尖端PT的长度 $\ell$ 小于约0.3μm的情况下，子层222'和对电极223在尖端PT周围没有被断开，并且湿气可以通过未断开的子层222'朝向显示区域DA的有机发光二极管OLED渗透。

[0121] 在尖端PT的长度 $\ell$ 偏离上述上限的情况下，在尖端PT中可能发生裂纹，或者在制造显示面板10的工艺期间或在制造工艺之后尖端PT可能被破坏。作为本公开的实验示例，已经制造了包括不同长度的尖端PT的显示面板10的样品。每个样品被制造成具有长度为约0.8μm至约2.0μm的尖端PT，并且在将制造的样品放置在湿度为约85%且温度为约85°C的腔室内部预定时间(例如，至少240小时)之后，测量尖端PT以确定尖端PT是否被损坏。作为测量的结果，在尖端PT的长度 $\ell$ 小于约2.0μm的情况下，尖端PT没有被损坏。相反，在尖端PT的长度 $\ell$ 大于约2.0μm的情况下，对尖端PT的损坏开始发生。在尖端PT的长度 $\ell$ 大于约2.0μm的情况下，尖端PT的损坏率(例如，损坏的尖端PT的数量/所有尖端PT的数量)为约46.7%。

[0122] 凹槽G可以具有预定的深度dp。这里，凹槽G的深度dp表示凹槽G的穿过第一层L1的部分的深度。例如，凹槽G的深度dp与从位于尖端PT正下方的第一层L1的顶表面到凹槽G的底表面的竖直距离对应。

[0123] 凹槽G的深度dp可以大于尖端PT的长度 $\ell$ 。在示例性实施例中，凹槽G的深度dp和尖端PT的长度 $\ell$ 之间的关系可以为约0.05<(ℓ/dp)<约0.50、约0.1<(ℓ/dp)<约0.50、约0.15<(ℓ/dp)<约0.50、约0.2<(ℓ/dp)<约0.50、约0.25<(ℓ/dp)<约0.50、约0.25<(ℓ/dp)<约0.45、约0.25<(ℓ/dp)<约0.40或者约0.25<(ℓ/dp)<约0.35。

[0124] 凹槽G的深度dp可以比在凹槽G周围断开的第一功能层222a和/或第二功能层222c的厚度、对电极223的厚度以及盖层230的厚度的总和ts大。可选择地，凹槽G的深度dp可以

为约 $3.0\mu\text{m}$ 或更大。

[0125] 参照图8A,凹槽G的深度dp可以小于第一层L1的厚度t,并且凹槽G的底表面可以位于第一层L1的顶表面与第一层L1的底表面之间。可选择地,如图8B中所示,凹槽G的深度dp可以与第一层L1的厚度t相同。因此,凹槽G的底表面可以位于第一层L1的底表面或设置在第一层L1之下的下层LL的顶表面上。下层LL可以包括诸如以有机绝缘材料或无机绝缘材料为例的绝缘材料。在示例性实施例中,深度dp可以等于或小于约 $6.0\mu\text{m}$ 。凹槽G的深度dp可以为约 $2.0\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 、约 $2.5\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 、约 $3.0\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 、约 $3.5\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 、约 $4.0\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 、约 $4.5\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 、约 $5.0\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 或者约 $5.5\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 。

[0126] 一对尖端PT之间的距离(即,第二宽度W2)可以大于尖端PT的长度 $\ell$ 。在示例性实施例中,第二宽度W2可以在尖端PT的长度 $\ell$ 的约三倍至约一百倍的范围内,在尖端PT的长度 $\ell$ 的约五倍到约七十倍的范围内,在尖端PT的长度 $\ell$ 的约五倍到约五十倍的范围内,在尖端PT的长度 $\ell$ 的约五倍到约三十倍的范围内,在尖端PT的长度 $\ell$ 的约五倍到约二十倍的范围内,或者在尖端PT的长度 $\ell$ 的约七倍到约二十倍的范围内。第二宽度W2可以大于凹槽G的深度dp。例如,第二宽度W2可以是凹槽G的深度dp的约1.5倍或更多倍,是凹槽G的深度dp的约2倍或更多倍,或者是凹槽G的深度dp的约2.5倍或更多倍。

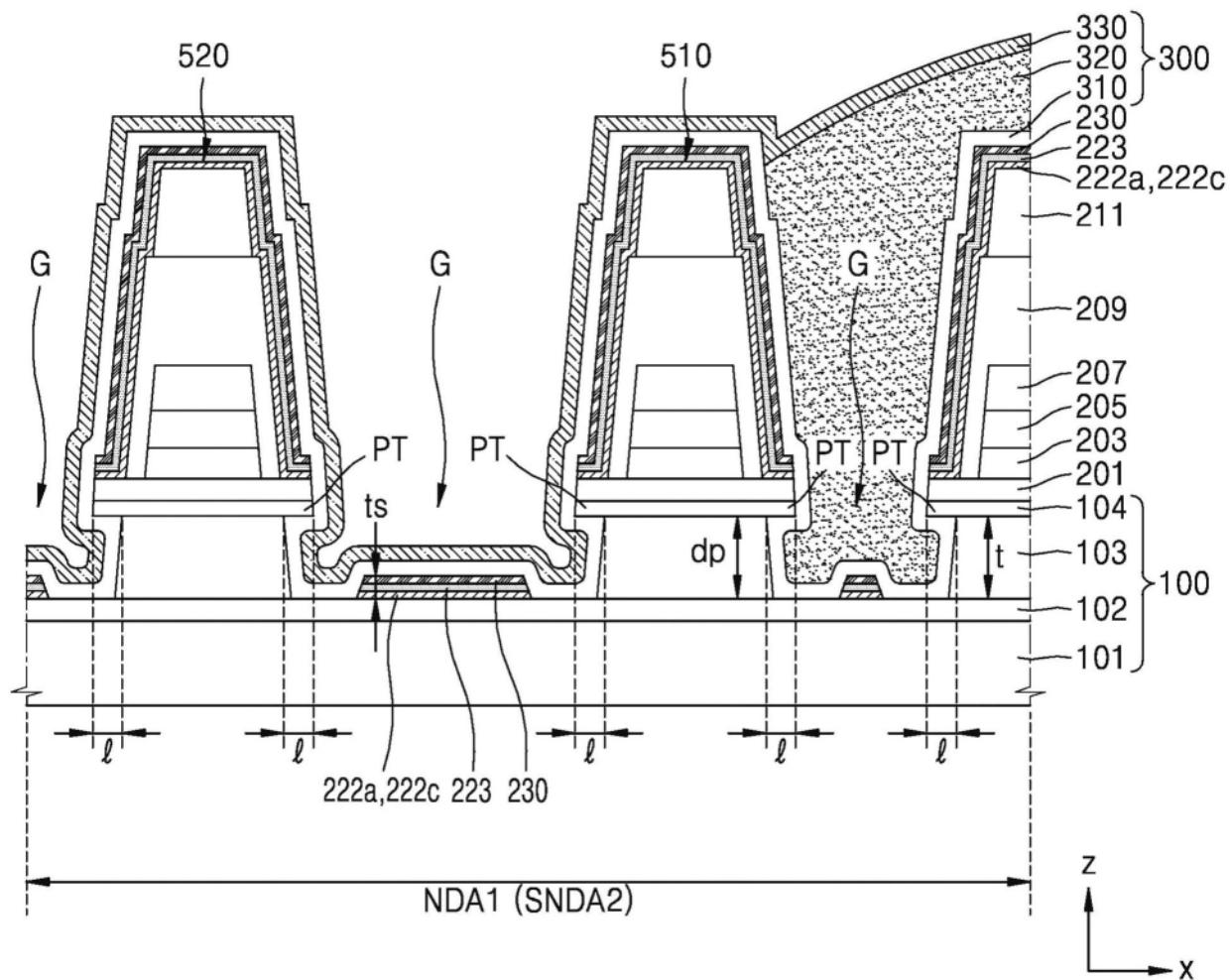

[0127] 尽管图8A和图8B示出了第一功能层222a、第二功能层222c、对电极223和盖层230在凹槽G或尖端PT周围被断开,但本公开不限于此。例如,在示例性实施例中,如图8C中所示,可以省略盖层230。在这种情况下,被凹槽G断开的层可以包括第一功能层222a、第二功能层222c和对电极223。例如,如图8C中所示,第一功能层222a、第二功能层222c和对电极223中的每个的第一部分设置在第二层L2的顶部上,第一功能层222a、第二功能层222c和对电极223中的每个的第二部分设置在凹槽G中,并且这些第一部分和第二部分彼此不连接。在示例性实施例中,可以省略第一功能层222a和第二功能层222c中的一个。如上所述,如图8C中所示,凹槽G的深度dp比包括第一功能层222a、第二功能层222c和对电极223的堆叠体的厚度ts'大。另外,在根据图8C的示例性实施例中,尖端PT的长度 $\ell$ 和凹槽G的深度dp的特征与参照图8A和图8B描述的那些相同。参照图8C描述的其中盖层230已被省略的结构适用于参照图8B描述的示例性实施例。

[0128] 在示例性实施例中,如图8D中所示,盖层230在凹槽G周围未被断开。例如,盖层230设置在第二层L2的上表面和侧表面上,并且延伸到凹槽G中而没有任何断裂或孔。盖层230可以包括诸如以氧化硅、氮化硅或氮氧化硅为例的无机绝缘材料,并且该无机绝缘材料可以通过化学气相沉积(CVD)形成。由于包括无机绝缘材料的盖层230与通过热蒸发形成的第一功能层222a、第二功能层222c和对电极223相比具有相对优异的台阶覆盖性,因此,如图8D中所示,盖层230可以完全地且连续地覆盖凹槽G的内表面。例如,盖层230可以以连续的方式覆盖凹槽G的内表面而没有任何断裂或孔。除了盖层230连续地覆盖凹槽G的内表面的特征之外,盖层230的其它特征与参照图8A和图8B描述的那些特征相同。

[0129] 在示例性实施例中,在盖层230包括有机材料的情况下,盖层230可以如参照图8A和图8B描述的在凹槽G周围断开。

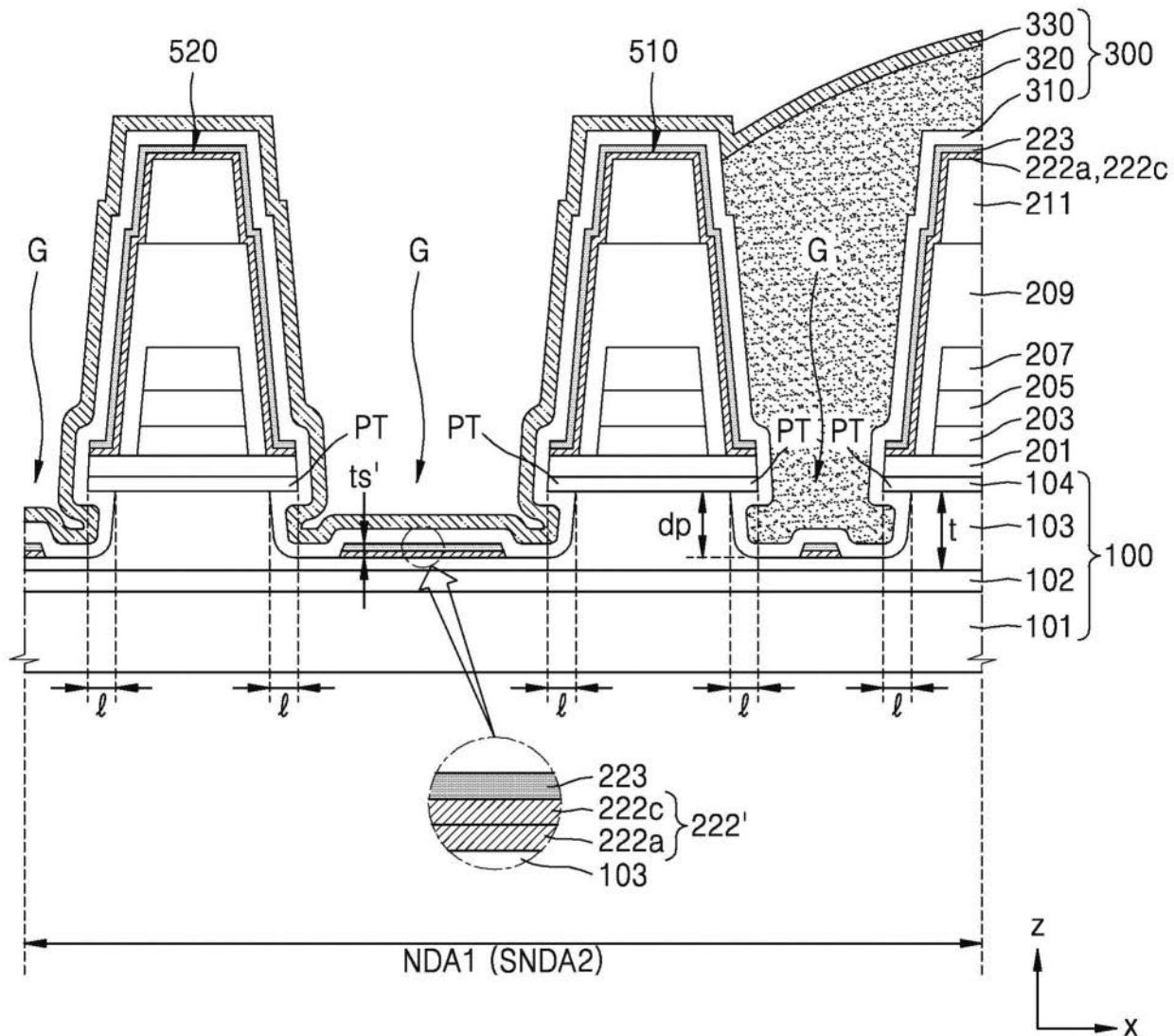

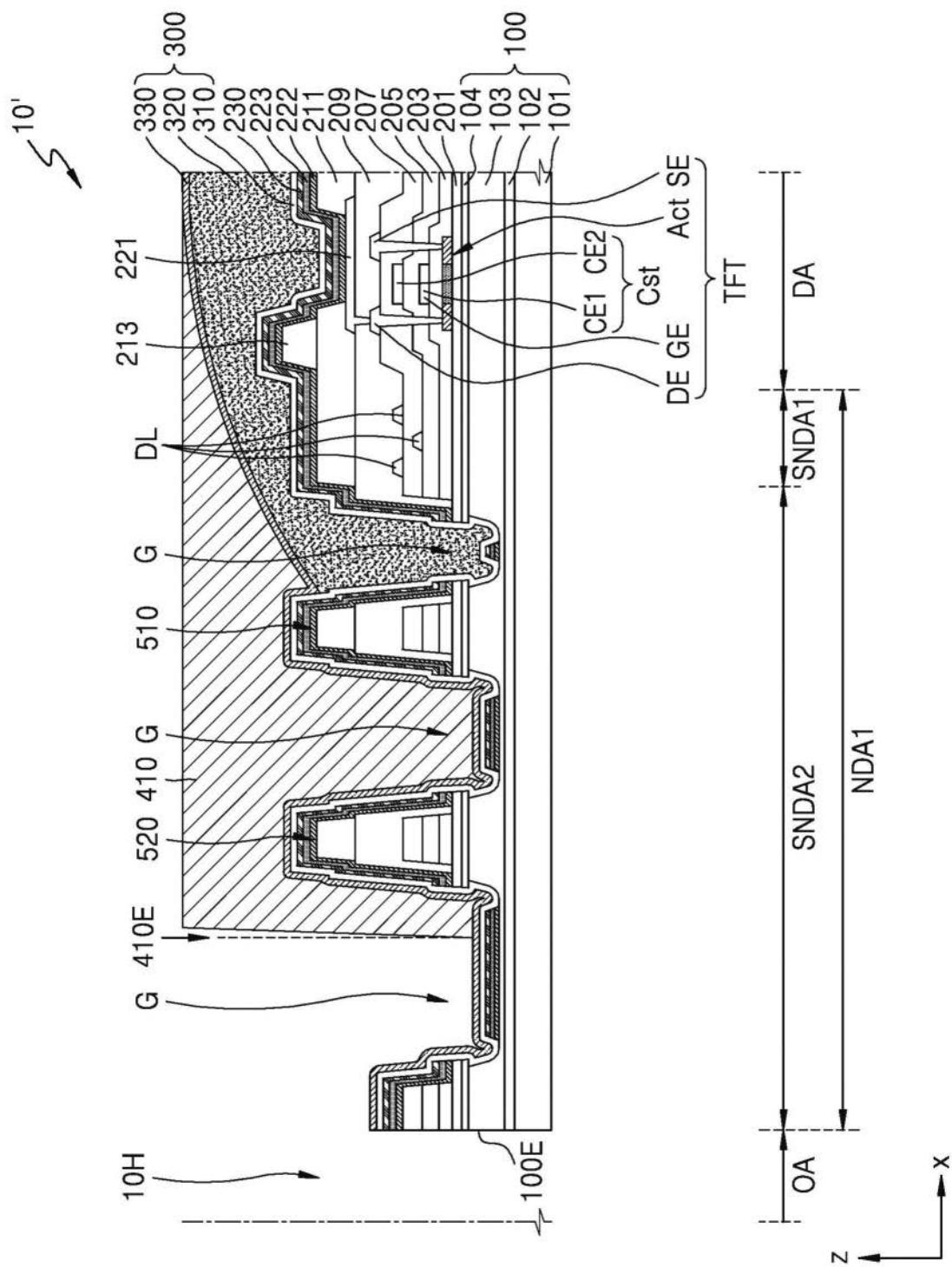

[0130] 图9是根据示例性实施例的显示面板10的剖视图。图10是根据示例性实施例的显示面板10的凹槽G的剖视图。图11是根据示例性实施例的显示面板10的凹槽G的剖视图。图9

可以对应于沿图6的线IX-IX'截取的剖面,图10可以对应于图9的凹槽G的放大剖面。

[0131] 参照图9,显示面板10包括开口区域OA、显示区域DA和第一非显示区域NDA1。显示面板10可以包括对应于开口区域OA的第一开口10H。例如,第一开口10H可以与开口区域OA对齐。

[0132] 参照图9的显示区域DA,薄膜晶体管TFT和存储电容器Cst在显示区域DA中布置在基底100之上。

[0133] 基底100可以包括多层。例如,基底100可以包括顺序地堆叠的第一基体层101、第一阻挡层102、第二基体层103和第二阻挡层104。

[0134] 第一基体层101和第二基体层103中的每个可以包括聚合物树脂。例如,第一基体层101和第二基体层103中的每个可以包括诸如聚醚砜(PES)、聚芳酯、聚醚酰亚胺(PEI)、聚萘二甲酸乙二醇酯(PEN)、聚对苯二甲酸乙二醇酯(PET)、聚苯硫醚(PPS)、聚酰亚胺(PI)、聚碳酸酯(PC)、三乙酸纤维素(TAC)或乙酸丙酸纤维素(CAP)的聚合物树脂。聚合物树脂可以是透明的。

[0135] 第一阻挡层102和第二阻挡层104中的每个可以包括被构造成防止外部异物的渗透的阻挡层,并且可以包括包含诸如氮化硅和/或氧化硅的无机材料的单层或多层。

[0136] 绝缘层201、203、205、207和209可以布置在基底100与像素电极221之间。电连接到薄膜晶体管TFT的像素电极221、中间层222、对电极223和盖层230可以布置在显示区域DA中,并且上述构造与上面参照图7描述的构造相同。

[0137] 包括像素电极221、中间层222和对电极223的显示元件被薄膜封装层300覆盖。薄膜封装层300可以包括至少一个有机封装层和至少一个无机封装层。在图9中示出了薄膜封装层300包括第一无机封装层310、第二无机封装层330以及设置在第一无机封装层310与第二无机封装层330之间的有机封装层320。然而,本公开不限于此。例如,在示例性实施例中,可以改变有机封装层的数量、无机封装层的数量以及它们的堆叠顺序。

[0138] 第一无机封装层310可以包括诸如以氧化铝、氧化钛、氧化钽、氧化铪、氧化锌、氧化硅、氮化硅和氮氧化硅为例的至少一种无机绝缘材料。第一无机封装层310可以通过CVD形成。有机封装层320可以包括聚合物类材料。聚合物类材料可以包括丙烯酸类树脂、环氧类树脂、聚酰亚胺和聚乙烯。

[0139] 参照图9的第一非显示区域NDA1,第一非显示区域NDA1可以包括第一子非显示区域SNDA1和第二子非显示区域SNDA2,第一子非显示区域SNDA1与显示区域DA相邻,第二子非显示区域SNDA2与开口区域OA或第一开口10H相邻。

[0140] 第一子非显示区域SNDA1可以是信号线(例如,参照图5描述的数据线DL)穿过的区域。图9中示出的数据线DL可以对应于在开口区域OA周围绕行/绕过的数据线。第一子非显示区域SNDA1可以是数据线DL穿过的布线区域或者绕行/绕过区域。

[0141] 如图9中所示,数据线DL可以交替地布置,并且绝缘层设置在数据线DL之间。例如,在示例性实施例中,数据线DL可以交替地布置在不同的绝缘层上。可选择地,数据线DL可以布置在同一层上。在相邻的数据线DL分别布置在绝缘层(例如,第二层间绝缘层207)上方和下方同时绝缘层(例如,第二层间绝缘层207)置于所述相邻的数据线DL之间的情况下,可以减小所述相邻的数据线DL之间的间隙(间距),并且可以减小第一非显示区域NDA1的宽度。尽管图9中示出了数据线DL位于第一子非显示区域SNDA1中,但是上面参照图5描述的绕行/

绕过开口区域0A的扫描线SL也可以位于第一子非显示区域SNDA1中。

[0142] 第二子非显示区域SNDA2是其中布置有凹槽G的凹槽区域。图9示出了位于第二子非显示区域SNDA2中的三个凹槽G。凹槽G可以形成在如上面参照图8A和图8B描述的包括分别包含不同材料的第一层L1和第二层L2的多层ML中。在示例性实施例中,凹槽G形成在如图9中示出的设置到基底100的子层中。

[0143] 参照图9和图10的第二子非显示区域SNDA2,可以通过去除第二阻挡层104的一部分和第二基体层103的一部分来形成凹槽G。例如,穿过第二阻挡层104和缓冲层201的孔以及形成在第二基体层103中的凹部可以在空间上彼此连接以构成凹槽G。第二基体层103可以对应于上面参照图8A和图8B描述的多层ML的第一层L1,并且第二阻挡层104可以对应于多层ML的第二层L2。

[0144] 如上所述,在形成凹槽G的工艺期间,设置在第二阻挡层104上的缓冲层201可以与第二阻挡层104同时被去除,以构成凹槽G。尽管缓冲层201和第二阻挡层104被描述为独立的元件,但是,在示例性实施例中,基底100上的缓冲层201可以是具有多层结构的第二阻挡层104的子层。

[0145] 凹槽G的尖端PT具有预定的长度  $\ell$ ,并且尖端PT的长度  $\ell$  的特征与如上面参照图8A和图8B描述的尖端PT的长度  $\ell$  的特征相同。例如,尖端PT的长度  $\ell$  可以小于约 $2.0\mu\text{m}$ 。

[0146] 如图10中所示,凹槽G的深度dp可以小于第二基体层103的厚度t。可选择地,如图11中所示,凹槽G的深度dp可以与第二基体层103的厚度t大约相同,并且深度dp的特征与上面参照图8A和图8B描述的深度dp的特征相同。

[0147] 如上所述,对电极223、盖层230和/或与中间层222的子层222'对应的第一功能层222a和第二功能层222c可以在第二子非显示区域SNDA2中被凹槽G断开。

[0148] 薄膜封装层300的第一无机封装层310与中间层222的子层222'、对电极223和/或盖层230相比具有相对优异的台阶覆盖性。因此,第一无机封装层310可以连续地形成而不会在凹槽G周围被断开。例如,第一无机封装层310可以在凹槽G周围连续地延伸而没有任何断裂或孔。

[0149] 如图9中所示,第一无机封装层310可以完全地覆盖显示区域DA和第一非显示区域NDA1。在第一非显示区域NDA1中,第一无机封装层310可以完全且连续地覆盖凹槽G的内表面。在尖端PT周围断开的第一功能层222a、第二功能层222c、对电极223和盖层230的堆叠件布置在凹槽G的底表面上。第一无机封装层310可以在覆盖所述堆叠件的同时与第二基体层103之下的层(例如,第一阻挡层102)接触。

[0150] 有机封装层320可以通过涂覆单体并使单体硬化来形成。可以通过分隔壁(例如,第一分隔壁510和第二分隔壁520)来控制单体的流动。在这方面,图9至图11示出了有机封装层320的一端位于第一分隔壁510的一侧上。有机封装层320可以至少部分地填充凹槽G中的一个。例如,位于显示区域DA与第一分隔壁510之间的凹槽G在第一无机封装层310之上的空间可以至少部分地填充有有机封装层320的材料。

[0151] 类似于第一无机封装层310,第二无机封装层330可以完全且连续地覆盖凹槽G的内表面。第二无机封装层330的一部分可以在第二子非显示区域SNDA2中与第一无机封装层310直接接触。第二无机封装层330可以在多个凹槽G中的至少一个上与第一无机封装层310直接接触。第一无机封装层310和第二无机封装层330也可以在第一分隔壁510和第二分隔

壁520的顶表面上彼此接触。

[0152] 图12是根据示例性实施例的显示面板10的凹槽G的剖视图。

[0153] 参照图12,与上面参照图10描述的显示面板10不同,可以省略盖层230。除了盖层230被省略之外的特征与上面参照图10描述的特征相同。例如,关于凹槽G的尖端PT的长度 $\ell$ 的特征与上面参照图8A至图8C描述的特征相同。例如,尖端PT的长度 $\ell$ 可以小于约2.0 $\mu\text{m}$ 。另外,如图10中所示,凹槽G的深度dp可以小于第二基体层103的厚度t。可选择地,如图11中所示,凹槽G的深度dp可以与第二基体层103的厚度t大约相同,并且关于深度dp的特征与上面参照图8A至图8C描述的特征相同。参照图12描述的其中盖层230已被省略的结构可适用于将参照图14至图17描述的示例性实施例以及由此衍生的示例性实施例。

[0154] 参照图9至图11描述的盖层230可以包括诸如以LiF为例的具有相对低的台阶覆盖性的材料。因此,尽管图9至图11示出了在凹槽G周围断开的结构,但本公开不限于此。

[0155] 图13是根据示例性实施例的显示面板10的凹槽G的剖视图。

[0156] 参照图13,盖层230可以包括无机绝缘材料。由于包括无机绝缘材料的通过诸如CVD的工艺形成的盖层230具有相对优异的台阶覆盖性,因此盖层230没有在凹槽G周围被断开,并且可以连续地覆盖凹槽G的内表面。

[0157] 盖层230可以包括诸如以氮化硅、氧化硅或氮氧化硅为例的无机材料。第一无机封装层310可以布置在盖层230上。第一无机封装层310可以包括无机绝缘材料。在示例性实施例中,包括无机绝缘材料的盖层230可以为第一无机封装层310的子层。在示例性实施例中,包括具有不同特性/性质的至少两个氮氧化硅层或至少两个氮化硅层的第一无机封装层310的一个子层可以是盖层230。

[0158] 参照图13描述的盖层230的结构可适用于参照图14至图17描述的示例性实施例和由此衍生的示例性实施例。

[0159] 图14是根据示例性实施例的显示面板10的凹槽G的剖视图。

[0160] 参照图14,凹槽G可以具有在深度方向(或基底100的厚度方向)上叠置的多个底切割面。例如,第一基体层101和第一阻挡层102可以具有底切割面(称为第一底切割面),第二基体层103和第二阻挡层104可以具有底切割面(称为第二底切割面)。凹槽G可以具有其中第一底切割面和第二底切割面彼此叠置的结构。

[0161] 第一阻挡层102的尖端PT具有第一长度 $\ell_1$ ,第二阻挡层104的尖端PT具有第二长度 $\ell_2$ 。第一长度 $\ell_1$ 和第二长度 $\ell_2$ 的特征与上面参照图8A和图8B描述的长度 $\ell$ 的特征相同。例如,第一长度 $\ell_1$ 和第二长度 $\ell_2$ 中的每个可以小于约2.0 $\mu\text{m}$ 。

[0162] 第一基体层101具有第一深度dp1,并且第二基体层103具有第二深度dp2。第二基体层103的第二深度dp2可以与第二基体层103的厚度t2相同,第一基体层101的第一深度dp1可以小于第一基体层101的厚度t1。当满足上述特征时,上面参照图8A和图8B描述的深度dp的特征同样地可适用于图14中示出的第一深度dp1和第二深度dp2。第一深度dp1和第二深度dp2可以大于尖端PT的长度 $\ell$ 。例如,第一深度dp1可以大于尖端PT的相应的第一长度 $\ell_1$ ,第二深度dp2可以大于尖端PT的相应的第二长度 $\ell_2$ 。第一深度dp1可以比在凹槽G周围断开的第一功能层222a、第二功能层222c、对电极223和盖层230的厚度的总和ts大。在示例性实施例中,第一深度dp1可以是约2.0 $\mu\text{m}$ 或更大,或约3.0 $\mu\text{m}$ 或更大。

[0163] 尽管在图9至图14中示出了包括凹槽G的多层形成在基底100的子层中,但本公开不限于此。如下面参照图15和图16描述的,根据示例性实施例,凹槽G可以位于基底100之上。

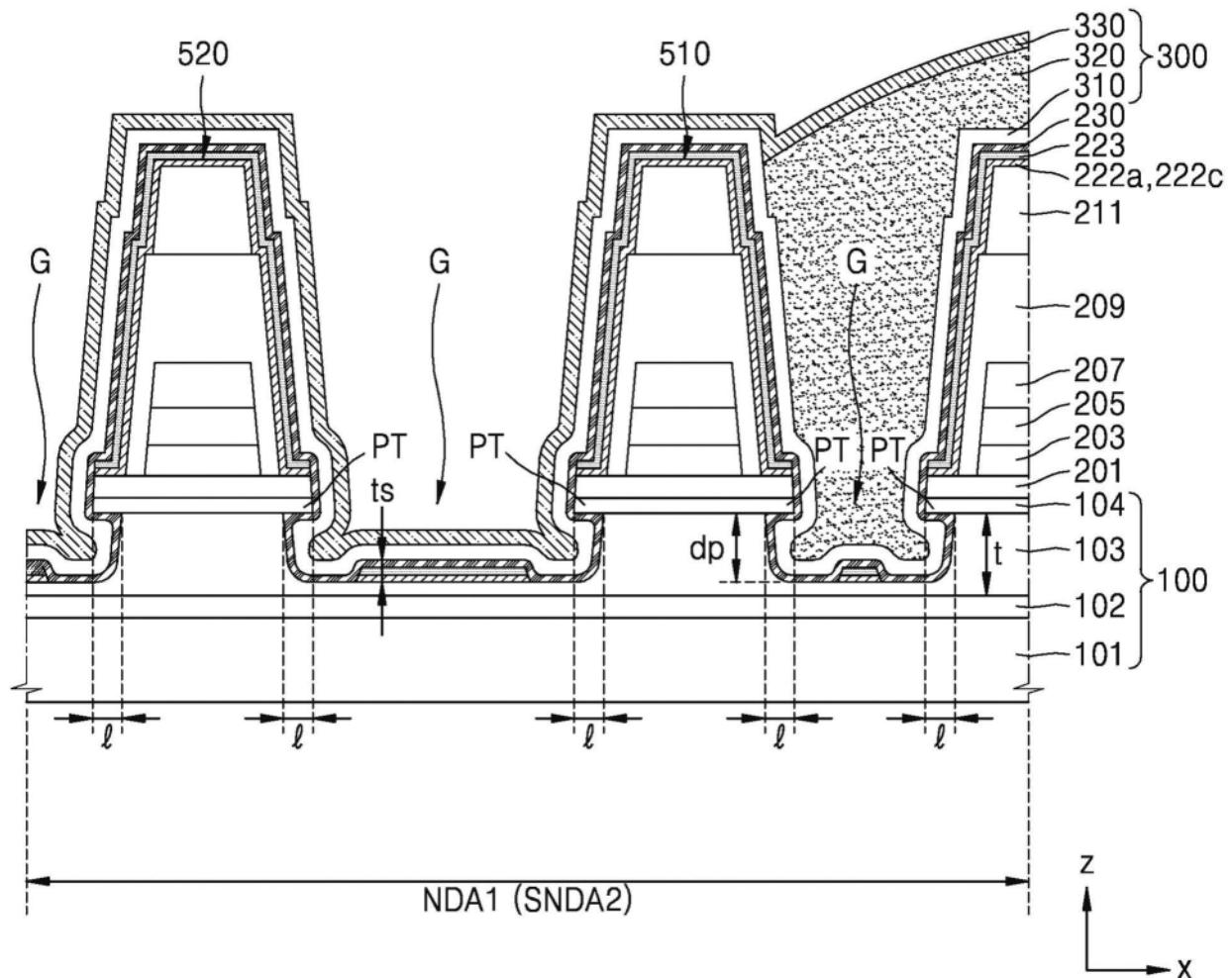

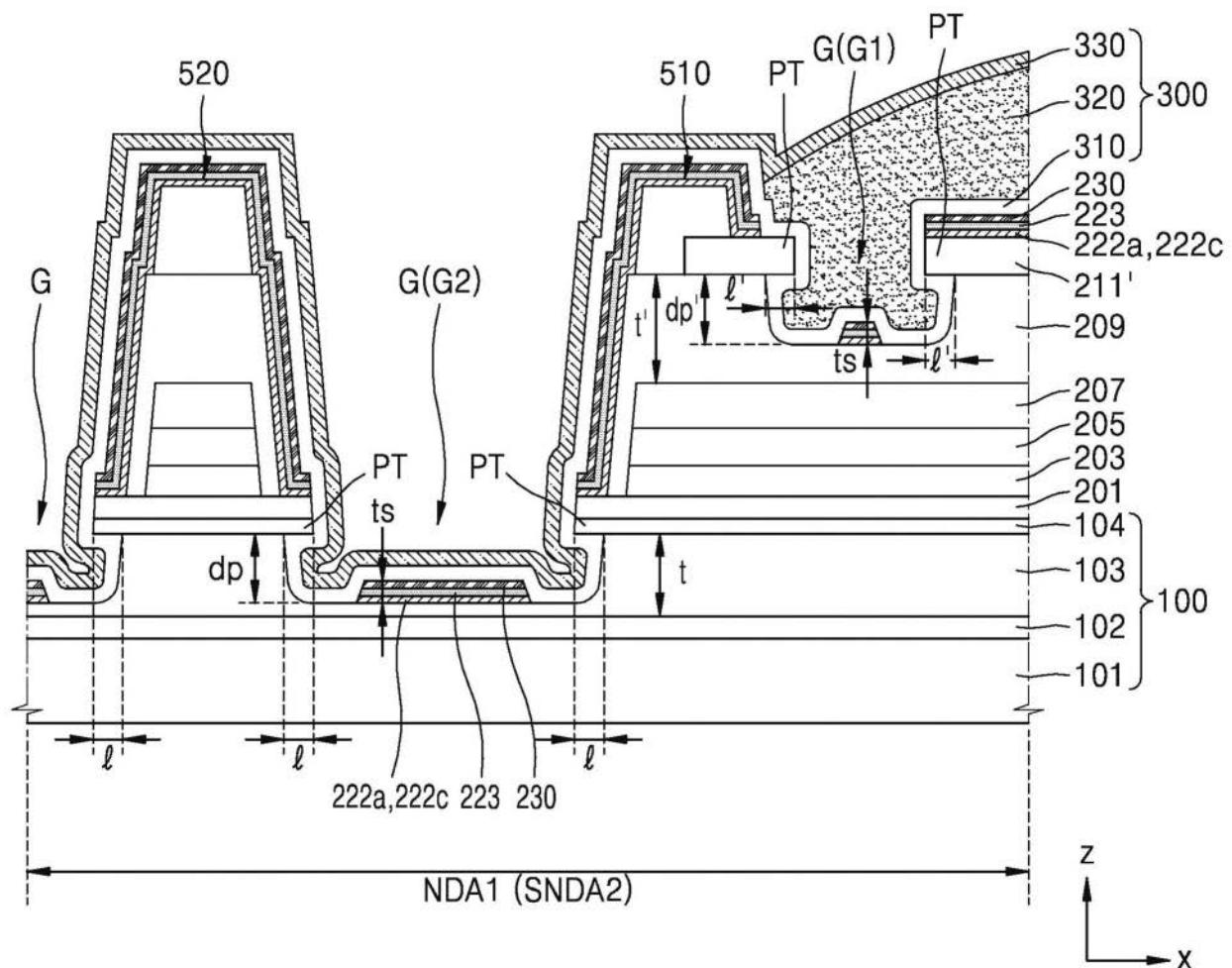

[0164] 图15是根据示例性实施例的布置在显示面板10的第一非显示区域NDA1中的凹槽G的剖视图。

[0165] 参照图15,多个凹槽G的一个凹槽G(称为第一凹槽G1)可以位于基底100之上,并且可以通过去除基底100的一些子层来形成另一凹槽G(称为第二凹槽G2)。由于第二凹槽G2的特征与参照图8A至图11描述的特征相同,因此下面主要描述第一凹槽G1。

[0166] 例如,第一凹槽G1可以通过去除第一绝缘层209的部分和设置在第一绝缘层209上的第二绝缘层211'来形成。第一绝缘层209可以对应于上面参照图8A和图8B描述的多层ML的第一层L1,并且第二绝缘层211'可以对应于多层ML的第二层L2。第一绝缘层209可以包括诸如以聚酰亚胺为例的有机材料,第二绝缘层211'可以包括诸如以氮化硅、氮氧化硅和/或氧化硅为例的无机材料。

[0167] 第一凹槽G1可以具有底切剖面。例如,如图15中所示,第二绝缘层211'的孔和第一绝缘层209的凹部可以构成第一凹槽G1。在示例性实施例中,第二绝缘层211'的孔和第一绝缘层209的孔可以构成第一凹槽G1。

[0168] 提供到第二绝缘层211'的尖端PT的长度 $\ell'$ 的特征与上面参照图8A和图8B描述的长度 $\ell$ 的特征相同。例如,尖端PT的长度 $\ell'$ 可以小于约2.0 $\mu\text{m}$ 。

[0169] 第一凹槽G1的深度 $dp'$ (即,第一绝缘层209的凹部或孔的深度)的特征与上面参照图8A和图8B描述的深度 $dp$ 的特征相同。例如,第一凹槽G1的深度 $dp'$ 可以大于尖端PT的长度 $\ell'$ 。第一凹槽G1的深度 $dp'$ 可以约等于或小于第一绝缘层209的厚度 $t'$ ,并且可以为例如约2.0 $\mu\text{m}$ 或更大、或约3.0 $\mu\text{m}$ 或更大。

[0170] 这里,第一绝缘层209的厚度 $t'$ 是第一绝缘层209的在其中布置有第一凹槽G1的区域中的顶表面与底表面之间的竖直距离。在图15中,第二层间绝缘层207的顶表面可以是第一绝缘层209的底表面。

[0171] 如参照图8A和图8B描述的,第一功能层222a、第二功能层222c、对电极223和盖层230可以在第一凹槽G1和第二凹槽G2周围断开,并且第一凹槽G1和第二凹槽G2各自的深度 $dp'$ 和 $dp$ 可以比第一功能层222a、第二功能层222c、对电极223和盖层230的堆叠件的厚度 $ts$ 大。

[0172] 第一凹槽G1和第二凹槽G2各自的内表面可以被第一无机封装层310连续地覆盖。第一凹槽G1的设置在第一无机封装层310之上的空间可以至少部分地填充有有机封装层320。第一分隔壁510可以位于第一凹槽G1与第二凹槽G2之间,并且有机封装层320的一端可以位于第一分隔壁510的一侧上。

[0173] 尽管图15中示出了第二凹槽G2具有与图10中示出的凹槽G的结构相同的结构,但本公开不限于此。例如,在示例性实施例中,第二凹槽G2可以具有与参照图11至图14描述的凹槽G的结构相同的结构。

[0174] 参照图15描述的特征(例如,第一非显示区域NDA1的凹槽G(例如,第一凹槽G1和第二凹槽G2)形成在不同的多层中的特征)可适用于其它示例性实施例。例如,上述特征可适用于上面参照图10至图14描述的示例性实施例以及下面参照图16描述的示例性实施例。

和/或由此衍生的示例性实施例。

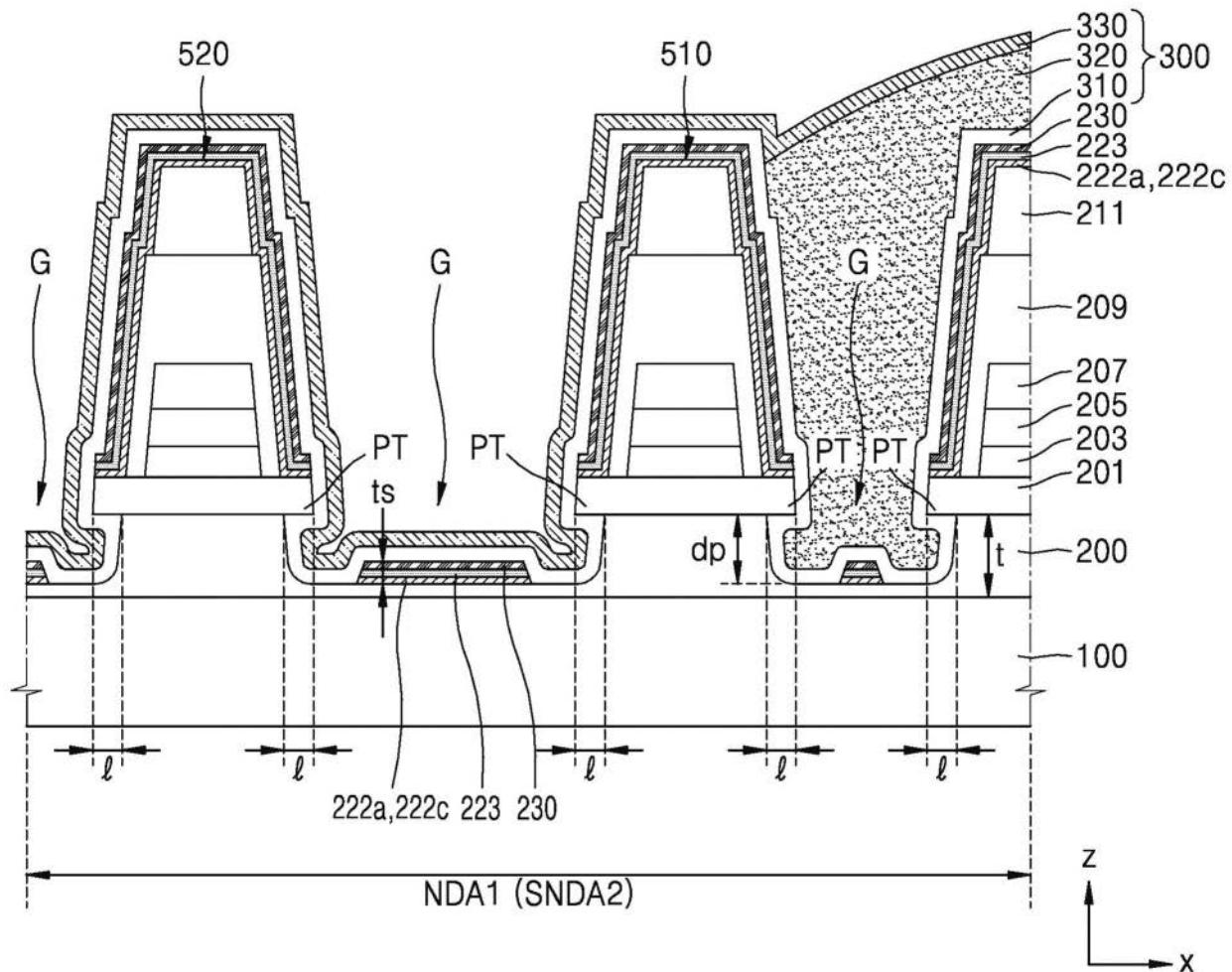

[0175] 图16是根据示例性实施例的布置在显示面板10的第一非显示区域NDA1中的凹槽G的剖视图。

[0176] 参照图16,一个或更多个凹槽G可以形成在多层(例如,包括位于基底100上的绝缘层200和缓冲层201的多层)中。绝缘层200可以包括与缓冲层201的材料不同的材料,诸如以有机材料(诸如聚酰亚胺)为例。缓冲层201可以包括如参照图7描述的无机材料。绝缘层200不仅可以设置在第一非显示区域NDA1中,而且可以设置在显示区域DA中,如图16中所示,并且可以位于基底100与缓冲层201之间。

[0177] 凹槽G可以具有底切剖面。缓冲层201的孔以及绝缘层200的凹部或孔可以在空间上彼此连接以构成凹槽G。缓冲层201的朝向凹槽G的中心延伸的尖端PT的长度 $\ell$ 与上面参照图8A和图8B描述的尖端PT的长度 $\ell$ 相同。例如,尖端PT的长度 $\ell$ 可以小于约 $2.0\mu\text{m}$ 。凹槽G的深度dp可以约等于或小于绝缘层200的厚度t。由于深度dp的其它特征与参照图8A和图8B描述的特征相同,因此省略了其重复描述。

[0178] 由于凹槽G形成在包括布置在基底100上的绝缘层200和缓冲层201的多层中,因此基底100可以包括各种类型的材料。例如,基底100可以包括无机材料或有机材料,或者可以包括无机材料和有机材料两者。例如,基底100可以包括诸如玻璃、金属和/或树脂的各种类型的材料。

[0179] 图17是根据示例性实施例的显示面板10'的剖视图。

[0180] 图17中示出的显示面板10'与上面参照图9描述的显示面板10的不同之处在于显示面板10'还包括平坦化层410。在下文中,为了便于描述,主要描述显示面板10'与显示面板10的不同之处。

[0181] 平坦化层410可以包括有机绝缘材料。在示例性实施例中,平坦化层410可以通过在薄膜封装层300上涂覆光致抗蚀剂(负性或正性光致抗蚀剂)或聚合物类有机材料并且对其进行图案化而形成。如图17中所示,平坦化层410的端部410E可以布置在穿过凹槽G中的一个凹槽G的竖直线上。在示例性实施例中,平坦化层410的端部410E可以与基底100的端部100E布置在同一条竖直线上。

[0182] 平坦化层410可以通过覆盖第二子非显示区域SNDA2的其中没有有机封装层320的区域来改善显示面板10'的平坦度。因此,可以防止直接形成在显示面板10'上或通过使用粘合剂层结合在显示面板10'上的输入感测构件或光学功能构件与显示面板10'分离或从显示面板10'脱落。

[0183] 根据这里描述的示例性实施例的显示面板可以防止具有底切剖面的凹槽被损坏,并且可以防止显示元件被诸如外部湿气的异物损坏。然而,这些效果作为示例被提供,本公开的范围不受这些效果的限制。

[0184] 虽然已经参照本公开的示例性实施例具体地示出并描述了本公开,但是本领域普通技术人员将理解的是,在不脱离如由所附权利要求限定的本公开的精神和范围的情况下,可以在其中作出形式和细节上的各种改变。

图1

图2

图3

图4

图5

图6

图7

图8A

图8B

图8C

图8D

图9

图10

图11

图12

图13

图14

图15

图16

图17