(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-330000

(P2007-330000A)

(43) 公開日 平成19年12月20日(2007.12.20)

|                  |           |             |

|------------------|-----------|-------------|

| (51) Int.CI.     | F 1       | テーマコード (参考) |

| <b>H02P 8/40</b> | H02P 8/00 | 5H572       |

| <b>H02P 5/00</b> | H02P 7/67 | 5H580       |

審査請求 未請求 請求項の数 7 O L (全 9 頁)

|           |                              |            |                                                                                                 |

|-----------|------------------------------|------------|-------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2006-157611 (P2006-157611) | (71) 出願人   | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号                                                   |

| (22) 出願日  | 平成18年6月6日 (2006.6.6)         | (74) 代理人   | 100079108<br>弁理士 稲葉 良幸                                                                          |

|           |                              | (74) 代理人   | 100080953<br>弁理士 田中 克郎                                                                          |

|           |                              | (74) 代理人   | 100093861<br>弁理士 大賀 真司                                                                          |

|           |                              | (72) 発明者   | 吉田 裕二<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内                                                          |

|           |                              | F ターム (参考) | 5H572 AA13 CC08 DD08 EE04 FF01<br>FF06 JJ03 JJ17<br>5H580 AA05 FA14 FA22 FB05 FC04<br>FD00 GG04 |

(54) 【発明の名称】モータ制御装置

## (57) 【要約】

【課題】複数のモータを独立に駆動制御できるモータ制御装置を提供することを目的とする。また、複数のモータを同時に駆動開始及び停止可能なモータ制御装置を提供することを目的とする。

【解決手段】複数のモータの駆動を制御するモータ制御装置100において、複数のモータMのそれぞれに、各モータMの駆動を独立に制御するモータ制御ブロック18を備えている。そして、各モータ制御ブロック18は、モータを駆動制御するための信号を生成するためのパルスデータ値を格納する記憶手段(テーブルバッファ)24と、記憶手段24から順次転送されるパルスデータ値に基づいて、モータを駆動制御するための信号を生成し、モータに出力するパルス生成手段22と、を備えている。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

複数のモータの駆動を制御するモータ制御装置において、

複数のモータのそれぞれに、各モータの駆動を独立に制御するモータ制御ブロックを備え、

各モータ制御ブロックは、

当該モータ制御ブロックに接続されたモータを駆動制御するための信号を生成するためのパルスデータ値を格納する記憶手段と、

前記記憶手段から順次転送されるパルスデータ値に基づいて、モータを駆動制御するための信号を生成し、当該モータ制御ブロックに接続されたモータに出力するパルス生成手段と、

を備えるモータ制御装置。

**【請求項 2】**

前記モータ制御装置は、

複数のモータの駆動開始及び停止を制御するスタート/ストップ手段を、複数のモータ制御ブロックが共有し、前記複数のモータに対して駆動開始及び停止を同時に制御できる、

前記請求項1記載のモータ制御装置。

**【請求項 3】**

前記記憶手段は、

記憶配列の末尾と先頭をつないでデータを環状に記憶管理するリングバッファ構成であり、無限長のパルスデータを設定可能である、

前記請求項1又は2記載のモータ制御装置。

**【請求項 4】**

前記記憶手段は、

二個の記憶配列を備えるダブルバッファ構成であり、一の記憶配列からパルスデータ値の読み出しを行っている間に、他の記憶配列へパルスデータ値の書き込みが可能である、

前記請求項1又は2記載のモータ制御装置。

**【請求項 5】**

前記モータ制御装置は、

前記モータ制御装置の動作全体を制御する制御手段と、

を備え、

前記記憶手段は、エンプティニアエンド又はエンド割り込みを出力し、前記記憶手段が空になるタイミングを前記制御手段に通知する機能を備え、

前記制御手段は、

前記記憶手段からエンプティニアエンド又はエンド割り込みを受信すると、前記記憶手段に対して、パルスデータ値の書換えを行う、

前記請求項1乃至4のいずれかに記載のモータ制御装置。

**【請求項 6】**

前記モータ制御装置は、

前記モータ制御装置の動作全体を制御する制御手段と、

を備え、

前記記憶手段は、現在読み出されているアドレスを読み出す機能を備え、

前記制御手段は、

前記記憶手段から受信したアドレスに基づいて、前記記憶手段に対して、出力済みのパルスデータ値の書換えを行う、

前記請求項1乃至5のいずれかに記載のモータ制御装置。

**【請求項 7】**

前記モータはステッピングモータであり、

前記パルスデータ値は、

10

20

30

40

50

各モータへ出力する信号の状態を規定する第1データと出力信号のパルス幅を規定する第2データとを備える、

前記請求項1乃至6記載のモータ制御装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はモータ制御装置、特に複数のモータの駆動制御を行うモータ制御装置に関するものである。

【背景技術】

【0002】

従来、プリンタなどの用紙搬送等の動力源として、相信号の組み合わせにより制御されるモータ（ステッピングモータ）が用いられている。ステッピングモータの制御は、CPUのタイマ機能を用いてステッピングモータへのパルス出力タイミングを生成し、タイマ割り込みが発生したときに、CPUからモータへ信号を出力している。このタイマの設定を、モータのステップ駆動間隔に設定することにより加減速および定速制御を実施している。

【0003】

しかし、この制御方式は、タイマ割り込み毎にCPUがモータへ信号を出力する必要があるためCPUに負荷がかかり、他の処理に支障ができる。また、タイマ割り込み処理が起動するまでに処理時間がかかるため、正確なステッピングパルス制御ができない。そこで、特許文献1記載の発明では、DMAコントローラ（Direct Memory Access Controller）の機能を利用して、CPUを介さずに外部メモリからステッピングパルスデータ値をモータ制御ブロックに直接転送し、所望の動作を得るようにしている。

【特許文献1】特開2001-286190号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、特許文献1記載のものは、モータに制御信号を出力する度ごとに、モータ制御ブロックに内蔵したDMAコントローラにより外部メモリに格納されたステッピングパルスデータ値をモータ制御ブロックが読み出しが、外部メモリは複数のモータで共通で使用されるため、複数のモータが同時に動作する場合は、調停時間がかかり、その結果、ステッピングパルス信号の出力タイミングが設定値からずれる可能性がある。

【0005】

また、外部メモリは有限長であるため、モータに対して無限長のステッピングパルスを出力したい場合は、DMAコントローラのデータ転送が終了した後、すぐに次のデータを外部メモリに設定し、DMAコントローラの再起動が必要となり、その間モータへ駆動パルス信号出力に遅延が発生する。

【0006】

本発明は、かかる事情に鑑みてなされたものであり、複数のモータを独立に駆動制御できるモータ制御装置を提供することを目的とする。また、複数のモータを同時に駆動開始及び停止可能なモータ制御装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明によるモータ制御装置は、複数のモータの駆動を制御するモータ制御装置において、複数のモータのそれぞれに、各モータの駆動を独立に制御するモータ制御ブロックを備えている。そして、各モータ制御ブロックは、当該モータ制御ブロックに接続されたモータを駆動制御するための信号を生成するためのパルスデータ値を格納する記憶手段と、記憶手段から順次転送されるパルスデータ値に基づいて、モータを駆動制御するための信号を生成し、当該モータ制御ブロックに接続されたモータに出力するパルス生成手段と、を備えている。かかる発明によれば、モータ制御ブロックに

パルスデータ値を格納するバッファを個別に設けることにより、モータと一対一のデータ格納、及び、複数モータの完全な独立駆動が可能となる。

#### 【0008】

また、モータ制御装置は、複数のモータの駆動開始及び停止を制御するスタート／ストップ手段を、複数のモータ制御ブロックが共有し、複数のモータに対して駆動開始及び停止を同時に制御できることが望ましい。かかる発明によれば、複数のモータに対して、同時に駆動開始及び停止を実現することが可能となる。

#### 【0009】

好適には、記憶手段は、記憶配列の末尾と先頭をつないでデータを環状に記憶管理するリングバッファ構成、又は、二個の記憶配列を備えるダブルバッファ構成である。リングバッファ構成を採用すると、無限長のパルスデータを設定可能である。また、ダブルバッファ構成を採用すると、一の記憶配列からパルスデータ値の読み出しを行っている間に、他の記憶配列へパルスデータ値の書き込みが可能である。

#### 【0010】

また、好適には、記憶手段はエンプティニアエンド又はエンド割り込みを出力し、記憶手段が空になるタイミングを制御手段に通知する機能を備えている。ここで、制御手段とは、モータ制御装置の動作全体を制御するものであり、記憶手段からエンプティニアエンド又はエンド割り込みを受信すると、記憶手段に対して、パルスデータ値の書換えを行うようになっている。或いは、記憶手段は、現在読み出されているアドレスを読み出す機能を備え、制御手段は、記憶手段から受信したアドレスに基づいて、記憶手段に対して、出力済みのパルスデータ値の書換えを行うようになっている。かかる発明によれば、記憶手段に格納されているパルスデータ値を適切なタイミングで書換えることができる。

#### 【0011】

さらに、好適には、モータはステッピングモータであり、パルスデータ値は、各モータへ出力する信号の状態を規定する第1データと出力信号のパルス幅を規定する第2データとを備える。

#### 【0012】

なお、本明細書等において、手段とは、単に物理的手段を意味するものではなく、その手段が有する機能をソフトウェアによって実現する場合も含む。また、1つの手段が有する機能が2つ以上の物理的手段により実現されても、2つ以上の手段の機能が1つの物理的手段により実現されてもよい。

#### 【発明を実施するための最良の形態】

#### 【0013】

以下、本発明の実施の形態について図面を参照しつつ詳細に説明する。なお、同一の要素には同一の符号を付し、重複する説明を省略する。

#### 【0014】

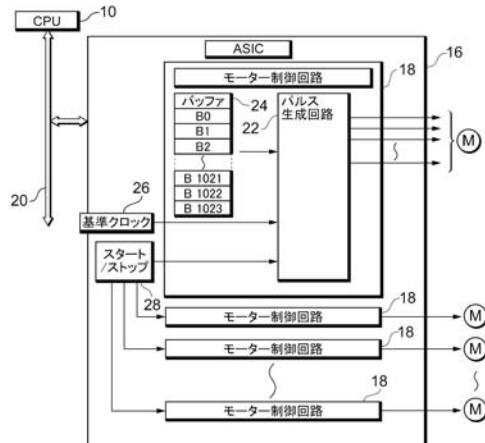

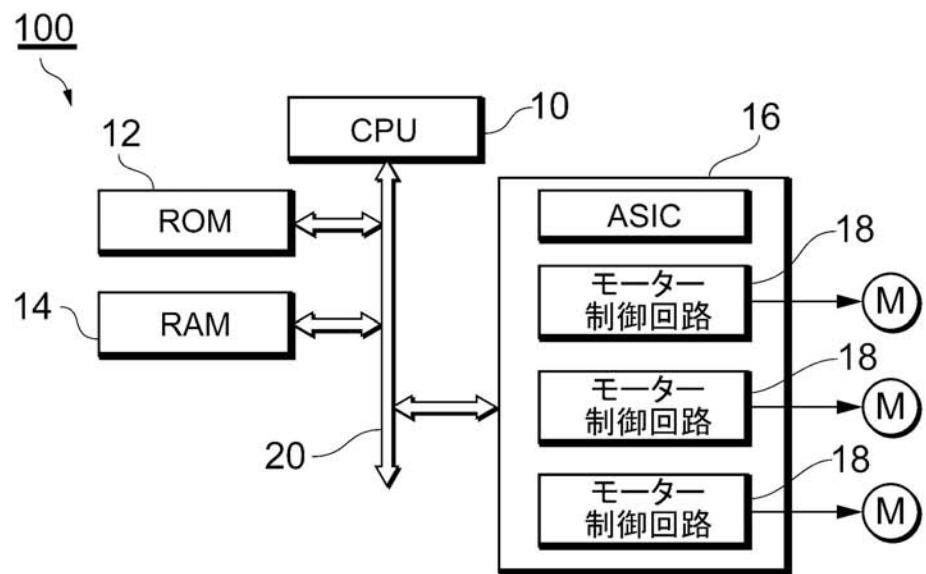

図1及び図2は、本発明によるモータ制御装置100のシステム構成の一例を示すブロック図である。図1は、モータ制御装置100の全体構成を示す図である。また、図2はモータ制御装置100の一部、特にモータ制御ユニット16の構成を示す図である。

#### 【0015】

図1に示すとおり、本実施形態におけるモータ制御装置100は、CPU10と、ROM12と、RAM14と、モータ制御ユニット16とが、それぞれバス20に接続され、これらの間で種々のデータを相互に伝達できるようになっている。また、モータ制御ユニット16は複数のモータ制御ブロック18を備え、各モータ制御ブロック18にモータMが接続されている。

#### 【0016】

ここで、CPU10は、モータ制御装置100の動作全体を制御する制御手段であり、RAM14をワークエリアとして、ROM12に格納されたプログラムに従って処理や命令を実行し、モータMの駆動制御を行う。また、複数のモータMは、プリンタの紙送り等のための動力源として用いられるステッピングモータであり、各モータMはそれぞれ各モ

10

20

30

40

50

ータ制御ブロック 18 により駆動制御される。

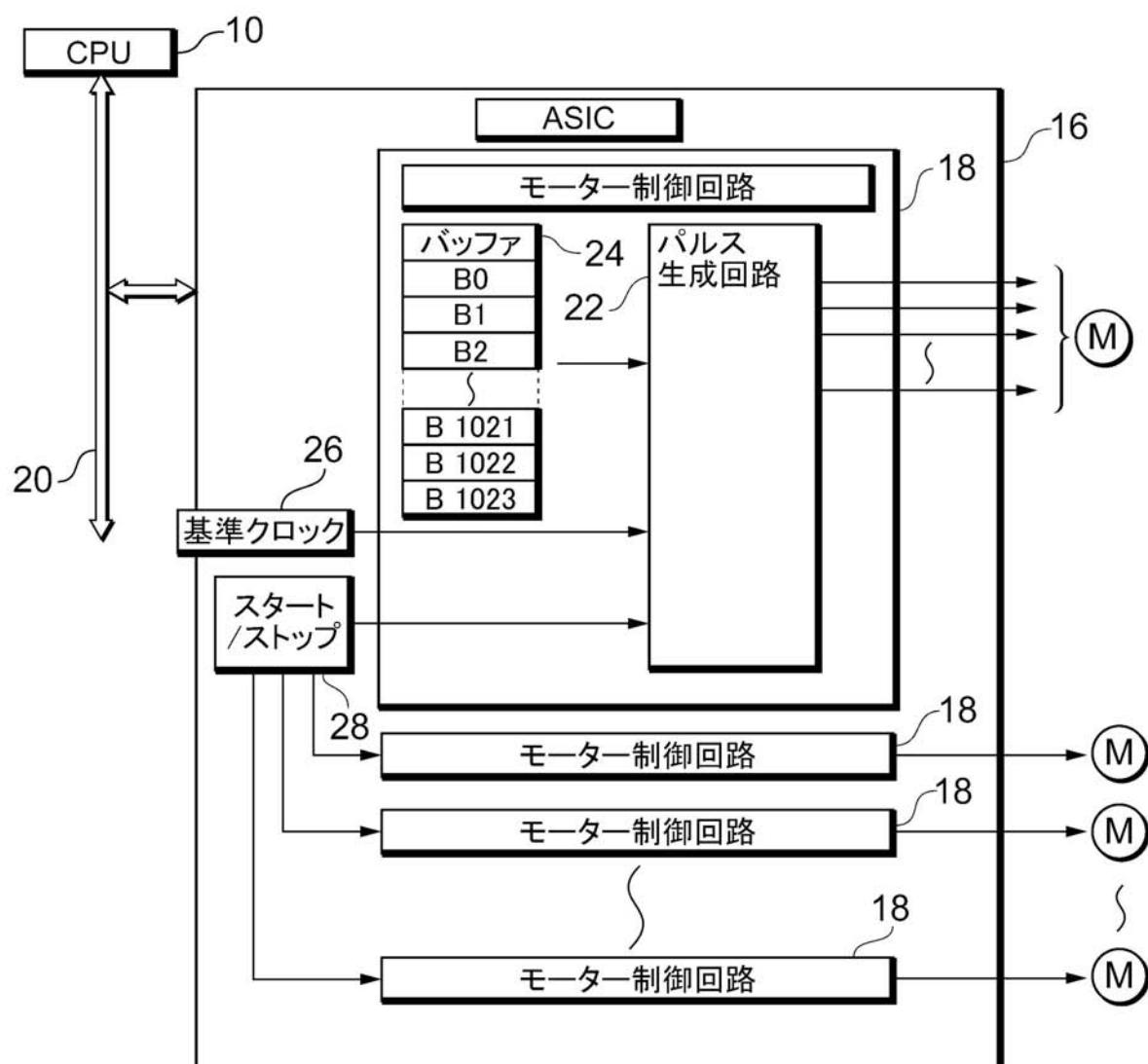

【0017】

また、モータ制御ユニット 16 は、モータ制御用に設計された集積回路（ASIC）であり、図2に示すとおり、複数のモータ制御ブロック 18 をパラレルに備えている。そして、複数のモータ制御ブロック 18 の各々は、モータMに入力される制御信号を生成するためのパルス生成回路 22 と、モータMを駆動制御するためのステッピングパルス信号を生成するためのパルスデータ値を格納するテーブルバッファ（RAM）24 とを備えている。なお、図2では図示を一部省略しているが、各モータ制御ブロック 18 は全て、パルス生成回路 22 及びテーブルバッファ 24 を備えている。このように、一のモータMに対して、一のテーブルバッファ 24 を設けることにより、モータMとパルスデータ値テーブルを一対一で備え、かつ、複数モータMの完全な独立駆動を可能としている。10

【0018】

そして、モータ制御ブロック 18 では、テーブルバッファ 24 に格納されているパルスデータ値がパルス生成回路 22 に順次転送され、パルス生成回路 22 は、転送されたパルスデータ値に基づいてモータ制御信号を生成し、モータMに出力する。このように、パルスデータ値がパルス生成回路 22 へ、CPU10 を介すこと無く、また、ROM12 や RAM14 等の外部メモリから毎回読み出されること無く、テーブルバッファ 24 からデータ転送がなされる。また、モータMに信号が出力されると、当該信号がフィードバックされ、パルス生成回路 22 に対して次のデータ転送が促される。なお、パルスデータ値は、テーブルバッファ 24 の任意のバッファアドレスからデータ転送が開始され、任意のバッファアドレスで終了可能であり、データ転送が終了した後に CPU10 への割り込みを発生する。20

【0019】

さらに、モータ制御ユニット 16 は、パルス生成用の基準クロックを各パルス生成回路 22 に送るための基準クロック回路 26 と、複数のモータMに対して駆動開始及び停止、すなわち各パルス生成回路 22 の動作の開始及び停止を制御するスタート/ストップ回路 28 と、を備えている。基準クロック回路 26 とスタート/ストップ回路 28 は、複数のモータ制御ブロック 18 により共有され、基準クロック回路 26 の出力信号とスタート/ストップ回路 28 の出力信号は、複数のモータ制御ブロック 18 のそれぞれに入力されるようになっている。基準クロック回路 26 は、各モータ制御ブロック 18 に対して共通の基準クロックを提供する。また、スタート/ストップ回路 28 は、CPU10 が、駆動を開始又は停止するモータMをスタート/ストップ回路 28 に指定すると、スタート/ストップ回路 28 から各モータ制御ブロック 18 に、スタート/ストップ信号が送出され、この信号に基づいて、モータ制御ブロック 18 が動作を開始又は停止するようになっている。スタート/ストップ回路 28 の出力信号は、モータ制御装置 100 の備えるモータMの数に等しいビット長を有し、各ビット毎に一のモータM（モータ制御ブロック 18 ）が割り当てられている。そして、各ビット毎に 1 又は 0 を立ててモータ制御ブロック 18 に信号を出力することにより、各ビットに対応するモータ制御ブロック 18 に対して、同時にかつ独立に、動作の開始又は停止を指示できるようになっている。30

【0020】

図3は、各モータ制御ブロック 18 が個別に備えるテーブルバッファ 24 に記憶されるパルスデータ値の一例を示す図である。図3に示すとおり、テーブルバッファ 24 は、1024 個のバッファからなり、各バッファは 12 ビットで構成されている。この 12 ビットのうち、上位 4 ビット（第1データ）はモータMへの出力信号（モータ制御信号）の状態を指示するためのものであり、各ビットの 0 / 1 により、各出力信号状態の L（ロー）/ H（ハイ）を規定している。また、下位 8 ビット（第2データ）はパルス幅を設定するためのものであり、上位 4 ビットで指定されるモータ制御信号の状態が出力される期間（出力周期）が設定されるようになっている。このように、上位 4 ビットの出力信号及び下位 8 ビットのパルス幅設定により、ステッピングモータMの種々様々な駆動に対応できるようになっている。40

## 【0021】

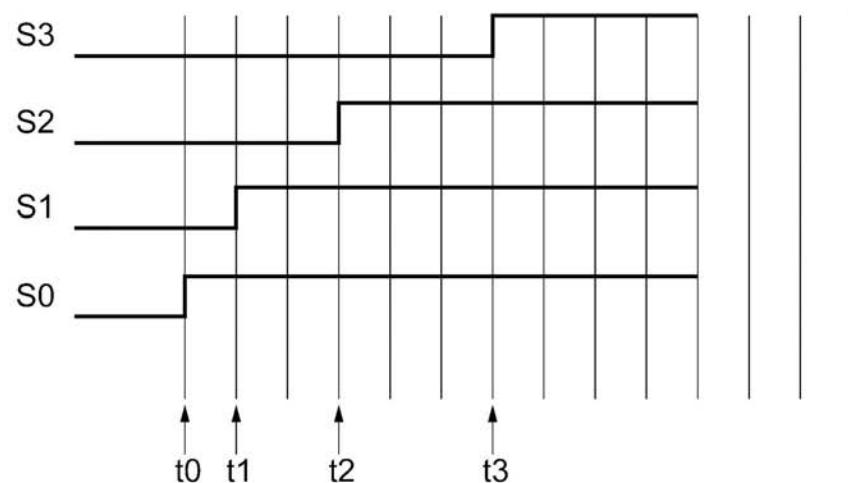

図4は、パルス生成回路22からモータMへ出力されるモータ制御信号を示す図である。パルス生成回路22は、スタート/ストップ回路28からスタート指示を受けると、テーブルバッファ24に格納されているパルスデータ値を順次読み出して、モータ制御信号を生成し、出力する。図4は、図3に示されるバッファ0からバッファ3までのテーブルデータによって出力されるモータ制御信号を示している。同図において、時間の刻み幅は、基準クロックの刻み幅を表している。図4に示す図では、時刻t0にスタート/ストップ回路28からスタート指示信号を受信して、モータ制御信号の出力を開始する。まず、スタート指示信号を受信すると、テーブルバッファ24のバッファB0に格納されているパルスデータ値がパルス生成回路22に転送され、パルス生成回路22が出力信号S0をH、出力信号S1, S2, S3をLで1パルス幅(基準クロック1つ分)のパルス信号(モータ制御信号)を生成し、モータMに出力する。そして、1パルス幅時間経過後(時刻t1)に、次のバッファB1からパルス生成回路22にパルスデータ値が転送され、パルス生成回路22が出力信号S0, S1をH、出力信号S2, S3をLで2パルス幅のパルス信号を生成し、モータMに出力する。その後、2パルス幅時間経過後(時刻t2)に、バッファB2からパルス生成回路22にパルスデータ値が転送され、出力信号S0, S1, S2をH、出力信号S3をLで3パルス幅のパルス信号を生成、出力する。以降同様の処理を繰り返し、モータ制御ブロック18は、テーブルバッファ24に格納されているパルスデータ値を順次パルス生成回路22に転送して、パルス生成回路22が転送されたパルスデータ値に基づいてパルス信号を生成し、モータMに出力する。そして、パルス生成ブロック18が、スタート/ストップ回路28からストップ信号を受信するまで、このモータ制御信号の生成・出力処理を繰り返す。

## 【0022】

本実施形態において、テーブルバッファ24は、記憶配列の末尾と先頭をつないでデータを環状に記憶管理するリングバッファ構成を有することが望ましい。リングバッファ構成を採用することにより、無限長のパルスデータを設定できるようになり、モータMの無限駆動が可能になる。また、バッファサイズを軽減することができ、コスト軽減にもつながる。

## 【0023】

また、テーブルバッファ24は、バッファエンドが近づいていることを示すバッファエンプティニアエンド又はバッファエンドにおいて、割込みをCPU10に出力できるようになっている。これにより、バッファが空になるタイミングをCPU10に通知できるので、CPU10は、バッファが空になる前に、ROM12又はRAM14に記憶されているパルスデータ値を、テーブルバッファ24に書き込むことが可能となる。書き込み(書換え)のタイミングは、CPU10の処理速度やテーブルバッファ24のサイズ等により決定するとよい。

## 【0024】

さらに、テーブルバッファ24に、現在読み出されている(パルス生成回路22に転送されている)バッファアドレスを読み出す機能を設けてもよい。これにより、CPU10は、どのパルスデータ値まで出力されているかを確認できるため、パルスデータ値の転送済み箇所に次のデータを設定できるようになる。

## 【0025】

また、テーブルバッファ24をリングバッファ構成とする代わりに、2個の記憶配列を切り替えて使用するダブルバッファ構成としてもよい。ダブルバッファ構成を採用することにより、一方の記憶配列からパルスデータ値を読み出している間に、他方の記憶配列にパルスデータ値を書き込むことができるので、継ぎ目無くモータMを駆動制御できる。

## 【0026】

以上のように構成されるモータ制御装置100の動作の概要について説明する。

## 【0027】

まず、CPU10は、各モータMの動作パターンに対応するパルスデータ値のテーブル

10

20

30

40

50

を R O M 1 2 又は R A M 1 4 から読み出し、各モータMに一対一に対応して備えられるテーブルバッファ2 4 を書き込んでおく。このとき、複数のモータMをそれぞれ異なる動作パターンで駆動制御する場合には、各テーブルバッファ2 4 に、それぞれ異なるパルスデータ値のテーブルが書き込まれることになる。そして、C P U 1 0 が、駆動を開始するモータMをスタート/ストップ回路2 8 に指定すると、スタート/ストップ回路2 8 から所定のモータ制御ブロック1 8 にスタート信号が送出され、この信号に基づいて、モータ制御ブロック1 8 が動作を開始する。

#### 【 0 0 2 8 】

モータ制御ブロック1 8 が動作を開始すると、テーブルバッファ2 4 からパルスデータ値が順次パルス生成回路2 2 に転送され、転送されたパルスデータ値によって示されるパルス信号が生成され、モータMに出力される。その後、テーブルバッファ2 4 の書換え時を除いて、C P U 1 0 を介することなく、テーブルバッファ2 4 からパルス生成回路2 2 へのデータ転送、及びモータ駆動信号の生成・出力処理が繰り返される。なお、テーブルバッファ2 4 がバッファエンプティニアエンド等を検出すると、C P U 1 0 に通知され、テーブルバッファ2 4 のパルスデータ値のテーブルが書き換えられる。

#### 【 0 0 2 9 】

モータMの駆動を停止するとき、C P U 1 0 は、スタート/ストップ回路2 8 に所定のモータMの駆動を停止するよう指示を出す。この指示に基づいて、スタート/ストップ回路2 8 から所定のモータ制御ブロック1 8 にストップ信号が送出され、この信号に基づいて、モータ制御ブロック1 8 が動作を停止する。

#### 【 0 0 3 0 】

以上のとおり、本発明のモータ制御装置は、複数のモータ制御ブロック1 8 のそれにテーブルバッファ2 4 を設け、モータMと一対一のデータ格納及び完全な独立駆動を可能にしている。また、これにより、複数のモータMに対して、同時に駆動開始及び停止を制御可能である。

#### 【 0 0 3 1 】

なお、本発明は、上記した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲内において他の様々な形で実施することができる。このため、上記実施形態はあらゆる点で単なる例示にすぎず、限定的に解釈されるものではない。

#### 【 0 0 3 2 】

例えば、上述の動作概要は処理内容に矛盾を生じない範囲で任意に順番を変更して又は並列に実行することができる。

#### 【 図面の簡単な説明 】

#### 【 0 0 3 3 】

【図1】モータ制御装置1 0 0 の全体構成を示す図である。

【図2】モータ制御ユニット1 6 の構成を示す図である。

【図3】テーブルバッファ2 4 に格納されるパルスデータ値の一例を示す図である。

【図4】パルス生成回路2 2 から出力されるモータ制御信号を示す図である。

#### 【 符号の説明 】

#### 【 0 0 3 4 】

1 0 C P U 、 1 2 R O M 、 1 4 R A M 、 1 6 モータ制御ユニット、 1 8 モータ制御ブロック、 2 0 バス、 2 2 パルス生成回路(パルス生成手段)、 2 4 テーブルバッファ(記憶手段)、 2 6 基準クロック回路、 2 8 スタート/ストップ回路、 1 0 0 モータ制御装置、 M モータ

10

20

30

40

【図1】

【図2】

【図3】

| 出力信号:3-0 |    |    |    | パルス幅設定7-0 |       |

|----------|----|----|----|-----------|-------|

|          | S3 | S2 | S1 | S0        |       |

| B0       | 0  | 0  | 0  | 1         | 1パルス幅 |

| B1       | 0  | 0  | 1  | 1         | 2パルス幅 |

| B2       | 0  | 1  | 1  | 1         | 3パルス幅 |

| B3       | 1  | 1  | 1  | 1         | 4パルス幅 |

【図4】