(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-105997

(P2006-105997A)

(43) 公開日 平成18年4月20日(2006.4.20)

(51) Int.C1.

GO1R 31/28 (2006.01)

GO1R 31/3183 (2006.01)

F 1

GO1R 31/28

GO1R 31/28

GO1R 31/28

テーマコード(参考)

G

V

Q

審査請求 未請求 請求項の数 10 O L (全 9 頁)

(21) 出願番号 特願2005-292299 (P2005-292299)

(22) 出願日 平成17年10月5日 (2005.10.5)

(31) 優先権主張番号 10/959856

(32) 優先日 平成16年10月5日 (2004.10.5)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

AGILENT TECHNOLOGIE

S, INC.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

最終頁に続く

(54) 【発明の名称】電子デバイスにスキャンパターンを提供する方法および装置

(57) 【要約】 (修正有)

【課題】 欠陥スキャン区間の識別を容易化する。

【解決手段】 電子デバイス(100)は、生産テストモードと診断テストモードを備えたBISTハードウェア(102、104)を有し、スキャンパターンを提供すると、生産テストモードで応答シグネチャを出力し、診断テストモードで生応答データを出力する。生産テストモードで、ATE(114)から、i)第1のスキャンテストパターンをBISTハードウェア(102、104)に提供し、ii)応答シグネチャと予想応答シグネチャとを比較して、欠陥スキャンテストパターンを識別する。次に、ATE(114)により、欠陥スキャンテストパターンと関連した固有ラベルを識別し、診断テストモードで、i)第2のスキャンテストパターンをBISTハードウェア(102、104)に提供し、ii)生応答データを捕捉する。第2のスキャンテストパターンは、識別されたラベルに対応する。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

組み込み自己テストハードウェアを有する電子デバイスにスキャンパターンを提供する方法であって、前記自己テストハードウェアが、生産テストモードと診断テストモードを有し、前記電子デバイスが、前記生産テストモードで1つまたは複数の応答シグネチャを出力し、前記診断テストモードで生応答データを出力し、

生産テストモードにおいて、自動テスト機器を使用して、i) 第1の一連のスキャンテストパターンを前記自己テストハードウェアに提供し、ii) 応答シグネチャを捕捉し予想応答シグネチャと比較して、いくつかの欠陥スキャンテストパターンを識別するステップと、

前記自動テスト機器を使用して、前記欠陥スキャンテストパターンと関連したいくつかの固有ラベルを識別すると、

診断テストモードにおいて、前記自動テスト機器を使用して、i) 第2の一連のスキャンテストパターンを前記自己テストハードウェアに提供し、前記第2の一連のスキャンテストパターンにおけるスキャンテストパターンが前記識別されたラベルに対応し、ii) 生応答データを捕捉するステップと、

を含むことを特徴とする方法。

**【請求項 2】**

それぞれの一連のスキャンテストパターンが、スキャンテストパターンの複数の区間を含み、前記いくつかの欠陥スキャンテストパターンが、スキャンテストパターンのいくつかの欠陥区間に対応するラベルを識別することによって識別されることを特徴とする請求項1に記載の方法。

**【請求項 3】**

前記第1の一連のスキャンテストパターンが、単一の生産テストベクトル内で実行されることを特徴とする請求項1に記載の方法。

**【請求項 4】**

前記ATE(114)が、前記識別したラベルを单一の診断テストベクトルに動的にコンパイルすることを特徴とする請求項1に記載の方法(200)。

**【請求項 5】**

前記自動テスト機器が、前記第2の一連のスキャンテストパターンにおける前記スキャンテストパターンを前記自己テストハードウェアに提供するときに複数の診断テストベクトルを動的に生成し実行することを特徴とする請求項1に記載の方法。

**【請求項 6】**

コンピュータ可読媒体と、

前記コンピュータ可読媒体に記憶され、自動テスト機器に、

電子デバイスの組み込み自己テストハードウェアを生産テストモードにする動作、

第1の一連のスキャンテストパターンを前記自己テストハードウェアに提供する動作、

前記スキャンテストパターンに対応する応答シグネチャを捕捉する動作、

前記捕捉した応答シグネチャを予想応答シグネチャと比較して、いくつかの欠陥スキャンテストパターンを識別する動作、

前記欠陥スキャンテストパターンと関連した固有ラベルの数を識別する動作、

前記自己テストハードウェアを診断テストモードにする動作、

前記自己テストハードウェアに第2の一連のスキャンテストパターンを提供する動作であって、前記第2の一連のスキャンテストパターンにおける前記スキャンテストパターンが前記識別したラベルに対応する動作、および、

前記スキャンテストパターンに対応する生応答データを捕捉する動作、

を実行させるプログラムコードと、

を有することを特徴とする装置。

**【請求項 7】**

それぞれの一連のスキャンテストパターンが、スキャンテストパターンの複数の区間を

10

20

30

40

50

含み、前記プログラムコードが、スキャンテストパターンのいくつかの欠陥区間を識別することによっていくつかの欠陥スキャンテストパターンを識別することを特徴とする請求項6に記載の装置。

【請求項8】

前記プログラムコードが、前記第1の一連のスキャンテストパターンを単一の生産テストベクトル内で実行させることを特徴とする請求項6に記載の装置。

【請求項9】

前記プログラムコードが、前記自動テスト機器に、前記識別したラベルを単一の診断テストベクトルに動的にコンパイルさせることを特徴とする請求項6に記載の装置。

【請求項10】

前記第2の一連のスキャンテストパターンにおけるスキャンテストパターンを前記自己テストハードウェアに提供するときに、前記プログラムコードが前記自動テスト機器に複数の診断テストベクトルを動的に生成させ実行させることを特徴とする請求項6に記載の装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子デバイスにスキャンパターンを提供する方法および装置荷冠するものである。

【背景技術】

【0002】

回路テストは、一般に、機能テストと構造テストの2つのクラスに分けることができる。機能テストでは、テスト技術者および/またはソフトウェアが、1)回路が通常の使用中にその入力で受け取り出力で生成する可能性のある刺激と応答をエミュレートし、2)刺激を回路の入力に印加し、3)刺激に対する応答を回路の出力で捕捉し、4)捕捉した応答を予想した応答と比較する。構造テストでは、回路の意図された機能は回路テストの生成にほとんどまたは全く関係がない。より正確に言うと、回路は、組み合せ論理「コア」のまわりにスキャンチェーンを形成するように連結された複数の記憶要素を備える。この場合、回路テストパターンが記憶要素内にシフトされ、そのパターンが論理コア内に開始され、次にテストパターンに対する応答が、スキャンチェーン要素によって捕捉される。次に、捕捉された応答が記憶要素からシフトされ、予想した応答と比較される。様々なテストパターンを使って論理コアを実行することにより、論理コアの構造が存在し適切に接続されていると推測することができる。論理コアの構造が存在し適切に接続されている場合は、設計通りに機能しているはずであると推測することができる。したがって、構造テストは、回路の機能をエミュートする必要もなく機能を理解する必要もなく、その論理を実行するだけでよいという点で有利である。

【0003】

構造テスト用に設計された回路は、一般に、「テスト容易化設計(design-for-test)(DFT)構造を含む。単純なケースでは、DFT構造は、スキャンチェーンを構成するように連結された複数の記憶要素しか含まないことがある。もっと複雑なケースでは、DFT構造は、複数のスキャンチェーンに連結された記憶要素を含むことがあり、すなわち、DFT構造は、1)被テストデバイスに対するスキャンパターンを内部で生成し、2)必要に応じてスキャンパターンに対する応答を収集しそれを1つまたは複数の出力シグナチャに詰め込む組み込み自己テスト(BIST)ハードウェアを含むことがある。

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明は、欠陥スキャン区間の識別を容易化することを課題としている。

【課題を解決するための手段】

10

20

30

40

50

## 【0005】

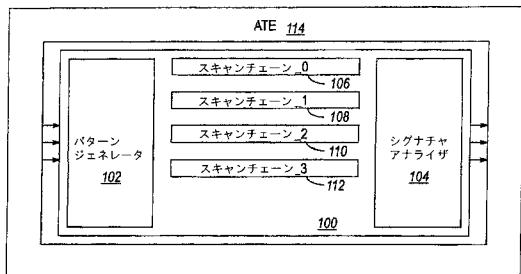

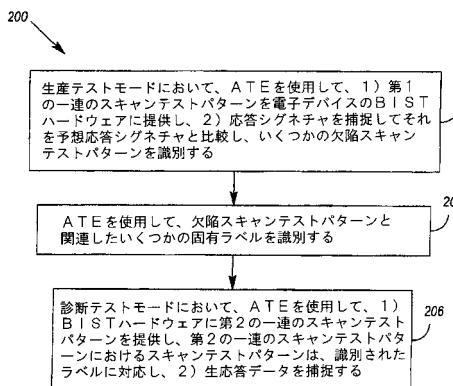

1つの実施形態において、方法は、組み込み自己テスト（BIST）ハードウェアを有する電子デバイスにスキャンパターンを提供する。BISTハードウェアは、生産テストモードと診断テストモードを有し、電子デバイスは、生産テストモードで1つまたは複数の応答シグネチャを出力し、診断テストモードで生応答データを出力する。生産テストモードにおいて、この方法は、自動テスト機器（ATE）を使用して、1) 第1の一連のスキャンテストパターンをBISTハードウェアに提供し、2) 応答シグネチャを捕捉しそれを予想応答シグネチャと比較して、いくつかの欠陥スキャンテストパターンを識別する。次に、方法は、ATEを使用して欠陥スキャンテストパターンと関連したいいくつかの固有ラベルを識別する。診断テストモードにおいて、方法は、ATEを使用して、1) 第2の一連のスキャンテストパターンをBISTハードウェアに提供し、2) 生応答データを捕捉する。スキャンテストパターンの第2の一連のスキャンテストパターンは、識別されたラベルに対応する。10

## 【0006】

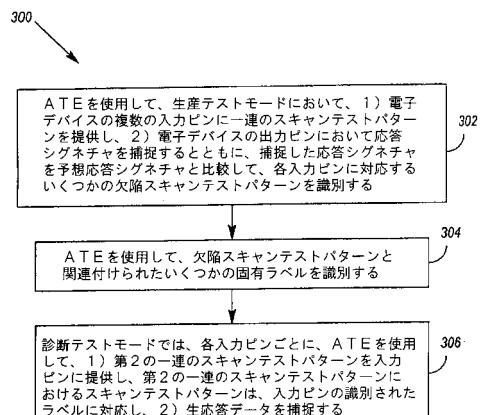

もう1つの実施形態において、方法は、スキャンパターンを電子デバイスの入力ピンに提供する。各入力ピンは、生産テストモードと診断テストモードを有する組み込み自己テスト（BIST）ハードウェアと関連付けられている。生産モードにおいて、電子デバイスは、装置の出力ピンに1つまたは複数の応答シグネチャを出力し、診断テストモードにおいて、装置は、出力ピンに生応答データを出力する。生産テストモードにおいて、この方法は、ATEを使用して、1) 装置の入力ピンに一連のスキャンテストパターンを提供し、2) 装置の出力ピンにおいて応答シグネチャを捕捉する。次に、捕捉した応答シグネチャを予想応答シグネチャと比較して、各入力ピンに対応するいくつかの欠陥スキャンテストパターンを識別する。次に、方法は、ATEを使用して、欠陥スキャンテストパターンと関連したいいくつかの固有ラベルを識別する。診断テストモードにおいて、各入力ピンごとに、方法は、ATEを使用して、1) 第2の一連のスキャンテストパターンを入力ピンに提供し、2) 生応答データを捕捉する。第2の一連のスキャンテストパターンのスキャンテストパターンは、入力ピンの識別されたラベルに対応する。20

## 【発明を実施するための最良の形態】

## 【0007】

他の実施形態も開示する。本発明の実例となる現在好ましい実施形態を図面に示す図である。30

## 【0008】

回路および詳細にはシステムオンチップ（SOC）に組み込まれることがある1つのDFT構造は、Synopsis, Inc.（米国カリフォルニア州マウンテンビュー）によって提供されているDBIST構造などの決定論的(deterministic)BIST構造である。

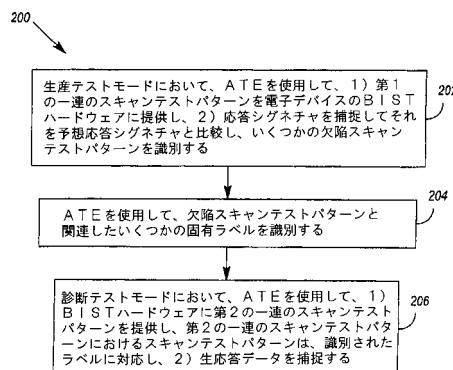

## 【0009】

図1に、決定論的BIST構造を含むSOC100を示す。例えば、決定論的BIST構造は、パターンジェネレータ102とシグナチャアナライザ104を含む。パターンジェネレータ102とシグナチャアナライザ104の間には、複数のスキャンチェーン106、108、110、112が結合されている。使用する際、外部で生成されたスキャン「シード」（すなわち、ATE114によって提供されたシード）が、パターンジェネレータ102に提供される。次に、パターンジェネレータ102は、そのシードを複数のスキャンパターンを生成する基準として使用し、スキャンパターンは様々なスキャンチェーン106～112内にシフトされる。スキャンチェーン106～112からのパターンを開始した後で、パターンに対する応答がスキャンチェーン106～112を介して捕捉され、シグナチャアナライザ104にシフトされる。決定論的BISTでは、シグナチャアナライザ104は、何十万ものシフトされたビットを128ビットシグナチャに変換することができる多入力シフトレジスタ（MISR）を含むことがある。40

## 【0010】

10

20

30

40

50

決定論的BIST構造は、生産テストモードと診断テストモードを含むいくつかのモードで動作することができる。生産テストモードでは、SOCのスキャンチェーン106～112が、図1に示したように、決定論的BISTパターンジェネレータ102とシグナチャアナライザ104の間に結合されている。診断テストモードでは、SOCのスキャンチェーン106～112は、パターンジェネレータ102に結合されるが、シグナチャアナライザ104から切り離されている（すなわち、その出力がシグナチャアナライザ104をバイパスする）。したがって、診断テストモードでは、スキャンチェーン106～112から生応答データを得ることができる。次に、この生応答データをSOC100の外部でより詳しく解析することができる。

## 【0011】

10

一般に、決定論的BISTハードウェア102、104は、スキャンテストの「第1のパス」の間生産テストモードにされる。この第1のパスの間に、欠陥スキャン区間（filling scan interval）（すなわち、スキャンパターンのグループ）が識別される。第2のパスの間に、決定論的BISTハードウェア102、104が診断テストモードにされ、欠陥区間のスキャンパターンが再実行されることがある。

## 【0012】

20

欠陥区間のスキャンパターンを再実行するために、テスト技術者は、一般に、設計技師から提供される情報を使用して欠陥区間の記憶場所を手作業で識別しなければならなかった。その場合、テスト技術者は、ベクトルデータを処理して欠陥区間を再実行しなければならず、またテスタメモリ制限を超えないようにしなければならなかった（すなわち、大量の生応答データがテスタメモリ制限を超えることがあるので）。これらのほとんど手作業の工程は、時間がかかり誤りが起きやすく、生産テストの際に大きな遅延と破壊を引き起こす可能性がある。したがって、図2は、図1に示したようなBISTハードウェアを有する電子デバイスにスキャンパターンを提供する新しい方法を示す。

## 【0013】

30

方法200は、次のように進行する。生産テストモードにおいて、自動テスト機器（ATE）を使用して、1) 第1の一連のスキャンテストパターンを電子デバイスのBISTハードウェアに提供し、2) 応答シグネチャを捕捉しそれを予想応答シグネチャと比較する202。次に、比較の結果を使用して、いくつかの欠陥スキャンテストパターンを識別することができる。次に、ATEを使用して、欠陥スキャンテストパターンと関連したいくつかの固有ラベルを識別する204。診断テストモードにおいて、ATEを使用して、1) BISTハードウェアに第2の一連のスキャンテストパターンを提供し、2) 生応答データを捕捉する206。第2の一連のスキャンテストパターンにおけるスキャンテストパターンは、識別されたラベルに対応する。

## 【0014】

40

方法200の1つの実施形態において、それぞれの一連のスキャンテストパターンは、スキャンテストパターンの複数の区間を含むことができる（例えば、Synopsys社のDBISTの場合のように）。次に、スキャンテストパターンのいくつかの欠陥区間に対応するラベルを識別することによって、いくつかの欠陥スキャンテストパターンを識別することができる。

## 【0015】

例えばそれぞれの様々なスキャンパターン（または、スキャンパターンの区間）を別々に記憶することによって、様々なスキャンパターンまたは様々なスキャンパターンの様々な区間と固有のラベルを関連付けることができる。このようにして、BISTハードウェアが生産テストモードか診断テストモードかに関係なく、スキャンパターンの様々なベクトルを同じテストパターンからコンパイルすることができる。各区間ごとにラベルを提供するだけだが、ラベルをさらに細かく細分することにより（すなわち、各スキャンパターンごとのラベル）、生産テストの時間とメモリをより効率的に使用することができる。

## 【0016】

50

場合によっては、生産テストモードの際に電子デバイスに提供される一連のスキャンテストパターンは、単一の生産テストベクトル内で実行されることがある（例えば、「バースト」モードで）。この場合、診断テストモードにおいて、ATEは、複数の診断テストベクトルを動的に生成し実行することもあり（例えば、「アンバースト（unburst）」モードでは各識別ラベルごとのベクトル、またはATEのメモリ制限内に収まる生応答データが作成されるラベルのグループのベクトル）、あるいは、ATEは、識別したラベルを単一の診断テストベクトルに動的にコンパイルすることもある（例えば、「バースト」モードで）。

#### 【0017】

例えば、方法200によって使用されるATEは、Agilent Technologies, Inc.（カリフォルニア州パロアルト）から提供されている93000S0Cテスタなどのシステムオンチップ（SOC）テスタでよい。しかしながら、93000SOCテスタが、データを並列に複数の装置ピンに提供し複数の装置ピンから収集できる場合は、方法300の方が93000SOCテスタの機能を利用するのに適している場合がある。

#### 【0018】

方法300は、以下のように動作する。ATEを使用して、生産テストモードにおいて、1)電子デバイスの複数の入力ピンに一連のスキャンテストパターンを提供し、2)電子デバイスの出力ピンにおいて応答シグネチャを捕捉する302。次に、捕捉した応答シグネチャを予想応答シグネチャと比較して、各入力ピンに対応するいくつかの欠陥スキャンテストパターンを識別する。次に、ATEを使用して、欠陥スキャンテストパターンと関連付けられたいいくつかの固有ラベルを識別する304。診断テストモードでは、各入力ピンごとに、ATEを使用して、1)第2の一連のスキャンテストパターンを入力ピンに提供し、2)生応答データを捕捉する306。第2の一連のテストパターンのスキャンテストパターンは、入力ピンの識別されたラベルに対応する。

#### 【0019】

方法300の1つの実施形態において、それぞれの一連のスキャンテストパターンは、スキャンテストパターンの複数の区間を含むことができる（例えば、Synopsys社のDBISTのような）。次に、スキャンテストパターンの欠陥区間に応するいくつかのラベルを識別することによって、いくつかの欠陥スキャンテストパターンを識別することができる。

#### 【0020】

いくつかの場合は、生産テストモードの間に入力ピンに提供される一連のスキャンテストパターンが、単一の生産テストベクトル内で実行されることがある。他の場合は、電子デバイスの入力ピンに提供される一連のすべてのスキャンテストパターンが単一の生産テストベクトル内で実行されることがある。

#### 【0021】

診断テストモードが終わると、ATEは、装置の各入力ピンごとに複数の診断テストベクトルを動的に生成し実行することができる。例えば、ATEは、識別されたラベルごとのベクトルを実行したり、ATEのメモリ制限内に収まる生応答データが作成されるラベルのグループのベクトルを実行したりすることができる。代替として、ATEは、識別したラベルを、各ピンごとの単一の診断テストベクトルまたは装置の単一の診断テストベクトルに動的にコンパイルすることができる。

#### 【0022】

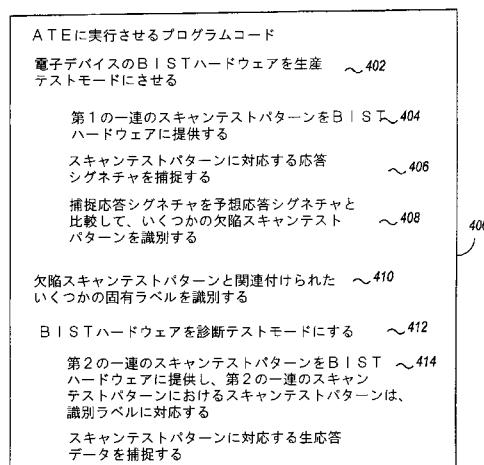

方法200、300はいずれも、その変形を含み、（固定式か取り外し式かに関係なく）メモリやディスクなどのコンピュータ可読媒体400に記憶されたプログラムコード402～414で実施することができる。本明細書において、「メモリ」は、統合メモリ構造あるいは分散型または機能固有のメモリ構造を両方とも対象として含むように解釈されることに注意されたい。例えば、93000SOCテスタは、93000SOCテスタの各ピンごとのベクトルとシーケンサ（すなわち、プログラム命令）をそれぞれ記憶するた

10

20

30

40

50

めに、ピンごとのベクトルとシーケンサメモリに分割されたメモリ構造を含む。

#### 【0023】

方法200の場合、プログラムコードは、ATEに電子デバイスのBISTハードウェアを生産テストモードにさせる402プログラムコードを含むことができる。次に、BISTハードウェアが生産テストモードの間、プログラムコードは、ATEに、1)第1の一連のスキャンテストパターンを前記BISTハードウェアに提供させ404、2)スキャンテストパターンに対応する応答シグネチャを捕捉させ406、3)捕捉応答シグネチャを予想応答シグネチャと比較させていくつかの欠陥スキャンテストパターンを識別させる408。次に、プログラムコードは、欠陥スキャンテストパターンと関連付けられにくつかの固有ラベルを識別することができる410。その後、プログラムコードは、ATEに装置のBISTハードウェアを診断テストモードにさせることができる412。BISTハードウェアが診断テストモードの間、プログラムコードは、ATEに、1)第2の一連のスキャンテストパターンをBISTハードウェアに提供させ414、2)スキャンテストパターンに対応する生応答データを捕捉させる416ことができる。前に述べたように、第2の一連のスキャンテストパターンにおけるスキャンテストパターンは、欠陥スキャンテストパターンと関連付けられたラベルによって識別されるものに対応することができる。10

#### 【0024】

方法200の他の特徴および変形、ならびに方法300の特徴および変形は、同じようにプログラムコードで実施することができる。20

#### 【図面の簡単な説明】

#### 【0025】

【図1】BISTハードウェアを含む例示的なシステムオンチップ(SOC)ならびにSOCをテストする自動テスト機器を示す図である。

【図2】図1に示したようなBISTハードウェアを有する電子デバイスにスキャンパターンを提供する例示的な方法を示す図である。

【図3】いくつかの入出力ピンのそれぞれと関連付けられたBISTハードウェア(図1に示したような)を有する電子デバイスにスキャンパターンを提供する例示的な方法を示す図である。

【図4】図2に示したような方法を実行させるためにコンピュータ可読媒体に記憶することができる例示的なプログラムコードを示す図である。30

#### 【符号の説明】

#### 【0026】

100 SOC

102 パターンジェネレータ

104 シグナチャアナライザ

106、108、110、112 スキャンチェーン

114 ATE

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ドメニコ・キンダーモ

イタリア国, 00151 ローマ, ヴィア・コッリ・ポルトゥエンシ 100

(72)発明者 アリアドネ・サラジアニス

アメリカ合衆国ペンシルヴァニア州18017, メリヴェイル・ロード 856

F ターム(参考) 2G132 AB01 AC03 AC04 AC14 AG01 AG11 AK23 AK29