(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5119020号

(P5119020)

(45) 発行日 平成25年1月16日(2013.1.16)

(24) 登録日 平成24年10月26日(2012.10.26)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| G09F 9/30 (2006.01)   | GO9F 9/30 338 |

| G02F 1/1362 (2006.01) | GO2F 1/1362   |

| G02F 1/1365 (2006.01) | GO2F 1/1365   |

| H01L 41/09 (2006.01)  | H01L 41/08 U  |

請求項の数 3 (全 21 頁)

(21) 出願番号 特願2008-73172 (P2008-73172)

(22) 出願日 平成20年3月21日 (2008.3.21)

(65) 公開番号 特開2008-268925 (P2008-268925A)

(43) 公開日 平成20年11月6日 (2008.11.6)

審査請求日 平成23年3月15日 (2011.3.15)

(31) 優先権主張番号 特願2007-78558 (P2007-78558)

(32) 優先日 平成19年3月26日 (2007.3.26)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100103159

弁理士 加茂 裕邦

(72) 発明者 本田 達也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 佐藤 久則

最終頁に続く

(54) 【発明の名称】スイッチ素子及びその作製方法並びに当該スイッチ素子を有する表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

一定の電位が印加される第1の電極と、

前記第1の電極と近接して設けられた第2の電極と、

前記第1の電極上に圧電材料で形成されたスペーサ層を介して設けられ、且つ前記第2の電極と空隙をもって架設された第3の電極と、

前記第2の電極と電気的に接続された画素電極とを有し、

前記第3の電極に前記第1の電極と異なる電位又は概略同一の電位を印加して、前記スペーサ層を伸縮させることにより、前記第2の電極と前記第3の電極との接触状態及び非接触状態を選択可能とすることを特徴とする表示装置。

10

## 【請求項2】

請求項1において、

前記第3の電極に前記第1の電極と異なる電位を印加することにより、前記第2の電極と前記第3の電極を接触状態とし、

前記第3の電極に前記第1の電極と概略同一の電位を印加することにより、前記第2の電極と前記第3の電極を非接触状態とすることを特徴とする表示装置。

## 【請求項3】

請求項1又は請求項2において、

前記圧電材料は、水晶(SiO<sub>2</sub>)でなる膜、チタン酸ジルコン酸鉛(PZT)膜、ニオブ酸リチウム(LiNbO<sub>3</sub>)膜、チタン酸バリウム(BaTiO<sub>3</sub>)膜、チタン酸鉛(

20

PbTiO<sub>3</sub>) 膜、メタニオブ酸鉛 (PbNb<sub>2</sub>O<sub>6</sub>) 膜、又は酸化亜鉛 (ZnO) 膜のいずれか一を有することを特徴とする表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチ素子及びその作製方法並びにスイッチ素子を有する表示装置に関し、特にメカニカルスイッチを有する表示装置に関する。

【背景技術】

【0002】

近年、液晶パネル等を用いた表示装置は、高精細化のために薄膜トランジスタ (TFT) を用いたアクティブ駆動型が多く用いられている。アクティブ駆動型では、各画素電極の電位を独立して制御でき、パッシブ駆動型のように隣接した画素に電界が漏れるといったクロストークがないため表示むらが少なくコントラスト比の高いパネルを作製することが可能である。

【0003】

しかし、アクティブ駆動は画素電極の電位のオン / オフのスイッチングを TFT を用いて電気的に行うため、オフ状態でもオフ電流（漏れ電流）が流れ、完全なオフ状態を保持することが難しいといった問題がある。オフ電流が生じると画素電極の電位を保持することが困難になるため、新たに保持容量を設けることが必要となる。また、オフ電流が高いほど保持容量も大きくする必要があり、その結果、駆動周波数の低下やフリッカ等の画面のちらつきの問題が生じる。また、保持容量に余分な電荷を供給する必要があるため消費電力が上昇してしまう。

【0004】

上述した問題を解決するために、スイッチ素子としてメカニカルスイッチを用いた構成の表示装置が提案されている（例えば、引用文献 1、引用文献 2）。メカニカルスイッチは、トランジスタ等のスイッチ素子の代わりとして、固定された板バネを静電気力により変位させ、板バネの先端部に設けられた導電膜（上部電極）と画素電極等の導電膜（下部電極）との接触又は非接触により動作する。他にも、圧電素子を収縮させることにより、上部電極と画素電極の接触又は非接触動作を行う表示装置が提案されている（例えば、引用文献 3）。

【0005】

【特許文献 1】特開平 9 - 92909 号公報

【特許文献 2】特開 2000 - 35591 号公報

【特許文献 3】特開平 11 - 174994 号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、スイッチ素子として片側が固定された板状の構造で設けた場合（引用文献 1）、スイッチ素子のスイッチ動作（上部電極と下部電極の接触又は非接触動作）時に応力が局所的に集中するため、スイッチ素子の破損が問題となる。また、支持台を用いて可撓薄膜及び導電膜を反らせて接触又は非接触動作を行う場合（引用文献 2）も、可撓薄膜の特定の部分に応力が生じるため素子の耐性が問題となる。また、空隙をある程度広く設ける必要があるため、スイッチ素子の微細化が困難となる。

【0007】

また、引用文献 3 に示されている圧電スイッチの構成は、スイッチ素子がオフの状態（上部電極と画素電極とが非接触の状態）であっても、下部電極となる信号線の変化に伴い圧電素子に電位差が生じるため、スイッチ素子を完全にオフすることができず誤動作のおそれがある。特に、上部電極と画素電極間との間に設けられた空隙（ギャップ）が小さい場合には、誤動作するおそれが顕著となる。

10

20

30

40

50

**【 0 0 0 8 】**

一方、誤動作を防止するためにギャップを大きくした場合、オンの状態とするために上部電極と下部電極との電位差を大きくする必要がありスイッチ素子の消費電力が増加する。この場合、さらに上部電極に接続された配線と下部電極に接続された配線の電位差も大きくなるため、配線が交差する部分においてリーク電流が生じる可能性がある。その結果、消費電力の上昇だけでなく圧電素子に印加される電圧が低下することにより表示不良が生じるおそれがある。

**【 0 0 0 9 】**

本発明は、上記問題に鑑み、スイッチ動作を繰り返し行う場合であっても十分な耐性を有し、微細化や低消費電力化にも対応しうるスイッチ素子及びその作製方法並びに当該スイッチ素子を有する表示装置を提供することを課題とする。

10

**【課題を解決するための手段】****【 0 0 1 0 】**

本発明のスイッチ素子の一は、一定の電位が印加される第1の電極と、第1の電極と近接して設けられた第2の電極と、第1の電極上に設けられ、第2の電極と空隙をもって架設された第3の電極とを有し、第1の電極と第3の電極との間には、圧電材料で形成されたスペーサ層を有し、第3の電極に第1の電極と異なる電位又は概略同一の電位を印加して、スペーサ層を伸縮させることにより、第2の電極と第3の電極との接触状態及び非接触状態を選択可能とする。

**【 0 0 1 1 】**

20

本発明のスイッチ素子の一は、上記構成において、第3の電極に第1の電極と異なる電位を印加することにより第2の電極と第3の電極を接触状態とし、第3の電極に第1の電極と概略同一の電位を印加することにより第2の電極と第3の電極を非接触状態とする。

**【 0 0 1 2 】**

また、本発明の表示装置の一は、一定の電位が印加される第1の電極と、第1の電極と近接して設けられた第2の電極と、第1の電極上に設けられ、第2の電極と空隙をもって架設された第3の電極と、第2の電極と電気的に接続された画素電極とを有し、第1の電極と第3の電極との間には、圧電材料で形成されたスペーサ層を有し、第3の電極に第1の電極と異なる電位又は概略同一の電位を印加して、スペーサ層を伸縮させることにより、第2の電極と第3の電極との接触状態及び非接触状態を選択可能とする。

30

**【 0 0 1 3 】**

また、本発明の表示装置の一は、上記構成において、第3の電極に第1の電極と異なる電位を印加することにより第2の電極と第3の電極を接触状態とし、第3の電極に第1の電極と概略同一の電位を印加することにより第2の電極と第3の電極を非接触状態とする。

**【 0 0 1 4 】**

本発明のスイッチ素子の作製方法の一は、基板上に第1の導電膜と第2の導電膜を形成し、第1の導電膜及び第2の導電膜を覆ってスペーサ層を形成し、スペーサ層に選択的に開口部を形成して少なくとも第2の導電膜の一部を露出させ、スペーサ層上の部及び露出した第2の導電膜上に犠牲層を形成し、犠牲層を覆って第3の導電膜を形成し、犠牲層を除去することにより、開口部において第2の導電膜と第3の導電膜の間に空隙を形成する。

40

**【 0 0 1 5 】**

また、本発明のスイッチ素子の作製方法の一は、基板上に第1の導電膜と第2の導電膜を形成し、第1の導電膜及び第2の導電膜を覆ってスペーサ層を形成し、スペーサ層に選択的に開口部を形成して少なくとも第2の導電膜の一部を露出させ、開口部に導電体を形成し、スペーサ層及び導電体を覆って第3の導電膜を形成し、熱処理により導電体を凝集させ導電体と第3の導電膜との間に空隙を形成する。

**【発明の効果】****【 0 0 1 6 】**

本発明によれば、導電膜間に設けられた絶縁膜の伸縮によりスイッチ動作（接触又は非接

50

触動作)を行うため、スイッチ素子の一部分に集中して応力が生じることがないため素子の破損を抑制することができる。また、導電膜間に設けられた絶縁膜の上下方向における伸縮を利用するため、空隙104を広く設ける必要がなくスイッチ素子を微細に設けることが可能となる。さらに、本発明は、スイッチ素子がオフ状態の際に上部電極となる導電膜と下部電極となる導電膜との電位差が一定であるため、スイッチ素子を低い消費電力で駆動させた場合であっても、スイッチ素子の誤動作を抑制することができる。

#### 【発明を実施するための最良の形態】

##### 【0017】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態および詳細を変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。10

##### 【0018】

###### (実施の形態1)

本実施の形態では、本発明のスイッチ素子及び当該スイッチ素子を有する表示装置について図面を参照して説明する。

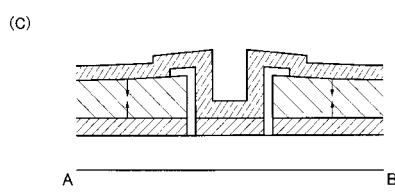

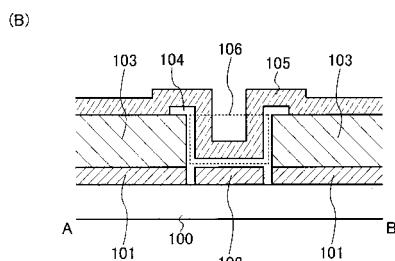

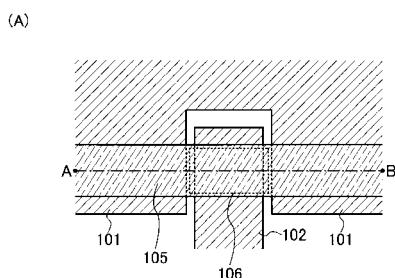

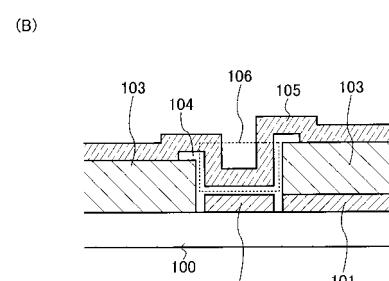

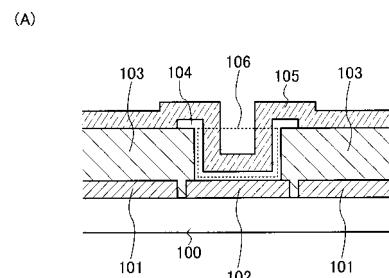

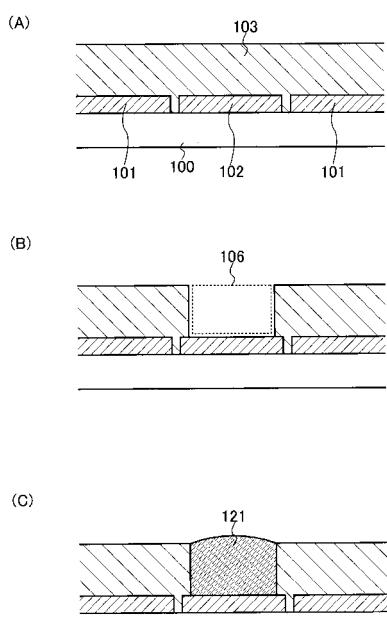

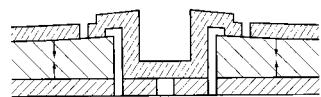

##### 【0019】

まず、スイッチ素子に関して図1を参照して説明する。なお、図1(A)はスイッチ素子の上面図を示しており、図1(B)、(C)は図1(A)におけるA-B間の断面図を示している。20

##### 【0020】

スイッチ素子は、基板100上に設けられた第1の導電膜101及び第2の導電膜102と、スペーサ層として機能する絶縁膜103と、空隙104と、第3の導電膜105とを有している(図1(A)、(B)参照)。スイッチ素子において、第1の導電膜101は第1の電極(下部電極)として機能し、第3の導電膜105は第3の電極(上部電極)として機能する。また、第2の導電膜102は第3の電極と接触又は非接触する第2の電極として機能する。

##### 【0021】

第1の導電膜101と第2の導電膜102は、基板100上において互いに近接して設けられており、当該第1の導電膜101と第2の導電膜102の上方に第3の導電膜105が設けられている。絶縁膜103は、少なくとも第1の導電膜101と第3の導電膜105が重畳する領域において、第1の導電膜101と第3の導電膜105の間に設けられている。また、第2の導電膜102と第3の導電膜105が重畳する部分の一部又は全部に絶縁膜103が形成されていない領域(開口部106)が設けられている。30

##### 【0022】

また、第3の導電膜105は、第2の導電膜102と空隙104をもって架設して設けられている。図1では、第3の導電膜105は、開口部106に沿って設けられており、当該開口部106において、第2の導電膜102と第3の導電膜105の間に空隙104が設けられている。また、開口部106において、第3の導電膜105とスペーサ層として機能する絶縁膜103の間にも空隙104が設けられている。40

##### 【0023】

図1に示すスイッチ素子は、絶縁膜103が伸縮して、第2の導電膜102と第3の導電膜105が接触又は非接触動作を行うことによりスイッチとして機能しうる(図1(C))。絶縁膜103の伸縮は、第1の導電膜101と第3の導電膜105との電位を制御することにより、第1の導電膜101及び第3の導電膜105に電荷を誘起させ、その間に設けられた絶縁膜103に圧縮応力を生じさせることにより行うことができる。

##### 【0024】

例えば、第1の導電膜101を一定の電位とし、第3の導電膜105に第1の導電膜1050

1の電位と異なる所定の電位（例えば、 $V_{in}$ ）を加えた場合、絶縁膜103を挟んだ第1の導電膜101と第3の導電膜105に電荷が誘起され、その間に設けられた絶縁膜103に圧縮応力が生じ絶縁膜103が収縮する。その結果、第2の導電膜102と第3の導電膜105とが接触してオンの状態（接触状態）となり、第2の導電膜102を第3の導電膜105の電位 $V_{in}$ と同じ電位とすることができる。

#### 【0025】

オフの状態（非接触状態）とするには、第3の導電膜105の電位を第1の導電膜101の電位と概略同じ電位にすればよい。このとき、絶縁膜103を挟む第1の導電膜101と第3の導電膜105間には電位差が生じないため絶縁膜103に圧縮応力は働くかず、第2の導電膜102と第3の導電膜105は物理的に分離され非接触状態となる。その結果、漏れ電流のない状態とすることができる。10

#### 【0026】

また、オフの状態において、上部電極に相当する第3の導電膜105と下部電極に相当する第1の導電膜101との電位差を一定に保つことによって、スイッチ素子の誤動作を抑制することができる。そのため、第2の導電膜102と第3の導電膜105との空隙104を狭く設けることができるため、スイッチ素子の低消費電力化を図ることができる。10

#### 【0027】

スペーサ層となる絶縁膜103は、電圧を加えた場合に収縮する圧電素子、電歪振動子等の材料で設けるのが好ましい。例えば、水晶（ $SiO_2$ ）でなる膜、チタン酸ジルコン酸鉛（PZT）膜、ニオブ酸リチウム（ $LiNbO_3$ ）膜、チタン酸バリウム（ $BaTiO_3$ ）膜、チタン酸鉛（ $PbTiO_3$ ）膜、メタニオブ酸鉛（ $PbNb_2O_6$ ）膜、酸化亜鉛（ $ZnO$ ）膜等の圧電材料で絶縁膜103を形成することができる。他にも、酸化珪素（ $SiO_x$ ）膜、酸化窒化珪素（ $SiO_xNy$ ）（ $x > y$ ）膜、窒化珪素（ $SiNx$ ）膜、窒化酸化珪素（ $SiN_xOy$ ）（ $x > y$ ）膜、窒化アルミニウム（ $AlNx$ ）膜で絶縁膜103を形成してもよいし、圧電材料とこれらの絶縁膜を組み合わせた多層膜を用いて絶縁膜103を形成してもよい。20

#### 【0028】

例えば、図1の構成において、絶縁膜103の膜厚は $0.1\mu m \sim 10\mu m$ 、開口部106において第2の導電膜102と第3の導電膜105の間隔（ギャップ）は $0.001\mu m \sim 1\mu m$ とすることができる。絶縁膜103の膜厚やギャップは、絶縁膜103の材料の収縮量や第3の導電膜105の電位に基づいて設定すればよい。30

#### 【0029】

このように、導電膜間に設けられた絶縁膜の伸縮によりスイッチ動作（接触又は非接触動作）を行うことにより、スイッチ素子の一部分に集中して応力が生じることがないため素子の破損を抑制することができる。また、接触又は非接触動作を繰り返し行った場合であっても、第5の導電膜152の跳ね返りが小さく素子の劣化を抑制できるため、スイッチ素子の信頼性を向上させることができる。また、絶縁膜103の上下方向における伸縮を利用するため、空隙104を広く設ける必要がなく、スイッチ素子の微細化が可能となる。さらに、スイッチ素子がオフ状態の際に上部電極に相当する導電膜と下部電極に相当する導電膜との電位差を一定とすることにより、スイッチ素子を低い消費電力で駆動させた場合であっても、スイッチ素子の誤動作を抑制することができる。40

#### 【0030】

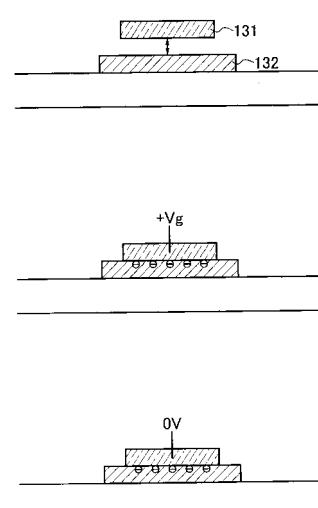

また、本実施の形態で示すスイッチ素子は、従来のメカニカルスイッチと比較して以下の点においても有効となる。

#### 【0031】

従来のスイッチ素子は、上部電極131と下部電極132間に静電気力によりスイッチ動作を行う（図18（A）参照）。例えば、上部電極131に所定の電位（ $+V_g$ ）を印加すると、下部電極132表面に負の電荷が誘起され、上部電極131と下部電極132が静電気力により接触しオンの状態となる（図18（B）参照）。次に、オフの状態（上部電極131と下部電極132を非接触状態）とするために、上部電極131を所定の電位50

(例えば、0V)としても、下部電極132の電位が一定でなく変化する場合には下部電極132から電荷が放出されないため、上部電極131と下部電極132とが接触したままの状態となり、オフの状態とならない問題があった(図18(C)参照)。

#### 【0032】

一方で、本実施の形態で示すスイッチ素子をオフの状態とする場合、下部電極に相当する第1の導電膜101の電位を所定の電位(例えば、Vcom)に保持し、上部電極に相当する第3の導電膜105の電位をVcomとするため、電極に電荷が溜まつたままの状態となることがない。そのため、上述したような問題が生じるおそれがなく、確実にオフの状態とすることができる。

#### 【0033】

なお、本実施の形態で示すスイッチ素子は、図1の構成に限られない。図1では、基板上に並んで配置された第1の導電膜101と第2の導電膜102の間にも空隙104が形成される構成としたが、第1の導電膜101と第2の導電膜102との間及び第2の導電膜102の端部を絶縁膜103で覆った構成としてもよい(図2(A))。また、図1では、第2の導電膜102を挟むように第1の導電膜101を配置した構成を示したが、第2の導電膜102の片側にのみ第1の導電膜101を配置する構成としてもよい(図2(B))。

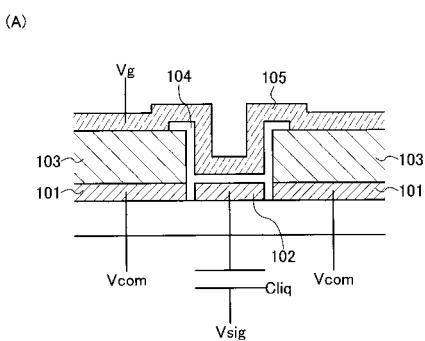

#### 【0034】

次に、図1に示したスイッチ素子を用いた表示装置の駆動方法の一例に関して図3を参照して以下に説明する。図3(A)、(B)は図1に示したスイッチ素子を用いた表示装置の駆動回路の模式図を示している。なお、ここでは、第2の導電膜102に画素電極が接続され、当該画素電極に対向して設けられた対向電極にデータ線が接続された構成について説明する。また、図3では、画素電極と対向電極間に液晶材料が設けられた液晶表示装置に関して説明するが、これに限られない。

#### 【0035】

まず、コモン線として機能しうる第1の導電膜101の電位をコモン線電位Vcomに保持し、ゲート線として機能しうる第3の導電膜105にゲート線電位Vgを与えることによって、スイッチ素子をオンの状態(第2の導電膜102と第3の導電膜105が接触している状態)とする。なお、対向電極にはデータ線電位Vsigを与えておく。

#### 【0036】

この場合、第2の導電膜102に接続された画素電極の電位がVgとなるため、画素電極と対向電極間に設けられた液晶材料には、Vsig - Vgの電位差が生じる。その結果、その電位差に応じて液晶材料の配向が変化する。

#### 【0037】

次に、第3の導電膜105の電位をコモン線電位Vcomと同等とすることにより、第1の導電膜101と第3の導電膜105間の電位差がなくなる(又は、小さくなる)ため、スイッチ素子がオフ状態(第2の導電膜102と第3の導電膜105が非接触の状態)となる。オフ状態において、第2の導電膜102及び画素電極は浮遊状態となるため、次にスイッチ素子がオンの状態となるまで、液晶材料はVsig - Vgの電位差を保持する。

#### 【0038】

このように、スイッチ素子を用いることによって、表示装置に設けられた各画素の液晶材料の配向を制御することができる。また、Vsigを変化させることにより液晶材料に生じる電位差を変化させることによりアナログ階調表示が可能となる。

#### 【0039】

なお、本実施の形態で示したスイッチ素子及び当該スイッチ素子を有する表示装置は、本明細書の他の実施の形態で示したスイッチ素子や表示装置の構成と組み合わせて行うことができる。

#### 【0040】

##### (実施の形態2)

本実施の形態では、上記実施の形態で示したスイッチ素子を具備する表示装置の構成及び

10

20

30

40

50

その作製方法について図面を参照して説明する。

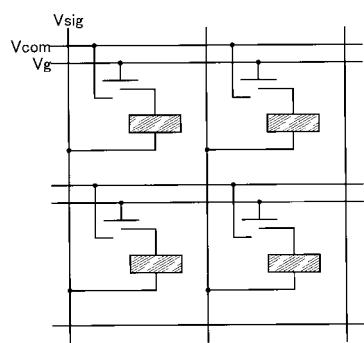

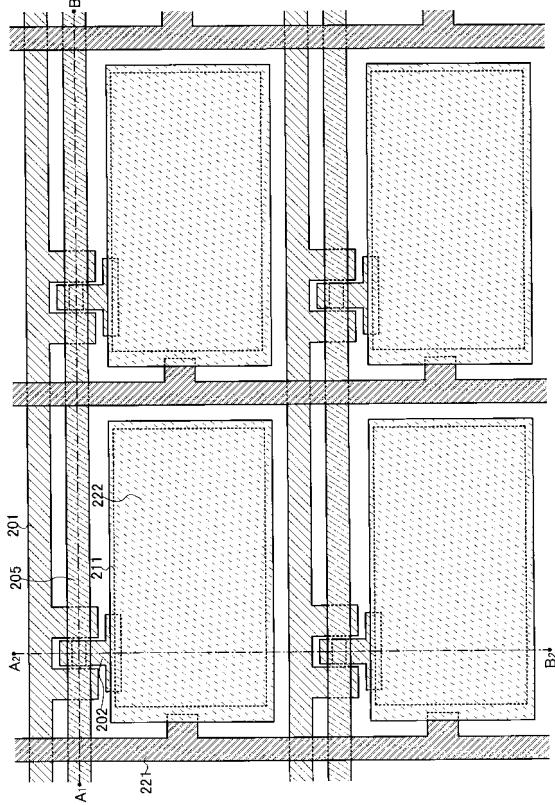

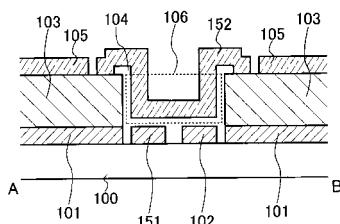

**【0041】**

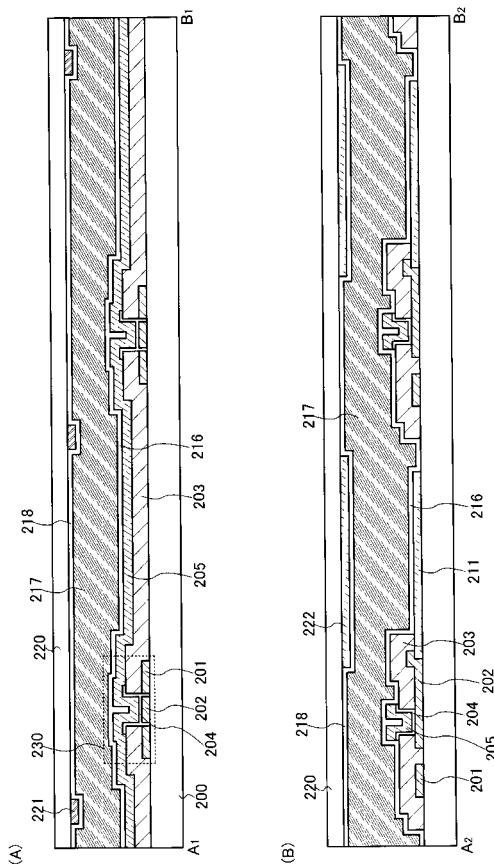

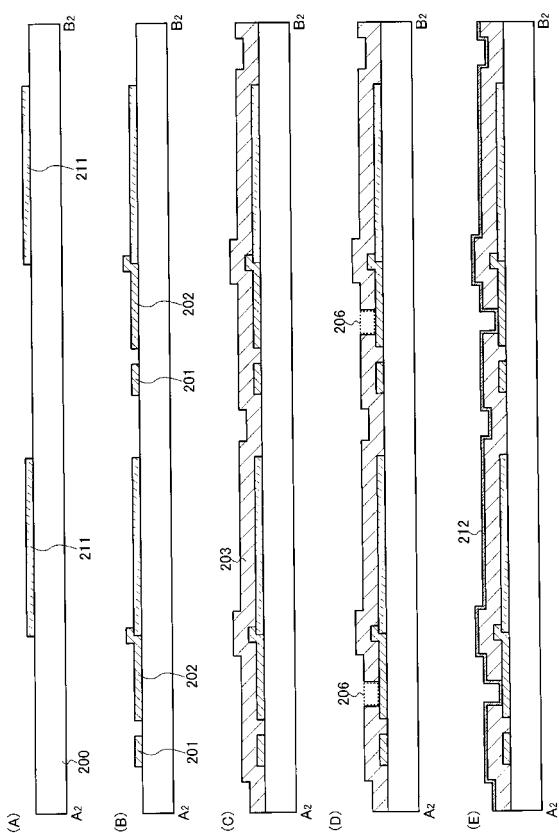

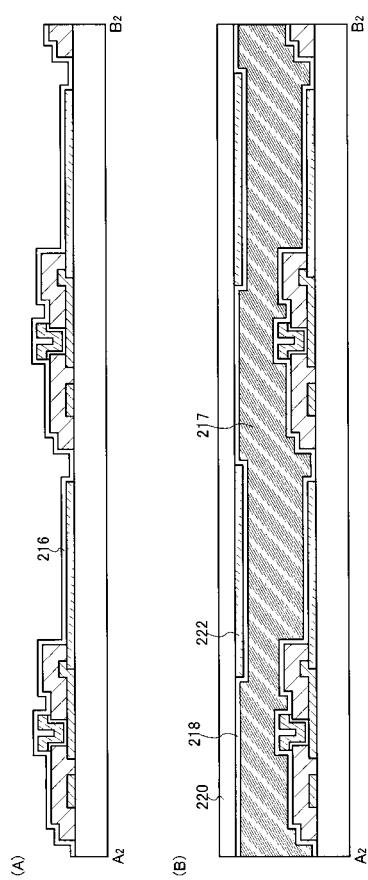

まず、本実施の形態で示す表示装置の構成について図4、図5を参照して説明する。なお、図4は表示装置における画素の上面図を示しており、図5(A)は図4におけるA1-B1間の断面図を示し、図5(B)は図4におけるA2-B2の断面図を示している。

**【0042】**

本実施の形態で示す表示装置は、ゲート線として機能しうる導電膜205と、コモン線として機能しうる導電膜201と、画素電極211と、当該画素電極211に電気的に接続された導電膜202と、データ線として機能しうる導電膜221と、当該導電膜221に電気的に接続された対向電極222を有している(図4参照)。また、導電膜201、導電膜202、絶縁膜203、導電膜205及び空隙204によりスイッチ素子230が構成されている(図5(A)参照)。スイッチ素子230において、導電膜201は第1の電極(下部電極)に相当し、導電膜202は第2の電極に相当し、導電膜205は第3の電極(上部電極)に相当し、絶縁膜203がスペーサ層に相当する。スイッチ素子230の構成は、本明細書における実施の形態で示したいずれかの構成を用いることができる。

10

**【0043】**

導電膜201、導電膜202及び画素電極211は、基板200上に設けられており、当該導電膜202の一部及び導電膜201を覆うように絶縁膜203が設けられている。また、絶縁膜203上に導電膜205が設けられており、導電膜202と導電膜205が重畠する領域の一部又は全部に絶縁膜203が形成されない領域(開口部)が設けられている。

20

**【0044】**

画素電極211を覆うように配向膜216が設けられ、当該配向膜216と対向基板220に設けられた配向膜218との間に液晶材料217が設けられている。なお、対向基板220には導電膜221、対向電極222が設けられており、当該導電膜221及び対向電極222を覆うように配向膜218が設けられている(図5(A)、(B)参照)。

**【0045】**

なお、絶縁膜203は、少なくとも導電膜201と導電膜205が重畠する領域において、当該導電膜201と導電膜205の間に設ければよく、その他の領域に設けない構成としてもよい(図6(A)、(B)参照)。

30

**【0046】**

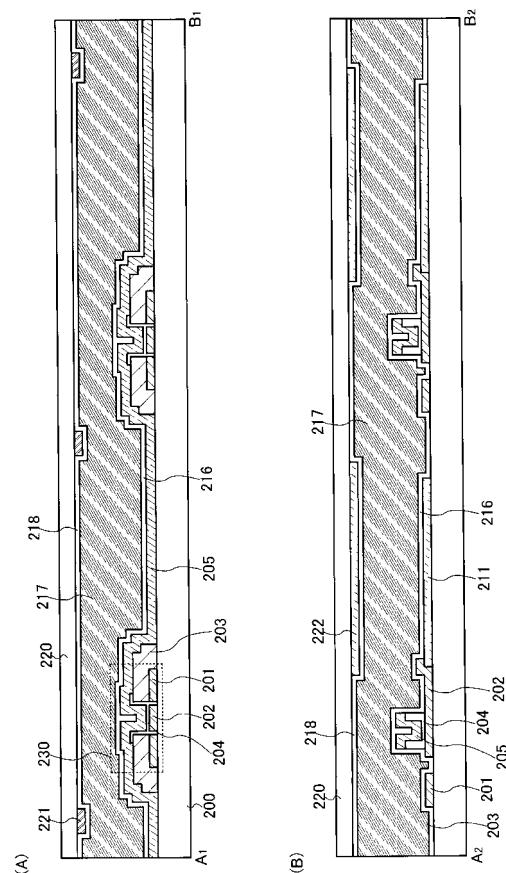

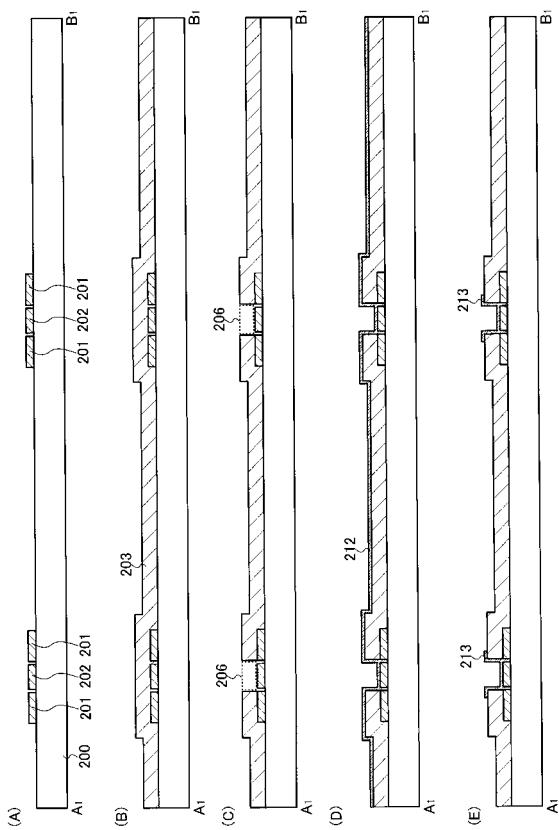

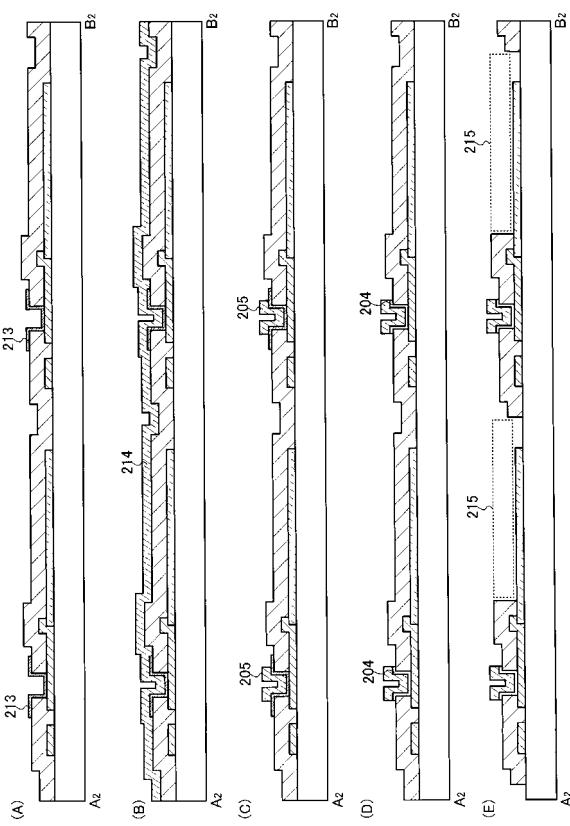

次に、スイッチ素子及び当該スイッチ素子を有する表示装置の作製方法について図面を参照して説明する。なお、以下の説明において、図7、図8は、図4におけるA1-B1間の断面を示しており、図9、図10、図11は、図4におけるA2-B2間の断面を示している。

**【0047】**

まず、基板200上に画素電極211を選択的に形成する(図9(A)参照)。

**【0048】**

基板200は、ガラス基板、石英基板、プラスチック基板等の透光性を有する基板を用いることができる。画素電極211は、酸化インジウムに酸化スズを混ぜたインジウムスズ酸化物(ITO)膜、インジウムスズ酸化物(ITO)に酸化珪素を混ぜたインジウムスズ珪素酸化物膜、酸化インジウムに酸化亜鉛を混ぜたインジウム亜鉛酸化物(IZO)膜、酸化亜鉛膜、または酸化スズ膜等を用いることができる。

40

**【0049】**

次に、基板200上に導電膜201、導電膜202を選択的に形成する(図7(A)、9(B)参照)。導電膜202は、画素電極211と電気的に接続されるように設ける。導電膜201及び導電膜202は、CVD法やスパッタリング法等により全面に導電膜を形成した後に選択的にエッティングすることにより設けてもよいし、液滴吐出法を用いて選択的に設けてもよい。

**【0050】**

50

導電膜 201、導電膜 202 は、アルミニウム (Al)、タンゲステン (W)、チタン (Ti)、タンタル (Ta)、モリブデン (Mo)、ニッケル (Ni)、白金 (Pt)、銅 (Cu)、金 (Au)、銀 (Ag)、マンガン (Mn)、ネオジム (Nd)、炭素 (C)、シリコン (Si) から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。

#### 【0051】

なお、ここでは、画素電極 211 を形成した後に、導電膜 202 を画素電極 211 に電気的に接続するように設ける場合を示したが、導電膜 201 及び導電膜 202 を形成した後に画素電極 211 を形成してもよい。

#### 【0052】

次に、導電膜 201、導電膜 202 及び画素電極 211 を覆うように絶縁膜 203 を形成する (図 7 (B)、9 (C) 参照)。絶縁膜 203 は、後に完成するスイッチ素子においてスペーサ層として機能するため、電圧を加えた場合に収縮する圧電素子等の材料で設けるのが好ましい。そのため、絶縁膜 203 は、水晶 ( $SiO_2$ ) でなる膜、チタン酸ジルコン酸鉛 (PZT) 膜、ニオブ酸リチウム ( $LiNbO_3$ ) 膜、チタン酸バリウム ( $BaTiO_3$ ) 膜、チタン酸鉛 ( $PbTiO_3$ ) 膜、メタニオブ酸鉛 ( $PbNb_2O_6$ ) 膜、酸化亜鉛 ( $ZnO$ ) 膜等で形成することができる。他にも、酸化珪素 ( $SiO_x$ ) 膜、酸化窒化珪素 ( $SiO_xNy$ ) ( $x > y$ ) 膜、窒化珪素 ( $SiNx$ ) 膜、窒化酸化珪素 ( $SiN_xOy$ ) ( $x > y$ ) 膜、窒化アルミニウム ( $AlNx$ ) 膜で形成してもよいし、圧電材料とこれらの絶縁膜を組み合わせた多層膜を用いて形成してもよい。

10

#### 【0053】

次に、導電膜 202 上に設けられた絶縁膜 203 の一部又は全部を選択的にエッチングすることにより、開口部 206 を形成する (図 7 (C)、9 (D) 参照)。開口部 206 は、後に形成されるゲート線として機能しうる導電膜 205 と導電膜 202 が重畠する部分の一部又は全部に少なくとも形成する。

#### 【0054】

次に、開口部 206 における導電膜 202 及び絶縁膜 203 上に犠牲層 212 を形成する (図 7 (D)、9 (E) 参照)。犠牲層とは、後の工程で除去される層を指し、犠牲層を除去することによって空隙が設けられることとなる。犠牲層 212 として金属元素、金属化合物、シリコン、シリコン酸化物、またはシリコン窒化物を有する材料から形成することができる。ここでは、犠牲層 212 として、スパッタリング法により亜鉛酸化物 ( $ZnO_x$ ) 又は亜鉛硫化物 ( $ZnS$ ) を形成する。

30

#### 【0055】

次に、犠牲層 212 を選択的にエッチングすることにより、開口部 206 及びその近傍の絶縁膜 203 上に設けられた犠牲層を残存させるようにエッチングを行う。ここでは、エッチングにより犠牲層 213 を残存させた例を示している (図 7 (E)、10 (A) 参照)。

#### 【0056】

次に、残存させた犠牲層 213 及び絶縁膜 203 上に導電膜 214 を形成する (図 8 (A)、10 (B) 参照)。導電膜 214 は、CVD 法やスパッタリング法等により、アルミニウム (Al)、タンゲステン (W)、チタン (Ti)、タンタル (Ta)、モリブデン (Mo)、ニッケル (Ni)、白金 (Pt)、銅 (Cu)、金 (Au)、銀 (Ag)、マンガン (Mn)、ネオジム (Nd)、炭素 (C)、シリコン (Si) から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。ここでは、アルミニウムを設ける。

40

#### 【0057】

次に、導電膜 214 をエッチングにより選択的に除去する。ここでは、エッチングにより導電膜 205 を残存させた例を示している (図 10 (C) 参照)。なお、本実施の形態では、導電膜 205 を開口部 206 及びその近傍の絶縁膜 203 上に形成した例を示したが、導電膜 205 を絶縁膜 203 の上方に設けない構成としてもよい。

50

**【0058】**

次に、犠牲層213を選択的に除去することにより、犠牲層213が設けられていた部分に空隙204を形成することによって、スイッチ素子230が得られる(図8(B)、10(D)参照)。なお、犠牲層213の除去は、導電膜214の除去と同時にあってよい。例えば、犠牲層213として亜鉛酸化物( $ZnO_x$ )を用い、導電膜214としてアルミニウムを用いた場合、導電膜214の除去にエッティング液(例えば、硝酸( $HNO_3$ )と酢酸( $CH_3COOH$ )とリン酸( $H_3PO_4$ )を含む混酸等)を用いたウェットエッティングを行う。このとき、硝酸( $HNO_3$ )と酢酸( $CH_3COOH$ )とリン酸( $H_3PO_4$ )を含む混酸に対する $ZnO_x$ のエッティング速度はアルミニウムのエッティング速度と比較して非常に早い(約200倍)ため、アルミニウムのエッティングと同時に $ZnO_x$ を除去することができる。10

**【0059】**

次に、画素電極211上に設けられた絶縁膜203を選択的に除去し、開口部215を形成する(10(E)参照)。なお、開口部215は、開口部206の形成と同時に(図7(C)、図9(D))に設けてよい。

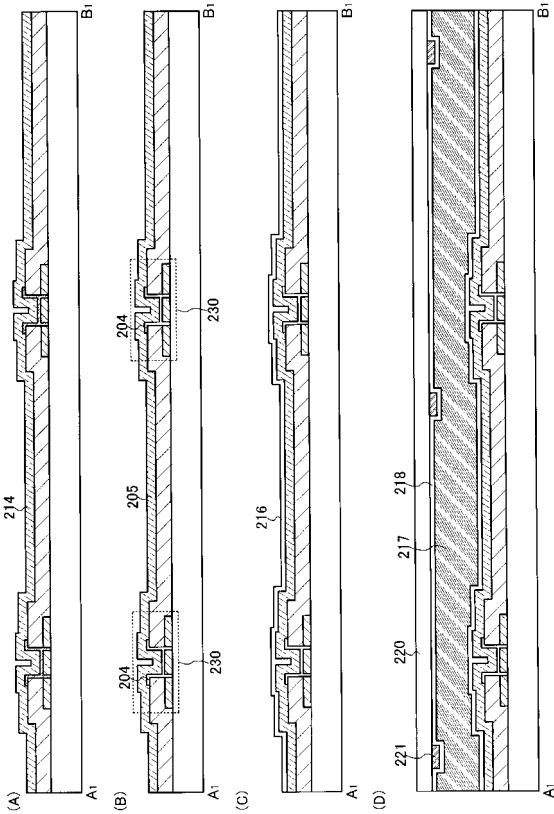

**【0060】**

次に、画素電極211等を覆うように配向膜216を形成する(図8(C)、11(A)参照)。

**【0061】**

次に、あらかじめ導電膜221、対向電極222、配向膜218が設けられた対向基板220を数 $\mu m$ の間隔を持たせて基板200に貼り合わせた後に、基板200と対向基板220間に液晶材料217を注入することにより表示装置をえることができる(図8(D)、11(B)参照)。なお、遮光膜、カラーフィルタ、スペーサ等を設けた対向基板220を用いてよい。また、他の作製方法として、配向膜216を形成した後、スペーサを設け液晶滴下により液晶材料217を形成した後に対向基板220と基板200を貼り合わせて設けてよい。20

**【0062】**

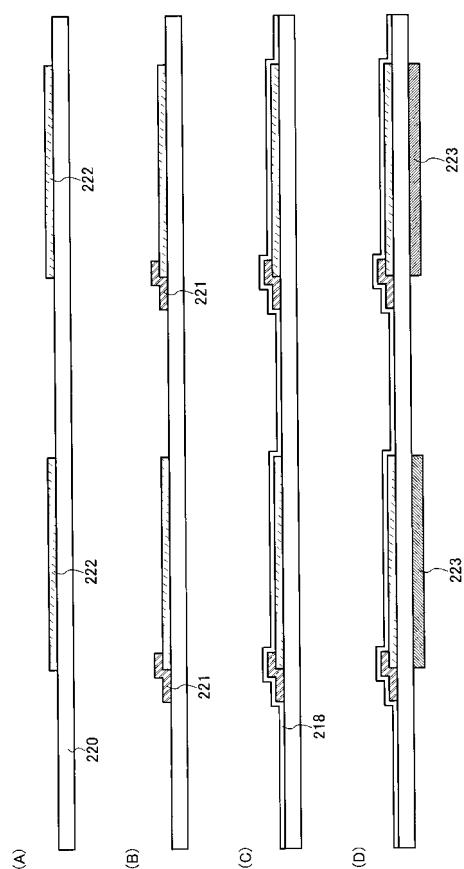

以下に、導電膜221、対向電極222等が設けられた対向基板220の作製方法について図12を参照して説明する。

**【0063】**

まず、対向基板220上に対向電極222を複数形成する(12(A)参照)。対向基板220は、ガラス基板、石英基板、プラスチック基板等の透光性を有する基板を用いることができる。対向電極222は、酸化インジウムに酸化スズを混ぜたインジウムスズ酸化物(ITO)膜、インジウムスズ酸化物(ITO)に酸化珪素を混ぜたインジウムスズ珪素酸化物膜、酸化インジウムに酸化亜鉛を混ぜたインジウム亜鉛酸化物(IZO)膜、酸化亜鉛膜、または酸化スズ膜等を用いることができる。30

**【0064】**

次に、対向基板220上に導電膜221を選択的に形成する。導電膜221は対向電極222と電気的に接続されるように設ける(図12(B)参照)。導電膜221は、表示装置においてデータ線として機能しうる。40

**【0065】**

導電膜221は、CVD法やスパッタリング法等により、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。また、液滴吐出法を用いて形成してもよい。

**【0066】**

なお、ここでは、対向電極222を形成した後に、導電膜221を対向電極222に電気的に接続するように設ける場合を示したが、導電膜221を形成した後に対向電極222

を形成してもよい。

**【0067】**

次に、対向電極222及び導電膜221を覆うように配向膜218を形成する(図12(C)参照)。さらに、対向電極222と重畠するようにカラーフィルタ223を設けてもよい(図12(D)参照)。

**【0068】**

以上の工程を経て、表示装置を得ることができる。

**【0069】**

また、本実施の形態で示した作製方法を用いることによって、薄膜トランジスタ(TFT)を用いた表示装置と比較して、半導体膜の結晶化や不純物元素の導入する工程がないため、作製プロセスの簡略化を図ることができる。その結果、低コストで表示装置を作製することが可能となる。10

**【0070】**

なお、本実施の形態で示したスイッチ素子及び当該スイッチ素子を有する表示装置は、本明細書の他の実施の形態で示したスイッチ素子や表示装置の構成と組み合わせて行うことができる。

**【0071】**

(実施の形態3)

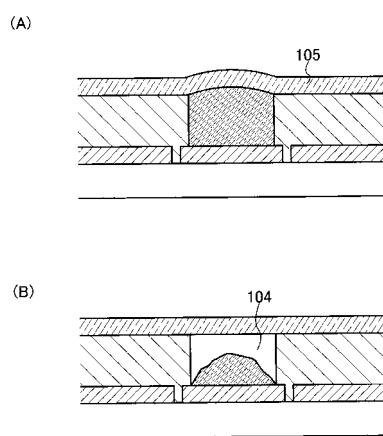

本実施の形態では、上記実施の形態と異なるスイッチ素子の作製方法に関して図面を参照して説明する。具体的には、スイッチ素子の作製方法において、犠牲層を用いずに空隙を形成する場合について説明する。20

**【0072】**

本実施の形態では、凝集により体積が収縮することを利用して空隙を形成する。以下に図13、図14を参照して説明する。

**【0073】**

まず、基板100上に第1の導電膜101、第2の導電膜102を選択的に形成した後、当該第1の導電膜101及び第2の導電膜102を覆うようにスペーサ層となる絶縁膜103を形成する(図13(A)参照)。

**【0074】**

第1の導電膜101、第2の導電膜102は、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。なお、ここでは、第1の導電膜101、第2の導電膜102として、チタン(Ti)を形成する。30

**【0075】**

絶縁膜103は、酸化珪素膜、酸化窒化珪素膜、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム(A1Nx)膜、チタン酸ジルコン酸鉛(PZT)膜、ニオブ酸リチウム(LiNbO<sub>3</sub>)膜、チタン酸バリウム(BaTiO<sub>3</sub>)膜、チタン酸鉛(PbTiO<sub>3</sub>)膜、メタニオブ酸鉛(PbNb<sub>2</sub>O<sub>6</sub>)膜、酸化亜鉛(ZnO)膜等の単層膜又はこれらを組み合わせた多層膜で設ける。ここでは、絶縁膜103として、窒化珪素(SiNx)膜を形成する。40

**【0076】**

次に、少なくとも第2の導電膜102の一部が露出するように絶縁膜103を選択的にエッチングして開口部106を設ける(図13(B)参照)。

**【0077】**

次に、開口部に導電体121を選択的に形成する(図13(C)参照)。導電体121は、銀(Ag)、銅(Cu)、ニッケル(Ni)等の導電性粒子で形成することができる。なお、ここでは、液滴吐出法により、銀(Ag)のナノ粒子を開口部106に選択的に形成する。50

**【0078】**

次に、開口部106に設けられた導電体121を覆うように第3の導電膜105を選択的に形成する(図14(A)参照)。第3の導電膜105は、アルミニウム(Al)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。なお、ここでは、第3の導電膜105として、モリブデン(Mo)を形成する。

**【0079】**

次に、熱処理を行うことにより、導電体121を凝集させることにより導電体121と第3の導電膜105との間に空隙104を形成する(図14(B)参照)。ここでは、200度～600度の窒素雰囲気で熱処理を行い、Agのナノ粒子を覆う有機膜を除去することによって、Agを凝集させる。この際、Agのナノ粒子は第1の導電膜101のチタン(Ti)とは密着性がよいが、第3の導電膜105のモリブデン(Mo)とは密着性が悪いため、Agが凝集し体積が小さくなると導電体121と第3の導電膜105との間に空隙104が形成される。その結果、スイッチ素子を作製することができる。

**【0080】**

本実施の形態で示した作製方法を用いることにより、犠牲層を用いずに空隙を形成できるため作製プロセスの簡略化を図ることができる。

**【0081】**

なお、本実施の形態で示したスイッチ素子の作製方法は、本明細書の他の実施の形態で示したスイッチ素子及びスイッチ素子を有する表示装置の作製方法と組み合わせて行うことができる。

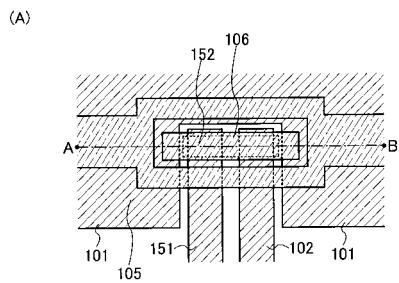

**(実施の形態4)**

本実施の形態では、上記実施の形態で示したスイッチ素子と異なる構成に関して図面を参照して説明する。

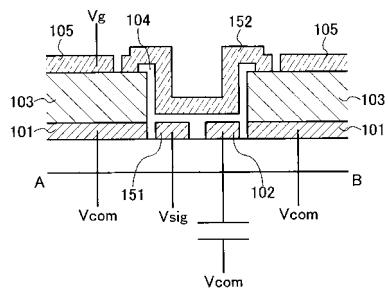

**【0082】**

本実施の形態で示すスイッチ素子は、基板100上に設けられた第1の導電膜101、第2の導電膜102及び第4の導電膜151と、絶縁膜103と、空隙104と、第3の導電膜105と、第5の導電膜152とを有している(図15(A)、(B)参照)。図15に示した構成は図1に示した構成と比較して、データ線として機能しうる第4の導電膜151を第2の導電膜102に並べて配置し、第2の導電膜102及び第4の導電膜151と重畳するように電気的に独立した第5の導電膜152が設けられている点で異なっている。

**【0083】**

具体的には、第1の導電膜101、第2の導電膜102及び第4の導電膜151は、基板100上に並んで配置されており、少なくとも第2の導電膜102及び第4の導電膜151の上方に第5の導電膜152が設けられており、少なくとも第1の導電膜101の上方に第3の導電膜105が設けられている。絶縁膜103は、少なくとも第1の導電膜101と第3の導電膜105の間に設けられており、第2の導電膜102及び第4の導電膜151と、第5の導電膜152とが重畳する部分の一部又は全部に開口部106が設けられている。

**【0084】**

また、開口部106において、第2の導電膜102と第5の導電膜152との間、及び第4の導電膜151と第5の導電膜152との間に空隙104が設けられている。

**【0085】**

図15に示すスイッチ素子は、絶縁膜103が伸縮することにより、第5の導電膜152が第2の導電膜102及び第4の導電膜151と接触又は非接触動作を行うことによりスイッチとして機能しうる(図15(C))。

**【0086】**

10

20

30

40

50

例えば、第1の導電膜101の電位をV<sub>com</sub>、第4の導電膜151の電位をV<sub>sig</sub>とし、第3の導電膜105に電位V<sub>in</sub>(V<sub>in</sub>-V<sub>com</sub>)を加えた場合、絶縁膜103を挟んだ第1の導電膜101と第3の導電膜105に電荷が誘起され、その間に設けられた絶縁膜103に圧縮応力が生じ絶縁膜103が収縮する。その結果、電気的に独立して設けられた第5の導電膜152が第2の導電膜102及び第4の導電膜151と接触し、第2の導電膜102に第4の導電膜151の電位V<sub>sig</sub>が伝わる。

#### 【0087】

このように、導電膜間に設けられた絶縁膜の伸縮によりスイッチ動作(接触又は非接触動作)を行うことにより、スイッチ素子の一部分に集中して応力が生じることがないため素子の破損を抑制することができる。また、接触又は非接触動作を繰り返し行った場合であっても、台5の導電膜152の跳ね返りが小さく素子の劣化を抑制できるため、スイッチ素子の信頼性を向上させることができる。また、絶縁膜103の上下方向における伸縮を利用するため、空隙104を広く設ける必要がなく、スイッチ素子の微細化が可能となる。さらに、スイッチ素子がオフ状態の際に上部電極に相当する導電膜と下部電極に相当する導電膜との電位差を概略一定とすることにより、スイッチ素子を低い消費電力で駆動させた場合であっても、スイッチ素子の誤動作を抑制することができる。

#### 【0088】

次に、図15に示したスイッチ素子を用いた表示装置の駆動方法の一例に関して図16を参考して以下に説明する。図16は図15に示したスイッチ素子を用いた表示装置の駆動回路の模式図を示している。ここでは、第2の導電膜102に画素電極が接続され、当該画素電極に対向して設けられた対向電極は一定の電位(V<sub>com</sub>)を保持している場合について説明する。

#### 【0089】

まず、コモン線として機能しうる第1の導電膜101をコモン線電位V<sub>com</sub>に保持し、ゲート線として機能しうる第3の導電膜105にゲート線電位V<sub>g</sub>を与えることによって、スイッチ素子をオンの状態(第5の導電膜152が第2の導電膜102及び第4の導電膜151と接触している状態)とする。なお、データ線として機能しうる第4の導電膜151にはデータ線電位V<sub>sig</sub>を与えておく。

#### 【0090】

この場合、第2の導電膜102に接続された画素電極には、第5の導電膜152を介して第4の導電膜151からV<sub>sig</sub>が伝わるため、画素電極と対向電極間に設けられた表示素子には、V<sub>com</sub>-V<sub>sig</sub>の電位差が生じる。その結果、表示素子として液晶材料を設けた場合には電位差に応じて液晶の配向が変化する。

#### 【0091】

次に、第3の導電膜105の電位をコモン線電位V<sub>com</sub>と同等とすることにより、スイッチ素子がオフ状態(第5の導電膜152が第2の導電膜102及び第4の導電膜151と非接触の状態)となる。オフ状態において、第2の導電膜102及び画素電極は浮遊状態となるため、次にスイッチ素子がオンの状態となるまで、液晶はV<sub>com</sub>-V<sub>sig</sub>の電位差を保持する。

#### 【0092】

このように、スイッチ素子を用いることによって、表示装置に設けられた各画素の液晶材料の配向を制御することができる。また、V<sub>sig</sub>を変化させることにより液晶材料に生じる電位差を変化させることによりアナログ階調表示が可能となる。

#### 【0093】

なお、上記実施の形態1~3、図16で示した表示装置の構成では、表示素子として液晶材料を用いた場合を示したが、本明細書で説明したスイッチ素子が適用できる表示装置は液晶に限られない。例えば、有機ELや無機ELを表示素子として用いた表示装置にスイッチ素子を適用することも可能である。

#### 【0094】

表示素子として無機EL材料を用いる場合には、駆動電圧が比較的高い(100~200

10

20

30

40

50

V)ためスイッチ素子として薄膜トランジスタ(TFT)を適用した場合には破壊等の問題がある。しかし、本明細書で示したスイッチ素子を適用することにより駆動電圧が高い場合であっても、スイッチ素子の破壊を抑制し、信頼性の高い表示装置を提供することができる。

**【0095】**

また、本明細書で示したスイッチ素子は表示装置に限らず、他にも、DRAM(Dynamic Random Access Memory)等のメモリ素子に適用することができます。この場合、上記実施の形態1~4又は本実施の形態で示した構成において、第2の導電膜102に画素電極の代わりに容量素子を設けることによって、メモリ素子を構成することができる。また、第2の導電膜102に電荷を保持しうる電荷蓄積層を接続し、電荷の蓄積状態の有無によりメモリ素子として適用することが可能となる。10

**【0096】**

なお、本実施の形態で示したスイッチ素子及び当該スイッチ素子を有する表示装置は、本明細書の他の実施の形態で示したスイッチ素子や表示装置の構成と組み合わせて行うことができる。

**【0097】**

(実施の形態5)

本発明は様々な電子機器に適用することができる。具体的には電子機器の表示部に適用することができる。そのような電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうる表示装置を備えた装置)などが挙げられる。20

**【0098】**

図17(A)はテレビ装置であり、筐体301、支持台302、表示部303、スピーカー部304、ビデオ入力端子305等を含む。上記実施の形態で示したスイッチ素子を用いて表示部303を駆動することができる。なお、テレビ装置は、パーソナルコンピュータ用、テレビジョン放送受信用、広告表示用などの全ての情報表示用発光装置が含まれる。30

**【0099】**

図17(B)はカメラであり、本体311、表示部312、受像部313、操作キー314、外部接続ポート315、シャッターボタン316等を含む。上記実施の形態で示したスイッチ素子を用いて表示部312に用いることができる。

**【0100】**

図17(C)はコンピュータであり、本体321、筐体322、表示部323、キーボード324、外部接続ポート325、ポインティングデバイス326等を含む。上記実施の形態で示したスイッチ素子を用いて表示部323を駆動することができる。

**【0101】**

図17(D)はモバイルコンピュータであり、本体331、表示部332、スイッチ333、操作キー334、赤外線ポート335等を含む。上記実施の形態で示したスイッチ素子を用いて表示部332を駆動することができる。40

**【0102】**

図17(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体341、筐体342、表示部A343、表示部B344、記録媒体(DVD等)読み込み部345、操作キー346、スピーカー部347等を含む。表示部A343は主として画像情報を表示し、表示部B344は主として文字情報を表示することができる。上記実施の形態で示したスイッチ素子を用いて表示部A343や表示部B344を駆動することができる。

**【0103】**

図17(F)はゴーグル型ディスプレイであり、本体351、表示部352、アーム部353を含む。本発明の表示装置を表示部352を駆動することができる。

【0104】

図17(G)はビデオカメラであり、本体361、表示部362、筐体363、外部接続ポート364、リモコン受信部365、受像部366、バッテリー367、音声入力部368、操作キー369等を含む。上記実施の形態で示したスイッチ素子を用いて表示部362を駆動することができる。

【0105】

図17(H)は携帯電話機であり、本体371、筐体372、表示部373、音声入力部374、音声出力部375、操作キー376、外部接続ポート237、アンテナ378等を含む。上記実施の形態で示したスイッチ素子を用いて表示部373を駆動することができる。

10

【0106】

このように本発明は、スイッチを具備するあらゆる電子機器に適用することが可能である。

【図面の簡単な説明】

【0107】

【図1】本発明の表示装置のスイッチ素子の構成を示す図。

【図2】本発明の表示装置のスイッチ素子の構成を示す図。

【図3】本発明の表示装置の駆動方法を示す図。

20

【図4】本発明の表示装置の構成を示す図。

【図5】本発明の表示装置の構成を示す図。

【図6】本発明の表示装置の構成を示す図。

【図7】本発明の表示装置の作製方法の一例を示す図。

【図8】本発明の表示装置の作製方法の一例を示す図。

【図9】本発明の表示装置の作製方法の一例を示す図。

【図10】本発明の表示装置の作製方法の一例を示す図。

【図11】本発明の表示装置の作製方法の一例を示す図。

【図12】本発明の表示装置の作製方法の一例を示す図。

【図13】本発明の表示装置の作製方法の一例を示す図。

30

【図14】本発明の表示装置の作製方法の一例を示す図。

【図15】本発明の表示装置のスイッチ素子の構成を示す図。

【図16】本発明の表示装置の駆動方法を示す図。

【図17】本発明の表示装置の使用形態の一例を示す図。

【図18】従来のスイッチ素子の問題点を説明する図。

【符号の説明】

【0108】

100 基板

101 導電膜

102 導電膜

103 絶縁膜

104 空隙

105 導電膜

106 開口部

121 導電体

131 上部電極

132 下部電極

151 導電膜

152 導電膜

200 基板

40

50

|       |             |    |

|-------|-------------|----|

| 2 0 1 | 導電膜         |    |

| 2 0 2 | 導電膜         |    |

| 2 0 3 | 絶縁膜         |    |

| 2 0 4 | 空隙          |    |

| 2 0 5 | 導電膜         |    |

| 2 0 6 | 開口部         |    |

| 2 1 1 | 画素電極        |    |

| 2 1 2 | 犠牲層         |    |

| 2 1 3 | 犠牲層         |    |

| 2 1 4 | 導電膜         | 10 |

| 2 1 5 | 開口部         |    |

| 2 1 6 | 配向膜         |    |

| 2 1 7 | 液晶材料        |    |

| 2 1 8 | 配向膜         |    |

| 2 2 0 | 対向基板        |    |

| 2 2 1 | 導電膜         |    |

| 2 2 2 | 対向電極        |    |

| 2 2 3 | カラーフィルタ     |    |

| 2 3 0 | スイッチ素子      |    |

| 2 3 7 | 外部接続ポート     | 20 |

| 3 0 1 | 筐体          |    |

| 3 0 2 | 支持台         |    |

| 3 0 3 | 表示部         |    |

| 3 0 4 | スピーカー部      |    |

| 3 0 5 | ビデオ入力端子     |    |

| 3 1 1 | 本体          |    |

| 3 1 2 | 表示部         |    |

| 3 1 3 | 受像部         |    |

| 3 1 4 | 操作キー        |    |

| 3 1 5 | 外部接続ポート     | 30 |

| 3 1 6 | シャッターボタン    |    |

| 3 2 1 | 本体          |    |

| 3 2 2 | 筐体          |    |

| 3 2 3 | 表示部         |    |

| 3 2 4 | キーボード       |    |

| 3 2 5 | 外部接続ポート     |    |

| 3 2 6 | ポインティングデバイス |    |

| 3 3 1 | 本体          |    |

| 3 3 2 | 表示部         |    |

| 3 3 3 | スイッチ        | 40 |

| 3 3 4 | 操作キー        |    |

| 3 3 5 | 赤外線ポート      |    |

| 3 4 1 | 本体          |    |

| 3 4 2 | 筐体          |    |

| 3 4 3 | 表示部 A       |    |

| 3 4 4 | 表示部 B       |    |

| 3 4 5 | 部           |    |

| 3 4 6 | 操作キー        |    |

| 3 4 7 | スピーカー部      |    |

| 3 5 1 | 本体          | 50 |

|       |         |

|-------|---------|

| 3 5 2 | 表示部     |

| 3 5 3 | アーム部    |

| 3 6 1 | 本体      |

| 3 6 2 | 表示部     |

| 3 6 3 | 筐体      |

| 3 6 4 | 外部接続ポート |

| 3 6 5 | リモコン受信部 |

| 3 6 6 | 受像部     |

| 3 6 7 | バッテリー   |

| 3 6 8 | 音声入力部   |

| 3 6 9 | 操作キー    |

| 3 7 1 | 本体      |

| 3 7 2 | 筐体      |

| 3 7 3 | 表示部     |

| 3 7 4 | 音声入力部   |

| 3 7 5 | 音声出力部   |

| 3 7 6 | 操作キー    |

| 3 7 8 | アンテナ    |

10

【図1】

【図2】

【 3 】

(B)

【 図 4 】

【 四 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

(B)

(C)

【図16】

【図17】

【図18】

---

フロントページの続き

(56)参考文献 特開平11-174994(JP,A)

特開2000-035591(JP,A)

特開2005-260208(JP,A)

特開2005-302711(JP,A)

特開2005-268297(JP,A)

特表平01-501186(JP,A)

(58)調査した分野(Int.Cl., DB名)

B81B 1/00-7/04、

B81C 1/00-99/00、

G02F 1/1343-1/1345、1/135-1/1368、

G09F 9/00-9/30、9/307-9/46、

H01H 49/00、51/00-59/00、

H01L 27/32、41/00-41/04、

41/06-41/083、41/09-41/26、

51/50、

H05B 33/00-33/28